Table 1. Main Parameters of JHF 50-GeV Main Ring

okVFP系统错误信息

Visual FoxPro 6.0 系统错误信息1 文件不存在。

78 ** 或 ^ 定义域错误。

216 显示方式不可用。

3 文件正在使用。

91 文件没有使用 LOAD 命令装入内存。

221 含缩进值的左页边距必须小于右页边距。

4 已到文件尾。

94 必须指定额外参数。

222 行号必须小于页长。

5 记录超出范围。

95 在交互方式下不能使用此语句。

223 列号必须在 0 到 255 之间。

6 打开的文件太多。

96 嵌套错误。

225 “名称”不是变量。

7 文件已存在。

101 打不开文件。

226 “名称”不是文件变量。

9 数据类型不匹配。

102 不能创建文件“文件”。

227 框大小定义无效。

10 语法错误。

103 超出允许的 DO 嵌套层次。

228 制表位必须按递增顺序。

11 函数参数的值、类型或数目无效。

104 不能识别的功能键。

230 数组维数无效。

12 找不到变量“变量”。

107 操作符/操作数类型不匹配。

231 SET 函数中使用了无效参数。

12 找不到变量“变量”。

108 其他用户正在使用文件。

232 “名称”不是数组。

13 找不到别名。

109 其他用户正在使用记录。

255 不是一个有效的 RapidFile 数据库。

15 不是一个表。

110 文件必须以独占方式打开。

256 不是一个有效的 Framework II 数据库或电子表格。

16 不能识别的命令谓词。

111 不能更新临时表。

279 菜单没有入栈。

17 表编号无效。

112 无效的关键字长度。

287 菜单尺寸太小。

18 行太长。

114 索引与表不匹配。

291 ASIN( ) 中的表达式超出范围。

19 索引文件与表不匹配。

115 .DIF 文件头无效。

292 不能使用 0 或负数作为 LOG10( ) 参数。

20 记录不在索引中。

116 .DIF 矢量无效 - .DBF 字段不匹配。

293 ACOS( ) 中的表达式超出范围。

21 变量字符串的长度超过了内存容量。

D5000系统命令行操作的简化方法

D5000系统平台采用先进的软件开发技术,具有标准、开放、可靠、安全和适应性强等特点,在实际使用过程中,大量系统维护操作需要在命令行方式下完成,本文通过将各种命令制作成Shell脚本程序等方法来简化命令行环境下的操作,为维护人员快速简便维护工作提供了一种方式。

1D5000系统结构D5000运行于国产Linux内核的操作系统之上。

Linux是在GUN 公共许可权限下符合POSIX标准的操作系统,Linux是一种类似UNIX的操作系统,具有和UNIX类似的文件系统、用户接口。

2标准Linux命令2.1Linux命令Linux命令是很重要的工具,所谓命令,是我们在命令行输入的一串字符。

Shell负责理解并执行这些字符串。

Linux系统将命令行分成3个字段:命令名、命令选项和命令参数。

以ls命令为例,“sy1-wh1:/home/d5000/suqian/data/screen_save#ls-l\Desktop”。

ls:命令名,-l:命令选项,\Desktop:命令参数。

2.2Shell简介Shell本身是一种用C语言编写的程序,从用户的角度来看,Shell是用户与Linux操作系统沟通的桥梁。

用户既可以输入命令执行,又可以利用Shell脚本编程,完成更加复杂的操作。

Shell种类众多,常见的有:Bourne Shell、Bourne Again Shell、C Shell、K Shell等,在D5000系统中,默认使用的是Bourne Again Shell。

以导出数据库中某一变电站信息表的操作为例。

操作步骤如下:从数据库中找出“**变**表”,保存显示内容,插入U盘,在Shell中输入命令拷贝内容至U盘sy1-wh1:/home/d5000/suqian/data/screen_save%su口令:sy1-wh1:/home/d5000/suqian/data/screen_save#fdisk-lsy1-wh1:/home/d5000/suqian/data/screen_save#mount/dev/sde1 /mntsy1-wh1:/home/d5000/suqian/data/screen_save#cp众兴变遥测表/mntsy1-wh1:/mnt#umount/mnt可以看出,一个简单的文件拷贝至U盘的过程在D5000系统中都需要进行如此烦琐的操作。

mysqldump命令参数

mysqldump命令参数一、简介mysqldump是MySQL数据库管理系统中的一种备份工具,可以将数据库的结构和数据导出为SQL文件,以便在需要时进行恢复或迁移。

mysqldump命令提供了丰富的参数选项,可以满足不同场景下的备份需求。

本文将介绍一些常用的mysqldump命令参数及其用法。

二、--databases参数--databases参数用于指定要备份的数据库,可以同时备份多个数据库。

语法如下:```mysqldump --databases db1 [db2 db3 ...]```其中,db1、db2、db3等为数据库的名称。

备份时会按照指定的顺序逐个备份各个数据库。

三、--tables参数--tables参数用于指定要备份的表,可以同时备份多张表。

语法如下:```mysqldump --databases db1 --tables table1 [table2 table3 ...]```其中,db1为数据库名称,table1、table2、table3为表的名称。

备份时会按照指定的顺序逐个备份各个表。

四、--where参数--where参数用于指定备份数据的条件,只备份符合条件的数据。

语法如下:```mysqldump --databases db1 --tables table1 --where="condition"```其中,db1为数据库名称,table1为表的名称,condition为备份数据的条件。

备份时只会备份符合条件的数据。

五、--routines参数--routines参数用于备份存储过程和函数。

语法如下:```mysqldump --routines --databases db1```其中,db1为数据库名称。

备份时会将数据库中的存储过程和函数一并备份。

六、--events参数--events参数用于备份事件。

语法如下:```mysqldump --events --databases db1```其中,db1为数据库名称。

matlab2012 readtable用法

MATLAB2012版本引入了readtable函数,用于读取表格数据并将其存储为Table数据类型。

这篇文章将介绍readtable函数的用法及其基本语法,帮助读者更好地理解和使用该函数。

一、readtable函数的基本语法readtable函数的基本语法如下:T = readtable(filename)T = readtable(filename, 'Name1',Value1, 'Name2',Value2, ...)其中,T表示读取到的表格数据存储的Table数据类型变量,filename表示要读取的数据文件名,'Name1',Value1,'Name2',Value2,...表示可选的参数名和参数值。

在不指定参数时,readtable函数会根据默认设置读取数据文件中的全部内容。

二、读取表格数据1. 读取CSV文件使用readtable函数读取CSV文件的基本语法如下:T = readtable('data.csv')其中,'data.csv'为要读取的CSV文件名,读取到的数据将以Table 数据类型存储在变量T中。

2. 读取Excel文件使用readtable函数读取Excel文件的基本语法如下:T = readtable('data.xlsx')其中,'data.xlsx'为要读取的Excel文件名,读取到的数据将以Table 数据类型存储在变量T中。

3. 读取其他格式文件除了CSV和Excel文件,readtable函数还可以读取其他格式的数据文件,例如txt文件、json文件等。

三、指定参数读取数据readtable函数还可以通过指定参数来读取指定范围的数据,指定数据类型等。

常用的参数及其功能如下:1. 'Range'参数使用'Range'参数可以指定读取数据的范围,例如:T = readtable('data.xlsx', 'Range', 'A1:D10')表示只读取Excel文件中A1到D10范围内的数据。

数据库管理器DBMGR参数设置手册

数据库管理器DBMGR参数设置手册脚本执行完成后,开启“电能量系统平台”,就要开始DBMGR的参数设置。

1.如下图,点击“置库界面”。

2.进入数据库管理器的主界面:点击“登录”,先登录系统。

登录界面如下:(密码为201203)图中红框部分,“系统类”和“基础类”在脚本执行以后就已经生成了。

不需要重新设置参数。

需要手动设置的有“网络类”、“权限类”“设备类”“采集类”。

(最后的“SCADA”用一个程序生成,后面再述。

)3.“网络类”的设置,如下图:(1)关于“节点参数表”的说明:“节点”即电脑,节点参数表是设置要连接终端采集设备的电脑的信息。

双击“节点参数表”,点击“添加”右边显示如图:必须填写的有“代码”“描述”“A网地址”“远程节点标志”。

“代码”:本机名,在我的电脑——右键——属性里查看。

“描述”:可随意填写,只是便于识别,可以与“代码”一样。

“A网地址”:本机的IP地址,在网络属性里查看。

“远程节点标志”:一般选“否”。

可添加多个节点,添加完注意保存。

添加完如图:(2)关于“节点服务器对照表”的说明:即添加的节点主要用于做什么事情,比如做数据采集服务器。

如设置刚才添加的节点用作数据采集服务器,双击“数据采集服务器”,点击“添加”,第一个“代码”,下拉菜单中选择添加的节点,如“test”。

第二个“代码”,下拉菜单中选择服务器类型,如“数据采集服务器”。

“优先级”,主要是用来判断主备机的,比如,有2个节点作数据采集服务器,有一个优先级要选0,作为主机,另一个优先级选1,作为备机。

添加完注意保存,如图:综上所述:我们设置了一个节点叫“test”,这个节点用作“数据采集服务器”和“数据处理服务器”。

4.“权限类”设置,如下图:(1)“角色表”:设置系统总共有哪些角色可以操作,一般系统已经设置好,可以根据客户需要修改即可。

如下图:(2)“角色功能表”:设置每一个角色能操作什么样的功能,一般系统已经设置好,可以根据客户需要修改即可。

table1函数 -回复

table1函数-回复Table1函数是一种常用于数据分析和数据可视化的功能强大的工具。

它可以帮助用户轻松地对数据进行整理和汇总,以便更好地理解和探索数据的特征和规律。

本文将介绍Table1函数的基本原理和用法,并通过一个具体的例子来演示其在数据分析中的应用。

首先,让我们介绍一下Table1函数的基本原理。

Table1函数主要是基于R语言中的Hmisc包实现的,它可以对数据集中的多个变量进行描述性统计,并将结果按照用户指定的格式输出。

这个函数广泛应用于临床医学研究和流行病学研究中,帮助研究人员迅速了解数据的特征和分布。

在使用Table1函数之前,我们首先需要确保已经安装了R语言和Hmisc包。

然后,我们可以通过以下步骤来使用Table1函数。

步骤一:导入数据首先,我们需要将需要分析的数据导入R语言的工作环境中。

可以使用read.csv()函数或其他相关的函数将数据导入到一个数据框中。

步骤二:安装和载入Hmisc包在使用Table1函数之前,我们需要安装Hmisc包。

可以通过使用install.packages()函数来完成安装。

安装完成后,我们需要使用library()函数来载入Hmisc包。

步骤三:整理数据在进行数据分析之前,我们经常需要对数据进行一些基本的整理工作,比如删除缺失值、清洗异常值等。

在这一步骤中,我们可以使用R语言中的各种函数和操作符来完成。

步骤四:生成Table1通过使用Table1函数,我们可以对数据中的多个变量进行描述统计。

可以使用formula参数来指定需要分析的变量以及其与其他变量的关系。

可以使用data参数来指定数据框对象。

可以使用非常多的选项来定制Table1的输出格式,比如添加百分比、标准差、置信区间等。

步骤五:输出结果最后,我们可以将Table1的结果输出到一个文件或者在R语言环境中显示。

可以使用print()函数将结果打印出来,也可以使用export()函数将结果保存到一个文件中。

table1函数 -回复

table1函数-回复Table1函数是一种常用的编程函数,用于创建和管理数据库中的表格。

在本文中,我们将一步一步地回答与Table1函数相关的问题。

第一步:什么是Table1函数?Table1函数是用于数据库中表格操作的函数。

它提供了创建、修改和查询表格的功能。

通过Table1函数,用户可以轻松地创建和管理数据库中的表格,包括定义表格的字段和属性,插入和删除数据,以及查询和修改表格中的数据。

第二步:如何创建一个表格?要创建一个表格,我们需要使用Table1函数的CREATE TABLE语句。

在这个语句中,我们需要指定表格的名称和字段。

每个字段都包括字段名和字段类型。

例如,下面是一个创建名为"customers"的表格的示例代码:CREATE TABLE customers (id INT PRIMARY KEY,name VARCHAR(50),email VARCHAR(100));在上述代码中,我们使用INT和VARCHAR作为字段的数据类型,分别用于存储整数和字符串。

PRIMARY KEY关键字指定了主键字段,以确保每个记录都具有唯一的标识。

第三步:如何插入数据到表格中?插入数据到表格中,我们使用Table1函数的INSERT INTO语句。

在这个语句中,我们需要指定要插入数据的表格名称和要插入的字段值。

例如,下面是插入数据到"customers"表格的示例代码:INSERT INTO customers (id, name, email)VALUES (1, 'John Doe', 'johndoeexample');在上述代码中,我们指定了要插入数据的表格名称和字段名称,然后使用VALUES子句指定要插入的具体值。

第四步:如何查询表格中的数据?查询表格中的数据,我们使用Table1函数的SELECT语句。

在这个语句中,我们可以指定要查询的字段和条件。

loadrunner 参数 table 和file

Loadrunner 是一款性能测试工具,被广泛应用于软件性能测试领域。

在使用Loadrunner进行性能测试时,参数 table 和 file 是两个非常重要的概念。

本文将对这两个概念进行深入解析,帮助读者更好地理解和使用Loadrunner。

一、参数 table1. 参数 table 的概念参数 table 是Loadrunner中用于存储动态参数和提取的参数值的一个数据结构。

在进行性能测试时,很多情况下需要模拟用户的行为,例如填写表单、进行登入等,这些操作中会涉及到需要从上一个请求中提取的参数值,或者需要在下一个请求中使用的动态参数。

参数table 的作用就是存储这些参数值,以便在后续的请求中使用。

2. 参数 table 的使用方法在Loadrunner中,可以通过函数和脚本来操作参数 table。

常见的操作包括向参数 table 中添加新的参数、修改已有参数的值、删除参数等。

通过对参数 table 的灵活使用,可以实现对复杂业务场景的模拟和测试。

3. 参数 table 的注意事项在使用参数 table 时,需要注意对参数的管理和维护。

特别是在测试复杂的业务流程时,参数 table 中的参数值可能会非常庞大,需要合理的管理和清理,避免对性能测试造成干扰。

二、file1. file 的概念file 是Loadrunner中用于存储测试脚本、日志、报告等文件的一个重要工具。

在进行性能测试时,通常会有大量的脚本文件、测试数据文件、日志文件等需要管理和使用,file 提供了一个统一的管理和操作接口。

2. file 的使用方法通过Loadrunner的接口和命令,可以对file进行创建、读取、写入、删除等操作。

在测试执行过程中,file可以帮助用户实现对测试结果的记录和管理,包括生成测试报告、保存测试日志等。

3. file 的注意事项在使用file时,需要注意文件的存储位置和命名规范。

合理的文件管理和命名规范可以避免文件混乱和丢失,有利于对测试结果的追溯和分析。

teradata like语句

一、Teradata数据库简介Teradata是一种用于大规模数据仓库和分析的关系型数据库管理系统。

它是世界上最大的并行处理数据库之一,被许多大型企业和组织用于数据存储和分析。

Teradata数据库以其高性能、可扩展性和并行处理能力而闻名,是大数据分析和数据驱动型决策的理想选择。

二、Teradata Like语句概述在Teradata数据库中,Like语句是用于在查询数据时进行模糊匹配的关键字。

它使得用户可以在匹配模式中使用通配符来查找满足特定条件的数据。

Like语句通常与SELECT语句一起使用,用于从表中检索符合特定模式的数据行。

三、Like语句的语法在Teradata数据库中,Like语句的基本语法如下所示:SELECT column1, column2, ...FROM table_nameWHERE column_name LIKE pattern;在这个语法中,column1, column2等表示需要检索的列,table_name表示需要检索的表,column_name表示需要进行匹配的列,而pattern则表示匹配模式。

在pattern中,通配符表示零个或多个字符,而_表示一个字符。

四、Like语句的应用实例1. 简单模糊匹配假设我们有一个名为employees的表,其中包含雇员的尊称信息。

我们可以使用Like语句来查找以字母“A”开头的员工尊称:SELECT *FROM employeesWHERE employee_name LIKE 'A';2. 复杂模糊匹配如果我们想要查找以字母“J”开头,且长度为5个字符的员工尊称,可以使用如下查询:SELECT *FROM employeesWHERE employee_name LIKE 'J____';3. 结合通配符我们还可以使用多个通配符结合来进行模糊匹配。

我们可以使用作为通配符,来查找包含字母“S”和“th”之间有0个或多个字符的员工尊称:SELECT *FROM employeesWHERE employee_name LIKE 'Sth';五、Like语句的性能和注意事项虽然Like语句在数据查询中非常灵活,但是它也可能导致性能问题,特别是在对大型表进行模糊匹配时。

Moxa CP-104UL 104JU Series PComm Lite Release Note

Utility for CP-104UL/104JU Series (PComm Lite) Release Notes Supported Operating SystemsNotesChangesApplicable ProductsBugs Fixed• Different versions of PComm Lite 2000 can be installed on the same PC.• Performance Analyzer can store previous configurations of the COM port list.• PComm Terminal users can set history depth in ANSI and VT100 mode.• PComm Terminal could not locate system file ws2_32.dll in Windows 2000 and Windows XP.• In the Send Pattern function, an individual port cannot be stopped but all ports can be stopped simultaneously.EnhancementsWindows 2000, Windows 7, Windows Server 2003, Windows Server 2008, Windows Server 2008 R2,Windows Vista, Windows XPUSB-to-Serial Converters, Multiport Serial Boards, Serial Device Servers• Added byte transmit/receive counter in PComm Terminal.• PComm Terminal supports pasting clipboard content to terminal.New FeaturesN/A• Terminal Emulator: Supports all serial products, including non-Moxa products.• Diagnostic Utility: Supports Moxa Multiport Serial Boards.• Monitor Utility: Supports Moxa Multiport Serial Boards.• Performance Analyzer: Supports Moxa Multiport Serial Boards, UPort Series, and NPort Series.• PComm Library: Supports all serial products, including non-Moxa products.Supported Operating SystemsNotesChangesApplicable ProductsBugs Fixed• ncludes VC project example code for PComm library • Read method using RX_CHAR event.• Supports opening multiple COM ports.• Log files can be stored in a specified path/link.N/AEnhancementsWindows 2000, Windows 7, Windows Server 2003, Windows Server 2008, Windows Server 2008 R2,Windows Vista, Windows XPUSB-to-Serial Converters, Multiport Serial Boards, Serial Device Servers• Supports Windows 2008/2008 R2 (x86/x64).• Supports HEX code display for dumb mode.• Supports linear baud rate configuration.• Supports send pattern for multiple COM ports.• Supports data file pattern.• Supports interval time between sending two patterns.• Supports network communication: TCP Server/Client, UDP.• Supports auto line wrap.• Supports customizing terminal size.• Supports DTR/DSR flow control configuration.• Supports Performance Analyzer.New FeaturesN/A• Terminal Emulator: Supports all serial products, including non-Moxa products.• Diagnostic Utility: Supports Moxa Multiport Serial Boards.• Monitor Utility: Supports Moxa Multiport Serial Boards.• Performance Analyzer: Supports Moxa Multiport Serial Boards, UPort Series, and NPort Series.• PComm Library: Supports all serial products, including non-Moxa products.Supported Operating SystemsNotesChangesApplicable ProductsBugs Fixed• VT100 added "DEL" key support.• Modified all online help to HTML format.• PComm Lite supports up to COM1024.• Updated PComm.dll to fix ASCII tx causing VB program to hang if tx is held by CTS flow control.EnhancementsWindows 2000, Windows 7, Windows Server 2003, Windows Vista, Windows XPUSB-to-Serial Converters, Multiport Serial Boards, Serial Device Servers• Supports Windows Vista/7.New FeaturesN/A• Terminal Emulator: Supports all serial products, including non-Moxa products.• Diagnostic Utility: Supports Moxa Multiport Serial Boards.• Monitor Utility: Supports Moxa Multiport Serial Boards.• Performance Analyzer: Supports Moxa Multiport Serial Boards, UPort Series, and NPort Series.• PComm Library: Supports all serial products, including non-Moxa products.Supported Operating SystemsNotesChangesApplicable ProductsBugs Fixed• PComm Terminal display performance.• PComm Terminal status bar display problem.• PComm Terminal display problem with Moxa UC Series/EtherDevice/W2004 console.EnhancementsWindows 2000, Windows Server 2003, Windows XPUSB-to-Serial Converters, Multiport Serial Boards, Serial Device Servers• Utilities support Moxa MSB x64 driver.• PComm Library supports Windows x64 Edition (AMD64, EM64T). For cross development, x86 & x64library will both be installed.New FeaturesN/A• Terminal Emulator: Supports all serial products, including non-Moxa products.• Diagnostic Utility: Supports Moxa Multiport Serial Boards.• Monitor Utility: Supports Moxa Multiport Serial Boards.• Performance Analyzer: Supports Moxa Multiport Serial Boards, UPort Series, and NPort Series.• PComm Library: Supports all serial products, including non-Moxa products.。

IOmeter各参数详解

介绍Iometer简介快速开始测试磁盘性能测试两台计算机之间的网络性能(A和B)详解“Disk T arget T ab”详解“Access Specifications T ab”详解“Results Display T ab”详解“T est Setup tab“介绍Iometer是一款用于单系统和集群系统的I/O子系统度量(measurement)和特征化(characterization)工具,它是一个负载生成器(workload generator),也是一个度量工具(measurement tool),可用于模拟任何程序或benchmark的磁盘或网络I/O操作,在单个或多个(联网)系统上生成并度量负载。

Iometer简介Iometer由两个程序组成,Iometer和Dynamo。

Iomter是控制程序/GUI,它告诉Dynamo 需要做什么,收集数据结果并总结到一个输出文件。

一次只应该运行一个Iometer,通常运行在服务器上。

Dynamo是一个负载生成器,它没有GUI,在Iometer的命令下执行I/O操作并记录性能信息,然后返回数据给Iometer。

一次可以运行多个Dynamo,通常是一个副本运行在服务器上,另一个副本运行在每一台客户端上。

Dynamo是多线程的,每一个副本可以模拟多个客户端程序的工作(workload),每一个正在运行的Dynamo副本被称为是一个Manager,Dynamo中的每一个线程被称为worker。

双击Iometer.exe运行Iometer,出现Iometer GUI(如下图所示),同时会在本地系统上启动Dynamo的一个副本。

双击一个.icf设置文件、将icf或.txt文件拖拽到Iometer.exe也能启动Iometer,并且加载配置信息。

命令行启动方式形如:c:\iometer myconfig.icf。

如果需要在其他机器上启动Dynamo,将机器名作为Iometer的命令行参数,例如c:\dynamo IOServer。

计算机常见屏幕英语

计算机常见屏幕英语(SCREEN ENGLISH)access 访问data 数据hard disk 硬盘files 文件directory 目录delete 删除(同:remove)exists 存在name 名称read-only 只读change 修改,改变save 保存password 密码connect 连接network网络device 设备error 错误shortcut key 快捷键sure 确定quit 退出(同:exit)Setup 安装(同:install)item 项目current 当前的temporary 临时的icon 图标window 窗口Windows “视窗”操作系统check 检查Control Panel 控制面板modem调制解调器choose 选择format 格式化click 单击double-click 双击)run 运行desktop 桌面button按钮drive 驱动器valid 有效的default 缺省的,默认的value 值miss 丢失(数据,文件等background 背景content 内容drag 拖动command 命令paste 粘贴(反:copy)register 注册,登记online联机,在线(反:off-line)ignore忽略illegal 无效的image 图像corrupt 坏的incorrect 不正确的version 版本insert 插入update 更新link 链接LAN 局域网backup备份screen 屏幕cursor 光标target drive 目标驱动器recovery 恢复recreate 重建require 需要reset 复位操作,热启动scan 扫描,检查saver 保护程序port 端口server 服务器copyright 版权skip 跳过specified 指定的source 源(文件,驱动器等)target 目标swap 交换switch 切换notepad 记事簿dialog box 对话窗口halt 停止out of paper 缺纸video 视频(audio 音频)remote 远程option 选项upgrade 升级previous 旧的,先前的(版本等)work station 工作站attach 连接计算机屏幕显示英语1.(C)Copyright 1985,1986,1987,1989(C)版权1985,1986,1987,1989Central Point Software, INC.中心点软件公司2. (c)Copyright Microsoft Corp. 1987(C)微软公司版权19873. * Available . Allocated* 可用 . 地址已指定4. … bytes available on disk字节在磁盘上可用5. … bytes total disk space字节为盘的总容量6. … bytes used by system 字节为系统(文件)所占用7. …bytes in bad sectors字节为坏扇区8. 15 sectors per track, 2 side(s) 每条磁道15个扇区,2面9. 9 Sectors /Track, Side(s) 9扇区/磁道,面10. Access denied 存取被拒绝11. And strike ENTER when ready 当准备好后按Enter键12. Attempted write protect violation 企图侵犯写保护13. B Boot record H hidden B 引导记录H 隐含14. Backup file sequence error 备份文件顺序错误15. Bad or missing command interpreter非法的或缺少命令解释程序16. Bad partition table 非法的分区表17. Bad unit 非法的装置18. Batch file missing 批处理文件丢失19. Can’t continue不可能继续20. Cannot execute FORMAT 不能执行FORMAT21. Cannot find system files 找不到系统文件22. Cannot open list file 不能打开清单文件23. Cannot open overly 不能打开覆盖段24. Cannot open run file 不能打开运行文件25. Choose one of the following 选取下列各项之一1.Create DOS partition 1.建立DOS分区2.Change active partition 2.改变活动分区3.Delete DOS partition 3.删除DOS 分区4.Display partition information 4.显示分区信息26. Compare error on side 0, track 5比较0面,磁道5上的错误27. Compare more file (Y/N)? 还做文件比较吗?28. Compare process ended 比较处理结束29. Comparing 80 tracks 比较80条磁道30. Copy another (Y/N)? 还要拷贝另一个吗?31. Copy another diskette (Y/N)? N复制另一张磁盘吗(是/否)?否32. Copy complete 拷贝完成33. Copyright 40 tracks 版权40条磁道34. Current date is Tue MM-DD-YYYY当前日期是星期二月—日—年35. Current fixed disk driver: 1 当前的固定盘驱动器:136. Current time is hh: mm: 当前时间是时:分:37. Cylinders at x x x x 柱面位于XXXX38. D Directory X Bad Cluster D 目录X 坏的簇39. Device fault 设备故障40. Device I/O error I/O 设备故障41. Device timeout 设备超时42. Disk full 磁盘满43. Disk Mapping Service 磁盘映射服务44. Disk not ready 磁盘没有准备好45. DISK SERVICES: Copy compare Find Rename磁盘服务:复制比较搜索改名Verify View/edit Map Locate initialize验证显示/编辑映射定位初始化46. Disk write protect 磁盘写保护47. Division by zero 除数为零48. Do you wish to use the entire fixed你希望将整个固定盘disk for DOS (Y/N)? [Y] 用作DOS吗(是/否)?[是]49. Double sided 双面50. Duplicate definition 重复定义51. Enter new date 输入新日期52. Enter new time 输入新时间53. Entire disk mapped 整个磁盘被映射54. Entry error 登记项错误55. Entry has a bad attribute (or size or link)登记项有一个非法的属性(或大小、或链接)56. Error loading operating system 装入操作系统错误57. Error writing partition table 写分区表错误58. Explanation of Codes 代码说明59. F File Allocate Table R Read Only F 文件分配表R 只读60. F10=change driver/path from C:\F10=从C盘(根目录)改变驱动器/路径61.F3=file srve F10=F3+chg drvF3=文件服务F10=F3+改变驱动器Esc=exit PC Tools ESC=退出P 工具软件C 62. F3=go directly to Disk and Special FunctionsF3=直接转至磁盘和特殊功能63. FDISK Options FDISK 选项64. File already exists 文件已经存在65. File already open 文件已经打开66. File are different sizes 文件大小不同67. File compare OK 文件比较成功68. File is read-only 文件是只读的69. File not found 文件找不到70. File sharing conflict 文件共享冲突71. FOR without NEXTFOR语句没有对应的NEXT语句72. Format failure 格式化失败73. Formatting while copying 在拷贝时格式化74. Illegal direct 非法的直接使用75. Illegal function call 非法的函数调用76. Incorrect DOS version 不正确的DOS版本77. Incorrect parameter 参数不正确78. Insert new diskette for driver B: 为B 驱动器插入79. Insert SOURCE diskette in drive A: 将“源”盘插入A驱动器80. Insert TARGET diskette in drive B: 将“目标”盘插入B驱动器81. Insufficient disk space 磁盘空间不足82. Insufficient memory 内存空间不足83. Internal error 内部错误84. Invalid country code 无效的国家代码85. Invalid device 无效的设备86. Invalid directory 无效的目录87. Invalid disk change 无效的磁盘替换88. Invalid driver or file name 无效的驱动器或目录名89. Invalid driver specification 无效的驱动器说明90. Keyboard routine not found 键盘程序没找到91. Label not found 标号没找到92. Last file not back up 最后的文件没有备份93. Maximum available space is x x x x 最大可用的容量是XXXX94. Memory allocation error 内存分配错误95. Missing operating system 操作系统丢失96. Non-System disk or disk error 无系统盘或磁盘错误97. Out of data 数据不够98. Out of memory 内存不够99. Out of paper 缺纸100.Overflow 溢出101.Path not found 路径找不到102.Path=A:\*.* 路径=A:\*.* 103.PC Tools Deluxe R4.30 ---- 工具软件Deluxe R4.30 ----disk and Special Functions PC 磁盘及特殊功能104.Press any key for File Functions 对于文件的各项功能,按下任意键OR 或者105.Press ESC to Exit 按ESC键退出106.Replace and press any key when ready 替换(盘),当准备好后按任意键107.Side 0, track 5 0面,第5磁道108.SPECIAL SERVICES: Directory maintain 特殊服务:目录维护不删除(Undelete system Info Park Help (恢复)系统显示信息驻留(加锁)帮助109.String too long 字符串过长110.Subscript out of rang 下标范围不够111.Syntax error 句法错误112.System complete 系统完成(任务)113.System transferred 系统被分配114.System will now restart 系统现在将重新启动115.Too many files 文件过多116.Total fixed disk space is x x x x cylinders 固定盘的总容量为XXXX个柱面117.Type mismatch 类型不匹配118.Unauthorized duplication prohibited 禁止非授权的复制119. Undefined line number 未定义行号120.Unrecoverable read error on drive A: 在A驱动器中有不可恢复的读出错误121.Warning! Data in the DOS’ partition could注意!在DOS分区中的数据可能丢失,be lost. Do you wish to continue … ?你希望继续吗…?[不]。

shgetfolderpathw函数

shgetfolderpathw函数是Windows操作系统中的一个API函数,其作用是获取特定文件夹的路径。

在Windows中,文件夹是组织和存储文件和其他文件夹的一种容器,如“我的文档”、“桌面”等。

shgetfolderpathw函数可以通过标识符来获取这些特定文件夹的路径,使得程序可以方便地访问这些文件夹中的内容。

shgetfolderpathw函数的参数包括:父窗口句柄、文件夹标识符、访问标志和路径字符串。

通过使用这些参数,程序可以调用shgetfolderpathw函数来获取特定文件夹的路径。

shgetfolderpathw函数的返回值为一个HRESULT类型的错误代码,用来指示函数调用的成功与否。

如果函数成功执行,返回值为S_OK;如果失败,返回值则为错误代码,程序可以根据返回值来处理相应的错误情况。

在使用shgetfolderpathw函数时,需要先通过SHGetFolderLocation函数来获取特定文件夹的标识符,再将标识符作为参数传递给shgetfolderpathw函数。

通过这个过程,程序可以获取到特定文件夹的路径,从而对其进行操作。

shgetfolderpathw函数在开发Windows应用程序时非常有用。

当程序需要将文件保存到特定的文件夹中时,可以使用shgetfolderpathw 函数来获取目标文件夹的路径;又或者当程序需要向用户展示特定文件夹中的内容时,也可以用shgetfolderpathw函数来获取文件夹路径。

通过调用shgetfolderpathw函数,程序可以方便地与特定文件夹进行交互,提高了应用程序的灵活性和用户体验。

shgetfolderpathw函数是Windows操作系统中一个十分实用的API 函数,它可以帮助程序快速获取特定文件夹的路径,方便地与文件夹进行交互。

在开发Windows应用程序时,如果需要操作特定文件夹的内容,可以考虑使用shgetfolderpathw函数来简化开发工作,提高程序的效率和用户体验。

IBM v5000存储调试手册

2.2.6

将卷映射到主机 ................................................................................................... 26

图目录

图 2-1 图 2-2 图 2-3 图 2-4

网口连接主控制柜示意图 ................................................................................. 2 磁阵登陆界面 .................................................................................................. 2 管理界面 ......................................................................................................... 2 磁阵地址设置 .................................................................................................. 3

2 磁阵始化操作 ..................................................................................................................... 1 2.1 基本设置 ................................................................................................................... 1

Sigmawin100中文

2.2连接通讯端口启动SigmaWin100时,出现连接对话框。

设定SigmaWin100和伺服模块之间的串口通讯通讯设定1.选择设定伺服模块的方法:在线或离线。

在连接状态下设定和调整伺服驱动器时选择在线。

在没有连接伺服模块时编辑参数,或为跟踪或机械分析检查屏幕时选择离线。

2.当选择在线时,输入通讯设定的必要参数。

端口(串口1到串口8)选择通讯(COM)端口。

在端口列表中,可看到您使用的个人电脑上所有串口列表。

通讯介质(RS-232C/RS-422A)选择适合您的电脑通讯端口类型的协议。

当两个或更多的伺服模块连接到同一个串口时选择RS-422A。

参考附录A获得多轴通讯的连接方法。

轴地址/最后轴地址3.设定好后,点击OK。

在所有伺服模块成功连接到SigmaWin100后,在屏幕上将显示已连接伺服模块列表。

2.3 Selecting a SERVOPACK2.3.选择一个伺服模块。

当启动SigmaWin100时,系统将通过串口扫描连接的伺服模块。

扫描结果将显示在伺服选择对话框中。

伺服选择对话框注意:选择RS-232C时,只显示一个伺服模块。

使用下面的方法选择连接的伺服模块选择连接的伺服模块,然后点击OK;或双击连接的伺服模块。

点击cancel,关闭对话框,系统将进入离线模式。

< 如果伺服选择对话框没有显示出来>如果没有发现伺服模块,将显示下面信息,系统将进入离线模式。

如果不管伺服模块是否连接都显示上述信息,可能出现了通讯问题。

检查项目注释电源开?连接松动?锁紧所有连接电缆接头选择了正确的端口?确认连接到通讯电缆上的端口和软件连接过程中选择的端口一致轴地址正确?(RS-232C:单轴连接)确认伺服模块中设置的轴地址(参数Pn000中的第二位数)和软件连接过程中选择的轴地址一致。

(RS-422A:多轴连接)确认连接的伺服模块轴地址:+在地址中没有使用数字“0”。

+不重复。

RS-232端口使能?为节能,可能在个人电脑中选择了不向RS-232C端口供电。

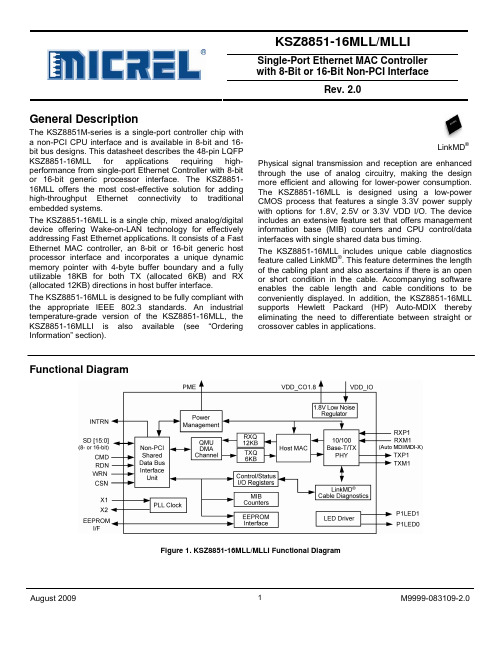

ksz8851

KSZ8851-16MLL/MLLISingle-Port Ethernet MAC Controllerwith 8-Bit or 16-Bit Non-PCI InterfaceRev. 2.0General DescriptionThe KSZ8851M-series is a single-port controller chip witha non-PCI CPU interface and is available in 8-bit and 16-bit bus designs. This datasheet describes the 48-pin LQFPKSZ8851-16MLL for applications requiring high-performance from single-port Ethernet Controller with 8-bitor 16-bit generic processor interface. The KSZ8851-16MLL offers the most cost-effective solution for addinghigh-throughput Ethernet connectivity to traditionalembedded systems.The KSZ8851-16MLL is a single chip, mixed analog/digitaldevice offering Wake-on-LAN technology for effectivelyaddressing Fast Ethernet applications. It consists of a FastEthernet MAC controller, an 8-bit or 16-bit generic hostprocessor interface and incorporates a unique dynamicmemory pointer with 4-byte buffer boundary and a fullyutilizable 18KB for both TX (allocated 6KB) and RX(allocated 12KB) directions in host buffer interface.The KSZ8851-16MLL is designed to be fully compliant withthe appropriate IEEE 802.3 standards. An industrialtemperature-grade version of the KSZ8851-16MLL, theKSZ8851-16MLLI is also available (see “OrderingInformation” section).LinkMD®Physical signal transmission and reception are enhancedthrough the use of analog circuitry, making the designmore efficient and allowing for lower-power consumption.The KSZ8851-16MLL is designed using a low-powerCMOS process that features a single 3.3V power supplywith options for 1.8V, 2.5V or 3.3V VDD I/O. The deviceincludes an extensive feature set that offers managementinformation base (MIB) counters and CPU control/datainterfaces with single shared data bus timing.The KSZ8851-16MLL includes unique cable diagnosticsfeature called LinkMD®. This feature determines the lengthof the cabling plant and also ascertains if there is an openor short condition in the cable. Accompanying softwareenables the cable length and cable conditions to beconveniently displayed. In addition, the KSZ8851-16MLLsupports Hewlett Packard (HP) Auto-MDIX therebyeliminating the need to differentiate between straight orcrossover cables in applications.Functional DiagramFigure 1. KSZ8851-16MLL/MLLI Functional DiagramFeatures•Integrated MAC and PHY Ethernet Controller fully compliant with IEEE 802.3/802.3u standards •Designed for high performance and high throughput applications•Supports 10BASE-T/100BASE-TX•Supports IEEE 802.3x full-duplex flow control and half-duplex backpressure collision flow control •Supports DMA-slave burst data read and write transfers•Supports IP Header (IPv4)/TCP/UDP/ICMP checksum generation and checking•Supports IPv6 TCP/UDP/ICMP checksum generation and checking•Automatic 32-bit CRC generation and checking •Simple SRAM-like host interface easily connects to most common embedded MCUs.•Supports multiple data frames for transmit and receive without address bus and byte-enable signals •Supports both Big- and Little-Endian processors •Larger internal memory with 12K Bytes for RX FIFO and 6K Bytes for TX FIFO. Programmable low, highand overrun watermark for flow control in RX FIFO •Shared data bus for Data, Address and Byte Enable •Efficient architecture design with configurable host interrupt schemes to minimize host CPU overhead and utilization•Powerful and flexible address filtering scheme •Optional to use external serial EEPROM configuration for MAC address•Single 25MHz reference clock for both PHY and MAC •HBM ESD Rating 6kVPower Modes, Power Supplies, and Packaging •Single 3.3V power supply with options for 1.8V, 2.5V and 3.3V VDD I/O•Built-in integrated 3.3V or 2.5V to 1.8V low noise regulator (LDO) for core and analog blocks •Enhanced power management feature with energy detect mode and soft power-down mode to ensurelow-power dissipation during device idle periodsComprehensive LED indicator support for link, activity and 10/100 speed (2 LEDs) - User programmable •Low-power CMOS design•Commercial Temperature Range: 0o C to +70o C •Industrial Temperature Range: –40o C to +85o C •Flexible package options available in 48-pin (7mm x 7mm) LQFP KSZ8851-16MLL or 128-pin PQFPKSZ8851-16/32MQL Additional FeaturesIn addition to offering all of the features of a Layer 2 controller, the KSZ8851-16MLL offers:•Flexible 8-bit and 16-bit generic host processor interfaces with same access time and single bustiming to any I/O registers and RX/TX FIFO buffers •Supports to add two-byte before frame header in order for IP frame content with double word boundary •Micrel LinkMD® cable diagnostic capabilities to determine cable length, diagnose faulty cables, anddetermine distance to fault• Wake-on-LAN functionality– Incorporates Magic Packet™, wake-up frame, network link state, and detection of energy signaltechnology•HP Auto MDI-X™ crossover with disable/enable option •Ability to transmit and receive frames up to 2000 bytes Network Features•10BASE-T and 100BASE-TX physical layer support •Auto-negotiation: 10/100 Mbps full and half duplex • Adaptive equalizer• Baseline wander correctionApplications• Video/Audio Distribution Systems•High-end Cable, Satellite, and IP set-top boxes •Video over IP and IPTV•Voice over IP (VoIP) and Analog Telephone Adapters (ATA)•Industrial Control in Latency Critical Applications •Home Base Station with Ethernet Connection •Industrial Control Sensor Devices (Temperature, Pressure, Levels, and Valves)•Security, Motion Control and Surveillance Cameras Markets• Fast Ethernet• Embedded Ethernet• Industrial Ethernet• Embedded SystemsOrdering InformationPart Number Temperature Range Package Lead FinishLQFP Pb-Free KSZ8851-16MLL 0o C to 70o C 48-PinKSZ8851-16MLLI –40o C to +85o C 48-PinLQFP Pb-Free KSZ8851-16MLL-Eval Evaluation Board for the KSZ8851-16MLLRevision HistoryRevision Date Summary of Changes1.0 06/30/2008 First released Information.1.1 2/13/2009 Improved EDS Rating up to 6KV, revised Ordering Information and Updated Table contentand description.2.0 8/31/2009 Change revision ID from “0” to “1” in CIDER (0xc0) register. Update pins 8, 14 and 29description for 1.8V VDD_IO supply. To add the command write (CMD=1) address indexregister in order for software to read back the CMD register value. To enable software reador write external EEPROM.ContentsPin Configuration (10)Pin Description (11)Strapping Options (13)Functional Description (14)Functional Overview (14)Power Management (14)Normal Operation Mode (14)Energy Detect Mode (14)Soft Power Down Mode (15)Power Saving Mode (15)Wake-on-LAN (15)Detection of Energy (15)Detection of Linkup (15)Wake-up Packet (15)Magic Packet™ (16)Physical Layer Transceiver (PHY) (16)100BASE-TX Transmit (16)100BASE-TX Receive (17)PLL Clock Synthesizer (Recovery) (17)Scrambler/De-scrambler (100BASE-TX only) (17)10BASE-T Transmit (17)10BASE-T Receive (17)MDI/MDI-X Auto Crossover (17)Straight Cable (18)Crossover Cable (18)Auto Negotiation (19)LinkMD® Cable Diagnostics (20)Access (20)Usage (20)Media Access Control (MAC) Operation (21)Inter Packet Gap (IPG) (21)Back-Off Algorithm (21)Late Collision (21)Flow Control (21)Half-Duplex Backpressure (22)Address Filtering Function (22)Clock Generator (23)Bus Interface Unit (BIU) (23)Supported Transfers (23)Physical Data Bus Size (23)Little and Big Endian Support (23)Asynchronous Interface (24)BIU Summation (24)Queue Management Unit (QMU) (24)Transmit Queue (TXQ) Frame Format (24)Frame Transmitting Path Operation in TXQ (26)Driver Routine for Transmit Packet from Host Processor to KSZ8851-16MLL (26)Receive Queue (RXQ) Frame Format (29)Frame Receiving Path Operation in RXQ (29)Driver Routine for Receive Packet from KSZ8851-16MLL to Host Processor (30)EEPROM Interface (31)Loopback Support (32)Near-end (Remote) Loopback (32)Far-end (Local) Loopback (32)CPU Interface I/O Registers (33)I/O Registers (33)Internal I/O Registers Space Mapping (34)Register Map: MAC, PHY and QMU (40)Bit Type Definition (40)0x00 – 0x07: Reserved (40)Chip Configuration Register (0x08 – 0x09): CCR (40)0x0A – 0x0F: Reserved (40)Host MAC Address Registers: MARL, MARM and MARH (40)Host MAC Address Register Low (0x10 – 0x11): MARL (41)Host MAC Address Register Middle (0x12 – 0x13): MARM (41)Host MAC Address Register High (0x14 – 0x15): MARH (41)0x16 – 0x1F: Reserved (41)On-Chip Bus Control Register (0x20 – 0x21): OBCR (41)EEPROM Control Register (0x22 – 0x23): EEPCR (42)Memory BIST Info Register (0x24 – 0x25): MBIR (42)Global Reset Register (0x26 – 0x27): GRR (42)0x28 – 0x29: Reserved (43)Wakeup Frame Control Register (0x2A – 0x2B): WFCR (43)0x2C – 0x2F: Reserved (43)Wakeup Frame 0 CRC0 Register (0x30 – 0x31): WF0CRC0 (43)Wakeup Frame 0 CRC1 Register (0x32 – 0x33): WF0CRC1 (43)Wakeup Frame 0 Byte Mask 0 Register (0x34 – 0x35): WF0BM0 (44)Wakeup Frame 0 Byte Mask 1 Register (0x36 – 0x37): WF0BM1 (44)Wakeup Frame 0 Byte Mask 2 Register (0x38 – 0x39): WF0BM2 (44)Wakeup Frame 0 Byte Mask 3 Register (0x3A – 0x3B): WF0BM3 (44)0x3C – 0x3F: Reserved (44)Wakeup Frame 1 CRC0 Register (0x40 – 0x41): WF1CRC0 (44)Wakeup Frame 1 CRC1 Register (0x42 – 0x43): WF1CRC1 (44)Wakeup Frame 1 Byte Mask 0 Register (0x44 – 0x45): WF1BM0 (45)Wakeup Frame 1 Byte Mask 1 Register (0x46 – 0x47): WF1BM1 (45)Wakeup Frame 1 Byte Mask 2 Register (0x48 – 0x49): WF1BM2 (45)Wakeup Frame 1 Byte Mask 3 Register (0x4A – 0x4B): WF1BM3 (45)0x4C – 0x4F: Reserved (45)Wakeup Frame 2 CRC0 Register (0x50 – 0x51): WF2CRC0 (45)Wakeup Frame 2 CRC1 Register (0x52 – 0x53): WF2CRC1 (46)Wakeup Frame 2 Byte Mask 0 Register (0x54 – 0x55): WF2BM0 (46)Wakeup Frame 2 Byte Mask 1 Register (0x56 – 0x57): WF2BM1 (46)Wakeup Frame 2 Byte Mask 2 Register (0x58 – 0x59): WF2BM2 (46)Wakeup Frame 2 Byte Mask 3 Register (0x5A – 0x5B): WF2BM3 (46)0x5C – 0x5F: Reserved (46)Wakeup Frame 3 CRC0 Register (0x60 – 0x61): WF3CRC0 (46)Wakeup Frame 3 CRC1 Register (0x62 – 0x63): WF3CRC1 (47)Wakeup Frame 3 Byte Mask 0 Register (0x64 – 0x65): WF3BM0 (47)Wakeup Frame 3 Byte Mask 1 Register (0x66 – 0x67): WF3BM1 (47)Wakeup Frame 3 Byte Mask 2 Register (0x68 – 0x69): WF3BM2 (47)Wakeup Frame 3 Byte Mask 3 Register (0x6A – 0x6B): WF3BM3 (47)0x6C – 0x6F: Reserved (47)Transmit Control Register (0x70 – 0x71): TXCR (47)Transmit Status Register (0x72 – 0x73): TXSR (48)Receive Control Register 1 (0x74 – 0x75): RXCR1 (48)Receive Control Register 2 (0x76 – 0x77): RXCR2 (50)TXQ Memory Information Register (0x78 – 0x79): TXMIR (50)0x7A – 0x7B: Reserved (50)Receive Frame Header Status Register (0x7C – 0x7D): RXFHSR (50)Receive Frame Header Byte Count Register (0x7E – 0x7F): RXFHBCR (51)TXQ Command Register (0x80 – 0x81): TXQCR (52)RXQ Command Register (0x82 – 0x83): RXQCR (52)TX Frame Data Pointer Register (0x84 – 0x85): TXFDPR (53)RX Frame Data Pointer Register (0x86 – 0x87): RXFDPR (53)0x88 – 0x8B: Reserved (54)RX Duration Timer Threshold Register (0x8C – 0x8D): RXDTTR (54)RX Data Byte Count Threshold Register (0x8E – 0x8F): RXDBCTR (54)Interrupt Enable Register (0x90 – 0x91): IER (54)Interrupt Status Register (0x92 – 0x93): ISR (55)0x94 – 0x9B: Reserved (56)RX Frame Count & Threshold Register (0x9C – 0x9D): RXFCTR (56)TX Next Total Frames Size Register (0x9E – 0x9F): TXNTFSR (57)MAC Address Hash Table Register 0 (0xA0 – 0xA1): MAHTR0 (57)MAC Address Hash Table Register 1 (0xA2 – 0xA3): MAHTR1 (57)MAC Address Hash Table Register 2 (0xA4 – 0xA5): MAHTR2 (57)MAC Address Hash Table Register 3 (0xA6 – 0xA7): MAHTR3 (57)0xA8 – 0xAF: Reserved (58)Flow Control Low Watermark Register (0xB0 – 0xB1): FCLWR (58)Flow Control High Watermark Register (0xB2 – 0xB3): FCHWR (58)Flow Control Overrun Watermark Register (0xB4 – 0xB5): FCOWR (58)0xB6 – 0xBF: Reserved (58)Chip ID and Enable Register (0xC0 – 0xC1): CIDER (58)0xC2 – 0xC5: Reserved (58)Chip Global Control Register (0xC6 – 0xC7): CGCR (58)Indirect Access Control Register (0xC8 – 0xC9): IACR (59)0xCA – 0xCF: Reserved (59)Indirect Access Data Low Register (0xD0 – 0xD1): IADLR (59)Indirect Access Data High Register (0xD2 – 0xD3): IADHR (59)Power Management Event Control Register (0xD4 – 0xD5): PMECR (59)Go-Sleep & Wake-Up Time Register (0xD6 – 0xD7): GSWUTR (61)PHY Reset Register (0xD8 – 0xD9): PHYRR (61)0xDA – 0xDF: Reserved (61)0xE0 – 0xE3: Reserved (61)PHY 1 MII-Register Basic Control Register (0xE4 – 0xE5): P1MBCR (61)PHY 1 MII-Register Basic Status Register (0xE6 – 0xE7): P1MBSR (62)PHY 1 PHY ID Low Register (0xE8 – 0xE9): PHY1ILR (63)PHY 1 PHY ID High Register (0xEA – 0xEB): PHY1IHR (63)PHY 1 Auto-Negotiation Advertisement Register (0xEC – 0xED): P1ANAR (63)PHY 1 Auto-Negotiation Link Partner Ability Register (0xEE – 0xEF): P1ANLPR (64)0xF0 – 0xF3: Reserved (64)Port 1 PHY Special Control/Status, LinkMD (0xF4 – 0xF5): P1SCLMD (64)Port 1 Control Register (0xF6 – 0xF7): P1CR (65)Port 1 Status Register (0xF8 – 0xF9): P1SR (66)0xFA – 0xFF: Reserved (67)MIB (Management Information Base) Counters (68)Additional MIB Information (69)Absolute Maximum Ratings(1) (70)Operating Ratings(2) (70)Electrical Characteristics(4, 5) (70)Timing Specifications (72)Asynchronous Read and Write Timing (72)Auto Negotiation Timing (73)Reset Timing (74)EEPROM Timing (75)Selection of Isolation Transformers (76)Selection of Reference Crystal (76)Package Information (77)Acronyms and Glossary (78)Figure 1. KSZ8851-16MLL/MLLI Functional Diagram (1)Figure 2. 48-Pin LQFP (10)Figure 3. Typical Straight Cable Connection (18)Figure 4. Typical Crossover Cable Connection (19)Figure 5. Auto Negotiation and Parallel Operation (20)Figure 6. KSZ8851-16MLL 8-Bit and 16-Bit Data Bus Connections (24)Figure 7. Host TX Single Frame in Manual Enqueue Flow Diagram (27)Figure 8. Host TX Multiple Frames in Auto- Enqueue Flow Diagram (28)Figure 9. Host RX Single or Multiple Frames in Auto-Dequeue Flow Diagram (30)Figure 10. PHY Port 1 Near-end (Remote) and Host Far-end (Local) Loopback Paths (32)Figure 11. Asynchronous Cycle (72)Figure 12. Auto Negotiation Timing (73)Figure 13. Reset Timing (74)Figure 14. EEPROM Read Cycle Timing Diagram (75)Figure 15. 48-Pin (7mm x 7mm) LQFP (77)Table 1. Internal Function Blocks Status (14)Table 2. MDI/MDI-X Pin Definitions (18)Table 3. Address Filtering Scheme (22)Table 4. Bus Interface Unit Signal Grouping (23)Table 5. Frame Format for Transmit Queue (25)Table 6. Transmit Control Word Bit Fields (25)Table 7. Transmit Byte Count Format (25)Table 8. Registers Setting for Transmit Function Block (26)Table 9. Frame Format for Receive Queue (29)Table 10. Registers Setting for Receive Function Block (29)Table 11. KSZ8851-16MLL EEPROM Format (31)Table 12. Format of MIB Counters (68)Table 13. Port 1 MIB Counters Indirect Memory Offsets (69)Table 14. Electrical Characteristics (71)Table 15. Asynchronous Cycle Timing Parameters (72)Table 16. Auto Negotiation Timing Parameters (73)Table 17. Reset Timing Parameters (74)Table 18. EEPROM Timing Parameters (75)Table 19. Transformer Selection Criteria (76)Table 20. Qualified Single Port Magnetics (76)Table 21. Typical Reference Crystal Characteristics (76)Pin ConfigurationFigure 2. 48-Pin LQFPPin DescriptionPin NumberPin NameTypePin Function1 P1LED1 Ipu/O2 P1LED0 OpuProgrammable LED output to indicate port activity/status. LED is ON when output is LOW; LED is OFF when output is HIGH.Port 1 LED indicators 1defined as follows:Chip Global Control Register: CGCR bit [9]0 (Default)1P1LED1 100BT ACT P1LED0 LINK/ACTLINK1. Link = LED On; Activity = LED Blink; Link/Act = LED On/Blink;Speed = LED On (100BASE-T); LED Off (10BASE-T)Config Mode: The P1LED1 pull-up/pull-down value is latched as 16/8-bit mode duringpower-up / reset. See “Strapping Options” section for details3 PME OpuPower Management Event (default active low): It is asserted (low or high depends on polarity set in PMECR register) when one of the wake-on-LAN events is detected by KSZ8851-16MLL. The KSZ8851-16MLL is requesting the system to wake up from low power mode. 4 INTRN OpuInterrupt: An active low signal to host CPU to indicate an interrupt status bit is set, this pin need an external 4.7K pull-up resistor. 5 RDN IpuRead Strobe Not Asynchronous read strobe, active low to indicate read cycle. 6 WRN IpuWrite Strobe Not Asynchronous write strobe, active low to indicate write cycle. 7 DGND GndDigital ground 8 VDD_CO1.8 P1.8V regulator output . This 1.8V output pin provides power to pins 14 (VDD_A1.8) and 29 (VDD_D1.8) for core VDD supply.If VDD_IO is set for 1.8V then this pin should be left floating, pins 14 (VDD_A1.8) and 29 (VDD_D1.8) will be sourced by the external 1.8V supply that is tied to pins 27, 38 and 46 (VDD_IO) with appropriate filtering.9 EED_IO Ipd/OIn/Out Data from/to external EEPROM. Config Mode: The pull-up/pull-down value is latched as with/without EEPROM during power-up / reset. See “Strapping Options” section for details 10 EESK Ipd/OEEPROM Serial Clock A 4μs (OBCR[1:0]=11 on-chip bus speed @ 25MHz) or 800ns (OBCR[1:0]=00 on-chip bus speed @ 125MHz) serial output clock cycle to load configuration data from the serial EEPROM.Config Mode: The pull-up/pull-down value is latched as big/little endian mode during power-up / reset. See “Strapping Options” section for details 11 CMD IpdCommand Type This command input decides the SD[15:0] shared data bus access information.When command input is low, the access of shared data bus is for data access in 16-bit mode shared data bus SD[15:0] or in 8-bit mode shared data bus SD[7:0].When command input is high, the access of shared data bus is for address A[7:2] access at shared data bus SD[7:2], byte enable BE[3:0] at SD[15:12] and the SD[11:8] is “don’t care” in 16-bit mode. It is for address A[7:0] access at SD[7:0] in 8-bit mode.Pin NumberPin Name Type Pin Function12CSNIpuChip Select NotChip select for the shared data bus access enable, active Low.13 AGND Gnd Analog ground 14VDD_A1.8P1.8V analog power supply from VDD_CO1.8 (pin 8) with appropriate filtering. If VDD_IO is 1.8V, this pin must be supplied power from the same source as pins 27, 38 and 46 (VDD_IO) with appropriate filtering.15 EECS Opd EEPROM Chip SelectThis signal is used to select an external EEPROM device.16 RXP1 I/O Port 1 physical receive (MDI) or transmit (MDIX) signal (+ differential). 17 RXM1 I/O Port 1 physical receive (MDI) or transmit (MDIX) signal (– differential). 18 AGND Gnd Analog ground.19 TXP1 I/O Port 1 physical transmit (MDI) or receive (MDIX) signal (+ differential). 20 TXM1 I/O Port 1 physical transmit (MDI) or receive (MDIX) signal (– differential). 21 VDD_A3.3 P 3.3V analog VDD input power supply with well decoupling capacitors. 22ISETOSet physical transmits output current.Pull-down this pin with a 3.01K 1% resistor to ground.23 RSTN Ipu Reset NotHardware reset pin (active Low). This reset input is required minimum of 10ms low after stable supply voltage 3.3V. 24 X1 I 25 X2 O25MHz crystal or oscillator clock connection.Pins (X1, X2) connect to a crystal. If an oscillator is used, X1 connects to a 3.3V tolerant oscillator and X2 is a no connect.Note: Clock requirement is ±50ppm for either crystal or oscillator. 26 DGND Gnd Digital ground 27 VDD_IO P 3.3V, 2.5V or 1.8V digital VDD input power supply for IO with well decoupling capacitors. 28 DGND Gnd Digital ground29VDD_D1.8P1.8V digital power supply from VDD_CO1.8 (pin 8) with appropriate filtering. If VDD_IO is1.8V, this pin must be supplied power from the same source as pins 27, 38 and 46 (VDD_IO) with appropriate filtering.30 SD15 I/O (pd)Shared Data Bus bit 15. Data D15 access when CMD=0. Byte Enable 3 at double-word boundary access (BE3, 4th byte enable and active high) in 16-bit mode when CMD=1. This pin must be tied to GND in 8-bit bus mode.31 SD14 I/O (pd)Shared Data Bus bit 14. Data D14 access when CMD=0. Byte Enable 2 at double-word boundary access (BE2, 3rd byte enable and active high) in 16-bit mode when CMD=1. This pin must be tied to GND in 8-bit bus mode.32 SD13 I/O (pd)Shared Data Bus bit 13. Data D13 access when CMD=0. Byte Enable 1 at double-word boundary access (BE1, 2nd byte enable and active high) in 16-bit mode when CMD=1. This pin must be tied to GND in 8-bit bus mode.33 SD12 I/O (pd)Shared Data Bus bit 12. Data D12 access when CMD=0. Byte Enable 0 at double-word boundary access (BE0, 1st byte enable and active high) in 16-bit mode when CMD=1. This pin must be tied to GND in 8-bit bus mode.34 SD11 I/O (pd) Shared Data Bus bit 11. Data D11 access when CMD=0. Don’t care when CMD=1. This pin must be tied to GND in 8-bit bus mode.35 SD10 I/O (pd) Shared Data Bus bit 10. Data D10 access when CMD=0. Don’t care when CMD=1. This pin must be tied to GND in 8-bit bus mode.36SD9I/O (pd)Shared Data Bus bit 9. Data D9 access when CMD=0. Don’t care when CMD=1. This pin must be tied to GND in 8-bit bus mode.37 DGND Gnd Digital groundPin Number Pin Name Type Pin Function38 VDD_IO P 3.3V, 2.5V or 1.8V digital VDD input power supply for IO with well decoupling capacitors.39 SD8 I/O (pd) Shared Data Bus bit 8. Data D8 access when CMD=0. Don’t care when CMD=1. This pinmust be tied to GND in 8-bit bus mode.40 SD7 I/O (pd) Shared Data Bus bit 7. Data D7 access when CMD=0. Address A7 access when CMD=1.41 SD6 I/O (pd) Shared Data Bus bit 6. Data D6 access when CMD=0. Address A6 access when CMD=1.42 SD5 I/O (pd) Shared Data Bus bit 5. Data D5 access when CMD=0. Address A5 access when CMD=1.43 SD4 I/O (pd) Shared Data Bus bit 4. Data D4 access when CMD=0. Address A4 access when CMD=1.44 SD3 I/O (pd) Shared Data Bus bit 3. Data D3 access when CMD=0. Address A3 access when CMD=1.45 SD2 I/O (pd) Shared Data Bus bit 2. Data D2 access when CMD=0. Address A2 access when CMD=1.46 VDD_IO P 3.3V, 2.5V or 1.8V digital VDD input power supply for IO with well decoupling capacitors.47 SD1 I/O (pd) Shared Data Bus bit 1. Data D1 access when CMD=0. In 8-bit mode, this is address A1access when CMD=1. In 16-bit mode, this is “Don’t care” when CMD=1.48 SD0 I/O (pd) Shared Data Bus bit 0. Data D0 access when CMD=0. In 8-bit mode, this is address A0access when CMD=1. In 16-bit mode, this is “Don’t care” when CMD=1.Legend:P = Power supply Gnd = GroundI/O = Bi-directional I = Input O = Output.Ipd = Input with internal pull-down (58K ±30%).Ipu = Input with internal pull-up (58K ±30%).Opd = Output with internal pull-down (58K ±30%).Opu = Output with internal pull-up (58K ±30%).Ipu/O = Input with internal pull-up (58K ±30%) during power-up/reset; output pin otherwise.Ipd/O = Input with internal pull-down (58K ±30%) during power-up/reset; output pin otherwise.I/O (pd) = Input/Output with internal pull-down (58K ±30%).Strapping OptionsPin Number Pin Name Type Pin Function1 P1LED1 Ipu/O 8 or 16-bit bus mode select during power-up / reset:NC or Pull-up (default ) = 16-bit busPull-down = 8-bit busThis pin value is also latched into register CCR, bit 6/7.9 EED_IO Ipd/O EEPROM select during power-up / reset:Pull-up = EEPROM presentNC or Pull-down (default ) = EEPROM not presentThis pin value is latched into register CCR, bit 9.10 EESK Ipd/O Endian mode select during power-up / reset:Pull-up = Big EndianNC or Pull-down (default) = Little EndianThis pin value is latched into register CCR, bit 10.When this pin is no connect or tied to GND, the bit 11 (Endian mode selection) inRXFDPR register can be used to program either Little (bit11=0 default) Endian mode orBig (bit11=1) Endian mode.Note: Ipu/O = Input with internal pull-up (58K ±30%) during power-up/reset; output pin otherwise.Ipd/O = Input with internal pull-down (58K ±30%) during power-up/reset; output pin otherwise.Pin strap-ins are latched during power-up or reset.Functional DescriptionThe KSZ8851-16MLL is a single-chip Fast Ethernet MAC/PHY controller consisting of a 10/100 physical layer transceiver (PHY), a MAC, and a Bus Interface Unit (BIU) that controls the KSZ8851-16MLL via an 8-bit or 16-bit host bus interface. The KSZ8851-16MLL is fully compliant to IEEE802.3u standards.Functional OverviewPower ManagementThe KSZ8851-16MLL supports enhanced power management feature in low power state with energy detection to ensure low-power dissipation during device idle periods. There are four operation modes under the power management function which is controlled by two bits in PMECR (0xD4) register as shown below:PMECR[1:0] = 00 Normal Operation ModePMECR[1:0] = 01 Energy Detect ModePMECR[1:0] = 10 Soft Power Down ModePMECR[1:0] = 11 Power Saving ModeTable 1 indicates all internal function blocks status under four different power management operation modes.Power Management Operation ModesKSZ8851-16MLLFunction Blocks Normal Mode Power Saving Mode Energy Detect Mode Soft Power Down ModeInternal PLL Clock Enabled Enabled Disabled Disabled Tx/Rx PHY Enabled Rx unused block disabled Energy detect at Rx Disabled MAC Enabled Enabled Disabled Disabled Host Interface Enabled Enabled Disabled DisabledTable 1. Internal Function Blocks StatusNormal Operation ModeThis is the default setting bit[1:0]=00 in PMECR register after the chip power-up or hardware reset (pin 67). When KSZ8851-16MLL is in this normal operation mode, all PLL clocks are running, PHY and MAC are on and the host interface is ready for CPU read or write.During the normal operation mode, the host CPU can set the bit[1:0] in PMECR register to transit the current normal operation mode to any one of the other three power management operation modes.Energy Detect ModeThe energy detect mode provides a mechanism to save more power than in the normal operation mode when the KSZ8851-16MLL is not connected to an active link partner. For example, if cable is not present or it is connected to a powered down partner, the KSZ8851-16MLL can automatically enter to the low power state in energy detect mode. Once activity resumes due to plugging a cable or attempting by the far end to establish link, the KSZ8851-16MLL can automatically power up to normal power state in energy detect mode.Energy detect mode consists of two states, normal power state and low power state. While in low power state, the KSZ8851-16MLL reduces power consumption by disabling all circuitry except the energy detect circuitry of the receiver. The energy detect mode is entered by setting bit[1:0]=01 in PMECR register. When the KSZ8851-16MLL is in this mode, it will monitor the cable energy. If there is no energy on the cable for a time longer than pre-configured value at bit[7:0] Go-Sleep time in GSWUTR register, KSZ8851-16MLL will go into a low power state. When KSZ8851-16MLL is in low power state, it will keep monitoring the cable energy. Once the energy is detected from the cable and is continuously presented for a time longer than pre-configured value at bit[15:8] Wake-Up time in GSWUTR register, the KSZ8851-16MLL will enter either the normal power state if the auto-wakeup enable bit[7] is set in PMECR register or the normal operation mode if both auto-wakeup enable bit[7] and wakeup to normal operation mode bit[6] are set in PMECR register.The KSZ8851-16MLL will also assert PME output pin if the corresponding enable bit[8] is set in PMECR (0xD4) register or。

VB300 G-Force Datalogger 用户手册说明书

User's Guide3-Axis G-Force Datalogger Model VB300IntroductionCongratulations on your purchase of the VB300 G-Force Datalogger. The Model VB300 can measure and record shock and vibration (acceleration) readings over its ± 18g measurement range. This device will record 3-axisg-force and related peaks to provide a history of shock and vibration conditions. The real time clock provides time stamps for all data.The user can easily configure the logging rate, high/low alarm and start-mode, and download the stored data by plugging the VB300 into a PC's USB port and running the supplied PC software. Measurement data can be plotted, printed and exported for use with other applications such as word processors and spreadsheets. The data logger is supplied with a long-life 1000 hour lithium battery.The VB300 memory uses a 4MB Flash device that can hold 85,764 peak acceleration samples and 210 freefall samples.This meter is shipped fully tested and calibrated and, with proper use, will provide years of reliable service.FeaturesRecords 3-axis g force shock and vibrationBuilt-in accelerometerMeasures static and dynamic accelerationReal time operation (time stamped data)Normal and Motion detection modeReal time FFT frequency analysisManual and Automatic datalogger start modesSelectable data sampling rateStatus Indication via Red and Green LEDsUSB Interface for Set-up and Data DownloadUser-Programmable motion thresholdsLong battery life - 1000 hoursDescriptionMeter Description1. USB connector2. RECORD LED3. ALARM LED4. Datalogger Start / Stop Button5. Axis reference diagramNote: Battery compartment access screws (2) located on rear of unit. Refer to the battery installation section for further details.Pedestal Mount Description1. Mounting screw holes2. Swivel latch3. Swivel latch lock4. Mounting magnetsFRONT VIEW REAR VIEWMounting the VB300The VB300 fits securely in the supplied mounting pedestal. Unscrew the pedestal latch and snap the VB300 into the pedestal. Secure the latch and follow one of the mounting methods below. There are three mounting methods for affixing the pedestal to the area under test:1. Magnetically: Powerful magnets are built into the rear of the pedestal2. Adhesive: Use glue (not supplied) to affix the pedestal to the area under test3. Screws: Three mounting holes are provided on the pedestal for screw mounting (screws not supplied) LED Status Indication* To save power, the VB300’s LED flashing cycle can be changed to via the supplied software.** To save power, alarm LEDs for temperature can be disabled via the supplied software.†When the battery is low, all operations will be disabled automatically. NOTE: Logging automatically stops when the battery weakens (logged data will be retained).Datalogging Software ProgramINSTALLING THE DATALOGGER SOFTWAREInstall the supplied Windows TM PC Datalogger Software by placing the supplied program disk in the PC’s CD-ROM drive. If the installation program does not automatically open and provide on-screen prompts (as shown in diagram below), open and browse the CD-ROM drive, then find and double-click on the SETUP.EXE file included on the program disk. Follow the on-screen prompts as shown below to complete the installation.Before running the datalogger software, please connect the VB300 to the PC and install the USB Driver software as described in the next section.INSTALLING THE USB DRIVERThe PC will prompt for the USB Driver installation immediately after the main software program is installed. A window similar to the one shown below will appear to prompt for the installation. Simply click INSTALL to continue.To install the driver manually, plug the VB300 into an available USB port on the PC. If this is the first time that the VB300 is connected to the particular port on the PC, the following screen will appear:Make sure the program disk is still in the PC CD-ROM drive. Select the ‘recommended’ installation and follow the on-screen prompts to complete the driver installation. If this is a repeat connection of the VB300 to the USB port, the driver installation process will be automatically skipped.RUNNING THE DATALOGGER SOFTWAREWith the VB300 inserted in the PC’s USB port, double-click the program icon (located on the desktop) to launch the program. The main software screen will appear.Instructions for using the Datalogger Software are contained in the HELP Utility available from the HELP menu in the software program. Please read the HELP Utility thoroughly in order to fully understand the software and the related functionality of the VB300.Note: When the VB300 is connected to the USB port, its battery discharges at a higher rate than normal. To conserve battery life, do not leave the VB300 connected to the USB port for a prolonged period of time.Basic Datalogger OperationThis section covers only the starting and stopping of the Datalogger’s recording functions. All other information is provided in the HELP utility within the software program.1. Configure the Datalogger’s sample rate, motion detection threshold, record mode, LED flash cycle and moreusing the supplied software program. Refer to the instructions included in the software program’s HELP utility to configure the datalogger and to otherwise use the software.2. If AUTO start is selected in the software, the datalogger will begin logging data the moment the softwarewindow is closed. If MANUAL is selected, press and hold the datalogger start/stop button until the green LED flashes; the datalogger LED flashes periodically (flash interval time selectable in software) indicating that the datalogger is recording.3. To stop datalogging, press and hold the start/stop button while the unit is datalogging. The red LED willquickly flash indicating that datalogging has stopped. Refer to the LED status table earlier in this manual for interpreting the LED flash information.4. Refer to the software HELP utility for transferring the data from the logger to the PC.1g OFFSETThe axis (or combination of axis) parallel to the earth surface will indicate the 1g force related to gravitational force.SpecificationsAcceleration Range: ± 18g Resolution: 0.00625gAccuracy ± 0.5gFrequency Range 0 to 60HzDatalog Memory 4MB Flash stores 85,764 peak acceleration recordsLogging rate Selectable sampling interval: From 50ms up to 24 hoursData format Time stamped peak acceleration and freefall; Average and Peak Vector sums Computer PC interface USBHardware requirements 8MB RAM; 2MB Hard Drive space for software program; USB jackSystem requirements Windows TM XP, VISTA, Windows TM 7 (32 and 64 bit)Operating temperature 32 to 104o F (0 to 40o C)Storage temperature 0 to 140o F (-10 to 60o C)Battery type 3.6V Lithium (1/2 AA)Power consumption 1mA (typical, while recording); < 15µA while idlingBattery life 1000 hours approx.Dimensions/Weight 3.7 x 1.1 x 0.8” (95 x 28 x 21mm) / 6oz (172g)Support line (781) 890-7440Technicalsupport:Extension200;E-mail:******************Repair&Returns:Extension210;E-mail:*****************Product specifications subject to change without noticeFor the latest version of this User Guide, Software updates, and other up-to-the-minute product information, visit our website: Extech Instruments Corporation, 285 Bear Hill Road, Waltham, MA 02451ISO9001 CertifiedBattery ReplacementThe VB300 does not lose its stored readings when the battery expires or when the battery is replaced. The data logging process will however be stopped and cannot be re-started until the battery has been replaced and the logged data has been downloaded to PC.The battery life is rated for approx. 1000 hours. If in doubt, replace the battery before logging critical data. Use only 3.6V lithium batteries. Before replacing the battery, remove the datalogger from the PC.Note: When the VB300 is connected to the USB port, its battery discharges at a higher rate than normal. Toconserve battery life, do not leave the VB300 connected to the USB port for a prolonged period of time .1. Remove the two Phillips screws identified with the two smaller arrows in the diagram below.2. Slide the battery compartment cover in the direction of the larger arrow.3. Replace the battery with one of the same type (3.6V lithium, ½ AA).4. Close the battery compartment and tighten with the two screws.WARNING: Handle lithium batteries carefully, observe warnings on battery casing. Dispose of in accordance with local regulations.WarrantyEXTECH INSTRUMENTS CORPORATION (A FLIR COMPANY) warrants this instrument to be free of defects in parts and workmanship for one year from date of shipment (a six month limited warranty applies to sensors and cables). If it should become necessary to return the instrument for service during or beyond the warranty period, contact the Customer Service Department at (781) 890-7440 ext. 210 for authorization or visit our website for contact information. A Return Authorization (RA) number must be issued before any product is returned to Extech. The sender is responsible for shipping charges, freight, insurance and proper packaging to prevent damage in transit. This warranty does not apply to defects resulting from action of the user such as misuse, improper wiring, operation outside of specification, improper maintenance or repair, or unauthorized modification. Extech specifically disclaims any implied warranties or merchantability or fitness for a specific purpose and will not be liable for any direct, indirect, incidental or consequential damages. Extech's total liability is limited to repair or replacement of the product. The warranty set forth above is inclusive and no other warranty, whether written or oral, is expressed or implied.Copyright © 2010 Extech Instruments Corporation (a FLIR company)All rights reserved including the right of reproduction in whole or in part in any form.。

ATA8-AST Draft Rev.3__T13