HT6116中文资料

TPS61161DRVT资料

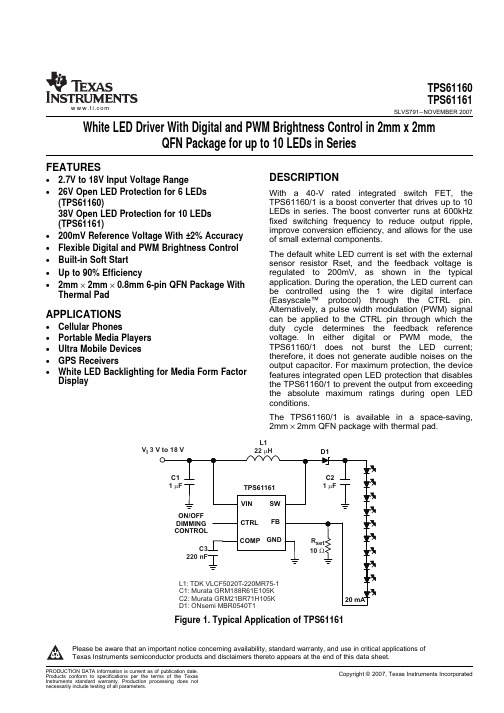

FEATURESDESCRIPTIONAPPLICATIONSV 3 V to 18 VI L1TPS61160TPS61161SLVS791–NOVEMBER 2007White LED Driver With Digital and PWM Brightness Control in 2mm x 2mmQFN Package for up to 10LEDs in Series• 2.7V to 18V Input Voltage Range•26V Open LED Protection for 6LEDs With a 40-V rated integrated switch FET,the TPS61160/1is a boost converter that drives up to 10(TPS61160)LEDs in series.The boost converter runs at 600kHz 38V Open LED Protection for 10LEDs fixed switching frequency to reduce output ripple,(TPS61161)improve conversion efficiency,and allows for the use •200mV Reference Voltage With ±2%Accuracy of small external components.•Flexible Digital and PWM Brightness Control The default white LED current is set with the external •Built-in Soft Start sensor resistor Rset,and the feedback voltage is regulated to 200mV,as shown in the typical •Up to 90%Efficiencyapplication.During the operation,the LED current can •2mm ×2mm ×0.8mm 6-pin QFN Package With be controlled using the 1wire digital interface Thermal Pad(Easyscale™protocol)through the CTRL pin.Alternatively,a pulse width modulation (PWM)signal can be applied to the CTRL pin through which the •Cellular Phonesduty cycle determines the feedback reference voltage.In either digital or PWM mode,the •Portable Media Players TPS61160/1does not burst the LED current;•Ultra Mobile Devices therefore,it does not generate audible noises on the •GPS Receiversoutput capacitor.For maximum protection,the device •White LED Backlighting for Media Form Factor features integrated open LED protection that disables Displaythe TPS61160/1to prevent the output from exceeding the absolute maximum ratings during open LED conditions.The TPS61160/1is available in a space-saving,2mm ×2mm QFN package with thermal pad.Figure 1.Typical Application of TPS61161Please be aware that an important notice concerning availability,standard warranty,and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.PRODUCTION DATA information is current as of publication date.Copyright ©2007,Texas Instruments IncorporatedProducts conform to specifications per the terms of the Texas Instruments standard warranty.Production processing does not necessarily include testing of all parameters.ABSOLUTE MAXIMUM RATINGSDISSIPATION RATINGSRECOMMENDED OPERATING CONDITIONSTPS61160TPS61161SLVS791–NOVEMBER 2007These devices have limited built-in ESD protection.The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.ORDERING INFORMATION (1)T AOPEN LED PROTECTIONPACKAGE (2)PACKAGE MARKING26V (typical)TPS61160DRV BZQ –40°C to 85°C 38V (typical)TPS61161DRVBZR(1)For the most current package and ordering information,see the TI Web site at .(2)The DRV package is available in tape and reel.Add R suffix (TPS61160DRVR)to order quantities of 3000parts per reel or add T suffix (TPS61160DRVT)to order 250parts per reel.over operating free-air temperature range (unless otherwise noted)(1)VALUE UNIT Supply Voltages on VIN(2)–0.3to 20V Voltages on CTRL (2)–0.3to 20V V IVoltage on FB and COMP (2)–0.3to 3V Voltage on SW (2)–0.3to 40V P D Continuous Power DissipationSee Dissipation Rating TableT J Operating Junction Temperature Range –40to 150°C T STG Storage Temperature Range–65to 150°C(1)Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device.These are stress ratings only,and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied.Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.(2)All voltage values are with respect to network ground terminal.DERATING FACTOR BOARD PACKAGER θJC R θJA T A <25°C T A =70°C T A =85°C ABOVE T A =25°CLow-K (1)DRV 20°C/W 140°C/W 7.1mW/°C 715mW 395mW 285mW High-K (2)DRV20°C/W65°C/W15.4mW/°C1540mW845mW615mW(1)The JEDEC low-K (1s)board used to derive this data was a 3in ×3in,two-layer board with 2-ounce copper traces on top of the board.(2)The JEDEC high-K (2s2p)board used to derive this data was a 3in ×3in,multilayer board with 1-ounce internal power and ground planes and 2-ounce copper traces on top and bottom of the board.MINTYP MAX UNIT V I Input voltage range,VIN 2.718V V O Output voltage range VIN 38V L Inductor(1)1022µH f dim PWM dimming frequency 5100kHz C IN Input capacitor 1µF C O Output capacitor(1)0.4710µF T A Operating ambient temperature –4085°C T J Operating junction temperature–40125°C(1)These values are recommended values that have been successfully tested in several applications.Other values may be acceptable in other applications but should be fully tested by the user.2Submit Documentation FeedbackCopyright ©2007,Texas Instruments IncorporatedProduct Folder Link(s):TPS61160TPS61161ELECTRICAL CHARACTERISTICSTPS61160TPS61161 SLVS791–NOVEMBER2007VIN=3.6V,CTRL=VIN,T A=–40°C to85°C,typical values are at T A=25°C(unless otherwise noted)PARAMETER TEST CONDITIONS MIN TYP MAX UNITSUPPLY CURRENTV I Input voltage range,VIN 2.718VI Q Operating quiescent current into VIN Device PWM switching no load 1.8mAI SD Shutdown current CRTL=GND,VIN=4.2V1µA UVLO Undervoltage lockout threshold VIN falling 2.2 2.5VV hys Undervoltage lockout hysterisis70mV ENABLE AND REFERENCE CONTROLV(CTRLh)CTRL logic high voltage VIN=2.7V to18V 1.2VV(CTRLl)CTRL logic low voltage VIN=2.7V to18V0.4VR(CTRL)CTRL pull down resistor4008001600kΩt off CTRL pulse width to shutdown CTRL high to low 2.5mst es_det Easy Scale detection time(1)CTRL pin low260µst es_delay Easy Scale detection delay100µst es_win Easy Scale detection window time Measured from CTRL high1ms VOLTAGE AND CURRENT CONTROLV REF Voltage feedback regulation voltage196200204mVV(REF_PWM)Voltage feedback regulation voltage under V FB=50mV475053mV brightness control VFB=20mV172023I FB Voltage feedback input bias current V FB=200mV2µAf S Oscillator frequency500600700kHzD max Maximum duty cycle V FB=100mV90%93%t min_on Minimum on pulse width40nsI sink Comp pin sink current100µAI source Comp pin source current100µAG ea Error amplifier transconductance240320400umhoR ea Error amplifier output resistance6MΩf ea Error amplifier crossover frequency5pF connected to COMP500kHz POWER SWITCHN-channel MOSFET on-resistance VIN=3.6V0.30.6R DS(on)ΩVIN=3.0V0.7I LN_NFET N-channel leakage current V SW=35V,T A=25°C1µAOC and OLPI LIM N-Channel MOSFET current limit D=D max0.560.70.84AI LIM_Start Start up current limit D=D max0.4At Half_LIM Time step for half current limit5msV ovp Open LED protection threshold Measured on the SW pin,TPS61160252627VTPS61161373839Open LED protection threshold on FB Measured on the FB pin,percentageV(FB_OVP)50%of Vref,Vref=200mV and20mVt REF V REF filter time constant180µst step VREF ramp up time213µs (1)To select EasyScale™mode,the CTRL pin has to be low for more than t es_det during t es_winCopyright©2007,Texas Instruments Incorporated Submit Documentation Feedback3Product Folder Link(s):TPS61160TPS61161DEVICE INFORMATIONVINCTRLSWFBCOMP GND TOPVIEW6-PIN 2mm x 2mm x 0.8mm QFNTPS61160TPS61161SLVS791–NOVEMBER 2007ELECTRICAL CHARACTERISTICS (continued)VIN =3.6V,CTRL =VIN,T A =–40°C to 85°C,typical values are at T A =25°C (unless otherwise noted)PARAMETERTEST CONDITIONS MIN TYP MAX UNIT EasyScale TIMING t start Start time of program stream 2µst EOS End time of program stream 2360µs t H_LB High time low bit Logic 02180µs t L_LB Low time low bit Logic 02×t H_LB 360µs t H_HB High time high bit Logic 12×t L_HB360µs t L_HB Low time high bitLogic 12180µs V ACKNL Acknowledge output voltage low Open drain,Rpullup =15k Ωto VIN 0.4V t valACKN Acknowledge valid timeSee (2)2µs t ACKN Duration of acknowledge condition See(2)512µs THERMAL SHUTDOWNT shutdown Thermal shutdown threshold160°C T hysteresis Thermal shutdown threshold hysteresis15°C(2)Acknowledge condition active 0,this condition will only be applied in case the RFA bit is set.Open drain output,line needs to be pulled high by the host with resistor load.TERMINAL FUNCTIONSTERMINAL I/O DESCRIPTIONNAME NO.VIN 6I The input supply pin for the IC.Connect VIN to a supply voltage between 2.7V and 18V.This is the switching node of the IC.Connect the inductor between the VIN and SW pin.This pin is also SW 4I used to sense the output voltage for open LED protection GND 3O GroundFB 1I Feedback pin for current.Connect the sense resistor from FB to GND.Output of the transconductance error amplifier.Connect an external capacitor to this pin to compensate the COMP 2O regulator.Control pin of the boost regulator.It is a multi-functional pin which can be used for enable control,PWM CTRL 5Iand digital dimming.The thermal pad should be soldered to the analog ground plane.If possible,use thermal via to connect to Thermal Padground plane for ideal power dissipation.4Submit Documentation FeedbackCopyright ©2007,Texas Instruments IncorporatedProduct Folder Link(s):TPS61160TPS61161FUNCTIONAL BLOCK DIAGRAMC2C1TYPICAL CHARACTERISTICSTABLE OF GRAPHSTPS61160TPS61161SLVS791–NOVEMBER 2007FIGUREEfficiency TPS61160/1VIN =3.6V;4,6,8,10LEDs;L =22µHFigure 2Efficiency TPS61160Figure 3Efficiency TPS61161Figure 4Current limit T A =25°CFigure 5Current limit Figure 6Easyscale step Figure 7PWM dimming linearity VIN =3.6V;PWM Freq =10kHz and 40kHzFigure 7Output ripple at PWM dimming 8LEDs;VIN =3.6V;I LOAD =20mA;PWM Freq =10kHz Figure 9Switching waveform 8LEDs;VIN =3.6V;I LOAD =20mA;L =22µH Figure 10Start-up8LEDs;VIN =3.6V;I LOAD =20mA;L =22µH Figure 11Open LED protection8LEDs;VIN =3.6V;I LOAD =20mA;L =22µH Figure 12Copyright ©2007,Texas Instruments Incorporated Submit Documentation Feedback5Product Folder Link(s):TPS61160TPS611614050607080901001020304050Output Current - mAE f f i c i e n c y - %4050607080901001020304050Output Current - mAE f f i c i e n c y - %30040050060070080090010002030405060708090Duty Cycle - %S w i t c h C u r r e n t L i m i t - mA405060708090100Output Current - mAE f f i c i e n c y -%3004005006007008009001000-40-2020406080100120140Temperature -C°S w i t c h C u r r e n t L i m i t - mA2040608010012014016018020002468101214161820222426283032Easy Scale Step StepF B V o l t a g e - m VTPS61160TPS61161SLVS791–NOVEMBER 2007EFFICIENCYEFFICIENCYvsvsOUTPUT CURRENTOUTPUT CURRENTFigure 2.Figure 3.EFFICIENCYSWITCH CURRENT LIMITvsvsOUTPUT CURRENTDUTY CYCLEFigure 4.Figure 5.SWITCH CURRENT LIMITFB VOLTAGEvsvsTEMPERATUREEASYSCALE STEPFigure 6.Figure 7.6Submit Documentation FeedbackCopyright ©2007,Texas Instruments IncorporatedProduct Folder Link(s):TPS61160TPS61161t - 100s/divm0408012016020020406080100PWM Duty Cycle - %F B V o l ta g e - m Vt - 2 ms/divt - 1s/divmt - 100s/divm TPS61160TPS61161SLVS791–NOVEMBER 2007FB VOLTAGEvsPWM DUTY CYCLEOUTPUT RIPPLE at PWM DIMMINGFigure 8.Figure 9.SWITCHING WAVEFORMSTART-UPFigure 10.Figure 11.OPEN LED PROTECTIONFigure 12.Copyright ©2007,Texas Instruments Incorporated Submit Documentation Feedback7Product Folder Link(s):TPS61160TPS61161DETAILED DESCRIPTIONOPERATIONSOFT START-UPOPEN LED PROTECTIONSHUTDOWNCURRENT PROGRAMI LED+V FBR SET(1)TPS61160TPS61161SLVS791–NOVEMBER2007The TPS61160/1is a high efficiency,high output voltage boost converter in small package size,The device is ideal for driving up to10white LED in series.The serial LED connection provides even illumination by sourcing the same output current through all LEDs,eliminating the need for expensive factory calibration.The device integrates40V/0.7A switch FET and operates in pulse width modulation(PWM)with600kHz fixed switching frequency.For operation see the block diagram.The duty cycle of the converter is set by the error amplifier output and the current signal applied to the PWM control comparator.The control architecture is based on traditional current-mode control;therefore,a slope compensation is added to the current signal to allow stable operation for duty cycles larger than50%.The feedback loop regulates the FB pin to a low reference voltage (200mV typical),reducing the power dissipation in the current sense resistor.Soft-start circuitry is integrated into the IC to avoid a high inrush current during start-up.After the device is enabled,the voltage at FB pin ramps up to the reference voltage in32steps,each step takes213µs.This ensures that the output voltage rises slowly to reduce the input current.Additionally,for the first5msec after the COMP voltage ramps,the current limit of the switch is set to half of the normal current limit spec.During this period,the input current is kept below400mA(typical).See the start-up waveform of a typical example, Figure11.Open LED protection circuitry prevents IC damage as the result of white LED disconnection.The TPS61160/1 monitors the voltage at the SW pin and FB pin during each switching cycle.The circuitry turns off the switch FET and shuts down the IC as soon as the SW voltage exceeds the Vovp threshold and the FB voltage is less than half of regulation voltage for8clock cycles.As a result,the output voltage falls to the level of the input supply. The device remains in shutdown mode until it is enabled by toggling the CTRL pin logic.To allow the use of inexpensive low-voltage output capacitor,the TPS61160/1has different open lamp protection thresholds to prevent the internal40V FET from breaking down.The threshold is set at26V for the TPS61160and38V for the TPS61161.The devices can be selected according to the number of external LEDs and their maximum forward voltage.The TPS61160/1enters shutdown mode when the CTRL voltage is logic low for more than2.5ms.During shutdown,the input supply current for the device is less than1µA(max).Although the internal FET does not switch in shutdown,there is still a DC current path between the input and the LEDs through the inductor and Schottky diode.The minimum forward voltage of the LED array must exceed the maximum input voltage to ensure that the LEDs remain off in shutdown.However,in the typical application with two or more LEDs,the forward voltage is large enough to reverse bias the Schottky and keep leakage current low.The FB voltage is regulated by a low0.2V reference voltage.The LED current is programmed externally using a current-sense resistor in series with the LED string.The value of the RSET is calculated using Equation1:WhereI LED=output current of LEDsV FB=regulated voltage of FBR SET=current sense resistorThe output current tolerance depends on the FB accuracy and the current sensor resistor accuracy.8Submit Documentation Feedback Copyright©2007,Texas Instruments IncorporatedProduct Folder Link(s):TPS61160TPS61161LED BRIGHTNESS DIMMING MODE SELECTIONCTRLlowhighFB200mV x duty cycleInsert batteryCTRLlowhighFBInsert batteryProgrammingcode50mV 50mVEnter ES modeV FB +Duty 200mV (2)TPS61160TPS61161SLVS791–NOVEMBER 2007The CTRL pin is used for the control input for both dimming modes,PWM dimming and 1wire dimming.The dimming mode for the TPS61160/1is selected each time the device is enabled.The default dimming mode is PWM dimming.To enter the 1wire mode,the following digital pattern on the CTRL pin must be recognized by the IC every time the IC starts from the shutdown mode.1.Pull CTRL pin high to enable the TPS61160/1,and to start the 1wire detection window.2.After the EasyScale detection delay (t es_delay ,100µs)expires,drive CTRL low for more than the EasyScale detection time (t es_detect ,260µs).3.The CTRL pin has to be low for more than EasyScale detection time before the EasyScale detection window (t es_win ,1msec)expires.EasyScale detection window starts from the first CTRL pin low to high transition.The IC immediately enters the 1wire mode once the above 3conditions are met.the EasyScale communication can start before the detection window expires.Once the dimming mode is programmed,it can not be changed without another start up.This means the IC needs to be shutdown by pulling the CTRL low for 2.5ms and restarts.See the Dimming Mode Detection and Soft Start (Figure 13)for a graphical explanation.Figure 13.Dimming Mode Detection and Soft Start PWM Brightness DimmingWhen the CTRL pin is constantly high,the FB voltage is regulated to 200mV typically.However,the CTRL pinallows a PWM signal to reduce this regulation voltage;therefore,it achieves LED brightness dimming.The relationship between the duty cycle and FB voltage is given by Equation 2.WhereDuty =duty cycle of the PWM signal 200mV =internal reference voltageAs shown in Figure 14,the IC chops up the internal 200mV reference voltage at the duty cycle of the PWM signal.The pulse signal is then filtered by an internal low pass filter.The output of the filter is connected to the error amplifier as the reference voltage for the FB pin regulation.Therefore,although a PWM signal is used for brightness dimming,only the WLED DC current is modulated,which is often referred as analog dimming.This eliminates the audible noise which often occurs when the LED current is pulsed in replica of the frequency and duty cycle of PWM control.Unlike other scheme which filters the PWM signal for analog dimming,TPS61160/1regulation voltage is independent of the PWM logic voltage level which often has large variations.Copyright ©2007,Texas Instruments Incorporated Submit Documentation Feedback9Product Folder Link(s):TPS61160TPS61161VBGDIGITAL1WIRE BRIGHTNESS DIMMINGEasyScale™:1WIRE DIGITAL DIMMINGTPS61160TPS61161SLVS791–NOVEMBER2007For optimum performance,use the PWM dimming frequency in the range of5kHz to100kHz.The requirement of minimum dimming frequency comes from the EasyScale detection delay and detection time specification in the dimming mode selection.Since the CTRL pin is logic only pin,adding external RC filter applied to the pin does not work.Figure14.Block Diagram of Programmable FB Voltage Using PWM SignalTo use lower PWM dimming,add an external RC network connected to the FB pin as shown in the additional typical application(Figure19).The CTRL pin features a simple digital interface to allow digital brightness control.The digital dimming can save the processor power and battery life as it does not require a PWM signal all the time,and the processor can enter idle mode if available.The TPS61160/1adopts the EasyScale™protocol for the digital dimming,which can program the FB voltage to any of the32steps with single command.The step increment increases with the voltage to produce pseudo logarithmic curve for the brightness step.See the Table1for the FB pin voltage steps.The default step is full scale when the device is first enabled(V FB=200mV).The programmed reference voltage is stored in an internal register.A power reset clears the register value and reset it to default.EasyScale is a simple but flexible one pin interface to configure the FB voltage.The interface is based on a master-slave structure,where the master is typically a microcontroller or application processor.Figure15and Table2give an overview of the protocol.The protocol consists of a device specific address byte and a data byte. The device specific address byte is fixed to72hex.The data byte consists of five bits for information,two address bits,and the RFA bit.The RFA bit set to high indicates the Request for Acknowledge condition.The Acknowledge condition is only applied if the protocol was received correctly.The advantage of EasyScale compared with other on pin interfaces is that its bit detection is in a large extent independent from the bit transmission rate.It can automatically detect bit rates between1.7kBit/sec and up to160kBit/sec.Table1.Selectable FB VoltageFB voltageD4D3D2D1D0(mV)00000001500001280001031100011414001005170010162000110723001118260100010Submit Documentation Feedback Copyright©2007,Texas Instruments IncorporatedProduct Folder Link(s):TPS61160TPS61161DATA INDATA OUT TPS61160TPS61161SLVS791–NOVEMBER 2007Table 1.Selectable FB Voltage (continued)FB voltage D4D3D2D1D0(mV)92901001103201010113501011123801100134401101145001110155601111166210000176810001187410010198010011208610100219210101229810110231041011124116110002512811001261401101027152110112816411100291761110130188111103120011111Figure 15.EasyScale™Protocol Overview Table 2.EasyScale™Bit DescriptionBIT TRANSMISSION BYTENAME DESCRIPTIONNUMBERDIRECTION7DA70MSB device address 6DA615DA51Device 4DA41Address INByte 3DA3072hex2DA201DA11DA00LSB device addressCopyright ©2007,Texas Instruments Incorporated Submit Documentation Feedback11Product Folder Link(s):TPS61160TPS61161Easy Scale Timing, without acknowledge RFA= 0DATA INEasy Scale Timing, with acknowledge RFA = 1Acknowledge true , Data Line pulled down by device DATA INDATA Acknowledge false , no pull downTPS61160TPS61161SLVS791–NOVEMBER 2007Table 2.EasyScale™Bit Description (continued)BIT TRANSMISSION BYTENAME DESCRIPTIONNUMBER DIRECTION7(MSB)RFA Request for acknowledge.If high,acknowledge is applied by device6A10Address bit 15A00Address bit 04D4Data bit 4Data byteIN3D3Data bit 32D2Data bit 21D1Data bit 10(LSB)D0Data bit 0Acknowledge condition active 0,this condition will only be applied in case RFA bit is set.Open drain output,Line needs to be pulled high by the host with a pullupACKOUT resistor.This feature can only be used if the master has an open drain output stage.In case of a push pull output stage Acknowledge condition may not be requested!Figure 16.EasyScale™—Bit Coding12Submit Documentation FeedbackCopyright ©2007,Texas Instruments IncorporatedProduct Folder Link(s):TPS61160TPS61161UNDERVOLTAGE LOCKOUT THERMAL SHUTDOWNTPS61160TPS61161 SLVS791–NOVEMBER2007All bits are transmitted MSB first and LSB last.Figure16shows the protocol without acknowledge request(Bit RFA=0),Figure16with acknowledge(Bit RFA=1)request.Prior to both bytes,device address byte and data byte,a start condition must be applied.For this,the CTRL pin must be pulled high for at least t start(2µs)before the bit transmission starts with the falling edge.If the CTRL pin is already at high level,no start condition is needed prior to the device address byte.The transmission of each byte is closed with an End of Stream condition for at least t EOS(2µs).The bit detection is based on a Logic Detection scheme,where the criterion is the relation between t LOW and t HIGH.It can be simplified to:High Bit:t HIGH>t LOW,but with t HIGH at least2x t LOW,see Figure16.Low Bit:t HIGH<t LOW,but with t LOW at least2x t HIGH,see Figure16.The bit detection starts with a falling edge on the CTRL pin and ends with the next falling edge.Depending on the relation between t HIGH and t LOW,the logic0or1is detected.The acknowledge condition is only applied if:•Acknowledge is requested by a set RFA bit.•The transmitted device address matches with the device address of the device.•16bits is received correctly.If the device turns on the internal ACKN-MOSFET and pulls the CTRL pin low for the time t ACKN,which is512µs maximum then the Acknowledge condition is valid after an internal delay time t valACK.This means that the internal ACKN-MOSFET is turned on after t valACK,when the last falling edge of the protocol was detected.The master controller keeps the line low in this period.The master device can detect the acknowledge condition with its input by releasing the CTRL pin after t valACK and read back a logic0.The CTRL pin can be used again after the acknowledge condition ends.Note that the acknowledge condition may only be requested in case the master device has an open drain output. For a push-pull output stage,the use a series resistor in the CRTL line to limit the current to500µA is recommended to for such cases as:•an accidentally requested acknowledge,or•to protect the internal ACKN-MOSFET.An undervoltage lockout prevents operation of the device at input voltages below typical2.2V.When the input voltage is below the undervoltage threshold,the device is shutdown and the internal switch FET is turned off.If the input voltage rises by undervoltage lockout hysteresis,the IC restarts.An internal thermal shutdown turns off the device when the typical junction temperature of160°C is exceeded. The device is released from shutdown automatically when the junction temperature decreases by15°C.Copyright©2007,Texas Instruments Incorporated Submit Documentation Feedback13Product Folder Link(s):TPS61160TPS61161APPLICATION INFORMATIONMAXIMUM OUTPUT CURRENTúûùêëé+-+´´=)V 1V V V 1(F L 1I in in f out s P (3)I out_max +Vin ǒI lim *I P ń2Ǔ hVout(4)INDUCTOR SELECTIONI in_DC +Vout IoutVin h (5)TPS61160TPS61161SLVS791–NOVEMBER 2007The overcurrent limit in a boost converter limits the maximum input current and thus maximum input power for a given input voltage.Maximum output power is less than maximum input power due to power conversion losses.Therefore,the current limit setting,input voltage,output voltage and efficiency can all change maximum current output.The current limit clamps the peak inductor current;therefore,the ripple has to be subtracted to derive maximum DC current.The ripple current is a function of switching frequency,inductor value and duty cycle.The following equations take into account of all the above factors for maximum output current calculation.Where:I p =inductor peak to peak ripple L =inductor valueV f =Schottky diode forward voltage Fs =switching frequencyV out =output voltage of the boost converter.It is equal to the sum of VFB and the voltage drop across LEDs.Where:I out_max =maximum output current of the boost converter I lim =over current limit η=efficiencyFor instance,when VIN is 3.0V,8LEDs output equivalent to VOUT of 26V,the inductor is 22µH,the Schottky forward voltage is 0.2V;and then the maximum output current is 65mA in typical condition.When VIN is 5V,10LEDs output equivalent to VOUT of 32V,the inductor is 22µH,the Schottky forward voltage is 0.2V;and then the maximum output current is 85mA in typical condition.The selection of the inductor affects steady state operation as well as transient behavior and loop stability.These factors make it the most important component in power regulator design.There are three important inductor specifications,inductor value,DC resistance and saturation current.Considering inductor value alone is not enough.The inductor value determines the inductor ripple current.Choose an inductor that can handle the necessary peak current without saturating,according to half of the peak-to-peak ripple current given by Equation 3,pause the inductor DC current given by:Inductor values can have ±20%tolerance with no current bias.When the inductor current approaches saturationlevel,its inductance can decrease 20%to 35%from the 0A value depending on how the inductor vendor defines saturation ing an inductor with a smaller inductance value forces discontinuous PWM when the inductor current ramps down to zero before the end of each switching cycle.This reduces the boost converter’s maximum output current,causes large input voltage ripple and reduces rge inductance value provides much more output current and higher conversion efficiency.For these reasons,a 10µH to 22µH inductor value range is recommended.A 22µH inductor optimized the efficiency for most application while maintaining low inductor peak to peak ripple.Table 3lists the recommended inductor for the TPS61160/1.When recommending inductor value,the factory has considered –40%and +20%tolerance from its nominal value.14Submit Documentation FeedbackCopyright ©2007,Texas Instruments IncorporatedProduct Folder Link(s):TPS61160TPS61161。

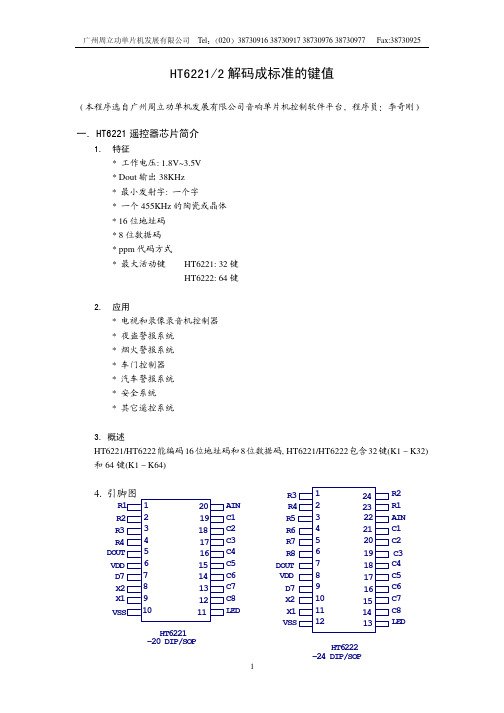

HT6221芯片中文资料

MOV

C,KREM

MOV

R3,#4

MOV

R0,#1DH

BYTE4:

MOV

A,@R0

RLC

A

MOV

@R0,A

DEC

R0

DJNZ

R3,BYTE4

DJNZ

R2,BYTE1

;至此 32 位代码已全部接收完成 并存放在 1AH~1DH 中

依次为低 8 位地址码 高 8 位地址码 8 位数据码

8 位数据的反代码

2 根 据码的格式 应该等待 9ms 的起始码和 4.5ms 的结果码完成后才能读码 3 从 上述两点 我们可得到解码程序的流程图

KREM=0

9ms Y

N

6ms,

Y 6ms

0.9ms

(

),

N 32

这样接收到的仅仅是普通的代码 要得到标准的键值 还必须进行代码识别和代码 转换 下面是从代码接收到获得标准值的子程

VDD

Pull-Low

CMOS IN Pull-Low

CMOS IN

CMOS OUT VDD

OSCILLATOR

X1

X2

10M

EN

2

广州周立功单片机发展有限公司 Tel 020 38730916 38730917 38730976 38730977 Fax:38730925

二 代码的特征

1 HT6221 键码的形成 当一个键按下超过 36ms 振荡器使芯片激活 如果这个键按下且延迟大约 108ms, 这 108ms 发射代码由一个起始码 9ms ,一个结果码 4.5ms ,低 8 位地址码 9ms~18ms ,高 8 位地址码 9ms~18ms ,8 位数据码 9ms~18ms 和这 8 位数 据的反码 9ms~18ms 组成 如果键按下超过 108ms 仍未松开 接下来发射的 代码 连发代码 将仅由起始码 9ms 和结束码 2.5ms 组成

高尔斯泵安装、操作和维护手册 Model HT 3196 i-FRAME说明书

安装、运行及维护手册

Model HT 3196 i-F.................................................................................................................................................................4 安全.....................................................................................................................................................................................4 安全警示等级...............................................................................................................................................................4 环境安全........................................................................................................................................................................4 用户健康与安全...........................................................................................................................................................5 易爆环境中防爆产品的安全规定...........................................................................................................................7 产品认证标准..................................................................................................................................................................8 CSA 合格证书..................................................................................................................................................................9 产品保修.........................................................................................................................................................................11

XC6106C418中文资料

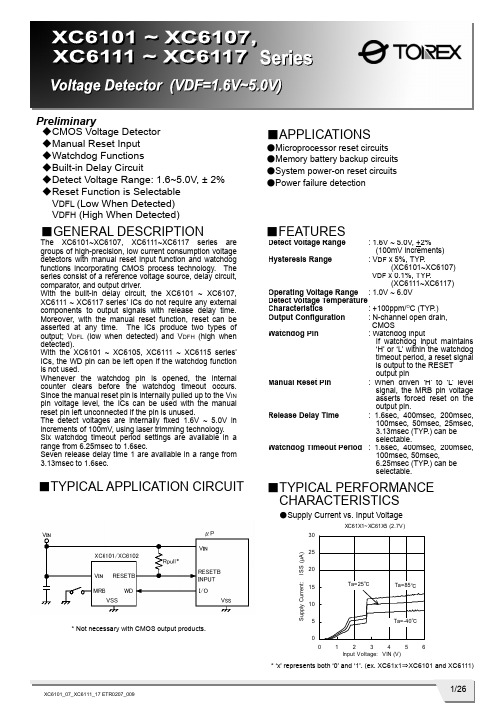

1/26XC6101_07_XC6111_17 ETR0207_009Preliminary◆CMOS Voltage Detector◆Manual Reset Input ◆Watchdog Functions ◆Built-in Delay Circuit ◆Detect Voltage Range: 1.6~5.0V, ± 2% ◆Reset Function is Selectable V DFL (Low When Detected) V DFH (High When Detected)■GENERAL DESCRIPTION The XC6101~XC6107, XC6111~XC6117 series aregroups of high-precision, low current consumption voltage detectors with manual reset input function and watchdog functions incorporating CMOS process technology. The series consist of a reference voltage source, delay circuit, comparator, and output driver.With the built-in delay circuit, the XC6101 ~ XC6107, XC6111 ~ XC6117 series’ ICs do not require any external components to output signals with release delay time. Moreover, with the manual reset function, reset can be asserted at any time. The ICs produce two types of output; V DFL (low when detected) and V DFH (high when detected).With the XC6101 ~ XC6105, XC6111 ~ XC6115 series’ ICs, the WD pin can be left open if the watchdog function is not used. Whenever the watchdog pin is opened, the internal counter clears before the watchdog timeout occurs. Since the manual reset pin is internally pulled up to the V IN pin voltage level, the ICs can be used with the manual reset pin left unconnected if the pin is unused.The detect voltages are internally fixed 1.6V ~ 5.0V in increments of 100mV, using laser trimming technology. Six watchdog timeout period settings are available in a range from 6.25msec to 1.6sec. Seven release delay time 1 are available in a range from 3.13msec to 1.6sec.■APPLICATIONS●Microprocessor reset circuits●Memory battery backup circuits ●System power-on reset circuits ●Power failure detection■TYPICAL APPLICATION CIRCUIT* Not necessary with CMOS output products.■FEATURESDetect Voltage Range: 1.6V ~ 5.0V, +2% (100mV increments)Hysteresis Range : V DF x 5%, TYP .(XC6101~XC6107)V DF x 0.1%, TYP .(XC6111~XC6117)Operating Voltage Range : 1.0V ~ 6.0V Detect Voltage Temperature Characteristics : +100ppm/O C (TYP .) Output Configuration : N-channel open drain,CMOSWatchdog Pin : Watchdog inputIf watchdog input maintains ‘H’ or ‘L’ within the watchdog timeout period, a reset signal is output to the RESET output pinManual Reset Pin : When driven ‘H’ to ‘L’levelsignal, the MRB pin voltage asserts forced reset on theoutput pin.Release Delay Time : 1.6sec, 400msec, 200msec,100msec, 50msec, 25msec, 3.13msec (TYP .) can be selectable.Watchdog Timeout Period : 1.6sec, 400msec, 200msec,100msec, 50msec,6.25msec (TYP .) can be selectable.■TYPICAL PERFORMANCE CHARACTERISTICS ●Supply Current vs. Input Voltage* ‘x’ represents both ‘0’ and ‘1’. (ex. XC61x1⇒XC6101 and XC6111)2/26XC6101~XC6107, XC6111~XC6117 SeriesPIN NUMBERXC6101, XC6102 XC6103 XC6104, XC6105XC6106, XC6107XC6111, XC6112 XC6113 XC6114, XC6115XC6116, XC6117SOT-25 USP-6C SOT-25 USP-6C SOT-25 USP-6C SOT-25USP-6CPIN NAMEFUNCTION1 4 - - 1 4 1 4 R ESETB Reset Output(V DFL : Low Level When Detected)2 5 2 5 2 5 2 5 V SSGround3 2 3 2 - -4 1 M RB ManualReset 4 1 4 1 4 1 - - WDWatchdog5 6 5 6 5 6 5 6 V IN Power Input - - 1 4 3 2 3 2 RESETReset Output (V DFH: High Level When Detected)■PIN CONFIGURATION SOT-25 (TOP VIEW)MRBV IN WD RESETBV SSMRBWD RESETV SSV IN RESETWD RESETBV SS V IN SOT-25 (TOP VIEW)RESETMRB RESETBV SS V IN SOT-25 (TOP VIEW) ■PIN ASSIGNMENT●SOT-25XC6101, XC6102 SeriesXC6111, XC6112 SeriesSOT-25 (TOP VIEW)XC6103 & XC6113 SeriesXC6104, XC6105 Series XC6114, XC6115 SeriesXC6106, XC6107 Series XC6116, XC6117 Series●USP-6CXC6101, XC6102 Series XC6111, XC6112 SeriesXC6103 & XC6113 SeriesXC6104, XC6105 Series XC6114, XC6115 SeriesXC6106, XC6107 Series XC6116, XC6117 SeriesUSP-6C (BOTTOM VIEW)USP-6C (BOTTOM VIEW)USP-6C (BOTTOM VIEW)USP-6C (BOTTOM VIEW)* The dissipation pad for the USP-6C package should be solder-plated in recommended mount pattern and metal masking so as to enhance mounting strength and heat release. If the pad needs to be connected to other pins, it should be connected to the V SS pin.3/26XC6101 ~ XC6107, XC6111~ XC6117SeriesRESET OUTPUTSERIES WATCHDOGMANUAL RESET V DFL (RESETB)V DFH (RESET)XC6101 XC6111 Available Available CMOS - XC6102XC6112AvailableAvailableN-channel open drain-XC6103 XC6113 Available Available - CMOS XC6104 XC6114 Available Not AvailableCMOS CMOS XC6105 XC6115 Available Not Available N-channel open drain CMOS XC6106 XC6116 Not Available AvailableCMOSCMOS XC6107XC6117Not AvailableAvailableN-channel open drainCMOSDESIGNATORDESCRIPTIONSYMBOLDESCRIPTION0 : V DF x 5% (TYP .) with hysteresis ① Hysteresis Range1 : V DF x 0.1% (TYP .) without hysteresis② Functions and Type of Reset Output1 ~ 7: Watchdog and manual functions, and reset output type as per Selection Guide in the above chartA : 3.13msec (TYP .)B : 25msec (TYP .) C: 50msec (TYP .) D : 100msec (TYP .) E : 200msec (TYP .) F : 400msec (TYP .) ③ Release Delay Time * H : 1.6sec (TYP .)0 : No WD timeout period forXC6106, XC6107, XC6116, XC6117 Series 1: 6.25msec (TYP .) 2 : 50msec (TYP .) 3 : 100msec (TYP .) 4 : 200msec (TYP .) 5 : 400msec (TYP .) ④ Watchdog Timeout Period6: 1.6sec (TYP .) ⑤⑥ Detect Voltage 16 ~ 50: Detect voltageex.) 4.5V: ⑤⇒4, ⑥⇒5M : SOT-25 ⑦ Package E : USP-6C R : Embossed tape, standard feed ⑧ Device OrientationL: Embossed tape, reverse feed* Please set the release delay time shorter than or equal to the watchdog timeout period. ex.) XC6101D427MR or XC6101D327MR■PRODUCT CLASSIFICATION ●Selection Guide ●Ordering Information XC61①②③④⑤⑥⑦⑧4/26XC6101~XC6107, XC6111~XC6117 Series■PACKAGING INFORMATION●SOT-25●USP-6C5/26XC6101 ~ XC6107, XC6111~ XC6117Series④ Represents production lot number0 to 9 and A to Z and inverted 0 to 9 and A to Z repeated. (G, I, J, O, Q, W expected.) * ‘X’ represents both ‘0’ and ‘1’. (ex. XC61X1⇒XC6101 and XC6111)■MARKING RULE●SOT-25①②③④SOT-25 (TOP VIEW)6/26XC6101~XC6107, XC6111~XC6117 Series① Represents product series② Represents release delay time MARK RELEASE DELAY TIME PRODUCT SERIES A 3.13msec XC61XxAxxxxx B 25msec XC61XxBxxxxx C 50msec XC61XxCxxxxx D 100msec XC61XxDxxxxx E 200msec XC61XxExxxxx F 400msec XC61XxFxxxxx H 1.6sec XC61XxHxxxxx③ Represents watchdog timeout period MARK WATCHDOG TIMEOUT PERIOD PRODUCT SERIES 0 XC61X6, XC61X7 series XC61Xxx0xxxx 1 6.25msec XC61Xxx1xxxx 2 50msec XC61Xxx2xxxx 3 100msec XC61Xxx3xxxx 4 200msec XC61Xxx4xxxx 5 400msec XC61Xxx5xxxx 6 1.6sec XC61Xxx6xxxx④⑤ Represents detect voltage MARK④ ⑤DETECT VOLTAGE (V)PRODUCT SERIES3 3 3.3 XC61Xxxx33xx 5 0 5.0XC61Xxxx50xx⑥ Represents production lot number0 to 9 and A to Z repeated. (G, I, J, O, Q, W excepted.)* No character inversion used. ** ‘X’ represents both ‘0’ and ‘1’. (ex. XC61X1⇒XC6101 and XC6111)MARK PRODUCT SERIES MARK PRODUCT SERIES 3 XC6101xxxxxx 8 XC6111xxxxxx 4 XC6102xxxxxx 9 XC6112xxxxxx 5 XC6103xxxxxx A XC6113xxxxxx 6 XC6104xxxxxx B XC6114xxxxxx 7 XC6105xxxxxx C XC6115xxxxxx 3 XC6106xxxxxx 8 XC6116xxxxxx 4 XC6107xxxxxx 9 XC6117xxxxxx■MARKING RULE (Continued)●USP-6CUSP-6C (TOP VIEW)7/26XC6101 ~ XC6107, XC6111~ XC6117Series■BLOCK DIAGRAMS●XC6101, XC6111 Series●XC6102, XC6112 Series●XC6103, XC6113 Series8/26XC6101~XC6107, XC6111~XC6117 Series■BLOCK DIAGRAMS (Continued)●XC6107, XC6117 Series●XC6106, XC6116 Series●XC6105, XC6115 Series●XC6104, XC6114 Series9/26XC6101 ~ XC6107, XC6111~ XC6117SeriesPARAMETERSYMBOL RATINGSUNITSV INV SS -0.3 ~ 7.0 VM RBV SS -0.3 ~ V IN +0.3 VInput Voltage WD V SS -0.3 ~ 7.0V Output Current I OUT 20 mACMOS Output RESETB/RESET V SS -0.3 ~ V IN +0.3Output Voltage N-ch Open Drain Output RESETB V SS -0.3 ~ 7.0VSOT-25 250Power Dissipation USP-6C Pd 100mWOperational Temperature Range Topr -40 ~ +85 OCStorage Temperature Range Tstg -40 ~ +125 OC■ABSOLUTE MAXIMUM RATINGSTa = 25O C10/26XC6101~XC6107, XC6111~XC6117 SeriesNOTE:*1: XC6101~XC6107 (with hysteresis) *2: XC6111~XC6117 (without hysteresis)*3: ‘X’ represents both ‘0’ and ‘1’. (ex. XC61X1⇒XC6101 and XC6111) *4: V DF(T): Setting detect voltage*5: If only “V DF ” is indicated, it represents both V DFL (low when detected) and V DFH (high when detected).PARAMETERSYMBOLCONDITIONSMIN.TYP .MAX. UNITS CIRCUITDetect Voltage V DFL V DFHV DF(T)× 0.98V DF(T) V DF(T)× 1.02 V 1 Hysteresis Range XC6101~XC6107 (*1) V HYS V DF × 0.02V DF × 0.05 V DF× 0.08 V 1Hysteresis Range XC6111~XC6117 (*2) V HYS 0 V DF × 0.001 V DFx 0.01V 1V IN =V DF(T)×0.9V - 5 11 V IN =V DF(T)×1.1V- 10 16 XC61X1/XC61X2/XC61X3XC61X4/XC61X5 (*3)(The MRB & the WD Pin: No connection) V IN =6.0V - 1218 V IN =V DF(T)×0.9V - 4 10 V IN =V DF(T)×1.1V - 8 14 Supply Current I SS XC61X6/XC61X7 (*3)(The MRB Pin: No connection)V IN = 6.0V - 1016 µA 2Operating Voltage V IN 1.0 - 6.0 V 1VIN = 1.0V 0.15 0.5 -V IN =2.0V (V DFL(T)> 2.0V) 2.0 2.5 - V IN =3.0V (V DFL(T) >3.0V) 3.0 3.5 -N-ch.V DS = 0.5V V IN =4.0V (V DFL(T) >4.0V) 3.5 4.0 - 3 V DFL Output Current (RESETB) I RBOUTCMOS,P-chV DS = 0.5V V IN = 6.0V - - 1.1 -0.8 mA 4 N-chV DS = 0.5VV IN =6.0V 4.4 4.9 - 3V IN =1.0V - - 0.08 - 0.02 V IN =2.0V (V DFH(T)> 2.0V)- - 0.50 - 0.30 V IN =3.0V (V DFH(T)>3.0V)- - 0.75 - 0.55V DFHOutput Current (RESET) I ROUT P-ch. V DS = 0.5V V IN =4.0V (V DFH(T)>4.0V)- - 0.95 - 0.75 mA 4Temperature Characteristics △V DF / △Topr ・V DF -40OC < Topr < 85 O C - +100 - ppm / O C12 3.13 5 13 25 3825 50 75 60 100 140 120 200 280 240 400 560Release Delay Time(V DF <1.8V)T DR Time until V IN is increased from1.0V to2.0Vand attains to the release time level,and the Reset output pin inverts.960 1600 2240 ms 5 2 3.13 5 13 25 38 25 50 7560 100 140 120 200 280 240 400 560 Release Delay Time(V DF >1.9V)T DRTime until V IN is increased from1.0V to (V DF x1.1V) and attains to the releasetime level,and the Reset output pin inverts. 960 1600 2240ms 5 Detect Delay Time T DFTime until V IN is decreased from 6.0V to 1.0V and attains to the detect voltage level, and the Reset output pin detectswhile the WD pin left opened.- 3 30 µs 5V DFL /V DFH CMOS Output Leak CurrentI LEAK V IN =6.0V, RESETB=6.0V (V DFL ) V IN =6.0V, RESET=0V (V DFH )- 0.01 - µA 3V DFL N-ch Open DrainOutput Leak CurrentI LEAKV IN =6.0V, RESETB=6.0V-0.010.10µA 3■ELECTRICAL CHARACTERISTICS●XC6101~XC6107, XC6111~XC6117 SeriesTa = 25O CSeriesPARAMETERSYMBOL CONDITIONS MIN.TYP . MAX. UNITS CIRCUIT3.13 6.25 9.38 25 50 7560 100 140 120 200 280240 400 560 Watchdog Timeout Period (V DF <1.8V)T WDTime until V IN increases form1.0V to2.0V andthe Reset output pin is released to go into the detection state. (WD=V SS )960 1600 2240 ms 6 3.13 6.25 9.38 25 50 75 60 100 140 120 200 280240 400 560 Watchdog Timeout Period (V DF >1.9V)T WDTime until V IN increases form1.0V to (V DF x1.1V)and the Reset output pin is released to go into the detection state. (WD=V SS )960 1600 2240 ms 6 WatchdogMinimum Pulse Width T WDIN V IN =6.0V,Apply pulse from 6.0V to 0Vto the WD pin. 300 - - ns 7 Watchdog High Level VoltageV WDH V IN =V DF x 1.1V ~ 6.0V V IN x 0.7- 6 V 7 Watchdog Low Level Voltage V WDL V IN =V DF x 1.1V ~ 6.0V0 - V IN x 0.3 V 7 V IN =6.0V, V WD =6.0V (Avg. when peak )- 12 19Watchdog Input Current I WD V IN =6.0V, V WD =0V (Avg. when peak) - 19 -12 -µA 8 Watchdog Input ResistanceR WDV IN =6.0V, V WD =0V, R WD =V IN / |I WD |315500880k Ω8PARAMETERSYMBOL CONDITIONS MIN.TYP . MAX.UNITS CIRCUITMRBHigh Level VoltageV MRH V IN =V DF x1.1V ~ 6.0V 1.4 - V IN 9MRBLow Level VoltageV MRL V IN =V DF x1.1V ~ 6.0V-0.35 V9MRBPull-up Resistance R MR V IN =6.0V, MRB=0V, R MR =V IN / |I MRB | 1.6 2.4 3.0 M Ω 10 MRB Minimum Pulse Width (*3) XC6101~XC6105 XC6111~XC6115 T MRINV IN =6.0V,Apply pulse from 6.0V to 0V tothe MRB pin 2.8 - -MRB Minimum Pulse Width (*4) XC6106, XC6107 XC6116, XC6117T MRIN V IN =6.0V,Apply pulse from 6.0V to 0V tothe MRB pin1.2 - -µs11●XC6101 ~ XC6103, XC6106 ~ XC6107, XC6111 ~ XC6113, XC6116 ~ XC6117 Series NOTE:*1: V DF(T): Setting detect voltage *2: If only “V DF ” is indicated, it represents both V DFL (low when detected) and V DFH (high when detected). *3: Watchdog function is available. *4: Watchdog function is not available.Ta = 25O CTa = 25O C ■ELECTRICAL CHARACTERISTICS (Continued)●XC6101~XC6105, XC6111~XC6115 Series■OPERATIONAL EXPLANATIONThe XC6101~XC6107, XC6111~XC6117 series compare, using the error amplifier, the voltage of the internal voltage reference source with the voltage divided by R1, R2 and R3 connected to the V IN pin. The resulting output signal from the error amplifier activates the watchdog logic, manual reset logic, delay circuit and the output driver. When the V IN pin voltage gradually falls and finally reaches the detect voltage, the RESETB pin output goes from high to low in the case of the V DFL type ICs, and the RESET pin output goes from low to high in the case of the V DFH type ICs.<RESETB / RESET Pin Output Signal>* V DFL (RESETB) type - output signal: Low when detected.The RESETB pin output goes from high to low whenever the V IN pin voltage falls below the detect voltage, or whenever the MRB pin is driven from high to low. The RESETB pin remains low for the release delay time (T DR) after the V IN pin voltage reaches the release voltage. If neither rising nor falling signals are applied to the WD pin within the watchdog timeout period, the RESETB pin output remains low for the release delay time (T DR), and thereafter the RESET pin outputs high level signal. * V DFH (RESET) type – output signal: High when detected.The RESET pin output goes from low to high whenever the V IN pin voltage falls below the detect voltage, or whenever the MRB pin is driven from high to low. The RESET pin remains high for the release delay time (T DR) after the V IN pin voltage reaches the release voltage. If neither rising nor falling signals are applied to the WD pin within the watchdog timeout period, the V OUT pin output remains high for the release delay time (T DR), and thereafter the RESET pin outputs low level signal.<Hysteresis>When the internal comparator output is high, the NMOS transistor connected in parallel to R3 is turned ON, activating the hysteresis circuit. The difference between the release and detect voltages represents the hysteresis range, as shown by the following calculations:V DF (detect voltage) = (R1+R2+R3) x Vref(R2+R3)V DR (release voltage) = (R1+R2) x Vref(R2)V HYS (hysteresis range)=V DR-V DF (V)V DR > V DF* Detect voltage (V DF) includes conditions of both V DFL (low when detected) and V DFH (high when detected).* Please refer to the block diagrams for R1, R2, R3 and Vref.Hysteresis range is selectable from V DF x 0.05V (XC6101~XC6107) or V DF x 0.001V (XC6111~XC6117).<Watchdog (WD) Pin>The XC6101~XC6107, XC6111~XC6117 series use a watchdog timer to detect malfunction or “runaway” of the microprocessor. If neither rising nor falling signals are applied from the microprocessor within the watchdog timeout period, the RESETB/RESET pin output maintains the detection state for the release delay time (T DR), and thereafter the RESET/RESETB pin output returns to the release state (Please refer to the FUNCTION CHART). The timer in the watchdog is then restarted. Six watchdog timeout period settings are available in 1.6sec, 400msec, 200msec, 100msec, 50msec, 6.25msec.<MRB Pin>Using the MRB pin input, the RESET/RESETB pin signal can be forced to the detection state. When the MRB pin is driven from high to low, the RESETB pin output goes from high to low in the case of the V DFL type ICs, and the RESET pin output goes from low to high in the case of the V DFH type. Even after the MRB pin is driven back high, the RESET/RESETB pin output maintains the detection state for the release delay time (T DR). Since the MRB pin is internally pulled up to the V IN pin voltage level, leave the MRB pin open if unused (Please refer to the FUNCTION CHART). A diode, which is an input protection element, is connected between the MRB pin and V IN pin. Therefore, if the MRB pin is applied voltage that exceeds V IN, the current will flow to V IN through the diode. Please use this IC within the stated maximum ratings (V SS -0.3 ~ V IN+0.3) on the MRB pin.<Release Delay Time>Release delay time (T DR) is the time that elapses from when the V IN pin reaches the release voltage, or when the watchdog timeout period expires with no rising signal applied to the WD pin, until the RESET/RESETB pin output is released from the detection state. Seven release delay time (T DR) watchdog timeout period settings are available in 1.6sec, 400msec, 200msec, 100msec, 50msec, 25msec, 3.13msec.<Detect Delay Time>Detect Delay Time (T DF) is the time that elapses from when the V IN pin voltage falls to the detect voltage until the RESET/ RESETB pin output goes into the detection state.Series■TIMING CHARTS●CMOS Output●T DF (CMOS Output)VINVDFL LevelGNDVIN Level VDFL Level GNDVIN x 0.1V■NOTES ON USE1. Please use this IC within the stated maximum ratings. Operation beyond these limits may cause degrading or permanent damage to the device.2. When a resistor is connected between the V IN pin and the input, the V IN voltage drops while the IC is operating and a malfunction may occur as a result of the IC’s through current. For the CMOS output products, the V IN voltage drops while the IC is operating and malfunction may occur as a result of the IC’s output current. Please be careful with using the XC6111~XC6117 series (without hysteresis).3. In order to stabilize the IC’s operations, please ensure that the V IN pin’s input frequency’s rise and fall times are more than 1 µ sec/V.4. Noise at the power supply may cause a malfunction of the watchdog operation or the circuit. In such case, please strength the line between V IN and the GND pin and connect about 0.22µF of a capacitor between the V IN pin and the GND pin.5. Protecting against a malfunction while the watchdog time out period, an ignoring time (no reaction time) occurs to the rise and fall times. Referring to the figure below, the ignoring time (no reaction time) lasts for 900µsec at maximum.GNDGNDGNDVIN Pin Wave FormWD Pin Wave FormRESETB Pin Wave Form (VDFL)SeriesPIN NAMELOGIC CONDITIONSH V IN >V DF +V HYS V IN L V IN <V DF H MRB>1.40V MRBL MRB<0.35V H When keeping W D >V WDH more than T WD L When keeping W D <V WDL more than T WD L → H V WDL → V WDH , T WDIN >300nsec WDH → L V WDH →V WDH , T WDIN >300nsecV IN MRB WD RESETB (*2) H HH LRepeat detect and release (H →L →H)H OpenH L → HH H or Open H → L H HLL *1 LV IN MRB WD RESETB (*3) H HH LRepeat detect and release (L →H →L)H OpenH L → HH H or Open H → L L HLL *1 HV IN WD RESETB (*2) RESET (*3) H HH L Repeat detect and release (H →L →H)Repeat detect and release (L →H →L)H OpenH L → HH H → L H L HL*1 L HV IN MRB RESETB (*2)RESET (*3)H H or Open H LH LL L H■PIN LOGIC CONDITIONSNOTE:*1: If only “V DF ” is indicated, it represents both V DFL (low when detected) and V DFH (high when detected).*2: For the details of each parameter, please see the electrical characteristics. V DF : Detect VoltageV HYS : Hysteresis RangeV WDH : WD High Level Voltage V WDL: WD Low Level Voltage T WDIN : WD Pulse Width T WD : WD Timeout Period■FUNCTION CHART●XC6103/XC61113 Series●XC6104/XC61114, XC6105/XC6115 Series●XC6106/XC61116, XC6107/XC6117 Series●XC6101/XC61111, XC6102/6112 Series*1: Including all logic of WD (WD=H, L, L →H, H →L, OPEN). *2: When the RESETB is High, the circuit is in the release state. When the RESETB is Low, the circuit is in the detection state. *3: When the RESET is High, the circuit is in the release state. When the RESET is Low, the circuit is in the detection state.■TEST CIRCUITSCircuit 1Circuit 2Circuit 3Circuit 4Series ■TEST CIRCUITS (Continued)Circuit 5Circuit 6Circuit 7■TEST CIRCUITS (Continued)Circuit 8Circuit 9Circuit 10Circuit 11Series■TYPICAL PERFORMANCE CHARACTERISTICS(1.1) Supply Current vs. Input Voltage(1.2) Supply Current vs. Input Voltage■TYPICAL PERFORMANCE CHARACTERISTICS (Continued)(2) Detect, Release Voltage vs. Ambient Temperature(1.2) Supply Current vs. Input Voltage (Continued)Series■TYPICAL PERFORMANCE CHARACTERISTICS (Continued) (3-1) Output Voltage vs. Input Voltage (V DFL ) (3.1) Detect, Release Voltage vs. Input Voltage (V DFL )(3.2) Detect, Release Voltage vs. Input Voltage (V DFH )■TYPICAL PERFORMANCE CHARACTERISTICS (Continued)(4) N-ch Driver Output Current vs. V DSSeries(6) P-ch Driver Output Current vs. Input Voltage 1■TYPICAL PERFORMANCE CHARACTERISTICS (Continued)(8) Release Delay Time vs. Ambient Temperature(7) P-ch Driver Output Current vs. Input Voltage 2■TYPICAL PERFORMANCE CHARACTERISTICS (Continued) (10) Release Delay Time vs. Input Voltage(11) Watchdog Timeout Period vs. Input VoltageSeries■TYPICAL PERFORMANCE CHARACTERISTICS (Continued)(14) MRB Low Level Voltage vs. Ambient Temperature(15) MRB High Level Voltage vs. Ambient Temperature* ‘X’ represents both ‘0’ and ‘1’. (ex. XC61X1⇒XC6101 and XC6111)。

IES6116系列 V1.0.0使用手册V1.0.0

产品使用手册IES6116系列网管型工业以太网交换机使用手册Version1.0.0,Aug.2014IES6016系列产品使用手册IES6116系列使用手册在使用本手册之前,请您认真阅读以下使用许可协议。

只有在同意以下使用许可协议的情况下方能使用本手册中介绍的产品。

商标、版权声明和是深圳市三旺通信技术有限公司的注册商标,本手册中的其他商标分别属于各自的公司所有。

本手册涉及内容归深圳市三旺通信技术有限公司版权所有。

未经深圳市三旺通信技术有限公司书面许可,任何公司或个人不得以任何形式复制或转译本手册全部或部分内容。

重要声明深圳市三旺通信技术有限公司在本手册中提供的任何信息,并不代表对这些信息提供了相应的授权。

深圳市三旺通信技术有限公司努力使本手册中提供的信息准确和适用,深圳市三旺通信技术有限公司并不对这些信息的使用承担任何责任,也不对这些信息的使用承担任何连带责任。

此说明书可作为参考使用,如有疑问,请与我们联系。

修订历史:版本号日期原因V1.0.02014.08创建文档符号说明-------指功能或者设置上的补充说明------配置中的注意事项目录目录 (2)第1章产品概述 (1)1.1产品介绍 (1)1.2性能特点 (1)第2章硬件描述 (3)2.1面板设计 (3)2.2电源输入 (5)2.3继电器连接 (6)2.4调试口 (6)2.5通信接口 (6)2.6LED指示灯 (8)2.7设备安装 (8)第3章外观尺寸图 (10)3.1外观 (10)3.2尺寸 (11)第4章包装清单 (12)第5章网络设置 (13)5.1设置PC的IP地址 (13)第6章WEB管理功能 (14)6.1配置准备 (14)6.2系统状态 (16)6.3端口配置 (17)6.3.1端口设置 (17)6.3.2带宽管理 (19)6.3.3广播、组播、未知单播风暴抑制 (20)6.4二层特性 (21)6.4.1基于端口的VLAN (21)6.4.2基于IEEE802.1Q VLAN (22)6.4.3组播过滤 (23)6.4.3.1IGMP SNooping (23)6.4.3.2GMRP (24)6.4.4静态多播表 (24)6.5QOS (25)6.5.1QOS分类 (25)6.5.1.1相对优先级 (26)6.5.1.2绝对优先级 (26)6.5.2COS (26)6.5.3DSCP (27)6.6链路备份 (28)6.6.1端口汇聚 (28)6.6.2快速环网 (29)6.6.2.1Ring V3单环配置 (31)6.6.2.2Ring V3双环配置 (31)6.6.2.3Ring V3耦合环配置 (32)6.6.2.4Ring V3链配置 (33)6.6.3RSTP快速生成树 (34)6.7访问控制 (35)6.7.1密码管理 (35)6.7.2登录控制 (37)6.7.3IEEE802.1X端口认证 (38)6.7.4认证数据库 (40)6.7.5MAC端口锁定 (41)6.8远程监控 (42)6.8.1SNMP管理 (42)6.8.2邮件报警 (44)6.8.3继电器报警 (45)6.9端口统计 (46)6.9.1接收帧统计 (46)6.9.2发送帧统计 (47)6.9.3总流量统计 (48)6.9.4MAC地址表 (49)6.10网络诊断 (50)6.10.1端口镜像 (50)6.11系统管理 (51)6.11.1时间配置 (51)6.11.2设备地址 (52)6.11.3系统信息 (54)6.11.4文件管理 (54)6.11.5系统注销 (56)第7章维修和服务 (57)7.1I NTERNET服务 (57)7.2打电话到技术支持办公室 (57)7.3产品返修或更换 (57)附录1性能参数 (58)附录2术语表 (59)附录3常见问题处理 (60)IES6016系列产品使用手册第1章产品概述1.1产品介绍IES6116系列是一款即插即用的工业以太网交换机,该系列包含单电源和双电源,IES6116-P(12/48VDC)支持16个RJ45以太网口;IES6116-2F-P(12/48VDC)支持14个RJ45以太网口和2个100M 光口;IES6116-4F-P(12/48VDC)支持12个RJ45以太网口和4个100M光口;IES6116-6F-P(12/48VDC)支持10个RJ45以太网口和6个100M光口;IES6116-8F-P(12/48VDC)支持8个RJ45以太网口和8个100M 光口。

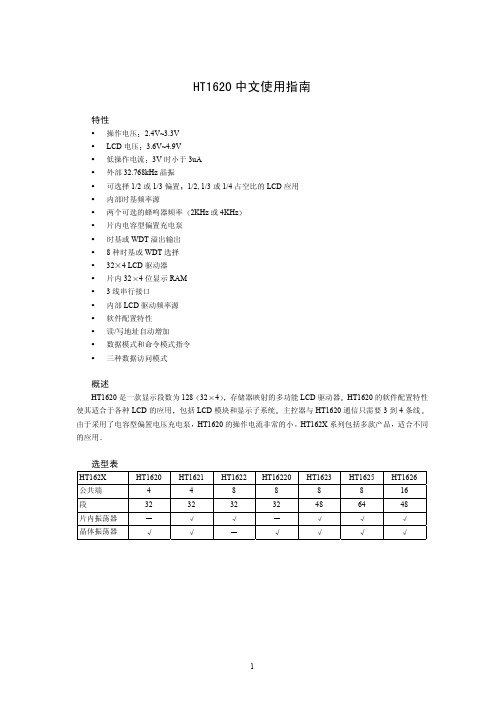

HT1621中文使用说明

特性

操作电压 LCD 电压 2.4V~3.3V 3.6V~4.9V

低操作电流 3V 时小于 3uA 外部 32.768kHz 晶振 可选择 1/2 或 1/3 偏置 内部时基频率源 两个可选的蜂鸣器频率 2KHz 或 4KHz 片内电容型偏置充电泵 时基或 WDT 溢出输出 8 种时基或 WDT 选择 32 4 LCD 驱动器 4 位显示 RAM 片内 32 1/2, 1/3 或 1/4 占空比的 LCD 应用

ab=00 ab=01 ab=10

命令格式 HT1620 可通过软件设定进行配置 有两种模式命令对 HT1620 进行配置和传输 LCD 显示数据 HT1620 的配置模式成为命令模式 LCD 配置命令 修改-写操作 READ WRITE READ-MODIFY-WRITE COMMAND 它的命令模式 ID 为 100 命令模式包含了系统配置命令 系统频率选择命令 而数据模式则包含读 写和读音调频率选择命令 定时器/WDT 设定命令和操作命令 模式 数据 数据 数据 命令 ID 110 101 101 100

焊盘排列

芯片尺寸 142

141 (mil)2

* IC 的衬底应当连接到 PCB 板上的 VDD

3

焊盘坐标

单位

mil

焊盘描述

焊盘编号 2 3 4~7 8~39 40 焊盘名称 VO15N VEE COM0~COM3 SEG0~SEG31 CS O O I I/O O 描述 半压电路输出管脚 倍压电路输出管脚 LCD 公共输出端 LCD 段输出 带上拉电阻的片选输入 低电平 41 RD I 当 CS 为高电平时 对 HT1620 数据 和命令的读/写被禁止 串口电路也处于复位状态 如果 CS 为 则读/写功能使能 HT1620 内部 RAM 的数据在 RD 带上拉电阻的读时钟输入 在下一个上升沿将数据锁存 42 43 44 45 46 47 48 49, 50 51, 1 WR DATA VSS OSCO OSCI VDD IRQ BZ, BZ CC1, CC2 O O I O I 电源 时基或 WDT 溢出标志 外部电容管脚 4 NMOS 开漏输出 三态输出缓冲器 I I/O 带上拉电阻的写时钟输入 DATA 线上的数据在 WR 信号的上 升沿锁存到 HT1620 带上拉电阻的串行数据输入/输出 地 OSCI 和 OSCO 连接 32.768kHz 晶振 用于产生系统时钟

ht1621中文资料_数据手册_参数

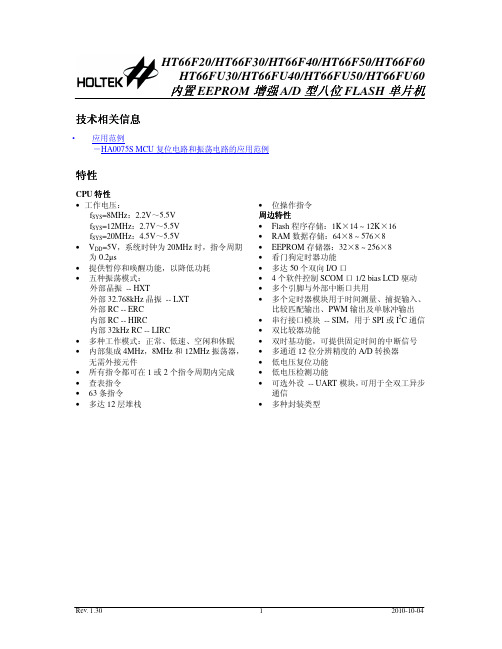

HT66FXX中文版详细资料

H T66F30 1 6 D IP -A /N S O P -A /S S O P -A

P A 0 /C 0 X /T P 0 _ 0 /A N 0 1 VSS&AVSS 2 P B 4 /X T 2 3 P B 3 /X T 1 4 P B 2 /O S C 2 5 P B 1 /O S C 1 6 VDD&AVDD 7 P B 0 /R E S 8

型号

外部 VDD ROM RAM EEPROM I/O 中断 A/D

TM 模块

接口 (SPI/I2C)

UART

堆栈

封装形式

HT66F20*

2.2V~ 5.5V

1K×14

64×8

32×8

18

2

12-bit×8

10-bit CTM×1 10-bit STM×1

√

√4

16DIP/NSOP/SSOP 20DIP/SOP/SSOP

在模拟特性方面,这款单片机包含一个多通道 12 位 A/D 转换器和双比较器功能。还带有多个 使用灵活的定时器模块,可提供定时功能、脉冲产生功能及 PWM 产生功能。内建完整的 SPI 和 I2C 功能,为设计者提供了一个易与外部硬件通信的接口。内部看门狗定时器、低电压复位和低电压检 测等内部保护特性,外加优秀的抗干扰和 ESD 保护性能,确保单片机在恶劣的电磁干扰环境下可靠 地运行。

fSYS=8MHz:2.2V~5.5V fSYS=12MHz:2.7V~5.5V fSYS=20MHz:4.5V~5.5V • VDD=5V,系统时钟为 20MHz 时,指令周期 为 0.2µs • 提供暂停和唤醒功能,以降低功耗 • 五种振荡模式: 外部晶振 -- HXT 外部 32.768kHz 晶振 -- LXT 外部 RC -- ERC 内部 RC -- HIRC 内部 32kHz RC -- LIRC • 多种工作模式:正常、低速、空闲和休眠 • 内部集成 4MHz,8MHz 和 12MHz 振荡器, 无需外接元件 • 所有指令都可在 1 或 2 个指令周期内完成 • 查表指令 • 63 条指令 • 多达 12 层堆栈

HGM6110LT_6120LT中文说明书

郑州众智科技股份有限公司SMARTGEN (ZHENGZHOU) TECHNOLOGY CO., LTD.HGM6100LT 系列(HGM6110LT/6120LT)发电机组控制器用户手册目次前言 (4)1概述 (5)2性能特点 (6)3规格 (8)4操作 (9)4.1按键功能描述 (9)4.2控制器面板 (10)4.3自动开停机操作 (11)4.4手动开停机操作 (12)4.5应急开机 (12)5保护 (13)5.1警告 (13)5.2停机报警 (14)6接线 (16)7编程参数范围及定义 (18)7.1参数设置内容及范围 (18)7.2可编程输出口1-4可定义内容 (23)7.3可编程输入口1-5定义内容 (24)7.4传感器选择 (25)7.5起动成功条件选择 (26)8参数设置 (27)9传感器设置 (28)10试运行 (29)11典型应用 (29)12安装 (31)12.1卡件 (31)12.2外形及开孔尺寸 (31)13控制器与发动机的J1939连接 (32)13.1CUMMINS ISB/ISBE(康明斯) (32)13.2CUMMINS QSL9 (32)13.3CUMMINS QSM11(进口) (32)13.4CUMMINS QSX15-CM570 (33)13.5CUMMINS GCS-MODBUS (33)13.6CUMMINS QSM11(西安康明斯) (34)13.7CUMMINS QSZ13(东风康明斯) (34)13.8DETROIT DIESEL DDEC III/IV(底特律) (34)13.9DEUTZ EMR2(道依茨) (35)13.10JOHN DEERE(强鹿) (35)13.11MTU MDEC (35)13.12MTU ADEC(SMART模块) (36)13.13MTU ADEC(SAM模块) (36)13.14PERKINS(珀金斯) (36)13.15SCANIA (37)13.16VOLVO EDC3(沃尔沃) (37)13.17VOLVO EDC4 (37)13.18VOLVO-EMS2 (38)13.19玉柴 (38)13.20潍柴 (38)14故障排除 (39)前言是众智的中文商标是众智的英文商标SmartGen ―Smart的意思是灵巧的、智能的、聪明的,Gen是generator(发电机组)的缩写,两个单词合起来的意思是让发电机组变得更加智能、更加人性化、更好的为人类服务!不经过本公司的允许,本文档的任何部分不能被复制(包括图片及图标)。

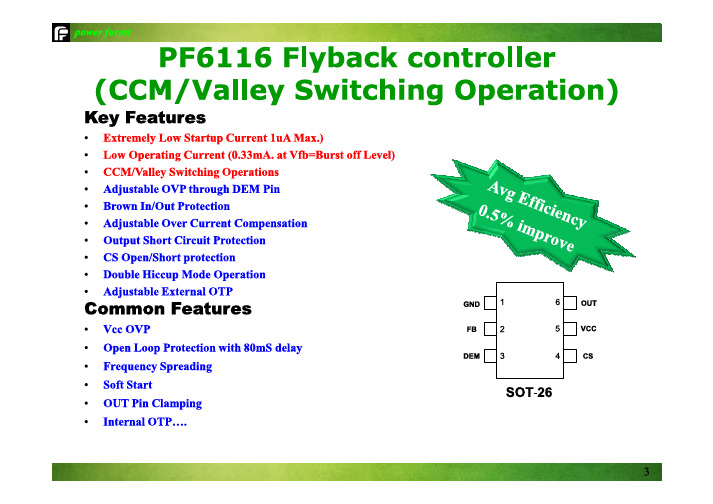

PF6116 资料

-பைடு நூலகம்-27

I D C J > B

$- "/ + ( , ! -")$ ! ") "# "/ 21 3 "/ 41 )/ 01 %& & 5 ")$. 01 2

8 8 9 : ; < = > ? @A D H ? : ; < = 9 ? @A 8 ? B

c( )( d # e 0f3 - !"# $%& & ' ( )' *

& !" #$

( & !" #$

'

0 1 2 3 4 6 1 4 3 7 8

9

9

9

9

9

9

9

9

9

! ! " # " $%# &

9 9 9 o v tl u

l ol u j v k l

g hi j k l ml n oqr st j u k j v wxv k k l y j z { | v }u j ~xxz ~ g qr sw l k u j y xv k k l y j z m} u j ~ v k j r ql l n

( )

0 1 2 3 4 6 1 4 3 7 8

K L M NPQRST N T QRU V W XYV Z[V W \ ]L ^Q_Q` a S

8 8 9 : ; < = > ? @A D H ? : ; < = 9 ? @A 8 ? B

9

9

ht1621中文资料

SD0432 中集成了一个简单的声音发生器,此发声器可输出一对不同的驱动信号至 BZ 和 BZ 以产生单音,执 行 TONE 4K 与 TONE 2K 命令,可选择两个不现的音频输出,即 4KHZ 与 2KHZ 这两个频率,TONE ON 及 TONE OFF 命令可打开或关闭语音输出,语音输出 BZ 和 BZ,是一对不同的带驱动蜂鸣器。当系统关闭或语音输出被禁止时, BZ 及 BZ 将处于低电平状态。

命令 LCD OFF 是通过关闭 LCD 偏压发生器来关闭 LCD 显示器。反之,LCD ON 则启动 LCD 显示。BIAS COM 是与

LCD 屏面相关命令。使用 LCD 相关命令,SD0432 可与绝大多数类型的 LCD 屏面兼容。

3. 6 命令格式

SD0432 可由 S/W 设置来配置。有两种命令模式分别用来配置 SD0432 和传送 LCD 显示数据。配置 SD0432 的命

令模式(普通模式)识别码为 100,此命令模式由系统配置命令、LCD 配置命令、音频选择命令、定时器/看门狗

定时器设置命令及操作命令组成。另一方面,数据模式包括 READ、WRITE 及 READ-MODIFY-WRITE 操作。下表为数

据模式及命令模式识别码:

com 操

作

. READ

s WRITE

le RAM 中的数据由 READ、WRITE 以及 READ-MODIFY-WRITE 指令进行存取,下图为由 RAM 控制 LCD 的映象图。

e SEG

COM

COM3

COM2

COM1

COM0

六位地址(A5,A4…A0)

. SEG0

0

ww SEG1

1

w SEG2

ht1621中文资料

典型 值

150 300 60 120

最大 值 5.2 300 600 120 240

单位

V

A A A A

rm.

IDD 工作电流

3V 不带负载 5V 外部时钟源

100 200 A 200 400 A

a

ISTB VIL VIH IOL1 IOH1 IOL2 IOH2 IOL3 IOH3 RPH

待机电流

时基和看门狗定时器 WDT 时基发生器是一个 8 态增值尖峰计数器 可以产生准确的时基 WDT 由时基发生器和 一个 2 态增值尖峰计数器组成 它可以在主控制器或其它子系统处于异常状态时产生中断 WDT 溢出时产生片内 WDT 溢出标志 可用一命令选项使时基发生器和 WDT 溢出标志输 出到/IRQ 管脚 时基发生器和 WDT 时钟频率有 8 种 fWDT=32KHz/2n 这里的 n 值为 0 7 由命令项决定 等式中 32KHz 为系统频率 由晶振 32.768KHz 片内振荡器 (256KHz)

海纳电子资讯网:www.fpga-arm.com 为您提供各种IC中文资料

广州周立功单片机发展有限公司 Tel 020 38730976 38730977 Fax:38730925

HOLTEK HT1621 LCD 驱动器

特性

* 工作电压 2.4 5.2V

* 内嵌 256KHz RC 振荡器 * 可外接 32KHz 晶片或 256KHz 频率源输入

32.768 32.768 256 256 fSYS1/102 4 fSYS2 /128 fSYS3/102 4

n/ fLCD

KHz KHz KHz KHz

Hz

Hz

rm.

a Hz

-s

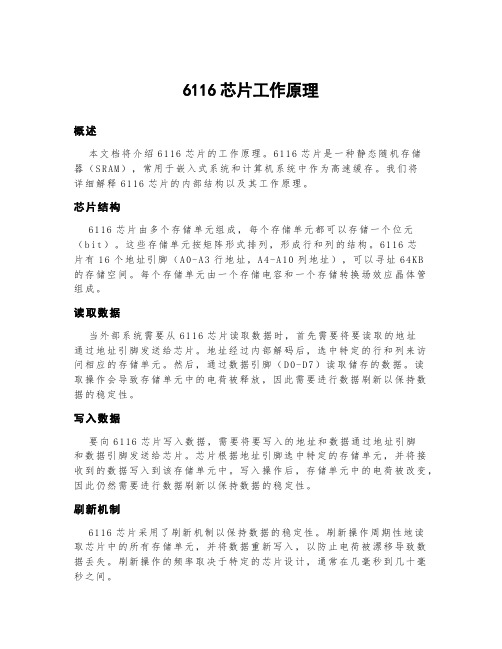

6116芯片工作原理

6116芯片工作原理概述本文档将介绍6116芯片的工作原理。

6116芯片是一种静态随机存储器(SR AM),常用于嵌入式系统和计算机系统中作为高速缓存。

我们将详细解释6116芯片的内部结构以及其工作原理。

芯片结构6116芯片由多个存储单元组成,每个存储单元都可以存储一个位元(b it)。

这些存储单元按矩阵形式排列,形成行和列的结构。

6116芯片有16个地址引脚(A0-A3行地址,A4-A10列地址),可以寻址64K B的存储空间。

每个存储单元由一个存储电容和一个存储转换场效应晶体管组成。

读取数据当外部系统需要从6116芯片读取数据时,首先需要将要读取的地址通过地址引脚发送给芯片。

地址经过内部解码后,选中特定的行和列来访问相应的存储单元。

然后,通过数据引脚(D0-D7)读取储存的数据。

读取操作会导致存储单元中的电荷被释放,因此需要进行数据刷新以保持数据的稳定性。

写入数据要向6116芯片写入数据,需要将要写入的地址和数据通过地址引脚和数据引脚发送给芯片。

芯片根据地址引脚选中特定的存储单元,并将接收到的数据写入到该存储单元中。

写入操作后,存储单元中的电荷被改变,因此仍然需要进行数据刷新以保持数据的稳定性。

刷新机制6116芯片采用了刷新机制以保持数据的稳定性。

刷新操作周期性地读取芯片中的所有存储单元,并将数据重新写入,以防止电荷被漂移导致数据丢失。

刷新操作的频率取决于特定的芯片设计,通常在几毫秒到几十毫秒之间。

特性与应用6116芯片具备以下特性:-高速读写能力:由于采用了静态存储技术,6116芯片具有快速的读写速度,适用于需要频繁读写的场景。

-低功耗:相较于动态存储器(D RA M),静态存储器不需要定期刷新,因此功耗更低。

-可靠性高:6116芯片的静态存储单元具有较好的稳定性,不容易出现数据错误。

基于以上特性,6116芯片被广泛应用于嵌入式系统和计算机系统的高速缓存中,用于快速存储和读取临时数据。

也常用于一些低功耗设备中,如便携式电子设备和电池供电系统。

HT1621

HT1621

SPI三线包括/CS(片选)【或者称STB】、CLK(时钟)、DIO(串行数据接口)。

主要工作方式:

①/CS:片选输入,接上拉电阻,当/CS为高电平时,读写HT1621数据和命令无效,串行口复位,当/CS为低电平或者作为输入时,读写HT1621的数据和命令有效。

②CLK:时钟脉冲,在片选为低电平时,才看其脉冲(此处1621的上升沿为1),根据其脉冲找出对应的data值。

③DIO:外接上拉电阻的串行数据输入/输出。

一般是一个字节(8个bit)一个字节地传输。

I平方c是两线串行总线,用于连接微控制器及外围设备,具有接线口少,控制方式简单,器件封装形式简单,通信速率高等优点。

但是有电压的匹配性问题,如果CPU额定电压2.5V,与它连接的另外两个模块额定电压为5V和3V,那么一定要在相连的连接线上加上有上拉电阻的2.5V电源,如果不加,CPU会烧坏。

PWM是脉宽调节。

即通过调节占空比来调节脉宽。

什么是占空比呢,就是在一个周期内,高电平所占的整个周期的百分比,比如LED灯,可以调节其脉宽,即增大占空比,可以使LED更亮。

其他相关资料见HT1621的Pdf文件。

6116芯片

6116芯片6116芯片是一种静态随机存储器(SRAM),采用16位数据总线和16位地址总线。

该芯片具有存储器容量为2048字节,即16K位,并且采用静电存储单元,可以实现数据的快速读写。

6116芯片是一种广泛应用于计算机以及其他电子设备中的存储器芯片,它在数据存储和读取方面具有高性能和可靠性。

下面将详细介绍6116芯片的架构、工作原理以及应用领域。

6116芯片的结构由多个存储元件组成,每个存储元件可以存储一个字节的数据。

这些存储元件以矩阵的形式排列,通过行和列地址进行访问。

6116芯片的地址总线宽度为16位,可以寻址2^16=65536个存储单元。

数据总线宽度也为16位,可以同时读取或写入16位的数据。

该芯片采用的是静电存储单元,即每个存储单元由六个电晶体管组成。

这种存储单元具有快速读取和写入的特性,但是也需要不断地刷新以保持数据的稳定性。

为了实现刷新操作,6116芯片内部集成了一个刷新计数器和一个刷新电路。

刷新计数器负责生成刷新周期,并通过刷新电路将刷新脉冲传递到存储单元,以防止数据丢失。

6116芯片的工作原理如下:首先,根据需要的地址,将地址信号传递给地址选择器。

地址选择器将地址信号转换为行和列地址信号,并将它们传递给存储单元。

存储单元根据行和列地址信号,选中需要读取或写入的存储单元。

如果需要读取数据,则存储单元将所选存储单元内的数据通过数据总线传递给数据输出缓冲器,然后再传递给外部设备。

如果需要写入数据,则将数据信号通过数据输入缓冲器传递给存储单元,并将其写入选中的存储单元。

6116芯片具有很多应用领域,其中最常见的是在计算机系统中作为主存储器使用。

它可以存储计算机程序、数据以及中间结果,以供CPU进行读取和写入。

另外,6116芯片还可以用于各种嵌入式系统中,如通信设备、工控设备以及嵌入式系统开发板等。

它的高性能和可靠性使得它成为了许多电子设备中不可或缺的组成部分。

此外,6116芯片还可以通过多个芯片并联来扩展存储容量,以满足更大规模的数据存储需求。

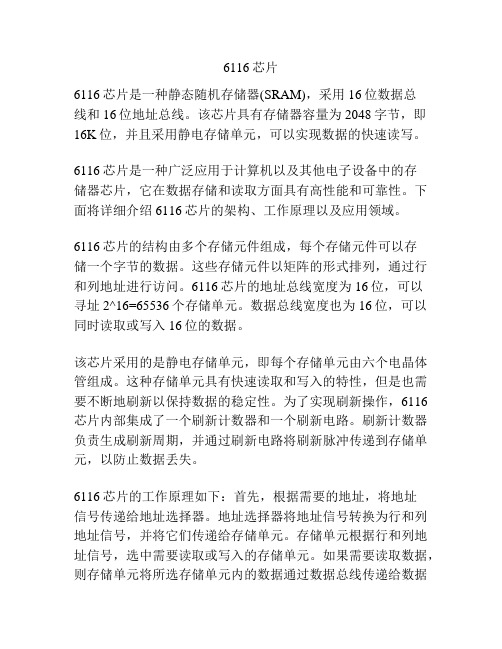

试验五存储器连接6116的使用

实验五存储器连接(6116的使用)【实验名称】存储器连接(6116的使用)。

【实验目的】掌握存储器译码及读写的方法。

【实验原理】微处理器通过数据总线、地址总线及控制总线与存储器连接,如下图所示:地址总线为地址信号,用来指明选中的存储单元地址。

数据总线为数据信号,它是微处理器送往存储器的信息或存储器送往微处理器的信息。

它包括指令和数据。

控制总线发出存储器读写信号,以便从ROM、RAM中读出指令或数据,或者向RAM写入数据。

在微机系统中,常用的静态RAM有6116、6264、62256等。

在本实验中使用的是6116。

6116为2K╳8位的静态RAM,其逻辑图如下:其中A0~10为11根地址线,I/O0~7为8根数据线,CS 为片选端,OE为数据输出选通端,WR为写信号端。

其工作方式见下表:FD-SJ86/88实验板上提供了一片6116用来作存储器读写实验。

在6116的上方三根跳线J57、J58、J59分别用来设置6116的片选端、读信号、写信号的连接状态。

当以短路块分别将J57、J58、J59上面两根针短路时,则6116片选端连接由U39产生的译码信号,其译码范围为0A0000H~0A07FFH,因6116为2K存储器,所以地址0A0000H~0A07FFH和0A0800H~0A0FFFH重叠。

6116的读写信号则分别接到系统总线上的存储器读写信号。

其数据通过74LS245(U38)接到系统的数据总线上。

【实验内容】在FD-SJ86/88实验板上的6116芯片内写入一些数据,然后读出显示在屏幕上以验证正确与否。

【实验连线】① 6264的地址线J8(A0~A10)接总线上的地址线A0~A10。

② J57、J58、J59的下面的两个脚以短路块连接。

【实验程序】DATA SEGMENTMESSAGE DB 'PLEASE ENTER A KEY TO SHOW THE CONTENTS',0DH,0AH,'$'DATA ENDSSTACK SEGMENT STACKSTA DW 50 DUP(?)TOP EQU LENGTH STASTACK ENDSCODE SEGMENTASSUME CS:CODE,DS:DATA,SS:STACK,ES:DATASTART: MOV AX,DATAMOV DS,AXMOV AX,STACKMOV SS,AXMOV SP,TOPMOV AX,0A000HMOV ES,AXMOV BX,0000HMOV CX,26MOV DL,40HWRITE: INC DLMOV ES:[BX],DLINC BXCMP DL,5AHJNZ SS1MOV DL,40HSS1: LOOP WRITEMOV DX,OFFSET MESSAGEMOV AH,9INT 21HMOV AH,01HINT 21HMOV AX,0A000HMOV ES,AXMOV BX,0000HMOV CX,26READ: MOV DL,ES:[BX]MOV AH,02HINT 21HINC BXLOOP READMOV AH,4CHINT 21HCODE ENDSEND START【思考题】将字符‘0’~‘9’写入存储器,再将其读出,应如何修改程序?。

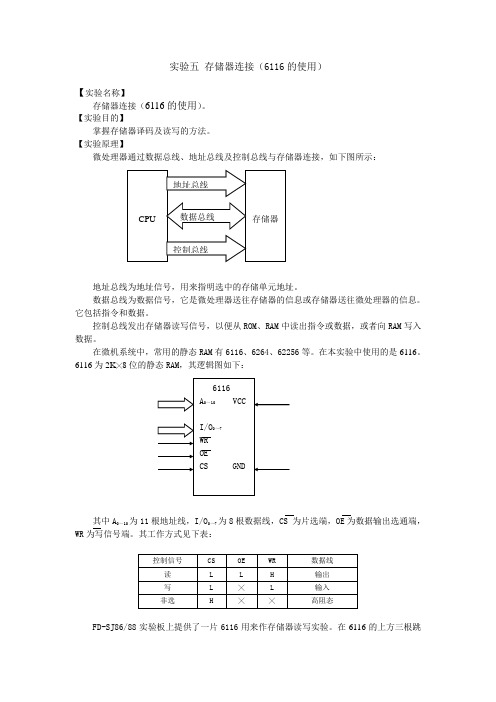

深圳市纳芯威科技有限公司NS6116输入输出同步降压稳压器说明书

NS61168-30V 输入3.1A 输出同步降压稳压器1特性●宽输入电压范围:8V 至30V ●宽输出电压范围:1.8V 至28V ●效率可高达92%以上●开关频率:130kHz ●过热保护●SOP-8封装●输出电流:3.1A2应用范围●车载充电器/适配器●线性调节前置稳压器●分布式供电系统●电池充电器3说明NS6116是支持高电压输入的同步降压电源管理芯片,在8~30V 的宽输入电压范围内可实现3.1A 的连续电流输出。

通过调节FB 端口的分压电阻,可以输出1.8V 到28V 的稳定电压。

NS6116具有优秀的负载调整率和线电压调整率,在全范围内不超过±3%。

NS6116采用电流模式的环路控制原理,实现了快速的动态响应。

NS6116工作开关频率为130kHz ,具有良好的EMI 特性。

NS6116内置线电压补偿,可通过调节FB 端口的分压电阻阻值来实现。

NS6116不仅可实现单芯片降压电源管理方案,还可以与QC2.0/QC3.0识别芯片构成快速充电电源管理方案。

另外,芯片包含多重保护功能:过温保护,输出短路保护和输入欠压/过压保护等。

NS6116采用SOP8的标准封装。

4典型应用电路深圳市百盛新纪元半导体有限公司FP6601Q NS6116,原装正品,技术支持,增值税代理商SOP-8的管脚图如下图所示:6极限工作参数●VIN 电压-0.3V ~33V ●FB 电压-0.3V ~33V ●SW 电压-0.3V ~33V ●EN 电压-0.3V ~33V ●工作温度范围-40℃~+85℃●存储温度范围-55℃~+150℃●结温范围+150℃●焊接温度(10s 内)+265℃注1:超过上述极限工作参数范围可能导致芯片永久性的损坏。

长时间暴露在上述任何极限条件下可能会影响芯片的可靠性和寿命。

注2:NS6116可以在0℃到70℃的限定范围内保证正常的工作状态。

超过-40℃至85℃温度范围的工作状态受设计和工艺控制影响。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

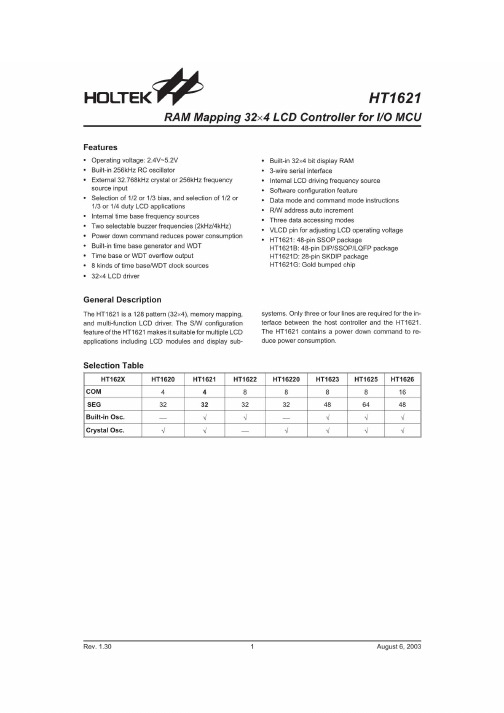

HT6116-70

CMOS 2K ×8-Bit SRAM

Pin Assignment Block Diagram

General Description

The HT6116-70 is a 16384-bit static random access memory . It is organized with 2048 words of 8 bits in length, and operates with a single 5V power supply . The IC is built with a high per-formance CMOS 0.8µm process in order to ob-tain a low standby current and high reliability .The IC contains six-transistor full CMOS mem-ory cells and TTL compatible inputs and out-puts, which are easily interface with common system bus structures. The Data bus of the HT6116-70 is designed as a tri-state type. The IC is in the standby mode if the CS pin is set to “high”.

Features

•Single 5V power supply •

Low power consumption –Operating: 400mW (Typ.)–Standby: 5µW (Typ.)

•70ns (Max.) high speed access time ••

TTL compatible interface levels

•Fully static operation

•Memory expansion by pin OE

•Common I/O using tri-state outputs

•Pin-compatible with standard 2K ×8 bits of EPROM/MASK ROM

•

24-pin DIP/SDIP/SOP package

Pin Description

Absolute Maximum Ratings*

Supply Voltage............................–0.3V to +7.0V Storage Temperature...............–50°C to +125°C Input Voltage.................V SS –0.3V to V DD +0.3V

Operating Temperature.............–40°C to +85°C

*Note: Stresses above those listed under “Absolute Maximum Ratings” may cause permanent

damage to the device. These are stress ratings only . Functional operation of this device at these or any other conditions above those indicated in the operational sections of this specification is not implied and exposure to absolute maximum rating conditions for extended periods may affect device reliability .

D.C. Characteristics

(Ta=25°C)

HT6116-70

23rd July ’97

A.C. Test Conditions

A.C. Characteristics

Read cycle(V DD=5V±10%, GND=0V, Ta=–40°C to +85°

C) Array Note: 1. A read occurs during the overlap of a low CS and a high WE

2. t CHZ and t OHZ are specified by the time when data out is floating

Write cycle(V DD=5V±10%, GND=0V, Ta=–40°C to +85°

C) Array

Note: 1. A write cycle occurs during the overlap of a low CS and a low WE

2. OE may be both high and low in a write cycle

3. t AS is specified from CS or WE, whichever occurs last

4. t WP

5. t WR, t DW and t DH is specified from CS or WE, whichever occurs first

6. t WHZ is specified by the time when DATA OUT is floating, not defined by output level

7. When I/O pins are data output mode, don’t force inverse signals to those pins

43rd July ’97

Timing Diagrams Read cycle (1)

Read cycle (1, 3, 4)

Notes:

(2) Device is continuously enabled, CS=V IL

IL

(5) Transition is measured±500mV from the steady state.

63rd July ’97

Write cycle 2

Notes:

(5)

the WE transition, outputs remain in a high impedance state.

(6)IL).

(7)D OUT is at the same phase of the write data of this write cycle.

(8)D OUT is the read data of the next address.

(9)

signals of the opposite phase to the outputs must not be applied to them.

(10)Transition is measured ± 500mV from the steady state.

Data Rentention Characteristics(Ta=–40°C to +85°C)

*t RC=Read Cycle Time

Low V DD Data Retention Timing

Characteristic Curves

HT6116-70

93rd July ’97。