Automatic Processor Lower Bound Formulas for Array Computations

Atmel Studio 6 微控制器开发环境介绍说明书

Atmel® Studio 6 is the integrated development environment (IDE) for developing and debugging embedded applications based on Atmel AVR® and ARM® Cortex™-M microcontrollers (MCUs) in C/C++ and assembly code. The IDE makes editing and debugging source code easier by seamlessly bringing together an intelligent editor with assisted code writing, a wizard for quickly creating new projects, the Atmel Software Framework with free source code library, a GNU C/C++ Compiler, a powerful simulator, and the front-end for all Atmel programmers and in-circuit debuggers.Atmel Studio 6 is free of charge and available for download at /atmelstudio.What’s New in Atmel Studio 6• Support for Atmel ARM Cortex-M based MCUs• Fully integrated Atmel QTouch® Composer• Full support for C++Your Avenue to Atmel AVR and ARM Cortex-M Based MCU DesignDesigners using AVR MCUs are already familiar with our IDE, previously known as AVR Studio® 5. Now, the communityof ARM Cortex-M design engineers can take advantage of the same easy-to-use, professional and highly integrated development platform.Integrated QTouch ComposerFully integrated into Atmel Studio 6, Atmel QTouch Composermakes it easy to build touch functionality into your design.QTouch Composer is the front-end software used to displayand evaluate the data reported from your touch design,making it easy for you to inspect how well your touchimplementation performs. With this integration, you can easilyand seamlessly develop capacitive touch functionality into yourapplication. You won’t need to toggle between different toolsto edit the code in Atmel Studio 6 and fine-tune your touchdesign in QTouch Composer.Atmel Software FrameworkThe Atmel Software Framework contains drivers for all peripherals,communication stacks, graphics, digital signal processing (DSP) and audiolibraries, and nearly 1,000 complete example designs. Using free source codefrom the Atmel Software Framework will accelerate the development of newapplications, while lowering your overall costs.Debugging Made EasyAtmel Studio 6 connects directly to Atmel debuggers and programmers. One of thebiggest advantages of modern MCUs is their ability to send debug data to your PC, givingyou a perfect view of what goes on inside. With a debugger connected, Atmel Studio 6can present the status of all processors, memories, communication interfaces and analoginterfaces in nicely formatted views, giving you access to critical system parameters. Theresimply is no faster way to identify bugs and optimize a design—in the lab or in the field.To learn more or download Atmel Studio 6 free of charge, visit /atmelstudio .© 2012 Atmel Corporation. All rights reserved. / Rev.: 8487B-Studio6-E-A4-09/12Atmel ®, Atmel logo and combinations thereof, and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. ARM ®, ARMPowered ® logo and others are the registered trademarks or trademarks of ARM Ltd. Other terms and product names may be the trademarks of others. Atmel logo and combinations thereof, and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries.Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and products descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life. Atmel Corporation 1600 Technology Drive, San Jose, CA 95110 USA T: (+1)(408) 441-0311 F: (+1)(408) 487-2600 | 。

RT9817 产品数据手册说明书

1DS9817-13 April 2022Features●Internally Fixed Threshold 1.2V to 5V in 0.1V Step ●High Accuracy ±1.5%●Low Supply Current 3μA●No External Components Required ●Quick Reset within 20μs●Built-in Recovery Delay Include 0ms, 55ms, 220ms,450ms Options●Low Functional Supply Voltage 0.9V ●CMOS Push-Pull Output●Small SC-82 and SOT-143 Packages●RoHS Compliant and 100% Lead (Pb)-FreePin ConfigurationApplications●Computers ●Controllers●Intelligent Instruments●Critical μP and μC Power Monitoring ●Portable/Battery-Powered EquipmentMicro-Power Voltage Detectors with Manual ResetOrdering InformationGeneral DescriptionThe RT9817 is a micro-power voltage detector with deglitched manual reset input supervising the power supply voltage level for microprocessors (μP) or digital systems. It provides internally fixed threshold levels with 0.1V per step ranging from 1.2V to 5V, which covers most digital applications. It features low supply current of 3μA.The RT9817 performs supervisory function by sending out a reset signal whenever the V DD voltage falls below a preset threshold level. This reset signal will last the whole period before V DD recovering. Once V DD recovered upcrossing the threshold level, the reset signal will be released after a certain delay time. To pull reset signal low manually, just pull the manual reset input (MR) below the specified V IL level. RT9817 is provided in SC-82 and SOT-143 packages.(TOP VIEW)SOT-143Marking Information For marking information, contact our sales representative directly or through a RichTek distributor located in your area, otherwise visit our website for detail.Note :Richtek p roducts are :❝RoHS compliant and compatible with the current require- ments of IPC/JEDEC J-STD-020.❝Suitable for use in SnPb or Pb-free soldering processes.SC-82RESET/RESET MRRESET/RESET MR RT9817A = 0ms (RESET)B = 55ms (RESET)C = 220ms (RESET)D = 450ms (RESET)E = 0ms (RESET)F = 55ms (RESET)G = 220ms (RESET)H = 450ms (RESET)2DS9817-13 April 2022 Functional Block DiagramTypical Application CircuitFunctional Pin DescriptionRESET/RESETMRPart StatusThe part status values are defined as below :Active : Device is in production and is recommended for new designs. Lifebuy : The device will be discontinued, and a lifetime -buy period is in effect. NRND : Not recommended for new designs.Preview : Device has been announced but is not in production. Obsolete : Richtek has discontinued the production of the device.3DS9817-13 April 2022Absolute Maximum Ratings (Note 1)●Terminal Voltage (with Respect to GND)V DD ------------------------------------------------------------------------------------------------------------------------−0.3V to 6.0V●All Other Inputs --------------------------------------------------------------------------------------------------------−0.3V to V DD +0.3V ●Input Current, I VDD -----------------------------------------------------------------------------------------------------20mA ●Power Dissipation, PD @ T A = 25°CSC-82--------------------------------------------------------------------------------------------------------------------0.25W SOT-143-----------------------------------------------------------------------------------------------------------------0.285W ●Package Thermal Resistance (Note 2)SC-82, θJA ---------------------------------------------------------------------------------------------------------------400°C SOT-143, θJA ------------------------------------------------------------------------------------------------------------350°C ●Lead Temperature (Soldering, 10sec.)---------------------------------------------------------------------------- 260°C●Storage T emperature Range ----------------------------------------------------------------------------------------−65°C to 125°C ●ESD Susceptibility (Note 3)HBM (Human Body Mode)------------------------------------------------------------------------------------------2kV MM (Machine Mode)--------------------------------------------------------------------------------------------------200VElectrical Characteristics(V= 3V, T = 25°C, unless otherwise specified)Recommended Operating Conditions (Note 4)●Junction T emperature Range ----------------------------------------------------------------------------------------−40°C to 125°C ●Ambient T emperature Range ----------------------------------------------------------------------------------------−40°C to 85°CTo be continued4DS9817-13 April 2022Note 1. Stresses listed as the above “Absolute Maximum Ratings ” may cause permanent damage to the device. These are forstress ratings. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may remain possibility to affect device reliability.Note 2. θJA is measured in the natural convection at T A = 25°C on a low effective thermal conductivity test board ofJEDEC 51-3 thermal measurement standard.Note 3. Devices are ESD sensitive. Handling precautions are recommended.Note 4. The device is not guaranteed to function outside its operating conditions.5DS9817-13 April 2022Typical Operating CharacteristicsSupply Current vs. Input Voltage01234123456Input Voltage (V)S u p p l y C u r r e n t I D D (u A )Output Voltage vs. Input Voltage012345670123456Input Voltage (V)O u t p u t V o l t a g e (V)Nch Driver Output Current vs. V DS020*********120012345V DS (V)O u t p u t C u r r e n t(m A )Supply Current vs. Input Voltage01234560123456Input Voltage (V)S u p p l y C u r r e n t (u A )Nch Driver Output Current vs. V DS010********600.511.522.533.5V DS (V)O u t p u t C u r r e n t (m A )Nch Driver Output Current vs. V DS00.40.81.21.622.400.30.60.91.21.5V DS (V)O u t p u t C u r r e n t(m A )6DS9817-13 April 2022 Nch Driver Sink Current vs. Input Voltage0102030400.511.522.533.5Input Voltage (V)S i n k C u r r e n t I S I N K (m A )Supply Current vs. Input Voltage01234123456Input Voltage (V)S u p p l y C u r re n t (u A )Power-Down Reset Delay vs. Temperature051015202530354045-50-25255075100125Temperature P o w e r -D o w n R e s e t D e l a y (u s)(°C)Power-Down Reset Delay vs. Temperature051015202530354045-50-25255075100125Temperature P o w e r -D o w n R e s e t D e l a y (u s )(°C)Power-Down Reset Delay vs. Temperature03691215-50-25255075100125Temperature P o w e r -D o w n R e s e t D e l a y (u s )(°C)Nch Driver Sink Current vs. Input Voltage0102030405012345Input Voltage (V)S i n k C u r r e n t I S I N K (m A )7DS9817-13 April 2022Output Delay Time vs. Load Capacitance0.010.111010010000.00010.00100.01000.1000 1.0000Load Capacitance (uF)O u t p u t D e l a y T i m e (m s )Power-Up Reset Time-Out vs. Temperature0255075100-50-25255075100125Temperature P o w e r -U p R e s e t T im e -O u t (m s )(°C)Reset Threshold Deviation vs. Temperature1.002.003.004.005.006.00-50-25255075100125Temperature R e s e t T h r e s h o l d D e v i a t i on (V )(°C)Pch Driver Output Current vs. Input Voltage0510152025123456Input Voltage (V)O u t p u t C u r r e n t(m A )Nch Driver Output Current vs. V DS204060801001201401600123456V DS (V)N c h D r i v e r O u t p u t C ur r e n t (m A )Power-Up Reset Time-Out vs. Temperature0100200300400500-50-25255075100125Temperature P o w e r -U p R e s e t T i me -O u t (m s )(°C)8DS9817-13 April 2022 Nch Driver Output Current vs. Input Voltage1020304050600123456Input Voltage (V)N c h D r i v e r O u t p u t C u r r e n t (m A )Output Voltage vs. Input Voltage01234567123456Input Voltage (V)O u t p u tV o l t a g e (V )Power-Down Reset Time-Out vs. Temperature051015202530-50-25255075100125Temperature P ow e r -D o w n R e s e t T i m e -O u t (u s )(°C)Power Down Reset Time-Out vs. Temperature0100200300400500-50-25255075100125Temperature P o w e r D o w n R e s e t T i m e -O u t (m s )(°C)9DS9817-13 April 2022Application InformationBenefits of Highly Accurate Reset ThresholdMost μP supervisor ICs have reset threshold voltages between 1% and 1.5% below the value of nominal supply voltages.This ensures a reset will not occur within 1% of the nominal supply, but will occur when the supply is 1.5% below nom inal.10DS9817-13 April 2022SOT-143 Surface Mount Package11DS9817-13 April Richtek Technology CorporationHeadquarter5F, No. 20, Taiyuen Street, Chupei CityHsinchu, Taiwan, R.O.C.Tel: (8863)5526789 Fax: (8863)5526611Information that is provided by Richtek Technology Corporation is believed to be accurate and reliable. Richtek reserves the right to make any change in circuit design,specification or other related things if necessary without notice at any time. No third party intellectual property infringement of the applications should be guaranteed by users when integrating Richtek products into any application. No legal responsibility for any said applications is assumed by Richtek.Richtek Technology Corporation Taipei Office (Marketing)5F, No. 95, Minchiuan Road, Hsintien City Taipei County, Taiwan, R.O.C.Tel: (8862)86672399 Fax: (8862)86672377Email:*********************SC -82 Surface Mount Package。

trimAl Phylogenetics Alignment Trimming Tool说明书

trimAl: a tool for automated alignment trimming in large-scale phylogenetics analyses Salvador Capella-Gutiérrez, Jose M. Silla-Martínez and Toni GabaldónTutorialVersion 1.2trimAl tutorialtrimAl is a tool for the automated trimming of Multiple Sequence Alignments. A format inter-conversion tool, called readAl, is included in the package. You can use the program either in the command line or webserver versions. The command line version is faster and has more possibilities,so it is recommended if you are going to use trimAl extensively.The trimAl webserver included in Phylemon 2.0 provides a friendly user interface and the opportunity to perform many different downstream phylogenetic analyses on your trimmed alignment. This document is a short tutorial that will guide you through the different possibilities of the program.Additional information can be obtained from where a more comprehensive documentation is available.If you use trimAl or readAl please cite our paper:trimAl: a tool for automated alignment trimming in large-scale phylogenetic analyses.Salvador Capella-Gutierrez;Jose M.Silla-Martinez;Toni Gabaldon.Bioinformatics 2009 25: 1972-1973.If you use the online webserver phylemon or phylemon2, please cite also this reference:Phylemon:a suite of web tools for molecular evolution,phylogenetics and phylogenomics.Tárraga J, Medina I, Arbiza L, Huerta-Cepas J, Gabaldón T, Dopazo J, Dopazo H. Nucleic Acids Res. 2007 Jul;35 (Web Server issue):W38-42.1. Program Installation.If you have chosen the trimAl command line version you can download the source code from the Download Section in trimAl's wikipage.For Windows OS users, we have prepared a pre-compiled trimAl version to use in this OS. Once the user has uncompressed the package, the user can find a directory,called trimAl/bin, where trimAl and readAl pre-compiled version can be found.Meanwhile for the OS based on Unix platform, e.g. GNU/Linux or MAC OS X, the user should compile the source code before to use these programs. To compile the source code, you have to change your current directory to trimAl/source and just execute "make".Once you have the trimAl and readAl binaries program, you should check if trimAl is running in appropriate way executing trimal program before starting this tutorial.2. trimAl. Multiple Sequence Alignment dataset.In order to follow this tutorial, we have prepared some examples. These examples have been taken from and you can use the codes from these files to get more information about it in this database.You can find three different directories called Api0000038, Api0000040 and Api0000080 with different files. The directory contains these files:A file .seqs with all the unaligned sequences.A file .tce with the Multiple Sequence Alignment produced by T-Coffee1.A file .msl with the Multiple Sequence Alignment produced by Muscle2.A file .mft with the Multiple Sequence Alignment produced by Mafft3.A file .clw with the Multiple Sequence Alignment produced by Clustalw4.A file .cmp with the different names of the MSAs in the directory. This file would be used by trimAl to get the most consistent MSA among the different alignments.You can use any directory to follow the present tutorial.3. Useful trimAl's features.Among the different trimAl parameters, there are some features that can be useful to interpret your alignment results:-htmlout filename. Use this parameter to have the trimAl output in an html file. In this way you can see the columns/sequences that trimAl maintains in the new alignment in grey color while the columns/sequences that have been deleted from the original alignment are in white color.-colnumbering. This parameter will provide you the relationship between the column numbers in the trimmed and the original alignment.-complementary. This parameter lets the user get the complementary alignment, in other words,when the user uses this parameter trimAl will render the columns/sequences that would be deleted from the original alignment.-w number. The user can change the windows size, by default 1, to take into account the surrounding columns in the trimAl's manual methods. When this parameter is fixed, trimAl take into account number columns to the right and to the left from the current position to compute any value, e.g. gap score, similarity score, etc. If the user wants to change a specific windows size value should use the correspond parameter-gw to change window size applied only a gap score assessments, -sc to change window size applied only to similiraty score calculations or -cw to change window size applied only to consistency part.4. Useful trimAl's/readAl's features.Both programs, trimAl and readAl, share common features related to the MSA conversion. It is possible to change the output format for a given alignment, by default the output format is the same than the input one, you can produce an output in different format with these options: -clustal. Output in CLUSTAL format.-fasta. Output in FASTA format.-nbrf. Output in PIR/NBRF format.-nexus. Output in NEXUS format.-mega. Output in MEGA format.-phylip3.2. Output in Phylip NonInterleaved format.-phylip. Output in Phylip Interleaved format.5. Getting Information from Multiple Sequence Alignment.trimAl computes different scores, such as gap score or similarity score distribution, from a given MSA. In order to obtain this information, we can use different parameters through the command line version.To do this part,we are going to use the MSA called Api0000038.msl.This file is in the Api0000038 directory.$ cd Api0000038$ trimal -in Api0000038.msl -sgt$ trimal -in Api0000038.msl -sgc$ trimal -in Api0000038.msl -sct$ trimal -in Api0000038.msl -scc$ trimal -in Api0000038.msl -sidentYou can redirect the trimAl output to a file. This file can be used in subsequent steps as input of other programs, e.g.gnuplot,,microsoft excel,etc,to do plots of this information.$ trimal -in Api0000038.msl -scc > SimilarityColumnsFor instance, in the lines below you can see how to plot the information generated by trimAl using the GNUPLOT program.$ gnuplotplot 'SimilarityColumns' u 1:2 w lp notitleset yrange [-0.05:1.05]set xrange [-1:1210]set xlabel 'Columns'set ylabel 'Residue Similarity Score'plot 'SimilarityColumns' u 1:2 w lp notitleexitIn this other example you can see the gaps distribution from the alignment. This plot also was generated using GNUPLOT$ trimal -in Api0000038.msl -sgt > gapsDistribution$ gnuplotset xlabel '% Alignment'set ylabel 'Gaps Score'plot 'gapsDistribution' u 7:4 w lp notitleexit6. Using user-defined thresholds.If you do not want to use any of the automated procedures included in trimAl (see sections 7 and 8) you can set your own thresholds to trim your alignment. We will use the parameter -htmlout filename for each example so differences can be visualized. In this example, we will use the Api0000038.msl file from the Api0000038 directory.Firstly, we are going to trim the alignment only using the -gt value which is defined in the [0 - 1] range. In this specific example, those columns that do not achieve a gap score, at least, equal to 0.190, meaning that the fraction of gaps on these columns are smaller than this value, will be deleted from the input alignment.$ trimal -in Api0000038.msl -gt 0.190 -htmlout ex01.htmlYou can see different parts of the alignment in the image below.This figure has been generated from the trimAl's HTML file for the previous example.In this other example, we can see the effect to be more strict with our threshold. An usual consequence of higher stringency is that the trimmed MSA has fewer columns. Be careful so you do not remove too much signal$ trimal -in Api0000038.msl -gt 0.8 -htmlout ex02.htmlTo be on the safe side, you can set a minimal fraction of your alignment to be conserved. In this example,we have reproduced the previous example with the difference that here we required to the program that, at least, conserve the 80% of the columns from the original alignment. This will remove the most gappy 20% of the columns or stop at the gap threshold set.$ trimal -in Api0000038.msl -gt 0.8 -cons 80 -htmlout ex03.htmlSecondly,we are going to introduce other manual threshold-st value.In this case,this threshold,also defined in the[0-1]range,is related to the similarity score.This score measures the similarity value for each column from the alignment using the Mean Distance method, by default we use Blosum62 similarity matrix but you can introduce any other matrix (see the manual). In the example below, we have used a smaller threshold to know its effect over the example.$ trimal -in Api0000038.msl -st 0.003 -htmlout ex04.htmlIn this example, similar to the previous example, we have required to conserve a minimum percentage of the original alignment in a independent way to fixed by the similarity threshold.A given threshold maintains a larger number of columns than the cons threshold, trimAl selects this first one.$ trimal -in Api0000038.msl -st 0.003 -cons 30 -htmlout ex05.htmlThirdly, we are going to see the effect of combining two different thresholds. In this case, trimAl only maintains those columns that achieve or pass both thresholds.$ trimal -in Api0000038.msl -st 0.003 -gt 0.19 -htmlout ex06.htmlFinally, we are going to see the effect of combining two different thresholds with the cons parameter. In this case, if the number of columns that achieve or pass both thresholds is equal or greater than the percentage fixed by cons parameter, trimAl chose these columns. However, if the number of columns that achieve or pass both thresholds is less than the number of columns fixed by cons parameter, trimAl relaxes both to thresholds in order to retrieve those columns that lets to achieve this minimum percentage.$ trimal -in Api0000038.msl -st 0.003 -gt 0.19 -cons 60 -htmlout ex07.html7. Selection of the most consistent alignment.trimAl can select the most consistent alignment when more than one alignment is provided for the same sequences (and in the same order) using the -compareset filename parameter. To do this part, we are going to move to Api0000040 directory, we can find there a file calledApi0000040.cmp listing the alignment paths. Using this file, we execute the instruction below to select the most consistent alignment among the alignment provided$ trimal -compareset Api0000040.cmpAs in previous section, once trimAl has selected the most consistent alignment, we can get information about the alignment selected using the appropriate parameters. For example, we can use the follow instructions to know the consistency value for each column in the alignment or its consistency values distribution$ trimal -compareset Api0000040.cmp -sct$ trimal -compareset Api0000040.cmp -sccAlso, we can trim the selected alignment using a specific threshold related to the consistency value. To do that, we should use the -ct value where the value is a number defined in the [0 - 1] range. This number refers to the average conservation of residue pars in that column with respect to the other alignments.$ trimal -compareset Api0000040.cmp -ct 0.6 -htmlout ex08.htmlOn the same way than the previous section, we can define a minimum percentage of columns that should be conserve in the new alignment. For this purpose, we have to use the cons parameter as we explained before.$ trimal -compareset Api0000040.cmp -ct 0.6 -cons 50 -htmlout ex09.htmlFinally, we can combine different thresholds, in fact, we can use all of them as well as we can define a minimum percentage of columns that should be conserve in the output alignment. In the line below, you can see an example of this situation.$ trimal -compareset Api0000040.cmp -ct 0.6 -cons 50 -gt 0.8 -st 0.01-htmlout ex10.html8. Applying automated methods.One of the most powerful aspects of trimAl is that it provides you with several automated options.This option will automatically select the most appropriate thresholds for your alignment after examining the distribution of various parameters along your alignment. Among the alignment features that trimAl takes into account to compute these optimal cut-off are the gap distribution, the similarity distribution, the identity score, etc.You can find a complete explanation about all of these methods in the trimAl's Publications Section.Here,we provide some examples on how to use these methods.The automated methods, gappyout, strict and strictpus, can be used independently if you are working with one or more than one alignment, in the last case, for the same sequences.In the lines below, you can see how to use the gappyout method in both ways. This method will eliminate the most gappy fraction of the columns from your alignment. For this, we are going to continue using the same directory than the previous section.$ trimal -compareset Api0000040.cmp -gappyout -htmlout ex11.html$ trimal -in Api0000040.mft -gappyout -htmlout ex12.htmlIn this case, we are going to use the same files than in the example before but we have changed the method to trim the alignmnet. Now, we are using strict and strictplus methods. These two methods combine the information on the fraction of gaps in a column and their similarity scores, being strictplus for more stringent than strict method.$ trimal -compareset Api0000040.cmp -strict -htmlout ex13.html$ trimal -in Api0000040.clw -strictplus -htmlout ex14.htmling an heuristic method to decide which is the best automated method for a given MSA.Finally, we implemented an heuristic method to decide which is the best automated method to trim a given alignment. The heuristic method takes into account alignment features such as the number of sequences in the alignment as well as some measures about the identity score among the sequences in the alignment or among the best pairwise sequences in that MSA. According to these characteristics trimAl will decide upon one of the two automated methods (gappyout or strictplus).To illustrate how to use this method, we provide a couple of example using the same directory than the section before. First, we used trimAl to selecte the most consistent alignment and then we trimmed that alignmnet using our heuristic method.$ trimal -compareset Api0000040.cmp -automated1 -htmlout ex15.htmlThen, we trim a single MSA using the previously mentioned method.$ trimal -in Api0000040.msl -automated1 -htmlout ex16.html10. Getting more information.We hope that this short introduction to trimAl's features has been useful to you.We advise you to visit periodically the trimAl's wikipage()where you could get the latest news about the program as well as more information, examples, etc, about trimAl's package. You can also subscribe to the mailing list if you want to be updated in new trimAl developing.11. References.1.T-Coffee: A novel method for fast and accurate multiple sequence alignment.Notredame C, Higgins DG, Heringa J. J Mol Biol. 2000 Sep 8;302(1):205-17.2.MUSCLE:multiple sequence alignment with high accuracy and highthroughput. Edgar RC.Nucleic Acids Res. 2004 Mar 19;32(5):1792-7.3.MAFFT: a novel method for rapid multiple sequence alignment based on fastFourier transform. Katoh K, Misawa K, Kuma K, Miyata T. Nucleic Acids Res. 2002 Jul 15;30(14):3059-66.4.CLUSTAL W:improving the sensitivity of progressive multiple sequencealignment through sequence weighting,position-specific gap penalties and weight matrix choice. Thompson JD, Higgins DG, Gibson TJ. Nucleic Acids Res. 1994 Nov 11;22(22):4673-80.。

INTERNORMEN-electronics Bottle Sampling System BSS

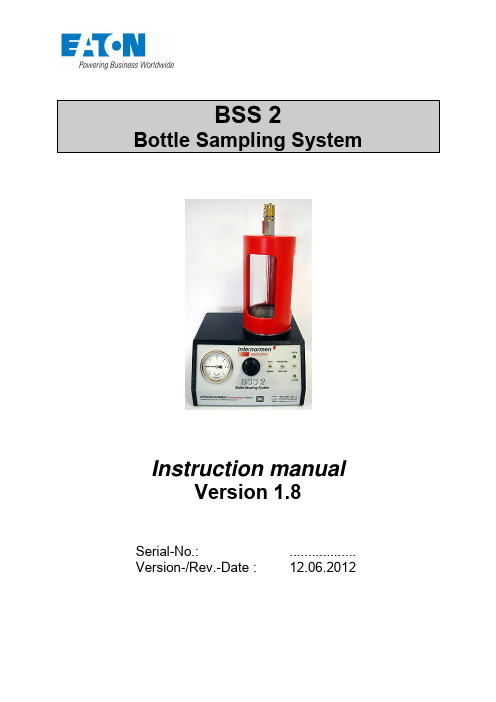

Instruction manualVersion 1.8Serial-No.: .................. Version-/Rev.-Date : 12.06.2012Contents1. General (3)2. Safety Instructions (4)3. Extent of Delivery (5)4. Switch Panel (6)5. Bottle Sampling (7)5.1. Reservoir (7)5.2. Sampling (7)6. Commissioning (8)6.1. Power supply (8)6.2. Compressed Air Supply (9)6.2.1. Operation with the Compressor from INTERNORMEN-electronics (10)6.2.2. Operation with Existing Compressed Air Supply (11)6.3. Connection to CCS 1 / CCS 2 (12)7. Before the Analysis (13)7.1. Conditioning of the Sample (14)8. Analysis of sample (14)8.1. Degassing (14)8.2. Sample Feed (17)9. Cleaning and Maintenance (19)10. Technical Data (20)10.1. Connections (20)10.1.1. Electrical (20)10.1.2. Pneumatic (20)1. GeneralDear CustomerWe congratulate you on buying the INTERNORMEN-electronics Bottle Sampling System BSS 2. Before commissioning please read this manual carefully to prevent damages to the BSS 2.You have purchased a product which is technically up-to-date and which enables you to perform a particle count in lab quality, at any points of your plant where an online-analysis is not possible.The sampling and the output of results only take a few minutes.In general an online-measurement is to be preferred rather than a bottle sample analysis. The process from sampling to particle counting involves many possibilities of mistakes. Therefore this kind of analysis should be carried out only by trained per-sonal.2. Safety Instructions☝To prevent accidents it is important to keep strictly to the manual during the oper-ation of the BSS 2.☝Never try to open the pressure chamber, when the system pressure varies from the ambient air pressure.☝Never try to pressurise the chamber before being sure that it is tightly closed (see the lighting diode!)☝ Never use damaged or defective components (threaded joints, hoses, connect-ors etc.)!☝ A damaged pressure vessel (scratches in the glass, bent housing etc.) must not be used.☝Never open the BSS 2 housing !3. Components of BSS 2The BSS 2 includes :- Case [1]- Instrument base with integrated service unit [2] - Pressure vessel [3] - Power supply unit [4] - Connector for pneumatics [5]- High pressure hose with mini-measuring connection M 16x2 [6] - Compressor [7] (optional) -Spiral hose [8] (optional)Illustration 1178235464. Switch PanelIllustration 2B1 – Vacuum + pressure gauge B2 – Regulator (pressure + vacuum) B3 – Switch VENT / WORKB4 – Switch PRESSURE / VACUUM B5 – Switch OPEN / CLOSEB6 – Green light emitting diode OPEN B7 – Yellow light emitting diode CLOSEB1B5 B3B2B6 B4B75. Bottle Sampling5.1. ReservoirBefore sampling make sure that the reservoir to be used can be put into the pressure chamber of the BSS 2.To guarantee reliable results of measurement you should only use reservoirs whose cleanliness according to ISO 3722 is proved. You can buy them directly from INTERNORMEN Technology GmbH (two sample bottle set, Best. Nr. 313427). These glasses should be used only once.5.2. SamplingThe bottle sampling requires a very careful handling. First flush the sampling point for a few seconds. Open the sample reservoir just directly before taking the sample, and close it immediately afterwards. Only this way the ambient influences do not impact your measuring results.Label your samples carefully. Note:Sampling pointDate and time of samplingSampler (name, first name)Special notes, if applicableThis is important for samplings at different plants, respectively different points of the plant to help prevent any unclearness.6. Commissioning6.1. Power supplyFor the operation of the BSS 2 you should only use the plug-in power supply supplied by INTERNORMEN-electronics, which is included in the system. Make sure that this power supply unit is set to the required output voltage of 12 V DC. (Illustration 3).Illustration 3Put the plug of the power supply unit into the current outlet (230 V~ 50 Hz) and the connection cable into the socket of the BSS 2 (Illustration 4) on the backside of the device. The actual unit might vary depending on the respective country's voltage.Illustration 4When correctly connected, one of the light emittingdiodes OPEN respectively CLOSE should light upafter a few seconds.Turn the switch VENT / WORK to the directionVENT, if it is in WORK.6.2. Compressed Air SupplyIn addition to the electric connection, the BSS 2 of INTERNORMEN-electronics also requires an external compressed air supply. This is provided either by an existing compressed air piping or the compressor optionally available.6.2.1. Operation with the Compressor from INTERNORMEN-electronics Instructions for the handling of the compressor are given in the enclosed manual.Connect the BSS 2 with the com-pressor. For this use the spiral hose(Pos. 8, Illustration 1) which is op-tionally available. Put the hose pluginto the coupler of the compressor.(Illustration 5).Illustration 5Now put the other end (coupler) into the quick con-nect plug at the backside of the BSS 2 (Illustration6). The coupler is locked, when you hear a clickingnoise while putting into one another.To release the plug connectors, pull back the lock-ing ring of the closing coupler.Before releasing make sure that the system is notunder pressure.Illustration 6Integrated service unitThe serialize inserted service unit prevents the entryof dirt and humidity into the BSS 2.To empty the container over knurled screw duringaccumulation of liquid.6.2.2. Operating with Existing Compressed Air SupplyConnect the BSS 2 to the pressure air supply. For this please use the optional attached plug-in connection to be connected with the device. This plug-in connection has an internal screw thread G 1/4 for the hose. Please make sure a firm seat and sealing between the hose and connector.Now slip the connection cap over the plug at thebackside of the BSS 2 (Illustration 7).To release the plug connectors, pull back thelocking ring of the closing coupler.Before releasing make sure that the system isnot under pressure.Illustration 7Integrated service unitThe serialize inserted service unit prevents the entryof dirt and humidity into the BSS 2.To empty the container over knurled screw duringaccumulation of liquid.6.3. Connection to CCS 1 / CCS 2Connect the BSS 2 to the contamination control system by means of the pressure hose (6, Illustration 1) included in the BSS 2. First remove the screw cap of the mini-measuring connection at the top of the pressure vessel (Illustration 8). Now you can mount the hose. The same way of connection applies to the CCS 1 as well as the CCS 2.Illustration 87. Before the AnalysisAfter following the instructions you are ready to operate the BSS 2. Make sure that you have sufficient air supply and pressure (max. 10 bar).Turn the compressor on (if operated by compressor), respectively open thefeeding main to the BSS 2 (existing compressed air supply). Set the pressure control valve to a rate between 6,0 and 6,5 bar. A different pressure rate might cause malfunctions or damages to the BSS 2.Turn the switch OPEN / CLOSE to the position OPEN. When the diodeOPEN (green) lights up, the pressure chamber lock is released. Now youcan remove the pressure vessel.Make sure that an O-ring (90x2,5) is inside the locking device (Illustration 9).Illustration 97.1. Conditioning of the SampleBefore putting the bottle into the BSS 2 for examination, homogenize thoroughly and ½ - 1 minute in the ultrasonic bath place. For exact measuring results an equal distribution of the particles is important. The following shakingprocedure should take about two minutes, dependent on the fluid viscosity, contamination and time interval between sampling and analysis.The vibration time depends directly on the fluid viscosity.< ISO-VG-32 2 minISO-VG-46 ... 100 3 ... 4 min> ISO-VG-100 5 ... 10 min (additional warming-up is indicated)8. Analysis of sampleInstructions for the operation of the CCS1, respectively the CCS2 can be taken from their manuals.Immediately after termination of the sample conditioning the analysis should be done.8.1. DegassingPlace the sample on the cover plate of the pressure chamber at the topside of the device. Please make sure once again that the O-ring is in proper position. Place the pressure vessel over the sample. Be aware of the correct position, i.e. it has to have slipped completely downwards. Now you can turn the switch OPEN / CLOSE to the position CLOSE (Illustration 12, 1). Wait until after a few seconds the diode CLOSE (yellow) lightens. Close the ball valve at the topside of the pressure vessel (Illustra-tion 10).Illustration 10Turn the switch VENT / WORK to the position WORK (Illustration 11, 2). Turn the switch PRESSURE / VACUUM to the position VACUUM (Illustration 11, 3).Illustration 11Pull out the handle of the pressure regulator.Illustration 12closeopen123Now turn the handle clockwise (Illustration 13) until – 1,0 bar. This will produce a vacuum in the pressure chamber. The more you turn, the lower the pressure in the chamber. You can observe this on the vacuum / pressure gauge (Illustration 13).Illustration 13Keep the vacuum in the chamber until there are no gas bub-bles in the fluid anymore.Illustration 14Turn the handle (illustration 15) anticlockwise until 0,0.Illustration 158.2. Sample FeedTurn the switch PRESSURE / VACUUM to the position PRESSURE (Illustration 16, 1).Now turn the handle (Illustration 16, 2) slowly clockwise. This will increase the pres-sure in the chamber. Continue turning until the gauge (Illustration 16) indicates a pressure of about approximate 3,0 bar. When you hear a hissing noise, the pressure in the chamber is too high. In this case turn the handle anticlockwise until this noise stops.Illustration 1612Open the ball valve at the top of the pressure vessel (Illustration 15). Turn the switch PRESSURE / VACUUM to the position PRESSURE (Illustration 16, 1).Illustration 15Now you can start the measurement at your particle counter. Please observe the in-st ructions for …Bottle Sampling“ in the manual of your contamination co ntroller.Illustration 17closeopenAfter finishing the measurements turn the switch VENT / WORK to the position VENT. You will then hear a hissing noise produced by the air escaping from the pressure chamber. Wait until this is ended, and then turn the switch OPEN / CLOSE to the position OPEN. When the green diode OPEN lights up, the vessel is unlocked and you can remove it by lifting upwards. Remove the sample glass.9. Cleaning and MaintenancePlease keep the device and the feeding tubes absolutely clean. After every use the device has to be flushed. For the flushing please use fine filtered low viscosity oil (e.g. ISOVG22 / ISOVG32). Before operating the BSS2 after a long time of not using it (about 2 weeks), the particle counting device should be flushed properly.For the cleaning of the pressure dome and the device housing please use a soft, fuzz-free cloth.Take care that the ascending tube is not bent while cleaning the pressure cham-ber. A contamination especially of this component would have negative affects on correct counting results, as it is in direct contact with the sample.Wipe the oil remains away from the plate of the pressure chamber lock and from the sealing area. For the cleaning do not use any aggressive chemical or rubbing agents.10. Technical DataDimensions: 220 x 240 x 390Weight: 6,5 kgInitial pressure: 0...4 barVacuum: 0...-0,95 bar10.1. Connections10.1.1. ElectricalPower supply / mains: 230V ~ 50 Hz or 110 V ~ 60 HzPower supply / device: 12 V DC10.1.2. PneumaticPressure range: 5...7 barFlow rate: min. 40 l/min airConnections: Rapid action coupling NW 7,2 with internal thread G ¼Mini-measuring connection with screw coupling M16 x 2 Subject to technical alterations!North America — HQ70 Wood Ave., South, 2nd Floor Iselin, NJ 08830Toll Free: (800) 656-3344 (North America Only)Voice: (732) 767-4200ChinaNo. 3, Lane 280, Linhong Road Changning District, 200335 Shanghai, P.R. ChinaVoice: +86-21-5200-0099 Singapore4 Loyang Lane #04-01/02 Singapore 508914Voice: +65-6825-1668Europe/Africa/Middle EastFriedensstraße 41D-68804 Altlussheim, GermanyVoice: +49-6205-2094-0Auf der Heide 253947 Nettersheim, GermanyVoice: +49-2486-809-0An den Nahewiesen 2455450 Langenlonsheim, GermanyVoice: +49 6704 204-0BrazilAv. Julia Gaioli, 474 –Bonsucesso07251-500 – Guarulhos, BrazilVoice: +55 (11) 2465-8822For more information, please e-mail us at filtra-******************Visit us online /filtration for a completelist of Eaton´s filtration products.©2012 Eaton Corporation. All Rights Reserved.All trademarks and registered trademarks are the property of their respectiveowners. Litho USA.All information and recommendations appearing in this brochure concerning theuse of products described herein are based on tests believed to be reliable.However, it is the user’s responsibility to determine the suitability for his own useof such products. Since the actual use by others is beyond our control, no guaran-tee, expressed or implied, is made by Eaton as to the effects of such use or theresults to be obtained. Eaton assumes no liability arising out of the use by othersof such products. Nor is the information herein to be construed as absolutelycomplete, since additional information may be necessary or desirable whenparticular or exceptional conditions or circumstances exist or because of applica-ble laws or government regulations.。

AutoDock4.2.6_UserGuide

User Guide AutoDock Version 4.2Updated for version 4.2.6Automated Docking of Flexible Ligands to Flexible Receptors Garrett M. Morris, David S. Goodsell, Michael E. Pique, William “Lindy” Lindstrom, Ruth Huey, Stefano Forli, William E. Hart, Scott Halliday, Rik Belew and Arthur J. OlsonModification date: July 28, 2014 15:30 D7/P7AutoDock, AutoGrid, AutoDockTools, Copyright © 1991-2009ContentsAutomated DockingIntroduction (3)Getting Started with AutoDock (3)Whatʼs New? (5)Support (7)TheoryOverview of the Free Energy Scoring Function (8)Using AutoDockSTEP 1: Preparing Coordinates (12)Creating PDBQT files with AutoDockTools (13)STEP 2: Running AutoGrid (18)Creating grid parameter files with AutoDockTools (19)STEP 3: Running AutoDock (20)Choosing a protocol for your application (21)Creating docking parameter files with AutoDockTools (23)STEP 4: Evaluating the Results of a Docking (24)Information in the docking log file (24)Analyzing docking results with AutoDockTools (24)Appendix I: AutoDock File FormatsPDBQT format for coordinate files (27)PDBQT format for flexible receptor sidechains (29)AutoGrid Grid Parameter File: GPF (30)Atomic Parameter File (33)Grid Map File (35)Grid Map Field File (36)AutoDock Docking Parameter File: DPF (37)Appendix II: Customizing the Docking ProtocolIntroduction (51)Docking parameter file examples (56)Appendix III: Docking Flexible Rings with AutoDock Introduction (61)Flexible RIngs (62)Reference (65)Appendix IV: AutoDock ReferencesAutomated DockingIntroductionAutoDock is an automated procedure for predicting the interaction of ligands with biomacromolecular targets. The motivation for this work arises from problems in the design of bioactive compounds, and in particular the field of computer-aided drug design. Progress in biomolecular x-ray crystallography continues to provide important protein and nucleic acid structures. These structures could be targets for bioactive agents in the control of animal and plant diseases, or simply key to the understanding of fundamental aspects of biology. The precise interaction of such agents or candidate molecules with their targets is important in the development process. Our goal has been to provide a computational tool to assist researchers in the determination of biomolecular complexes.In any docking scheme, two conflicting requirements must be balanced: the desire for a robust and accurate procedure, and the desire to keep the computational demands at a reasonable level. The ideal procedure would find the global minimum in the interaction energy between the substrate and the target protein, exploring all available degrees of freedom (DOF) for the system. However, it must also run on a laboratory workstation within an amount of time comparable to other computations that a structural researcher may undertake, such as a crystallographic refinement. In order to meet these demands a number of docking techniques simplify the docking procedure. AutoDock combines two methods to achieve these goals: rapid grid-based energy evaluation and efficient search of torsional freedom.The current version of AutoDock, using the Lamarckian Genetic Algorithm and empirical free energy scoring function, typically will provide reproducible docking results for ligands with approximately 10 flexible bonds. Our related software, AutoDock Vina (), uses a simpler scoring function that allows a faster search method, and provides reproducible results for larger systems with upwards of 20 flexible bonds. A more complete discussion of options is included below in the section "Choosing a Protocol for Your Application."This guide includes information on the methods and files used by AutoDock and information on use of AutoDockTools to generate these files and to analyze results.Getting Started with AutoDockAutoDock and AutoDockTools, the graphical user interface for AutoDock are available on the WWW at:/The WWW site also includes many resources for use of AutoDock, including detailed Tutorials that guide users through basic AutoDock usage, docking with flexible rings, and virtual screening with AutoDock. Tutorials may be found at:/faqs-help/tutorialAutoDock calculations are performed in several steps: 1) preparation of coordinate files using AutoDockTools, 2) precalculation of atomic affinities using AutoGrid, 3) docking of ligands using AutoDock, and 4) analysis of results using AutoDockTools.Step 1—Coordinate File Preparation. AutoDock4.2 is parameterized to use a model of the protein and ligand that includes polar hydrogen atoms, but not hydrogen atoms bonded to carbon atoms. An extended PDB format, termed PDBQT, is used for coordinate files, which includes atomic partial charges and atom types. The current AutoDock force field uses several atom types for the most common atoms, including separate types for aliphatic and aromatic carbon atoms, and separate types for polar atoms that form hydrogen bonds and those that do not. PDBQT files also include information on the torsional degrees of freedom. In cases where specific sidechains in the protein are treated as flexible, a separate PDBQT file is also created for the sidechain coordinates. AutoDockTools, the Graphical User Interface for AutoDock, may be used for creating PDBQT files from traditional PDB files.Step2—AutoGrid Calculation. Rapid energy evaluation is achieved by precalculating atomic affinity potentials for each atom type in the ligand molecule being docked.In the AutoGrid procedure the protein is embedded in a three-dimensional grid and a probe atom is placed at each grid point. The energy of interaction of this single atom with the protein is assigned to the grid point. AutoGrid affinity grids are calculated for each type of atom in the ligand, typically carbon, oxygen, nitrogen and hydrogen, as well as grids of electrostatic and desolvation potentials. Then, during the AutoDock calculation, the energetics of a particular ligand configuration is evaluated using the values from the grids.Step 3—Docking using AutoDock. Docking is carried out using one of several search methods. The most efficient method is a Lamarckian genetic algorithm (LGA), but traditional genetic algorithms and simulated annealing are also available. For typical systems, AutoDock is run several times to give several docked conformations, and analysis of the predicted energy and the consistency of results is combined to identify the best solution.Step 4—Analysis using AutoDockTools. AutoDockTools includes a number of methods for analyzing the results of docking simulations, including tools for clustering results by conformational similarity, visualizing conformations, visualizing interactions between ligands and proteins, and visualizing the affinity potentials created by AutoGrid.Whatʼs New?AutoDock 4.2 includes several enhancements over the methods available in AutoDock 3.0.Sidechain Flexibility. AutoDock 4.2 allows incorporation of limited sidechain flexibility into the receptor. This is achieved by separating the receptor into two files, and treating the rigid portion with the AutoGrid energy evaluation and treating the flexible portion with the same methods as the flexible ligand.Force Field. The AutoDock 4.2 force field is designed to estimate the free energy of binding of ligands to receptors. It includes an updated charge-based desolvation term, improvements in the directionality of hydrogen bonds, and several improved models of the unbound state. Expanded Atom Types. Parameters have been generated for an expanded set of atom types including halogens and common metal ions.Desolvation Model. The desolvation model is now parameterized for all supported atom types instead of just carbon. Because of this, the constant function in AutoGrid is no longer used, since desolvation of polar atoms is treated explicitly. The new model requires calculation of a new map in AutoGrid that holds the charge-based desolvation information.Unbound State. Several models are available for estimating the energetics of the unbound state, including an extended model and a model where the unbound state is assumed to be identical with the protein-bound state.For users of AutoDock 4.0, there are several changes in AutoDock 4.2:Default Unbound State. The default model for the unbound state has been changed from “extended” to “bound=unbound”. This is in response to persistent problems when docking sterically-crowded ligands. The “extended” unbound state model is available in AutoDock 4.2 through use of the “unbound extended” keyword.Backwards Compatibility. We have made every attempt to ensure that docking parameter files generated for use in AutoDock 4.0 should be correctly run by AutoDock 4.2.For users of AutoDock 4.2.3 or 4.2.4, there are several changes in AutoDock 4.2.5:Finer Control of Output. In response to the widespread use of AutoDock in virtual screening, we have modified the “outlev” command to allow more control over the level of output. The default of “1” will now output primarily information on the docked conformations and analysis, and higher levels will provide diagnostic information.Program will Halt with Critical Errors. Several error conditions that previously gave warnings will now cause AutoDock to halt. This is a response to use of AutoDock in virtual screening,where the user may not examine each individual docking experiment, and critical errors may not be noticed.Ligand Internal Electrostatics are now ‘on’ by Default. The electrostatic interactions between non-bonded atoms in flexible ligands are now considered ‘on’ by default. Previous releases of AutoDock required the “intelec” command to turn this on. If you wish to ignore these interactions and restore the previous default behavior, use “intelec off” in your DPF.Force Field Consistency. Smoothing of potentials has been added to internal energy potentials, to make them consistent with intermolecular energy potentials. This will have a small effect on conformations when docking with rigid receptors, and possibly a significant effect on conformations and predicted free energies when docking with flexible receptors. In addition, an error in output of energies with flexible receptors has been corrected, and AutoDock’s intra-ligand desolvation potential cutoff distance has been increased to match AutoGrid’s.For users of AutoDock 4.2.5, there are several changes in AutoDock 4.2.6:Platforms. More computer platforms are supported:•Linux2 on Intel i86 (32-bit) and on Intel x86_64 (64-bit)•Linux3 on Intel x86_64 (64-bit)•Macintosh OS X 10.5 (Leopard) on PowerPC (32- and 64-bit), OS X 10.5-10.9 (Leopard, Snow Leopard, Lion, Mountain Lion, and Mavericks) on Intel i86 (32-bit) and Intelx86_64 (64-bit)•Solaris 8 (SunOS 5.8) on SPARC•Windows 5 (XP), 6 (Vista), 7, 8.1 on Intel i86.Now, both AutoDock and AutoGrid are compiled using double-precision arithmetic. There is also better cross-platform compatibility of the internal random number generator.Improved Error Checking. There is improved error checking of command-line arguments. AutoDock now checks the atom numbers that define internal and “flexres” torsions.Job and Run Provenance and Reproducibility. Each docking log file (dlg) always contains the host name, run date, working directory, and names of input PDBQT files. Each docking run always contains its initial random number seeds, its ending total energy, and its final state in a uniform format suitable for automated analysis. Invoking “autodock4 (or autogrid4) –version” reports compile-time configuration options.Clustering of Multiple Search Algorithms. Now, multiple search methods can be used in a single AutoDock job: for example, 50 runs of Lamarckian Genetic Algorithm followed by 50 runs of Simulated Annealing. The runs are done serially: no results carry over from one algorithm to the next. All results are ranked and clustered together in the analysis step at the end of the entire job.Visualization of Simulated Annealing and Local-Search-Only Runs. You can now use ADT (AutoDock Tools) to visualize results from AutoDock jobs that use simulated annealing or local-search-only. You must download the latest build of ADT from/downloads/latest4.2.6 Release Limitation. The “do_local_only” command runs the pseudo-solis-wets algorithm, even if the solis-wets has been specified using “set_local sw1”. This applies only to“do_local_only”: the “ga_run” command will use whichever local search has been specified. (We recommend the pseudo-solis-wets for all local searches: “set psw1”).For more information about this release, see the Release 4.2.6 Notes on the AutoDock 4.2 download web page.SupportAutoDock is distributed, with full source code, free of charge. There are some caveats, however. Firstly, since we receive limited funding to support the academic community of users, we cannot guarantee response to queries on installation and use. While there is documentation, it may require at least some basic Unix abilities to install. If you still need help:(1) Ask your local system administrator or programming guru for help about compiling, using Unix/Linux, etc.(2) Consult the AutoDock web site, where you will find a wealth of information and a FAQ (Frequently Asked Questions) page with answers on AutoDock:/faqs-help(3) If you can’t find the answer to your problem, send your question to the AutoDock List (ADL) or the AutoDock Forum. There are many seasoned users of computational chemistry software and some AutoDock users who may already know the answer to your question. You can find out more about the ADL on the WWW at:/mailman/listinfo/autodockThe Forum is available on the WWW at:/forum(4) If you have tried (1), (2) and (3), and you still cannot find an answer, send email to goodsell@ for questions about AutoGrid or AutoDock; or to rhuey@ for questions about AutoDockTools.Thanks for your understanding!E-mail addressesArthur J. Olson, Ph.D. olson@David S. Goodsell, Ph.D. goodsell@Ruth Huey, Ph.D. rhuey@Fax: +1 (858) 784-2860The Scripps Research InstituteMolecular Graphics LaboratoryDepartment of Molecular Biology, Mail Drop MB-510550 North Torrey Pines RoadLa Jolla, CA 92037-1000, U.S.A.TheoryOverview of the Free Energy Scoring FunctionAutoDock 4.2 uses a semi-empirical free energy force field to evaluate conformations during docking simulations. The force field was parameterized using a large number of protein-inhibitor complexes for which both structure and inhibition constants, or K i , are known.The force field evaluates binding in two steps. The ligand and protein start in an unbound conformation. In the first step, the intramolecular energetics are estimated for the transition from these unbound states to the conformation of the ligand and protein in the bound state. The second step then evaluates the intermolecular energetics of combining the ligand and protein in their bound conformation.The force field includes six pair-wise evaluations (V) and an estimate of the conformational entropy lost upon binding (ΔS conf ):"G =(V bound L #L #V unbound L #L )+(V bound P #P #V unbound P #P )+(V bound P #L #V unbound P #L +"S conf )where L refers to the “ligand” and P refers to the “protein” in a ligand-protein docking calculation.Each of the pair-wise energetic terms includes evaluations for dispersion/repulsion, hydrogen bonding, electrostatics, and desolvation:The weighting constants W have been optimized to calibrate the empirical free energy based on a set of experimentally determined binding constants. The first term is a typical 6/12 potential for dispersion/repulsion interactions. The parameters are based on the Amber force field. The second term is a directional H-bond term based on a 10/12 potential. The parameters C and D are assigned to give a maximal well depth of 5 kcal/mol at 1.9Å for hydrogen bonds with oxygen and nitrogen, and a well depth of 1 kcal/mol at 2.5Å for hydrogen bonds with sulfur. The function E(t) provides directionality based on the angle t from ideal H-bonding geometry. The third term is a screened Coulomb potential for electrostatics. The final term is a desolvation potential based on the volume of atoms (V) that surround a given atom and shelter it from solvent, weighted by a solvation parameter (S) and an exponential term with distance-weighting factor σ=3.5Å. For a detailed presentation of these functions, please see our published reports, included in Appendix IV.By default, AutoGrid and AutoDock use a standard set of parameters and weights for the force field. The parameter_file keyword may be used, however, to use custom parameter files. The format of the parameter file is described in Appendix I.Several methods for estimating the contribution of the unbound state are implemented in AutoDock. In Autodock 3.0 and earlier versions, an assumption is made that the unbound formof the ligand (V L-Lbound in the equation above) is the same as the final docked conformation of theligand (V L-Lunbound ), yielding a final contribution V L-Lbound-V L-Lunbound= 0. AutoDock 4.1introduced a method of generating an extended form of the ligand to model the unbound state. Reports from users, however, revealed that the method caused significant problems with sterically-crowded molecules, and the default method was changed to the bound=unbound assumption in AutoDock 4.2 and later. In addition, there is an option for a user-defined unbound state.Viewing Grids in AutoDockTools. The protein is shown on the left in white bonds, and the grid box is shown on the right side. The blue contours surround areas in the box that are most favorable for binding of carbon atoms, and the red contours show areas that favor oxygen atoms. A ligand is shown inside the box at upper right.AutoDock Potentials. Examples of the four contributions to the AutoDock force field are shown in this graph. The dispersion/repulsion potential is for interaction between two carbon atoms. The hydrogen bond potential, which extends down to a minimum of about –2 kcal/mol, is shown for an oxygen-hydrogen interaction. The electrostatic potential is shown for interaction of two oppositely-charged atoms with a full atomic charge. The desolvation potential is shown for acarbon atom, with approximately 10 atoms displacing water at each distance.Using AutoDockSTEP 1: Preparing CoordinatesThe first step is to prepare the ligand and receptor coordinate files to include the information needed by AutoGrid and AutoDock. These coordinate files are created in an AutoDock-specific coordinate file format, termed PDBQT, which includes:1) Polar hydrogen atoms;2) Partial charges;3) Atom types;4) Information on the articulation of flexible molecules.For a typical docking calculation, you will create a file of coordinates for the receptor, and a separate file of coordinates for the ligand. In dockings where selected amino acids in the receptor are treated as flexible, you will create a third file that includes the coordinates of the atoms in the flexible portions of the receptor.In a typical study, the user prepares coordinate files in several steps using AutoDockTools. A detailed tutorial is available on the AutoDock WWW site to guide you through this process. The first two steps may be performed using the tools in the Edit menu of AutoDockTools, or with other molecular modeling programs:1) Add hydrogen atoms to the molecule.2) Add partial charges.Then, read the molecule into AutoDockTools using the Ligand (for the ligand) or Grid (for the receptor) menus, and create the PDBQT file:3) Delete non-polar hydrogens and merge their charges with the carbon atoms.4) Assign atom types, defining hydrogen bond acceptors and donors and aromatic and aliphatic carbon atoms.5) Choose a root atom that will act as the root for the torsion tree description of flexibility.6) Define rotatable bonds and build the torsion tree.There are a few things to keep in mind during this process:Be Critical. AutoDockTools and PMV currently use a modified version of Babel to add hydrogen atoms and assign charges. Unfortunately the method has trouble with some molecules. In those cases, hydrogen positions and charges may be assigned by the user’s preferred method, e.g. using Reduce, InsightII, Quanta, Sybyl, AMBER or CHARMm.Check Your Hydrogen Positions. In addition, most modeling systems add polar hydrogens in a default orientation, typically assuming each new torsion angle is 0° or 180°. Without some formof refinement, this can lead to spurious locations for hydrogen bonds. One option is to relax the hydrogens and perform a molecular mechanics minimization on the structure. Another is to use a program like “pol_h” which takes as input the default-added polar hydrogen structure, samples favorable locations for each movable proton, and selects the best position for each. This “intelligent” placement of movable polar hydrogens can be particularly important for tyrosines, serines and threonines.Watch for Disordered Residues. Care should be taken when the PDB file contains disordered residues, where alternate location indicators (column 17) have been assigned. For each such atom, the user must select only one of the possible alternate locations, making sure that a locally consistent set is chosen.Randomize Starting Coordinates When Redocking.In redocking experiments, where coordinates from a known protein-ligand complex are separated and docked, it is important to randomize the conformation of the ligand before it is docked. The techniques used to implement rotation of the ligand may be biased to prefer values of zero rotation, so to obtain an unbiased result, create a pdbqt file with the randomized ligand coordinates using the "Randomize" command in the ADT Ligand menu, then use this randomized coordinate file for docking experiments.Please note: coordinate preparation is the most important step in the docking simulation. The quality and accuracy of the docked results will only be as good as the quality of the starting coordinates. Be critical and carefully examine hydrogen positions, atom type assignments, partial charges, and articulation of the molecules to ensure that they make sense chemically. If you are using the Babel method within AutoDockTools to add charges and hydrogens, carefully check the results and make corrections if necessary—it often has trouble with molecules such as nucleotides.Creating PDBQT files in AutoDockToolsOverview of AutoDockToolsAutoDockTools is a set of commands implemented within the Python Molecular Viewer (PMV), providing a Graphical User Interface for AutoGrid and AutoDock. It is available at: /resources/adt.The AutoDockTools window has several parts:1) at the top are menus that access the general methods available in PMV. These include tools for reading and writing coordinates and images, for modifying coordinates, for selection, and for visualization.2) a row of buttons at the top allows quick access to the most popular tools of PMV3) below the buttons, there are a series of menus that access the AutoDock-specific tools of AutoDockTools.4) the 3-D molecular viewer is at center right.5) the Dashboard, located to the left of the viewer, allows quick selection, visualization, and coloring of molecules currently displayed in the viewer.Hydrogen Atoms and ChargesThe tools available in PMV are used to read coordinates in PDB and other formats, to add hydrogens, to select portions of the molecule, and to add partial charges. These functions are all accessed through menus at the top of the PMV window. A few useful commands will be described here—for more information on the many other functions of PMV, please see the PMV documentation.File>ReadMolecule: opens a browser that allows reading of PDB coordinate files.Edit>Delete:several options for deleting entire molecules, selected sets of atoms, or hydrogen atoms.Edit>Hydrogens>Add: options for adding all hydrogens or polar hydrogens using Babel. Edit>Charges: options for computing Gasteiger charges for arbitrary molecules using Babel. Ligand PDBQT Files – the “Ligand” MenuOnce ligand coordinates are created with hydrogen atoms and charges, they can be processed in the “Ligand” menu to create the ligand PDBQT file.Ligand>Input>QuickSetup:uses defaults to create the PDBQT file. PDB files can be read from the PMV viewer or from a file, and written directly to a new PDBQT file. Please note that hydrogen atoms will not be added.Ligand>Input>Open: reads coordinates from a file.Ligand>Input>Choose: chooses a molecule already read into PMV.Ligand>Input>OpenAsRigid: reads an existing PDBQT file and writes a new file with NO active torsions.Ligand>TorsionTree>ChooseRoot: manual selection of the root atom.Ligand>TorsionTree>DetectRoot:automatic detection of the root that provides the smallest largest subtree.Ligand>TorsionTree>ShowRootExpansion: for molecules with several atoms in the root, displays small spheres to show all atoms in the root, including atoms connected to each root atom by rigid bonds.Ligand>TorsionTree>ShowRootMarker: displays a sphere on the root atom.Ligand>TorsionTree>ChooseTorsions: launches an interactive browser for choosing rotatable bonds. Rotatable bonds are shown in green, and non-rotatable bonds are shown in red. Bonds that are potentially rotatable but treated as rigid, such as amide bonds and bonds that are made rigid by the user, are shown in magenta. Rotation of rotatable bonds may be switched on and off by clicking on the bonds.Ligand>TorsionTree>SetNumberOfTorsions: sets the number of rotatable bonds in the ligand by leaving the specified number of bonds as rotatable. The two options will choose the torsions that rotate either the fewest atoms in the ligand or the most atoms in the ligand. Ligand>AromaticCarbon>SetNames:clicking on atom positions will switch carbon atoms between aromatic and aliphatic. Aromatic carbons are shown in green. Click on the “Stop” button when finished.Ligand>AromaticCarbon>AromaticityCriterion: Sets the angular deviation from planarity that AutoDockTools uses to identify aromatic rings.Ligand>Output>RandomizethenSaveasPDBQT:randomizes the conformation of the ligand and writes the formatted PDBQT file.Ligand>Output:opens a browser to write the formatted PDBQT file.Rigid Receptor PDBQT Files – the “Grid” MenuFor docking calculations using rigid receptor coordinates, add the hydrogen atoms and charges in PMV, then read the coordinates into AutoDockTools using the “Grid” menu.Grid>Macromolecule>Open: launches a browser to open an existing PDBQT file.Grid>Macromolecule>Choose:chooses a molecule that has been previously read into PMV. It will merge non-polar hydrogen atoms and charges, assign aromatic carbons, and prompt the user to write a PDBQT file.Flexible Receptor PDBQT Files – the “FlexibleResidues” MenuFor docking calculations with selected flexibility in the receptor, add the hydrogen atoms and charges in PMV, then create two PDBQT files in AutoDockTools, one for the rigid portion of the receptor and one for the flexible atoms.FlexibleResidues>Input>OpenMacromolecule:launches a browser to open an existing PDBQT file.。

Altair Basic 3.X和4.X 88-PIO 引导加载器说明书

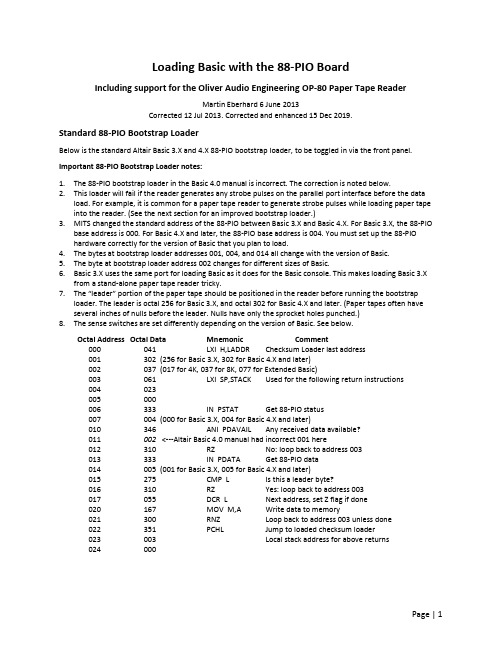

Loading Basic with the 88-PIO BoardIncluding support for the Oliver Audio Engineering OP-80 Paper Tape ReaderMartin Eberhard 6 June 2013Corrected 12 Jul 2013. Corrected and enhanced 15 Dec 2019.Standard 88-PIO Bootstrap LoaderBelow is the standard Altair Basic 3.X and 4.X 88-PIO bootstrap loader, to be toggled in via the front panel. Important 88-PIO Bootstrap Loader notes:1.The 88-PIO bootstrap loader in the Basic 4.0 manual is incorrect. The correction is noted below.2.This loader will fail if the reader generates any strobe pulses on the parallel port interface before the dataload. For example, it is common for a paper tape reader to generate strobe pulses while loading paper tape into the reader. (See the next section for an improved bootstrap loader.)3.MITS changed the standard address of the 88-PIO between Basic 3.X and Basic4.X. For Basic 3.X, the 88-PIObase address is 000. For Basic 4.X and later, the 88-PIO base address is 004. You must set up the 88-PIO hardware correctly for the version of Basic that you plan to load.4.The bytes at bootstrap loader addresses 001, 004, and 014 all change with the version of Basic.5.The byte at bootstrap loader address 002 changes for different sizes of Basic.6.Basic 3.X uses the same port for loading Basic as it does for the Basic console. This makes loading Basic 3.Xfrom a stand-alone paper tape reader tricky.7.The “leader” portion of the paper tape should be positioned in the reader before running the bootstraploader. The leader is octal 256 for Basic 3.X, and octal 302 for Basic 4.X and later. (Paper tapes often have several inches of nulls before the leader. Nulls have only the sprocket holes punched.)8.The sense switches are set differently depending on the version of Basic. See below.Octal Address Octal Data Mnemonic Comment000 041 LXI H,LADDR Checksum Loader last address001 302 (256 for Basic 3.X, 302 for Basic 4.X and later)002 037 (017 for 4K, 037 for 8K, 077 for Extended Basic)003 061 LXI SP,STACK Used for the following return instructions004 023005 000006 333 IN PSTAT Get 88-PIO status007 004 (000 for Basic 3.X, 004 for Basic 4.X and later)010 346 ANI PDAVAIL Any received data available?011 002 <---Altair Basic 4.0 manual had incorrect 001 here012 310 RZ No: loop back to address 003013 333 IN PDATA Get 88-PIO data014 005 (001 for Basic 3.X, 005 for Basic 4.X and later)015 275 CMP L Is this a leader byte?016 310 RZ Yes: loop back to address 003017 055 DCR L Next address, set Z flag if done020 167 MOV M,A Write data to memory021 300 RNZ Loop back to address 003 unless done022 351 PCHL Jump to loaded checksum loader023 003 Local stack address for above returns024 000Improved 88-PIO Bootstrap LoaderThe 88-PIO will latch and hold its input-port data until the input port is read by software. It is common for the 88-PIO’s data latch to contain a garbage data byte that was generated, for example, by loading paper tape into the reader. (It is nearly impossible not to create a garbage byte while setting up an OP-80 paper tape reader.)If the 88-PIO input port does contain a garbage byte at the beginning of the load, then the load will fail – since the MITS bootstrap loader will interpret the garbage byte as the first byte of the paper tape data.The simple solution (implemented in the following bootstrap loader) is for the bootstrap loader to perform one read of the 88-PIO data port during its initialization phase, to clear out any potential garbage data. This improvement should work for any device that is attached to the 88-PIO.Important notes for this modified 88-PIO Bootstrap Loader1.MITS changed the standard address of the 88-PIO between Basic 3.X and Basic 4.X. For Basic 3.X, the 88-PIObase address is 000. For Basic 4.X and later, the 88-PIO base address is 004. You must set up the 88-PIO hardware correctly for the version of Basic that you plan to load.2.The bytes at bootstrap loader addresses 001, 004, 011 and 016 all change with the version of Basic.3.The byte at bootstrap loader address 002 changes for different sizes of Basic.4.Basic 3.X uses the same port for loading Basic as it does for the Basic console. This makes loading Basic 3.Xfrom a stand-alone paper tape reader tricky.5.The “leader” portion of the paper tape should be positioned in the reader before running the bootstraploader. The leader is octal 256 for Basic 3.X, and octal 302 for Basic 4.X and later. (Paper tapes often have several inches of nulls before the leader. Nulls have only the sprocket holes punched.) For an OP-80 reader, position the tape such that the optical sensors are blocked by paper tape (between holes in the leader) before running the bootstrap loader.6.Set the sense switches for loading from the 88-PIO, before running the bootstrap loader. See below.Octal Address Octal Data Mnemonic Comment000 041 LXI H,LADDR Checksum Loader last address001 302 (256 for Basic 3.X, 302 for Basic 4.X and later)002 037 (017 for 4K, 037 for 8K, 077 for Extended Basic)003 333 IN PDATA Read 88-PIO data to clear OP-80004 005 (001 for Basic 3.X, 005 for Basic 4.X and later)005 061 LXI SP,STACK Used for the following return instructions006 025007 000010 333 IN PSTAT Get 88-PIO status011 004 (000 for Basic 3.X, 004 for Basic 4.X and later)012 346 ANI PDAVAIL Any received data available?013 002014 310 RZ No: loop back to address 003015 333 IN PDATA Get 88-PIO data016 005 (001 for Basic 3.X, 005 for Basic 4.X and later)017 275 CMP L Is this a leader byte?020 310 RZ Yes: loop back to address 003021 055 DCR L Next address, set Z flag if done022 167 MOV M,A Write data to memory023 300 RNZ Loop back to address 003 unless done024 351 PCHL Jump to loaded checksum loader025 003 Local stack address for above returns026 000Basic 3.X Sense Switch SettingsThe Basic 3.X loader uses the same port for loading Basic and for the Console.Load & Console A15 A14 A13 A12 A11 A10 A9 A888-SIOA,B,C (not rev 0) 0 0 0 0 0 0 0 088-SIOA,B,C (rev 0) 0 1 0 0 0 0 0 088-PIO 0 0 1 0 0 0 0 088-4PIO 0 0 0 1 0 0 0 088-2SIO-0 (1 stop bit) 0 0 0 0 1 1 0 088-2SIO-0(2 stop bits) 0 0 0 0 1 0 0 0Basic 4.X Sense Switch SettingsThe Basic 4.X loader makes a distinction between the Load Source and the Console Device, allowing you to load from one device, and use another for the Basic console.Load Source A11 A10 A9 A8 Console Device A15 A14 A13 A12 88-2SIO-0 (2 stop bits) 0 0 0 0 88-2SIO-0 (2 stop bits) 0 0 0 0 88-2SIO-0 (1 stop bit) 0 0 0 1 88-2SIO-0 (1 stop bit) 0 0 0 1 88-SIO 0 0 1 0 88-SIO 0 0 1 0 88-ACR 0 0 1 1 (not allowed) 0 0 1 1 88-4PIO 0 1 0 0 88-4PIO 0 1 0 0 88-PIO 0 1 0 1 88-PIO 0 1 0 1 HSR 0 1 1 0 (not allowed) 0 1 1 0Basic 4.X Loader Error MessagesError Code MeaningC Checksum error. Bad tape data.M Memory error. Data won’t store properly.O Overlay error. Attempt to overwrite checksum loader.I Invalid Load source. Illegal sense -switch setting.Basic 4.X Initialization Dialog4K BasicMEMORY SIZE? (<RETURN> to use all memory. Basic uses 3.4K.)TERMINAL WIDTH? (<RETURN> for 72 columns)SIN? (Y saves SIN, SQR and RND. N deletes SIN and brings next question.)SQR? (Y saves SQR and RND. N deletes SQR and brings next question.)RND? (Y saves RND, N deletes RND.)8K BasicMEMORY SIZE? (<RETURN> to use all memory. Basic uses 6.2K.)TERMINAL WIDTH? (<RETURN> for 72 columns)WANT SIN-COS-TAN-ATN? (Y or N)Extended BasicMEMORY SIZE? (<RETURN> to use all memory. Basic uses 14.6K.)LINEPRINTER? (O for 80LP, C for C700, Q for Q70)WANT SIN-COS-TAN-ATN? (Y or N)Connecting the OP-80 to the 88-PIOThe OP-80 has just one configuration jumper, that selects either active-high or active-low acknowledge. This jumper should be set for Active low acknowledge, since the BIN output from the 88-PIO is active low.Connect the OP-80 to the 88-PIO via a DB25 connector set on the back of the Altair, as follows. The wire colors for the 88-PIO are just suggestions. The DB25 pinout is compatible with the Altair 88-4PIO. The wire colors for the OP-80 are those found on its rainbow ribbon cable.88-PIO DB25 OP-80 Function 8212 function Pin Wire color Pin Wire Color Pin Function N/C 1 Orange 7 RDASBI H STB 19 Orange/black 2 Brown 6 /RDABIN H /INT 20 White 3 White 5 /ACKDI0 H DI0 11 Brown 4 Brown 1 D0DI1 H DI1 12 Red 5 Red 16 D1Ground Note 1Green/black 6 Green 8 GroundVcc Note 1 Blue/black 7 Blue 9 +5V89DO6 G DO6 7 Grey/black 10DO7 G DO7 8 Pink 11SBO G STB 9 Light Blue 12BO G /INT 10 Light Green 13DI2 H DI2 13 Orange 14 Orange 2 D2DI3 H DI3 14 Yellow 15 Yellow 15 D3DI4 H DI4 15 Green 16 Green 3 D4DI5 H DI5 16 Blue 17 Blue 14 D5DI6 H DI6 17 Violet 18 Violet 4 D6DI7 H DI7 18 Grey 19 Grey 13 D7DO0 G DO0 1 Yellow/black 20 Yellow 10 S1DO1 G DO1 2 Red/black 21 Red 11 S2DO2 G DO2 3 Black 22 Black 12 SPAREDO3 G DO3 4 Brown/black 23DO4 G DO4 5 Violet/black 24DO5 G DO5 6 White/black 25Note 1: The 88-PIO (amazingly) has no ground pin on its interface. (See page 12 of the 88-PIO manual.) Because the OP-80 is powered by the interface, it is necessary to provide both ground and regulated +5V tothe DB25, from the 88-PIO. You can do this (without damaging the 88-PIO board) by tack-soldering a 3-pin connector onto the back of the 88-PIO board, at the top, where the +5V trace is parallel to the groundtrace. (Use a 3-pin connector so that you can key it, to prevent connecting it the wrong way.) Then put a mating connector on the wires from DB25 pins 06 and 08, and plug this connector into the one that you installed on the 88-PIO.•Since Basic 3.X uses the same port for loading Basic as it does for the console, the OP-80 (or any stand-alone paper tape reader) is not practical for loading Basic 3.X. However, the OP-80 works great for loading Basic 4.X. •Pull the paper tape through the OP-80 at about 2 feet per second. A crank-driven paper tape winder is an excellent addition to the OP-80.。

Flex System x440 Compute Node(7917)产品指南(已撤销产品)说明书