PT4302中文规格书

正宗原版430说明书

雷霆、航科410/420/430是TVRO界的一个亮点,它们主板相同,但外接的卡座数量分别为1、2、3个,其中430(3卡座)可以解开三个加密系统,用遥控器可以随时切换,已成为普遍使用的机型,目前产地很多,但各种牌号430机器所配的说明书内容简单,对使用者帮助不大。

机器内的中文菜单虽说非常详尽,但欧洲式的菜单对于初次使用的人来说,还不是很容易掌握。

要过年了,瘦子抽空编个详细的说明书,作为给广大星友的节日礼物。

为避免有做广告之嫌,用XSA T430来表示所有牌号的430机器。

----这类机器的前面版基本都一样,后背板的接口也大同小异,但接口位置有所差异。

通常背板都配有电源开关,打开后机器处于待机状态,需要再按动面板上的电源键或遥控器上的电源键来进入工作状态。

用的较多的机器系统为南瓜系统和V+I双系统这种,通过按动遥控器上的Format键来转换不同的接收系统。

机器前后共三个卡座,后面的卡座为I系统使用,前面左右两个为N系统和V系统使用。

具体前面那个卡座是N系统用的,因厂家而异,试试就知道了。

初次使用该机器要注意,在南瓜系统下只能接收146、88、75等星上的加密节目,76.5、110.5等星上的加密节目是需要在V+I系统下设置接收的。

如果接收免费节目不受此限制。

通过按动遥控器上的Menu键,可以进入设置菜单。

如果有密码的话,默认为1234。

如果不行,可输入6931通用密码进入。

设置前,要安装好接收天线和高频头,用同轴线将高频头与接收机正确连接。

如果多面天线的话,需要连接22K脉冲转换开关或四切一DiSEqC开关。

用随机配的音视频线与电视机连接,打开电视机和接收机电源,使其都处于工作状态。

设置中主要使用上、下、左、右四个方向键来选择菜单项目和删除数字,用OK键来确定,说明中不再重复。

下面根据接收机安装操作的顺序,来介绍菜单中各项的设置。

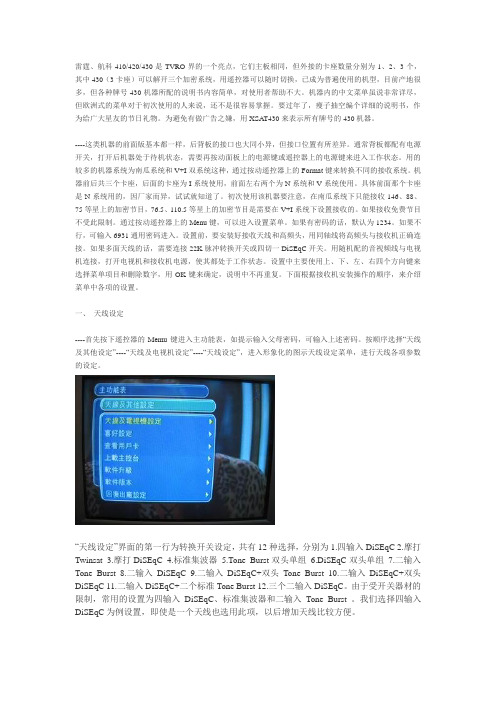

一、天线设定----首先按下遥控器的Memu键进入主功能表,如提示输入父母密码,可输入上述密码。

福禄克Power Log 430-II用户手册

福禄克(Fluke)公司 Fluke Power Log Software 许可协议 您只要通过任何一种方式使用了本产品即表示您同意接受下列条款和条件。 Fluke 公司 (Fluke) 授予您在单个个人计算机或工作站(节点)上使用 Fluke Power Log 文档编制软件(产品)的非 独有权。您也可以享有在多节点上使用本产品的非独有权,前提条件是您已经从 Fluke 公司获得了多使用许 可权且使用本产品的节点数量不超过使用许可费用所含盖的节点数量。此使用授权不包括复制、修改、出租、 销售、转让或分销产品的权利、或其中的部分权利。您不得对产品进行逆向工程设计、反编译或拆分。 Fluke 保证,从接受许可之日起的 90 天内,产品在规定的环境下运行,大体上符合产品附带的书面资料上所 规定的指标。Fluke 不保证不出现任何下载错误,或产品不出现错误,或不间断运行。 FLUKE 不负责任何其它保修,无论这些保修是明确表达的还是暗示的,但不限于关于软件和附带书面资料 的,针对特定用途的可销售性和适应性暗示的保证内容。任何情况下 Fluke 不承担任何由于使用本产品或不 会使用本产品而造成的损害赔偿,即使 Fluke 已被告知可能会出现这些损害(包括但不局限于 间接、继发的或 偶然的损害、业务利润损失、业务中断、业务信息的丢失、或其它金钱方面的损失)。

Power Log

PC Application Software

用户பைடு நூலகம்册

May 2007 Rev. 3, 3/13 (Simplified Chinese) © 2007-2013 Fluke Corporation. All rights reserved. Specifications are subject to change without notice. All product names are trademarks of their respective companies.

4302-52;4302-00;中文规格书,Datasheet资料

Page 1 of 11Document No. 70-0056-04 │©2003-2008 Peregrine Semiconductor Corp. All rights reserved.Figure 1. Functional Schematic DiagramRF OutputTable 1. Electrical Specifications @ +25°C, V DD = 3.0 VParameter Test Conditions Frequency Minimum Typical Maximum UnitsOperation Frequency DC 4000 MHz Insertion Loss 2 DC - 2.2 GHz -1.51.75dB Attenuation Accuracy Any Bit or Bit CombinationDC ≤ 1.0 GHz 1.0 < 2.2 GHz - -±(0.10 + 3% of atten setting)±(0.15 + 5% of atten setting) dB dB 1 dB Compression 31 MHz - 2.2 GHz 30 34 - dBm Input IP31,2 Two-tone inputs+18 dBm1 MHz - 2.2 GHz - 52 - dBm Return LossDC - 2.2 GHz15 20 - dB Switching Speed50% control to 0.5 dBof final value--1µsNotes: 1. Device Linearity will begin to degrade below 1 Mhz2. See Max input rating in Table 3 & Figures on Pages 2 to 4 for data across frequency.3. Note Absolute Maximum in Table 3. Figure 2. Package Type 4x4 mm 20-Lead QFNPE4302Product Specification ArrayPage 2 of 11Product SpecificationPE4302Page 3 of 11Document No. 70-0056-04 │©2003-2008 Peregrine Semiconductor Corp. All rights reserved.-1-0.8-0.6-0.4-0.20.20.4510152025303540A t t e n u a t i o n E r r o r (dB )Attenuation Setting (dB)-1.5-1-0.50.5510152025303540A t t e n u a t i o n E r r o r (dB )Attenuation Setting (dB)-10-8-6-4-225001000150020002500300035004000A t t e n u a t i o n E r r o r (dB )RF Frequency (MHz)-0.6-0.4-0.20.20.40.6510152025303540A t t e n u a t i o n E r r o r (dB )Attenuation Setting (dB)Figure 8. Attenuation Error Vs. Attenuation SettingFigure 10. Attenuation Error Vs. AttenuationSettingFigure 9. Attenuation Error Vs. AttenuationSettingFigure 7. Attenuation Error Vs. FrequencyTypical Performance Data @ 25°C, V DD = 3.0 V Note: Positive attenuation error indicates higher attenuation than target valuePE4302Product Specification ArrayPage 4 of 11Product SpecificationPE4302Page 5 of 11Document No. 70-0056-04 │©2003-2008 Peregrine Semiconductor Corp. All rights reserved.Table 2. Pin DescriptionsElectrostatic Discharge (ESD) PrecautionsWhen handling this UltraCMOS™ device, observe the same precautions that you would use with other ESD-sensitive devices. Although this device contains circuitry to protect it from damage due to ESD,precautions should be taken to avoid exceeding the rate specified in Table 3.Exposed Solder Pad ConnectionThe exposed solder pad on the bottom of the package must be grounded for proper device operation. Note 1: Both RF ports must be held at 0 V DC or DC blocked with anexternal series capacitor.2: Latch Enable (LE) has an internal 100 k Ω resistor to V DD. 3: Connect pin 12 to GND to enable internal negative voltage generator. Connect pin 12 to V SS (-VDD) to bypass and disable internal negative voltage generator. 4. Place a 10 k Ω resistor in series, as close to pin as possible to avoid frequency resonance. Figure 14. Pin Configuration (Top View)V D DP U P 1P U P 2V D DG N DC16RF1Data Clock LEGNDVss/GND P/S RF2C8C 4C 2G N DC 1C 0.5Pin No.Pin NameDescription1 C16 Attenuation control bit, 16dB (Note 4).2 RF1 RF port (Note 1).3 Data Serial interface data input (Note 4).4 Clock Serial interface clock input. 5LELatch Enable input (Note 2). 6 V DD Power supply pin.7 PUP1 Power-up selection bit, MSB. 8PUP2Power-up selection bit, LSB. 9 V DDPower supply pin.10 GND Ground connection. 11 GND Ground connection. 12 V ss /GND Negative supply voltage or GNDconnection(Note 3) 13 P/S Parallel/Serial mode select. 14 RF2 RF port (Note 1).15 C8 Attenuation control bit, 8 dB. 16 C4 Attenuation control bit, 4 dB. 17C2Attenuation control bit, 2 dB.18 GND Ground connection. 19 C1 Attenuation control bit, 1 dB. 20 C0.5 Attenuation control bit, 0.5 dB. PaddleGNDGround for proper operationLatch-Up AvoidanceUnlike conventional CMOS devices, UltraCMOS™ de-vices are immune to latch-up.Switching FrequencyThe PE4302 has a maximum 25 kHz switching rate. Resistor on Pin 1 & 3A 10 k Ω resistor on the inputs to Pin 1 & 3 (see Figure 16) will eliminate package resonance between the RF input pin and the two digital inputs. Specifiedattenuation error versus frequency performance is dependent upon this condition.Table 3. Absolute Maximum RatingsTable 4. Operating RangesSymbol Parameter/Conditions Min Max UnitsV DD Power supply voltage -0.3 4.0 V V IVoltage on any DC input -0.3 V DD + 0.3 V T ST Storage temperature range -65 150 °C P IN Input power (50Ω) +30 dBm V ESDESD voltage (Human BodyModel)500VParameter Min Typ Max UnitsV DD Power Supply Voltage2.73.0 3.3 V I DD Power Supply Current100 µA Digital Input High 0.7xV DDVDigital Input Low 0.3xV DD V Digital Input Leakage1 µA Input Power +24 dBm Temperature range-4085°CExceeding absolute maximum ratings may cause per-manent damage. Operation should be restricted to the limits in the Operating Ranges table. Operation be-tween operating range maximum and absolute maxi-mum for extended periods may reduce reliability.PE4302Product Specification ArrayPage 6 of 11Product SpecificationPE4302Page 7 of 11Document No. 70-0056-04 │©2003-2008 Peregrine Semiconductor Corp. All rights reserved.Evaluation KitThe Digital Attenuator Evaluation Kit board was designed to ease customer evaluation of the PE4302 Digital Step Attenuator.J9 is used in conjunction with the supplied DC cable to supply VDD, GND, and –VDD. If use of the internal negative voltage generator is desired, then connect –VDD (Black banana plug) toground. If an external –VDD is desired, then apply -3V.J1 should be connected to the parallel port of a PC with the supplied ribbon cable. The evaluation software is written to operate the DSA in serial mode, so Switch 7 (P/S) on the DIP switch SW1 should be ON with all other switches off. Using the software, enable or disable each attenuation setting to the desired combined attenuation. The software automatically programs the DSA each time an attenuation state is enabled or disabled.To evaluate the Power Up options, first disconnect the parallel ribbon cable from the evaluation board. The parallel cable must be removed to prevent the PC parallel port from biasing the control pins.During power up with P/S=1 high and LE=0 or P/S=0 low and LE=1, the default power-up signal attenuation is set to the value present on the six control bits on the six parallel data inputs (C0.5 to C16). This allows any one of the 64 attenuation settings to be specified as the power-up state.During power up with P/S=0 high and LE=0, the control bits are automatically set to one of four possible values presented through the PUPinterface. These four values are selected by the two power-up control bits, PUP1 and PUP2, as shown in the Table 6.Resistor on Pin 1 & 3 A 10 k Ω resistor on the inputs to Pin 1 & 3 (Figure 16) will eliminate package resonance between the RF input pin and the two digital inputs. Specified attenuation error versus frequency performance is dependent upon this condition.Figure 15. Evaluation Board LayoutFigure 16. Evaluation Board SchematicNote: Resistors on pins 1 and 3 are required to avoid package resonance and meet error specifications over frequency.Peregrine Specification 101/0112Peregrine Specification 102/0144PE4302Product Specification ArrayPage 8 of 11Product SpecificationPE4302Page 9 of 11Document No. 70-0056-04 │ ©2003-2008 Peregrine Semiconductor Corp. All rights reserved.Figure 19. Package DrawingDETAIL A0.020.20 R E FTERMINAL PADS.801. Dimension applies to metallized terminal and is measured between 0.25 and 0.30 from terminal tip.2. Coplanarity applies to the exposed heat sink slug as well as the terminals.3. Dimensions are in millimeters.Product SpecificationPE4302Page 10 of 11Table 10. Ordering InformationOrder CodePart Marking DescriptionPackage 4302-00 PE4302-EK PE4302-20MLP 4x4mm-EKEvaluation Kit4302-51 4302PE4302G-20MLP 4x4mm-75A Green 20-lead 4x4mm QFN4302-52 4302 PE4302G-20MLP 4x4mm-3000C Green 20-lead 4x4mm QFN分销商库存信息:PSC4302-524302-00。

pt7c4302时钟芯片规格书

PT7C4302时钟芯片规格书一、产品概述1.1 产品名称:PT7C4302时钟芯片1.2 产品型号:PT7C43021.3 产品功能:PT7C4302是一款宽温工作范围,低成本,实时时钟/日历集成电路(IC)。

它具有秒,分,时,日,月,年,星期和12/24小时模式的实时时钟。

1.4 适用范围:PT7C4302广泛应用于计算机,汽车电子,工业控制系统和家用电器等领域。

二、产品特点2.1 宽温工作范围:-40°C至+85°C2.2 低功耗设计:工作电流仅为1.5μA(最大)2.3 高精度:时钟精度为±2分钟/年(25°C下)2.4 可编程:支持12小时/24小时模式切换,支持闰年计算2.5 封装形式:采用8引脚SOIC(小外形集成线路)封装2.6 通信接口:SPI接口,便于与微处理器或微控制器连接三、产品功能描述3.1 实时时钟功能:PT7C4302在低功耗模式下持续正常工作,能够提供准确的实时时钟功能,包括秒,分,小时,日,月,年和星期等显示。

3.2 闰年计算:PT7C4302内置闰年计算功能,可自动判断闰年和平年。

3.3 电源监控:PT7C4302内置电源监控电路,能够实时监测供电电压,确保时钟芯片在电压不稳定的情况下仍然能够正常工作。

四、产品应用4.1 计算机:PT7C4302可以作为计算机主板的实时时钟芯片,提供精准的时间信息,并支持系统待机和节能模式。

4.2 汽车电子:PT7C4302可用于汽车电子系统中,提供车辆的精准时间信息,并支持车载设备的定时控制功能。

4.3 工业控制系统:PT7C4302适用于工业控制系统中的时间同步和定时功能,确保生产流程的准确控制。

4.4 家用电器:PT7C4302可作为家用电器中的时间显示和定时控制芯片,如微波炉、洗衣机等设备中的时钟显示和定时启动功能。

五、产品性能指标5.1 工作电压范围:2.7V至5.5V5.2 工作温度范围:-40°C至+85°C5.3 存储温度范围:-55°C至+125°C5.4 封装形式:8引脚SOIC封装5.5 通信接口:SPI接口5.6 尺寸:5mm×6mm×1.5mm六、产品包装及贮存6.1 包装形式:PT7C4302采用卷装或者盒装形式,符合RoHS环保要求。

监控宝430 522用户手册说明书

• OSD (On Screen Display) Menu • OSD menu is provided to display the status of camera and to configure the functions interactively. • The information such as Camera ID, Pan/Tilt Angle, Direction, Alarm Input and Preset is displayed on screen.

AMP04FSZ,AMP04FPZ,AMP04EPZ,AMP04FSZ-RL,AMP04FSZ-R7,AMP04FS-REEL7,AMP04ESZ-R7, 规格书,Datasheet 资料

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site:

Fax: 781/326-8703

© Analog Devices, Inc., 2000

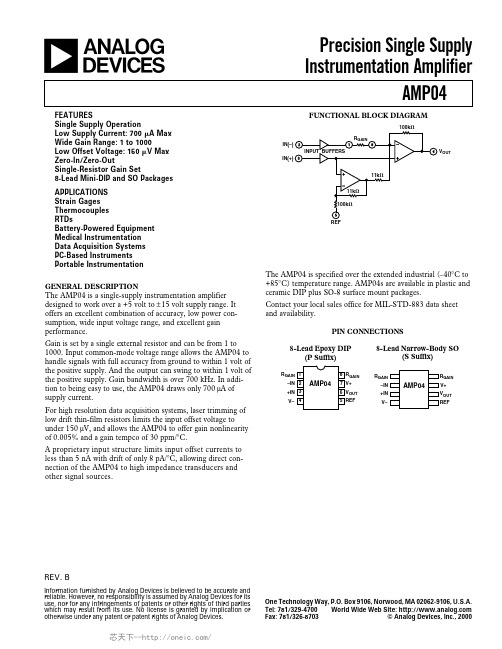

For high resolution data acquisition systems, laser trimming of low drift thin-film resistors limits the input offset voltage to under 150 µV, and allows the AMP04 to offer gain nonlinearity of 0.005% and a gain tempco of 30 ppm/°C.

1000 1 0.005 0.015 0.025 30

0.75 %

1.0 %

0.75

%

1000 V/V

%

%

%

50

ppm/°C

OUTPUT Output Voltage Swing High

Output Voltage Swing Low Output Current Limit

VOH

RL = 2 kΩ

Contact your local sales office for MIL-STD-883 data sheet and availability.

PIN CONNECTIONS

8-Lead Epoxy DIP (P Suffix)

8-Lead Narrow-Body SO (S Suffix)

25

PT7C4302资料

元器件交易网Data Sheet PT7C4302 Real-time Clock Module (3-wire Interface) DescriptionThe PT7C4302 serial real-time clock is a lowpower clock/calendar with a programmable square-wave output and 31 bytes of nonvolatile RAM. Address and data are transferred serially via a 3wire bus. The clock/calendar provides seconds, minutes, hours, day, date, month, and year information. The date at the end of the month is automatically adjusted for months with fewer than 31 days, including corrections for leap year. The clock operates in either the 24-hour or 12-hour format with AM/PM indicator. Table 1 shows the basic functions of PT7C4302. More details are shown in section: overview of functions.|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||Features• • Using external 32.768kHz quartz crystal Real-time clock (RTC) counts seconds, minutes hours, date of the month, month, day of the week, and year with leap-year compensation valid up to 2099 • • • • • • • • • • 31-byte, nonvolatile (NV) RAM for data storage 2.0V to 5.5V full operation Uses less than 300nA at 2.0V Simple 3-wire interface Serial I/O for minimum pin count Burst mode for reading/writing successive addresses in clock/RAM TTL-compatible (VCC = 5V) Optional industrial temperature range: -40°C to +85°C Battery backup Trickle charger on chip for rechargeable energy source backupTable 1 Basic functions of PT7C4302 Item Function Source: Crystal: 32.768kHz 1 Oscillator Oscillator enable/disable Oscillator fail detect Time display 2 Time 12-hour 24-hourOrdering InformationPart Number PT7C4302P PT7C4302W Package 8-Pin DIP 8-Pin SOICNote: Lead free package is available by adding “E” after each part number. For example: PT7C4302PE.PT7C4302 √ √ √ √ √ √ √ 31×8 √ √3Communicat ionCentury bit Time count chain enable/disable 2-wire I2C bus 3-wire bus Burst mode Write protection External clock test mode Power-on reset override4 5 6 7Control RAM Charger Battery backupPT0225(11/05) 1Ver: 0元器件交易网Data Sheet PT7C4302 Real-time Clock Module (3-wire Interface)|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||Function BlockPT7C4302X132.768 kHzCDOSCCounter ChainTime Counter(Sec,Min,Hour,Day,Date,Month,Year)31 x 8 RAMX2CGAddress Decoder Power ManagerAddress Register I /O Interface (3-wires)SCLK RST I/OVCC2 VCC1Shift RegistersRecommended Layout for CrystalPT7C4302 PT7C4307X132.768kHz CrystalX2Local Ground plane Layer 2 Guard Ring (connect to gound)Crystal SpecificationsParameter Nominal Frequency Series Resistance Load Capacitance Symbol fO ESR CL Min Typ 32.768 6 Max 45 Unit kHz kΩ pFThe crystal, traces and crystal input pins should be isolated from RF generating signals.PT0225(11/05) 2Ver: 0元器件交易网Data Sheet PT7C4302 Real-time Clock Module (3-wire Interface)|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||Pin ConfigurationPT7C43021VCC2 X1 X2 GNDVCC1 SCLK I/O RST8273645DIP-8 SOIC-8Pin DescriptionPin no. 1 2 3 Pin VCC2 X1 X2 Type P I O Description Primary power. When VCC2 is greater than VCC1 + 0.2V, VCC2 will power the PT7C4302. Oscillator Circuit Input. Together with X2, 32.768kHz crystal is connected between them. Oscillator Circuit Output. Together with X1, 32.768kHz crystal is connected between them.4GND RST I/O SCLKPGround. Reset. The reset signal must be asserted high during a read or a write. This pin has a 40kΩ internal pull-down resistor. Serial Data Input/Output. I/O is the input/output pin for the 3-wire serial interface. The pin has a 40kΩ internal pull-down resistor. Serial Clock Input. SCLK is used to synchronize data movement on the 3-wire serial interface. The pin has a 40kΩ internal pull-down resistor. Backup power. When VCC2 is less than VCC1, VCC1 will power the PT7C4302. VCC1 provides low-power operation in single supply and battery-operated systems as well as low power battery backup. In systems using the trickle charger, the rechargeable energy source is connected to this pin. UL recognized to ensure against reverse charging current when used in conjunction with a lithium battery.5 6 7I I/O I8VCC1PPT0225(11/05) 3Ver: 0元器件交易网Data Sheet PT7C4302 Real-time Clock Module (3-wire Interface)|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||Function DescriptionOverview of Functions1.Clock functionCPU can read or write data including the year (last two digits), month, date, day, hour, minute, and second. Any (two-digit) year that is a multiple of 4 is treated as a leap year and calculated automatically as such until the year 2099.2.Interface with CPUSimple 3-wire interface.3.Oscillator enable/disableOscillator can be enabled or disable by /EOSC bit. But time count chain does not shut down when the bit is logic 1.4.Charger functionThe function is controlled by trickle charge register. Customer can select the charge current by select the number of diode and resistor value through the register. For example: Assume that a system power supply of 5V is applied to VCC2 and a super cap is connected to VCC1. Also assume that the trickle charger has been enabled with one diode and resistor R1 between VCC2 and VCC1. The maximum current IMAX would, therefore, be calculated as follows: IMAX = (5.0V - diode drop)/R1 _ (5.0V - 0.7V) / 2kΩ _ 2.2mA As the super cap charges, the voltage drop between VCC1 and VCC2 will decrease and, therefore, the charge current will decrease.PT0225(11/05) 4Ver: 0元器件交易网Data Sheet PT7C4302 Real-time Clock Module (3-wire Interface)|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||Registers1. Allocation of registers Function Seconds (00-59) Minutes (00-59) Hours (00-23 / 01-12) Dates (01-31) Months (01-12) Days of the week (01-07) Years (00-99) Control Trickle charger Clock burst*7 RAM*9 RAM burst*8 Register definition Bit 7 /EOSC*2 0 12, /24 0 0 0 Y80 WP*3 TCS*4 Bit 6 S40 M40 0 0 0 0 Y40 0 TCS Bit 5 S20 M20 H20 or P /A D20 0 0 Y20 0 TCS Bit 4 S10 M10 H10 D10 MO10 0 Y10 0 TCS Bit 3 S8 M8 H8 D8 MO8 0 Y8 0 DS*5 Bit 2 S4 M4 H4 D4 MO4 W4 Y4 0 DS Bit 1 S2 M2 H2 D2 MO2 W2 Y2 0 RS*6 Bit 0 S1 M1 H1 D1 MO1 W1 Y1 0 RS -Addr. (hex) *1 00 01 02 03 04 05 06 07 08 1F 20~3E 3FCaution points: *1. PT7C4302 uses 5 bits for address. It’s address byte consists of 1 + RAM/Clock select bit +5-bit addr. + Read/Write select bit. *2. Oscillator Enable bit. When this bit is set to 1, oscillator is stopped but time count chain is still active. *3. WP: Write Protect bit. WP bit should be cleared before attempting to write to the device. *4. TCS: Trickle Charger Select. *5. DS: Diode Select. *6. RS: Resistor Select. *7. Clock burst register address is used as clock/calendar burst mode operation address for consecutively read/write 0~7H registers. Clock/calendar burst mode operation can continuously read 0H to maximum 7H registers in order; write 0~7H registers in order. Less or larger than 8 bytes in clock burst write mode are ignored. *8. RAM burst register address is used as RAM burst mode operation address for consecutively read/write 20~3EH RAM. Less than 31 bytes in RAM burst read/write mode are valid. *9. PT7C4302 has 31×8 static RAM for customer use. It is volatile RAM. *10. All bits marked with "0" are read-only bits. Their value when read is always "0". All bits marked with "-" are customer using space. PT0225(11/05) 5 Ver: 0元器件交易网Data Sheet PT7C4302 Real-time Clock Module (3-wire Interface)|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||2.Control and status registerAddr. (hex) 07Description Control (default)D7 WP 0D6 0 0D5 0 0D4 0 0D3 0 0D2 0 0D1 0 0D0 0 0WP: Write Protect bit. WP Read / Write Data 0 1 Write operation is enabled. Prevent a write operation to any other register. Description Default3.Time CounterTime digit display (in BCD code): • Second digits: Range from 00 to 59 and carried to minute digits when incremented from 59 to 00. • Minute digits: Range from 00 to 59 and carried to hour digits when incremented from 59 to 00. • Hour digits: See description on the /12, 24 bit. Carried to day and day-of-the-week digits when incremented from 11 p.m. to 12 a.m. or 23 to 00. Addr. (hex) 00 01 02 Description Seconds (default) Minutes (default) Hours (default) D7 /EOSC* 1 0 0 12, /24 Undefined D6 D5 D4 D3 D2 D1 D0S40 S20 S10 S8 S4 S2 S1 Undefined Undefined Undefined Undefined Undefined Undefined Undefined M40 M20 M10 M8 M4 M2 M1 Undefined Undefined Undefined Undefined Undefined Undefined Undefined 0 0 H20 or P,/A H10 H8 H4 H2 H1 Undefined Undefined Undefined Undefined Undefined Undefined* Note: /EOSC bit must be written into 0 to start the time count.PT0225(11/05) 6Ver: 0元器件交易网Data Sheet PT7C4302 Real-time Clock Module (3-wire Interface)|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||a)12 / 24 bitThis bit is used to select between 12-hour clock operation and 24-hour clock operation. 12, /24 Description Hours register 24-hour clock 00 01 02 03 04 05 06 07 08 09 10 11 12-hour clock 92 ( AM 12) 81 ( AM 01 ) 82 ( AM 02 ) 83 ( AM 03 ) 84 ( AM 04 ) 85 ( AM 05 ) 86 ( AM 06 ) 87 ( AM 07 ) 88 ( AM 08 ) 89 ( AM 09 ) 90 ( AM 10 ) 91 ( AM 11 ) 24-hour clock 12 13 14 15 16 17 18 19 20 21 22 23 12-hour clock B2 ( PM 12 ) A1 ( PM 01 ) A2 ( PM 02 ) A3 ( PM 03 ) A4 ( PM 04 ) A5 ( PM 05 ) A6 ( PM 06 ) A7 ( PM 07 ) A8 ( PM 08 ) A9 ( PM 09 ) B0 ( PM 10 ) B1 ( PM 11 )024-hour time display112-hour time displayBe sure to select between 12-hour and 24-hour clock operation before writing the time data. 4. Days of the week CounterThe day counter is a divide-by-7 counter that counts from 01 to 07 and up 07 before starting again from 01. Values that correspond to the day of week are user defined but must be sequential (i.e., if 1 equals Sunday, then 2 equals Monday, and so on). Illogical time and date entries result in undefined operation. Addr. (hex) 05 Description Days of the week (default) D7 0 0 D6 0 0 D5 0 0 D4 0 0 D3 0 0 D2 D1 D0W4 W2 W1 Undefined Undefined UndefinedPT0225(11/05) 7Ver: 0元器件交易网Data Sheet PT7C4302 Real-time Clock Module (3-wire Interface)|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||5.Calendar CounterThe data format is BCD format. • Day digits: Range from 1 to 31 (for January, March, May, July, August, October and December). Range from 1 to 30 (for April, June, September and November). Range from 1 to 29 (for February in leap years). Range from 1 to 28 (for February in ordinary years). Carried to month digits when cycled to 1. • Month digits: Range from 1 to 12 and carried to year digits when cycled to 1. • Year digits: Range from 00 to 99 and 00, 04, 08, …, 92 and 96 are counted as leap years. Addr. (hex) 03 04 06 Description Dates (default) Months (default) Years (default) D7 0 0 0 0 D6 0 0 0 0 D5 D4 D3 D2 D1 D0D20 D10 D8 D4 D2 D1 Undefined Undefined Undefined Undefined Undefined Undefined 0 0 M10 M8 M4 M2 M1 Undefined Undefined Undefined Undefined UndefinedY80 Y40 Y20 Y10 Y8 Y4 Y2 Y1 Undefined Undefined Undefined Undefined Undefined Undefined Undefined UndefinedNote: Any registered imaginary time should be replaced by correct time, otherwise it will cause the clock counter malfunction. 6. Trickle Charger Description Trickle charger (default) D7 TCS 0 D6 TCS 1 D5 TCS 0 D4 TCS 1 D3 DS 1 D2 DS 1 D1 RS 0 D0 RS 0Addr. 8a) Trickle Charger Select Control the selection of the trickle charger. TCS Data Read/ Write Other patent 1010 Disable the trickle charger Enable the trickle chargerDescription * Default 0101PT0225(11/05) 8Ver: 0元器件交易网Data Sheet PT7C4302 Real-time Clock Module (3-wire Interface)|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||b) Diode Select Select whether one diode or two diodes are connected between VCC2 and VCC1. DS Data Description 00 or 11 Read/ Write 01 10 The trickle charger is disabled independently of TCS. One diode is selected. Two diodes are selected. * Defaultc) Resistor Select Select whether one diode or two diodes are connected between VCC2 and VCC1. RS Data Description 00 Read/ Write 01 10 11 No resistor. R1 with typ. 2kΩ R2 with typ. 4kΩ R3 with typ. 8kΩ * DefaultCommunication1. a) 3-wire Interface Command ByteFigure 1 Command byte The command byte is shown in Figure 1. Each data transfer is initiated by a command byte. The MSB (Bit 7) must be a logic 1. If it is 0, writes to the PT7C4302 will be disabled. Bit 6 specifies clock/calendar data if logic 0 or RAM data if logic 1. Bits 1 through 5 specify the designated registers to be input or output, and the LSB (bit 0) specifies a write operation (input) if logic 0 or read operation (output) if logic 1. The command byte is always input starting with the LSB (bit 0). b) RST and SCL Signal All data transfers are initiated by driving the RST input high and terminated by driving the RST input low. A clock cycle is a sequence of a falling edge followed by a rising edge. For data inputs, data must be valid during the rising edge of the clock and data bits are output on the falling edge of clock. If the RST input is low all data transfer terminates and the SDA pin goes to a high impedance state. Data transfer is illustrated in Figure 2 and Figure 3. At power-up, RST must be a logic 0 until VCC > 2.0V. Also SCLK must be at a logic 0 when RST is driven to a logic 1 state.PT0225(11/05) 9Ver: 0元器件交易网Data Sheet PT7C4302 Real-time Clock Module (3-wire Interface)|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||c)Single Byte ReadFigure 2 Single byte read Following the eight SCLK cycles that input a read command byte, a data byte is output on the falling edge of the next eight SCLK cycles. Note that the first data bit to be transmitted occurs on the first falling edge after the last bit of the command byte is written. Additional SCLK cycles will transmit the same data bytes by PT7C4302 so long as RST remains high. This operation permits continuous burst mode read capability. Also, the SDA pin is tri-stated upon each rising edge of SCLK. Data is output starting with bit 0. d) Single Byte WriteFigure 3 Signal byte write Following the eight SCLK cycles that input a write command byte, a data byte is input on the rising edge of the next eight SCLK cycles. Additional SCLK cycles are ignored. Data is input starting with bit 0. e) Burst Mode Burst mode is specified for either the clock/calendar or the RAM registers by addressing location 31 decimal (Address bits: A4 A3 A2 A1 A0 = 1 1 1 1 1 showed in Figure 1). As before, bit 6 specifies clock or RAM and bit 0 specifies read or write. There is no data storage capacity at locations 9 through 31 in the Clock/Calendar Registers or location 31 in the RAM registers. Reads or writes in burst mode start with bit 0 of address 0. When writing to the clock registers in the burst mode, the first eight registers must be written in order for the data to be transferred. If the number of transferred bytes is less than eight, the data will be ignored. However, when writing to RAM in burst mode, it is not necessary to write all 31 bytes for the data to transfer. Each byte that is written will be transferred to RAM regardless of whether all 31 bytes are written or not. Additional SCLK cycles are ignored. • Clock/Calendar Burst Mode The clock/calendar command byte specifies burst mode operation. In this mode the first eight clock/calendar registers can be consecutively read or written starting with bit 0 of address 0. If the write protect bit is set high when a write clock/calendar burst mode is specified, no data transfer will occur to any of the eight clock/calendar registers (this includes the control register). The trickle charger is not accessible in burst mode. At the beginning of a clock burst read, the current time is transferred to a second set of registers. The time information is read from these secondary registers, while the clock may continue to run. This eliminates the need to re-read the registers in case of an update of the main registers during a read.PT0225(11/05) 10Ver: 0||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||| •RAM Burst ModeThe RAM command byte specifies burst mode operation. In this mode, the 31 RAM registers can be consecutively read or written starting with bit 0 of address 0.Note: PT7C4302 use 94H, 96H as test mode address. Customer should not use the address.Maximum RatingsStorage Temperature.......................................................................................................................-65o Cto +150o CAmbient Temperature with Power Applied...........................................................................-40o Cto +85o CSupply Voltage to Ground Potential (Vcc to GND) ..........................................................-0.3V to +6.5VDC Input (All Other Inputs except Vcc & GND)................................................................-0.3V to +6.5VDC Output Voltage (SDA, /INTA, /INTB pins)..................................................................-0.3V to +6.5VPower Dissipation............................................................................................................................320mW (Depend on package)Note:Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.Recommended Operating ConditionsUnitMax Symbol Description MinTypeV CC1,V CC2Power voltage. V CC = V CC2, when V CC2 > V CC1 + 0.2;2 - 5.5V CC = V CC1, when V CC1 > V CC2.V V IH Input high level 2 - V CC+0.3V IL Input low level -0.3 - 0.3temperature -40 - 85 ºC T A Operating|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||DC Electrical CharacteristicsUnless otherwise specified, GND =0V, T A = 25 °C, Oscillation frequency = 32.768kHz. Sym Item Pin ConditionsMin Typ MaxUnitV CC Supply voltageV CC1, V CC2Note 52.0 - 5.5 V V CC1: 2V - - 0.4OSC on, Note 2,6V CC1: 5V - - 1.2 mAV CC1: 2V - 0.5 -OSC on, Note 1,6 V CC1: 5V - 1 - µAV CC1: 2V - 100-I CC1 Current consumptionV CC1OSC off, Note 4,6,8 V CC1: 5V - 100- nAV CC1: 2V - - 0.425OSC on, Note 2,7V CC1: 5V - - 1.28mAV CC1: 2V - - 25.3OSC on, Note 1,7 V CC1: 5V - - 81 µAV CC1: 2V - - 25I CC2 Current consumptionV CC2OSC off, Note 4,7V CC1: 5V- - 80 µAV CC1: 5V- 1.1 0.8V IL1 Low-level input voltage SCL, /RST V CC1: 2V - 0.6 0.4 VV CC1: 5V 2.0 1.3 -V IH1 High-level input voltage SCL, /RST V CC1: 2V 1.4 0.9 - VV CC1: 5V - 1.9 0.8V IL2 Low-level input voltage X1 V CC1: 2V - 0.9 0.6 VV CC1: 5V 2.0 1.9 -V IH2 High-level input voltage X1 V CC1: 2V1.4 0.9 - VI OH = 1.5mA, V CC = 2V - 0.080.4V OL Low-level output voltage I/O I OH = 4.0mA, V CC = 5V - 0.110.4 VI OH = -0.4mA, V CC = 2V 1.6 1.9 -V OH High-level output voltage I/O I OH = -1.0mA, V CC = 5V 2.4 4.9 - VI IL Input leakage current /RST, SCLKNote 3- - 500µA I OZOutput current when OFF I/O Note 3--500µAV TD Trickle Charge Diode Voltage Drop - -- 0.7 - VR1 - -- 2 -R2 - - - 4 -R3 Trickle charge resistors - -- 8 -k Ω Note :1. I/O open, /RST set to a logic 0, and /EOSC bit = 0 (oscillator enabled).2. I/O pin open, /RST high, SCLK=2MHz at V CC = 5V; SCLK = 500kHz, V CC = 2.0V, and /EOSC bit = 0 (oscillator enabled).3. /RST, SCLK, and I/O all have 40k Ω pull-down resistors to ground.4. /RST, I/O, and SCLK open. The /EOSC bit = 1 (oscillator disabled).5. VCC = VCC2, when VCC2 > VCC1 + 0.2V; VCC = VCC1, when VCC1 > VCC2.6. VCC2 = 0V.7. VCC1 = 0V.8. Typical values are at 25°C.|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||AC Electrical CharacteristicsFigure 6 a Timing diagram: Read data transfer Figure 6 b Timing diagram: Write data transferT= -40 °C to +85 °C. Unless otherwise specified. ================1. Measured at V IH = 2.0V or V IL = 0.8V and 10ns maximum rise and fall time. 2. Measured at V OH = 2.4V or V OL = 0.4V. 3. Load capacitance = 50pF.|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||Mechanical InformationP/PE (8-Pin DIP)81 .240 .280 6.09 7.11.210 Max .355 .400 SEATING PLANE.008.014.430Max .300.325.015 Min .014 .022 .100 typical .115 .150 5.330.3817.628.250.200.350.6356 0.5582.9213.812.549.01 10.160° 15°|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||W/WE (8-Pin SOIC) SEATING PLANE18.189 .196 4.80 5.00.149 .157 3.78 3.99.016 .026 0.406 0.660 REF.053 .068 1.35 1.75.0099.01960.25 0.50x 45° 0-8°.016 .0500.401.27.0075.00980.19 0.25.2284|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||NotesPericom Technology Inc.Email: support@Web Site: , China: No. 20 Building, 3/F, 481 Guiping Road, Shanghai, 200233, ChinaTel: (86)-21-6485 0576 Fax: (86)-21-6485 2181Asia Pacific: Unit 1517, 15/F, Chevalier Commercial Centre, 8 Wang Hoi Rd, Kowloon Bay, Hongkong Tel: (852)-2243 3660 Fax: (852)- 2243 3667U.S.A.: 3545 North First Street, San Jose, California 95134, USATel: (1)-408-435 0800 Fax: (1)-408-435 1100Pericom Technology Incorporation reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or performance and to supply the best possible product. Pericom Technology does not assume any responsibility for use of any circuitry described other than the circuitry embodied in Pericom Technology product. The company makes no representations that circuitry described herein is free from patent infringement or other rights, of Pericom Technology Incorporation.。

CA42中英文对照规格书全正文(新) FREE

修改记录Revision Record目录CATALOG1.适用范围Scope (3)2.产品代码说明 Product identification (3)3.规格范围 The range of the specification (3)4.电性参数检测标准、检测条件及其温度特性Temperature characteristic (4)5.形状及尺寸 Appearance & Dimensions (4)6.标志 Marking (5)7.容量范围、壳号The range of the capacitance and case (5)8.可靠性试验Reliable performance (6)9.无铅产品识别标识The lead-free product identifying label 710.特性曲线Typical Characteristic curve (7)11.包装Packing (9)12.安装方法 The method of mounting (12)13.使用注意事项Note in use (12)14.贮存 Storage (13)15.订货资料 Ordering information (13)1. 适用范围Scope本规格书适用于树脂包封固体电解质钽电容器(无铅)。

This specification applies to Epoxy-coated Solid Electrolytic Tantalum Capacitors (LEAD FREE ).2.产品代码说明 Product identification⑴ ⑵⑶ ⑷⑸ ⑹⑺说明Explain :⑴企业代码company logo ⑵产品型号series: CA42表示树脂包封固体电解质钽电容器的型号.CA42 representseries number of epoxy-coated solid electrolytic tantalum capacitors⑶容 量capacitance code :容量用皮法拉表示,前两位数字是有效数字,第三位数字是跟随零的个数。

NTP4302中文资料

NTP4302, NTB4302Power MOSFET 74 Amps, 30 VoltsN−Channel TO−220 and D 2PAKFeatures•Low R DS(on)•Higher Efficiency Extending Battery Life •Diode Exhibits High Speed, Soft Recovery •Avalanche Energy Specified•I DSS Specified at Elevated TemperatureTypical Applications•DC−DC Converters•Low V oltage Motor Control•Power Management in Portable and Battery Powered Products: Ie:Computers, Printers, Cellular and Cordless Telephones, and PCMCIA CardsMAXIMUM RATINGS (T= 25°C unless otherwise noted)Size, (Cu Area 0.412 in 2).2.Current limited by internal lead wires.Device Package Shipping ORDERING INFORMATIONNTP4302TO−220AB 50 Units/Rail NTB4302D 2PAK 50 Units/Rail NTB4302T4D 2PAK800/T ape & ReelELECTRICAL CHARACTERISTICS(T= 25°C unless otherwise noted)4.Switching characteristics are independent of operating junction temperatures.30I D , D R A I N C U R R E N T (A M P S )0R D S (o n ), D R A I N −T O −S O U R C E R E S I S T A N C E (Ω)7010204050601.41.210.6Figure 5. On−Resistance Variation withTemperature T J , JUNCTION TEMPERATURE (°C)Figure 6. Drain−to−Source Leakage Currentversus VoltageV DS , DRAIN−TO−SOURCE VOLTAGE (VOLTS)−5050250−257510002025151030R D S (o n ), D R A I N −T O −S O U R C E R E S I S T A N C E (N O R M A L I Z E D )0.81501250.040.060.080.021.61000100101C , C A P A C I T A N C E (p F ))10001001t , T I M E (n s )Figure 11. Maximum Rated Forward BiasedSafe Operating Area V DS , DRAIN−TO−SOURCE VOLTAGE (VOLTS)Figure 12. Maximum Avalanche Energy versusStarting Junction TemperatureT J , STARTING JUNCTION TEMPERATURE (°C)I D , D R A I N C U R R E N T (A M P S )0.110110025125100755015010S )SAFE OPERATING AREATIMEFigure 13. Thermal ResponseFigure 14. Diode Reverse Recovery Waveformr (t ), N O R M A L I Z E D E F F E C T I V E T R A N S I E N T T H E R M A L R E S I S T A N C Et, TIME (s)TO−220 THREE−LEADTO−220ABCASE 221A−09ISSUE AASTYLE 5:PIN 1.GATE2.DRAIN3.SOURCE4.DRAIND2PAKCASE 418AA−01ISSUE OVIEW W−W VIEW W−W VIEW W−W 123ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATION。

高精度芯片抑制器PAT3042 4556 3060H产品说明书

Applications

ɾAttenuator for coaxial lines/circuit ɾAttenuator for measuring instrumentation

˗Part numbering system

1"5$E#"5

Series code Size ɿPAT3042,PAT4556,PAT3060H

Impedance: C=50Ω

Packing quantity: T=Tape (T1/T2), B=Bulk

Attenuation toleranceʢ PAT3042/4556)

Attenuation来自˗Electrical Specification

Type

1"5

1"5 1"5)

1"5

1"5)

#PUUPN

5ZQF 4J[F JODI

4ZNCPM 8 U 8 8 8 - -

E#

ʶ ʶ ʶ

ʔ ʶ

E#

ʶ ʶ ʶ ʶ ʶ

PAT series W type High frequency surface mount components 3BUJPUPSBUFEQPXFSʢˋʣ

Operating frequency

%$ ʙ ()[

%$ ʙ ()[

Rated power

N8

N8

8

Rated operating temperature

ˆ

Operating temperature

ʵˆʙʴˆ

Packaging quantity

QDTCBH #

High Precision Chip Attenuator

430BOOST-C55AUDIO1;中文规格书,Datasheet资料

software library• Stereo single-jack headset connector (supports stereo/mono headphones with built-in mic)• microSD card with pre-programmed DSP code for MP3 playback, record and music storage (file storage)• USB mass storage device capability for the microSD card with provided USB cable • OLED display (monochrome, 96×16 pixels) • Quick Start Guide includedB010208Important Notice: The products and services of Texas Instruments Incorporated and its subsidiaries described herein are sold subject to TI’s standard terms and conditions of sale. Customers are advised to obtain the most current and complete information about TI products and services before placing orders. TI assumes no liability for applications assistance, customer’s applications or product designs, software performance, or infringement of patents. The publication of information regarding any other company’s products or services does not constitute TI’s approval, warranty or endorsement thereof.© 2012 Texas Instruments IncorporatedThe platform bar C5000 and MSP430 are trademarks of Texas Instruments. All other trademarks are the property of their respective owners.SPRT630Technical DetailsThe Audio Capacitive Touch BoosterPack allows quick evaluation and simplified design of audio capacitive touch products and includes:• BoosterPack board with ultra-low-power C5000 DSP for crystal clear playback and recording of MP3 audio and video files • microSD card pre-programmed with the DSP function code -- MP3 playback, record and music storage (file storage)• Mini-USB cable for connection with a computer to power up the system • Stereo single-jack headset connector (supports stereo/mono headphones with built-in mic)• Initial demo headset with integrated microphone• MSP430G2553 Value Line Microcontroller pre-programmed with the ACTBP host demo application – this will replace the MSP430 on the separate LaunchPad (not included).• Supported by a user interface for OLED display and MP3 playback/record application APIs• Capacitive touch scroll wheel, proximity sensor and on-board LEDs• Supported by a complete capacitive touch software library• USB mass storage device capability for the microSD card with provided USB cable • OLED display (monochrome, 96×16 pixels) • Quick start guideSoftwareThrough the MSP430 LaunchPad (not included),designers can interface with integrated software environments such as Code Composer Studio version 4 or IAR Embedded Workbench. These free IDEs include an assembler, linker, simulator,source-level debugger and C-compiler to help developers integrate new and customized audio and voice applications. TI also offers a complete capacitive touch software library,enabling designers to quickly and easily prototype and test new designs.SupportWith the Audio Capacitive Touch BoosterPack designers also get unlimited access to the LaunchPad Wiki. This Wiki promotescollaboration and simple sharing of solutions and ideas, making LaunchPad along with the BoosterPack a complete development environment for audio capacitive touch designs. This active and growing online community supplements the hardware and software components of the LaunchPad andBoosterPack package and provides instant support, projects and helpful hints that will be shared through the Wiki pages and E2ETM forums.For customers looking for extra support for the C5000 DSP , TI offers complete support by TI’s extensive Developer Network, as well as a complete Chip Support Library, comprehensive application notes, reference designs, application guides, videos and online communities.Get Started TodayEasily upgrade low-power applications with TI’s new C5000 DSP-based Audio Capacitive Touch BoosterPack for the MSP430 LaunchPad development kit. For the first time, new functionalities can be enabled on the DSP and controlled solely by the MCU, includingcrystal clear audio capabilities.For more information on the C5000 Audio Capacitive Touch BoosterPack, please visit /audioboosterpack.IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,modifications,enhancements,improvements, and other changes to its products and services at any time and to discontinue any product or service without notice.Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by government requirements,testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design.Customers are responsible for their products and applications using TI components.To minimize the risks associated with customer products and applications,customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any TI patent right,copyright,mask work right, or other TI intellectual property right relating to any combination,machine,or process in which TI products or services are rmation published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.Reproduction of this information with alteration is an unfair and deceptive business practice.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements.TI products are not authorized for use in safety-critical applications(such as life support)where a failure of the TI product would reasonably be expected to cause severe personal injury or death,unless officers of the parties have executed an agreement specifically governing such use.Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications,and acknowledge and agree that they are solely responsible for all legal,regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications,notwithstanding any applications-related information or support that may be provided by TI.Further,Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or"enhanced plastic."Only products designated by TI as military-grade meet military specifications.Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk,and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use. TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS16949requirements.Buyers acknowledge and agree that,if they use any non-designated products in automotive applications,TI will not be responsible for any failure to meet such requirements.Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAudio /audio Automotive and Transportation /automotiveAmplifiers Communications and Telecom /communicationsData Converters Computers and Peripherals /computersDLP®Products Consumer Electronics /consumer-appsDSP Energy and Lighting /energyClocks and Timers /clocks Industrial /industrialInterface Medical /medicalLogic Security /securityPower Mgmt Space,Avionics and Defense /space-avionics-defense Microcontrollers Video and Imaging /videoRFID OMAP Mobile Processors /omapWireless Connectivity /wirelessconnectivityTI E2E Community Home Page Mailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2012,Texas Instruments Incorporated分销商库存信息:TI430BOOST-C55AUDIO1。

PT4302 中文版

数据输出噪声

当发射器没有送出讯号的时候,OOK/ASK 的数据输出看起来是类似任意的噪声。大多数的译码器是可分办讯号与噪声, 但对于部份的解调系统却会构成困扰。要减少这些噪声可以有两个方式: 1. 改变 ASK 解调器的门坎电压,使得较小讯号不被解调出。 2. 在数据输出时增加滤波器过滤高频噪声或突波。 最简单的方法将 CTH 脚接一大电阻到 VSS 或是芯片内部的电源,通常为 5.1 MΩ 到 8.2 MΩ,使的门坎电压有 20 mV 到 30 mV 的位移。这时候较小的射频讯号就无法被解调出来,形成类似静音的效果。代价是会对接收感度造成影响,好处 是当无讯号输入或是讯号很小的时候,数据输出噪声会大幅减少。 下图为一个示范电路。当大电阻 R6 接到芯片内部电源,Pin15 VLO 时,在类似静音的情况下 DO 输出会保持在低电位。 如果使用的环境噪声非常严重,可降低 R6 的电阻值,以得到更好的噪声抑制效果;但也必须牺牲更多的接收感度。

For NaterTech

PT4302

应用电路

应用电路组件表

编号 L1 L2 C1 C2, C3, C4 C5 C6 R1 R2, R3, R4, R5 R6 F1 X1 U1 数值 315 MHz 82 n 39 n 1.8 p 100 n 470 n 220 p 10 10 K 8.2 M 10.7 9.509 PT4302 IC 433.92 MHz 47 n 27 n 1.0 p 100 n 470 n 220 p 10 10 K 8.2 M 10.7 13.226 PT4302 IC 单位 H H F F F F Ω Ω Ω MHz MHz U1 說明 天线端输入阻抗匹配, 使用绕线电感 天线端静电防护, 使用绕线电感 (option) 天线端输入阻抗匹配 电源滤波电容 CTH 电容, 影响编码格式及起动时间 可视晶振厂家或频率修正调整数值 电源滤波电阻 (option) 与 MCU 界面电阻(option) 降低数据输出噪声 (option) 带通滤波器 晶振 接收芯片

TI产品MSP430FR2422中文说明书

ProductFolder OrderNowTechnicalDocumentsTools &SoftwareSupport &CommunityMSP430FR2422ZHCSHB5A–JANUARY2018–REVISED AUGUST2018MSP430FR2422混合信号微控制器1器件概述1.1特性•嵌入式微控制器–16位精简指令集(RISC)架构–支持的时钟频率最高可达16MHz– 3.6V至1.8V的宽电源电压范围(最低电源电压受限于SVS电平,请参阅SVS规格)•优化的超低功耗模式–激活模式:120µA/MHz(典型值)–待机:LPM3.5,采用32768Hz晶振的实时时钟(RTC)计数器:710nA(典型值)–关断(LPM4.5):36nA,无SVS•低功耗铁电RAM(FRAM)–高达7.5KB的非易失性存储器–内置错误修正码(ECC)–可配置的写保护–对程序和常量数据统一进行存储–1015写入周期持久性–抗辐射和非磁性–铁电随机存取存储器(FRAM)与静态随机存取存储器(SRAM)之比最高达4:1•高性能模拟–高达8通道10位模数转换器(ADC)– 1.5V内部基准电压–采样与保持200ksps•智能数字外设–两个16位计时器,每个计时器有3个捕捉/比较寄存器(Timer_A3)–一个仅用作计数器的16位RTC–16位循环冗余校验(CRC)•增强型串行通信,支持引脚重映射功能(请参阅器件比较)–一个eUSCI_A接口,支持UART、IrDA和SPI –一个eUSCI_B接口,支持SPI和I2C •时钟系统(CS)–片上32kHz RC振荡器(REFO)–带有锁频环(FLL)的片上16MHz数字控制振荡器(DCO)–室温下的精度为±1%(具有片上基准)–片上超低频10kHz振荡器(VLO)–片上高频调制振荡器(MODOSC)–32kHz外部晶振(LFXT)–可编程MCLK预分频器(1至128)–通过可编程预分频器(1、2、4或8)从MCLK 获得的SMCLK•通用输入/输出和引脚功能–共计15个I/O(采用VQFN-20封装)–15个中断引脚(P1和P2)可以将MCU从低功耗模式下唤醒•开发工具和软件–开发工具–MSP-TS430RHL20目标开发套件•系列成员(另请参阅器件特性)–MSP430FR2422:7.25KB程序FRAM+256B 信息FRAM+2KB RAM•封装选项–20引脚:VQFN(RHL)–16引脚:TSSOP(PW)•有关完整模块说明,请参见《MSP430FR4xx和MSP430FR2xx系列器件用户指南》1.2应用•工业传感器•电池组•便携式设备•电动牙刷•低功耗医疗、健康和健身器材1.3说明MSP430FR2422是MSP430™超值系列微控制器(MCU)产品组合的其中一个器件,该超值系列微控制器是TI成本最低的MCU系列,适用于检测和测量应用。

MAXIM DS4302数字输出数据手册

General DescriptionThe DS4302 is a 5-bit digital-to-analog converter (DAC)with three programmable digital outputs. The DS4302communicates through a 2-wire, SMBus™-compatible,serial interface. The tiny 8-pin µSOP package is ideal for use in space-constrained applications.ApplicationsCCFL Backlight Brightness Control Power-Supply CalibrationFeatures♦SO Package is a Drop-In Replacement for the MPS1251 and MPS1252♦Single 5-Bit DAC (32 Steps)♦0V to 2V and 0V to 1.9V Versions ♦Three Programmable Digital Outputs ♦SMBus-Compatible Serial Interface ♦4.5V to 5.5V Supply Voltage Range ♦8-Pin SO and 8-Pin µSOP Packages♦Industrial Temperature Range: -40°C to +85°CDS43022-Wire, 5-Bit DAC with Three Digital Outputs______________________________________________Maxim Integrated Products 1Pin ConfigurationOrdering InformationRev 1; 6/04For pricing, delivery, and ordering information,please contact Maxim/Dallas Direct!at 1-888-629-4642, or visit Maxim’s website at .Add “/T&R” for tape-and-reel orders.*Contact factory for availability.SMBus is a trademark of Intel Corp.D S 43022-Wire, 5-Bit DAC with Three Digital Outputs 2_____________________________________________________________________ABSOLUTE MAXIMUM RATINGSRECOMMENDED DC OPERATING CONDITIONSStresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.Voltage Range on V CC , SDA, and SCL PinsRelative to Ground.............................................-0.5V to +6.0V Operating Temperature Range ...........................-40°C to +85°CStorage Temperature Range.............................-55°C to +125°C Soldering Temperature.....See IPC/JEDEC J-STD-020A SpecificationDC ELECTRICAL CHARACTERISTICS(V CC = +4.5V to 5.5V, T A = -40°C to +85°C.)DS43022-Wire, 5-Bit DAC with Three Digital Outputs_____________________________________________________________________3AC ELECTRICAL CHARACTERISTICS (Figure 3)(V CC = +4.5V to 5.5V, T A = -40°C to +85°C, timing referenced to V IL(MAX)and V IH(MIN).)Note 1:All voltages referenced to ground.Note 2:I STBY specified for the inactive state measured with SDA = SCL = V CC and with V OUT , P0, P1, and P2 floating.Note 3:No load on V OUT .Note 4:The DS4302 will not obstruct the SDA and SCL lines if V CC is switched off as long as the voltages applied to these inputs does not violate their min and max input-voltage levels.Note 5:C B —total capacitance of one bus line in picofarads.D S 43022-Wire, 5-Bit DAC with Three Digital Outputs 4_____________________________________________________________________Typical Operating Characteristics(V CC = +5.0V, T A = +25°C.)STANDBY SUPPLY CURRENTvs. SUPPLY VOLTGESUPPLY VOLTAGE (V)S T A N D B Y S U P P L Y C U R R E N T (µA )5.255.004.755010015020025030004.505.50STANDBY SUPPLY CURRENTvs. TEMPERATURETEMPERATURE (°C)S T A N D B Y S U P P L Y C U R R E N T (µA )2040600-20501001502002503000-4080SUPPLY CURRENT vs. SCL FREQUENCYSCL FREQUENCY (kHz)S U P P L Y C U R R E N T(µA )3002001005010015020025030000400V OUT vs. DAC SETTINGDAC SETTING (dec)V O U T (V )302520151050.51.01.52.000V OUT vs. SUPPLY VOLTAGESUPPLY VOLTAGE (V)V O U T (V )5.255.004.751.952.002.052.101.904.505.50V OUT PERCENT CHANGE FROM +25°Cvs. TEMPERATURETEMPERATURE (°C)V O U T P E R C E N T C H A N G E (%)80604020-20-0.50.51.0-1.0-40DS43022-Wire, 5-Bit DAC with Three Digital Outputs_____________________________________________________________________5Functional DiagramD S 4302Detailed DescriptionThe DS4302 contains a 5-bit DAC and three programma-ble digital outputs. The DAC setting and the pro-grammed output levels are contained in a 1-byte data word that defaults to 00h on power-up (see Figure 1 for data byte configuration). The upper 5 MSbits of the byte set the DAC and control the voltage produced on V OUT .A setting of 1111 1XXX sets the minimum output voltage from the DAC while a setting of 0000 0XXX sets the maxi-mum output voltage from the DAC. The three LSbits of the data byte control the three output pins, P0, P1, and P2. Setting any of these control bits to a 0 pulls the corre-sponding outputs low and setting the bits to a 1 pulls the outputs high.The DS4302 communicates through a 2-wire (SMBus-compatible) digital interface and has a 2-wire address of 58h. Write and read operations are used to access the DAC and output settings. Each operation begins with a 2-wire START condition, consists of three bytes, and ends with a 2-wire STOP condition (see Figure 2). Using the write operation, the 2-wire master can program the5-bit DAC to adjust the voltage on VOUT and set the level of the three output pins: P0, P1, and P2. The read operation is used to recall the programmed settings.2-Wire DefinitionsThe following terminology is commonly used to describe 2-wire data transfers.Master Device:The master device controls the slave devices on the bus. The master device generates SCL clock pulses, START, and STOP conditions.Slave Devices:Slave devices send and receive data at the master’s request.Bus Idle or Not Busy:Time between STOP and START conditions when both SDA and SCL are inactive and in their logic-high states. When the bus is idle, it initiates a low-power mode for slave devices.START Condition:A START condition is generated by the master to initiate a new data transfer with a slave.Transitioning SDA from high to low while SCL remains high generates a START condition. See Figure 3 for applicable timing.STOP Condition:A STOP condition is generated by the master to end a data transfer with a slave. Transitioning SDA from low to high while SCL remains high generates a STOP condition. See Figure 3 for applicable timing.Bit Write:Transitions of SDA must occur during the low state of SCL. The data on SDA must remain valid and unchanged during the entire high pulse of SCL plus the setup and hold time requirements (see Figure 3). Data is shifted into the device during the rising edge of the SCL.2-Wire, 5-Bit DAC with Three Digital Outputs 6_____________________________________________________________________Figure 2. 2-Wire Communication ExamplesBit Read:At the end a write operation, the master must release the SDA bus line for the proper amount of setup time (see Figure 3) before the next rising edge of SCL during a bit read. The device shifts out each bit of data on SDA at the falling edge of the previous SCL pulse and the data bit is valid at the rising edge of the current SCL pulse. Remember that the master generates all SCL clock pulses including when it is reading bits from the slave.Acknowledgement (ACK):An Acknowledgement (ACK) is always the 9th bit transmitted during a byte transfer. The device receiving data (the master during a read or the slave during a write operation) performs an ACK by transmitting a zero during the 9th bit. For tim-ing, see Figure 3. An ACK is the acknowledgement that the device is properly receiving data.Byte Write:A byte write consists of 8 bits of informa-tion transferred from the master to the slave (most sig-nificant bit first) plus a 1-bit acknowledgement from the slave to the master. The 8 bits transmitted by the mas-ter are done according to the bit write definition and the acknowledgement is read using the bit read definition.Byte Read:A byte read is an 8-bit information transfer from the slave to the master plus a 1-bit ACK from the master to the slave. The 8 bits of information that are transferred (most significant bit first) from the slave to the master are read by the master using the bit read definition above, and the master transmits an ACK using the bit write definition to receive additional data bytes. The master must ACK the last byte read to termi-nated communication so the slave returns control of SDA to the master.Slave Address and the R/W Bit:Each slave on the 2-wire bus responds to a slave addressing byte sent immediately following a START condition. The slave address byte contains the slave address and the R/W bit. The slave address (see Figure 4) is the most signifi-cant 7 bits and the R/W bit is the least significant bit.The DS4302’s slave address is 0101100X (binary),where X is the R/W bit. If the R/W bit is zero (01011000), the master will write data to the slave. If the R/W is a one (01011001), the master will read data from the slave.Memory Address:During a 2-wire write operation, the master must transmit a memory address to identify the memory location where the slave is to store the data.The memory address is the second byte transmitted during a write or read operation following the slave address byte (R/W =0). For a write operation, the mem-ory address is 10101010 (AAh) and for a read opera-tion, the memory address is 00000000 (00h).DS43022-Wire, 5-Bit DAC with Three Digital Outputs_____________________________________________________________________7Figure 4. Slave Address and the R/W BitFigure 3. 2-Wire Timing DiagramD S 43022-Wire, 5-Bit DAC with Three Digital Outputs Maxim c annot assume responsibility for use of any c irc uitry other than c irc uitry entirely embodied in a Maxim produc t. No c irc uit patent lic enses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.8_____________________Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600©2004 Maxim Integrated ProductsPrinted USAis a registered trademark of Maxim Integrated Products.DALLAS is a registered trademark of Dallas Semiconductor Corporation.2-Wire CommunicationWriting to a Slave:The master must generate a START condition, write the slave address (R/W = 0), write the memory address, write the byte of data, and generate a STOP condition. Remember the master must read the slave’s acknowledgement during all byte-write opera-tions. See Figure 2 for the write command example.Reading from a Slave:To read from the slave, the master generates a START condition, writes the slave address with R/W = 1, receives an ACK from the slave,reads a memory address of 00h from the slave, sends an ACK to the slave, reads the data byte, then sends an ACK to indicate the end of the transfer, and gener-ates a STOP condition. See Figure 2 for the read com-mand example.Application InformationPower-Supply DecouplingTo achieve the best results when using the DS4302,decouple the power supply with a 0.01µF or a 0.1µF capacitor. Use high-quality, ceramic, surface-mount capacitors, and mount the capacitors as close as pos-sible to the V CC and GND pins of the DS4302 to mini-mize lead inductance.SDA and SCL Pullup ResistorsPullup resistor values for SDA and SCL should be cho-sen to ensure that the rise and fall times listed in the AC electrical characteristics are within specification.。

Ritter MA4302 打印机安装和使用说明书

104 ExaminationTableTo purchase a printed copy of this manual,click on the "Place Order" button below.Style COwner’s Product Identification(information that you will need to provide for servicing - key information is highlighted) Date of Purchase Serial NumberModel NumberName of Owner / Facility / DepartmentName of Authorized Ritter Dealer Telephone # of Authorized Ritter DealerCONTENTSIMPORTANT INFORMATION (2)Intended Use of Product (2)Safety Instructions (2)Explanation of Safety Symbols and Notes (2)Transportation and Storage Conditions (2)Electromagnetic Interference (2)Symbols (3)INSTALLATION (3)Unpacking (3)Leveling The Table (4)Installing Paper Retaining Straps (5)Installing Paper Roll Dowel Rod (5)Electrical Requirements (5)DESCRIPTION (6)Introduction (6)Features (6)COMPONENTS OVERVIEW (7)CONTROLS & INDICATORS (8)OPERATION (9)Back Section (9)Stirrups (9)Footstep (10)Footrest (10)Irrigation Pan (11)Paper Roll (11)Pelvic Lift (Optional) (12)Drawer Heater (Optional) (12)List of Authorized Accessories (13)Patient Positioning (13)OPERATOR MAINTENANCE (13)Preventive Maintenance (13)Cleaning (14)CALLING FOR SERVICE (15)SPECIFICATIONS (15)LIMITED WARRANTY (16)IMPORTANT INFORMATIONIntended Use of ProductThis product is intended for use in examination / procedure environments wherepatient positioning is required to accomplish general medical examinations and /or procedures.Safety InstructionsThe primary concern of Midmark is that this equipment is operated and main-tained with the safety of the patient and staff in mind. To assure safer and morereliable operation:•Read and understand this manual before attempting to install or operate the table.•Assure that appropriate personnel are informed on the contents of this man-ual; this is the responsibility of the purchaser.•Assure that this manual is located near the table, or if possible, permanently affixed to the table.Explanation of Safety Symbols and Notes•Ambient Temperature Range:.....-30°C to +60°C (-22°F to 140°F)•Relative Humidity........................10% to 90% (non-condensing)•Atmospheric Pressure................ 500hPa to 1060 hPa (0.5 bar to 1.06 bars)Electromagnetic InterferenceThis product is designed and built to minimize electromagnetic interference withother devices, however, if interference is noticed between another device andthis product, remove interfering device from room or plug this product into anisolated circuit.23INSTALLATIONUnpackingCarefully remove the packaging from the table and then inspect the table for any shipping damage. Report any damage to the shipping company and fill out a concealed damage report.Unbolt the table from the wooden shipping skid by removing two bolts (1, Figure 2) from the underside of the table’s base.Fragile Height (palletted units)NOTE: Refer to SPECIFICATIONS section in this manual.This product is Listed by Underwriters Laboratories Inc. Representa-tive samples of this Product have been evaluated by UL and meet theapplicable U.S. safety requirements.This product has been evaluated with respect to electrical shock,fire, & mechanical hazards only, in accordance with UL60601-1 andCAN/CSA C22.2, No. 601.1.507U94XMSymbolsImportant Information InstallationAfter unbolting, remove the table from the shipping skid (3), lifting at points (4and 5). Do not lift at points (2); these are unsupported areas. Position the tablein room as desired.Remove red tape from stirrups. Pull out foot extension (6) and remove redpacking tape from the foot extension components. Return foot extension to itsstowed position.45Leveling The TableA leveling screw pad (7, Figure 2) is located under each corner of the table’s base. Adjust the four leveling screw pads (7) up or down (by turning them) untila solid, level installation is achieved.Installing Paper Retaining StrapsNOTEThe retaining straps may have to be stretched in order for them to be in-stalled. The material will recover, becoming taut again after installation.Two retaining straps are shipped in a side drawer. Install one retaining strap (8, Figure 2) on two snaps (9) and the other retaining strap (8) on two snaps (10).Installing Paper Roll Dowel RodA wood dowel rod (11, Figure 2) for supporting up to a 21 in. x 3-1/2 in. (53.3 cm x 8.9 cm) diameter paper roll (12 {not provided}) is shipped in a side drawer. To install, slide the dowel rod (11) through the paper roll (12) and then place the dowel rod ends in the two dowel rod sockets (13), located on the rear side of the table’s back section.Electrical RequirementsThe three-pronged grounding plug on the table power cord must be plugged into a matching three-pronged, grounded, non-isolated, correctly polarized 115 VAC receptacle. (Refer to Specifications for individual electrical ratings for specific Models).InstallationDESCRIPTIONIntroductionThe 104 Medical Examination Table is primarily used in examination rooms forgeneral examinations and minor procedures. The table top is adjustable from afull horizontal table position to a chair position. Also, when supported with anoptional pelvic lift bar, the lithotomy position can be achieved. There are fivestorage drawers which accommodate supplies used during examinations.FeaturesThe Model 104 Examination Table has . . .• a manually adjustable back section which is controlled by a spring assisted release handle, located on both the left and right sides of the table. Theback section is adjustable from a full horizontal table position to a chair posi-tion.•an optional pelvic lift bar which allows the seat section to be positioned in the Lithotomy position.•an optional drawer warmer which warms the foot end, top drawer.•an extendable footrest shelf which includes a positionable upholstered pad and a removable treatment pan.•right and left stirrups which can be extended to an infinite number of posi-tions as well as laterally in four positions.•five storage drawers on steel ball bearing glides; two on the foot end of the table and three on either the right or left side of the table (selected at time ofpurchase).• a self-locking steel step with a non-skid surface. The steps extends from the foot end of the table to assist patient entry and exit.• a duplex, hospital grade 115 VAC receptacle, located on the foot end, left side of the table.• a paper roll holder which is hidden in the head end of the upholstered top and tear strips, located at the foot end and head end of the upholstered top,to secure examination paper during a patient examination or procedure.67COMPONENTS OVERVIEWThe illustration below (Figure 3) shows the location of the table’s major compo-DESCRIPTION OF COMPONENTS 1.Back Section (adjustable)7.Storage Drawers2.Seat Section 8.Release Handle 3.Foot Rest Shelf (extendable)9.Duplex Receptacle4.Footrest Pad (removable)10.Drawer Warmer (optional)5.Treatment Irrigation Pan 11.Footstep (stowable)6.Stirrups 12.Paper Roll Dowel Description Components Overview8CONTROLS & INDICATORSRef.Control Function 1release handleused to release the back section so it may be lowered.2duplex receptacle provides power to small accessories used during an examination or procedure.3heater on / off switch (optional equipment)turns the drawer warmer heater on or off. The switch illuminates to indicate that the heater is operating.4pelvic lift support bar / release (optional equip-ment)automatically supports seat section in pelvic lift posi-tion when seat section is raised. To release seat sec-tion, operator rotates pelvic lift support bar and lowers seat section.Figure 4. Controls and IndicatorsOPERATION1011Irrigation Pantioned as desired.Paper RollA wood dowel rod (1) for sup-porting up to a 21 in. x 3-1/2in. (53.3 cm x 8.9 cm) diame-ter paper roll is supplied with the table. To install a paperroll, slide the dowel rod (1)through the paper roll (2) andthen place the dowel rod endsin the two dowel rod sockets(3), located on the rear side of the table’s back section. Pull the paper over table top andfeed the paper under two re-taining straps (4).Operationing.12List of Authorized AccessoriesListed below are the accessories which are authorized for use with the table.Accessory Name Order Number•Knee Crutch9A0100X•Armboard9A0200X(Do not use simultaneously on sameside of table with 9A21000X, SideRail)•Procto Rest9A0400X•Stainless Steel Pan9A7000X(Do not use simultaneously with9A10400X, Urology Drain Pan)•Urology Drain Pan9A10400X(Do not use simultaneously with9A7000X, Stainless Steel Pan •Pelvic Lift9A10500X•Welch Allen Bracket9A18000X•Knee Crutch9A20600X•Side Rail9A21000X(Do not use simultaneously on sameside of table with 9A0200X, Arm-board)Patient PositioningThe table is designed to accommodate the following examination / procedure positions:•Full Flat Table Position•Chair Position•Lithotomy (Pelvic) PositionOPERATOR MAINTENANCEPreventive MaintenanceLittle routine maintenance is required other than periodic inspection of the elec-trical cord to ensure it is free of cuts or damage, periodic inspection of the me-chanical functions to ensure satisfactory operation, and periodic check offasteners to ensure they are present and tightened securely.Have your authorized dealer inspect your table every six months.Oil moving parts (such as back hinge, pelvic tilt points, and the stirrup indexing pivot) with a light machine oil to assure quiet, smooth, and dependable opera-tion.Operation OperatorMaintenance13CleaningPainted Metal SurfacesWipe all painted metal surfaces with a clean cloth at least once a week. Applypaste wax periodically to preserve the surface luster.DrawersThe drawers may be removed for cleaning by pulling drawer straight out.Unpainted Metal SurfacesWipe all unpainted metal surfaces with a clean cloth. Use petroleum jelly or oth-er white lubricants on moving parts. Lubrication will allow free movement ofsliding parts and reduce noise.T read on FootstepThe protective tread material should be cleaned periodically by a light scrubbingwith a stiff bristle brush, mild soap, and water.CALLING FOR SERVICEIf you are having a problem or have a question, refer to the inside front cover ofthis manual and call your dealer. Make sure that you have the information thatis highlighted on the inside front cover of this manual available. If you can’t re-solve your question or problem with your dealer, call the following number:1-800-Midmark (1-800-643-6275)8:00 a.m until 5:00 p.m. (Eastern Standard time in the U.S.)Monday thru Friday, except for standard U.S. holidays.1415SPECIFICATIONSPatient Weight (Maximum)..................325 lbs (147.4 kgs)Weight of Table .....................................250 lbs (113.4 kgs)Back Section Adjustment ....................0° to 80°Dimensions:Upholstered top......................................27.0 in. wide x 55.0 in. long(68.6 cm x 139.7 cm)With Footrest Extended..........................72 in. (182.9 cm)Seat Height............................................31.75 in. (80.6 cm) to top of upholsteredseat at foot endStep........................................................10.75 x 17.75 x 10.75 high(27.3 cm x 45.1 cm x 27.3 cm)Base.......................................................17.5 in. x 42.375 in. x 4.125 in. high(44.4 cm x 107.6 cm x 10.5 cm)Paper Roll .............................................Can accept a paper roll up to 21 in. x3.5 in. (53.3 cm x 8.9 cm).Electrical Ratings / Compliance Standards:Model Complies to Standards:Electrical Ratings:104-035, 036UL 544115 VAC, 6.0 A, 60 Hz 104-037, 038115 VAC, 6.5 A, 60 Hz 104-039, 040UL60601-1 & CAN/CSA C22.2, No. 601.1N\AFire Code Ratings:All Midmark Upholstery sets comply with CaliforniaBureau of Home Furnishing T echnical Bulletin 117.Calling ForServiceSpecificationsOperatorMaintenanceLIMITED WARRANTYSCOPE OF WARRANTYMidmark Corporation (“Midmark”) warrants to the original purchaser its new Alter-nate Care products and components (except for components not warranted under“Exclusions”) manufactured by Midmark to be free from defects in material andworkmanship under normal use and service. Midmark’s obligation under this war-ranty is limited to the repair or replacement, at Midmark’s option, of the parts or theproducts the defects of which are reported to Midmark within the applicable warrantyperiod and which, upon examination by Midmark, prove to be defective.APPLICABLE WARRANTY PERIODThe applicable warranty period, measured from the date of delivery to the originaluser, shall be one (1) year for all warranted products and components.EXCLUSIONSThis warranty does not cover and Midmark shall not be liable for the following: (1)repairs and replacements because of misuse, abuse, negligence, alteration, acci-dent, freight damage, or tampering; (2) products which are not installed, used, andproperly cleaned as required in the Midmark “Installation” and or “Installation / Oper-ation Manual for this applicable product. (3) products considered to be of a consum-able nature; (4) accessories or parts not manufactured by Midmark; (5) charges byanyone for adjustments, repairs, replacement parts, installation, or other work per-formed upon or in connection with such products which is not expressly authorizedin writing in advance by Midmark.EXCLUSIVE REMEDYMidmark’s only obligation under this warranty is the repair or replacement of defec-tive parts. Midmark shall not be liable for any direct, special, indirect, incidental,exemplary, or consequential damages or delay, including, but not limited to, dam-ages for loss of profits or loss of use.NO AUTHORIZATIONNo person or firm is authorized to create for Midmark any other obligation or liabilityin connection with the products.THIS WARRANTY IS MIDMARK’S ONLY WARRANTY AND IS IN LIEU OF ALLOTHER WARRANTIES, EXPRESS OR IMPLIED. MIDMARK MAKES NOIMPLIED WARRANTIES OF ANY KIND INCLUDING ANY WARRANTIES OFMERCHANTABILITY OR FITNESS FOR ANY PARTICULAR PURPOSE. THISWARRANTY IS LIMITED TO THE REPAIR OR REPLACEMENT OF DEFECTIVEPARTS.SF-1487 REV. A116NOTES:LimitedWarranty17003-1527-00 Rev. A (2/05) Midmark Corporation 60 Vista DriveP.O. Box 286Versailles, Ohio 45380-0286937-526-3662Fax © Midmark Corporation - 2004。

UIM24302 智能带脉冲 微型一体化步进电机控制驱动器 说明书