apl1581

APL5912中文资料

C1 (pF) 27 36 68

Absolute Maximum Ratings

Symbol VCNTL VIN VI/O VPOK PD PPEAK TJ TSTG TSDR VESD Parameter VCNTL Supply Voltage (VCNTL to GND) VIN Supply Voltage (VIN to GND) EN and FB to GND POK to GND Average Power Dissipation Peak Power Dissipation (<20mS) Junction Temperature Storage Temperature Soldering Temperature, 10 Seconds Minimum ESD Rating (Human Body Mode) Rating -0.3 ~ 7 -0.3 ~ 3.3 -0.3 ~ VCNTL+0.3 -0.3 ~ 7 3 20 150 -65 ~ 150 300 ±2 Unit V V V V W W

APL5912 KA :

APL5912 XXXXX

Note: ANPEC lead-free products contain molding compounds/die attach materials and 100% matte tin plate termination finish; which are fully compliant with RoHS and compatible with both SnPb and lead-free soldiering operations. ANPEC lead-free products meet or exceed the lead-free requirements of IPC/JEDEC J STD-020C for MSL classification at lead-free peak reflow temperature.

火电厂几种主流DCS系统介绍

FoxboroA2自动化控制系统更适合于中小型 装置,采用以太网系统架构.符合lSO/OSl标 准.传输速率最高为100Mb/s,通信介质为 光缆或双绞线,用于连FoxboroA2的控制站、 工程师站、操作员站,也可与多种现场总线 相连.模块采用欧陆公司的2500系列和技术, 人机界面采Wonderware产品和技术.

由于FSSS对作为事件顺序的操作记录的要 求很高,而且可能是多系统组合来完成该项 功能,所以SOE的带有时间戳的开关量输入 设备及相关功能是必须具备的.在时间同步 方面,除了DCS系统内时钟同步方式,还有目 前正兴起的GPS卫星时间同步方式.

由于电厂的主要产品电能的特殊性及电网 调度和电业管理的要求,电厂已推行火力发 电厂厂级监控信息系统技术要求SIS,现在也 基本上做到很好和DCS之间的衔接问题.

优缺点

优点:系统可靠,在中国电力方面用户多达 200多个,新系统和老系统兼容,这有利于以 后的设备改造更新.图形化组态 ,方便于机组 运行中查找维护. 缺点:不能在软件中进行强制. PS:省内电厂使用该系统的有大唐洛河电厂.

西门子Siemens

在全世界已有超过1500套DCS控制系统装 置,是成功的电力和I&C系统供应商.在我国 电站中采用西门子的Tele-perm系统较多.近 年在全集成自动化的架构下,西门子推出 SPPA—T3000系统,已经在国内大型电站项 目陆续使用,效果相当不错.现就SPPATDCS系统进入21世纪,在通信和信息管理技 术、集成电路技术的进步以及工艺设备大 型化的影响下,在节能环保和提高生产效率 的需求下,形成了新一代的DCS,或称为第四 代DCS.在电厂方面,我们重点介绍ABB、西 门子SiemensT3000、艾默生 OvationFOXBORO和日立Hitachi五家相关 产品,这五家也是现在电厂DCS的主流厂家.

UZ1085 友顺UTC 电子元器件芯片

Dropout Voltage

VD △VREF%=1%, lOUT=3A

Current Limit

ILIMIT (VIN-VOUT)=2V

Minimum Load Current

IO(MIN) 1.5V≤ (VIN-VOUT) ≤12V

Quiescent Current

IQ VIN=12V

Ripple Rejection

UZ1085G-xx-TN3-R

TO-252 A/G

O

I

UZ1085L-xx-TQ2-T

UZ1085G-xx-TQ2-T

TO-263 A/G

O

I

UZ1085L-xx-TQ2-R

UZ1085G-xx-TQ2-R

TO-263 A/G

O

I

UZ1085L-xx-TQ3-T

UZ1085G-xx-TQ3-T

TO-263-3 A/G

MARKING

UTC UZ1085 XX 1

L: Lead Free G: Halogen Free

Date Code

VIN

+ 1.25V VREF

Thermal Current

Limit

Limit

VOUT

For Fixed Voltage

GND

UNISONIC TECHNOLOGIES CO., LTD

UNISONIC TECHNOLOGIES CO., LTD

3 of 7

QW-R102-013.J

UZ1085

LINEAR INTEGRATED CIRCUIT

ELECTRICAL CHARACTERISTICS (TA=25°C, COUT=22μF, unless otherwise specified.)

精确电压基准MCP1525、MCP1541中文资料

2.5Vਜ਼4.096V࢟ኹᓰ—M C P1525/1541特性z精确电压基准z输出电压2.5V和4.096Vz初始精度:最大1%z温度漂移: 最大50ppm/z输出电流驱动: 2mAz最大操作电流:最大100A@25z TO-92,SOT23-3封装z工业级温度范围:-4085应用z电池供电系统z手持设备z仪器和过程控制z测试设备z数据采集系统z通讯设备z医疗设备z精密功率供给电源z8位,10位,12位A/D转换器z D/A转换器描述Microchip公司的MCP1525和MCP1541设备是2.5V和4.096V精确电压基准,它们采用了先进的CMOS电路和EPROM微调技术的组合所以该器件可以达到1%最大的初始精度和最大50ppm/¢的温漂同时在25时静态电流可以低至100A最大,这些设备在超过时间和温度时还提供一个优于传统齐纳技术的新特性.MCP1525的输出电压为2.5V,MCP1541为4.096V.这些器件采用TO-92和SOT23-3封装,工业级温度范围:-4085.器件选择表封装MCP1541温度漂移1.0 电特性1.1 最大范围V IN 7.0V输入电流(V IN) 20mA输出电流(V OUT) 20mA连续电压损耗(T A=15) 140mW所有输入和输出w.r.t -0.6V~(V IN+1.0V)存储温度 -65150输入电压时环境温度 -55125对所有引脚的ESD保护4kV电特性说明 1.输出电压滞后指25时测量的输出电压在温度从85变化到-40前后的电压变化.2.输出温度系数用一个”BOX”的方法来测量,其方法是在25时将输出电压尽量修整为典型值,然后85时输出电压再次被修整为零.2.0 典型性能曲线除非特别说明,V=5V,I OUT=0mA,C L=1F,T A=25图2-1 输出电压变化与温度对应关系图2-2 负载变化与温度关系图2-3 输入电流与温度关系图2-4 线性变化与温度关系图2-5 输出阻抗与频率关系图2-6 输出电压噪音与频率关系图2-7 输入电压抑制率与频率图2-8 输出电压与输入电压对应关系图2-9 三角输出电压变化与时间(DLT DATA)关系图2-10 MCP1541输出电压与输出电流关系图2-11 MCP1525输出电压与输出电流关系图2-12 最大负载电流与电源电压关系图2-13 输入电流与输入电压关系图2-14 MCP1541 0.1Hz~10Hz噪音图2-15 开启瞬时时间图2-16 MCP1525负载瞬时响应图2-17 MCP1525 线性瞬时响应图2-18 压差电压与输出电流关系3.0 引脚功能名字功能输出引脚(V)基准输出OUT输入引脚(V)正输入电压IN接地引脚(V)负电源或接地SS4.0 详细描述4.01 输出电压输出电压就是引脚(V OUT)上输出的基准电压.4.0.2 操作(输入)电压输入电压是一个电压范围,它可以加到VIN 脚,使器件在VOUT脚产生指定的输出电压.4.0.3 输出电压漂移(TCVOUT)输出温度系数或电压漂移是测量输出电压(TCVOUT)将会随着温度变化偏离初始值的程度.在电特性中的值可以由以下等式计算得出:其中:MCP1525 VNOM=2.5VMCP1541 V NOM=4.096V4.0.4 压差电压这些器件压差电压是通过将VIN电压减到输出降低1%的那一点在这种情况下压差电压应等于:压差丢失电压受温度和负载电流的影响.在图2-18中,显示了压差电压相对输出电流得正的和负的对应关系当电流在0毫安以上时,压差电压为正值.在这种情况下,电压基准主要被VIN驱动. 当电流在0毫安以下时,压差电压为负值当输出电压负值更大时,输入电流IIN减小.在这种情况下,输出电流开始为电压基准提供所需的电能.4.0.5 线性度是衡量输入电压V IN变换对应会改变输出电压V OUT变化多少的量被表示成V OUT/V IN,单位为V/V或ppm.例如,一个由VIN 脚500mA变化而引起的VOUT脚1V变化会得到VOUT/V IN等于2V/V或2ppm的结果.4.0.6 负载率VOUT/I OUT负载率是测量输出电压(VOUT)变化引起输出电流(I OUT)变化的量其单位为mV/mA.4.0.7 输入电流输入电流是从V IN到V SS的电流,不是输出引脚的负载电流.该电流受温度和输出电流的影响.4.0.8 输入电压抑制比输入电压抑制比是在输入电压超频的情况下输出电压与之对应的关系如图2-7所示,可以用下面的公式计算:4.0.9 长期输出稳定性长期输出稳定性是通过将设备暴露在125下,同时电路设计成图4-1形式,测量数据的稳定性在这个测试中,芯片的所有电特性都是25下周期测量的,如图2-9所示.4.0.10 输出电压滞后输出电压滞后是芯片在整个温度范围下工作时的输出电压的变化量滞后的数量可通过测量在温度从25到85再到25,或者从25到-40再到25变化量来确定.5.0 应用信息5.1 旁路电容MCP1525和MCP1541电压基准不需要在V IN和V SS间加输入电容,但是为了增加系统稳定性和减少输入电压瞬时噪音,还是推荐使用一个0.1F的陶瓷电容,如图5-1所示.这个电容必须尽量靠近器件(在1英尺距离内).5.2 负载电容从V OUT到V SS的输出电容作为对基准的频率补偿是不应该被省略的电容值因该在1.0F到10F 之间值稍大一点的输出电容器会略微改善基准输出的噪音,与此同时额外增加的负荷也会影响负载的快速响应5.3 印刷电路板布置考虑由于PC主板安装所带来的机械压力会使输出电压偏离其初始值SOT23-2封装的设备比TO-92封装的设备更容易受到压力的影响为减少和输出电压偏离有关的压力建议把基准安装的PC板的低压区例如板的边缘和拐角处6.0 典型应用电路6.1 基本电路配置MCP1525和MCP1541电压基准设备在所有应用中应如图5-1所示:如图5-1所示,输入电压通过一个0.1F的陶瓷电容连接在设备的V IN输入脚.如果输入电压有过多的噪音那么就需要这个电容. 0.1F的陶瓷电容会阻止近似1MHz到2MHz的噪音.低于这个频率的噪音会被电压基准阻止超过2MHz的噪音会超过电压基准的带宽因此不从输入通过设备传送给输出负载电容C L是用来稳定电压基准的.5.2 输出滤波如果电压基准的输出噪音对特定的应用来说很大,可以简单地通过一个外部的R/C网络和放大器来过滤.R/C网络是由一个需要的屏蔽频率来选择的,屏蔽频率等于:图5-2所显示的值(10到1F)的RC网络组成一个低通滤波器该滤波器的角频率为15.9Hz带有20dB/decade的衰减MCP606放大器应用电路的剩余部分隔离出这个低传送滤波器的负载这个放大器也提供额外的驱动能力并提供和电压基准相比更快的响应5.3 精度可调基准一个精度可调电压基准可按图5-3所示的电路设置:在这个电路中,MCP1541电压基准被用来驱动MCP41010数字电位器的电阻元件. MCP41010是256抽头10K可编程的电位器使用SPI TM接口这个可调基准的范围从接地到4.096V,每16mV为一增量5.4 负电压基准一个负精确电压基准通过使用MCP1525或MCP1541来产生如图5-4所示在这个电路中使用MCP606和两个等值的电阻实现电压隔离MCP1525电压基准的输出电压驱动R1,R1和MCP606放大器的反向输入连接.既然放大器的输入为0第二个10K电阻器被放置在放大器的反馈回路放大器的放大倍数为1因此输出电压就等于-2.5V.5.5 A/D转换器基准MCP1525和MCP1541为Microchip的10位,12位A/D系列转换器提供电压基准.图5-5显示MCP1541为MCP3201,一个12位的A/D转换器提供基准.使用Microchip的Filter Lab TM 软件来设计Sallen Key滤波器.要获得其他信息,请参阅AN699,”Anti-Aliasing,Analog Filters for Data Acquisition Systems”,DS00699封装信息封装标志信息。

NCP1581DR2G, 规格书,Datasheet 资料

NCP1581High Frequency Synchronous Step Down PWM Controller for Tracking ApplicationsThe NCP1581 controller IC is designed to provide a simple synchronous buck regulator for on −board DC to DC applications in a 14−pin SOIC. The NCP1581 is designed specifically for tracking applications by providing the track input.The NCP1581 operates at a fixed internal 400 kHz switching frequency allowing the use of small external components. The device features a programmable soft start set by an external capacitor,under −voltage lockout and output under −voltage detection that latches off the device when an output short is detected.Features•Power up Sequencing / Tracking •Enable Input•Internal 400 kHz Oscillator •Programmable Soft −Start•Fixed Frequency V oltage Mode •V oltage Mode Adaptive Deadtime •This is a Pb −Free DeviceApplications•Tracking Applications •Game Consoles•Computing Peripheral V oltage Regulators •Graphics Cards•General DC to DC ConvertersFigure 1. Typical Application CircuitNCP1581SOIC −14D SUFFIX CASE 751ANCP1581G AWLYWW A = Assembly Location WL = Wafer Lot Y = YearWW = Work WeekG= Pb −Free PackageMARKING DIAGRAMPIN CONNECTIONSSee detailed ordering and shipping information in the package dimensions section on page 13 of this data sheet.ORDERING INFORMATION(Top View)NC SS COMP NC VC HDRV PGNDLDRV GNDNC VCC NC VP FB 11NCP1581Circuit Description:Block DiagramFigure 2. Simplified Block DiagramV C CG N DCD R VD R VG N DC O M PF BS SV P /E NTable 1. PIN FUNCTION DESCRIPTIONPin Name Description1FB Inverting input to the error amplifier. This pin is connected to the output of the regulator via resistor divider to set the output voltage and provide feedback to the error amplifier.2VP/EN Dual function pin. Non inverting input to the error amplifier. Enable input.3NC No Connect4VCC This pin provides power for the internal blocks of the IC as well as powers the low side driver. A minimum of 0.1 m F, high frequency capacitor must be connected from this pin to power ground.5NC No Connect6LDRV Output driver for low side MOSFET.7GND IC ground for internal control circuitry.8PGND Power Ground. This pin serves as a separate ground for the MOSFET drivers and should be connected to the system’s power ground plane.9HDRV Output driver for high side MOSFET. The negative voltage at this pin may cause instability for the gatedrive circuit. To prevent this, a low forward voltage drop diode (e.g. BAT54 or 1N4148) is requiredbetween this pin and Power Ground.10VC This pin powers the high side driver.11NC No Connect12COMP Output of error amplifier. An external resistor and capacitor network is typically connected from this pin to ground to provide loop compensation.13SS Soft start. This pin provides user programmable soft−start function. Connect an external capacitor fromthis pin to ground to set the start up time of the output voltage.14NC No ConnectTable 2. ABSOLUTE MAXIMUM RATINGSRating Symbol min max Unit Main Supply Voltage Input V CC−0.320V Main Supply Voltage Input200 ns wide spikes, 400 kHz V CC_SPK−0.322V Supply Voltage for the High side driver V C−0.320V Supply Voltage for the High side driver 200 ns wide spikes, 400 kHz V C_SPK−0.322V VP/EN pin Voltage V P/EN−0.310 or V CC(Note 1)V FB pin Voltage V FB−0.310 or V CC(Note 1)VRating Symbol Value Unit Thermal Resistance, Junction−to−Ambient (Note 2)R thja90K/W Storage Temperature Range T stg−65 to 150°C Junction Operating Temperature T J0 to 150°CESD Withstand Voltage (Note 3) Human Body ModelMachine Model V ESD2.0200kVVMoisture Sensitivity Level MSL JEDEC Level 1 @ 260°CStresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.NOTE:All voltages are referenced to GND pin unless otherwise stated.1.Maximum = 10 V or V CC, whichever is lower.2.JEDEC High−K model3.This device series contains ESD protection and exceeds the following tests:Human Body Model (HBM) ±2.0 kV per JEDEC standard: JESD22−A114Machine Model (MM) ±200 V per JEDEC standard: JESD22−A115Table 3. RECOMMENDED OPERATING CONDITIONSSymbol Definition Min Max Units V CC Supply Voltage720V V C Supply Voltage Converter Voltage + 5 V, (Note 4)20V T J Junction Temperature0125°C NOTE:All voltages are referenced to GND pin.4.Depend on high side MOSFET V GSTable 4. ELECTRICAL SPECIFICATIONS Unless otherwise specified, V CC = V C = 12 V, 0°C < T J < 125°CParameter Symbol Test Condition Min Typ Max Units SUPPLY CURRENTV CC Supply Current (Static)I CC(Static)V P/EN = 0 V, No Switching 1.53mA V CC Supply Current (Dynamic)I CC(Dynamic)f SW = 400 kHz, C L = 1.5 nF1015mA V C Supply Current (Static)I C(Static)V P/EN = 0 V, No Switching0.050.1mA V C Supply Current (Dynamic)I C(Dynamic)f SW = 400 kHz, C L = 1.5 nF915mA UNDER VOLTAGE LOCKOUTV CC−Start−Threshold V CC UVLO (R)Supply voltage Rising 6.3 6.67.0V V CC−Stop−Threshold V CC UVLO (F)Supply voltage Falling 6.0 6.3 6.6V V CC−Hysteresis V CC (Hyst)Supply ramping up and down0.20.30.4V Enable−Start−Threshold V P/EN UVLO (R)Supply voltage Rising0.60.650.7V Enable−Stop−Threshold V P/EN UVLO (F)Supply voltage Falling0.560.60.66V Enable−Hysteresis V P/EN (Hyst)Supply ramping up and down40mV FB UVLO V FB UVLO FB ramping down0.30.40.5V OSCILLATORFrequency f SW370400430kHz Ramp Amplitude V RAMP(Note 5) 1.25V Min Duty Cycle D MIN V FB =1V, V P/EN= 0.8 V0% Max Duty Cycle D MAX f SW= 400 kHz, V FB= 0.6 V, V P/EN = 0.8 V838595% ERROR AMPLIFIERFB Input Bias Current I FB1V SS = 3 V−0.1−0.5m A FB Input Bias current I FB2V SS = 0 V64m A VP/EN Input Bias Current I VP/EN V SS = 3 V−0.1−0.5m A Transconductance gm4401300m mho Input Offset Voltage V OS V P/EN= 0.8 V, V COMP = 2.0 V−60+6mV VP/EN Common Mode Range V COMN(Note 5)0.6 1.5V ERROR AMPLIFIER DESIGN SPECIFICATIONS100m A OTA output current I OTA(SINK)V FB = 1.2 V, V P/EN = 1.0 V,V COMP = 2.0 V, (Note 5)OTA output current I OTA(SOURCE)V FB = 0.8 V, V P/EN = 1.0 V,100m AV COMP = 2.0 V, (Note 5)5.Guaranteed by Design but not tested in production.Table 5. ELECTRICAL SPECIFICATIONS Unless otherwise specified, V CC = V C = 12 V, 0°C < T J < 125°CParameterSymbolTest ConditionMinTypMaxUnitsSOFT START Soft Start Current I SS V SS = 0 V122232m A Soft Start Turn On SS (on)1.822.2VOUTPUT DRIVERS LO Drive Rise Time tr(Lo)C L = 1.5 nF (See Figure 3)2050ns HI Drive Rise Time tr(Hi)C L = 1.5 nF (See Figure 3)3060ns LO Drive Fall Time tf(Lo)C L = 1.5 nF (See Figure 3)2050nsHI Drive Fall Time tf(Hi)C L = 1.5 nF (See Figure 3)3060ns Dead Band Time t DEAD (See Figure 3)354590ns Adaptive DBT LevelVADT2.0VFigure 3. Definition of Rise/Fall Time and Deadband TimeTYPICAL CHARACTERISTICSFigure 4. V CC UVLO TEMPERATURE (°C)V C C (V )TYPICAL CHARACTERISTICSFigure 5. V P/EN UVLOFigure 6. FB UVLOTEMPERATURE (°C)TEMPERATURE (°C)1201008060402000.300.320.340.380.400.440.480.50Figure 7. Maximum Duty CycleFigure 8. Switching FrequencyTEMPERATURE (°C)TEMPERATURE (°C)12010080604020818385878991939512010080604020360370380390400410430440Figure 9. Error Amplifier Transconductance Figure 10. DeadtimeTEMPERATURE (°C)TEMPERATURE (°C)12010080604020400500600700900100011001300V P /E N (V )V F B (V )D M A X (%)f S W (k H z )g m (m m h o )t (n s )0.360.420.464208001200Detailed Description IntroductionThe NCP1581 is voltage mode PWM synchronouscontroller designated to drive two external N-channel MOSFETs. Switching frequency is fixed at 400 kHz. Outputvoltage is determined by feedback resistor divider andexternal reference voltage. Reference voltage input can beused to enabling and disabling operation and for trackingfunction.Under-Voltage LockoutThe undervoltage lockout circuit ensures that the IC doesnot start and work until V CC and V P/EN are over set thresholds. If these conditions are not fulfilled output driversare in the off state.Disable FunctionThe output voltage can be disabled by pulling the VP/ENpin below 0.6 V. At this time are output drivers in the offstate.Output VoltageOutput voltage can be set by an external resistor dividerand external reference voltage at VP/EN pin according toEquation(1):V OUT+V PńEN@ǒ1)R1R2Ǔ(eq. 1)where V P/EN is the external reference voltage at VP/EN pinthat is connected to noninverting input of error amplifier. R1and R2 resistors create voltage divider from output to FB pinthat is connected to inverting input of error amplifier.Absolute values of resistors R1 and R2 depend on the compensation network type. See discussion of compensation description for details.Inductor SelectionThe inductor selection is based on the output power, frequency, input and output voltages, and efficiency requirements. High inductor values cause low currentripple, slower transient response, higher efficiency andincreased size. Inductor design can be reduced to desiredmaximum current ripple in the inductor. It is good to havecurrent ripple (D I Lmax) between 20% and 50% of the outputcurrent.For a buck converter, the inductor should be chosenaccording to Equation (2).L+ǒV OUTf SW@D I Lmax Ǔǒ1*V OUT VINmaxǓ(eq. 2)Output Capacitor SelectionThe output voltage ripple and transient requirements determine the output capacitor type and value. The important parameter for the selection of the output capacitor is equivalent serial resistance (ESR). If the capacitor has low ESR, it often has sufficient capacity for filtering as well as an adequate RMS current rating.The value of the output capacitor should be calculated using the following equation:C OUT wD I L8@f SW@(D V OUT*D I L@ESR)(eq. 3) For a higher switching frequency, it is suitable to use a multilayer ceramic capacitor (MLCC) with very low ESR. The advantages are small size, low output voltage ripple and fast transient response. The disadvantage of the MLCC type is the requirement to use a Type III compensation network. Input Capacitor SelectionThe input capacitor is used to supply current pulses while the high side MOSFET is on. When the MOSFET is off, the input capacitor is being charged. The value of this capacitor can be selected with the Equation (4):C IN wI OUT@V OUTV IN@ǒ1*V OUT V INǓf SW@D V IN(eq. 4)where D V IN is the input voltage ripple and the recommended value is about 2–5% of V IN. The input capacitor must be able to handle the input ripple current.Its value should be calculated using Equation (5):I RMS+I OUT@V OUT@ǒ1*V OUT V INǓV INǸ(eq. 5)Power MOSFET SelectionThe NCP1581 uses two N-channel MOSFETs. They can be primarily selected according to R DS(ON), maximum drain to source voltage, and gate charge. R DS(ON)impacts conductive losses and gate charge impacts switching losses. The low side MOSFET is selected primarily for conduction losses, and the high side MOSFET is selected to reduce switching losses especially when the output voltage is less than 30% of the input voltage. The drain to source breakdown voltage must be higher than the maximum input voltage. Conductive power losses can be calculated using the following Equations (6) and (7):P COND−HIGHFET+I OUT2@R DS(ON)@V OUTV IN(eq. 6) P COND−LOWFET+I OUT2@R DS(ON)@ǒ1*V OUT V INǓ(eq. 7)Switching losses are dependent on the drain to source voltage at turn-off state, output current, and switch-on and switch-off times, as is shown by Equation (8).P SW+V DS(OFF)2@(t ON)t OFF)@f SW@I OUT(eq. 8) t ON and t OFF times are dependent on the transistor gate charge.The MOSFET output capacitance loss is caused by the charging and discharging during the switching process and can be computed using Equation (9).P COSS+C OSS@V IN2@f SW2(eq. 9)where C OSS = C DS + C GS.Some power dissipation is caused by the reverse recovery charge in the low side MOSFET body diode, which conducts at dead time. This charge is needed to close the diode. The current from the input power supply flows through the high side MOSFET to the low side MOSFET body diode. This power dissipation can be calculated using the following Equation (10):P QRR+Q RR@V IN@f SW(eq. 10) Q RR is the diode recovery charge as given in the manufacturer’s datasheet. For some types of MOSFETs, this dissipation may be dominant at high input voltages. It is necessary to take care when selecting a MOSFET. An external Schottky diode across the low side MOSFET can be used to eliminate the reverse recovery charge power loss. The Schottky diode’s forward voltage should be lower than that of the body diode, and reverse recovery time (t rr) should be lower then that of the body diode. The Schottky diode’s capacitance loss can be calculated as shown in Equation(11).P C(schottky)+C schottky@V IN2@f SW2(eq. 11)Adaptive DeadtimeThe NCP1581 includes voltage mode adaptive dead time feature. This block waits for full turn off of the one of MOSFETs before the second one can be turned on. Detection is based on driver voltage, when this voltage drops below V ADT second driver can be turned on. There is fixed time t DEAD between turn off detection and internal logical turn on signal that increase safety. There can’t be used additional gate resistors due to voltage base detection, because these resistors would create voltage divider with driver’s pull down transistor and correct turn off detection is impossible. Gate resistors may be used only if MOSFETs turn off time is at all operation conditions shorter than t DEAD. MOSFETs’ timing diagram can be seen at Figure 11.Figure 11. MOSFETs Timing DiagramR DS R R DS (ON R R R DS (ON Soft StartThe soft start time is set by a capacitor connected between the SS pin and ground. This function is used for controlling the output voltage slope and limiting start-up currents. The start-up sequence initiates when the Power On Ready (POR)internal signal rises to logic level high. That means the supply voltage and V P/EN voltage are over the set thresholds.The soft start capacitor is charged by a 22 m A current source.If POR is low, the SS pin is internally pulled to GND, whichmeans that the NCP1581 is in a shutdown state. The SS pin voltage (0 V to 2 V) controls the internal current source (64 m A to 0 m A) with a negative linear characteristic. This current source injects current into the resistor (25 k W )connected between the FB pin and the negative input of the error amplifier and into the external feedback resistor network. V oltage drop on these resistors is over 1.6 V , which is enough to force the error amplifier into a negative saturation state and to block switching.When the soft start pin reaches around 1.2 V (exact value depends on feedback and compensation network and on the soft start capacitor; a larger soft start capacitor and a lower compensation capacity decrease this level), the IC starts switching. The impact of the controlled current source decreases and the output voltage starts to rise. When the soft start capacitor voltage reaches 2 V , the output voltage is at nominal value.The soft start time must be at least 10 times longer than the time needed to charge the compensation network from the output of the error amplifier. If the soft start time is not long enough, the soft start sequence would be faster than the charging compensation network and the IC would start without slowly increasing the output voltage. The soft start capacitance can be calculated using Equation 12:C SS +22@10−6@T SS(eq. 12)Figure 12. Start-up SequenceV CC = V V V V V Internal I V V Start to Pre-biased OutputThe NCP1581 is able to start up into a pre-biased output capacitor. The low side MOSFET does not turn on before the output voltage is at set value. During this time, the energy is not discharged by the low side MOSFET (current flows through low side MOSFET body diode) until the soft start sequence ends.Figure 13. Start-up to Pre-biased OutputV outV SSV LDRVV HDRVShort Circuit ProtectionThe output of convertor with NCP1581 is protected against short circuit conditions. This protection is sensing output voltage through feedback divider on FB pin. On thispin is comparator that compares FB voltage to 0.4 V . If FB voltage is below 0.4 V then IC goes to latch state and switch output drivers to off state. Latch state can be released by decrease V CC or V P/EN voltage below threshold.Figure 14. Short Circuit Protection (Start Up,Short, Latch, Latch Release and New Start-up)V CC V V V V VCompensation CircuitThe NCP1581 is a voltage mode buck converter with a transconductance error amplifier compensated by an external compensation network. Compensation is needed to achieve accurate output voltage regulation and fast transient response. The goal of the compensation circuit is to provide a loop gain function with the highest crossing frequency and adequate phase margin (minimally 45°).The transfer function of the power stage (the output LC filter) is a double pole system. The resonance frequency of this filter is expressed as follows:f PO +12@p @L @C OUTǸ(eq. 13)One zero of this LC filter is given by the output capacitance and output capacitor ESR. Its value can be calculated using the following equation:f Z0+12@p @C OUT @ESR(eq. 14)The next parameter that must be chosen is the zero crossover frequency f 0. It can be chosen to be 1/10–1/5 of the switching frequency. These three parameters show the necessary type of compensation that can be selected from Table 6.Table 6. COMPENSATION TYPESZero Crossover Frequency ConditionCompensation TypeTypical Output Capacitor Typef P0 < f Z0< f 0 < f SW /2Type II (PI)Electrolytic, Tantalum f P0 < f 0< f Z0 < f SW /2Type III (PID) Method I Tantalum, Ceramicf P0 < f 0 < f SW /2 < fZ0Type III (PID) Method IICeramicCompensation Type II (PI)This compensation is suitable for low-cost electrolytic capacitors. The zero created by the capacitor’s ESR is a few kHz, and the zero crossover frequency is chosen to be 1/10of the switching frequency. Components of the PI compensation (Figure 15) network can be specified by the following equations:Figure 15. PI compensation (Type II)V C2*R C1+2@p @f 0@L @V RAMP @V OUTESR @V IN @V P ńEN @gm (eq. 15)C C1+10.75@2@p @f P0@R C1C C2+1p @R C1@f SWR1+V OUT *V P ńENV P ńEN@R2V RAMP is the peak-to-peak voltage of the oscillator ramp,and gm is the transconductance error amplifier gain.Capacitor C C2 is optional.Compensation Type III (PID)Tantalum and ceramic capacitors have lower ESR than electrolytic capacitors, so the zero of the output LC filter goes to a higher frequency above the zero crossover frequency. This situation needs to be compensated by the PID compensation network that is shown in Figure 16.Figure 16. PID Compensation (Type III)C FB1R There are two methods to select the zeros and poles of the compensation network. The first one (method I) is usable for tantalum output capacitors, which have a higher ESR than ceramics, and its zeros and poles can be calculated as shown below:f Z1+0.75@f P0(eq. 16)f Z2+f P0f P2+f Z0f P3+f SW 2The second one (method II) is for ceramic capacitors:f Z2+f 0@1*sin q max 1)sin q max Ǹ(eq. 17)f Z1+0.5@f Z2f P3+0.5@f SWf P2+f 0@1)sin q max 1*sin q maxǸThe remaining calculations are the same for both methods.R C1uu 2gm (eq. 18)C FB1+2@p @f 0@L @V RAMP @C OUTV IN @R C1C C1+12@p @f Z1@R C1C C2+12@p @f P3@R C1R FB1+12@p @C FB1@f P2R1+12@p @C FB1@f Z2*R FB1R2+V P ńENV OUT *V P ńEN@R1To check the design of this compensation network, the following equation must be true:R1@R2@R FB1R1@R FB1)R2@R FB1)R1@R2u 1gm(eq. 19)If it is not true, then a higher value of R C1 must be selected.ORDERING INFORMATIONDevicePackage Shipping †NCP1581DR2GSOIC −14(Pb −Free)2500 / Tape & Reel†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.PACKAGE DIMENSIONSSOIC −14CASE 751A −03ISSUE JNOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: MILLIMETER.3.DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION.4.MAXIMUM MOLD PROTRUSION 0.15 (0.006)PER SIDE.5.DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127(0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.SBM0.25 (0.010)AST SEATING PLANEDIM MIN MAX MIN MAX INCHESMILLIMETERS A 8.558.750.3370.344B 3.80 4.000.1500.157C 1.35 1.750.0540.068D 0.350.490.0140.019F 0.40 1.250.0160.049G 1.27 BSC 0.050 BSC J 0.190.250.0080.009K 0.100.250.0040.009M 0 7 0 7 P 5.80 6.200.2280.244R0.250.500.0100.019____DIMENSIONS: MILLIMETERSSOLDERING FOOTPRINT**For additional information on our Pb −Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates,and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATION。

淸江连接器C1581系列商品说明书

Reference Informations:*Used in CJT C1581HFB,C1581HFC series HousingOrdering information & Specifications:Unit:mmReference Informations:*Used in CJT C1581HFB,C1581HFC series HousingOrdering information & Specifications:Unit:mmReference Informations:*Material:Nylon 66,UL94V-2*C1581HMB(Suitable Terminal:C1581M-T(-L))*C1581HFB(Suitable Terminal:C1581F-T(-L))*Color:NaturalOrdering Information:C1581HFB-XP - *** 1 21.Part No.2.Material:(blank):Nylon 66,UL94V-2/Natural V0:Nylon 66,UL94V-0/WhiteGWT:Nylon 66,UL94V-0,GWT 750°COrdering Information:C1581HMB-XP - *** 1 21.Part No.2.Material:(blank):Nylon 66,UL94V-2/Natural V0:Nylon 66,UL94V-0/WhiteGWT:Nylon 66,UL94V-0,GWT 750°CReference Informations:*Material:Nylon 66,UL94V-2*C1581HMB(Suitable Terminal:C1581M-T(-L))*C1581HFB(Suitable Terminal:C1581F-T(-L))*Color:NaturalOrdering Information:C1581HFB-2xXP - *** 1 21.Part No.2.Material:(blank):Nylon 66,UL94V-2/Natural V0:Nylon 66,UL94V-0/WhiteGWT:Nylon 66,UL94V-0,GWT 750°COrdering Information:C1581HMB-2xXP - *** 1 21.Part No.2.Material:(blank):Nylon 66,UL94V-2/Natural V0:Nylon 66,UL94V-0/WhiteGWT:Nylon 66,UL94V-0,GWT 750°CReference Informations:*Material:Nylon 66,UL94V-2*C1581HMB(Suitable Terminal:C1581M-T(-L))*C1581HFB(Suitable Terminal:C1581F-T(-L))*Color:NaturalOrdering Information:C1581HFB-3xXP - *** 1 21.Part No.2.Material:(blank):Nylon 66,UL94V-2/Natural V0:Nylon 66,UL94V-0/WhiteGWT:Nylon 66,UL94V-0,GWT 750°COrdering Information:C1581HMB-3xXP - *** 1 21.Part No.2.Material:(blank):Nylon 66,UL94V-2/Natural V0:Nylon 66,UL94V-0/WhiteGWT:Nylon 66,UL94V-0,GWT 750°CReference Informations:*Material:Nylon 66,UL94V-2*C1581HMC(Suitable Terminal:C1581M-T(-L))*C1581HFC(Suitable Terminal:C1581F-T(-L))*Color:NaturalOrdering Information:C1581HFC-XP - *** 1 21.Part No.2.Material:(blank):Nylon 66,UL94V-2/Natural V0:Nylon 66,UL94V-0/WhiteGWT:Nylon 66,UL94V-0,GWT 750°COrdering Information:C1581HMC-XP - *** 1 21.Part No.2.Material:(blank):Nylon 66,UL94V-2/Natural V0:Nylon 66,UL94V-0/WhiteGWT:Nylon 66,UL94V-0,GWT 750°CReference Informations:*Material:Nylon 66,UL94V-2*C1581HMC(Suitable Terminal:C1581M-T(-L))*C1581HFC(Suitable Terminal:C1581F-T(-L))*Color:NaturalOrdering Information:C1581HFC-2xXP - *** 1 21.Part No.2.Material:(blank):Nylon 66,UL94V-2/Natural V0:Nylon 66,UL94V-0/WhiteGWT:Nylon 66,UL94V-0,GWT 750°COrdering Information:C1581HMC-2xXP - *** 1 21.Part No.2.Material:(blank):Nylon 66,UL94V-2/Natural V0:Nylon 66,UL94V-0/WhiteGWT:Nylon 66,UL94V-0,GWT 750°CReference Informations:*Material:Nylon 66,UL94V-2*C1581HMC(Suitable Terminal:C1581M-T(-L)) *C1581HFC(Suitable Terminal:C1581F-T(-L)) *Color:NaturalOrdering Information:C1581HFC-3xXP - ***1 21.Part No.2.Material:(blank):Nylon 66,UL94V-2/NaturalV0:Nylon 66,UL94V-0/WhiteGWT:Nylon 66,UL94V-0,GWT 750°C Ordering Information:C1581HMC-3xXP - ***1 21.Part No.2.Material:(blank):Nylon 66,UL94V-2/NaturalV0:Nylon 66,UL94V-0/WhiteGWT:Nylon 66,UL94V-0,GWT 750°C。

L1581D资料

ABSOLUTE MAXIMUM RATINGSz Input Supply Voltage, V IN Control Input Voltage, V CTRL7V13.2Vz Operating JunctionTemperature Range, T J0 to 125 °Cz Power Dissipation, P D InternallyLimitedz Storage TemperatureRange, T STG-40 to 150 °Cz Thermal Resistance Junction to Case, θJC 3 °C/Wz Lead Temperature, T LEAD(Soldering, 10 Seconds) 260 °Cz Thermal ResistanceJunction to Ambient, θJA60 °C/WELECTRICAL CHARACTERISTICS (Unless otherwise specified, V out = V sns , V adj = 0V , C ctl = C in= C out =10 uF,T J = 25 °C)Parameter Symbol Test Conditions Typical LimitsV CTRL=4.5V, V IN=2.05V, I OUT=10mA 1.237V~1.263VReference Voltage(1) (Adj. Voltage Versions) V REFV CTRL = 4.5V, 10mA < I OUT < 5A,V IN = 2.05V1.25V1.231V~1.269VDropout Voltage(1) (2) Minimum V IN V I - V O V CTRL = 4.75V, I OUT = 5A 0.54V 0.62V(Max) V CTRL = 5V, V IN = V OUT + 0.8V,I OUT=10mA± 1%Output Voltage(1) (Fixed Voltage Versions) V OUT VCTRL= 5V, 10mA < I OUT < 5A,V IN = V OUT + 0.8VV OUT± 1.5%Line Regulation(1)REG(LINE)V CTRL = 4.5V to 12V, V IN = (V OUT+0.8V) to 5.5V, I OUT = 10mA1.0mV 3.0mVLoad Regulation REG(LOAD)V CTRL = 4.5V, V IN = (V OUT+0.8V) ,I OUT = 10mA ~ 5A1.0mV 5.0mVThermal Regulation(6)REG(Thermal) 0.002% / W0.02% / WMinimum LoadCurrent(4)I O V CTRL = 5V, V IN = V OUT+0.8V 5mA 10mAAdjust Pin Current I ADJ V CTRL = 4.5V, V IN = V OUT+0.8V,I OUT = 10mA50µA 120µAControl Pin Current(3)I CTRL V CTRL = 4.5V, V IN = V OUT+0.8V,I OUT = 5A33mA 120mACurrent Limit I CL V CTRL = 4.5V, V IN = V OUT+0.8VΔV OUT = 100mV 5.1A(Min)PIN FUNCTIONSNO FUNCTIONDESCRIPTION1 Sense This pin is the positive side of the reference voltage for the device. Withthis pin it is possible to Kelvin sense the output voltage at the load. 2 Adjust This pin is the negative side of the reference voltage for the device. Transient response can be improved by adding a small bypass capacitorfrom the adjust pin to ground.3 Output This is the power output of the device, and is electrically connected tothe TAB.4 ControlThis pin is the supply pin for the control circuitry for the device. The current flow into this pin will be approximately 1% of the output. For thedevice to regulate, the voltage at this pin must be between 1.0V and 1.3V greater than the output voltage (see dropout specifications).5 Input This is the collector input to the power device of the L1581. The output load current is supplied through this pin. For the device to regulate, thevoltage on this pin must be between 0.1V and 0.7V greater than theoutput, depending upon load current (see dropout specifications).。

SPC58NH-DISP开发板用户手册说明书

UM2697User manualSPC58NH-DISP discovery boardIntroductionThe SPC58NH-DISP discovery board is a standalone hardware platform to evaluate and develop applications with theSPC58NH92C5, packaged in a FPBGA386 microcontroller at budget price.This document provides information about the hardware architecture and how to configure the jumpers to enable specific functions.SPC58NH-DISP discovery board 1SPC58NH-DISP discovery boardThe SPC58NH-DISP discovery board is based on the microcontroller SPC58NH92C5, a high performancee200z4d triple core 32-bit Power Architecture technology CPU, 200 MHz core frequency with 10496 KB on chipFlash (10240 KB code Flash + 256 KB data Flash) in an FPBGA386 package.The several peripherals such as DSPI, LIN (LIN and UART), FlexRay, CAN-FD, two independent ethernet ports(10/100 Mbps and 1 Gbps), make the SPC58NH-DISP an excellent starter kit for the SW designer to quicklyevaluate the microcontroller as well as to develop and to debug applications.Free ready-to-run application firmware examples are available inside SPC5Studio web page (http//:/spc5studio) to quickly support evaluation and development.The PCB, the components and all HW parts assembled in this board meet the requirements of the applicableRoHS directives.1.1Interfaces and connectors• 1 ethernet port 10/100 Mbps• 1 ethernet port 1 Gbps•eMMC•SD card reader•HyperFlash and HyperRam• 3 CAN FD ports with transceiver DB9 connector•12 CAN port (GPIO level, 2 connectors)• 4 x I²C connector• 1 LIN and 1 K-Line with transceivers• 2 FlexRay channels (a single transceiver is shared with jumpers)• 2 UART channels with a DB9 and connector 4x0.1”•USB to UART (with opto-coupler option)•1xST33xx connector•JTAG (header 2x7 0.1” pin)•RESET push button• 3 user push buttons• 4 user LEDs• 2 trimmers to ADC (fast ADG evaluation)•LCD TFT display (320 x 240) with touch screen (option)•12 V DC power supply (external PSU)•40 MHz and 32.768 KHz crystalsHardware description 2Hardware description2.1Power supplyFigure 1 shows the PSU block diagram.Figure 1. PSU block diagramThe DC input source is 12 V DC: L5963 is used to generate 3.3 V (VDD_HV_xxx), 1.2 V (VDD_LV_xx) and 3.3 Vfor ADC section. A linear regulator is used to generate 5 V for ADC.The LEDs LD2, LD3, LD4, and LD5 are used to check the output of each voltage regulator and 12 V input source.A resettable fuse (F1) protects the application against the overload or short-circuit.2.2Microcontroller2.2.1JTAGA standard JTAG connector 14x0.1” is available for programming and debugging.Figure 2.JTAG2.2.2ResetFigure 3 shows the reset circuit.Figure 3.ResetThe reset signal level is driven to low level when:•VDD_HV is lower than a fixed level. This feature is used to monitor the VDD_HV level and then to resetthe microcontroller when the level is out of specification. This feature allows to set the reset only when the VDD_HV is stable.•the pushbutton is pressed (manual reset); the reset pulse width is fixed.Microcontroller2.3Ethernet 10/100 MbpsSection 2.3 shows the ethernet 10-100 Mbps communication channel.Figure 4.Ethernet 10/100 MbpsJP15 allows configuring the communication in MII or RMII mode.The current absorption of this section can be estimated by removing SB7 then applying a low impedance current meter or a current probe.Ethernet 10/100 Mbps2.4Ethernet 1 GbpsThe ethernet 1 Gbps section is depicted here below.Figure 5.Ethernet 1 GbpsThe resistors from R85 to R84, from R88 to R91, from R95 to R98 and from R100 to R103 are used to configure the device.With SB9 close and SB8 left open, the 1V2_ETH supply voltage is controlled by an integrated LDO and anexternal MOSFET. The user can exclude the LDO regulator and connect the 1V2_ETH to the 1.2 V source form the PSU section setting SB9 open and SB8 close.Ethernet 1 Gbps2.5eMMC and μSDFigure 6 and Figure 7 are showing the eMMC and µSD card reader section respectively.From the microcontroller, the signals Data 0÷3, CMD, CLK and FBCLK are shared among these sections and this means only one section can be active at a time.These signals must be connected to the active section by selecting the jumpers from JP17 to JP22 properly: see Figure 8.Figure 6.eMMC cardFigure 7.μSD cardeMMC and μSDFigure 8.eMMC and μSD jumpers configuration2.6Octal SPIThe OctalSPI section is visible in Section 2.6 . In this application the OctalSPI is connected to a HyperFlash and HyperRAM device.The microcontroller ports PF[4] and PN[12] are used to drive CS1# and CS2#.Figure 9.HyperFlash and HyperRAMOctal SPI2.7LIN and K-LineLIN and K-Line channels with the dedicated transceivers are described in the Figure 10.Figure 10.LIN and K-Line2.8Flex RayFlex Ray section is reported in Section 2.8 ; JP33, JP34 and JP35 allow selecting which channel from the microcontroller is connected to the transceiver.Figure 11.Flex RayLIN and K-Line2.9I²CFour I²C channels are available. A pull-up resistor is connected to each line and a jumper allows disconnecting it.Figure 12.I²C2.10CAN-FDThree CAN-FD channels with fast transceivers are connected to DB9 connectors. Further 6 + 6 channels are connected to 2 connectors without transceivers (GPIO level).Figure 13.CAN-FDI²C2.11UARTTwo UART channels with transceiver are available and connected to a 2x4 connector. The channel T1 (ports PL[0] and PL[1]) is connected to J5 (DB9 connector).Figure 14.UART2.12USB to UARTThis section shows a USB to UART communication channel. An option allows to include opto-couplers in order to have the USB port electrically insulated with respect to all the sections.Figure 15.USB to UARTUART2.13ST33 connectorThe aim of this connector is to allow plugging an evaluation board to evaluate and to demonstrate security features.Figure 16.ST33 connector2.14User interfaceThe user interface section includes 3 pushbuttons, 4 LEDS for user purpose, to simplify the debug and in addition to have a user interface port.Two potentiometers allow the evaluation of the ADC module; each potentiometer is connected to the VDD_HV_ADR supply source, it is the reference level of the ADC converters in the microcontroller.Figure 17.User interfaceST33 connector2.15LCDA display with SPI can be plugged in the board using two male pin arrays (one of them is used only as mechanical support). Figure 18 shows how the signals are connected.Figure 18.LCD moduleLCD3PCB layoutThe PCB layout is reported in Figure 19.Some copper tracks have been placed paying attention to have the same mechanical length and a specificimpedance; in detail the critical paths involve the ethernet 1 Gbps - ethernet 10/100 Mbps sections as well as the eMMC and the Hyper bus signals.Figure 19.PCB layoutPCB layoutRevision historyTable 1. Document revision historyContentsContents1SPC58NH-DISP discovery board (2)1.1Interfaces and connectors (2)2Hardware description (3)2.1Power supply (3)2.2Microcontroller (4)2.2.1JTAG (4)2.2.2Reset (4)2.3Ethernet 10/100 Mbps (5)2.4Ethernet 1 Gbps (6)2.5eMMC and μSD (7)2.6Octal SPI (8)2.7LIN and K-Line (9)2.8Flex Ray (9)2.9I²C (10)2.10CAN-FD (10)2.11UART (11)2.12USB to UART (11)2.13ST33 connector (12)2.14User interface (12)2.15LCD (13)3PCB layout (14)Revision history (15)List of figuresList of figuresFigure 1. PSU block diagram (3)Figure 2. JTAG (4)Figure 3. Reset (4)Figure 4. Ethernet 10/100 Mbps (5)Figure 5. Ethernet 1 Gbps (6)Figure 6. eMMC card (7)Figure 7. μSD card (7)Figure 8. eMMC and μSD jumpers configuration (8)Figure 9. HyperFlash and HyperRAM (8)Figure 10. LIN and K-Line (9)Figure 11. Flex Ray (9)Figure 12. I²C (10)Figure 13. CAN-FD (10)Figure 14. UART (11)Figure 15. USB to UART (11)Figure 16. ST33 connector (12)Figure 17. User interface (12)Figure 18. LCD module (13)Figure 19. PCB layout (14)IMPORTANT NOTICE – PLEASE READ CAREFULLYSTMicroelectronics NV and its subsidiaries (“ST”) reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST’s terms and conditions of sale in place at the time of order acknowledgement.Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers’ products.No license, express or implied, to any intellectual property right is granted by ST herein.Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.ST and the ST logo are trademarks of ST. For additional information about ST trademarks, please refer to /trademarks. All other product or service names are the property of their respective owners.Information in this document supersedes and replaces information previously supplied in any prior versions of this document.© 2021 STMicroelectronics – All rights reserved。

一种USB2.0数据传输的实现方式

一种USB2.0数据传输的实现方式摘要:USB (Universal Serial Bus,通用串行总线)是外围设备与计算机进行连接的新型接口,其诞生对计算机外设连接技术产生重大变革。

对Philips公司的工业级USB2.0控制芯片ISP1581的性能特点作了介绍,并重点讨论了其硬件电路及固件程序的设计。

此外还简要提及了其上层程序的编写。

关键词:USB2.0;ISP1581;DMA传输中图分类号:TP301 文献标识码:A 文章编号:1672-7800(2011)09-0040-030 引言??通用串行总线USB(Universal Serial Bus)接口是近年来开始普遍应用于PC领域的新型接口;同时,USB2.0在USB1.1的基础上又有了质的提高,其理论速度可以达到480Mbps。

??目前市场上供应的USB2.0控制器主要有两种:带USB 接口的单片机和纯粹的USB接口芯片。

但此类芯片基本上用于商业领域,无法适用工控领域的恶劣环境;纯粹的USB 接口芯片仅处理USB通信,必须有个外部微控制器/处理器来进行协议处理和数据交换。

纯粹的USB接口芯片主要特点是接口方便、可靠性强、适用范围广,尤其Philips公司提供的ISP1581芯片,能够在-40℃~+85℃的温度范围内正常工作,十分适合工控领域数据传输的需要。

??1 ISP1581的芯片性能特点??ISP1581是一款性能非常出众的USB2.0控制器,它实现了USB2.0/1.1物理层以及数据协议层需要完成的任务,接口速度可达12.5M字节/s或12.5M字/s;同时还做到可以与大部分类型的微控制器/处理器相连,非常适合做很多外围设备与PC的通讯接口。

其一些具体的性能特点如下:①ISP1581含有7个IN端点,7个OUT端点和2个控制端点。

芯片的工作频率为12MHZ,同时内部集成了一个40×PLL时钟乘法器可产生480MHZ的内部抽样时钟;②通过Philips串行接口引擎(SIE)来完成所有USB协议层的功能,主要完成以下功能:同步方式的识别、并行/串行的转换、位填充/解除填充等。

一种基于ISP1581的USB2.0接口设计

一种基于ISP1581的USB2.0接口设计张华;代睿【摘要】本论述设计的USB2.0接口主要由高速通用串行总线USB2.0接口器件ISP1581和微处理器C8051F310构成。

以ISP1581为核心,所设计的USB2.0接口具有高速数据传输、即插即用,以及结构简单等优点。

给出了系统实现的硬件电路原理图和固件程序的各主要子程序的流程图。

【期刊名称】《甘肃科技纵横》【年(卷),期】2012(041)005【总页数】3页(P28-29,35)【关键词】USB2.0;ISP1581;C8051F310【作者】张华;代睿【作者单位】海军装备部,甘肃兰州730070;海军装备部,甘肃兰州730070【正文语种】中文【中图分类】TP334.220 引言通用串行总线USB(Universal Serial Bus)是近年来被广泛应用于现代电子系统的一种串行总线标准。

其协议主要有USB1.0和USB2.0两个版本。

在实际应用中,由于USB2.0接口具有高速数据传输等优点,从而逐渐取代了USB1.0接口的应用。

目前的USB2.0接口器件主要有两类:一类是带微控制器的接口器件;另一类是不带微控制器的接口器件,而需要一个外部的微控制器。

本设计使用的接口器件ISP1581属于后者,所设计的系统以C8051F310单片机为外部微控制器,控制ISP1581完成USB通信[1]。

1 接口硬件电路设计由C8051F310和ISP1581构成的USB2.0接口电路原理图如图1所示。

BUS_CONF下拉,即C8051F310和ISP1581的连接采用断开总线模式,这时AD[7:0]为本地微处理器多路复用地址/数据总线,DATA[15:0]只作DMA总线使用。

MODE0上拉,读和写选通信号为8051类型。

MODE1上拉,A0用来指示传送的地址或数据。

C8051F310的P2口与ISP1581的AD[7:0]相连。

ISP1581的复位、片选和与数据控制总线相关的引脚分别与 C8051F310的P1.0~P1.4引脚相连,(见图 1所示)。

APL1581中文资料

Ordering and Marking Information

APL1581

Assembly Material Handling Code Temperature Range Package Code Voltage Code

Package Code

F : TO-220-5 G : TO-263-5 U :TO-252-5

KA : SOP-8P

Temperature Range

C : 0 to 70°C

Handling Code

TR : Tape & Reel

Voltage Code :

15 : 1.5V

18 : 1.8V

25 : 2.5V

Blank : Adjustable Version

Assembly Material

The APL1581 series of high performance positive voltage regulators are designed for use in applications requiring very low dropout voltage at 5Amp.

The APL1581 can provide a output voltage at the range of 1.25V to 2.55V where both 5V and 3.3V voltage supplies are available.

Supply pin of the control circuitry, which must be always higher than VOUT for the device to regulate. (See electrical characteristics)

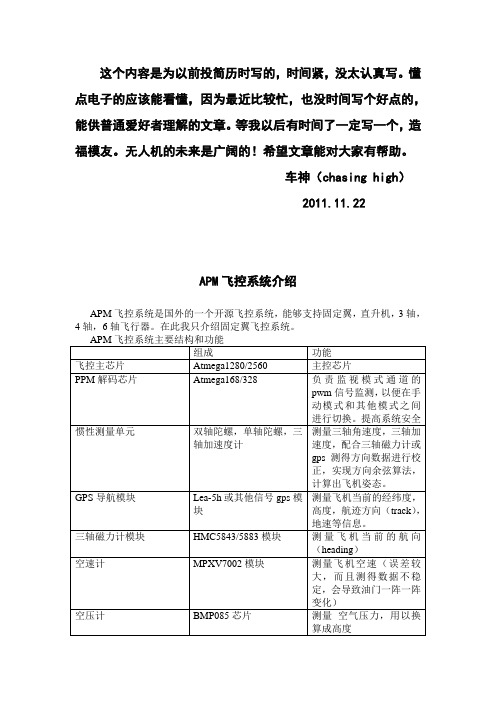

APM飞控介绍

这个内容是为以前投简历时写的,时间紧,没太认真写。

懂点电子的应该能看懂,因为最近比较忙,也没时间写个好点的,能供普通爱好者理解的文章。

等我以后有时间了一定写一个,造福模友。

无人机的未来是广阔的!希望文章能对大家有帮助。

车神(chasing high)2011.11.22APM飞控系统介绍APM飞控系统是国外的一个开源飞控系统,能够支持固定翼,直升机,3轴,4轴,6轴飞行器。

在此我只介绍固定翼飞控系统。

APM飞控系统主要结构和功能组成功能飞控主芯片Atmega1280/2560 主控芯片PPM解码芯片Atmega168/328 负责监视模式通道的pwm信号监测,以便在手动模式和其他模式之间进行切换。

提高系统安全惯性测量单元双轴陀螺,单轴陀螺,三轴加速度计测量三轴角速度,三轴加速度,配合三轴磁力计或gps测得方向数据进行校正,实现方向余弦算法,计算出飞机姿态。

GPS导航模块Lea-5h或其他信号gps模块测量飞机当前的经纬度,高度,航迹方向(track),地速等信息。

三轴磁力计模块HMC5843/5883模块测量飞机当前的航向(heading)空速计MPXV7002模块测量飞机空速(误差较大,而且测得数据不稳定,会导致油门一阵一阵变化)空压计BMP085芯片测量空气压力,用以换算成高度AD芯片ADS7844芯片将三轴陀螺仪、三轴加速度计、双轴陀螺仪输出温度、空速计输出的模拟电压转换成数字量,以供后续计算其他模块电源芯片,usb电平转换芯片等飞控原理在APM飞控系统中,采用的是两级PID控制方式,第一级是导航级,第二级是控制级,导航级的计算集中在medium_loop( ) 和fastloop( )的update_current_flight_mode( )函数中,控制级集中在fastloop( )的stabilize( )函数中。

导航级PID控制就是要解决飞机如何以预定空速飞行在预定高度的问题,以及如何转弯飞往目标问题,通过算法给出飞机需要的俯仰角、油门和横滚角,然后交给控制级进行控制解算。

ISP1581固件程序及其解析

两三年曾经在ADSP-TS101下用汇编语言写过ISP1581的固件程序,此前对于USB没有任何先验知识,协议又太厚,还是英文版的。

想认认真真的看完协议再写估计时间上不允许,所有我的固件程序是从Philips公司提供的示例程序开始的,摸着石头过河,前前后后大约花了一个月的时间终于把程序写出来并调试通过,也解决了一些不稳定的问题。

如今再有机会精读USB2.0协议,很多原来不明白的地方一下子清楚了,所以:如果时间允许,在写USB的固件程序前,最好阅读一下USB2.0的协议。

至少把第4,8,9章看一下。

废话不多说,下面就开始解析ISP1581的固件程序。

先看下文件结构:1. 在D14.h中主要定义了ISP1581的内部寄存器数据结构,要看懂这个文件必须和ISP1581的Datasheet结合起来。

2. dmadebug.c中定义了一个用于初始化ISP1581 DMA的函数,这个对于固件程序来说不是必须的,因此如果时间不允许的话,这个文件的分析就不做了。

3. i2c.c和i2c.h定义了一些IIC总线的操作,因为在Philips的设计中ISP1581的51系列微控制器通过IIC总线连接到其他处理器或者ASIC的。

这两个文件爱你对于固件程序来说也不是必须的,因此如果时间不允许的话,这两个文件的分析也不做的。

4. init.c中定义了一些系统初始化的操作,这个文件中定义的函数大都将在程序开始的时候被调用,用来完成微处理器以及ISP1581的初始化。

5. intrpt.c中定义了51系列微处理器的中断处理函数,其中主要包括一个定时中断和一个ISP1581的中断处理函数。

6. kernel.c和kernel.h两个文件为固件程序的main函数所在的文件,kernel.h 中定义了一系列的宏,在kernel.c中主要包括一个main函数和两个用于定时的函数。

7. REG51.h中定义了51系列微控制器的一些宏,主要包括IO和内部寄存器的定义。

IT-158 datasheet-201409

Available in Variety of Constructions

Available in a various of constructions, copper weights and glass styles, including standard(HTE), RTF and VLP copper foil.

Excellent thermal reliability and CAF resistance providing long-term reliability for industrial boards and automobile application.

Applications

PC and Notebook Memory Module Game Player Multilayer PCB Automobile Servers and Networking Telecommunications Heavy Copper Application

Industrial Approval

UL 94 V-0

IPC-4101C Spec / 99

RoHS Compliant

REV 09-14

ITEQ Laminate/ Prepreg : IT-158TC / IT-158BS

IPC-4101C Spec /99

LAMINATE (IT-158TC)

Friendly Processing and CAF Resistance

Friendly to PCB process that users can easily handle the process by current equipment and chemical.

Infineon TLI4971高精度无核电流传感器说明书

TLI4971 high precision coreless current sensor for industrial applications in 8x8mm SMD packageFeatures & Benefits∙ Integrated current rail with typical 220µΩ insertion resistance enables ultra-low power loss∙ Smallest form factor, 8x8mm SMD, for easy integration and board area saving∙ High accurate, scalable, DC & AC current sensing ∙ Bandwidth typical 240kHz enables wide range of applications∙ Very low sensitivity error over temperature (< 2.5%) ∙ Galvanic functional isolation up to 1150V peak V IORM ∙ V ISO 3500V RMS agency type-tested for 60 seconds per UL1577∙ Differential sensor principle ensures superior magnetic stray field suppression∙ Two independent fast Over-Current Detection (OCD)outputssCoreless current sensor in PG-TISON-8 packageDescriptionTLI4971 is a high precision miniature coreless magnetic current sensor for AC and DC measurements with analog interface and two fast over-current detection outputs.Infineon's well-established and robust monolithic Hall technology enables accurate and highly linear measurement of currents with a full scale up to ±120A. All negative effects (saturation, hysteresis) commonly known from open loop sensors using flux concentration techniques are avoided. The sensor is equipped with internal self-diagnostic feature.Typical applications are electrical drives and general purpose inverters.The differential measurement principle allows great stray field suppression for operation in harsh environments.Two separate interface pins (OCD) provide a fast output signal in case a current exceeds a pre-set threshold.The sensor is shipped as a fully calibrated product without requiring any customer end-of-line calibration.All user-programmable parameters such as OCD thresholds, blanking times and output configuration modes are stored in an embedded EEPROM memory.2) Semi-differential mode, non-ratiometric output sensitivityPin ConfigurationFigure 1 Pin layout PG-TISON-8-5The current I PN is measured as a positive value when it flows from pin 8 (+) to pin 7 (-) through the integrated current rail.Pin configurationTarget ApplicationsThe TLI4971 is suitable for AC as well as DC current measurement applications: ∙ Electrical drives∙ General purpose inverters ∙ Chargers∙ Current monitoring∙ Overload and over-current detection ∙ etc.Due to its implemented magnetic interference suppression, it is extremely robust when exposed to external magnetic fields. The device is suitable for fast over-current detection with a configurable threshold level. This allows the control unit to switch off and protect the affected system from damage, independently from the main measurement path.1 2 3 456 78+- I PNGeneral DescriptionThe current flowing through the current rail on the primary side induces a magnetic field that is differentially measured by two Hall probes. The differential measurement principle of the magnetic field combined with the current rail design provides superior suppression of any ambient magnetic stray fields. A high performance amplifier combines the signal resulting from the differential field and the internal compensation information provided by the temperature and stress compensation unit. Finally the amplifier output signal is fed into a differential output amplifier which is able to drive the analog output of the sensor.Depending on the selected programming option, the analog output signal can be provided either as: ∙Single-ended∙Fully-differential∙Semi-differentialIn single-ended mode, the pin VREF is used as a reference voltage input. The analog output signal is provided on pin AOUT. In fully-differential mode, both AOUT (positive polarity) and VREF (negative polarity) are used as signal outputs whereas VDD is used as reference voltage input. Compared to the single-ended mode, the fully-differential mode enables doubling of the output voltage swing.In semi-differential mode a chip-internal reference voltage is used and provided on VREF (output). The current sensing information is provided in a single-ended way on AOUT.For fast over-current detection, the raw analog signal provided by the Hall probes is fed into comparators with programmable switching thresholds.A user-programmable deglitch filter is implemented to enable the suppression of fast switching transients. The open-drain outputs of the OCD pins are active “low” and they can be directly combined into a wired-AND configuration on board level to have a general over-current detection signal.All user-programmable parameters such as OCD thresholds, deglitching filter settings and output configuration mode are stored in an embedded EEPROM memory.Programming of the memory can be performed in the application through a Serial Inspection and Configuration Interface (SICI). The interface is descripded in detail in the programming guide which can be found on the Infineon webside. Please contact your local Infineon sales office for further documentation. Standard Product Configuration∙The pre-configured full scale range is either set to ±120A, ±75A, ±50A or ±25A depending on the choosen product variant.∙The pre-configured output mode is set to semi-differential mode.∙The quiescent voltage is set to 1.65V.∙The OCD threshold of channel 1 is set to the factor 1.25 of the full scale range.∙The OCD threshold of channel 2 is set to the factor 0.82 of the full scale range.∙The pre-defined setting of the OCD deglitching filter time is set to 0µs.∙The sensor is pre-configured to work in the non-ratiometric mode.∙The sensitivity and the derived measurement range (full scale) can be reprogrammed by user according to the sensitivity ranges listed in Table 4.∙The sensor can be reprogrammed into single-ended operating mode or fully-differential mode by user without any recalibration of the device.∙The OCD thresholds and filter settings can be reprogrammed by the user according to the values listed in Table 6 and Table 7.∙For semi-differential uni-directional mode or ratiometric output sensitivity, please contact your local Infineon sales office.Block DiagramThe current flowing through the current rail on the primary side induces a magnetic field, which is measured by two Hall probes differentially. The differential measurement principle provides superior suppression of any ambient magnetic stray fields. A high performance amplifier combines the signal resulting from the differential field and the compensation information, provided by the temperature and stress compensation unit. Finally the amplifier output signal is fed into a differential output amplifier, which is able to drive the analog output of the sensor.Absolute Maximum RatingsTable 1 Absolute Maximum RatingsThermal equilibrium reached after 2 min.2)Tested with primary nominal rated current of 70A rms on Infineon reference PCB at High Frequency (HF).Thermal equilibrium reached after 2 min.3)Human Body Model (HBM), according to standard AEC-Q 100-0024)Accor ding to standard IEC 61000−4−2 e lectrostatic discharge immunity testStress above the limit values listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Maximum ratings are absolute ratings. Exceeding only one of these values may cause irreversible damage to the integrated circuit.Product Characteristics Table 2 Operating RangesTable 3 Operating ParametersFunctional Output DescriptionThe analog output signal depends on the selected output mode:∙Single-ended∙Fully-differential∙Semi-differentialSingle-Ended Output ModeIn single-ended mode VREF is used as an input pin to provide the analog reference voltage, V REF. The voltage on AOUT, V AOUT, is proportional to the measured current I PN at the current rail:V AOUT(I PN)=V OQ+S∙I PNThe quiescent voltage V OQ is the value of V AOUT when I PN=0. V OQ tracks the voltage on VREFV OQ(V REF)=V REFThe reference voltage can be set to different values which allow either bidirectional or uniderictional current sensing. The possible values of V REFNOM are indicated in Table 2.The sensitivity is by default non ratiometric to V REF. If ratiometricity is activated the sensitivity becomes as follows:S(V REF)=S(V REFNOM)∙V REF V REFNOMFully-Differential Output ModeIn fully-differential output mode, both VREF and AOUT are analog outputs to achieve double voltage swing: AOUT is the non-inverting output, while VREF is the inverting output:V AOUT(I PN)=V QAOUT+S∙I PNV REF(I PN)=V QREF−S∙I PNThe quiescent voltage is derived from the supply pins VDD and GND and has the same value on both AOUT and VREF:V QAOUT(V DD)=V QREF(V DD)=V DD2The sensitivity in the fully-differential mode can begenerally expressed as:S(V DD)diff=S(3.3V)diff∙V DD3.3VIn this mode, the quiescent voltages and thesensitivity are both ratiometric with respect to V DDif ratiometricity is enabled.Semi-Differential Output ModeIn semi-differential output mode, the sensor isusing a chip-internal reference voltage to generatethe quiescent voltage that is available on pin VREF(used as output).The analog measurement result is available assingle-ended output signal on AOUT. Thedependence of sensitivity and output offset onreference voltage is the same as described in single-ended output mode.The quiescent voltage is programmable at 3different values, V OQbid_1and V OQbid_2forbidirectional current and V OQuni for unidirectionalcurrent (see Table 4).Total error distributionFigure 3 shows the total output error at 0h (E TOTT)and over lifetime (E TOTL) over the full scale range forsensitivity range S1 (10mV/A).Table 4 Analog Output Characteristics2) Can be programmed by user.3) Values refer to semi-differential mode or single-ended mode, with VREF =1.65 V. In fully-differential mode the sensitivity value is doubled.4) Not subject to production test. Verified by design and characterization.5) Typical value in fully-differential mode, sensitivity range S66) Noise Density=RMS√ π2 ∗ BW[Hz]1Sensitivity[VA]Table 4 Analog Output Characteristics (cont’d)Fast Over-Current Detection (OCD)The Over-Current Detection (OCD) function allows fast detection of over-current events. The raw analog output of the Hall probes is fed directly into comparators with programmable switching thresholds. A user programmable deglitch filter is implemented to enable the suppression of fast switching transients. The two different open-drain OCD pins are active low and can be directly combined into a wired-AND configuration on board level to have a general over-current detection signal. TLI4971 supports two independent programmable OCD outputs, suited for different application needs.The OCD pins are providing a very fast response, thanks to independence from the main signal path. They can be used as a trap functionality to quickly shut down the current source as well as for precise detection of soft overload conditions.OCD pins external connectionThe OCD pins can be connected to a logic input pin of the microcontroller and/or the gate-driver to quickly react to over-current events. They are designed as open-drain outputs to easily setup a wired-AND configuration and allow monitoring of several current sensors outputs via only one microcontroller pin. OCD thresholdsThe symmetric threshold level of the OCD outputs is adjustable and triggers an over-current event in case of a positive or negative over-current. The possible threshold levels are listed in Table 6 and Table 7. The instruction for the settings is documented in the TLI4971 programming guide. OCD outputs timing behaviorBoth output pins feature a deglitch filter to avoid false triggers by noise spikes on the current rail. Deglitch filter settings can be programmed according to application needs. Available options are listed in Table 6 and Table 7.Figure 4 shows the OCD output pin typical behavior during an over-current event.Over-current Pulse 1: duration exceeds the over-current response time t D_OCDx + response time jitter Δt D_OCDx + deglitch filter time t deglitch. The OCD output voltage is set low until the current value drops below the OCD threshold.Over-current Pulse 2: duration does not exceed the over-current response time t D_OCDx and therefore no OCD event is generated.Over-current Pulse 3: duration exceeds the response time t D_OCDx + response time jitter Δt D_OCDx, but does not exceed the glitch filter time t deglitch and no OCD event is generated.Fast Over-Current Detection (OCD) Output ParametersTable 5 Common OCD Parameters2) Can be programmed by user.3) Pre-configured threshold level4) Time between primary current exceeding current threshold and falling edge of OCD1-pin at 50%.5) Not subject to production test. Verified by design and characterization.6) The specified deglitching timing is valid when input current step overtakes the threshold of at least 10%.2) Can be programmed by user.3) Pre-configured threshold level.4) Time between primary current exceeding current threshold and falling edge of OCD2-pin at 50%.5) Not subject to production test. Verified by design and characterization.6) The specified deglitching timing is valid when input current step overtakes the threshold of at least 10%.Undervoltage / Overvoltage detectionTLI4971 is able to detect undervoltage or overvoltage condition of its own power supply (V DD). When an undervoltage (V DD<U VLOH) or overvoltage (V DD>O VLOH) condition is detected both OCD pins are pulled down in order to signal such a condition to the user.The undervoltage detection on OCD pins is performed only if V DD > V DD,OCD.Both OCD pins are pulled down at start up. When V DD exceeds the undervoltage threshold U VLOH_R and the power on delay time t POR has been reached, the sensor indicates the correct functionality and high accuracy by releasing the OCD pins.Isolation CharacteristicsTLI4971 conforms functional isolation.2) After stress test according to qualification plan.3) Not subject to production test. Verified by design and characterization.4) Agency type tested for 60 seconds by UL according to UL 1577 standard.System integrationFor bandwidth limitation an external filter is recommended as shown in the above application circuits.Typical Performance CharacteristicsFigure 8 Typical error in sensitivity over temperature Figure 9 Typical offset drift over temperaturePackageThe TLI4971 is packaged in a RoHS compliant, halogen-free leadless package (QFN-like). PG-TISON-8 Package OutlineRevision HistoryMajor changes since the last revisionPublished byInfineon Technologies AG 81726 München, Germany © 2021 Infineon Technologies AG. All Rights Reserved.Do you have a question about this document?Email: ********************Document reference IMPORTANT NOTICEThe information given in this document shall in no event be regarded as a guarantee of conditions or chara cteristics (“Beschaffenheitsgarantie”) .With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.In addition, any information given in this document is subject to customer’s compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer’s products and any use of the product of Infineon Technologies in customer’s applications.The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer’s technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document withFor further information on the product, technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies office ( ).WARNINGSDue to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies’ products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.Edition 12-02-2021----Trademarks of Infineon Technologies AGµHVIC™, µIPM™, µPFC™, AU -ConvertIR™, AURIX™, C166™, CanPAK™, CIPOS™, CIPURSE™, CoolDP™, CoolGaN™, COOLiR™, CoolMOS™, CoolSET™, CoolSiC™, DAVE™, DI -POL™, DirectFET™, DrBlade™, EasyPIM™, EconoBRIDGE™, EconoDUAL™, EconoPACK™, EconoPIM™, EiceDRIVER™, eupec™, FCOS™, GaNpowIR™, HEXFET™, HITFET™, HybridPACK™, iMOTION™, IRAM™, ISOFACE™, IsoPACK™, LEDrivIR™, LITIX™, MIPAQ™, ModSTACK™, my -d ™, NovalithIC™, OPTIGA™, OptiMOS™, ORIGA™, PowIRaudio™, PowIRStage™, PrimePACK™, PrimeSTACK™, PROFET™, PRO -SIL™, RASIC™, REAL3™, SmartLEWIS™, SOLID FLASH™, SPOC™, StrongIRFET™, SupIRBuck™, TEMPFET™, TRENCHSTOP™, TriCore™, UHVIC™, XHP™, XMC™ Trademarks updated November 2015 Other Trademarks All referenced product or service names and trademarks are the property of their respective owners.。

B1581S资料

Features

• • • • • • Adjustable Output Down to 1.2V Fixed Output Voltages 2.5V, 3.0V 3.3V, and 5.0V Output Current of 5.0A Low Dropout Voltage 700mV Typ. Current & Thermal Limiting Standard 3-Terminal Low Cost TO-220, D2 Packages Similar to industry Standard EZ1581/CS5205

ul1581中文版.doc

电线电缆和软线参考标准REFERENCESTANDRDFORELECTRICAL WIRESCABLESAND FLEXIBLE CORDSUL1581-2001上海电缆研究所电线电缆信息中心前言A:本标准包含美国保险商实验所(UL)产品的跟踪服务时涉及的产品基本要求,些产品受下列条文的限制,且处于本标准适用范围之内。

这些要求是以可信的工程原理,研究成果。

试验数据和现场经验以及对制造安装和使用的问题的评估为依据而制定的。

这些依据来自向制造商,用户检验机构以及其它具有专业经验的人员咨询或是从他们处获的情报。

上述对产品的要求可能由于经验丰富的研究人员深入而必须或是有必要进行修订。

B:满足本标准对产品的要求是制造商产品继续获得UL认证的条件之一。

C:符合本标准条文的产品如果经检验发现还具有其它有损于本标准的安全水平的性能,则不一定认为符合本标准。

D:采用本标准规定不同的材料制成的产品或是具有与本标准规定不同的结构的产品,可按本标准的要求的含义进行检验和测试,如果性能基本相同,则认为该产品符合本标准。

E:UL按其宗旨履行职能时,不为制造商或是任何一方担当或开脱责任。

UL 的意见和调查结果是代表一种充分考虑到UL标准制定时实际运行的必要限制和工艺水平专业性评定,UL对此不负任何责任。

如果因使用,解释UL标准或是其它依据而造成的损失包括重大损失,UL不负任何责任和义务。

F:本UL标准规定的许多试验本身具有一定的危险性,因此在做些试验时应采取恰当的人员和设备防护措施。

导引1:范围1.1本标准包含橡皮绝缘电线电缆(UL44)热塑性料绝缘电线电缆(UL83)软线装置线(UL62)和用户引入电缆(UL854)等标准对于导体,绝缘,护套及其它护层的要求细则以及对于试样制备。

样品选取,温度处理和测量与计算方法的要求细则。

本标准的条文也被其它标准所引用。

1.2对于特定型号的电线电缆或软线的专用材料、结构、性能和标志的要求,载于相应的成品电缆标准中,本参考标准不包含这些内容。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Current limit is trimmed to ensure specified output current and controlled short-circuit current. On-chip thermal limiting provides protection against any combination of overload that would create excessive junction temperature.

VSENSE 1 ADJ (or GND) 2

VCNTL 3 VIN 4

8 VOUT 7 VOUT 6 VOUT 5 VOUT

SOP-8-P (Top View)

NC = No internal connection = Thermal Pad (connected to VOUT plane for better heat dissipation)

L : Lead Free Device

G : Halogen and Lead Free Device

15 APL1581-15 F/G/U : APL1581 XXXXX - Date Code

XXXXX

APL1581 KA :

APL1581 XXXXX

XXXXX - Date Code

Note: ANPEC lead-free products contain molding compounds/die attach materials and 100% matte tin plate termination finish; which are fully compliant with RoHS. ANPEC lead-free products meet or exceed the lead-free requirements of IPC/JEDEC J-STD-020C for MSL classification at lead-free peak reflow temperature. ANPEC defines “Green” to mean lead-free (RoHS compliant) and halogen free (Br or Cl does not exceed 900ppm by weight in homogeneous material and total of Br and Cl does not exceed 1500ppm by weight).

The APL1581 series of high performance positive voltage regulators are designed for use in applications requiring very low dropout voltage at 5Amp.

The APL1581 can provide a output voltage at the range of 1.25V to 2.55V where both 5V and 3.3V voltage supplies are available.

APL1581

DUAL INPUT LOW DROPOUT REGULATOR

Features

General Description

• Adjustable or Fixed Output • 520mV typ. Dropout at 5A in Dual Power

Voltage Mode • Remote Sense Pin Available • 2% Accuracy Over Temperature Range • Build-in Over Temperature Protection • Build-in Current Limit • 5 Pin TO-220 and TO-263, TO-252, SOP-8-P

Copyright © ANPEC Electronics Corp.

1

Rev. B.5 - Mar., 2008

APL1581

Pin Configuration

5

4

TAB is VOUT

3

2

1

VIN VCNTL VOUT ADJ (or GND) VSENSE

TAB is VOUT

Supply pin of the control circuitry, which must be always higher than VOUT for the device to regulate. (See electrical characteristics)

Power input pin of the regulator, which must be always higher than VOUT for the device to regulate. (See electrical characteristics)

150

°C

TSTG

Storage Temperature Range

-65 to +150

°C

TSDR

Maximum Lead Soldering Temperature, 10 Seconds

260

°C

Note 1: Absolute Maximum Ratings are those values beyond which the life of a device may be impaired. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

The APL1581 is available in both the through-hole and surface mount versions of the industry standard 5-Pin TO-220 and TO-263, TO-252, SOP-8P power packages.

5

VIN

4

VCNTL

3

VOUT

2

ADJ(or GND)

1

VSENSE

Front View of TO-220-5

Front View of TO-252-5

TAB is VOUT

5

VIN

4

VCNTL

3

VOUT

2

ADJ (or GND)

1

VSENSE

Front View of TO-263-5

Pin Description

Note 2: The maximum allowable power dissipation at any TA (ambient temperature) is calculated using: PD (max) = (TJ – TA) / θJA; TJ = 125°C. Exceeding the maximum allowable power dissipation will result in excessive die temperature.

Packages • Lead Free and Green Devices Available

(RoHS Compliant)

Applications

• Microprocessor Supplies • Chip Set Supplies • VGA Card Power • LCD Monitor Power

Copyright © ANPEC Electronics Corp.

2

Rev. B.5 - Mar., 2008

APL1581

Block Diagram

VIN VCNTL

VOUT

Current Limit

VSENSE

Thermal Protection

Voltage Regulation

KA : SOP-8P

Temperature Range

C : 0 to 70°C

Handling Code

TR : Tape & Reel

Voltage Code :

15 : 1.5V

18 : 1.8V

25 : 2.5V

Blank : Adjustable Version

Assembly Material

The superior dropout characteristics result in reducing heat dissipation compared to regular LDOs. The APL1581 also provides excellent regulation over line, load, and temperature variations.

Thermal Characteristics

Symbol

Parameter

Typical Value

Unit

Junction-to-Байду номын сангаасmbient Resistance in free air (Note 3)

θJA

TO-263-5 (Toplayer plane size : 15mm x 15 mm) TO-252-5 (Toplayer plane size : 10mm x 10 mm)