LF33AB中文资料

ANT8823 2×3W 3.7V THD+N=1%内置同步升压,防破音,AB D 类双模立体声音频

ANT8823产品手册特性●2×3W /3.7V THD+N=1%ALC ON ●高效同步升压●ALC 防破音控制●AB 类/D 类切换双模式●超低EMI 、超低底噪●优异的上、下电pop-click 噪声抑制●全差分电路结构,抗干扰能力强●3V~5V 单电源电压供电。

●过热保护,过流保护●eSOP16封装应用●便携式蓝牙音箱,WiFi 音箱●智能音箱●便携式扩音器订购信息概要ANT8823是一款内置高效同步升压的高信噪比,低底噪,具有ALC (防破音)功能的AB/D 类双模立体声音频功放。

在锂电池3.7V 供电时,驱动双通道4Ω负载可以输出2×3W 恒定功率。

当电池电压低于3.3V 时,芯片会主动降低功率,避免拉死电池。

特有的防破音功能能够确保输出的音频信号不会出现较大的失真。

在各种应用场合都可以提供高效稳定的输出功率。

ALC 功能能够自动检测输出失真,动态调整放大器增益,可以避免因为音乐等输入信号幅度过大,或者电池电压波动而引起的输出削顶失真,显著提高音乐品质并且可以提高听感。

AB 类工作模式,可以确保在带有收音机功能的应用中无任何干扰。

AB/D 类切换功能同IC 使能管脚复用,应用非常灵活。

同时,外置输入限流功能,可以完全解决应用中拉死电池的现象。

此外,ANT8823内置过流保护、过热保护功能,确保芯片在各种应用环境中的可靠性,稳定性。

典型应用电路引脚定义eSOP16(TOP VIEW )引脚功能描述电气特性限定条件:(VDD=3.7V,TA=25℃)CTRL使能控制CTRL管脚为芯片使能控制以及模式选择管脚。

可以通过硬件分压设置不同的工作模式。

入下表所示:电平>2V音频打开,D类1.3V<电平<1.7V音频打开,AB类低电平音频关闭实际应用中可以通过两个GPIO口以及电阻网络设置。

如下图,PD与AB/D端口的电平值通过GPIO 接口设置为“H”(VIO)或者“L”(GND)。

LF33中文资料

Symbol

Parameter

Vi DC Input Voltage

Io Output Current

Ptot Power Dissipation

Tstg Storage Temperature Range

Top Operating Junction Temperature Range

(*) For 18 < VIN < 40 the regulator is in shut-down

LF12CP LF12ABP LF15CP LF15ABP LF25CP LF25ABP LF27CP LF27ABP LF30CP LF30ABP LF33CP LF33ABP LF35CP LF35ABP LF40CP LF40ABP LF45CP LF45ABP LF47CP LF47ABP LF50CP LF50ABP LF52CP LF52ABP LF55CP LF55ABP LF60CP LF60ABP LF80CP LF80ABP LF85CP LF85ABP LF90CP LF90ABP LF120CP LF120ABP

ORDERING NUMBERS

Type

PENTAWAT T

TO-220

ISOWATT 220

DPAK

PPAK

LF12C (*)

LF12CV5V

LF12AB (*) LF15C (*) LF15AB (*) LF25C LF25AB LF27C LF27AB LF30C LF30AB

LF12ABV5V LF15CV5V LF15ABV5V LF25CV5V LF25ABV5V LF27CV5V LF27ABV5V LF30CV5V LF30ABV5V

元器件交易网

LF13333中文资料

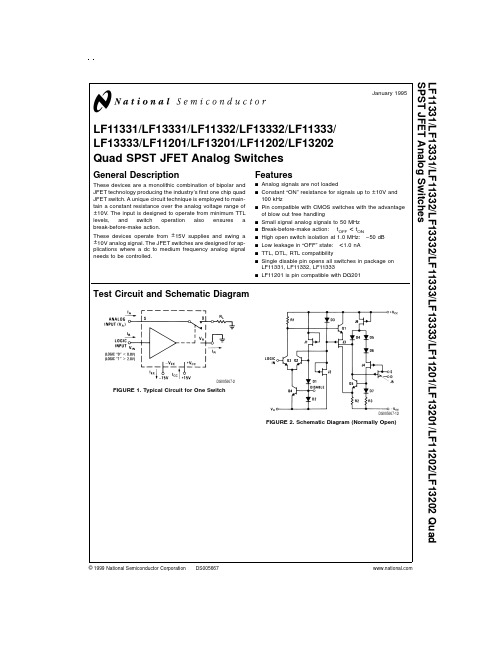

LF11331/LF13331/LF11332/LF13332/LF11333/LF13333/LF11201/LF13201/LF11202/LF13202Quad SPST JFET Analog SwitchesGeneral DescriptionThese devices are a monolithic combination of bipolar and JFET technology producing the industry’s first one chip quad JFET switch.A unique circuit technique is employed to main-tain a constant resistance over the analog voltage range of ±10V.The input is designed to operate from minimum TTL levels,and switch operation also ensures a break-before-make action.These devices operate from ±15V supplies and swing a ±10V analog signal.The JFET switches are designed for ap-plications where a dc to medium frequency analog signal needs to be controlled.Featuresn Analog signals are not loadedn Constant “ON”resistance for signals up to ±10V and 100kHzn Pin compatible with CMOS switches with the advantage of blow out free handlingn Small signal analog signals to 50MHz n Break-before-make action:t OFF <t ONn High open switch isolation at 1.0MHz:−50dB n Low leakage in “OFF”state:<1.0nA n TTL,DTL,RTL compatibilityn Single disable pin opens all switches in package on LF11331,LF11332,LF11333n LF11201is pin compatible with DG201Test Circuit and Schematic DiagramDS005667-2FIGURE 1.Typical Circuit for One SwitchDS005667-12FIGURE 2.Schematic Diagram (Normally Open)January 1995LF11331/LF13331/LF11332/LF13332/LF11333/LF13333/LF11201/LF13201/LF11202/LF13202Quad SPST JFET Analog Switches©1999National Semiconductor Corporation Absolute Maximum Ratings(Note1)If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.(Note2)Supply Voltage(V CC−V EE)36V Reference Voltage V EE≤V R≤V CC Logic Input Voltage V R−4.0V≤V IN≤V R+6.0V Analog Voltage V EE≤V A≤V CC+6V;V A≤V EE+36V Analog Current|I A|<20mA Power Dissipation(Note3)Molded DIP(N Suffix)500mW Cavity DIP(D Suffix)900mW Operating Temperature RangeLF11201,2and LF11331,2,3−55˚C to+125˚C LF13201,2and LF13331,2,30˚C to+70˚C Storage Temperature−65˚C to+150˚C Soldering InformationN and D Package(10sec.)300˚C SO Package:Vapor Phase(60sec.)215˚C Infrared(15sec.)220˚CElectrical Characteristics(Note4)LF11331/2/3LF13331/2/3Symbol Parameter Conditions LF11201/2LF13201/2UnitsMin Typ Max Min Typ MaxR ON“ON”Resistance V A=0,I D=1mA T A=25˚C150200150250Ω200300200350ΩR ON Match“ON”Resistance Matching T A=25˚C5201050ΩV A Analog Range±10±11±10±11V I S(ON)+Leakage Current in“ON”Condition Switch“ON,”V S=V D=±10V T A=25˚C0.350.310nA I D(ON)3100330nA I S(OFF)Source Current in“OFF”Condition Switch“OFF,”V S=+10V,T A=25˚C0.450.410nAV D=−10V3100330nA I D(OFF)Drain Current in“OFF”Condition Switch“OFF,”V S=+10V,T A=25˚C0.150.110nAV D=−10V3100330nA V INH Logical“1”Input Voltage 2.0 2.0V V INL Logical“0”Input Voltage0.80.8VI INH Logical“1”Input Current V IN=5V T A=25˚C 3.610253.640100µAI INL Logical“0”Input Current V IN=0.8T A=25˚C0.10.1µA11µA t ON Delay Time“ON”V S=±10V,(Figure3)T A=25˚C500500ns t OFF Delay Time“OFF”V S=±10V,(Figure3)T A=25˚C9090ns t ON−t OFF Break-Before-Make V S=±10V,(Figure3)T A=25˚C8080ns C S(OFF)Source Capacitance Switch“OFF,”V S=±10V T A=25˚C 4.0 4.0pF C D(OFF)Drain Capacitance Switch“OFF,”V D=±10V T A=25˚C 3.0 3.0pF C S(ON)+Active Source and Drain Capacitance Switch“ON,”V S=V D=0V T A=25˚C 5.0 5.0pF C D(ON)I SO(OFF)“OFF”Isolation(Figure4),(Note5)T A=25˚C−50−50dB CT Crosstalk(Figure4),(Note5)T A=25˚C−65−65dB SR Analog Slew Rate(Note6)T A=25˚C5050V/µsI DIS Disable Current(Figure5),(Note7)T A=25˚C0.4 1.00.6 1.5mA0.6 1.50.9 2.3mAI EE Negative Supply Current All Switches“OFF,”V S=±10V T A=25˚C 3.0 5.0 4.37.0mA4.27.5 6.010.5mAI R Reference Supply Current All Switches“OFF,”V S=±10V T A=25˚C 2.0 4.0 2.7 5.0mA2.8 6.03.87.5mAI CC Positive Supply Current All Switches“OFF,”V S=±10V T A=25˚C 4.5 6.07.09.0mA6.39.09.813.5mANote1:“Absolute Maximum Ratings”indicate limits beyond which damage to the device may occur.Operating Ratings indicate conditions for which the device is functional,but do not guarantee specific performance limits.Note2:Refer to RETSF11201X,RETSF11331X,RETSF11332X and RETSF11333X for military specifications.Note3:For operating at high temperature the molded DIP products must be derated based on a+100˚C maximum junction temperature and a thermal resistance of+150˚C/W,devices in the cavity DIP are based on a+150˚C maximum junction temperature and are derated at±100˚C/W.2Electrical Characteristics(Note4)(Continued)Note4:Unless otherwise specified,V CC=+15V,V EE=−15V,V R=0V,and limits apply for−55˚C≤T A≤+125˚C for the LF11331/2/3and the LF11201/2,−25˚C≤T A≤+85˚C for the LF13331/2/3and the LF13201/2.Note5:These parameters are limited by the pin to pin capacitance of the package.Note6:This is the analog signal slew rate above which the signal is distorted as a result of finite internal slew rates.Note7:All switches in the device are turned“OFF”by saturating a transistor at the disable node as shown in Figure5.The delay time will be approximately equal to the t ON or t OFF plus the delay introduced by the external transistor.Note8:This graph indicates the analog current at which1%of the analog current is lost when the drain is positive with respect to the source.Note9:θJA(Typical)Thermal ResistanceMolded DIP(N)85˚C/WCavity DIP(D)100˚C/WSmall Outline(M)105˚C/WConnection Diagrams(Top View for SO and Dual-In-Line Packages)(All Switches Shown are For Logical“0”)LF11331/LF13331DS005667-1LF11332/LF13332DS005667-13LF11333/LF13333DS005667-14LF11201/LF13201DS005667-15 3Connection Diagrams(Top View for SO and Dual-In-Line Packages)(All Switches Shown are For Logical “0”)(Continued)LF11202/LF13202DS005667-16Order Number LF13201D,LF11201D,LF11201D/883,LF13202D,LF11202D,LF11202D/883,LF13331D,LF11331D, LF11331D/883,LF13332D,LF11332D,LF11332D/883,LF13333D,LF11333D or LH11333D/883See NS Package Number D16COrder Number LF13201M,LF13202M,LF13331M,LF13332M or LF13333MSee NS Package Number M16AOrder Number LF13201N,LF13202N,LF13331N,LF13332N or LF13333NSee NS Package Number N16A4Test Circuit and Typical Performance CurvesDelay Time,Rise Time,Settling Time,andSwitching TransientsDS005667-17DS005667-18DS005667-19DS005667-20DS005667-21DS005667-225Additional Test CircuitsTypical Performance CharacteristicsDS005667-39DS005667-40FIGURE 3.t ON ,t OFF Test Circuit and Waveforms for a Normally Open SwitchDS005667-41FIGURE 4.“OFF”Isolation,Crosstalk,Small Signal Response“ON”ResistanceDS005667-23“ON”ResistanceDS005667-24“ON”ResistanceDS005667-25 6Typical Performance Characteristics(Continued)Break-Before-Make ActionDS005667-26Switching TimesDS005667-27Crosstalk and“OFF”Isolation vs FrequencyUsing Test Circuit ofFigure5DS005667-28Supply CurrentDS005667-29Supply CurrentDS005667-30Supply CurrentDS005667-31Switch Leakage CurrentsDS005667-32Switch Leakage CurrentDS005667-33Switch CapacitancesDS005667-34 7Typical Performance Characteristics(Continued)Application HintsGENERAL INFORMATIONThese devices are monolithic quad JFET analog switches with “ON”resistances which are essentially independent of analog voltage or analog current.The leakage currents are typically less than 1nA at 25˚C in both the “OFF”and “ON”switch states and introduce negligible errors in most applica-tions.Each switch is controlled by minimum TTL logic levels at its input and is designed to turn “OFF”faster than it will turn “ON.”This prevents two analog sources from being tran-siently connected together during switching.The switches were designed for applications which require break-before-make action,no analog current loss,medium speed switching times and moderate analog currents.Because these analog switches are JFET rather than CMOS,they do not require special handling.LOGIC INPUTSThe logic input (IN),of each switch,is referenced to two for-ward diode drops (1.4V at 25˚C)from the reference supply (V R )which makes it compatible with DTL,RTL,and TTL logic families.For normal operation,the logic “0”voltage can range from 0.8V to −4.0V with respect to V R and the logic “1”voltage can range from 2.0V to 6.0V with respect to V R ,pro-vided V IN is not greater than (V CC −2.5V).If the input voltage is greater than (V CC −2.5V),the input current will increase.Ifthe input voltage exceeds 6.0V or −4.0V with respect to V R ,a resistor in series with the input should be used to limit the input current to less than 100µA.ANALOG VOLTAGE AND CURRENTAnalog VoltageEach switch has a constant “ON”resistance (R ON )for analog voltages from (V EE +5V)to (V CC −5V).For analog voltages greater than (V CC −5V),the switch will remain ON indepen-dent of the logic input voltage.For analog voltages less than (V EE +5V),the ON resistance of the switch will increase.Al-though the switch will not operate normally when the analog voltage is out of the previously mentioned range,the source voltage can go to either (V EE +36V)or (V CC +6V),whichever is more positive,and can go as negative as V EE without de-struction.The drain (D)voltage can also go to either (V EE +36V)or (V CC +6V),whichever is more positive,and can go as negative as (V CC −36V)without destruction.Analog CurrentWith the source (S)positive with respect to the drain (D),the R ON is constant for low analog currents,but will increase at higher currents (>5mA)when the FET enters the saturation region.However,if the drain is positive with respect to the source and a small analog current loss at high analog cur-rents (Note 6)is tolerable,a low R ON can be maintained for analog currents greater than 5mA at 25˚C.Slew Rate of Analog Voltage Above Which Signal Loading OccursDS005667-35Small Signal ResponseDS005667-36Maximum Accurate Analog Current vs TemperatureDS005667-37Logical “1”Input Bias CurrentDS005667-38 8Application Hints(Continued)LEAKAGE CURRENTSThe drain and source leakage currents,in both the ON and the OFF states of each switch,are typically less than1nA at 25˚C and less than100nA at125˚C.As shown in the typical curves,these leakage currents are Dependent on power supply voltages,analog voltage,analog current and the source to drain voltage.DELAY TIMESThe delay time OFF(t OFF)is essentially independent of both the analog voltage and temperature.The delay time ON (t ON)will decrease as either(V CC−V A)decreases or the tem-perature decreases.POWER SUPPLIESThe voltage between the positive supply(V CC)and either the negative supply(V EE)or the reference supply(V R)can be as much as36V.To accommodate variations in input logic refer-ence voltages,V R can range from V EE to(V CC−4.5V).Care should be taken to ensure that the power supply leads for the device never become reversed in polarity or that the device is never inadvertently installed backwards in a test socket.If one of these conditions occurs,the supplies would zener an internal diode to an unlimited current;and result in a de-stroyed device.SWITCHING TRANSIENTSWhen a switch is turned OFF or ON,transients will appear at the load due to the internal transient voltage at the gate of the switch JFET being coupled to the drain and source by the junction capacitances of the JFET.The magnitude of these transients is dependent on the load.A lower value R L produces a lower transient voltage.A negative transient oc-curs during the delay time ON,while a positive transient oc-curs during the delay time OFF.These transients are rela-tively small when compared to faster switch families. DISABLE NODEThis node can be used,as shown in Figure5,to turn all the switches in the unit off independent of logic inputs.Normally, the node floats freely at an internal diode drop(≈0.7V)above V R.When the external transistor in Figure5is saturated,the node is pulled very close to V R and the unit is disabled.Typi-cally,the current from the node will be less than1mA.This feature is not available on the LF11201or LF11202series.Typical ApplicationsDS005667-6FIGURE5.Disable FunctionSample and Hold with ResetDS005667-42 9Typical Applications(Continued)Programmable Inverting Non-Inverting Operational AmplifierDS005667-43Programmable Gain Operational AmplifierDS005667-44 10Typical Applications(Continued)DemultiplexerDS005667-45Multiplexer/MixerDS005667-4611Typical Applications(Continued)8-Channel Analog Commutator with6-Channel Select LogicDS005667-47Chopper Channel AmplifierDS005667-48 12Typical Applications(Continued)Self-Zeroing Operational AmplifierDS005667-49Programmable Integrator with Reset and HoldDS005667-5013Typical Applications(Continued)Staircase Transfer Function Operational AmplifierDS005667-51 14Typical Applications(Continued)DSB Modulator-DemodulatorDS005667-111516Physical Dimensions inches(millimeters)unless otherwise notedOrder Number LF11201D,LF11201D/883,LF13201D,LF11202D,LF11202D/883,LF13202D,LF11331D,LF11331D/883,LF13331D,LF11332D,LF11332D/883,LF13332D,LF11333D,LF11333D/883or LF13333DNS Package Number D16COrder Number LF113201M,LF13202M,LF13331M,LF13332M or LF13333MNS Package Number M16A17Physical Dimensions inches(millimeters)unless otherwise noted(Continued)LIFE SUPPORT POLICYNATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DE-VICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMI-CONDUCTOR CORPORATION.As used herein:1.Life support devices or systems are devices or sys-tems which,(a)are intended for surgical implant intothe body,or(b)support or sustain life,and whose fail-ure to perform when properly used in accordancewith instructions for use provided in the labeling,canbe reasonably expected to result in a significant injuryto the user.2.A critical component is any component of a life supportdevice or system whose failure to perform can be rea-sonably expected to cause the failure of the life supportdevice or system,or to affect its safety or effectiveness.National SemiconductorCorporationAmericasTel:1-800-272-9959Fax:1-800-737-7018Email:support@National SemiconductorEuropeFax:+49(0)180-5308586Email:europe.support@Deutsch Tel:+49(0)180-5308585English Tel:+49(0)180-5327832Français Tel:+49(0)180-5329358Italiano Tel:+49(0)180-5341680National SemiconductorAsia Pacific CustomerResponse GroupTel:65-2544466Fax:65-2504466Email:sea.support@National SemiconductorJapan Ltd.Tel:81-3-5639-7560Fax:81-3-5639-7507Order Number LF13201N,LF13202N,LF13331N,LF13332N or LF13333NNS Package Number N16ALF11331/LF13331/LF11332/LF13332/LF11333/LF13333/LF1121/LF1321/LF1122/LF1322QuadSPSTJFETAnalogSwitchesNational does not assume any responsibility for use of any circuitry described,no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.。

L1119L-33-AA3-O-T中文资料

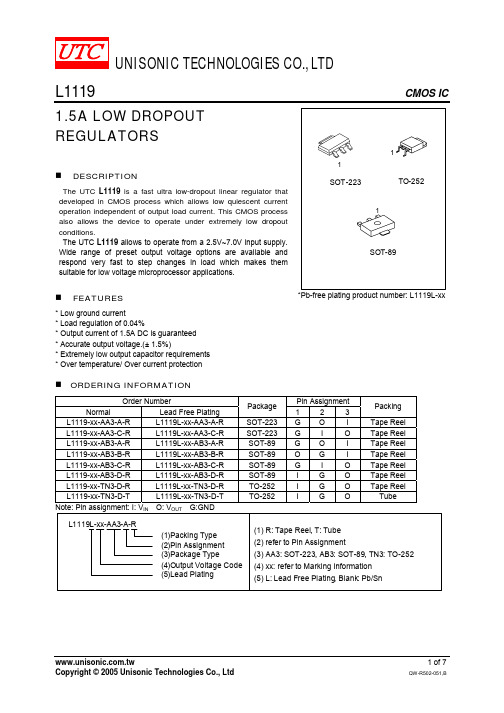

UNISONIC TECHNOLOGIES CO., LTDL1119 CMOS IC1.5A LOW DROPOUT REGULATORSDESCRIPTIONThe UTC L1119 is a fast ultra low-dropout linear regulator that developed in CMOS process which allows low quiescent current operation independent of output load current. This CMOS process also allows the device to operate under extremely low dropout conditions.The UTC L1119 allows to operate from a 2.5V~7.0V input supply. Wide range of preset output voltage options are available and respond very fast to step changes in load which makes them suitable for low voltage microprocessor applications.FEATURES* Low ground current* Load regulation of 0.04%* Output current of 1.5A DC is guaranteed * Accurate output voltage.(± 1.5%)* Extremely low output capacitor requirements * Over temperature/ Over current protection*Pb-free plating product number: L1119L-xxORDERING INFORMATIONOrder Number Pin AssignmentNormal Lead Free Plating Package 1 2 3PackingL1119-xx-AA3-A-R L1119L-xx-AA3-A-R SOT-223 G O I Tape Reel L1119-xx-AA3-C-R L1119L-xx-AA3-C-R SOT-223 G I O Tape Reel L1119-xx-AB3-A-R L1119L-xx-AB3-A-R SOT-89 G O I Tape Reel L1119-xx-AB3-B-R L1119L-xx-AB3-B-R SOT-89 O G I Tape Reel L1119-xx-AB3-C-R L1119L-xx-AB3-C-R SOT-89 G I O Tape Reel L1119-xx-AB3-D-R L1119L-xx-AB3-D-R SOT-89 I G O Tape Reel L1119-xx-TN3-D-R L1119L-xx-TN3-D-R TO-252 I G O Tape Reel L1119-xx-TN3-D-T L1119L-xx-TN3-D-T TO-252 I G O TubeMARKING INFORMATIONBLOCK DIAGRAMGNDABSOLUTE MAXIMUM RATINGSPARAMETER SYMBOL RATINGSUNIT Input Supply Voltage V IN-0.3 ~ +7.5 VOutput Voltage V OUT-0.3 ~ +7.5 VOutput Current I OUT Short Circuit ProtectedPower Dissipation P D InternallyLimitedOperating Junction Temperature T OPR-40 ~ +125Storage Temperature T STG-65 ~ +150Note Absolute maximum ratings are those values beyond which the device could be permanently damaged.Absolute maximum ratings are stress ratings only and functional device operation is not implied.RECOMMENDED OPERATING RATINGSPARAMETER SYMBOL RATINGSUNIT Input Supply Voltage V IN 2.5 ~ 7.0 VMaximum Operating Current (DC) I OPR(MAX) 1.5 A Operating Junction Temperature T J-40 ~ +125Note: Absolute maximum ratings are those values beyond which the device could be permanently damaged.Absolute maximum ratings are stress ratings only and functional device operation is not implied.ELECTRICAL CHARACTERISTICS(T J=25°C, V IN =V OUT+1V, I L=10mA, C OUT=33µF,unless otherwise specified.)PARAMETER SYMBOL TESTCONDITIONSMINTYPMAX UNITI L = 150 mA 38 45Dropout Voltage (Note) V DI L = 1.5 A 870mVPeak Output Current I PEAK 2.0 2.5 AI L = 150 mA 4 9Ground Pin Current I GNDI L = 1.5 A 5 14mAOutput Voltage Tolerance V OUT 10 mA ≤ I L≤ 1.5AV OUT +1 ≤ V IN≤ 7.0V-1.5 0 +1.5 %Line Regulation ∆V OUT V OUT+1V<V IN<7.0V 0.1 % Load Regulation ∆V OUT10 mA < I L < 1.5 A 1.5 % SHORT CIRCUIT PROTECTIONShort Circuit Current I SC 4.5 A AC PARAMETERSOutput Noise Density ρN(l/f) f = 120Hz 0.8 µVBW = 10Hz – 100kHz 150Output Noise Voltage eNBW = 300Hz – 300kHz 100µV(rms)V IN = V OUT + 1.5VC OUT =100uF, V OUT = 3.3V 60Ripple Rejection RRV IN = V OUT + 0.3VC OUT =100uF, V OUT = 3.3V 40dBOVER TEMPERATURE PROTECTIONShutdown Threshold T SHDN165 °C Thermal Shutdown Hysteresis T HYS 10 °C Note: Dropout voltage is defined as the minimum input to output differential voltage at which the output drops 2% below the nominal value. Dropout voltage specification applies only to output voltages of 2.5V and above. For output voltages below 2.5V, the drop-out voltage is nothing but the input to output differential, since the minimum input voltage is 2.5V.TYPICAL CHARACTERISTICS(V IN =V OUT +1V, V OUT =2.5V, C OUT =33µF, I OUT =10mA, C IN =68µF, Ta =25°C.)-40-200204060801001201400.050.10.150.20.25Temperature (℃)D r o p -O u t (V )Drop-Out Voltage vs Temperature (I L )-40-200204060801001201400.150.1750.20.225Temperature (℃)D r o p -O u t (V )Drop-Out Voltage vs Temperature (V OUT )0.125V OUT vs Temperature0.00D e l t a V O U T (%)-0.10-0.20-0.30-0.40-0.50-0.60-0.70-0.80-0.90-75-50-25255075100125Temperature (℃)100.01010Frequency (Hz)N o i s e ( V / H z )Noise Density1.0000.10010010001000001000003V IN (V)V O U T (V )Input Voltage vs Output Voltage2.50.51.5211234TYPICAL CHARACTERISTICS(Cont.)100Frequency (Hz)Output Noise Density100010000100000100Output Noise Density100010000100000Frequency (Hz)10-1090Frequency (Hz)Ripple Rejection vs Frequency1M100K10K1K1001020304050607080R i p p l e R e j e c t i o n (d B )Load Transient Response20 I O U T (A)VO U T (V )Line Transient Response10 s/DIV V I N (V )V O U T (V )Line Transient Response10 s/DIVV I N (V )V O U T (V )TYPICAL CHARACTERISTICS(Cont.)Line Transient Response10s/DIVV I N (V )V O U T (V )Line Transient Response10 3.253.33.35V I N (V )V O U T (V ) 5.34.33.453.4。

ACPL-331J CN的中文资料

ACPL-331J 1.5A电流输出的IGBT门极驱动光耦集成的(Vce)饱和度检测,欠压锁定,故障状态反馈和有源米勒钳位综述:ACPL - 331J是一种先进的1.5 A的输出电流,方便易用的智能化的门极驱动器使得IGBT的Vce的故障保护更加紧凑,价格合理,且易于实现功能,如集成的Vce检测,欠压锁定(UVLO),IGBT的“软”关断,隔离的集电极开路故障反馈和有源米勒钳位提供最大的设计灵活性和保护电路。

ACPL - 331J包含了一个GaAsP的LED。

通过该LED完成光电信号的耦合。

ACPL-331J非常适合用于驱动电机控制领域的功率IGBT和MOSFET。

这些光耦的电压、电流供给使其非常适用用于直接驱动1200V 100A以下的IGBT。

对于更高功率等级的IGBT,ACPL-331J通常被用来驱动由分离器件构成的IGBT门极驱动器。

ACPL-331J具备一个峰值为891V的绝缘电压。

结构框图:产品特点:z滞后的欠压封锁功能z饱和度侦测z米勒钳位z隔离的开路集电极故障反馈z IGBT软关断z IGBT下个开通周期的故障复位z提供SO - 16封装z安规认证详细说明:z 1.5A的最大输出峰值电流z 1.0A的最小输出峰值电流z温度范围内最大250nS的传输延时z100nS最大脉冲宽度失真z在V CM = 1500 V时,最小15 kV/µs的共模抑制能力z最大供电电流I CC(max) < 5 mAz温度范围内工作电压可达15V-30Vz1A的米勒钳位。

该脚不用时必须同VEE短接z宽的工作温度范围:–40°C to 100°C应用:z IGBT和功率MOSFET的驱动z交流和直流无刷电机驱动z变频器和UPS引脚功能介绍订货信息ACPL-331J 经过3750 Vrms 1分钟测试,符合UL1577标准。

备注 表面 符合IEC / EN产品编号 符合ROHS 标准 封装方式 安装 卷带装 DIN EN 60747-5-2 数量-000E SO-16 X X 45/管ACPL-331J -500E X X X 850/卷 订购时,从产品编号列表中选择产品编号,并结合其他所需的选项形成定单输入。

FGA180N33ATDTU;中文规格书,Datasheet资料

tmFGA180N33ATD 330V, 180A PDP Trench IGBTApril 2008Absolute Maximum RatingsNotes:1: Repetitive test, pulse width = 100usec, Duty = 0.1* I C_pulse limited by max TjThermal CharacteristicsSymbolDescriptionRatingsUnitsV CES Collector to Emitter Voltage 330V V GES Gate to Emitter Voltage ± 30V I CCollector Current@ T C = 25o C180A I C pulse (1)Pulsed Collector Current @ T C = 25o C 450A P D Maximum Power Dissipation @ T C = 25o C 390W Maximum Power Dissipation @ T C = 100o C156WT J Operating Junction Temperature -55 to +150o C T stg Storage Temperature Range-55 to +150oCT LMaximum Lead Temp. for soldering Purposes, 1/8” from case for 5 seconds300o CSymbolParameterTyp.Max.UnitsR θJC (IGBT)Thermal Resistance, Junction to Case -0.32oC /W R θJC (Diode)Thermal Resistance, Junction to Case -0.82o C /W R θJAThermal Resistance, Junction to Ambient-40oC /WGECG EC TO-3PFGA180N33ATD330V, 180A PDP Trench IGBTFeatures•High Current Capability•Low saturation voltage: V CE(sat) =1.03V @ I C = 40A •High input impedance •RoHS compliantApplications•PDP SYSTEMGeneral DescriptionUsing Novel Trench IGBT Technology, Fairchild’s new series of trench IGBTs offer the optimum performance for PDP applica-tions where low conduction and switching losses are essential.FGA180N33ATD 330V, 180A PDP Trench IGBTElectrical Characteristics of the Diode TC = 25°C unless otherwise notedSymbol Parameter Test Conditions Min.Typ.Max UnitsV FM Diode Forward Voltage I F = 20A T C = 25o C- 1.2 1.6V T C = 125o C- 1.04-t rr Diode Reverse Recovery TimeI F = 20AdI/dt = 200A/µs T C = 25o C-27-ns T C = 125o C-39-I rr Diode Peak Reverse Recovery Cyrrent T C = 25o C- 3.5-A T C = 125o C- 6.0-Q rr Diode Reverse Recovery Charge T C = 25o C-48-µCT C = 125o C-117-FGA180N33ATD 330V, 180A PDP Trench IGBTFGA180N33ATD 330V, 180A PDP Trench IGBTFGA180N33ATD 330V, 180A PDP Trench IGBTFGA180N33ATD 330V, 180A PDP Trench IGBTFGA180N33ATD 330V, 180A PDP Trench IGBTFGA180N33ATD 330V, 180A PDP Trench IGBTFGA180N33ATD 330V, 180A PDP Trench IGBT* EZSWITCH™ and FlashWriter ® are trademarks of System General Corporation, used under license by Fairchild Semiconductor.DISCLAIMERFAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD’S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.LIFE SUPPORT POLICYFAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.As used herein:1. Life support devices or systems are devices or systems which,(a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user. 2.A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.PRODUCT STATUS DEFINITIONS Definition of Terms ACEx ®Build it Now™CorePLUS™CorePOWER™CROSSVOLT ™CTL™Current Transfer Logic™EcoSPARK ®EfficentMax™EZSWITCH™ *™Fairchild ®Fairchild Semiconductor ®FACT Quiet Series™FACT ®FAST ®FastvCore™FlashWriter ® *FPS™F-PFS™FRFET ®Global Power Resource SM Green FPS™Green FPS™ e-Series™GTO™IntelliMAX™ISOPLANAR™MegaBuck™MICROCOUPLER™MicroFET™MicroPak™MillerDrive™MotionMax™Motion-SPM™OPTOLOGIC ®OPTOPLANAR ®®PDP-SPM™Power-SPM™PowerTrench ®Programmable Active Droop™QFET ®QS™Quiet Series™RapidConfigure™Saving our world 1mW at a time™SmartMax™SMART START™SPM ®STEALTH™SuperFET™SuperSOT™-3SuperSOT™-6SuperSOT™-8SuperMOS™®The Power Franchise ®TinyBoost™TinyBuck™TinyLogic ®TINYOPTO™TinyPower™TinyPWM™TinyWire™µSerDes™UHC ®Ultra FRFET™UniFET™VCX™VisualMax™®Datasheet Identification Product Status DefinitionAdvance InformationFormative or In DesignThis datasheet contains the design specifications for product development. Specifications may change in any manner without notice.Preliminary First ProductionThis datasheet contains preliminary data; supplementary data will be pub-lished at a later date. Fairchild Semiconductor reserves the right to make分销商库存信息: FAIRCHILDFGA180N33ATDTU。

HQxxxx-xxx-3AA中文资料

HQ SeriesSPECIFICATIONS STANDARD*SPECIAL ELECTRICALCenter Frequency (Fc)100 to 1000 Mhz80 to 1400 MHz 3dB Relative Bandwidth (% of FC) 4 to 40 4 to 50 Number of Sections Available 3 to 8 2 to 10 Nominal Impedance50 Ohms50 to 75 Ohms Maximum Insertion Loss See Curve See Curve Maximum VSWR 1.5/1 1.3/1 Attenuation in the Stopband See Graph See GraphMaximum Input Power (Average)(Watts to10,000 ft.)500 x 3dB BW (MHz)(Loss Factor)(Fc MHz)See StandardMaximum Input Power (Peak)(Watts to10,000 ft.)300 x 3dB BW (MHz)Fc (MHz)2,000ENVIRONMENTALShock15 G's25 G's Vibration 5 G's10 G's Humidity90% relative100% relativeINSERTION LOSS:The Maximum Insertion Loss at center frequency is equal to :LF x (N + 0.5) / % 3 dB BW + 0.2 Where:LF= Loss Factor, N= Number of Sections% 3dB BW:3dB BW (MHz) x 100divided byCenter Frequency (MHz) Example:A 3 section HQ with a center frequency of 400 MHz and a 3dB BW of 40 MHz would have,1.5 x 3.5 / 10 = 5.25 / 10 = 0.525 0.525 + 0.2 = 0.8 dBConnectors Available on HQ Series:Lark Code Type C DIM.Inches & MMLarkCodeType C DIM.Inches & MMA SMA JACK.800 & 20.3G N JACK 1.625 & 41.3B SMA PLUG.855 & 22.5H N PLUG 1.585 & 40.3C TNC JACK 1.350 & 34.3L SOLDER MPINAXIAL.625 & 15.9D TNC PLUG 1.280 & 32.5*M SOLDER PINRADIAL.625 & 15.9E BNC JACK 1.350 & 34.3S SPECIALF BNC PLUG 1.280 & 32.5*Not recommended for use with this series.LENGTH:The approximate length of a Lark HQ series filter can be determined by the formula:( 0.5 N + 2 / %BW ) x LC = LWhere N is the number of sections used, % BW is:3dB BW (MHz) x 100divided byCENTER FREQUENCY (MHz)LC is the length constant at the specified center frequency, L is the dimension between theconnectors; C1 and C2 are the connector lengths as shown above. All of the length information given here is approximate. Exact length specifications must be quoted by the factory. If a special length is needed,please submit all of your requirements - both electrical and mechanical. This will enable Lark Engineering to quote the optimum design for your application.Example:A 3 section HQ with a center frequency of 400 MHz a 3dB BW of 40 MHz and SMA jack input and output connectors would be:(1.5 + 0.2) x 1.38 = 2.35 + C1 + C2In most cases, the L dimension is rounded to the nearest 1/4 inch which in this instance would be 2.25inches and the O.A.L. is:2.25 + .800 + .800 =3.85 inches.To convert inches to millimeters multiply x 25.40.Lark Engineering HQ SERIES元器件交易网STOPBAND ATTENUATIONThe graph on the following pages defines the normal specification limits on attenuation Lark bandpass filter series HP, HQ, SF, and SM. The minimum level of attenuation in dB is shown as a "number of 3dB bandwidths from center frequency".Since the frequency characteristics vary for differing bandwidths, it is necessary to establishspecifications for each bandwidth of filter. The different graphs represent various 3dB percentage bandwidths. Intermediate values should be interpolated. The 3dB percentage bandwidth is defined asfollows:STOPATT5.HTM元器件交易网As the 3dB bandwidth is exactly 10% of the center frequency, the answer can be read directly from the 10% graph. Using the 5 section curve at the point -1.5 (255 MHz) we find the minimum level of attenuation is 36dB. At +1.6 (348 MHz) the minimum level of attenuation is 48dB.For special requirements, please contact our Application Engineering Department.STOPBAND ATTENUATIONSTOPBAND ATTENUATIONSTOPATT5.HTM元器件交易网STOPBAND ATTENUATIONSTOPBAND ATTENUATIONSTOPBAND ATTENUATION。

BCW33LT1G中文资料

BCW33LT1General Purpose TransistorNPN SiliconFeatures•Pb−Free Packages are AvailableMAXIMUM RATINGSRatingSymbol Value Unit Collector − Emitter Voltage V CEO 32Vdc Collector − Base Voltage V CBO 32Vdc Emitter − Base Voltage V EBO 5.0Vdc Collector Current − ContinuousI C100mAdcTHERMAL CHARACTERISTICSCharacteristicSymbol Max UnitTotal Device Dissipation FR−5 Board (Note 1)T A = 25°CDerate above 25°C P D2251.8mW mW/°C Thermal Resistance,Junction−to−Ambient R q JA 556°C/WTotal Device DissipationAlumina Substrate (Note 2),T A= 25°CDerate above 25°C P D3002.4mWmW/°C Thermal Resistance,Junction−to−AmbientR q JA 417°C/W Junction and Storage TemperatureT J , T stg−55 to +150°CMaximum ratings are those values beyond which device damage can occur.Maximum ratings applied to the device are individual stress limit values (not normal operating conditions) and are not valid simultaneously. If these limits are exceeded, device functional operation is not implied, damage may occur and reliability may be affected.1.FR−5 = 1.0 0.75 0.062 in.2.Alumina = 0.4 0.3 0.024 in. 99.5% alumina.Device Package Shipping †ORDERING INFORMATIONBCW33LT1SOT−233000/Tape & Reel BCW33LT1G SOT−23(Pb−Free)3000/Tape & Reel †For information on tape and reel specifications,including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.BCW33LT3SOT−2310,000/Tape & Reel BCW33LT3GSOT−23(Pb−Free)10,000/Tape & ReelELECTRICAL CHARACTERISTICS (T A = 25°C unless otherwise noted)CharacteristicSymbolMinMaxUnitOFF CHARACTERISTICSCollector −Emitter Breakdown Voltage (I C = 2.0 mAdc, I B = 0)V (BR)CEO 32−Vdc Collector −Base Breakdown Voltage (I C = 10 m Adc, I B = 0)V (BR)CBO 32−Vdc Emitter −Base Breakdown Voltage (I E = 10 m Adc, I C = 0)V (BR)EBO 5.0−VdcCollector Cutoff Current (V CB = 32 Vdc, I E = 0)(V CB = 32 Vdc, I E = 0, T A = 100°C)I CBO−−10010nAdc m AdcON CHARACTERISTICSDC Current Gain(I C = 2.0 mAdc, V CE = 5.0 Vdc)hFE420800−Collector −Emitter Saturation Voltage (I C = 10 mAdc, I B = 0.5 mAdc)V CE(sat)−0.25Vdc Base −Emitter On Voltage(I C = 2.0 mAdc, V CE = 5.0 Vdc)V BE(on)0.550.70VdcSMALL−SIGNAL CHARACTERISTICS Output Capacitance(V CB = 10 Vdc, I E = 0, f = 1.0 MHz)C obo − 4.0pF Noise Figure(V CE = 5.0 Vdc, I C = 0.2 mAdc, R S = 2.0 k W , f = 1.0 kHz, BW = 200 Hz)NF−10dBFigure 1. Turn−On Time Figure 2. Turn−Off TimeEQUIVALENT SWITCHING TIME TEST CIRCUITS*Total shunt capacitance of test jig and connectors− 0Figure 3. Noise Voltage f, FREQUENCY (Hz)5.07.010203.0Figure4. Noise Currentf, FREQUENCY (Hz)2.0e n , N O I S E V O L T A G E (n V )(V CE = 5.0 Vdc, T A = 25°C)500 k R S , S O U R C E R E S I S T A N C E (O H M S )Figure 7. WidebandI C , COLLECTOR CURRENT (m A)10R S , S O U R C E R E S I S T A N C E (O H M S )501002005001 k 10 k 5 k 20 k 50 k 100 k 200 k 2 k 500 k 501002005001 k 10 k 5 k 20 k 50 k 100 k 200 k 2 k 203050701002003005007001 k NOISE FIGURE CONTOURS(V CE = 5.0 Vdc, T A = 25°C)I C , COLLECTOR CURRENT (mA)1.4I C , COLLECTOR CURRENT (mA)V , V O L T A G E (V O L T S )Figure 10. “On” Voltages 0.40.60.81.00.2V C E , C O L L E C T O R −E M I T T E R V O L T A G E (V O L T S )Figure 11. Temperature Coefficients1.21.00.80.60.40.20Figure 12. Turn−On Time I C , COLLECTOR CURRENT (mA)300Figure 13. Turn−Off TimeI C , COLLECTOR CURRENT (mA)2.05.010*******.01.0t , T I M E (n s )3.05.07.010203050701002007.0701002.05.0102030503.01.07.070100C , C A P A C I T A N C E (p F )Figure 14. Current−Gain — Bandwidth ProductI C , COLLECTOR CURRENT (mA)Figure 15. CapacitanceV R , REVERSE VOLTAGE (VOLTS)5000.510f , C U R R E N T −G A I N B A N D W I D T H P R O D U C T (M H z )T 50701002003000.7 1.02.03.0 5.07.0102030501.02.03.05.07.0Figure 16. Thermal Responset, TIME (ms)1.00.01r (t ) T R A N S I E N T T H E R M A L R E S I S T A N C E (N O R M A L I Z E D )0.010.020.030.050.070.10.20.30.50.70.020.050.10.20.51.02.05.0102050100200500 1.0 k 2.0 k 5.0 k 10 k 20 k 50 k 100 kFigure 16A.T J , JUNCTION TEMPERATURE (°C)104−40I C , C O L L E C T O R C U R R E N T (n A )DESIGN NOTE: USE OF THERMAL RESPONSE DATAA train of periodical power pulses can be represented by the model as shown in Figure 16A. Using the model and the device thermal response the normalized effective transient thermal resistance of Figure 16 was calculated for various duty cycles.To find Z q JA(t), multiply the value obtained from Figure 16 by the steady state value R q JA .Example:The MPS3904 is dissipating 2.0 watts peak under the following conditions:t 1 = 1.0 ms, t 2 = 5.0 ms. (D = 0.2)Using Figure 16 at a pulse width of 1.0 ms and D = 0.2, the reading of r(t) is 0.22.The peak rise in junction temperature is therefore D T = r(t) x P (pk) x R q JA = 0.22 x 2.0 x 200 = 88°C.For more information, see AN−569.10−210−1100101102103−20+20+40+60+80+100+120+140+160PACKAGE DIMENSIONSSOT−23 (TO−236)CASE 318−08ISSUE ANNOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: INCH.3.MAXIMUM LEAD THICKNESS INCLUDES LEAD FINISH THICKNESS. MINIMUM LEADTHICKNESS IS THE MINIMUM THICKNESS OF BASE MATERIAL.4.318−01 THRU −07 AND −09 OBSOLETE, NEW STANDARD 318−08.VIEW CDIM A MIN NOM MAX MIN MILLIMETERS0.89 1.00 1.110.035INCHESA10.010.060.100.001b 0.370.440.500.015c 0.090.130.180.003D 2.80 2.90 3.040.110E 1.20 1.30 1.400.047e 1.78 1.90 2.040.070L 0.100.200.300.0040.0400.0440.0020.0040.0180.0200.0050.0070.1140.1200.0510.0550.0750.0810.0080.012NOM MAX L1STYLE 6:PIN 1.BASE2.EMITTER3.COLLECTOR2.10 2.40 2.640.0830.0940.104H E 0.350.540.690.0140.0210.029SOLDERING FOOTPRINT**For additional information on our Pb−Free strategy and solderingdetails, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates,and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATION。

RT9186A-33PF中文资料

EN

Shutdown Logic

Thermal Shutdown ADJ Output Mode Comparator

PGOOD + Current Limit Sensor + 0.8V Reference

Error Amplifier

80% Reference

VIN

EN

Shutdown Logic

元器件交易网

RT9186A/B

Pin Description

Pin Name Pin Function VIN VOUT GND EN PGOOD RST ADJ Power Input Voltage. Output Voltage. Ground. Chip Enable (Active-High). There should be a pull low resistor 100kΩ connected to GND when the control signal is floating. Power Good Indicator. (RT9186A). Open-Drain Active-Low Reset Output. Connect a 100kΩ to VOUT to obtain output voltage. In shutdown the RST output is low. (RT9186B). Output Voltage Setting. Connect to GND for Fixed output voltage model.

RST + + Delay Timer -

80% Reference

DS9186AB-10 August 2007

+

CA3318CE资料

®November 2002CA3318CMOS Video Speed,8-Bit, Flash A/D ConverterFN3103.3Features•CMOS Low Power with SOS Speed (Typ) . . . . . . . .150mW •Parallel Conversion Technique•15MHz Sampling Rate (Conversion Time). . . . . . .67ns •8-Bit Latched Three-State Output with Overflow Bit •Accuracy (Typ). . . . . . . . . . . . . . . . . . . . . . . . . . ±1 LSB •Single Supply Voltage. . . . . . . . . . . . . . . . . . 4V to 7.5V • 2 Units in Series Allow 9-Bit Output• 2 Units in Parallel Allow 30MHz Sampling RateApplications•TV Video Digitizing (Industrial/Security/Broadcast)•High Speed A/D Conversion •Ultrasound Signature Analysis •Transient Signal Analysis•High Energy Physics Research •General-Purpose Hybrid ADCs •Optical Character Recognition •Radar Pulse Analysis•Motion Signature Analysis •µP Data Acquisition SystemsDescriptionThe CA3318 is a CMOS parallel (FLASH) analog-to-digital converter designed for applications demanding both low power consumption and high speed digitization.The CA3318 operates over a wide full scale input voltage range of 4V up to 7.5V with maximum power consumption depending upon the clock frequency selected. When operated from a 5V supply at a clock frequency of 15MHz,the typical power consumption of the CA3318 is 150mW.The intrinsic high conversion rate makes the CA3318 ideally suited for digitizing high speed signals. The overflow bit makes possible the connection of two or more CA3318s in series to increase the resolution of the conversion system. A series connection of two CA3318s may be used to produce a 9-bit high speed converter. Operation of two CA3318s in parallel doubles the conversion speed (i.e., increases the sampling rate from 15MHz to 30MHz).256 paralleled auto balanced voltage comparators measure the input voltage with respect to a known reference to produce the parallel bit outputs in the CA3318.255 comparators are required to quantize all input voltage levels in this 8-bit converter, and the additional comparator is required for the overflow bit.Part Number InformationPinoutCA3318(PDIP, SBDIP, SOIC)TOP VIEWPART NUMBER LINEARITY (INL, DNL)SAMPLING RATE TEMP. RANGE (o C)PACKAGE PKG. NO.CA3318CE ±1.5 LSB 15MHz (67ns)-40 to 8524 Ld PDIP E24.6CA3318CM ±1.5 LSB 15MHz (67ns)-40 to 8524 Ld SOIC M24.3CA3318CD±1.5 LSB15MHz (67ns)-40 to 8524 Ld SBDIPD24.6123456789101112161718192021222324151413(LSB) B1B2B3B4B5B6B7(MSB) B8OVERFLOW 1/4R (DIG. GND) V SS (DIG. SUP.) V DD V AA + (ANA. SUP.)V REF +V IN p PHASE V AA - (ANA. GND)V REF -CE1CE23/4R CLKV IN F O R A P O S S IB L E S U B S T I T U T E P R O D UC T c o n t a c t o u r T e c h n i c a l S u p p o r t C e n t e r a t 1-888-I N T E R S I L o r w w w .i n t e r s i l .c o m /t s c O B S O L E T E P R O D U C TCAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.1-888-INTERSIL or 321-724-7143|Intersil (and design) is a registered trademark of Intersil Americas Inc.Functional Block DiagramLATCH 256DQENCODER LOGIC ARRAYCLKD Q CLKD Q CLKD Q CLKD QCLKD QCLKD Q CLKD Q CLKD Q CLKD Q CAB LATCHDQDQCOUNT 193CAB LATCH D Q D QCOUNT 129CAB LATCHDQDQCOUNT 65CAB LATCH 1DQ LATCH 11D QCOUNT1CAB # 256# 193# 129# 65233/4REF 201/2REF 101/4REF 2221241615V REF +V IN V AA +V IN V REF -(NOTE 1)COMPARATOR #1LATCHLATCH LATCH9OVER-FLOWTHREE-STATE DRIVERS OUTPUTREGISTER DIGITAL SUPPLY12V DDφ2φ1φ1φ1φ1φ2φ18BIT 8(MSB)7BIT 76BIT 65BIT 54BIT 43BIT 32BIT 21BIT 1(LSB)14CE113CE2DIGITALGND11V SS 18CLOCK 19PHASE 17V AA -ANALOG GNDφ1 (AUTO BALANCE)φ2 (SAMPLE UNKNOWN)NOTE:≅ 50K1/2R = 4Ω= 30Ω= 7ΩR = 2ΩRRRRRR ≅ 2K ANALOG SUPPLY1/2 RRLATCH 256COUNT 256DQ1.Cascaded Auto Balance (CAB).Absolute Maximum RatingsThermal InformationDC Supply Voltage Range (V DD or V AA +). . . . . . . . . . -0.5V to +8V (Referenced to V SS or V AA - Terminal, Whichever is More Negative)Input Voltage RangeCE2 and CE1 . . . . . . . . . . . . . . . . . . . .V AA - -0.5V to V DD + 0.5V Clock, Phase, V REF -, 1/2 Ref. . . . . . . V AA - -0.5V to V AA + + 0.5V Clock, Phase, V REF -, 1/4 Ref. . . . . . . .V SS - -0.5V to V DD + 0.5V V IN , 3/4 REF, V REF + . . . . . . . . . . . . . .V AA - -0.5V to V AA - + 7.5V Output Voltage Range,. . . . . . . . . . . . . . . V SS - 0.5V to V DD + 0.5V Bits 1-8, Overflow (Outputs Off)DC Input Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±20mA Clock, Phase, CE1, CE2, V IN , Bits 1-8, OverflowOperating ConditionsOperating Voltage Range (V DD or V AA +) . . 4V (Min) to 7.5V (Max)Recommended V AA + Operating Range. . . . . . . . . . . . . . . V DD ±1V Recommended V AA - Operating Range . . . . . . . . . . . . . . . V SS ±1V Operating Temperature Range (T A ). . . . . . . . . . . . . .-40o C to 85o CThermal Resistance (Typical, Note 1)θJA (o C/W)θJC (o C/W)SBDIP Package. . . . . . . . . . . . . . . . . . . . 6022PDIP Package. . . . . . . . . . . . . . . . . . . . . 60N/A SOIC Package. . . . . . . . . . . . . . . . . . . . . 75N/A Maximum Junction TemperatureCeramic Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .175o C Plastic Packages. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .150o C Maximum Storage Temperature Range . . . . . . . . . .-65o C to 150o C Maximum Lead Temperature (Soldering 10s). . . . . . . . . . . . .265o C (SOIC - Lead Tips Only)CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.NOTE:1.θJA is measured with the component mounted on an evaluation PC board in free air.Electrical SpecificationsAt 25o C, V AA + = V DD = 5V, V REF + = 6.4V, V REF - = V AA - = V SS , CLK = 15MHz,All Reference Points Adjusted, Unless Otherwise SpecifiedPARAMETERTEST CONDITIONSMIN TYP MAX UNITS SYSTEM PERFORMANCE Resolution8--Bits Integral Linearity Error --± 1.5LSB Differential Linearity Error --+1, -0.8LSB Offset Error, Unadjusted V IN = V REF - + 1/2 LSB -0.5 4.5 6.4LSB Gain Error UnadjustedV IN = V REF + - 1/2 LSB -1.51.5LSBDYNAMIC CHARACTERISTICS Maximum Input Bandwidth (Note 1) CA3318 2.5 5.0-MHz Maximum Conversion Speed CLK = Square Wave 1517-MSPS Signal to Noise Ratio (SNR)f S = 15MHz, f IN = 100kHz -47-dB f S = 15MHz, f IN = 4MHz -43-dB Signal to Noise Ratio (SINAD)f S = 15MHz, f IN = 100kHz -45-dB f S = 15MHz, f IN = 4MHz -35-dB Total Harmonic Distortion, THD f S = 15MHz, f IN = 100kHz --46-dBc f S = 15MHz, f IN = 4MHz --36-dBc Effective Number of Bits (ENOB)f S = 15MHz, f IN = 100kHz -7.2-Bits f S = 15MHz, f IN = 4MHz - 5.5-Bits Differential Gain Error Unadjusted -2-%Differential Phase Error Unadjusted -1-%ANALOG INPUTSFull Scale Range, V IN and (V REF +) - (V REF -)Notes 2, 44-7V Input Capacitance, V IN -30-pF Input Current, V IN , (See Text)V IN = 5V, V REF + = 5V-- 3.5mA REFERENCE INPUTS Ladder Impedance270500800Ω=RMSSignal RMSNoise--------------------------------=RMSSignalRMSNoise+Distortion -----------------------------------------------------------DIGITAL INPUTSLow Level Input Voltage, V OL CE1, CE2Note 4--0.2V DD V Phase, CLKNote 4--0.2V AAV High Level Input Voltage, V IN CE1, CE2Note 40.7V DD --V Phase, CLKNote 40.7V AA--V Input Leakage Current, I I (Except CLK Input)Note 3-±0.2±5µA Input Capacitance, C I -3-pFDIGITAL OUTPUTS Output Low (Sink) Current V O = 0.4V 410-mA Output High (Source) CurrentV O = 4.5V-4-6-mA Three-State Output Off-State Leakage Current, I OZ -±0.2±5µA Output Capacitance, C O -4-pF TIMING CHARACTERISTICS Auto Balance Time (φ1)33-∞ns Sample Time (φ2)Note 425-500ns Aperture Delay -15-ns Aperture Jitter -100-ps Data Valid Time, t D Note 4-5065ns Data Hold Time, t H Note 42540-ns Output Enable Time, t EN -18-ns Output Disable Time, t DIS-18-nsPOWER SUPPLY CHARACTERISTICS Device Current (I DD + I A ) (Excludes I REF )Continuous Conversion (Note 4)-3060mA Auto Balance (φ1)-3060mANOTES:1.A full scale sine wave input of greater than f CLOCK /2 or the specified input bandwidth (whichever is less) may cause an erroneous code. The -3dB bandwidth for frequency response purposes is greater than 30MHz.2.V IN (Full Scale) or V REF + should not exceed V AA + + 1.5V for accuracy.3.The clock input is a CMOS inverter with a 50k Ω feedback resistor and may be AC coupled with 1V P-P minimum source.4.Parameter not tested, but guaranteed by design or characterization.Timing WaveformsFIGURE 1.INPUT TO OUTPUT TIMING DIAGRAMElectrical SpecificationsAt 25o C, V AA + = V DD = 5V, V REF + = 6.4V, V REF - = V AA - = V SS , CLK = 15MHz,All Reference Points Adjusted, Unless Otherwise Specified (Continued)PARAMETERTEST CONDITIONSMINTYPMAXUNITSCOMPARATOR DATA IS LATCHED DECODED DATA IS SHIFTED TO OUTPUT REGISTERSφ2SAMPLEN φ2φ1φ1φ2CLOCK (PIN 18)IF PHASE (PIN 19)IS LOWCLOCK IF PHASE IS HIGH AUTO BALANCESAMPLE N + 1t Dt HDATA N - 2AUTO BALANCESAMPLE N + 2DATA N - 1DATA NFIGURE 2.OUTPUT ENABLE TIMING DIAGRAMFIGURE 3A.STANDBY IN INDEFINITE AUTO BALANCE (SHOWN WITH PHASE = LOW)FIGURE 3B.STANDBY IN SAMPLE (SHOWN WITH PHASE = LOW)FIGURE 3.PULSE MODE OPERATIONTiming Waveforms(Continued)t DISt ENHIGH IMPEDANCEDATACE1CE2BITS 1 - 8OFt DISt ENHIGH IMPEDANCEDATADATADATAHIGH IMPEDANCECLOCKDATAAUTO BALANCENO MAX LIMIT25ns MIN33ns MIN25ns MIN50ns MINAUTO BALANCESAMPLEN SAMPLE N + 1500ns 33ns MIN 25ns MIN50ns TYPAUTO BALANCESAMPLE N + 2AUTO BALANCESAMPLE N + 1SAMPLEN MAXDATACLOCKDATA N - 1DATA NTypical Performance CurvesFIGURE 4.DEVICE CURRENT vs SAMPLE FREQUENCY FIGURE 5.DEVICE CURRENT vs TEMPERATUREFIGURE 6.ENOB vs TEMPERATURE FIGURE 7.NON-LINEARITY vs TEMPERATUREFIGURE 8.NON-LINEARITY vs SAMPLE FREQUENCY FIGURE 9.NON-LINEARITY vs REFERENCE VOLTAGEf S (MHz)40353025201510302010I D D (m A )TEMPERATURE (o C)-50282726252423100500I D D (m A )-252575TEMPERATURE (o C)308.0907050E N O B (L S B )4060802010-10-20-30-407.87.67.47.27.06.86.66.46.26.0f S = 15MHz, f I = 1MHzTEMPERATURE (o C)301.00907050N O N -L I N E A R I T Y (L S B )4060802010-10-20-30-400.900.800.700.600.500.400.300.200.10INLDNL f S = 15MHzf S (MHz)1.2025155N O N -L I N E A R I T Y (L S B )10201.080.960.840.720.600.480.360.240.120INLDNL V REF (V)11.00753N O N -L I N E A R I T Y (L S B )2461.801.601.401.201.000.800.600.400.200INLDNLf S = 15MHzTheory of OperationA sequential parallel technique is used by the CA3318converter to obtain its high speed operation. The sequence consists of the “Auto-Balance” phase, φ1, and the “Sample Unknown” phase, φ2. (Refer to the circuit diagram.) Each conversion takes one clock cycle (see Note). With the phase control (pin 19) high, the “Auto-Balance” (φ1) occurs during the high period of the clock cycle, and the “Sample Unknown”(φ2) occurs during the low period of the clock cycle.NOTE:The device requires only a single phase clock The terminology of φ1 and φ2 refers to the high and low periods of the same clock.During the “Auto-Balance” phase, a transmission switch is used to connect each of the first set of 256 commutating capacitors to their associated ladder reference tap. Those tap voltages will be as follows:V TAP (N) = [(N/256) V REF ] - (1/512) V REF ]= [(2N - 1)/512] V REF ,Where:V TAP (n)= reference ladder tap voltage at point n,V REF = voltage across V REF - to V REF +,N= tap number (1 through 256).The other side of these capacitors are connected to single-stage amplifiers whose outputs are shorted to their inputs by switches. This balances the amplifiers at their intrinsic trip points, which is approximately (V AA + - V AA -)/2. The first set of capacitors now charges to their associated tap voltages.FIGURE 10.ENOB vs INPUT FREQUENCYTypical Performance Curves(Continued)f I (MHz)8.0 5.0E N O B (L S B )7.67.26.86.46.05.65.24.84.44.00.00.51.01.52.02.53.03.54.04.5f S = 15MHzPin Descriptions PIN NAMEDESCRIPTION1B1Bit 1 (LSB)Output Data Bits (High = True)2B2Bit23B3Bit34B4Bit45B5Bit 56B6Bit 67B7Bit 78B8Bit 8 (MSB)9OFOverflow101/4RReference Ladder 1/4 Point 11V SS Digital Ground12V DD Digital Power Supply, +5V 13CE2Three-State Output Enable Input, Active Low, See Truth Table.14CE1Three-State Output Enable Input Active High. See Truth Table.15V REF -Reference Voltage Negative Input 16V IN Analog Signal Input 17V AA -Analog Ground 18CLK Clock Input19PHASESample clock phase control input. When PHASE is low, “SampleUnknown” occurs when the clock is low and “Auto Balance” occurs when the clock is high (see text).201/2R Reference Ladder Midpoint 21V IN Analog Signal Input22V REF +Reference Voltage Positive Input 233/4R Reference Ladder 3/4 Point 24V AA +Analog Power Supply, +5VCHIP ENABLE TRUTH TABLECE1CE2B1 - B8OF 01Valid Valid 11Three-State Valid XThree-StateThree-StateX = Don’t CareAt the same time a second set of commutating capacitors and amplifiers is also auto-balanced. The balancing of the second-stage amplifier at its intrinsic trip point removes any tracking differences between the first and second amplifier stages. The cascaded auto-balance (CAB) technique, used here, increases comparator sensitivity and temperature tracking.In the “Sample Unknown” phase, all ladder tap switches and comparator shorting switches are opened. At the same time V lN is switched to the first set of commutating capacitors. Since the other end of the capacitors are now looking into an effectively open circuit, any input voltage that differs from the previous tap voltage will appear as a voltage shift at the comparator amplifiers. All comparators that had tap voltages greater than V lN will go to a “high” state at their outputs. All comparators that had tap voltages lower than V lN will go to a “low” state.The status of all these comparator amplifiers is AC coupled through the second-stage comparator and stored at the end of this phase (φ2) by a latching amplifier stage. The latch feeds a second latching stage, triggered at the end of φ1. This delay allows comparators extra settling time. The status of the comparators is decoded by a 256 to 9-bit decoder array, and the results are clocked into a storage register at the end of the next φ2.A 3-stage buffer is used at the output of the 9 storage regis-ters which are controlled by two chip-enable signals. CE1 will independently disable B1 through B6 when it is in a high state. CE2 will independently disable B1 through B8 and the OF buffers when it is in the low state.To facilitate usage of this device, a phase control input is provided which can effectively complement the clock as it enters the chip.Continuous-Clock OperationOne complete conversion cycle can be traced through the CA3318 via the following steps. (Refer to timing diagram.) With the phase control in a “low” state, the rising edge of the clock input will start a “sample” phase. During this entire “high” state of the clock, the comparators will track the input voltage and the first-stage latches will track the comparator outputs. At the falling edge of the clock, all 256 comparator outputs are captured by the 256 latches. This ends the “sam-ple” phase and starts the “auto-balance” phase for the com-parators. During this “low” state of the clock, the output of the latches settles and is captured by a second row of latches when the clock returns high. The second-stage latch output propagates through the decode array, and a 9-bit code appears at the D inputs of the output registers. On the next falling edge of the clock, this 9-bit code is shifted into the output registers and appears with time delay t D as valid data at the output of the three-state drivers. This also marks the end of the next “sample” phase, thereby repeating the conversion process for this next cycle.Pulse-Mode OperationThe CA3318 needs two of the same polarity clock edges to complete a conversion cycle: If, for instance, a negative going clock edge ends sample “N”, then data “N” will appear after the next negative going edge. Because of this require-ment, and because there is a maximum sample time of 500ns (due to capacitor droop), most pulse or intermittent sample applications will require double clock pulsing.If an indefinite standby state is desired, standby should be in auto-balance, and the operation would be as in Figure 3A. If the standby state is known to last less than 500ns and lowest average power is desired, then operation could be as in Figure 3B.Increased AccuracyIn most cases the accuracy of the CA3318 should be sufficient without any adjustments. In applications where accuracy is of utmost importance, five adjustments can be made to obtain better accuracy, i.e., offset trim; gain trim; and 1/4, 1/2 and 3/4 point trim.Offset TrimIn general, offset correction can be done in the preamp circuitry by introducing a DC shift to V lN or by the offset trim of the op amp. When this is not possible the V REF- input can be adjusted to produce an offset trim. The theoretical input voltage to produce the first transition is 1/2 LSB. The equa-tion is as follows:V lN (0 to 1 transition) = 1/2 LSB = 1/2 (V REF/256)= V REF/512.If V lN for the first transition is less than the theoretical, then a single-turn 50Ω pot connected between V REF- and ground will accomplish the adjustment. Set V lN to 1/2 LSB and trim the pot until the 0-to-1 transition occurs.If V lN for the first transition is greater than the theoretical, then the 50Ω pot should be connected between V REF- and a negative voltage of about 2 LSBs. The trim procedure is as stated previously.Gain TrimIn general, the gain trim can also be done in the preamp circuitry by introducing a gain adjustment for the op amp. When this is not possible, then a gain adjustment circuit should be made to adjust the reference voltage. To perform this trim, V lN should be set to the 255 to overflow transition. That voltage is 1/3 LSB less than V REF+ and is calculated as follows:V lN (255 to 256 transition) = V REF - V REF/512= V REF(511/512).To perform the gain trim, first do the offset trim and then apply the required V lN for the 255 to overflow transition. Now adjust V REF+ until that transition occurs on the outputs.1/4Point Trims The 1/4, 1/2 and 3/4 points on the reference ladder arebrought out for linearity adjusting or if the user wishes to create a nonlinear transfer function. The 1/4 points can be driven by the reference drivers shown (Figure 12) or by 2-K pots connected between V REF + and V REF -. The 1/2 (mid-)point should be set first by applying an input of 257/512 x (V REF ) and adjusting for an output changing from 128 to 129. Similarly the 1/4 and 3/4 points can be set with inputs of 129/512 and 385/512 x (V REF ) and adjusting for counts of 192 to 193 and 64 to 65. (Note that the points are actually 1/4, 1/2 and 3/4of full scale +1 LSB.)9-Bit ResolutionTo obtain 9-bit resolution, two CA3318s can be wired together. Necessary ingredients include an open-ended lad-der network, an overflow indicator, three-state outputs, and chip-enable controls - all of which are available on the CA3318.The first step for connecting a 9-bit circuit is to totem-pole the ladder networks, as illustrated in Figure 13. Since the absolute resistance value of each ladder may vary, external trim of the mid-reference voltage may be required.The overflow output of the lower device now becomes the ninth bit. When it goes high, all counts must come from the upper device. When it goes low, all counts must come from the lower device. This is done simply by connecting the lower overtlow signal to the CE1 control of the lower A/D converter and the CE2 control of the upper A/D converter. The three-state outputs of the two devices (bits 1 through 8) are now connected in parallel to complete the circuitry. The complete circuit for a 9-bit A/D converter is shown in Figure 13.Grounding/BypassingThe analog and digital supply grounds of a system should be kept separate and only connected at the A/D. This keeps digital ground noise out of the analog data to be converted.Reference drivers, input amps, reference taps, and the V AA supply should be bypassed at the A/D to the analog side of the ground. See Figure 15 for a block diagram of this con-cept. All capacitors shown should be low impedance 0.1µF ceramics and should be mounted as close to the A/D as pos-sible. If V AA + is derived from V DD , a small (10Ω resistor or inductor and additional filtering (4.7µF tantalum) may be used to keep digital noise out of the analog system.Input LoadingThe CA3318 outputs a current pulse to the V lN terminal at the start of every sample period. This is due to capacitor charging and switch feedthrough and varies with input volt-age and sampling rate. The signal source must be capable of recovering from the pulse before the end of the sample period to guarantee a valid signal for the A/D to convert.Suitable high speed amplifiers include the HA-5033,HA-2542; and CA3450. Figure 16 is an example of an ampli-fier which recovers fast enough for sampling at 15MHz.Output LoadingThe CMOS digital output stage, although capable of driving large loads, will reflect these loads into the local ground. It is recommended that a local QMOS buffer such as CD74HC541 E be used to isolate capacitive loads.DefinitionsDynamic Performance DefinitionsFast Fourier Transform (FFT) techniques are used to evaluate the dynamic performance of the converter. A low distortion sine wave is applied to the input, it is sampled, and the output is stored in RAM. The data is then transformed into the frequency domain with a 4096 point FFT and analyzed to evaluate the dynamic performance of the A/D. The sine wave input to the part is -0.5dB down from fullscale for all these tests.Signal-to-Noise (SNR)SNR is the measured RMS signal to RMS noise at a specified input and sampling frequency. The noise is the RMS sum of all of the spectral components except the fundamental and the first five harmonics.+10V TO 30VINPUT3218476+10µF, TAN18Ω(NOTE)5K IOT V REF +(PIN 22)4.7µF,CW(NOTE)1.5KCA3085E+TAN/IOVNOTE:Bypass V REF + to analog GND near A/D with 0.1µF ceramic cap. Parts noted should have low temperature drift.FIGURE 11.TYPICAL VOLTAGE REFERENCE SOURCE FORDRIVING V REF + INPUT10Ω3/4REF (PIN 23)10Ω1/2REF (PIN 20)10Ω1/4REF (PIN 10)CWCWCWV REF +(PIN 22)1K IOT510Ω+10V TO +30V 3411211K IOT1K IOT 510Ω7856109+-+-+-NOTES:1.All Op Amps = 3/4 CA324E.2.Bypass all reference points to analog ground near A/D with 0.1µF ceramic caps.3.Adjust V REF+ first, then 1/3, 3/4 and 1/4 points.FIGURE 12.TYPICAL 1/4 POINT DRIVERS FOR ADJUSTINGLINEARITY (USE FOR MAXIMUM LINEARITY)Signal-to-Noise + Distortion Ratio (SINAD)SINAD is the measured RMS signal to RMS sum of all other spectral components below the Nyquist frequency excluding DC. Effective Number of Bits (ENOB)The effective number of bits (ENOB) is derived from the SINAD data. ENOB is calculated from:ENOB = (SINAD - 1.76 + V CORR)/6.02,where:V CORR = 0.5dB.Total Harmonic Distortion (THD)THD is the ratio of the RMS sum of the first 5 harmonic components to the RMS value of the measured input signal.+6.4V REF+5VA VIN10V TO 6.4VNC+5VD+5V6.4V REFMID-POINTDRIVER+5VAADABIT 9BIT 8BIT 1CLOCKPHASEV REF+V AA+V AA-V INV INV REF-OFV DDBIT 8BIT 1CLPHCE2CE1V SSV REF+V INV INV AA+V AA-V REF-V DDCE2CE1OFBIT 8BIT 1CLPHV SSFIGURE ING TWO CA3318s FOR 9-BIT RESOLUTION4.7µF/10V TANTALUM+5V (ANALOG SUPPLY)+4V TO +6.5V REFERENCEOPTIONAL CAP (SEE TEXT)CLOCK SOURCEINPUT SIGNALAMPLIFIER/BUFFER(SEE TEXT)ADCA3318V AA +3/4REF V REF +V IN1/2REF PHASE CLK V AA -V IN V REF -CE1CE2ADIGITAL OUTPUTBIT 1BIT 2BIT 3BIT 4BIT 5BIT 6BIT 7BIT 8OVF1/4REF V SS V DDAD4.7µFTANTALUM/10V+5V (DIGITAL SUPPLY)0.01µF++FIGURE 14.TYPICAL CIRCUIT CONFIGURATION FOR THE CA3318 WITH NO LINEARITY ADJUSTSIGNAL SOURCESIGNAL GROUNDAMPREF-+ANALOG SUPPLIESV AA SUPPLYSYSTEM DIGITAL GROUNDTODIGITAL SYSTEMV DD SUPPLYV IN V IN V REF +REFERENCE TAPS V AA +V REF -V AA -OUTPUT DRIVERSV DD V SSFIGURE 15.TYPICAL SYSTEM GROUNDING/BYPASSING10Ω75Ω1V P-P VIDEO INPUT75Ω5pFNOTE:Ground-planing and tight layoutare extremely important.141193451213687+8V10ΩCA345039011075010Ω-4V 0.11621A/D FLASH INPUT0.001µF0.001µF0V TO -10VOFFSET SOURCE R S < 10ΩFIGURE 16.TYPICAL HIGH BANDWIDTH AMPLIFIER FOR DRIVING THE CA3318Reducing PowerMost power is consumed while in the auto-balance state. When operating at lower than 15MHz clock speed, power can be reduced by stretching the sample (φ2) time. The con-straints are a minimum balance time (φ1) of 33ns, and a maximum sample time of 500ns. Longer sample times cause droop in the auto-balance capacitors. Power can also be reduced in the reference string by switching the reference on only during auto-balance.Clock InputThe Clock and Phase inputs feed buffers referenced to V AA+ and V AA-. Phase should be tied to one of these two potentials, while the clock (if DC coupled) should be driven at least from 0.2 to 0.7 x (V AA+ - V AA-). The clock may also be AC coupled with at least a 1V P-P swing. This allows TTL drive levels or 5V QMOS levels when V AA+ is greater than 5V.TABLE 1.OUTPUT CODE TABLECODE DESCRIPTION(NOTE 1)INPUT VOLTAGE BINARY OUTPUT CODEDECIMALCOUNT V REF6.40V (V)V REF5.12V (V)OFMSBB8B7B6B5B4B3B2LSBB1Zero0.000.000000000000 1LSB0.0250.020********* 2LSB0.050.040000000102•••••••••••••••1/4Full Scale 1.60 1.2800100000064•••••••••••••••1/2Full Scale-1LSB 3.175 2.540011111111271/2Full Scale 3.20 2.560100000001281/2Full Scale+1LSB 3.225 2.58010000001129•••••••••••••••3/4Full Scale 4.80 3.84011000000192•••••••••••••••Full Scale-1LSB 6.35 5.08011111110254 Full Scale 6.375 5.10011111111255 Over Flow 6.40 5.12111111111511 NOTE:1.The voltages listed above are the ideal centers of each output code shown as a function of its associated reference voltage.All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification. Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reli-able. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.For information regarding Intersil Corporation and its products, see web site 。

卡乐IR33通用电子控制器用户手册Carel ir33 Universale electronic control-中文版

7. 参数表

44

7.1 只能通过串行连接读取的变量........................................49

8. 警报

50

8.1 警报类型.........................................................................................................50 8.2 手动复位警报..............................................................................................50 8.3 显示警报序列..............................................................................................50 8.4 警报列表.........................................................................................................50 8.5 警报参数.........................................................................................................52 8.6 警报参数.........................................................................................................52

2. 安装

SL33资料

SL32 THRU SL34LOW VF SURFACE MOUNT SCHOTTKY BARRIER RECTIFIERVOLTAGE - 20 to 40 Volts CURRENT - 3.0 AmperesFEATURESl Plastic package has Underwriters Laboratory Flammability Classification 94V-O l For surface mounted applications l Low profile package l Built-in strain relief l Metal to silicon rectifier majority carrier conductionl Low power loss, High efficiency l High current capability, low V Fl High surge capacityl For use in low voltage high frequency inverters, free wheeling, and polarity protection applications l High temperature soldering guaranteed: 260¢J /10 seconds at terminals MECHANICAL DA TACase: JEDEC DO-214AB molded plasticTerminals: Solder plated, solderable per MIL-STD-750, Method 2026Polarity: Color band denotes cathodeStandard packaging: 16mm tape (EIA-481)Weight: 0.007 ounce, 0.21 gramMAXIMUM RA TINGS AND ELECTRICAL CHARACTERISTICSRatings at 25¢J ambient temperature unless otherwise specified.Resistive or inductive load.SYMBOLS SL32SL33SL34UNITS Maximum Recurrent Peak Reverse Voltage V RRM 203040Volts Maximum RMS Voltage V RMS 142128Volts Maximum DC Blocking Voltage V DC 203040VoltsMaximum Average Forward Rectified Current at T L (See Figure 1)I (AV) 3.0Amps Peak Forward Surge Current 8.3ms single half sine-wave superimposed on rated load(JEDEC method)I FSM100.0Amps Maximum Instantaneous Forward Voltage at 3.0A (Note 1)V F 0.380.380.40Volts Maximum DC Reverse Current T A =25¢J (Note 1)At Rated DC Blocking Voltage T A =100¢J I R 0.520.0mA Maximum Thermal Resistance (Note 2)R £K JLR £K JA1755¢J /W Operating Junction Temperature Range T J -50 to +125¢J Storage Temperature Range T STG -50 to +150¢JNOTES:1. Pulse Test with PW=300£g s, 1% Duty Cycle.2. Mounted on P.C.Board with 14mm 2(.013mm thick) copper pad areas.S MC/DO-214ABRATING AND CHARACTERISTIC CURVES SL32 THRU SL34LEAD TEMPERATURE,¢JTYPICAL INSTANTANEOUS FORWARD CHARACTERISTICSFig. 1-FORWARD CURRENT DERATING CURVE Fig. 2-TYPICAL INSTANTANEOUS FORWARDCHARACTERISTICSREVERSE VOLTAGE. VOLTSFig. 4-TYPICAL JUNCTION CAPACITANCEPERCENT OF RATED PEAK REVERSE VOLTAGEFig. 3-TYPICAL REVERSE CHARACTERISTICSNUMBER OF CYCLES AT 60HzFig. 5-MAXIMUM NON-REPETITIVE PEAK FORWARDSURGE CURRENT。

P6KE33CA中文资料

PEAK PULSE POWER :600W (10/1000µs)BREAKDOWN VOLTAGE RANGE :From 6.8V to 440V.UNI AND BIDIRECTIONAL TYPES.LOW CLAMPING FACTOR.FAST RESPONSE TIME.UL RECOGNIZED.FEATURESCB417Symbol ParameterValue Unit P PP Peak pulse power dissipation (see note 1)Tj initial =T amb 600W P Power dissipation on infinite heatsink T amb =75°C 5W I FSM Non repetitive surge peak forward current For Unidirectional types.Tj initial =T amb tp =10ms100A T stg T j Storage temperature range Maximum junction temperature-65to +175175°C °C T LMaximum lead temperature for soldering during 10s at 5mm from case230°CNote 1:For a surge greater than the maximum values,the diode will fail in short-circuit.ABSOLUTE MAXIMUM RATINGS (Tamb =25°C)DESCRIPTIONTransil diodes provide high overvoltage protection by clamping action.Their instantaneous response to transient overvoltages makes them particularly suited to protect voltage sensitive devices such as MOS Technology and low voltage supplied IC’s.November 1998-Ed:2A P6KE6V8A/440A P6KE6V8CA/440CA®TRANSIL TMSymbol ParameterValue Unit R th (j-l)Junction-leads20°C/W R th (j-a)Junction to ambient on printed circuit.L lead =10mm75°C/WTHERMAL RESISTANCES 1/6I I FV F V CLV BRV RMI PPI RMVSymbol ParameterV RM Stand-off voltage.V BR Breakdown voltage.V CL Clamping voltage.I RM Leakage current @V RM .I PPSurge current.αTVoltage temperature coefficient.V FForward Voltage drop.ELECTRICAL CHARACTERISTICS (Tamb =25°C)TYPESI RM @V RM V BR@I RV CL @I PPV CL @I PPαT C maxminnom max max max maxtyp note210/1000µs 8/20µs note3note4Unidirectional Bidirectional µA V V V V mA V A V A 10-4/°C pF P6KE6V8A P6KE6.8CA 1000 5.8 6.45 6.87.141010.55713.4298 5.74000P6KE7V5A P6KE7.5CA 500 6.47.137.57.881011.35314.5276 6.13700P6KE10A P6KE10CA 108.559.51010.5114.54118.62157.52800P6KE12A P6KE12CA 510.211.41212.6116.73621.71847.82300P6KE15A P6KE15CA 112.814.31515.8121.22827.21478.41900P6KE18A P6KE18CA 115.317.11818.9125.22432.51238.81600P6KE22A P6KE22CA 118.820.92223.1130.62039.31029.21350P6KE24A P6KE24CA 120.522.82425.2133.21842.8939.41250P6KE27A P6KE27CA 123.128.72728.4137.51648.3839.61150P6KE30A P6KE30CA 125.628.53031.5141.514.553.5759.71075P6KE33A P6KE33CA 128.231.43324.7145.713.159689.81000P6KE36A P6KE36CA 130.834.23637.8149.91264.3629.9950P6KE39A P6KE39CA 133.337.13941.0153.911.169.75710.0900P6KE47A P6KE47CA 140.244.74749.4164.89.3844810.1800P6KE56A P6KE56CA 147.853.25658.81777.81004010.3700P6KE68A P6KE68CA 158.164.66871.4192 6.51213310.4625P6KE82A P6KE82CA 170.177.98286.11113 5.31462710.5550P6KE100A P6KE100CA 185.595.010******** 4.417822.510.6500P6KE120A P6KE120CA 11021141201261165 3.62121910.7450P6KE150A P6KE150CA 11281431501581207 2.92651510.8400P6KE180A P6KE180CA 11541711801891246 2.431712.610.8360P6KE200AP6KE200CA117119020021012742.235311.310.8350P6KExx2/6TYPESI RM @V RM V BR @I R V CL @I PP V CL @I PP αT C maxmin nom maxmaxmax max typ note210/1000µs 8/20µs note3note4Unidirectional Bidirectional µA V V V V mA V A V A 10-4/°C pF P6KE220A P6KE220CA 11882092202311328238810.310.8330P6KE250A P6KE250CA 121323725026313442442911310P6KE300A P6KE300CA 12562853003151414 1.65297.611290P6KE350A P6KE350CA 12993323503681482 1.6618 6.511270P6KE400A P6KE400CA 13423804004201548 1.3706 5.711360P6KE440AP6KE440CA137641844046216031.37765.211350Note 2:Pulse test :tp <50ms.Note 3:∆V BR =αT *(Ta -25)*V BR (25°C).Note 4V R =0V,F =1MHz.For bidirectional types,capacitance value is divided by 2.Fig 1:Peak pulse power dissipation versus initial junction temperature (printed circuit board).10s1000s%I PP 50tPULSE WAVEFORM 10/1000s100P6KExx3/60.0010.010.1110100Ppp (W)Fig.2:Peak pulse power versus exponentialpulse duration.Fig.3:Clamping voltage versus peak pulse current.exponentialwaveform :t p =20µs________t p =1ms-------------t p =10ms...............Note :The curves of the figure 3are specified for a junction temperature of 25°C beforesurge.The given results may be extrapolated for other junction temperatures by using the following formula :∆V (BR)= αT (V(BR))*[T a -25]*V (BR).For intermediate voltages,extrapolate the given results.P6KExx4/6Fig.6:Transient thermal impedance junction-am-bient versus pulse duration (For FR4PC Board with L lead =10mm).Fig.5:Peak forward voltage drop versus peak forward current (typical values for unidirectional types).Fig.4b :Capacitance versus reverse applied voltage for bidirectional types (typical values).Fig.4a :Capacitance versus reverse applied voltage for unidirectionaltypes (typical values).Note :multiply by 2for units with V BR >220V.Fig.7:Relative variation of leakage current versus junction temperature.P6KExx5/6Packaging:standard packaging is in tape and reel.PACKAGE MECHANICAL DATA CB417(Plastic)CAB O/O /DO /DCORDER CODEP6KE 100C A RLPACKAGING:=Ammopack tape RL =Tape and reel.REF.DIMENSIONSMillimetres Inches Min.Max.Min.Max.A 8.890.350B3.6830.145C 25.41.000D1.0920.043Weight =0.65g.600WBREAKDOWN VOLTAGEMARKING :Logo,Date Code,Type Code,Cathode Band (for unidirectional types only).BIDIRECTIONALInformation furnished is believed to be accurate and reliable.However,STMicroelectronics assumes no responsIbility for the consequences ofuse of such information nor for any infringement of patents or other rights of third parties which may result from its use.No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics.Specifications mentioned in this publication are subject to change without notice.This publication supersedes and replaces all information previously supplied.STMicroelectronics products are not authorized for use as critical component s in life support devices or systems without express written ap-proval of STMicroelectronics.The ST logo is a registered trademark of STMicroelectronics ©1998STMicroelectronics -Printed in Italy -All rights reserved.STMicroelectronics GROUP OF COMPANIESAustralia -Brazil -Canada -China -France -Germany -Italy -Japan -Korea -Malaysia -Malta -Mexico -Morocco -The Netherlands -Singapore -Spain -Sweden -Switzerland -Taiwan -Thailand -United Kingdom -U.S.A.P6KExx6/6。

88C33L-AF5-R资料