74ls573中文资料

74AC573介绍

74HC573和74LS373原理一样,8数据锁存器。

主要用于数码管、按键等等的控制1. 真值表参见74LS373的PDF的第2页:Dn LE OE OnH H L HL H L LX L L QoX X H Z这个就是真值表,表示这个芯片在输入和其它的情况下的输出情况。

每个芯片的数据手册(datasheet)中都有真值表。

布尔逻辑比较简单,在此不赘述;2. 高阻态就是输出既不是高电平,也不是低电平,而是高阻抗的状态;在这种状态下,可以多个芯片并联输出;但是,这些芯片中只能有一个处于非高阻态状态,否则会将芯片烧毁;高阻态的概念在RS232和RS422通讯中还可以用到。

3. 数据锁存当输入的数据消失时,在芯片的输出端,数据仍然保持;这个概念在并行数据扩展中经常使用到。

4. 数据缓冲加强驱动能力。

74LS244/74LS245/74LS373/74LS573都具备数据缓冲的能力。

OE:output_enable,输出使能;LE:latch_enable,数据锁存使能,latch是锁存的意思;Dn:第n路输入数据;On:第n路输出数据;再看这个真值表,意思如下:第四行:当OE=1是,无论Dn、LE为何,输出端为高阻态;第三行:当OE=0、LE=0时,输出端保持不变;第二行第一行:当OE=0、LE=1时,输出端数据等于输入端数据;结合下面的波形图,在实际应用的时候是这样做的:a. OE=0;b.先将数据从单片机的口线上输出到Dn;c.再将LE从0->1->0d.这时,你所需要输出的数据就锁存在On上了,输入的数据在变化也影响不到输出的数据了;实际上,单片机现在在忙着干别的事情,串行通信、扫描键盘……单片机的资源有限啊。

在单片机按照RAM方式进行并行数据的扩展时,使用movx @dptr, A这条指令时,这些时序是由单片机来实现的。

后面的表格中还有需要时间的参数,你不需要去管它,因为这些参数都是几十ns级别的,对于单片机在12M下的每个指令周期最小是1us的情况下,完全可以实现;如果是你自己来实现这个逻辑,类似的指令如下:mov P0,A ;将数据输出到并行数据端口clr LEsetb LEclr LE ;上面三条指令完成LE的波形从0->1->0的变化74ls573跟74LS373逻辑上完全一样,只不过是管脚定义不一样,数据输入和输出端。

完整word版74HC573功能说明原创编辑

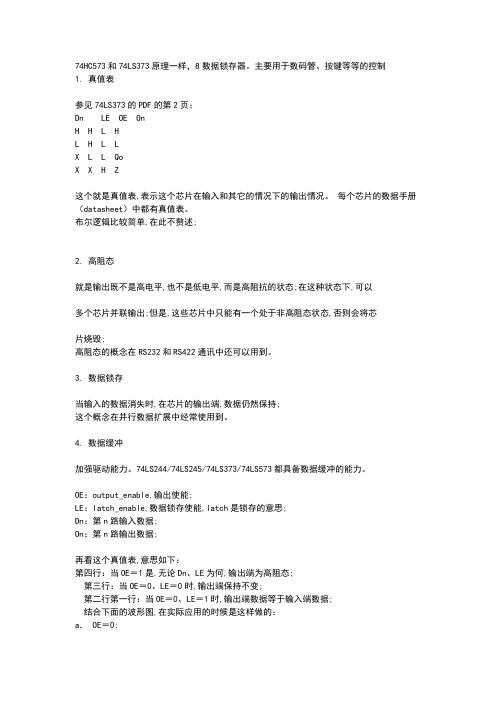

1锁存器的功74CH5774LS37原理一样数据锁存器。

主要用于数码管、按键等等的控74HC57个脚,数据的进和出没有逻辑关系,这个芯片主要是看高电压激活还是274HC57电压激活是低电压激活芯D7D2~脚是数据的输入脚脚是接1脚是高电压激活芯112~1脚是数据的输出是电20121.真值表意思如下:74HC573真值表,1时,输出端数据等于输入端数据;、LE==?第一行/第二行:当OE0 时,输出端保持不变;=、LE0?第三行:当OE=0 为何,输出端为高阻态;Dn、LE 第四行:当OE=1是无论? 2. 高阻态在这种状态下,可以多而是高阻抗的状态;就是输出既不是高电平,也不是低电平,这些芯片中只能有一个处于非高阻态状态,否则会将芯片烧毁。

高个芯片并联输出;但是,通讯中还可以用到。

RS422 阻态的概念在RS232和数据锁存3.数据仍然保持;这个概念在并行数据扩展中当输入的数据消失时,在芯片的输出端, 经常使用到。

4. 数据缓冲加强驱动能力:74LS244/74LS245/74LS373/74LS573都具备数据缓冲的能力。

,输出使能;:output_enable? OE 是锁存的意思;atch:latch_enable,数据锁存使能,LE?路输入数据;:第n ?Dn 路输出数据;On :第n?23在实际应用的时候是这样做的:74HC573波形图,;OE=0a.;先将数据从单片机的口线上输出到Dnb.从0->1->0 ;c.再将LE 这时,你所需要输出的数据就锁存在On上了,输入的数据在变化也影响不到输d.……单出的数据了;实际上,单片机现在在忙着干别的事情,串行通信、扫描键盘片机的资源有限啊。

这条方式进行并行数据的扩展时RAM,使用movx @dptr, A在单片机按照指令时,这些时序是由单片机来实现的。

因为这些参数都是几后面的表格中还有需要时间的参数,你不需要去管它,的情况下,完12M下的每个指令周期最小是1us十ns级别的,对于单片机在全可以实现;如果是你自己来实现这个逻辑,类似的指令如下:MOV P0,A ; //将数据输出到并行数据端口LE CLRSETB LE的波形从LE ; //上面三条指令完成LE0->1->0的变化CLR数据输入和,,74LS37374LS573跟逻辑上完全一样只不过是管脚定义不一样输出端.3。

74ls573

首先说74LS373不是单片机,而是一个逻辑芯片,看下面:

74ls373是常用的地址锁存器芯片,它实质是一个是带三态缓冲输出的8D触发器,在单片机系统中为了扩展外部存储器,通常需要一块74ls373芯片。

<74ls373内部结构图> <74ls373引脚图>

(1).1脚是输出使能(OE),是低电平有效,当1脚是高电平时,不管输入3、4、7、8、13、14、17、18如何,也不管11脚(锁存控制端,G)如何,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)全部呈现高阻状态(或者叫浮空状态);

(2).当1脚是低电平时,只要11脚(锁存控制端,G)上出现一个下降沿,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)立即呈现输入脚3、4、7、8、13、14、17、18的状态.

锁存端LE 由高变低时,输出端8 位信息被锁存,直到LE 端再次有效。

当三态门使能信号OE为低电平时,三态门导通,允许Q0~Q7输出,OE为高电平时,输出悬空。

当74LS373用作地址锁存器时,应使OE为低电平,此时锁存使能端C为高电平时,输出Q0~Q7 状态与输入端D1~D7状态相同;当C发生负的跳变时,输入端D0~D7 数据锁入Q0~Q7。

51单片机的ALE信号可以直接与74LS373的C连接。

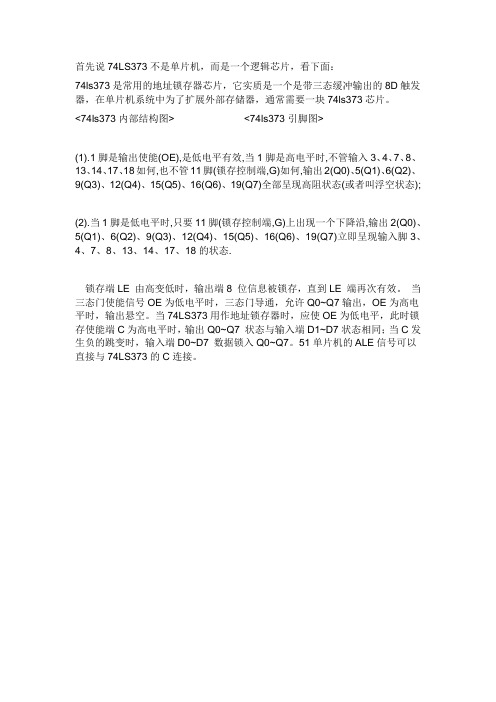

SN74LS57中文资料

IMPORTANT NOTICETexas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage (“Critical Applications”).TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.In order to minimize risks associated with the customer’s applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.Copyright © 1996, Texas Instruments Incorporated。

74ls573中文资料

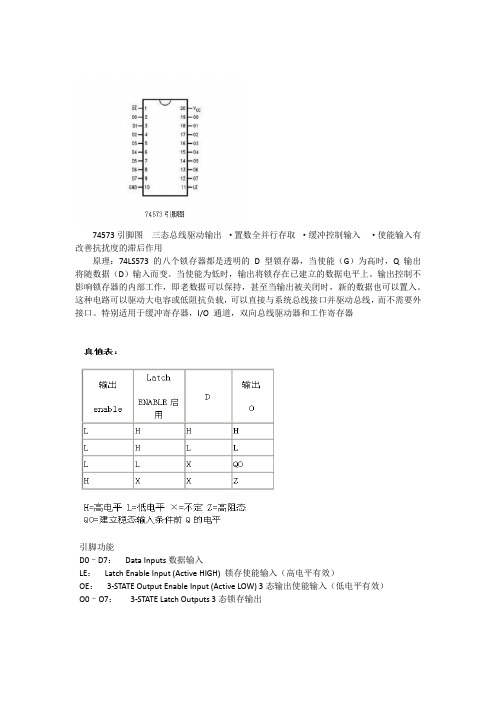

74ls573中文资料三态总线驱动输出·置数全并行存取·缓冲控制输入·使能输入有改善抗扰度的滞后作用原理:74LS573 的八个锁存器都是透明的D 型锁存器,当使能(G)为高时,Q 输出将随数据(D)输入而变。

当使能为低时,输出将锁存在已建立的数据电平上。

输出控制不影响锁存器的内部工作,即老数据可以保持,甚至当输出被关闭时,新的数据也可以置入。

这种电路可以驱动大电容或低阻抗负载,可以直接与系统总线接口并驱动总线,而不需要外接口。

特别适用于缓冲寄存器,I/O 通道,双向总线驱动器和工作寄存器。

H=高电平 L=低电平×=不定 Z=高阻态QO=建立稳态输入条件前Q的电平引脚图及功能图Operating Conditions 操作条件Symbol 符号Parameter 参数DM74LS最小典型最大VCC Supply Voltage 电源电压 4.75 5 5.25VIH High Level Input Voltage输入高电平电压 2 - -VIL LOW Level Input Voltage 输入低电平电压- - 0.8IOH HIGH Level Input Current输入高电平电流- - −2.6IOL LOW Level Output Current低电平输出电流- - 24TA Free Air Operating Temperature工作温度0 - 70Note 1: The “Absolute Maximum Ratings” are those values beyond which the safety of th cannot be guaranteed. The device should not be operated at these limits. The parametri defined in the “Electrical Characteristics” table are not guaranteed at the absolute ratings. The “Recommended Operating Conditions” table will define the conditions fo device operation.Electrical Characteristics 直流电气特性Over recommended operating free air temperature range (unless otherwise noted)Symbol 符号Parameter 参数Conditions 条件最小典型最大单VI Input Clamp Voltage输入钳位电压VCC=最小, II=−18 mA - - −1.5VOH High Level OutputVoltage输出高电平电压VCC = 最小, IOH=最大,VIL = 最大2.73.4 -VOL Low Level OutputVoltage输出低电平电压VCC = 最小, IOL=最大- 0.35 0.5VIH = 最小- - -。

74H573介绍

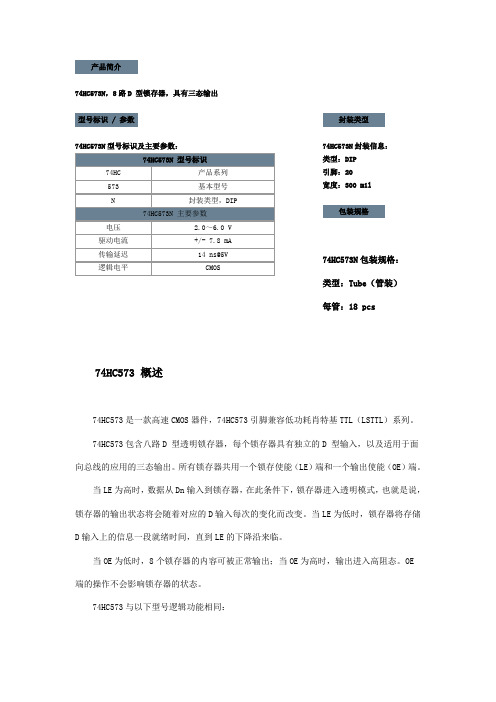

74HC573N,8路D 型锁存器,具有三态输出74HC573N型号标识及主要参数:74HC573N封装信息:类型:DIP引脚:20宽度:300 mil74HC573N包装规格:类型:Tube(管装)每管:18 pcs74HC573 概述74HC573是一款高速CMOS器件,74HC573引脚兼容低功耗肖特基TTL(LSTTL)系列。

74HC573包含八路D 型透明锁存器,每个锁存器具有独立的D 型输入,以及适用于面向总线的应用的三态输出。

所有锁存器共用一个锁存使能(LE)端和一个输出使能(OE)端。

当LE为高时,数据从Dn输入到锁存器,在此条件下,锁存器进入透明模式,也就是说,锁存器的输出状态将会随着对应的D输入每次的变化而改变。

当LE为低时,锁存器将存储D输入上的信息一段就绪时间,直到LE的下降沿来临。

当OE为低时,8个锁存器的内容可被正常输出;当OE为高时,输出进入高阻态。

OE端的操作不会影响锁存器的状态。

74HC573与以下型号逻辑功能相同:74HC563,但输出为反相74HC373,但引脚布局不同74HC573 参数74HC573 基本参数电压 2.0~6.0V 驱动电流+/-7.8 mA 传输延迟14 ns@5V 74HC573 其他特性逻辑电平CMOS功耗考量低功耗或电池供电应用74HC573 封装与引脚SO20, SSOP20, DIP20, TSSOP2074HC573 特性∙输入输出分布在芯片封装的两侧,为微处理器提供简便的接口∙用于微控制器和微型计算机的输入输出口∙三态正相输出,用于面向总线的应用∙共用三态输出使能端∙逻辑功能与74HC563、74HC373相同∙遵循JEDEC标准no.7A∙ESD保护o HBM EIA/JESD22-A114-C超过2000 Vo MM EIA/JESD22-A115-A超过200 V∙温度范围o-40~+85 ℃o-40~+125 ℃。

74573锁存器 STC12c5a60s2 资料

74573引脚图三态总线驱动输出·置数全并行存取·缓冲控制输入·使能输入有改善抗扰度的滞后作用原理:74LS573 的八个锁存器都是透明的 D 型锁存器,当使能(G)为高时,Q 输出将随数据(D)输入而变。

当使能为低时,输出将锁存在已建立的数据电平上。

输出控制不影响锁存器的内部工作,即老数据可以保持,甚至当输出被关闭时,新的数据也可以置入。

这种电路可以驱动大电容或低阻抗负载,可以直接与系统总线接口并驱动总线,而不需要外接口。

特别适用于缓冲寄存器,I/O 通道,双向总线驱动器和工作寄存器引脚功能D0–D7:Data Inputs数据输入LE:Latch Enable Input (Active HIGH) 锁存使能输入(高电平有效)OE:3-STATE Output Enable Input (Active LOW) 3态输出使能输入(低电平有效)O0–O7:3-STATE Latch Outputs 3态锁存输出Operating Conditions 操作条件VCC :Supply Voltage 电源电压最小4.75V最大5.25VVIH :High Level Input Voltage输入高电平电压最小2VVIL:LOW Level Input Voltage 输入低电平电压最大0.8VIOH:HIGH Level Input Current输入高电平电流最大-2.6mAIOL:LOW Level Output Current低电平输出电流最大24mATA :Free Air Operating Temperature工作温度最大70摄氏度直流电气特性VI Input Clamp Voltage输入钳位电压VCC=最小, II=−18 mA - - −1.5 VVOH High Level OutputVoltage输出高电平电压VCC = 最小, IOH=最大,VIL = 最大 2.7 3.4 - VVOL Low Level OutputVoltage输出低电平电压VCC = 最小, IOL=最大- 0.35 0.5 - VIH = 最小- - - VIOL=4 mA, VCC=最小- - - -II Input Current @ 最大Input Voltage输入电压VCC=最大, VI=7V - - 1 mAIIH HIGH Level Input Current输入高电平电流VCC=最大, VI=2.7V - - 20 μAIIL LOW Level Input Current低电平输入电流VCC=最大, VI=0.4V - - −0.4 mAIOS Short CircuitOutput Current输出短路电流VCC=最大(Note 3) −30 - −130 mA -ICC Supply Current电源电流VCC=最大- - 50 mAIOZH 3-STATE Outputoff Current High 3态输出高阻态时高电平电流IOZL 3-STATE Outputoff Current Low 3态输出高阻态时低电平电流tPLH tPHL Propagation Delay传播延迟tPLH tPHL Propagation Delay传播延迟LE to Q - 36 25 ns tPZH tPZL 3-STATE Enable Time3态启用时间OE to Q - 20 25 nstPHZ tPLZ 3-STATE Enable Time3态启用时间OE to Q - 20 25 nsts(H)ts(L) Setup Time (High/Low) 设置时间(高/低)Data to LE 3 7 - nsth(H)th(L) Hold Time (High/Low)保持时间(高/低)Le Data to LE 10 10 - ns tw(H) - Pulse Width (High) 脉冲宽度(高)LeData to LE 15 - - ns看一下STC12C5A60S2系列1T单片机的功能就明白较89C51的优势了: 1.增强型8051 CPU,1T,单时钟/ 机器周期,指令代码完全兼容传统8051 2.工作电压:STC12C5A60S2 系列工作电压:5.5V - 3.3V STC12LE5A60S2 系列工作电压:3.6V - 2.2V 3. 工作频率范围:0 - 35MHz,相当于普通8051 的0~420MHz 4. 用户应用程序空间8K /16K / 20K / 32K / 40K / 48K / 52K / 60K / 62K 字节...... 5. 片上集成1280 字节RAM 6. 通用I/O 口(36/40/44 个),复位后为:准双向口/ 弱上拉(普通8051 传统I/O 口)可设置成四种模式:准双向口/ 弱上拉,推挽/ 强上拉,仅为输入/ 高阻,开漏每个I/O 口驱动能力均可达到20mA,但整个芯片最大不要超过120mA 7. I S P(在系统可编程)/IAP (在应用可编程),无需专用编程器,无需专用仿真器可通过串口(P3.0/P3.1)直接下载用户程序,数秒即可完成一片8. 有EEPROM 功能(STC12C5A62S2/AD/PWM 无内部EEPROM) 9. 看门狗10.内部集成MAX810 专用复位电路(外部晶体12M 以下时,复位脚可直接1K 电阻到地)11. 外部掉电检测电路: 在P4.6 口有一个低压门槛比较器5V 单片机为1.32V,误差为+/-5%,3.3V 单片机为1.30V,误差为+/-3% 12. 时钟源:外部高精度晶体/ 时钟,内部R/C 振荡器(温漂为+/-5% 到+/-10% 以内) 用户在下载用户程序时,可选择是使用内部R/C 振荡器还是外部晶体/ 时钟常温下内部R/C 振荡器频率为:5.0V 单片机为:11MHz ~15.5MHz 3.3V 单片机为:8MHz ~12MHz 精度要求不高时,可选择使用内部时钟,但因为有制造误差和温漂,以实际测试为准13. 共4 个16 位定时器:两个与传统8051 兼容的定时器/ 计数器,16 位定时器T0 和T1,没有定时器2,但有独立波特率发生器,做串行通讯的波特率发生器,再加上2 路PCA 模块可再实现2 个16 位定时器14. 2 个时钟输出口,可由T0 的溢出在P3.4/T0 输出时钟,可由T1 的溢出在P3.5/T1 输出时钟15. 外部中断I/O 口7 路,传统的下降沿中断或低电平触发中断,并新增支持上升沿中断的PCA 模块,Power Down 模式可由外部中断唤醒,INT0/P3.2, INT1/P3.3, T0/P3.4, T1/P3.5, RxD/P3.0, CCP0/P1.3(也可通过寄存器设置到P4.2 ), CCP1/P1.4 (也可通过寄存器设置到P4.3) 16. PWM(2 路)/PCA(可编程计数器阵列,2 路)--- 也可用来当2 路D/A 使用--- 也可用来再实现2 个定时器--- 也可用来再实现2 个外部中断(上升沿中断/ 下降沿中断均可分别或同时支持) 17. A/D 转换, 10 位精度ADC,共8 路,转换速度可达250K/S(每秒钟25 万次) 18. 通用全双工异步串行口(UART),由于STC12 系列是高速的8051,可再用定时器或PCA 软件实现多串口19. STC12C5A60S2 系列有双串口,后缀有S2 标志的才有双串口,RxD2/P1.2(可通过寄存器设置到P4.2),TxD2/P1.3(可通过寄存器设置到P4.3) 20. 工作温度范围:-40 - +85℃(工业级) / 0 - 75℃(商业级) 21. 封装:PDIP-40,LQFP-44,LQFP-48 I/O 口不够时,可用 2 到 3 根普通I/O 口线外接74HC164/165/595(均可级联)来扩展I/O 口,还可用A/D 做按键扫描来节省I/O 口,或用双CPU,三线通信,还多了串口。

74LV573A中文资料

74LV573A中⽂资料PACKAGING INFORMATIONOrderable Device Status (1)Package Type Package Drawing Pins Package Qty Eco Plan (2)Lead/Ball Finish MSL Peak Temp (3)SN74LV573ADBR ACTIVE SSOP DB 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573ADBRE4ACTIVE SSOPDB 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573ADGVR ACTIVE TVSOP DGV 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573ADGVRE4ACTIVE TVSOP DGV 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573ADW ACTIVE SOIC DW 2025Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573ADWE4ACTIVE SOIC DW 2025Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573ADWR ACTIVE SOIC DW 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573ADWRE4ACTIVE SOIC DW 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573AGQNRACTIVEBGA MI CROSTA R JUNI ORGQN201000TBDSNPBLevel-1-240C-UNLIMSN74LV573ANSR ACTIVE SO NS 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573ANSRE4ACTIVE SO NS 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573APW ACTIVE TSSOP PW 2070Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573APWE4ACTIVE TSSOP PW 2070Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573APWR ACTIVE TSSOP PW 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573APWRE4ACTIVE TSSOP PW 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573APWRG4ACTIVE TSSOP PW 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573APWT ACTIVE TSSOP PW 20250Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573APWTE4ACTIVE TSSOP PW 20250Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573ARGYR ACTIVE QFN RGY 201000Green (RoHS &no Sb/Br)CU NIPDAU Level-2-260C-1YEAR SN74LV573ARGYRG4ACTIVE QFN RGY 201000Green (RoHS &no Sb/Br)CU NIPDAU Level-2-260C-1YEAR SN74LV573AZQNRACTIVEBGA MI CROSTA R JUNI ORZQN201000Green (RoHS &no Sb/Br)SNAGCULevel-1-260C-UNLIM(1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part ina new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan-The planned eco-friendly classification:Pb-Free(RoHS),Pb-Free(RoHS Exempt),or Green(RoHS&no Sb/Br)-please check /doc/c811093619.html/productcontent for the latest availability information and additional product content details.TBD:The Pb-Free/Green conversion plan has not been defined.Pb-Free(RoHS):TI's terms"Lead-Free"or"Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all6substances,including the requirement that lead not exceed0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Pb-Free(RoHS Exempt):This component has a RoHS exemption for either1)lead-based flip-chip solder bumps used between the die and package,or2)lead-based die adhesive used between the die and leadframe.The component is otherwise considered Pb-Free(RoHS compatible)as defined above.Green(RoHS&no Sb/Br):TI defines"Green"to mean Pb-Free(RoHS compatible),and free of Bromine(Br)andAntimony(Sb)based flame retardants(Br or Sb do not exceed0.1%by weight in homogeneous material)(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.。

74hc573中文资料参数

74hc573中文资料参数

特点:

·三态总线驱动输出

·置数全并行存取

·缓冲控制输入

·使能输入有改善抗扰度的滞后作用

原理说明:

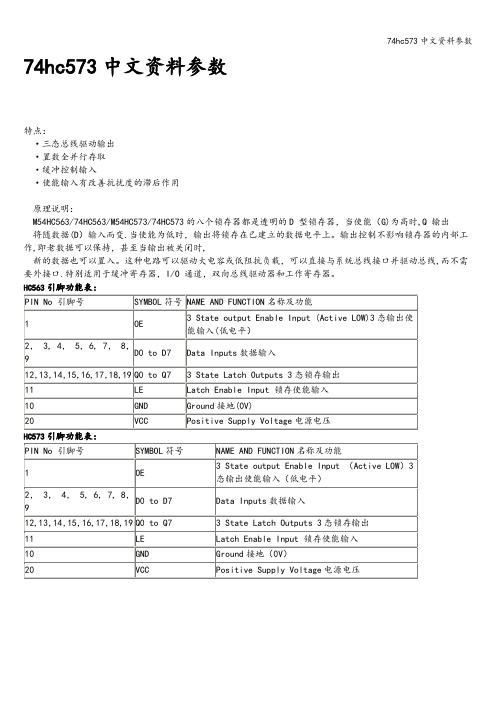

M54HC563/74HC563/M54HC573/74HC573的八个锁存器都是透明的D 型锁存器,当使能(G)为高时,Q 输出将随数据(D)输入而变.当使能为低时,输出将锁存在已建立的数据电平上。

输出控制不影响锁存器的内部工作,即老数据可以保持,甚至当输出被关闭时,

新的数据也可以置入。

这种电路可以驱动大电容或低阻抗负载,可以直接与系统总线接口并驱动总线,而不需要外接口.特别适用于缓冲寄存器,I/O 通道,双向总线驱动器和工作寄存器。

图1 HC573引脚

图图2 HC573 国际电工委员会逻辑符号

图3 HC563引脚

图图4 HC563 国际电工委员会逻辑符号

图5 HC563 逻辑图

图6 HC573 逻辑图

图7 输入输出等效电路

真值表:

INPUTS 输入Outputs输出

OE LE D Q (HC573) Q (HC563)

H X X Z Z

L L X NO CHANGE *NO CHANGE *

L H L L H

L H H H L

ABSOLUTE MAXIMUM RATINGS绝对最大额定值:

Symbol 符号Parameter 参数Value 数值Unit 单位

RECOMMENDED OPERATING CONDITIONS建议操作条件:

DC SPECIFICATIONS直流电气规格:

应用电路图:点击图片查看大图

图8

图9。

74573引脚图

8D数据锁存器和373一样

74573引脚图

三态总线驱动输出

·置数全并行存取

·缓冲控制输入

·使能输入有改善抗扰度的滞后作用

原理:74LS573 的八个锁存器都是透明的D 型锁存器,当使能(G)为高时,Q 输出将随数据(D)输入而变。

当使能为低时,输出将锁存在已建立的数据电平上。

输出控制不影响锁存器的内部工作,即老数据可以保持,甚至当输出被关闭时,新的数据也可以置入。

这种电路可以驱动大电容或低阻抗负载,可以直接与系统总线接口并驱动总线,而不需要外接口。

特别适用于缓冲寄存器,I/O 通道,双向总线驱动器和工作寄存器。

真值表:

输出enable

Latch

ENABLE启

用

D

输出

O

L H H H L H L L L L X QO H X X Z

H=高电平 L=低电平×=不定 Z=高阻态QO=建立稳态输入条件前Q的电平

引脚功能表:

Operating Conditions 操作条件。

HD74LVC573AT资料

HD74LVC573AOctal D-type Transparent Latches with 3-state OutputsADE-205-116B(Z)3rd EditionDecember 1996 DescriptionThe HD74LVC573A has eight D type latches with three state outputs in a 20 pin package. When the latch enable input is high, the Q outputs will follow the D inputs. When the latch enable goes low, data at the D inputs will be retained at the outputs until latch enable returns high again. When a high logic level is applied to the output control input, all outputs go to a high impedance state, regardless of what signals are present at the other inputs and the state of the storage elements. Low voltage and high speed operation is suitable at the battery drive product (note type personal computer) and low power consumption extends the life of a battery for long time operation.Features•V CC = 2.0 V to 5.5 V•All inputs V IH (Max.) = 5.5 V (@V CC = 0 V to 5.5 V)•All outputs V OUT (Max.) = 5.5 V (@V CC = 0 V or output off state)•Typical V OL ground bounce < 0.8 V (@V CC = 3.3 V, Ta = 25°C)•Typical V OH undershoot > 2.0 V (@V CC = 3.3 V, Ta = 25°C)•High output current ±24 mA (@V CC = 3.0 V to 5.5 V)HD74LVC573ARev.3, Dec. 1996, page 2 of 11Function TableInputsOC LE D Output Q L H H H L H L L L L X Q 0H XXZH :High level L :Low level X :ImmaterialZ :High impedanceQ 0 :Level of Q before the indicated steady input conditions were established.Pin ArrangementHD74LVC573ARev.3, Dec. 1996, page 3 of 11Absolute Maximum RatingsItemSymbol Ratings Unit ConditionsSupply voltage V CC –0.5 to 6.0V Input diode current I IK –50mA V I = –0.5 V Input voltage V I –0.5 to 6.0V Output diode current I OK –50mA V O = –0.5 V 50mA V O = V CC +0.5 V Output voltage V O –0.5 to V CC +0.5V Output "H" or "L"–0.5 to 6.0V Output "Z" or V CC :OFF Output current I O±50mA V CC , GND current / pin I CC or I GND 100mA Storage temperatureTstg–65 to +150°CNote:The absolute maximum ratings are values which must not individually be exceeded, and furthermore,no two of which may be realized at the same time.Recommended Operating ConditionsItemSymbol Ratings Unit Conditions Supply voltage V CC 1.5 to 5.5V Data hold 2.0 to 5.5V At operation Input / output voltageV I 0 to 5.5V OC , LE, D V O0 to V CC V Output "H" or "L"0 to 5.5V Output "Z" or V CC :OFFOperating temperature Ta –40 to 85°C Output currentI OH –12mA V CC = 2.7 V –24*2mA V CC = 3.0 V to 5.5 V I OL12mA V CC = 2.7 V 24*2mA V CC = 3.0 V to 5.5 V Input rise / fall time *1t r , t f10ns/VNotes: 1.This item guarantees maximum limit when one input switches.Waveform : Refer to test circuit of switching characteristics.2.duty cycle ≤ 50%HD74LVC573ARev.3, Dec. 1996, page 4 of 11Electrical CharacteristicsTa = –40 to 85°CItem Symbol V CC (V)Min Max Unit Test Conditions Input voltageV IH 2.7 to 3.6 2.0—V 4.5 to 5.5V CC ×0.7—V V IL2.7 to3.6—0.8V 4.5 to 5.5—V CC ×0.3V Output voltageV OH2.7 to 5.5V CC –0.2—V I OH = –100 µA 2.7 2.2—V I OH = –12 mA3.0 2.4—V 3.0 2.2—V I OH = –24 mA4.53.8—V V OL2.7 to 5.5—0.2V I OL = 100 µA 2.7—0.4V I OL = 12 mA3.0—0.55V I OL = 24 mA4.5—0.55V Input currentI IN 0 to 5.5—±5.0µA V IN = 5.5 V or GND Off state output current I OZ 2.7 to 5.5—±5.0µA V IN = V CC , GNDV OUT = 5.5 V or GND Output leak currentI OFF0—20µA V IN / V OUT = 5.5 V Quiescent supply current I CC2.7 to3.6—±10µA V IN / V OUT = 3.6 to 5.5 V 2.7 to 5.5—10µA V IN = V CC or GND∆I CC3.0 to 3.6—500µAV IN = one input at(V CC –0.6)V,other inputs at V CC or GNDHD74LVC573ARev.3, Dec. 1996, page 5 of 11Switching CharacteristicsTa = –40 to 85°CItemSymbol V CC (V)Min Typ Max Unit From (Input)To (Output)Propagation delay timet PLH 2.7——9.0ns DQt PHL 3.3±0.3 1.5—8.0ns 5.0±0.5—— 6.5ns t PLH 2.7——9.5ns LEQt PHL3.3±0.3 1.5—8.5ns 5.0±0.5——7.0ns Output enable timet ZH 2.7——9.5ns OCQt ZL3.3±0.3 1.5—8.5ns 5.0±0.5——7.0ns Output disable timet HZ 2.7——8.5ns OCQt LZ3.3±0.3 1.5—7.5ns 5.0±0.5—— 6.5ns Setup timet su2.7 2.0——ns3.3±0.3 2.0——ns 5.0±0.52.0——ns Hold timet h2.7 1.5——ns3.3±0.3 1.5——ns 5.0±0.51.5——ns Pulse widtht w2.73.3——ns 3.3±0.3 3.3——ns 5.0±0.53.3——ns Between output pins skew *1t OSLH 2.7———ns t OSHL3.3±0.3—— 1.0ns 5.0±0.5—— 1.0ns Input capacitance C IN 2.7— 3.0—pF Output capacitance C O2.7—15.0—pFNote:1.This parameter is characterized but not tested.tos LH = | t PLHm - t PLHn |, tos HL = | t PHLm - t PHLn |HD74LVC573ATest CircuitWaveforms – 1Rev.3, Dec. 1996, page 6 of 11HD74LVC573A Waveforms – 2Waveforms – 3Rev.3, Dec. 1996, page 7 of 11HD74LVC573A Waveforms – 4Rev.3, Dec. 1996, page 8 of 11HD74LVC573A Package DimensionsRev.3, Dec. 1996, page 9 of 11HD74LVC573ARev.3, Dec. 1996, page 10 of 11HD74LVC573ARev.3, Dec. 1996, page 11 of 11Disclaimer1.Hitachi neither warrants nor grants licenses of any rights of Hitachi’s or any third party’s patent,copyright, trademark, or other intellectual property rights for information contained in this document.Hitachi bears no responsibility for problems that may arise with third party’s rights, including intellectual property rights, in connection with use of the information contained in this document.2.Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.3.Hitachi makes every attempt to ensure that its products are of high quality and reliability. However,contact Hitachi’s sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation,traffic, safety equipment or medical equipment for life support.4.Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installationconditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.5.This product is not designed to be radiation resistant.6.No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.7.Contact Hitachi’s sales office for any questions regarding this document or Hitachi semiconductor products.Sales OfficesHitachi, Ltd.Semiconductor & Integrated Circuits.Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan Tel: Tokyo (03) 3270-2111 Fax: (03) 3270-5109Copyright Hitachi, Ltd., 2000. All rights reserved. Printed in Japan.Hitachi Asia Ltd. Hitachi Tower16 Collyer Quay #20-00, Singapore 049318Tel : <65>-538-6533/538-8577 Fax : <65>-538-6933/538-3877URL : .sg URLNorthAmerica : /Europe : /hel/ecg Asia : Japan : http://www.hitachi.co.jp/Sicd/indx.htmHitachi Asia Ltd.(Taipei Branch Office)4/F, No. 167, Tun Hwa North Road, Hung-Kuo Building, Taipei (105), Taiwan Tel : <886>-(2)-2718-3666 Fax : <886>-(2)-2718-8180 Telex : 23222 HAS-TPURL : Hitachi Asia (Hong Kong) Ltd.Group III (Electronic Components) 7/F., North Tower, World Finance Centre,Harbour City, Canton Road Tsim Sha Tsui, Kowloon, Hong KongTel : <852>-(2)-735-9218 Fax : <852>-(2)-730-0281URL : Hitachi Europe Ltd.Electronic Components Group.Whitebrook ParkLower Cookham Road MaidenheadBerkshire SL6 8YA, United Kingdom Tel: <44> (1628) 585000Fax: <44> (1628) 585160Hitachi Europe GmbHElectronic Components Group Dornacher Stra ße 3D-85622 Feldkirchen, Munich GermanyTel: <49> (89) 9 9180-0Fax: <49> (89) 9 29 30 00Hitachi Semiconductor (America) Inc.179 East Tasman Drive,San Jose,CA 95134 Tel: <1> (408) 433-1990Fax: <1>(408) 433-0223For further information write to:Colophon 2.0。

74LCX573T资料

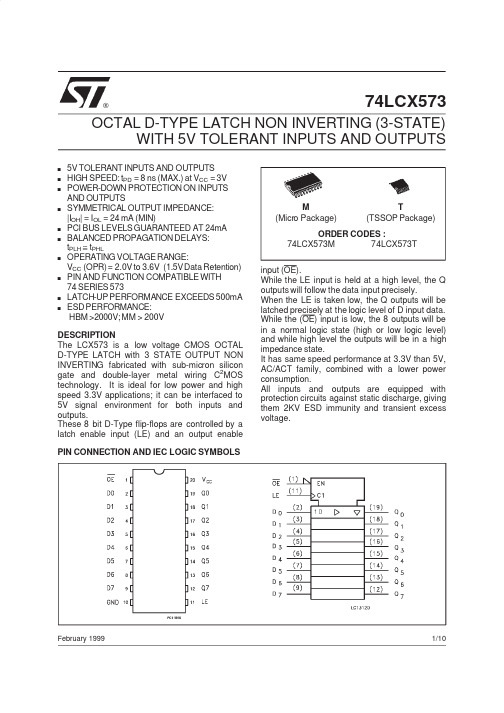

74LCX573OCTAL D-TYPE LATCH NON INVERTING (3-STATE)WITH 5V TOLERANT INPUTS AND OUTPUTS®February 1999s 5V TOLERANT INPUTS AND OUTPUTS s HIGH SPEED:t PD =8ns (MAX.)at V CC =3V sPOWER-DOWN PROTECTION ON INPUTS AND OUTPUTSsSYMMETRICAL OUTPUT IMPEDANCE:|I OH |=I OL =24mA (MIN)s PCI BUS LEVELSGUARANTEED AT 24mA sBALANCED PROPAGATION DELAYS:t PLH ≅t PHLsOPERATING VOLTAGERANGE:V CC (OPR)=2.0V to 3.6V (1.5VData Retention)sPIN AND FUNCTION COMPATIBLE WITH 74SERIES 573s LATCH-UP PERFORMANCE EXCEEDS 500mA sESD PERFORMANCE:HBM >2000V;MM >200VDESCRIPTIONThe LCX573is a low voltage CMOS OCTAL D-TYPE LATCH with 3STATE OUTPUT NON INVERTING fabricated with sub-micron silicon gate and double-layer metal wiring C 2MOS technology.It is ideal for low power and high speed 3.3V applications;it can be interfaced to 5V signal environment for both inputs and outputs.These 8bit D-Type flip-flops are controlled by a latch enable input (LE)and an output enable input (OE).While the LE input is held at a high level,the Q outputs will follow the data input precisely.When the LE is taken low,the Q outputs will be latched precisely at the logic level of D input data.While the (OE)input is low,the 8outputs will be in a normal logic state (high or low logic level)and while high level the outputs will be in a high impedance state.It has same speed performance at 3.3V than 5V,AC/ACT family,combined with a lower power consumption.All inputs and outputs are equipped with protection circuits against static discharge,giving them 2KV ESD immunity and transient excess voltage.PIN CONNECTION AND IEC LOGIC SYMBOLSORDER CODES :74LCX573M 74LCX573TM(Micro Package)T(TSSOP Package)1/10PIN DESCRIPTIONPIN NoSYMBOLNAME AND FUNCTION 1OE 3State Output Enable Input (Active LOW)2,3,4,5,6,7,8,9D0to D7Data Inputs12,13,14,15,16,17,18,19Q0to Q73State Latch Outputs11LE Latch Enable Input 10GND Ground (0V)20V CCPositive Supply VoltageTRUTH TABLEINPUTSOUTPUTSOE LE D Q H X X ZL L X NO CHANGE *L H L L LHHHX:Don’t careZ:High impe dance*Q output arelatched at the timewhen the LE input is taken LOWLOGIC DIAGRAMINPUT AND OUTPUT EQUIVALENT CIRCUIT74LCX5732/1074LCX573ABSOLUTE MAXIMUM RATINGSSymbol Parameter Value Unit V CC Supply Voltage-0.5to+7.0V V I DC Input Voltage-0.5to+7.0V V O DC Output Voltage(OFF state)-0.5to+7.0V V O DC Output Voltage(High or Low State)(note1)-0.5to V CC+0.5VI IK DC Input Diode Current-50mAI OK DC Output Diode Current(note2)±50mAI O DC Output Source/Sink Current±50mAI CC DC Supply Current per Supply Pin±100mAI GND DC Ground Current per Supply Pin±100mAT stg Storage Temperature-65to+150o C T L Lead Temperature(10sec)300o C Absolute Maximum Ratingsarethose values beyond which dam age to the device may occur.Functional operation un der these condition is not implied.1)I O absolute maximum rating must be observed2)V O<GND,V O>V CCRECOMMENDED OPERATING CONDITIONSSymbol Parameter Value Unit V CC Supply Voltage(note1) 2.0to3.6V V I Input Voltage0to5.5V V O Output Voltage(OFF state)0to5.5V V O Output Voltage(High or Low State)0to V CC VI OH,I OL High or Low Level Output Current(V CC= 3.0to3.6V)±24mAI OH,I OL High or Low Level Output Current(V CC= 2.7to3.0V)±12mAT op Operating Temperature:-40to+85o Cdt/dv Input Transition Rise or Fall Rate(V CC=3.0V)(note2)0to10ns/V1)Truth Table guaranteed:1.5V to3.6V2)V IN from0.8V to2.0V3/10DC SPECIFICATIONSSymbol Parameter Test Conditions Value UnitV CC (V)-40to85o C Min.Max.V IH High Level Input Voltage2.7to3.62.0VV IL Low Level Input Voltage0.8VV OH High Level Output Voltage 2.7to3.6V I=V I H orV IL I O=-100µA V CC-0.2V2.7I O=-12mA 2.23.0I O=-18mA 2.4 I O=-24mA 2.2V OL Low Level Output Voltage 2.7to3.6V I=V I H orV IL I O=100µA0.2V2.7I O=12mA0.43.0I O=16mA0.43.0I O=24mA0.55I I Input Leakage Current 2.7to3.6V I=0to5.5V±5µAI OZ3State Output Leakage Current 2.7to3.6V I=V IH or V ILV O=0to5.5V±5µAI off Power Off Leakage Current0V I or V O=5.5V100µAI CC Quiescent Supply Current 2.7to3.6V I=V CC or GND10µAV I or V O=3.6to5.5V±10∆I CC ICC incr.per input 2.7to3.6V IH=V CC-0.6V500µA DYNAMIC SWITCHING CHARACTERISTICSSymbol Parameter Test Conditions Value UnitV CC (V)T A=25o C Min.Typ.Max.V OLP Dynamic Low Voltage Quiet Output (note1)3.3C L=50pFV IL=0VV IH=3.3V0.8VV OLV-0.81)Number ofoutputs de fined as”n”.Measured with”n-1”outputs switchingfrom HIGH to LOW or LOW t o HIGH.The remaining output is measured in the LOW state.74LCX5734/10CAPACITIVE CHARACTERISTICSSymbolParameterTest ConditionsValue UnitV CC (V)T A =25o C Min.Typ.Max.C IN Input Capacitance 3.3V IN =0to V CC 6pF C i/o I/O Capacitance3.3V IN =0to V CC 12pF C PDPower Dissipation Capacitance (note 1)3.3f IN =10MHz V IN =0or V CC25pF 1)C PD isdefined as the value of the IC’sinternal equiva lent capacitance which is calculated fromthe operating current consumption without load.Average operting current can be obtaine d by the following equation.I CC (opr)=C PD •V CC •f IN +I CC /8(per Latch )AC ELECTRICAL CHARACTERISTICS (C L =50pF,R L =500Ω,Input t r =t f =2.5ns)SymbolParameterTest ConditionValue UnitV CC (V)Waveform-40to 85o C Min.Max.t PLH t PHL Propagation Delay Time Dn to Qn 2.73 1.59.0ns 3.0to 3.6 1.58.0t PLH t PHL Propagation Delay Time LE to Qn 2.71 1.59.5ns 3.0to 3.6 1.58.5t PZL t PZH Output Enable Time to HIGH and LOW level2.72 1.59.5ns3.0to 3.6 1.58.5t PLZ t PHZ Output Disable Time from HIGH and LOW level2.72 1.58.5ns3.0to 3.6 1.57.5t s Setup Time,HIGh or LOW level Dn to LE2.71 2.5ns3.0to 3.6 2.5t h Hold Time,HIGh or LOW level Dn to LE 2.71 1.5ns 3.0to 3.6 1.5t w LE Pulse Width,HIGH2.713.3ns 3.0to 3.6 3.3t OSLH t OSHLOutput to Output Skew Time (note 1,2)3.0to 3.61.0ns1)Skew is defined as the absolute value of the difference between theactual propagation delay for any twooutputs of the sam e device switching in the same direction,either HIGHor LOW (t OSLH =|t PLH m -t PLHn |,t OSH L =|t PHLm -t pHLn |)2)Parameter gu aranteed bydesign74LCX5735/1074LCX573TEST CIRCUITTEST SWITCH t PLH,t PHL Open t PZL,t PLZ6Vt PZH,t PHZ GND C L=50pF or equivalent(includes jigand probe capacitance)R L=R1=500ΩorequivalentR T=Z OU T of pulse generator(typ ically50Ω)WAVEFORM1:LE TO Qn PROPAGATION DELAYS,LE MINIMUM PULSE WIDTH,Dn TO LE SETUP AND HOLD TIMES(f=1MHz;50%duty cycle)6/1074LCX573 WAVEFORM2:OUTPUT ENABLE AND DISABLE TIMES(f=1MHz;50%duty cycle)WAVEFORM3:PROPAGATION DELAY TIME(f=1MHz;50%duty cycle)7/10DIM.mm inch MIN.TYP.MAX.MIN.TYP.MAX.A 2.650.104a10.100.200.0040.007a2 2.450.096b 0.350.490.0130.019b10.230.320.0090.012C 0.500.020c145(typ.)D 12.6013.000.4960.512E 10.0010.650.3930.419e 1.270.050e311.430.450F 7.407.600.2910.299L 0.50 1.270.190.050M 0.750.029S8(max.)P013LSO-20MECHANICAL DATA74LCX5738/10DIM.mminch MIN.TYP.MAX.MIN.TYP.MAX.A 1.10.433A10.050.100.150.0020.0040.006A20.850.90.950.3350.3540.374b 0.190.300.00750.0118c 0.090.20.00350.0079D 6.4 6.5 6.60.2520.2560.260E 6.25 6.4 6.50.2460.2520.256E1 4.34.4 4.480.1690.1730.176e 0.65BSC0.0256BSCK 0o 4o 8o 0o 4o 8o L0.500.600.700.0200.0240.028cEbA2AE1D1PIN 1IDENTIFICATIONA1LK eTSSOP20MECHANICAL DATA74LCX5739/1074LCX573Information furnished is believed to be accurate and reliable.However,STMicroelectronics assumes no responsibility for the consequence s of use of such information nor for any infringement of patents or other rights of third parties which may result from its use.No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics.Specification mentioned in this publication are subject to change without notice.This publication supersedes and replaces all information previously supplied.STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.The ST logo is a trademark of STMicroelectronics©1999STMicroelectronics–Printed in Italy–All Rights ReservedSTMicroelectronics GROUP OF COMPANIESAustralia-Brazil-Canada-China-France-Germany-Italy-Japan-Korea-Malaysia-Malta-Mexico-Morocco-The Netherlands-Singapore-Spain-Sweden-Switzerland-Taiwan-Thailand-United Kingdom-U.S.A..10/10。

74ls573工作原理

74ls573工作原理Title: Understanding the Working Principle of 74LS573The 74LS573 is a 3-state octal D-type latch with three-state outputs. It is designed to operate with low power consumption and high speed, making it a popular choice in various digital circuits.74LS573是一个具有三态输出的3态8位D型锁存器。

它设计用于低功耗和高速操作,因此在各种数字电路中备受欢迎。

The latch function of the 74LS573 allows it to store and retain data even when the input signals change. This is achieved through the use of internal latches that capture the data on the rising edge of the latch enable (LE) input.74LS573的锁存功能使其能够在输入信号改变时存储和保留数据。

这是通过内部锁存器实现的,这些锁存器在锁存使能(LE)输入的上升沿捕获数据。

When the LE input is high, the data present on the D inputs is latched and appears on the Q outputs. Conversely, when LE is low, the Q outputs are in a high-impedance state, effectively disconnecting them from the internal circuitry.当LE输入为高电平时,D输入上的数据被锁存并出现在Q输出上。

74hc573完整中文资料

74hc573中文资料参数-74hc573引脚图-功能原理-74hC573的作用-应用电路-74hC563-54hC57高性能硅门CMOS器件SL74HC573跟LS/AL573的管脚一样。

器件的输入是和标准CMOS输出兼容的;加上拉电阻,他们能和LS/ALSTTL输出兼容。

当锁存使能端为高时,这些器件的锁存对于数据是透明的(也就是说输出同步)。

当锁存使能变低时,符合建立时间和保持时间的数据会被锁存。

×输出能直接接到CMOS,NMOS和TTL接口上×操作电压范围:2.0V~6.0V×低输入电流:1.0uA×CMOS器件的高噪声抵抗特性·三态总线驱动输出·置数全并行存取·缓冲控制输入·使能输入有改善抗扰度的滞后作用原理说明:M54HC563/74HC563/M54HC573/74HC573的八个锁存器都是透明的D 型锁存器,当使能(G)为高时,Q 输出将随数据(D)输入而变。

当使能为低时,输出将锁存在已建立的数据电平上。

输出控制不影响锁存器的内部工作,即老数据可以保持,甚至当输出被关闭时,新的数据也可以置入。

这种电路可以驱动大电容或低阻抗负载,可以直接与系统总线接口并驱动总线,而不需要外接口。

特别适用于缓冲寄存器,I/O 通道,双向总线驱动器和工作寄存器。

HC563引脚功能表:HC573引脚功能表:图1 HC573引脚图图2 HC573 国际电工委员会逻辑符号图3 HC563引脚图图4 HC563 国际电工委员会逻辑符号图5 HC563 逻辑图图6 HC573 逻辑图图7 输入输出等效电路真值表:ABSOLUTE MAXIMUM RATINGS绝对最大额定值:Top Operating Temperature: M54HC Series M74HC Series 操作温度:M54HC系列M74HC系列-55 to +125 -40 to +85℃tr,tf Input Rise and Fall Time输入上升和下降时间VCC =2V0 to 1000ns VCC=4.5V0 to 500VCC =6V0 to 400VOHHigh Level Output Voltage输出高电平电压2.0 VI = VIH or VILIO=-20 μA1.92.0-1.9 -1.9 -V4.54.44.54.44.4---6.05.96.05.95.9-4.5IO=-6.0mA4.184.314.134.10-6.0IO=-7.8 mA5.685.85.635.60-VOLLow Level Output Voltage输出低电平电压2.0 VI = VIH or VILIO=20μA-0.0 0.1 -0.1-0.1V4.5-0.00.1 0.10.16.0-0.00.10.10.14.5IO=6.0mA-0.170.260.330.406.0IO=7.8mA-0.180.260.330.40IIInput Leakage Current输入漏电流6.0VI =VCC or GND--±0.1-±1±1μA IOZState Output Off State Current关断状态3态输出电流6.0VI =VIH or VIL VO =VCC or GND--±0.5-±5.0-±10μAICCQuiescent Supply Current静态电源电流6.0VI =VCC or GND--4-40-80μA应用电路图:点击图片查看大图图8。

74hc573中文资料参数

74hc573中文资料参数

特点:

·三态总线驱动输出

·置数全并行存取

·缓冲控制输入

·使能输入有改善抗扰度的滞后作用

原理说明:

M54HC563/74HC563/M54HC573/74HC573的八个锁存器都是透明的D 型锁存器,当使能(G)为高时,Q 输出

将随数据(D)输入而变。

当使能为低时,输出将锁存在已建立的数据电平上。

输出控制不影响锁存器的内部工作,即老数据可以保持,甚至当输出被关闭时,

新的数据也可以置入。

这种电路可以驱动大电容或低阻抗负载,可以直接与系统总线接口并驱动总线,而不需要外接口。

特别适用于缓冲寄存器,I/O 通道,双向总线驱动器和工作寄存器。

HC563

HC573

图1 HC573引脚图图2 HC573 国际电工委员会逻辑符号

图3 HC563引脚图图4 HC563 国际电工委员会逻辑符号

图5 HC563 逻辑图

图6 HC573 逻辑图

图7 输入输出等效电路

真值表:

应用电路图:点击图片查看大图

图8

图9。

74ls573中文资料

74ls573中文资料三态总线驱动输出·置数全并行存取·缓冲控制输入·使能输入有改善抗扰度的滞后作用原理:74LS573 的八个锁存器都是透明的D 型锁存器,当使能(G)为高时,Q 输出将随数据(D)输入而变。

当使能为低时,输出将锁存在已建立的数据电平上。

输出控制不影响锁存器的内部工作,即老数据可以保持,甚至当输出被关闭时,新的数据也可以置入。

这种电路可以驱动大电容或低阻抗负载,可以直接与系统总线接口并驱动总线,而不需要外接口。

特别适用于缓冲寄存器,I/O 通道,双向总线驱动器和工作寄存器。

H=高电平 L=低电平×=不定 Z=高阻态QO=建立稳态输入条件前Q的电平引脚图及功能图Operating Conditions 操作条件Symbol 符号Parameter 参数DM74LS最小典型最大VCC Supply Voltage 电源电压 4.75 5 5.25VIH High Level Input Voltage输入高电平电压 2 - -VIL LOW Level Input Voltage 输入低电平电压- - 0.8IOH HIGH Level Input Current输入高电平电流- - −2.6IOL LOW Level Output Current低电平输出电流- - 24TA Free Air Operating Temperature工作温度0 - 70Note 1: The “Absolute Maximum Ratings” are those values beyond which the safety of th cannot be guaranteed. The device should not be operated at these limits. The parametri defined in the “Electrical Characteristics” table are not guaranteed at the absolute ratings. The “Recommended Operating Conditions” table will define the conditions fo device operation.Electrical Characteristics 直流电气特性Over recommended operating free air temperature range (unless otherwise noted)Symbol 符号Parameter 参数Conditions 条件最小典型最大单VI Input Clamp Voltage输入钳位电压VCC=最小, II=−18 mA - - −1.5VOH High Level OutputVoltage输出高电平电压VCC = 最小, IOH=最大,VIL = 最大2.73.4 -VOL Low Level OutputVoltage输出低电平电压VCC = 最小, IOL=最大- 0.35 0.5VIH = 最小- - -。

(完整word版)74HC573功能说明(原创编辑)

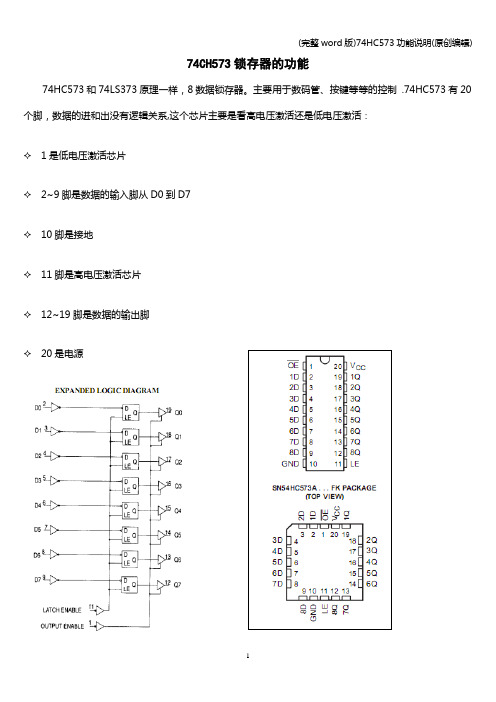

74CH573锁存器的功能74HC573和74LS373原理一样,8数据锁存器。

主要用于数码管、按键等等的控制 .74HC573有20个脚,数据的进和出没有逻辑关系,这个芯片主要是看高电压激活还是低电压激活:✧1是低电压激活芯片✧2~9脚是数据的输入脚从D0到D7✧10脚是接地✧11脚是高电压激活芯片✧12~19脚是数据的输出脚✧20是电源1.真值表74HC573真值表,意思如下:➢第一行/第二行:当OE=0、LE=1时,输出端数据等于输入端数据;➢第三行:当OE=0、LE=0时,输出端保持不变;➢第四行:当OE=1是无论Dn、LE为何,输出端为高阻态;2. 高阻态就是输出既不是高电平,也不是低电平,而是高阻抗的状态;在这种状态下,可以多个芯片并联输出;但是,这些芯片中只能有一个处于非高阻态状态,否则会将芯片烧毁。

高阻态的概念在RS232和RS422通讯中还可以用到。

3。

数据锁存当输入的数据消失时,在芯片的输出端,数据仍然保持;这个概念在并行数据扩展中经常使用到。

4. 数据缓冲加强驱动能力:74LS244/74LS245/74LS373/74LS573都具备数据缓冲的能力。

◆OE:output_enable,输出使能;◆LE:latch_enable,数据锁存使能,atch是锁存的意思;◆Dn:第n路输入数据;◆On:第n路输出数据;74HC573波形图,在实际应用的时候是这样做的:a.OE=0;b.先将数据从单片机的口线上输出到Dn;c.再将LE从0->1-〉0 ;d.这时,你所需要输出的数据就锁存在On上了,输入的数据在变化也影响不到输出的数据了;实际上,单片机现在在忙着干别的事情,串行通信、扫描键盘……单片机的资源有限啊。

在单片机按照RAM方式进行并行数据的扩展时,使用movx @dptr,A这条指令时,这些时序是由单片机来实现的.后面的表格中还有需要时间的参数,你不需要去管它,因为这些参数都是几十ns级别的,对于单片机在12M下的每个指令周期最小是1us的情况下,完全可以实现;如果是你自己来实现这个逻辑,类似的指令如下:MOV P0,A ; //将数据输出到并行数据端口CLR LESETB LECLR LE ;//上面三条指令完成LE的波形从0—〉1->0的变化74LS573跟74LS373逻辑上完全一样,只不过是管脚定义不一样,数据输入和输出端.。

74LS573抢答器的设计与调试

74LS573抢答器的设计与调试一、任务与要求1. 抢答器同时供8名选手或8个代表队比赛,分别用8个按钮S0 ~ S7表示。

2. 设置一个系统清除和抢答控制开关S,该开关由主持人控制。

3. 抢答器具有锁存与显示功能。

即选手按动按钮,锁存相应的编号,并在LED数码管上显示选手抢答实行优先锁存,优先抢答选手的编号一直保持到主持人将系统清除为止二、独立设计过程1、选用的电子元件a)数码管b)7448七端显示译码器c)74LS148 8-3线译码器d)74LS573 8输入8输出的D触发器2、元件功能介绍a)数码管七段LED数码管有共阴极型和共阳极型两种,试验中采用的是共阴极型数码管,管脚接受相应译码器的a,b,c,d,e,f,g信号,来显示相应树值。

b)74LS48七端显示译码器CT74LS48及数码管管脚图由于我们选手抢答后是数字显示哪位选手抢答,所以用7448来实现数字显示。

7448七端显示译码器输出高电平有效,用以驱动阴极显示器。

该集成显示译码器设有多个辅助控制端如LT、RBI、BI/RBO试灯输入LT当LT=0时,,且RBO=1,此时无论其他的输入输出是什么状态,所有个段的输出a—g均为1,显示的字形为8。

该端常用于检查7448本身及显示器的好坏。

动态灭零输入RBI当LT=1,RBI=0且输入代码DCBA=0000时,各段输入a—g均为低电平,与BCD码相应的字形熄0灭,故称“灭零”。

利用LT=1与RBI=0可以实现某一位的“消隐”。

但是在我们做的实验当中,为了保证实验的顺利进行,我们直接将LT 和RBI接+5v ,于是在显示为零的时候,看不到灭零,但是这对枪答过程没有实质性的影响。

真值表如下c)74LS148 8-3线译码器由于是8路抢答器,其译码器必须是8-3线译码器,记过资料查证以及分析,我选择了74LS148优先编码器,此编码器可以实现将8位输入状态编译为3输出状态,以便与以后的锁存器的锁存.该编码起7的功能图如下图所示:74LS148的功能真值表以上的IN0~~IN7即为8位选手,ST端是使能端,控制74LS148的工作,当ST输入为0的时候,74LS148便开始工作,否则处于非工作状态.,且输入为低电平有效.由上图可知输出端Yex 当74LS148不工作的时候或者8个输入端都为高电平时候,输出的为高电平,刚好可以用来翻转后控制该片芯片的工作,于是我把它同RS触发器连接起来,当有一个选手按下开关且输入低电平的时候,Yex输出0经过翻转后可以把ST端锁住,达到不让后来按到抢答器的选手干扰抢答的目的.d)74LS573 8输入8输出的D触发器74LS573为8输入端,8输出端的D触发器,用它可以实现8位选手的抢答与主持人清零功能。