LMC6034IM中文资料

LMC长袋低压脉冲袋式除尘器产品说明书

LMC系列长袋低压脉冲袋式除尘器使用说明书LMC长袋低压脉冲袋式除尘器技术说明一、概述LMC系列长袋低压脉冲袋式除尘器是在喷吹脉冲(Jet Pulse)除尘技术的基础上,为满足大风量净化需要而专门研制的具有九十年代先进水平的脉冲袋式除尘器,不但具有喷吹脉冲除尘器的清灰能力强、除尘效率高、排放浓度低等特点,还具有稳定可靠、耗气量低、占地面积小的特点,特别适合处理大风量的烟气。

LMC系列低压脉冲袋式除尘器已在全世界范围内得到应用,在中国也已经大量推广,广泛适用于冶金、机械、化工、建材等行业的大风量烟气净化。

二、工作原理LMC长袋低压脉冲袋式除尘器主要由上箱体、中箱体、灰斗、卸灰系统和控制系统等几部分组成,并采用下进气分室结构。

含尘烟气由进风口经中箱体下部进入灰斗,部分较大的尘粒由于惯性碰撞、自然沉降等作用直接落入灰斗,其它尘粒随气流上升进入各个袋室。

经滤袋过滤后,粉尘被阻留在滤袋外表面,净化后的气体从滤袋内部经过袋口、上箱体、出风口由引风机排入大气。

灰斗中的粉尘定时或连续由输送系统卸出。

随着过滤过程的不断进行,滤袋外表面所附积的粉尘不断增加,从而导致除尘器本身的阻力也逐步升高。

当阻力达到一定值时,清灰控制器发出信号,首先令一袋室的提升阀关闭以切断该室的过滤气流,然后打开电磁脉冲阀压缩空气顺序经气包、脉冲阀、喷吹管上的喷嘴以极短的时间(0.065–0.085秒)向滤袋内喷射。

压缩空气在滤袋内高速膨胀,使滤袋产生高频振动变形,再加上逆气流的作用,使滤袋外侧所附尘饼变形脱落。

在充分考虑了粉尘的沉降时间(保证所脱落的粉尘能够有效落入灰斗)后,提升阀打开,此袋室滤袋恢复到过滤状态,而下一袋室则进入清灰状态,如此直到最后一袋室清灰完毕为一清灰周期。

LMC长袋低压脉冲袋式除尘器是由多个独立的袋室组成的,各室按须序分别进行清灰,互不干扰,实现长期连续运行。

上述清灰过程均由清灰控制器进行自动控制,分为定时和定阻两种,可根据用户的要求决定采用哪一种。

LMC-PCIE-V6K3-SPI 系列激光控制卡 电气使用说明书

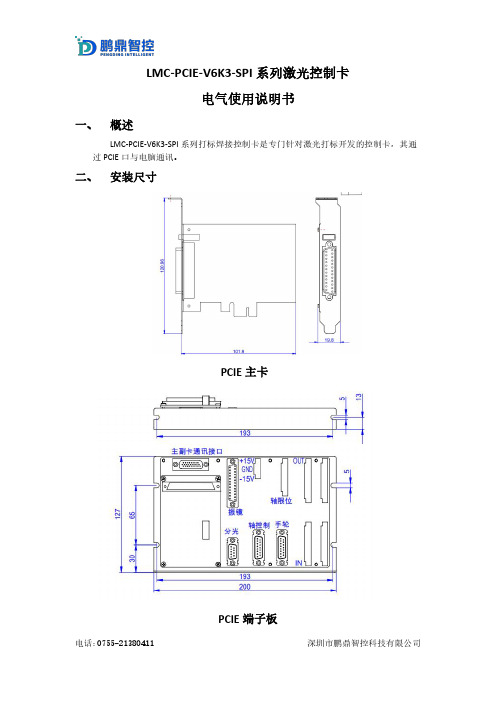

LMC-PCIE-V6K3-SPI系列激光控制卡电气使用说明书一、概述LMC-PCIE-V6K3-SPI系列打标焊接控制卡是专门针对激光打标开发的控制卡,其通过PCIE口与电脑通讯。

二、安装尺寸PCIE主卡PCIE端子板三、外观介绍PCIE主卡PCIE端子板四、LED指示灯说明注意:在对控制卡上电后第一时间查看亮灯情况,如果异常马上断电检查接线情况。

主卡灯状态:位号说明状态三色灯绿色指示灯空闲灯黄色指示灯运行灯红色指示灯报警灯端子板灯状态位号说明LED1负向电源指示灯LED6正向电源指示灯LED8外接24V电源指示灯(IO)LED3板卡空闲指示灯LED4板卡工作中指示灯LED5板卡错误指示灯五、接口说明5.1电源接口(J1,3PIN接线端子)5.1.1振镜不通过板卡J1端口供电接线方式管脚号板卡端丝印名称方向供电电源电压电源功率1+15V输入8V~28V>5W2GND输入GND3-15V不接注:如是以上方式接线,为避免振镜或板卡损坏需将振镜电源参考地与板卡电源参考地短接。

5.1.2振镜通过板卡J1端口供电接线方式管脚号板卡端丝印名称方向供电电源电压电源功率供电线径1+15V输入振镜正向电源电压(8~28V范围内)振镜功率+5W不小于0.75平方mm2GND输入GND振镜功率+5W不小于0.75平方mm 3-15V输入振镜负向电源电压(-8~-28V范围内)振镜功率+5W不小于0.75平方mm例如:鹏鼎Ⅰ、Ⅱ代振镜供电,J1端口如下接线:管脚号板卡端丝印名称方向供电电源电压电源功率供电线径1+15V输入+15V振镜功率+5W不小于0.75平方mm 2GND输入GND振镜功率+5W不小于0.75平方mm 3-15V输入-15V振镜功率+5W不小于0.75平方mm管脚号板卡端丝印名称方向供电电源电压电源功率供电线径1+15V输入+24V振镜功率+5W不小于0.75平方mm 2GND输入GND振镜功率+5W不小于0.75平方mm 3-15V输入不接5.2振镜控制接口定义(J3,DB25母头)(XY2-100协议接口定义)管脚名称说明信号方向管脚名称说明信号方向1Clk-时钟信号-输出14Clk+时钟信号+输出2Sync-同步信号-输出15Sync+同步信号+输出3X_data-X振镜信号-输出16X_data+X振镜信号+输出4Y_data-Y振镜信号-输出17Y_data+Y振镜信号+输出5X_fb-(A-)X振镜反馈-(复用,飞行A-)输入18X_fb+(A+)X振镜反馈+(复用,飞行A+)输入6Y_fb-(B-)Y振镜反馈-(复用,飞行B-)输入19Y_fb+(B+)Y振镜反馈+(复用,飞行B+)输入9/10 /22+15V振镜供电电源+15V输出,与J1的1脚直连11/23/24GND GND,电源参考点输出,与J1的2脚直连12/1 3/25-15V振镜供电电源-15V输出,与J1的3脚直连7/8/20/21NC留用5.2.1振镜控制接口(J3,DB25母头)(SL2-100协议接口定义)振镜接线(SL2-100)SCANLAB振镜接口控制卡振镜接口振镜管脚号振镜信号定义控制卡管脚号接口定义1DATA IN+16x-data+6DATA IN-3X-data-5DATA OUT+18X-FB+9DATA OUT-5X-FB-7,8GND11,23,24GND注:①振镜信号(+,-)为一对差分信号,信号线要用屏蔽双绞线,振镜信号线长度<20m.②如果振镜电源从J3供电,供电线缆线径不小于0.75平方mm。

三菱电机 第4代大型DIPIPM 应用手册

三菱电机株式会社和三菱电机机电(上海)有限公司拥有本手册内所有资料的版权。 任何个人和企业在未得到书面许可的情况下,不得传播、复制、转载、出版和出售涉及本手册的任何内 容。如有违反,我们将保留追究其法律责任的权利。敬请留意。

2009 年 3 月

第 4 代大型 DIPIPM 应用手册

目录

第 1 章 产品概要 ......................................................................................................................................... 1

2.2 保护功能及其工作时序.......................................................................................................................... 9 2.2.1 短路保护......................................................................................................................................... 9 2.2.2 控制电源欠压保护(UV) ..................................................................................................... 12 2.2.............................................................................................. 13

洛克威爾自動化 PowerFlex 750 系列交流變頻器 技術資料说明书

技術資料PowerFlex 750 系列交流變頻器原始說明主題頁次其他資源2產品概述2認證和規格6設計考量11保險絲及斷路器額定值36電纜考量事項59馬達考量事項61尺寸及重量64變頻器選項1152洛克威爾自動化出版品 750-TD001H-ZC-P - 2013 年 6 月PowerFlex 750 系列交流變頻器其他資源這些文件包含與洛克威爾自動化產品相關的其他資訊。

您可以至以下網址檢視或下載出版品:/literature/。

若要訂購書面的技術文件,請向本地 Allen-Bradley 自動化經銷商或洛克威爾銷售代表洽詢。

產品概述PowerFlex 750 系列是功能強大的交流變頻器系列,不僅易於使用,而且為眾多不同的工業應用系統提供絕佳彈性及效能。

PowerFlex 753 提供的一般用途控制器適用於功率最高達 350HP 及250kW 的應用系統。

PowerFlex 755 提供高達 2000HP 及 1500kW 的最大彈性及效能。

以下是 PowerFlex 750 系列具備的重要功能,善用這些功能所帶來的優勢可大幅提高產能。

•DeviceLogix ™ — 內嵌式控制器技術,支援離散輸出及變頻器控制功能之操作,變頻器更內建離散輸入和變頻器狀態資訊。

•預測診斷系統 — 讓變頻器隨時掌握影響冷卻風扇使用壽命及繼電器輸出的資訊。

此外,亦可編輯變頻器的程式,以監控機器或馬達軸承的運行時間。

•選項卡 — 每個變頻器都具備插槽式架構。

提供兩種產品共通的硬體控制選項,有助您降低庫存及零件的需求。

•安全扭力關斷及安全速度監控 — 可根據您的應用系統需求提供安全層級的選擇。

•通訊 — PowerFlex 755 附帶內建乙太網路連接埠。

可利用通訊模組輕鬆新增乙太網路至 PowerFlex 753。

•I/O — 適用額外類比和離散 I/O 之選項卡。

PowerFlex 753 附帶內建 I/O ,可透過選項卡輕鬆擴充。

OMEGA PCL431 手持电流校准器说明书

PCL431Current CalibratorOperator’s ManualM1889/0994GENERAL DESCRIPTIONThe OMEGA®PCL431 Hand-Held Current Calibrator is designed to be a complete 4-20mA loop calibrator delivering high accuracy in a small, easy to use package. Its microprocessor based circuitry gives the usera large number of input/output options and operating modes without unnecessary complexity.Current can be sourced into loads up to 1000 ohms or simulated with external power supplies of up to60VDC. When operated in the read mode the user can input a current from a signal source directly, or in the read/power mode the PCL431 will supply 24 volt loop power to a two wire device and simultaneously monitor the resultant loop current. Both read and source measurements can be displayed directly inmilliamps or as a percentage of a 4-20mA loop.Commonly used outputs (up to 3) can be stored in the PCL431’s non-volatile memory for quick recall. In addition, an auto-step mode allows the calibrator to step through the selected setpoints at a user defined dwell time of 5 to 60 seconds.INSTALLATIONUNPACKINGRemove the Packing List and verify that all equipment has been received. If you have any questions about the shipment, please call the OMEGA Customer Service Department at 1-800-622-2378 or (203) 359-1660.When you receive the shipment, inspect the container and equipment for any signs of damage. Note any evidence of rough handling in transit. Immediately report any damage to the shipping agent.NOTE:The carrier will not honor any claims unless all shipping material is saved for theirexamination. After examining and removing contents, save packing material and carton in theevent reshipment is necessary.Check to see if your calibrator kit is complete - it should include:1. Carrying case (Qty=1)2. T est leads (Qty=1 set)3. 9V battery (Installed)4. Operator’s Manual (Qty=1)SET-UPBefore beginning, become familiar with the keypad layout and the configuration of the input/output jacks.Remember, these jacks are used in multiple configurations so pay careful attention to how the test leads are connected for the specific application.CJS0994RAF2BAOPERATING PROCEDURE1. Turn on power and select the desired range by depressing the ”RANGE SELECT” key.NOTE: When operating in the “%” range, 4mA=0% and 20mA=100%.2. Connections are made as follows:Current Source - Use jacks 1 and 2 (1 is +).Current Simulate - Use jacks 2 and 3 (2 is +).Current Read - Use jacks 3 and 4 (4 is +).Current Read/Power - Use jacks 1 and 4 (1 is +).3. The and keys adjust the output value up or down. Holding the ramp keys continuously forseveral seconds will increase the scroll rate. Going beyond the endpoints (0 and 24mA) will cause theoutput to wrap around, thus allowing a quick return to either end of the scale.4. Three calibration points can be stored in non-volatile memory by scrolling to the desired output,depressing the Store key, and then the desired setpoint key.5. The auto step will automatically step through the stored setpoints at pre-defined intervals. When theauto-step key is first depressed, the display will indicate the dwell time (in seconds) between steps.The factory set value is 15 seconds but you can set this value, from 5 to 60 seconds, by usingthe and keys when the dwell time is being displayed. Once you have scrolled to the desireddwell time, release the or key and wait approximately 3 seconds until the calibrator begins toautomatically step through the 3 setpoints. The calibrator will continue the stepping process until anykey is pressed. Your chosen dwell time will remain in a non-volatile memory location until you chooseto change it.OPERATING CONSIDERATIONS AND PRECAUTIONS1. When operating in the current source mode, the PCL431 has the capability to drive loads up to 1000ohms as shown in Figure 1.Figure 1 - Current Source Mode2. When operating in the current simulate mode, the PCL431 acts like a two-wire transmitter controlling acurrent loop with an external voltage of up to 60 VDC as shown in Figure 2.Figure 2 - Current Simulate Mode3. When reading a current loop, the PCL431 can measure over a range of 0-24mA. Connections areshown in Figure 3.Figure 3 - Current Loop Readings4. The PCL431 can simultaneously power a device with 24 volts and display the current flowing throughthe loop. This is particularly useful when calibrating a two-wire transmitter. A typical application isshown in Figure 4.Figure 4 - PCL431 Simultaneous Power/DisplayACCURACYThe PCL431 is checked against an NIST traceable reference before shipment to verify that each range falls within the 0.05%, ±1 count, of full scale accuracy specification. Long term accuracy should remain within0.1%, ±1 count, of FSR. All of these ratings are based on a 25°C ambient temperature. A change of 10°Cwill cause approximately a 1000 ppm change (based on 100 ppm/C temp.) in the output or the equivalent of a 0.1% output change. Therefore, allowances must be made for error caused by wide temperaturevariations.。

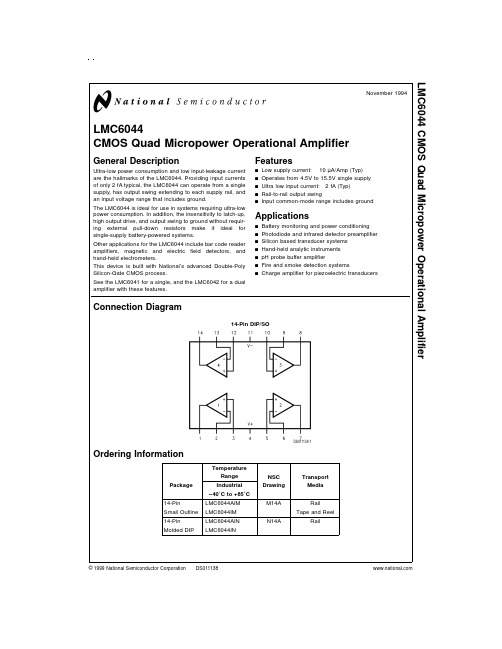

LMC6044中文资料

Features

n n n n n Low supply current: 10 µA/Amp (Typ) Operates from 4.5V to 15.5V single supply Ultra low input current: 2 fA (Typ) Rail-to-rail output swing Input common-mode range includes ground

16V (Note 12) (Note 2) 260˚C

Operating Ratings

Temperature Range LMC6044AI, LMC6044I Supply Voltage Power Dissipation Thermal Resistance (θJA), (Note 11) 14-Pin DIP 14-Pin SO −40˚C ≤ TJ ≤ +85˚C 4.5V ≤ V+ ≤ 15.5V (Note 10) 85˚C/W 115˚C/W

Applications

n n n n n n n Battery monitoring and power conditioning Photodiode and infrared detector preamplifier Silicon based transducer systems Hand-held analytic instruments pH probe buffer amplifier Fire and smoke detection systems Charge amplifier for piezoelectric transducers

Connection Diagram

14-Pin DIP/SO

镁合金定量出料机电器说明书

镁合金定量出料机电器使用说明书一、主要规格及技术参数:1、交流输入电源:交流380V(三相4线制)额定功率:30.8KW额定电流:136A2、PLC:S7-200,AC/DC/继电器CPU224:14I/10O3、SSR:过零型:电压:<240V电流:250A,80A触发电流:>5mA开启电压:>4v二、工作原理:主要控制开关说明:SA1——总电源开关 QF1——加热器电源开关 SA4——温度显示开关 SA3——PLC电源开关整个电器控制系统主要由加热控制电路和气动阀控制电路组成。

1、加热控制部分由温控器(SDC15)和固态继电器(SSR)以及热电耦(K系列)组成。

温控器是日本三武公司的SDC15(SSR型)。

它具有PID温度调节,加热器断路报警输出,SSR驱动输出(V<24V,I<360mA)。

固态继电器采用杭州西子的过零型SSR。

触发电压3—32VDC,触发电流<50mA。

SDC15通过热电耦把加热丝的实际温度采样进来与事先设定的温度值比较后由事先设定PID值确定通过事件输出端口向SSR发出通或断的信号。

同时SDC15还设定了PV(现场温度值)低限报警值,一旦加热丝的温度低于此值就向PLC发出报警信号(PLC EM223 I1.6)。

PLC程序就会停止。

2、气动控制部分由传感器,电磁阀,PLC组成。

PLC采用西门子的S7-200,阀门位置传感器和液位传感器、旋转汽缸位置传感器共同组成反馈系统。

3、控制过程:在加热丝加热一段时间后,加热丝温度处于正常值,PLC上电,(此时坩锅内熔液已准备就绪),抽液/放液旋钮从中间位置拨到抽液位置,打开气路单向阀5YV(开始抽真空),真空泵抽管内空气同时二位五通气路换向阀1YV得电(抽液通道)打开,2YV失电(放液通道)断开,利用真空泵产生的负压将坩锅内熔液抽到定量筒中,当定量筒内镁液的液面到达指定位置S1(液面传感器)动作,此时立即关5YV(抽真空结束)关闭真空泵,同时1YV失电(抽液通道)关闭,2YV得电(放液通道)打开。

变频器滤波器选型

五、变频器滤波器选型 变频器干扰范围图示

六、变频器滤波器选型安装接线图

电源滤波器厂家

如有需要请您联系《上海民恩电气有限公司》咨询!

变频器滤波器选型

安 装 位 置 示 意 图

七、变频器滤波器选型安装使用说明

滤波器安装前请先阅读此注意事项!!! 1. 测试 上海民恩电气有限公司的每一只产品在出厂前均经过严格的测试,

变频器专用输入EMC滤波器,主要是由(L)滤波电感、(C)滤波电容和(R)电阻构成。

变频器专用输入EMC滤波器,是利用“阻抗失配”的原理进行工作的;

一般情况下,我们默认为电源端是低阻抗的,所以,我们变频器输入滤波器的输入端是高阻抗的;

而负载侧,我们默认为其是高阻抗的,而我们的变频器输入滤波器的输出端,则是低阻抗的;

变频器滤波器选型

五、变频器专用滤波器外形尺寸 -

A

B

C

D

EF

G

H

N2 110 125±1.0 140 70±0.5 93 56 5.3*7 M4

N5 120 168±1.5 186 85±0.5 108 60 6.4*9 M6

N10 200 220±1.5 240 100±1.0 125 80 6.4*9 M6

4. 安装位置 滤波器的安装应尽量靠近变频器侧,通常情况下滤波器与变频 器之间的连线越短越好,不宜超过 1 米;

5. 布线 滤波器的输入线与输出线不得平行或交叉;应使输入、输出线尽量 远离;

6. 检查 每年应最少一次对滤波器的连接进行检查。

维护注意事项

1. 一切测试、拆卸工作应在切断电源 5 分钟后进行,这是为了保证滤波器内 部元件充分放电。

变频器滤波器为双向可逆器件,即能防止电网上的电磁噪声通过电源进入设备,也能防 止设备本身的电磁噪声对电网的污染。变频器滤波器是用来抑制传导干扰的有效工具。

LMC6084中文资料

LMC6084Precision CMOS Quad Operational AmplifierGeneral DescriptionThe LMC6084is a precision quad low offset voltage opera-tional amplifier,capable of single supply operation.Perfor-mance characteristics include ultra low input bias current,high voltage gain,rail-to-rail output swing,and an input com-mon mode voltage range that includes ground.These fea-tures,plus its low offset voltage,make the LMC6084ideally suited for precision circuit applications.Other applications using the LMC6084include precision full-wave rectifiers,integrators,references,and sample-and-hold circuits.This device is built with National’s advanced Double-Poly Silicon-Gate CMOS process.For designs with more critical power demands,see the LMC6064precision quad micropower operational amplifier.For a single or dual operational amplifier with similar fea-tures,see the LMC6081or LMC6082respectively.PATENT PENDINGFeatures(Typical unless otherwise stated)n Low offset voltage:150µVn Operates from 4.5V to 15V single supply n Ultra low input bias current:10fAn Output swing to within 20mV of supply rail,100k load n Input common-mode range includes V −n High voltage gain:130dB n Improved latchup immunityApplicationsn Instrumentation amplifiern Photodiode and infrared detector preamplifier n Transducer amplifiers n Medical instrumentation n D/A converternCharge amplifier for piezoelectric transducersConnection DiagramOrdering InformationPackageTemperature Range NSC DrawingTransport MediaMilitary Industrial −55˚C to +125˚C−40˚C to +85˚C 14-Pin LMC6084AMNLMC6084AlN N14ARailMolded DIP LMC6084lN 14-Pin LMC6084AlM M14ARail Small OutlineLMC6084lMTape and ReelFor MlL-STD-883C qualified products,please contact your local National Semiconductor Sales Office or Distributor for availability and specification information.14-Pin DIP/SODS011467-1Top ViewNovember 1994LMC6084Precision CMOS Quad Operational Amplifier©1999National Semiconductor Corporation Absolute Maximum Ratings(Note1)If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications. Differential Input Voltage±Supply Voltage Voltage at Input/Output Pin(V+)+0.3V,(V−)−0.3V Supply Voltage(V+−V−)16V Output Short Circuit to V+(Note11) Output Short Circuit to V−(Note2) Lead Temperature(Soldering,10Sec.)260˚C Storage Temp.Range−65˚C to+150˚C Junction Temperature150˚C ESD Tolerance(Note4)2kV Current at Input Pin±10mA Current at Output Pin±30mA Current at Power Supply Pin40mA Power Dissipation(Note3)Operating Ratings(Note1)Temperature RangeLMC6084AM−55˚C≤T J≤+125˚C LMC6084AI,LMC6084I−40˚C≤T J≤+85˚C Supply Voltage 4.5V≤V+≤15.5V Thermal Resistance(θJA)(Note12)14-Pin Molded DIP81˚C/W 14-Pin SO126˚C/W Power Dissipation(Note10)DC Electrical CharacteristicsUnless otherwise specified,all limits guaranteed for T J=25˚C.Boldface limits apply at the temperature extremes.V+=5V, V−=0V,V CM=1.5V,V O=2.5V and R L>1M unless otherwise specified.Typ LMC6084AM LMC6084AI LMC6084ISymbol Parameter Conditions(Note5)Limit Limit Limit Units(Note6)(Note6)(Note6)V OS Input Offset Voltage150350350800µV10008001300Max TCV OS Input Offset Voltage 1.0µV/˚C Average DriftI B Input Bias Current0.010pA10044Max I OS Input Offset Current0.005pA10022Max R IN Input Resistance>10TeraΩCMRR Common Mode0V≤V CM≤12.0V85757566dB Rejection Ratio V+=15V727263Min +PSRR Positive Power Supply5V≤V+≤15V85757566dB Rejection Ratio V O=2.5V727263Min −PSRR Negative Power Supply0V≤V−≤−10V94848474dB Rejection Ratio818171Min V CM Input Common-Mode V+=5V and15V−0.4−0.1−0.1−0.1V Voltage Range for CMRR≥60dB000MaxV+−1.9V+−2.3V+−2.3V+−2.3VV+−2.6V+−2.5V+−2.5Min A V Large Signal R L=2kΩSourcing1400400400300V/mVVoltage Gain(Note7)300300200MinSinking35018018090V/mV7010060MinR L=600ΩSourcing1200400400200V/mV(Note7)15015080MinSinking150********V/mV355035Min 2DC Electrical Characteristics(Continued)Unless otherwise specified,all limits guaranteed for T J=25˚C.Boldface limits apply at the temperature extremes.V+=5V,V−=0V,V CM=1.5V,V O=2.5V and R L>1M unless otherwise specified.Typ LMC6084AM LMC6084AI LMC6084ISymbol Parameter Conditions(Note5)Limit Limit Limit Units(Note6)(Note6)(Note6)V O Output Swing V+=5V 4.87 4.80 4.80 4.75VR L=2kΩto2.5V 4.70 4.73 4.67Min0.100.130.130.20V0.190.170.24MaxV+=5V 4.61 4.50 4.50 4.40VR L=600Ωto2.5V 4.24 4.31 4.21Min0.300.400.400.50V0.630.500.63MaxV+=15V14.6314.5014.5014.37VR L=2kΩto7.5V14.3014.3414.25Min0.260.350.350.44V0.480.450.56MaxV+=15V13.9013.3513.3512.92VR L=600Ωto7.5V12.8012.8612.44Min0.79 1.16 1.16 1.33V1.42 1.32 1.58MaxI O Output Current Sourcing,V O=0V22161613mAV+=5V8108MinSinking,V O=5V21161613mA111310MinI O Output Current Sourcing,V O=0V30282823mAV+=15V182218MinSinking,V O=13V34282823mA(Note11)192218MinI S Supply Current All Four Amplifiers 1.8 3.0 3.0 3.0mAV+=+5V,V O=1.5V 3.6 3.6 3.6MaxAll Four Amplifiers 2.2 3.4 3.4 3.4mAV+=+15V,V O=7.5V 4.0 4.0 4.0Max3AC Electrical CharacteristicsUnless otherwise specified,all limits guaranteed for T J=25˚C,Boldface limits apply at the temperature extremes.V+=5V, V−=0V,V CM=1.5V,V O=2.5V and R L>1M unless otherwise specified.Typ LMC6084AM LMC6084AI LMC6084I Symbol Parameter Conditions(Note5)Limit Limit Limit Units(Note6)(Note6)(Note6) SR Slew Rate(Note8) 1.50.80.80.8V/µs0.50.60.6MinGBW Gain-Bandwidth Product 1.3MHz φm Phase Margin50Deg Amp-to-Amp Isolation(Note9)140dBe n Input-Referred Voltage Noise F=1kHz22nV/√Hzi n Input-Referred Current Noise F=1kHz0.0002pA/√HzT.H.D.Total Harmonic Distortion F=10kHz,A V=−10R L=2kΩ,V O=8V PP0.01%±5V SupplyNote1:Absolute Maximum Ratings indicate limits beyond which damage to the device may occur.Operating Ratings indicate conditions for which the device is in-tended to be functional,but do not guarantee specific performance limits.For guaranteed specifications and test conditions,see the Electrical Characteristics.The guaranteed specifications apply only for the test conditions listed.Note2:Applies to both single-supply and split-supply operation.Continuous short circuit operation at elevated ambient temperature can result in exceeding the maximum allowed junction temperature of150˚C.Output currents in excess of±30mA over long term may adversely affect reliability.Note3:The maximum power dissipation is a function of T J(Max),θJA,and T A.The maximum allowable power dissipation at any ambient temperature is P D=(T J(Max)−T A)/θJA.Note4:Human body model,1.5kΩin series with100pF.Note5:Typical values represent the most likely parametric norm.Note6:All limits are guaranteed by testing or statistical analysis.Note7:V+=15V,V CM=7.5V and R L connected to7.5V.For Sourcing tests,7.5V≤V O≤11.5V.For Sinking tests,2.5V≤V O≤7.5V.Note8:V+=15V.Connected as Voltage Follower with10V step input.Number specified is the slower of the positive and negative slew rates.Note9:Input referred V+=15V and R L=100kΩconnected to7.5V.Each amp excited in turm with1kHz to produce V O=12V PP.Note10:For operating at elevated temperatures the device must be derated based on the thermal resistanceθJA with P D=(T J−T A)/θJA.All numbers apply for pack-ages soldered directly into a PC board.Note11:Do not connect output to V+,when V+is greater than13V or reliability will be adversely affected.Note12:All numbers apply for packages soldered directly into a PC board.4Typical Performance CharacteristicsDistribution of LMC6084Input Offset Voltage (T A =+25˚C)DS011467-17Distribution of LMC6084Input Offset Voltage (T A =−55˚C)DS011467-18Distribution of LMC6084Input Offset Voltage (T A =+125˚C)DS011467-19Input Bias Current vs Temperature DS011467-20Supply Current vs Supply Voltage DS011467-21Input Voltagevs Output VoltageDS011467-22Common Mode Rejection Ratio vs FrequencyDS011467-23Power Supply Rejection Ratio vs Frequency DS011467-24Input Voltage Noise vs FrequencyDS011467-255Typical Performance Characteristics(Continued)Output Characteristics Sourcing CurrentDS011467-26Output Characteristics Sinking CurrentDS011467-27Gain and Phase Response vs Temperature (−55˚C to +125˚C)DS011467-28Gain and PhaseResponse vs Capacitive Load with R L =600ΩDS011467-29Gain and PhaseResponse vs Capacitive Load with R L =500k ΩDS011467-30Open LoopFrequency ResponseDS011467-31Inverting Small Signal Pulse Response DS011467-32Inverting Large Signal Pulse Response DS011467-33Non-Inverting Small Signal Pulse ResponseDS011467-34 6Typical Performance Characteristics(Continued)Applications HintsAMPLIFIER TOPOLOGYThe LMC6084incorporates a novel op-amp design topology that enables it to maintain rail-to-rail output swing even when driving a large load.Instead of relying on a push-pull unity gain output buffer stage,the output stage is taken directly from the internal integrator,which provides both low output impedance and large gain.Special feed-forward compensa-tion design techniques are incorporated to maintain stability over a wider range of operating conditions than traditional micropower op-amps.These features make the LMC6084both easier to design with,and provide higher speed than products typically found in this ultra-low power PENSATING FOR INPUT CAPACITANCEIt is quite common to use large values of feedback resis-tance for amplifiers with ultra-low input current,like the LMC6084.Although the LMC6084is highly stable over a wide range of operating conditions,certain precautions must be met to achieve the desired pulse response when a large feedback resistor is rge feedback resistors and even small values of input capacitance,due to transducers,photo-diodes,and circuit board parasitics,reduce phase margins.When high input impedances are demanded,guarding of the LMC6084is suggested.Guarding input lines will not only re-duce leakage,but lowers stray input capacitance as well.(See Printed-Circuit-Board Layout for High Impedance Work).The effect of input capacitance can be compensated for by adding a capacitor,C f ,around the feedback resistors (as in Figure 1)such that:orR 1C IN ≤R 2C fSince it is often difficult to know the exact value of C IN ,C f can be experimentally adjusted so that the desired pulse re-sponse is achieved.Refer to the LMC660and LMC662for a more detailed discussion on compensating for input capacitance.Non-Inverting Large Signal Pulse ResponseDS011467-35Crosstalk Rejection vs FrequencyDS011467-36Stability vs Capacitive Load,R L =600ΩDS011467-37Stability vs Capacitive Load R L =1M ΩDS011467-38DS011467-4FIGURE 1.Cancelling the Effect of Input Capacitance7Applications Hints(Continued)CAPACITIVE LOAD TOLERANCEAll rail-to-rail output swing operational amplifiers have volt-age gain in the output stage.A compensation capacitor is normally included in this integrator stage.The frequency lo-cation of the dominant pole is affected by the resistive load on the amplifier.Capacitive load driving capability can be op-timized by using an appropriate resistive load in parallel with the capacitive load (see typical curves).Direct capacitive loading will reduce the phase margin of many op-amps.A pole in the feedback loop is created by the combination of the op-amp’s output impedance and the ca-pacitive load.This pole induces phase lag at the unity-gain crossover frequency of the amplifier resulting in either an os-cillatory or underdamped pulse response.With a few exter-nal components,op amps can easily indirectly drive capaci-tive loads,as shown in Figure 2.In the circuit of Figure 2,R1and C1serve to counteract the loss of phase margin by feeding the high frequency compo-nent of the output signal back to the amplifier’s inverting in-put,thereby preserving phase margin in the overall feedback loop.Capacitive load driving capability is enhanced by using a pull up resistor to V +Figure 3.Typically a pull up resistor conducting 500µA or more will significantly improve capaci-tive load responses.The value of the pull up resistor must be determined based on the current sinking capability of the amplifier with respect to the desired output swing.Open loop gain of the amplifier can also be affected by the pull up resis-tor (see Electrical Characteristics).PRINTED-CIRCUIT-BOARD LAYOUT FOR HIGH-IMPEDANCE WORKIt is generally recognized that any circuit which must operate with less than 1000pA of leakage current requires special layout of the PC board.When one wishes to take advantage of the ultra-low bias current of the LMC6084,typically less than 10fA,it is essential to have an excellent layout.Fortu-nately,the techniques of obtaining low leakages are quite simple.First,the user must not ignore the surface leakage of the PC board,even though it may sometimes appear accept-ably low,because under conditions of high humidity or dust or contamination,the surface leakage will be appreciable.To minimize the effect of any surface leakage,lay out a ring of foil completely surrounding the LMC6084’s inputs and the terminals of capacitors,diodes,conductors,resistors,relay terminals,etc.connected to the op-amp’s inputs,as in Fig-ure 4.To have a significant effect,guard rings should be placed on both the top and bottom of the PC board.This PC foil must then be connected to a voltage which is at the same voltage as the amplifier inputs,since no leakage current can flow between two points at the same potential.For example,a PC board trace-to-pad resistance of 1012Ω,which is nor-mally considered a very large resistance,could leak 5pA if the trace were a 5V bus adjacent to the pad of the input.This would cause a 100times degradation from the LMC6084’s actual performance.However,if a guard ring is held within 5mV of the inputs,then even a resistance of 1011Ωwould cause only 0.05pA of leakage current.See Figure 5for typi-cal connections of guard rings for standard op-amp configurations.DS011467-5FIGURE 2.LMC6084Noninverting Gain of 10Amplifier,Compensated to Handle Capacitive Loads DS011467-6FIGURE pensating for Large Capacitive Loadswith a Pull Up ResistorDS011467-7FIGURE 4.Example of Guard Ring in P .C.BoardLayout8Applications Hints(Continued)The designer should be aware that when it is inappropriate to lay out a PC board for the sake of just a few circuits,there is another technique which is even better than a guard ring on a PC board:Don’t insert the amplifier’s input pin into the board at all,but bend it up in the air and use only air as an in-sulator.Air is an excellent insulator.In this case you may have to forego some of the advantages of PC board con-struction,but the advantages are sometimes well worth the effort of using point-to-point up-in-the-air wiring.See Figure tchupCMOS devices tend to be susceptible to latchup due to theirinternal parasitic SCR effects.The(I/O)input and output pinslook similar to the gate of the SCR.There is a minimum cur-rent required to trigger the SCR gate lead.The LMC6084isdesigned to withstand100mA surge current on the I/O pins.Some resistive method should be used to isolate any capaci-tance from supplying excess current to the I/O pins.In addi-tion,like an SCR,there is a minimum holding current for anylatchup mode.Limiting current to the supply pins will also in-hibit latchup susceptibility.Typical Single-SupplyApplications(V+=5.0V DC)The extremely high input impedance,and low power con-sumption,of the LMC6084make it ideal for applications thatrequire battery-powered instrumentation amplifiers.Ex-amples of these types of applications are hand-held pHprobes,analytic medical instruments,magnetic field detec-tors,gas detectors,and silicon based pressure transducers. Figure7shows an instrumentation amplifier that featureshigh differential and common mode input resistance(>1014Ω),0.01%gain accuracy at A V=1000,excellent CMRR with1kΩimbalance in bridge source resistance.In-put current is less than100fA and offset drift is less than2.5µV/˚C.R2provides a simple means of adjusting gainover a wide range without degrading CMRR.R7is an initialtrim used to maximize CMRR without using super precisionmatched resistors.For good CMRR over temperature,lowdrift resistors should be used.DS011467-8 Inverting AmplifierDS011467-9 Non-Inverting AmplifierDS011467-10FollowerFIGURE5.Typical Connections of Guard RingsDS011467-11 (Input pins are lifted out of PC board and soldered directly to components.All other pins connected to PC board).FIGURE6.Air Wiring 9Typical Single-SupplyApplications(Continued)DS011467-12 If R1=R5,R3=R6,and R4=R7;then∴A V≈100for circuit shown(R2=9.822k).FIGURE7.Instrumentation AmplifierDS011467-13FIGURE8.Low-Leakage Sample and HoldDS011467-14FIGURE9.1Hz Square Wave Oscillator10Physical Dimensions inches(millimeters)unless otherwise noted14-Pin Small Outline Package(M)Order Number LMC6084AIM or LMC6084IMNS Package Number M14A14-Pin Molded Dual-In-Line Package(N)Order Number LMC6084AMN,LMC6084AIN or LMC6084INNS Package Number N14A11LIFE SUPPORT POLICYNATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DE-VICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMI-CONDUCTOR CORPORATION.As used herein:1.Life support devices or systems are devices or sys-tems which,(a)are intended for surgical implant intothe body,or (b)support or sustain life,and whose fail-ure to perform when properly used in accordancewith instructions for use provided in the labeling,can be reasonably expected to result in a significant injury to the user.2.A critical component is any component of a life support device or system whose failure to perform can be rea-sonably expected to cause the failure of the life support device or system,or to affect its safety or effectiveness.National Semiconductor Corporation AmericasTel:1-800-272-9959Fax:1-800-737-7018Email:support@National Semiconductor EuropeFax:+49(0)180-5308586Email:europe.support@Deutsch Tel:+49(0)180-5308585English Tel:+49(0)180-5327832Français Tel:+49(0)180-5329358Italiano Tel:+49(0)180-5341680National Semiconductor Asia Pacific Customer Response Group Tel:65-2544466Fax:65-2504466Email:sea.support@National Semiconductor Japan Ltd.Tel:81-3-5639-7560Fax:81-3-5639-7507L M C 6084P r e c i s i o n C M O S Q u a d O p e r a t i o n a l A m p l i f i e rNational does not assume any responsibility for use of any circuitry described,no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.。

FM33LG0 低功耗 MCU 芯片产品说明书

FM33LG0低功耗MCU芯片产品说明书2022.03本资料是为了让用户根据用途选择合适的上海复旦微电子集团股份有限公司(以下简称复旦微电子)的产品而提供的参考资料,不转让属于复旦微电子或者第三者所有的知识产权以及其他权利的许可。

在使用本资料所记载的信息最终做出有关信息和产品是否适用的判断前,请您务必将所有信息作为一个整体系统来进行评价。

采购方对于选择与使用本文描述的复旦微电子的产品和服务全权负责,复旦微电子不承担采购方选择与使用本文描述的产品和服务的责任。

除非以书面形式明确地认可,复旦微电子的产品不推荐、不授权、不担保用于包括军事、航空、航天、救生及生命维持系统在内的,由于失效或故障可能导致人身伤亡、严重的财产或环境损失的产品或系统中。

未经复旦微电子的许可,不得翻印或者复制全部或部分本资料的内容。

今后日常的产品更新会在适当的时候发布,恕不另行通知。

在购买本资料所记载的产品时,请预先向复旦微电子在当地的销售办事处确认最新信息,并请您通过各种方式关注复旦微电子公布的信息,包括复旦微电子的网站(/)。

如果您需要了解有关本资料所记载的信息或产品的详情,请与上海复旦微电子集团股份有限公司在当地的销售办事处联系。

商标上海复旦微电子集团股份有限公司的公司名称、徽标以及“复旦”徽标均为上海复旦微电子集团股份有限公司及其分公司在中国的商标或注册商标。

上海复旦微电子集团股份有限公司在中国发布,版权所有。

章节列表章节列表 (3)表目录 (23)图目录 (26)1产品综述 (33)1.1概述 (33)1.2芯片结构框图 (36)1.3产品型号列表 (37)1.4产品特性对照表 (38)2引脚和封装 (39)2.1封装和引脚排列 (39)2.1.1LQFP80封装图(FM33LG0x8) (39)2.1.2LQFP64封装图(FM33LG0x6) (40)2.1.3LQFP48封装图(FM33LG0x5) (41)2.1.4QFN32封装图(FM33LG0x3) (42)2.1.5引脚功能定义(FM33LG0xx) (43)2.1.6封装尺寸图 (50)2.2焊接安装说明 (56)2.3MSL等级 (57)2.4热阻特性 (58)3电参数 (59)3.1参数说明 (59)3.2参数测试条件 (59)3.2.1供电方案 (59)3.3极限参数 (61)3.4性能参数 (62)3.4.1典型工作条件 (62)3.4.2功耗参数 (62)3.4.3复位和电源监控 (64)3.4.4高精度基准源 (65)3.4.5低功耗模式唤醒时间 (67)3.4.6外部时钟源特性 (68)3.4.7内部时钟源特性 (70)3.4.8PLL特性 (71)3.4.9ADC特性 (72)3.4.10DAC特性 (78)3.4.11温度传感器 (81)3.4.12运算放大器特性 (83)3.4.13模拟比较器特性 (85)3.4.14Flash存储器特性 (86)3.4.15GPIO特性 (87)3.4.16LCD特性 (89)3.4.17VBAT测量特性 (90)4总线与存储 (91)4.1系统总线 (91)4.2存储空间分配 (92)4.2.1概述 (92)4.2.2外设模块寄存器地址分配 (95)4.3RAM (97)4.3.1概述 (97)4.4F LASH (98)4.4.1概述 (98)4.4.2特殊信息扇区说明 (98)4.4.3指令Prefetch (103)4.4.4Flash编程 (103)4.4.5Data Flash (108)4.4.6Flash的内容保护 (109)4.5寄存器 (112)4.5.1Flash读取控制寄存器(FLS_RDCR) (112)4.5.2预取指控制寄存器(FLS_PFCR) (113)4.5.3用户配置字寄存器(FLS_OPTBR) (113)4.5.4ACLOCK寄存器1(FLS_ACLOCK1) (114)4.5.5ACLOCK寄存器2(FLS_ACLOCK2) (115)4.5.6Flash擦写控制寄存器(FLS_EPCR) (115)4.5.7Flash Key输入寄存器(FLS_KEY) (116)4.5.8Flash中断使能寄存器(FLS_IER) (116)4.5.9Flash标志寄存器(FLS_ISR) (117)5电源管理单元(PMU) (119)5.1芯片工作电源 (119)5.1.1电源域划分 (119)5.1.2电源结构图 (120)5.1.3ADC和基准电压的独立供电 (120)5.1.4片内快速基准源(AVREF) (121)5.1.5片内高精度基准源(VREF1p2) (121)5.1.6VREFP产生(VREFP_VREG) (121)5.2功耗模式 (122)5.2.1概述 (122)5.2.2功耗模式与系统频率 (123)5.2.3Active模式 (124)5.2.4LP Active模式 (124)5.2.5LP Run模式 (125)5.2.6SLEEP模式 (125)5.2.7DEEPSLEEP模式 (126)5.2.8VBAT模式 (127)5.3唤醒源 (128)5.3.1VREF1p2延迟唤醒功能 (129)5.4休眠唤醒后的时钟控制 (130)5.5寄存器 (131)5.5.1低功耗控制寄存器(PMU_CR) (131)5.5.2唤醒时间控制寄存器(PMU_WKTR) (132)5.5.3唤醒源标志查询寄存器(PMU_WKFR) (133)5.5.4PMU中断使能寄存器(PMU_IER) (134)5.5.5PMU中断标志寄存器(PMU_ISR) (135)5.5.6ULPBG调校寄存器(PMU_ULPB_TR) (135)5.5.7VREFP控制寄存器(PMU_VREFP_CR) (136)5.5.8VREFP配置寄存器(PMU_VREFP_CFGR) (136)5.5.9VREFP状态标志寄存器(PMU_VREFP_ISR) (137)5.5.10VREFP调校寄存器(PMU_VREFP_TR) (138)6.1概述 (139)6.2基准电压的应用 (139)6.3温度传感器 (139)6.4输出缓冲器 (140)6.5芯片休眠 (140)6.6寄存器 (141)6.6.1VREF1p2控制寄存器(VREF_CR) (141)6.6.2VREF1p2配置寄存器(VREF_CFGR) (141)6.6.3VREF1p2标志寄存器(VREF_ISR) (142)6.6.4VREF1p2中断使能寄存器(VREF_IER) (143)6.6.5模拟BUFFER控制寄存器(VREF_BUFCR) (143)7VREFP基准电压(VREFP_VREG) (145)7.1概述 (145)7.2功能描述 (145)7.2.1概述 (145)7.2.2时钟和复位 (150)7.2.3参考电压 (150)7.2.4输出电压 (150)7.2.5工作模式 (151)7.2.6中断和标志 (152)7.3寄存器 (153)8备份电源域(VAO DOMAIN) (154)8.1概述 (154)8.2结构框图 (155)8.3电源切换 (155)8.4复位 (155)8.5低频晶体振荡电路(XTLF) (156)8.5.1概述 (156)8.5.2工作方式 (156)8.5.3停振检测 (156)8.6实时时钟(RTCB) (157)8.7IO (157)8.7.1使用PH15输入实现tamper检测 (157)8.8寄存器 (159)8.8.1VAO复位控制寄存器(VAO_RSTCR) (159)8.8.2XTLF控制寄存器(VAO_XTLFCR) (160)8.8.3XTLF振荡强度寄存器(VAO_XTLFPR) (160)8.8.4停振检测中断使能寄存器(VAO_FDIER) (161)8.8.5停振检测中断标志寄存器(VAO_FDISR) (162)8.8.6VAO IO输入使能寄存器(VAO_INEN) (162)8.8.7VAO IO上拉使能寄存器(VAO_PUEN) (163)8.8.8VAO IO开漏使能寄存器(VAO_ODEN) (163)8.8.9VAO IO功能选择寄存器(VAO_FCR) (164)8.8.10VAO IO输出数据寄存器(VAO_DOR) (164)8.8.11VAO IO输入数据寄存器(VAO_DIR) (165)8.8.12VAO IO输入低阈值配置寄存器(VAO_VILR) (165)9跨电源域接口(CDIF) (167)9.1概述 (167)9.2总线地址 (167)9.4寄存器(CPU DOMAIN) (168)9.4.1接口控制寄存器(CDIF_CR) (168)9.4.2接口预分频寄存器(CDIF_PRSC) (168)10处理器(CPU) (170)10.1概述 (170)10.1.1处理器配置 (170)10.2内核寄存器 (171)10.3异常和中断 (172)10.3.1中断向量表 (172)10.3.2中断优先级 (173)10.3.3错误处理 (173)10.3.4锁定(Lockup) (174)10.4MPU (174)10.4.1MPU寄存器 (175)10.5调试特性 (179)10.5.1调试功能引脚 (179)10.5.2调试状态下的看门狗控制 (179)10.5.3DEBUG的复位 (179)11复位管理单元(RMU) (180)11.1概述 (180)11.2模块框图 (181)11.3VDD上下电复位 (182)11.4软件复位 (183)11.5NRST引脚复位 (183)11.6寄存器 (184)11.6.1PDR配置寄存器(RMU_PDRCR) (184)11.6.2BOR配置寄存器(RMU_BORCR) (185)11.6.3复位配置寄存器(RMU_LKPCR) (185)11.6.4软件复位寄存器(RMU_SOFTRST) (186)11.6.5复位标志寄存器(RMU_RSTFR) (186)11.6.6外设复位使能寄存器(RMU_PRSTEN) (187)11.6.7AHB外设复位寄存器(RMU_AHBRSTCR) (187)11.6.8APB1外设复位寄存器(RMU_APBRSTCR1) (188)11.6.9APB2外设复位寄存器(RMU_APBRSTCR2) (190)12独立看门狗(IWDT) (192)12.1概述 (192)12.2结构框图 (192)12.3IWDT功能描述 (192)12.4IWDT窗口功能 (193)12.5IWDT冻结 (194)12.6寄存器 (195)12.6.1IWDT清除寄存器(IWDT_SERV) (195)12.6.2IWDT配置寄存器(IWDT_CR) (195)12.6.3IWDT计数值寄存器(IWDT_CNT) (196)12.6.4IWDT窗口寄存器(IWDT_WIN) (197)12.6.5IWDT中断使能寄存器(IWDT_IER) (197)12.6.6IWDT中断标志寄存器(IWDT_ISR) (197)13窗口看门狗(WWDT) (199)13.1功能描述 (199)13.3WWDT工作方式 (200)13.4寄存器 (202)13.4.1WWDT控制寄存器(WWDT_CR) (202)13.4.2WWDT配置寄存器(WWDT_CFGR) (202)13.4.3WWDT计数寄存器(WWDT_CNT) (203)13.4.4WWDT中断使能寄存器(WWDT_IER) (203)13.4.5WWDT中断标志寄存器(WWDT_ISR) (204)13.4.6WWDT预分频寄存器(WWDT_PSC) (204)14时钟管理单元(CMU) (206)14.1概述 (206)14.2时钟架构 (207)14.2.1时钟树 (207)14.2.2SYSCLK切换说明 (208)14.2.3时钟安全性 (208)14.2.4主要时钟说明 (208)14.2.5外设模块的总线时钟和工作时钟 (209)14.2.6休眠模式下的外设时钟 (210)14.2.7LSCLK切换逻辑 (211)14.3高频RC振荡器(RCHF) (212)14.3.1概述 (212)14.3.2软件使用指南 (212)14.4低频RC振荡器(RCLF) (213)14.4.1概述 (213)14.5低功耗RC振荡器(RCLP) (214)14.5.1概述 (214)14.5.2软件使用指南 (214)14.6高频晶体振荡电路(XTHF) (215)14.6.1概述 (215)14.6.2工作方式 (215)14.6.3停振检测(HFDET) (215)14.7锁相环(PLL) (216)14.7.1概述 (216)14.7.2软件应用指南 (216)14.8时钟校准 (217)14.9低功耗模式下的时钟源 (218)14.10休眠唤醒的时钟处理 (218)14.11寄存器 (219)14.11.1系统时钟配置寄存器(CMU_SYSCLKCR) (220)14.11.2RCHF时钟控制寄存器(CMU_RCHCR) (221)14.11.3RCHF调校寄存器(CMU_RCHFTR) (222)14.11.4PLL控制寄存器(CMU_PLLCR) (222)14.11.5RCLP控制寄存器(CMU_RCLPCR) (223)14.11.6RCLP调校寄存器(CMU_RCLPTR) (224)14.11.7LSCLK选择寄存器(CMU_LSCLKSEL) (224)14.11.8XTHF控制寄存器(CMU_XTHFCR) (225)14.11.9RCLF控制寄存器(CMU_RCLFCR) (225)14.11.10RCLF调校寄存器(CMU_RCLFTR) (226)14.11.11CMU中断使能寄存器(CMU_IER) (226)14.11.12CMU中断标志寄存器(CMU_ISR) (227)14.11.13外设总线时钟控制寄存器1(CMU_PCLKCR1) (228)14.11.14外设总线时钟控制寄存器2(CMU_PCLKCR2) (228)14.11.15外设总线时钟控制寄存器3(CMU_PCLKCR3) (229)14.11.16外设总线时钟控制寄存器4(CMU_PCLKCR4) (230)14.11.17外设工作时钟配置寄存器1(CMU_OPCCR1) (231)14.11.18外设工作时钟配置寄存器2(CMU_OPCCR2) (232)14.11.19外设工作时钟配置寄存器3(CMU_OPCCR3) (233)14.11.20AHB Master控制寄存器(CMU_AHBMCR) (234)14.11.21时钟校准控制寄存器(CMU_CCCR) (235)14.11.22时钟校准配置寄存器(CMU_CCFR) (235)14.11.23时钟校准计数值寄存器(CMU_CCNR) (236)14.11.24时钟校准中断标志寄存器(CMU_CCISR) (237)15电源电压监测(SVD) (238)15.1概述 (238)15.2结构框图 (238)15.3引脚定义 (239)15.4功能描述 (239)15.5间歇使能模式 (241)15.6外部电源检测 (241)15.7电源检测阈值 (242)15.8寄存器 (246)15.8.1SVD配置寄存器(SVD_CFGR) (246)15.8.2SVD控制寄存器(SVD_CR) (247)15.8.3SVD中断使能寄存器(SVD_IER) (247)15.8.4SVD状态和标志寄存器(SVD_ISR) (248)15.8.5SVD参考电压选择寄存器(SVD_VSR) (248)16AES硬件运算单元(AES) (250)16.1功能描述 (250)16.2工作模式 (250)16.3AES数据流处理模式 (251)16.3.1ECB模式 (251)16.3.2CBC模式 (252)16.3.3暂停模式 (254)16.3.4CTR模式 (255)16.3.5CTR模式下的暂停模式 (256)16.3.6GCM模式 (256)16.3.7MultH模块 (259)16.3.8推荐的GCM流程 (260)16.4数据类型 (261)16.5工作流程 (262)16.5.1模式1:加密 (262)16.5.2模式2:密钥扩展 (263)16.5.3模式3:解密 (264)16.5.4模式4:密钥扩展+解密 (264)16.5.5使用MultH模块 (265)16.6DMA接口 (266)16.6.1MultH模块与DMA间接口 (267)16.7错误标志 (267)16.8寄存器 (268)16.8.1AES控制寄存器(AES_CR) (268)16.8.2AES中断使能寄存器(AES_IER) (270)16.8.3AES中断标志寄存器(AES_ISR) (271)16.8.4AES数据输入寄存器(AES_DIR) (271)16.8.6AES秘钥寄存器(AES_KEYx) (272)16.8.7AES初始向量寄存器(AES_IVRx) (273)16.8.8AES MultH参数寄存器(AES_Hx) (273)17随机数发生器(TRNG) (274)17.1概述 (274)17.2功能描述 (275)17.2.1随机数产生 (275)17.2.2工作时钟 (275)17.2.3随机数读取 (276)17.2.4CRC运算 (276)17.3寄存器 (277)17.3.1随机数控制寄存器(RNG_CR) (277)17.3.2随机数/CRC结果输出寄存器(RNG_DOR) (277)17.3.3RNG标志寄存器(RNG_SR) (278)17.3.4CRC控制寄存器(RNG_CRCCR) (278)17.3.5CRC输入数据寄存器(RNG_CRCDIR) (279)17.3.6CRC标志寄存器(RNG_CRCSR) (279)18运算放大器(OPA1) (281)18.1概述 (281)18.2结构框图 (282)18.3引脚定义 (283)18.4功能描述 (283)18.4.1时钟和复位 (283)18.4.2Standalone模式(non-inverting amplifier) (284)18.4.3Standalone模式(inverting amplifier) (285)18.4.4Buffer模式 (285)18.4.5同相PGA模式 (286)18.4.6反相PGA模式 (288)18.4.7Offset校准 (290)18.4.8低功耗模式 (291)18.4.9休眠模式下的OPA (292)18.5寄存器 (293)18.5.1OPA1控制寄存器(OPA1_CR) (293)18.5.2OPA1校准寄存器(OPA1_CALR) (294)18.5.3OPA1校准输出寄存器(OPA1_COR) (295)19模拟比较器(COMPARATOR) (297)19.1概述 (297)19.2结构框图 (298)19.3功能描述 (299)19.3.1基本功能 (299)19.3.2内部比较基准选择和产生 (299)19.3.3时钟和复位 (300)19.3.4引脚和内部信号连接 (300)19.3.5窗口功能 (301)19.3.6功耗和速度模式 (302)19.3.1比较器中断 (303)19.3.2比较器输出和触发输出 (303)19.3.3输出数字滤波 (305)19.4寄存器 (306)控制寄存器()19.4.3COMP3控制寄存器(COMP3_CR) (309)19.4.4COMP中断配置寄存器(COMP_ICR) (310)19.4.5COMP中断标志寄存器(COMP_IF) (311)19.4.6COMP缓冲器控制寄存器(COMP_BUFCR) (311)20除法/开方运算加速器(DIVAS) (313)20.1概述 (313)20.2时钟和复位 (313)20.3硬件除法工作流程 (313)20.4硬件开方工作流程 (314)20.5寄存器 (315)20.5.1操作数寄存器 (315)20.5.2除数寄存器 (315)20.5.3商寄存器 (316)20.5.4余数寄存器 (316)20.5.5根寄存器 (317)20.5.6状态标志寄存器 (317)20.5.7控制寄存器 (318)21双线串行总线(I2C) (319)21.1概述 (319)21.2结构框图 (319)21.3引脚定义和上拉电阻范围 (320)21.4时钟和复位 (324)21.5接口时序 (325)21.5.1接口时序图 (325)21.5.2接口时序描述 (326)21.6I2C工作模式 (328)21.7I2C从机地址格式 (329)21.8I2C初始化 (330)21.8.1IO配置 (330)21.8.2主机波特率配置 (330)21.8.3从机的输入模拟滤波和输出延迟 (331)21.9I2C主机功能 (332)21.9.17bit寻址 (332)21.9.210bit寻址 (337)21.9.3DMA (340)21.9.4SCL延展(Slave Clock Stretching) (344)21.9.5超时机制 (344)21.9.6可编程时序 (344)21.10I2C从机功能 (346)21.10.1从机寻址 (346)21.10.2从机发送数据 (346)21.10.3从机接收数据 (347)21.10.4从机低功耗接收唤醒 (349)21.10.5DMA (349)21.10.6从机时序 (353)21.11寄存器 (354)21.11.1I2C主机配置寄存器(I2C_MSPCFGR) (354)21.11.2I2C主机控制寄存器(I2C_MSPCR) (355)21.11.3I2C主机中断使能寄存器(I2C_MSPIER) (356)21.11.4I2C主机中断标志寄存器(I2C_MSPISR) (357)21.11.5I2C主机状态寄存器(I2C_MSPSR) (357)21.11.6I2C主机波特率设置寄存器(I2C_MSPBGR) (358)21.11.7I2C主机收发缓冲寄存器(I2C_MSPBUF) (359)21.11.8I2C主机时序控制寄存器(I2C_MSPTCR) (359)21.11.9I2C主机超时寄存器(I2C_MSPTOR) (360)21.11.10I2C从机控制寄存器(I2C_SSPCR) (360)21.11.11I2C从机中断使能寄存器(I2C_SSPIER) (361)21.11.12I2C从机中断标志寄存器(I2C_SSPISR) (362)21.11.13I2C从机状态寄存器(I2C_SSPSR) (363)21.11.14I2C从机收发缓冲寄存器(I2C_SSPBUF) (364)21.11.15I2C从机地址寄存器(I2C_SSPADR) (364)22通用异步收发传输器(UART) (366)22.1概述 (366)22.2结构框图 (367)22.3引脚定义 (368)22.4UART类型区分 (369)22.5UART字符描述 (369)22.6功能描述 (371)22.6.1时钟和复位 (371)22.6.2位接收采样 (371)22.6.3数据发送 (372)22.6.4数据接收 (374)22.6.5低功耗休眠唤醒(UART0/1) (375)22.6.6使用DMA进行UART收发 (375)22.6.7DMA模式下的发送完成中断 (376)22.7波特率发生 (376)22.7.1波特率发生 (376)22.7.1波特率自适应 (377)22.8红外调制 (378)22.9接收超时 (379)22.10发送延迟 (379)22.11寄存器 (380)22.11.1红外调制寄存器(UART_IRCR) (381)22.11.2UARTx控制状态寄存器(UARTx_CSR) (382)22.11.3UARTx中断使能寄存器(UARTx_IER) (383)22.11.4UARTx中断标志寄存器(UARTx_ISR) (384)22.11.5UARTx超时和延迟寄存器(UARTx_TODR) (385)22.11.6UARTx接收缓冲寄存器(UARTx_RXBUF) (385)22.11.7UARTx发送缓冲寄存器(UARTx_TXBUF) (386)22.11.8UATRx波特率产生寄存器(UARTx_BGR) (386)23低功耗UART(LPUART) (388)23.1概述 (388)23.2结构框图 (389)23.3引脚定义 (390)23.4时钟和复位 (390)23.5字符描述 (391)23.6功能描述 (393)23.6.1位接收采样和发送 (393)23.6.2接收流程 (394)23.6.3发送流程 (394)23.6.4使用DMA进行LPUART收发 (394)23.6.5休眠模式下的数据接收唤醒 (395)23.6.6LPRUN模式下的数据DMA收发 (395)23.6.7DMA模式下的发送完成中断 (395)23.7寄存器 (397)23.7.1LPUARTx控制状态寄存器(LPUARTx_CSR) (398)23.7.2LPUARTx中断使能寄存器(LPUARTx _IER) (399)23.7.3LPUARTx中断标志寄存器(LPUARTx _ISR) (400)23.7.4LPUARTx波特率调制寄存器(LPUARTx _BMR) (400)23.7.5LPUARTx接收数据寄存器(LPUARTx _RXBUF) (401)23.7.6LPUARTx发送数据寄存器(LPUARTx _TXBUF) (402)23.7.7LPUARTx数据匹配寄存器(LPUARTx _DMR) (402)24串行外设接口(SPI) (404)24.1概述 (404)24.2结构框图 (404)24.3引脚定义 (406)24.4时钟和复位 (406)24.5接口时序 (406)24.5.1CPHA=0 (406)24.5.2CPHA=1 (407)24.5.14线半双工模式(主机) (407)24.6功能描述 (409)24.6.1I/O配置 (409)24.6.2全双工数据通信 (410)24.6.3TX-ONLY模式 (411)24.6.4RX-ONLY模式 (412)24.6.5主机SSN控制 (412)24.6.6数据冲突 (413)24.6.7使用DMA进行SPI收发 (413)24.7寄存器 (415)24.7.1SPI控制寄存器1(SPIx_CR1) (416)24.7.2SPI控制寄存器2(SPIx_CR2) (417)24.7.3SPI控制寄存器3(SPIx_CR3) (418)24.7.4SPI中断控制寄存器(SPIx_IER) (419)24.7.5SPI中断标志寄存器(SPIx_ISR) (419)24.7.6SPI发送缓存寄存器(SPIx_TXBUF) (420)24.7.7SPI发送缓存寄存器(SPIx_RXBUF) (420)25智能卡接口(ISO7816) (422)25.1概述 (422)25.2结构框图 (422)25.3时钟和复位 (423)25.4接口时序 (423)25.5功能描述 (424)25.5.1数据接收 (424)25.5.2数据发送 (424)25.5.3使用DMA进行7816收发 (426)25.6寄存器 (427)25.6.1U7816控制寄存器(U7816_CR) (427)25.6.2U7816帧格式控制寄存器(U7816_FFR) (428)25.6.3U7816额外保护时间寄存器(U7816_EGTR) (429)25.6.4U7816工作时钟分频寄存器(U7816_PSC) (429)25.6.5U7816波特率寄存器(U7816_BGR) (430)25.6.6U7816数据接收缓冲寄存器(U7816_RXBUF) (430)25.6.7U7816数据发送缓冲寄存器(U7816_TXBUF) (431)25.6.8U7816中断使能寄存器(U7816_IER) (431)25.6.9U7816状态标志寄存器(U7816_ISR) (432)26控制器区域网络(CAN) (434)26.1概述 (434)26.2结构框图 (434)26.3引脚定义 (435)26.4功能描述 (435)26.4.1时钟和复位 (435)26.4.2Bit timing (435)26.4.3Bit stream processor (436)26.4.4控制器工作模式 (436)26.4.5消息帧存储和消息帧结构(Message storage and structure) (437)26.4.6消息滤波器(Acceptance Filter) (439)26.4.7错误管理 (439)26.5编程模型 (443)26.5.1寄存器配置 (443)26.5.2消息传输 (443)26.6寄存器 (445)26.6.1CAN控制寄存器(CAN_CR) (446)26.6.2CAN模式选择寄存器(CAN_MSR) (447)26.6.3CAN波特率预分频寄存器(CAN_BRPR) (447)26.6.4CAN位时序寄存器(CAN_BTR) (448)26.6.5CAN错误计数寄存器(CAN_ECR) (448)26.6.6CAN错误状态寄存器(CAN_ESR) (449)26.6.7CAN状态标志寄存器(CAN_SR) (450)26.6.8CAN中断标志寄存器(CAN_ISR) (451)26.6.9CAN中断使能寄存器(CAN_IER) (452)26.6.10CAN中断清除寄存器(CAN_ICR) (453)26.6.11CAN发送FIFO ID寄存器(CAN_TXFIDR) (453)26.6.12CAN发送FIFO DLC寄存器(CAN_TXFDLCR) (454)26.6.13CAN发送FIFO DataWord1寄存器(CAN_TXFDW1R) (454)26.6.14CAN发送FIFO DataWord2寄存器(CAN_TXFDW2R) (455)26.6.15CAN高优先级发送缓冲ID寄存器(CAN_HPBIDR) (455)26.6.16CAN高优先级发送缓冲DLC寄存器(CAN_HPBDLCR) (456)26.6.17CAN高优先级发送缓冲DataWord1寄存器(CAN_HPBDW1R) (456)26.6.18CAN高优先级发送缓冲DataWord2寄存器(CAN_HPBDW2R) (457)26.6.19CAN接收FIFO ID寄存器(CAN_RXF_IDR) (457)26.6.20CAN接收FIFO DLC寄存器(CAN_RXFDLCR) (458)26.6.21CAN接收FIFO DataWord1寄存器(CAN_RXFDW1R) (458)26.6.22CAN接收FIFO DataWord2寄存器(CAN_RXFDW2R) (459)26.6.23CAN接收滤波寄存器(CAN_AFR) (459)26.6.24CAN接收滤波掩码寄存器x(CAN_AFMRx) (460)26.6.25CAN接收滤波ID寄存器x(CAN_AFIRx) (461)27直接存储访问控制器(DMA) (462)27.1概述 (462)27.2工作原理 (463)27.3结构框图 (464)27.4工作流程 (464)27.5访问带宽 (466)27.6通道控制 (467)27.6.1DMA请求映射 (467)27.6.2通道优先级 (468)27.6.3传输方向定义 (468)27.6.4循环模式 (468)27.7寄存器 (469)27.7.1DMA全局控制寄存器(DMA_GCR) (469)27.7.2通道x控制寄存器(DMA_CHxCR) (470)27.7.3通道x存储器指针寄存器(DMA_CHxMAD) (471)27.7.4通道7控制寄存器(DMA_CH7CR) (472)27.7.5通道7 Flash指针寄存器(DMA_CH7FLSAD) (473)27.7.6通道7 RAM指针寄存器(DMA_CH7RAMAD) (473)27.7.7DMA状态标志寄存器(DMA_ISR) (474)28循环冗余校验(CRC) (475)28.1概述 (475)28.2软件配置过程 (476)28.3G OLDEN 数据 (477)28.4DMA接口 (477)28.5F LASH数据完整性校验 (478)28.6寄存器 (479)28.6.1CRC数据寄存器(CRC_DR) (479)28.6.2CRC控制状态寄存器(CRC_CR) (479)28.6.3CRC LFSR寄存器(CRC_LFSR) (481)28.6.4CRC输出异或寄存器(CRC_XOR) (481)28.6.5CRC多项式寄存器(CRC_POLY) (481)29高级定时器(ATIM) (483)29.1概述 (483)29.2主要特性 (483)29.3结构框图 (484)29.4功能描述 (485)29.4.1定时单元 (485)29.4.2定时器工作模式 (487)29.4.3重复计数器 (494)29.4.4Preload寄存器 (495)29.4.5计数器工作时钟 (496)29.4.6内部触发信号(ITRx) (501)29.4.7捕捉/比较通道 (502)29.4.8输入捕捉模式 (504)29.4.9软件Force输出 (506)29.4.10输出比较模式 (507)29.4.11PWM输出 (508)29.4.12互补输出和死区插入 (510)29.4.13刹车功能 (511)29.4.14互补输出通道信号状态逻辑表 (513)29.4.156-step PWM输出 (514)29.4.16单脉冲输出 (515)29.4.17外部事件清除OCxREF (517)29.4.18编码器接口模式(encoder interface) (518)29.4.19TIM从机模式 (520)29.4.20DMA访问 (523)29.4.21DMA Burst (524)29.4.22输入异或功能 (525)29.4.23霍尔传感器接口 (525)29.4.24Debug模式 (526)29.5.1ATIM控制寄存器1(ATIM_CR1) (527)29.5.2ATIM控制寄存器2(ATIM_CR2) (529)29.5.3ATIM从机模式控制寄存器(ATIM_SMCR) (530)29.5.4ATIM DMA和中断使能寄存器(ATIM_DIER) (532)29.5.5ATIM状态寄存器(ATIM_ISR) (533)29.5.6ATIM事件产生寄存器(ATIM_EGR) (535)29.5.7ATIM捕捉/比较模式寄存器1(ATIM_CCMR1) (535)29.5.8ATIM捕捉/比较模式寄存器2(ATIM_CCMR2) (538)29.5.9ATIM捕捉/比较使能寄存器(ATIM_CCER) (540)29.5.10ATIM计数器寄存器(ATIM_CNT) (541)29.5.11ATIM预分频寄存器(ATIM_PSC) (541)29.5.12ATIM自动重载寄存器(ATIM_ARR) (542)29.5.13ATIM重复计数寄存器(ATIM_RCR) (542)29.5.14ATIM捕捉/比较寄存器1(ATIM_CCR1) (543)29.5.15ATIM捕捉/比较寄存器2(ATIM_CCR2) (544)29.5.16ATIM捕捉/比较寄存器3(ATIM_CCR3) (544)29.5.17ATIM捕捉/比较寄存器4(ATIM_CCR4) (545)29.5.18ATIM刹车和死区控制寄存器(ATIM_BDTR) (545)29.5.19ATIM DMA控制寄存器(ATIM_DCR) (547)29.5.20ATIM DMA访问寄存器(ATIM_DMAR) (548)29.5.21ATIM刹车输入控制寄存器(ATIM_BKCR) (548)30通用定时器(GPTIM0,1,2) (550)30.1概述 (550)30.2主要特性 (550)30.3结构框图 (551)30.4功能描述 (552)30.4.1定时单元 (552)30.4.2定时器工作模式 (554)30.4.3计数器工作时钟 (561)30.4.4内部触发信号(ITRx)的捕捉 (567)30.4.5捕捉/比较通道 (568)30.4.6输入捕捉模式 (569)30.4.7软件Force输出 (571)30.4.8输出比较模式 (571)30.4.9PWM模式 (572)30.4.10单脉冲输出 (573)30.4.11外部事件清除OCxREF (575)30.4.12编码器接口模式(encoder interface) (575)30.4.13GPTIM从机模式 (576)30.4.14DMA访问 (579)30.4.15DMA Burst (580)30.4.16输入异或功能 (580)30.4.17Debug模式 (580)30.5寄存器 (581)30.5.1GPTIMx控制寄存器1(GPTIMx_CR1) (583)30.5.2GPTIMx控制寄存器2(GPTIMx_CR2) (584)30.5.3GPTIMx从机模式控制寄存器(GPTIMx_SMCR) (585)30.5.4GPTIMx DMA和中断使能寄存器(GPTIMx_DIER) (587)30.5.5GPTIMx状态寄存器(GPTIMx_ISR) (588)30.5.6GPTIMx事件产生寄存器(GPTIMx_EGR) (589)30.5.7GPTIMx捕捉/比较模式寄存器1(GPTIMx_CCMR1) (590)30.5.8GPTIMx捕捉/比较模式寄存器2(GPTIMx_CCMR2) (592)30.5.9GPTIMx捕捉/比较使能寄存器(GPTIMx_CCER) (595)30.5.10GPTIMx计数器寄存器(GPTIMx_CNT) (596)30.5.11GPTIMx预分频寄存器(GPTIMx_PSC) (596)30.5.12GPTIMx自动重载寄存器(GPTIMx_ARR) (597)30.5.13GPTIMx捕捉/比较寄存器1(GPTIMx_CCR1) (597)30.5.14GPTIMx捕捉/比较寄存器2(GPTIMx_CCR2) (598)30.5.15GPTIMx捕捉/比较寄存器3(GPTIMx_CCR3) (598)30.5.16GPTIMx捕捉/比较寄存器4(GPTIMx_CCR4) (599)30.5.17GPTIMx DMA控制寄存器(GPTIMx_DCR) (599)30.5.18GPTIMx DMA访问寄存器(GPTIMx_DMAR) (600)30.5.19GPTIMx ITR选择寄存器(GPTIMx_ITRSEL) (601)3132位基本定时器(BSTIM32) (603)31.1概述 (603)31.2主要特性 (603)31.3结构框图 (603)31.4功能描述 (604)31.4.1定时单元 (604)31.4.2定时器工作模式 (606)31.4.3计数器工作时钟 (608)31.4.1Debug模式 (609)31.5寄存器 (610)31.5.1BSTIM32控制寄存器1(BSTIM32_CR1) (610)31.5.2BSTIM32控制寄存器2(BSTIM32_CR2) (611)31.5.3BSTIM32中断使能寄存器(BSTIM32_IER) (611)31.5.4BSTIM32中断标志寄存器(BSTIM32_ISR) (612)31.5.5BSTIM32事件产生寄存器(BSTIM32_EGR) (613)31.5.6BSTIM32计数器寄存器(BSTIM32_CNT) (613)31.5.7BSTIM32预分频寄存器(BSTIM_PSC) (614)31.5.8BSTIM32自动重载寄存器(BSTIM32_ARR) (614)3216位基本定时器(BSTIM16) (615)32.1概述 (615)32.2主要特性 (615)32.3结构框图 (615)32.4功能描述 (616)32.4.1定时单元 (616)32.4.2定时器工作模式 (618)32.4.3计数器工作时钟 (620)32.4.4Debug模式 (621)32.5寄存器 (622)32.5.1BSTIM16控制寄存器1(BSTIM16_CR1) (622)32.5.2BSTIM16控制寄存器2(BSTIM16_CR2) (623)32.5.3BSTIM16中断使能寄存器(BSTIM16_IER) (624)32.5.4BSTIM16中断标志寄存器(BSTIM16_ISR) (624)32.5.5BSTIM16事件产生寄存器(BSTIM16_EGR) (625)32.5.1BSTIM16计数器寄存器(BSTIM16_CNT) (625)32.5.1BSTIM16预分频寄存器(BSTIM16_PSC) (626)32.5.1BSTIM16自动重载寄存器(BSTIM16_ARR) (626)3332位低功耗定时器(LPTIM32) (628)33.1概述 (628)33.2结构框图 (629)33.5定时器功能 (630)33.5.1普通定时器 (630)33.5.2外部脉冲触发计数 (630)33.5.3外部异步脉冲计数 (631)33.5.4Timeout模式 (631)33.6捕捉比较功能 (632)33.6.132bit PWM (632)33.6.2输入捕捉 (633)33.7触发信号输出 (634)33.8寄存器 (635)33.8.1LPTIM32配置寄存器(LPTIM32_CFGR) (635)33.8.2LPTIM32计数值寄存器(LPTIM32_CNT) (637)33.8.3LPTIM32捕捉比较控制和状态寄存器(LPTIM32_CCSR) (637)33.8.4LPTIM32目标值寄存器(LPTIM32_ARR) (639)33.8.5LPTIM32中断使能寄存器(LPTIM32_IER) (640)33.8.6LPTIM32中断标志寄存器(LPTIM32_ISR) (641)33.8.7LPTIM32控制寄存器(LPTIM32_CR) (642)33.8.8LPTIM32捕捉比较寄存器1(LPTIM32_CCR1) (643)33.8.9LPTIM32捕捉比较寄存器2(LPTIM32_CCR2) (643)33.8.10LPTIM32捕捉比较寄存器3(LPTIM32_CCR3) (644)33.8.11LPTIM32捕捉比较寄存器4(LPTIM32_CCR4) (644)3416位低功耗定时器(LPTIM16) (645)34.1概述 (645)34.2结构框图 (646)34.3时钟和复位 (646)34.4相关引脚 (647)34.5定时器功能 (647)34.5.1普通定时器 (647)34.5.2外部脉冲触发计数 (647)34.5.3外部异步脉冲计数 (648)34.5.4Timeout模式 (648)34.6捕捉比较功能 (649)34.6.116bit PWM (649)34.6.2输入捕捉 (650)34.6.3输入数字滤波 (651)34.7正交编码器 (652)34.8触发信号输出 (653)34.9寄存器 (654)34.9.1LPTIM16配置寄存器(LPTIM16_CFGR) (654)34.9.2LPTIM16计数值寄存器(LPTIM16_CNT) (656)34.9.3LPTIM16捕捉比较控制和状态寄存器(LPTIM16_CCSR) (656)34.9.4LPTIM16目标值寄存器(LPTIM16_ARR) (658)34.9.5LPTIM中断使能寄存器(LPTIM_IER) (659)34.9.6LPTIM16中断标志寄存器(LPTIM16_ISR) (659)34.9.7LPTIM16控制寄存器(LPTIM16_CR) (660)34.9.8LPTIM16捕捉比较寄存器1(LPTIM16_CCR1) (661)34.9.9LPTIM16捕捉比较寄存器2(LPTIM16_CCR2) (661)35实时时钟(RTCA) (663)35.1概述 (663)35.2结构框图 (663)35.3工作原理 (664)35.3.2LTBC数字调校 (665)35.3.3BCD时间 (666)35.3.4RTC使能与停止 (667)35.3.5RTC时间设置 (667)35.3.6RTC时间读取 (667)35.3.7闰年判断 (668)35.4寄存器 (669)35.4.1RTCA写使能寄存器(RTCA_WER) (669)35.4.2RTCA中断使能寄存器(RTCA_IER) (670)35.4.3RTCA中断标志寄存器(RTCA_ISR) (671)35.4.4BCD时间秒寄存器(RTCA_BCDSEC) (672)35.4.5BCD时间分钟寄存器(RTCA_BCDMIN) (673)35.4.6BCD时间小时寄存器(RTCA_BCDHOUR) (673)35.4.7BCD时间天寄存器(RTCA_BCDDAY) (674)35.4.8BCD时间星期寄存器(RTCA_BCDWEEK) (674)35.4.9BCD时间月寄存器(RTCA_BCDMONTH) (675)35.4.10BCD时间年寄存器(RTCA_BCDYEAR) (675)35.4.11闹钟寄存器(RTCA_ALARM) (676)35.4.12RTC时间信号输出寄存器(RTCA_TMSEL) (676)35.4.13LTBC数值调整寄存器(RTCA_ADJUST) (677)35.4.14毫秒计数值寄存器(RTCA_SBSCNT) (678)35.4.15RTCA控制寄存器RTCA_CR (678)36实时时钟(RTCB) (679)36.1概述 (679)36.2结构框图 (679)36.3工作原理 (680)36.3.1工作时钟 (680)36.3.2时基计数器(LTBC) (680)36.3.3LTBC数字调校 (680)36.3.4BCD时间 (682)36.3.5RTC使能与停止 (682)36.3.6RTC时间设置 (683)36.3.7RTC时间读取 (683)36.3.8闰年判断 (684)36.3.9RTC时间戳 (684)36.3.10备份寄存器 (685)36.4寄存器 (686)36.4.1RTCB写使能寄存器(RTCB_WER) (687)36.4.2RTCB中断使能寄存器(RTCB_IER) (687)36.4.3RTCB中断标志寄存器(RTCB_ISR) (688)36.4.4BCD时间秒寄存器(RTCB_BCDSEC) (689)36.4.5BCD时间分钟寄存器(RTCB_BCDMIN) (689)36.4.6BCD时间小时寄存器(RTCB_BCDHOUR) (690)36.4.7BCD时间天寄存器(RTCB_BCDDAY) (690)36.4.8BCD时间星期寄存器(RTCB_BCDWEEK) (691)36.4.9BCD时间月寄存器(RTCB_BCDMONTH) (691)36.4.10BCD时间年寄存器(RTCB_BCDYEAR) (692)36.4.11RTCB时间信号输出寄存器(RTCB_TMSEL) (692)36.4.12RTCB时钟调校寄存器(RTCB_ADJR) (693)36.4.13RTCB控制寄存器(RTCB_CR) (693)36.4.14RTCB时间戳控制寄存器(RTCB_STPCR) (694)36.4.15RTCB时间戳时钟寄存器(RTCB_STPCLKRR) (695)36.4.16RTCB时间戳日历寄存器(RTCB_STPCALRR) (695)36.4.17RTCB备份寄存器组(RTCB_BKRx) (696)37段码液晶驱动(LCD) (697)37.1概述 (697)37.2结构框图 (697)37.3IO配置 (699)37.4功能说明 (699)37.4.1工作时钟和显示帧频率 (699)37.4.2LCD Type A扫描波形 (699)37.4.3LCD Type B扫描波形 (704)37.4.4片内buffer驱动模式 (708)37.4.5片外电容驱动模式 (708)37.4.6显示闪烁功能 (709)37.4.7偏置电压调整 (709)37.5低功耗模式 (710)37.6寄存器 (711)37.6.1显示控制寄存器(LCD_CR) (711)37.6.2显示测试控制寄存器(LCD_TEST) (713)37.6.3显示频率控制寄存器(LCD_FCR) (714)37.6.4闪烁时间寄存器(LCD_FLKT) (715)37.6.5显示中断使能寄存器(LCD_IER) (715)37.6.6显示中断标志寄存器(LCD_ISR) (716)37.6.7显示数据寄存器(LCD_DATAx) (716)37.6.8LCD COM使能控制寄存器(LCD_COMEN) (723)37.6.9LCD SEG使能控制寄存器0(LCD_SEGEN0) (723)37.6.10LCD SEG使能控制寄存器1(LCD_SEGEN1) (724)38模数转换器(ADC) (725)38.1概述 (725)38.2结构框图 (726)38.3输入通道 (727)38.4单端和差分输入 (728)38.5工作时序 (730)38.6功能描述 (732)38.6.1使用VDDA作为基准 (732)38.6.2使用VREFP作为基准 (733)38.6.3温度传感器 (733)38.6.4温度传感器的斜率和标定 (734)38.6.5可编程采样时间 (734)38.6.6输出位宽选择 (736)38.6.7输入缓冲器 (736)38.6.8VBAT和VDD电源电压采样 (737)38.6.9内部信号采样 (737)38.6.10转换模式 (738)38.6.11转换触发 (741)38.6.12过采样和硬件平均 (742)38.6.13ADC工作时钟 (743)38.6.14数据冲突和自动等待 (743)38.6.15DMA (744)38.6.16模拟窗口看门狗(AWD) (750)38.6.17ADC校准 (751)38.8寄存器 (753)38.8.1ADC中断和状态寄存器(ADC_ISR) (753)38.8.2ADC中断使能寄存器(ADC_IER) (754)38.8.3ADC控制寄存器1(ADC_CR1) (755)38.8.4ADC控制寄存器2(ADC_CR2) (755)38.8.5ADC校准控制寄存器(ADC_CALR) (756)38.8.6ADC配置寄存器1(ADC_CFGR1) (757)38.8.7ADC配置寄存器2(ADC_CFGR2) (758)38.8.8ADC采样时间控制寄存器(ADC_SMTR) (760)38.8.9ADC通道控制寄存器(ADC_CHER) (762)38.8.10ADC通道差分控制寄存器(ADC_DCR) (763)38.8.11ADC数据寄存器(ADC_DR) (763)38.8.12AWD阈值寄存器(ADC_HLTR) (764)39数模转换器(DAC) (765)39.1概述 (765)39.2结构框图 (765)39.3引脚定义 (766)39.4DAC输出与引脚和其他模块的互联 (766)39.5功能描述 (767)39.5.1工作时钟与信号时序 (767)39.5.2DAC输出模式 (767)39.5.3DAC触发源选择 (769)39.5.4DAC输出电压 (769)39.5.5DMA (769)39.5.6采样保持 (770)39.5.7DAC输出Buffer (772)39.5.8低功耗模式下的DAC (773)39.6寄存器 (774)39.6.1DAC控制寄存器1(DAC_CR1) (774)39.6.2DAC控制寄存器2(DAC_CR2) (774)39.6.1DAC配置寄存器(DAC_CFGR) (775)39.6.2DAC软件触发寄存器(DAC_SWTRGR) (776)39.6.3DAC数据保持寄存器(DAC_DHR) (776)39.6.4DAC状态标志寄存器(DAC_ISR) (777)39.6.5DAC中断使能寄存器(DAC_IER) (777)39.6.1DAC采样保持时间寄存器(DAC_SHTR) (778)40可编程胶合逻辑(PGL) (780)40.1概述 (780)40.2结构框图 (780)40.3引脚定义 (782)40.4功能描述 (783)40.4.1LUT真值表 (783)40.4.2LUT输入 (784)40.4.3LUT输出 (784)40.4.4滤波和采样 (784)40.4.5中断和触发 (785)40.4.6低功耗模式 (786)40.5寄存器 (787)40.5.1PGL控制寄存器(PGL_CR) (787)40.5.2PGL配置寄存器0(PGL_CFGR0) (788)40.5.3PGL配置寄存器1(PGL_CFGR1) (789)40.5.5PGL配置寄存器3(PGL_CFGR3) (791)40.5.6PGL中断使能寄存器(PGL_IER) (792)40.5.7PGL中断标志寄存器(PGL_ISR) (793)40.5.8LUT0真值表寄存器(PGL_LUT0) (793)40.5.9LUT1真值表寄存器(PGL_LUT1) (794)40.5.10LUT2真值表寄存器(PGL_LUT2) (794)40.5.11LUT3真值表寄存器(PGL_LUT3) (795)41I/O端口(GPIO) (796)41.1概述 (796)41.2引脚类型 (796)41.2.1GPIO,输入输出使能,可控上拉电阻,可控开漏输出 (797)41.2.2GPIO,输入输出使能,2个可控上拉电阻,可控开漏输出(仅PC12-7816数据口) (798)41.3IO端口功能定义 (798)41.3.1GPIO输入 (798)41.3.2GPIO输出 (799)41.3.3数字外设功能 (799)41.3.4模拟功能 (801)41.3.5使用外部晶体引脚 (802)41.4VBAT供电引脚 (802)41.5SWD引脚 (803)41.6WKUP X引脚 (803)41.7外部引脚中断(EXTI) (804)41.7.1功能说明 (804)41.7.2应用指南 (805)41.8快速GPIO输出 (806)41.9寄存器 (807)41.9.1GPIO输入使能寄存器(GPIOx_INEN) (810)41.9.2GPIO上拉使能寄存器(GPIOx_PUEN) (810)41.9.3GPIO开漏使能寄存器(GPIOx_ODEN) (811)41.9.4GPIO功能选择寄存器(GPIOx_FCR) (811)41.9.5GPIO输出数据寄存器(GPIOx_DO) (813)41.9.6GPIO输出数据置位寄存器(GPIOx_DSET) (814)41.9.7GPIO输出数据复位寄存器(GPIOx_DRST) (814)41.9.8GPIO输入数据寄存器(GPIOx_DIN) (815)41.9.9GPIO额外数字功能选择寄存器(GPIOx_DFS) (816)41.9.10GPIO模拟开关使能寄存器(GPIOx_ANEN) (816)41.9.11GPIO输入低阈值配置寄存器(GPIOx_VILR) (817)41.9.12EXTI输入选择寄存器0(GPIO_EXTISEL0) (817)41.9.13EXTI输入选择寄存器1(GPIO_EXTISEL1) (819)41.9.14EXTI边沿选择和使能寄存器0(GPIO_EXTIEDS0) (820)41.9.1EXTI边沿选择和使能寄存器1(GPIO_EXTIEDS1) (821)41.9.2EXTI数字滤波控制寄存器(GPIO_EXTIDF) (822)41.9.3EXTI中断标志(GPIO_EXTIISR) (822)41.9.4EXTI输入信号寄存器(GPIO_EXTIDI) (823)41.9.5FOUT配置寄存器(GPIO_FOUTSEL) (823)41.9.6WKUP控制寄存器(GPIO_PINWKEN) (824)42专用编程接口 (826)42.1概述 (826)42.2编程器使用 (826)43调试支持 (827)43.1概述 (827)43.2D EBUG引脚 (828)43.2.1SWD引脚 (828)43.2.2上拉电阻 (828)43.3SWD接口协议 (829)43.3.1协议简介 (829)43.3.2传输序列 (829)43.3.3SW-DP ID code (830)43.3.4主机读操作 (830)43.3.5主机写操作 (831)43.4SWD-DP寄存器 (832)43.4.1寄存器列表 (832)43.5C ORE DEBUG寄存器 (832)43.6低功耗调试支持 (832)43.7D EBUG相关的配置项 (833)43.8寄存器 (833)43.8.1系统模式配置寄存器 (833)43.8.2MCU DEBUG配置寄存器 (834)43.8.3HardFault查询寄存器 (835)44器件签名信息 (837)44.1存储器容量查询 (837)44.2器件UID (838)版本列表 (839)上海复旦微电子集团股份有限公司销售及服务网点 (840)。

艾默生 PACSystems RX3i CPE400和CPL410 边缘控制器 数据表

PACSystems™ RX3i CPE400和CPL410采用PACEdge™软件的边缘控制器PACSystems00813-0106-0102产品数据表2021年12月设计用来满足实时控制领域的需求艾默生PACSystems RX3i CPE400和CPL410边缘控制器是适合广泛应用的,具有非常灵活和高性能特点的理想控制系统,应用的行业包括水和污水处理、地铁、工业蒸汽、汽车、化工、石油天然气、离散制造和需要模块化的机器设计等场合。

这些多样化的应用需要紧凑型的控制器,用来提供可靠运行特定应用程序控制所需的高性能和灵活性。

RX3i CPE400和CPL410通过内嵌的PAC 边缘计算(PACEdge )软件增强了实时确定性控制,通过对市场、大型联合体和企业数据或用户的资产/过程知识的分析,提供了近乎于实时的建议,进而优化业务产出。

RX3i 边缘控制器提供了一个可靠的,能够进行安全通信和分析的开放平台,用于基于云或基于边缘计算的应用。

现在可以对控制过程进行加强来动态地影响业务产出,产生新形式的收入并且提高盈利能力。

可靠、高速的性能RX3i CPE400和CPL410运行在一个实时操作系统上,使得它们能够提供可靠和安全的工业应用。

它们提供了卓越的高速性能和安全数据处理能力可以用于多种行业的控制系统。

一个大容量的工作内存可以容纳大型程序和大量的数据存储。

具有四核的高速微处理器,执行程序比以往任何时候更快。

它们支持工业标准的PROFINET®网络,当I/O 更新速率是1毫秒时可连接16个设备。

以太网的接口速率可高达1Gpbs ,RX3i CPE400和CPL410专门为快速、可靠的数据交换而设计。

采用PACEdge 软件实现工业互联网连接艾默生的边缘控制器使用实时的虚拟机监视器(Hypervisor )技术在运行实时确定性控制应用的同时并发运行PACEdge 软件,这两种应用以安全和协作的方式同时运行而不会彼此影响。

LMC6442中文资料

LMC6442Dual Micropower Rail-to-Rail Output Single Supply Operational AmplifierGeneral DescriptionThe LMC6442is ideal for battery powered systems,where very low supply current (less than one microamp per ampli-fier)and Rail-to-Rail output swing is required.It is character-ized for 2.2V to 10V operation,and at 2.2V supply,the LMC6442is ideal for single (Li-Ion)or two cell (NiCad or al-kaline)battery systems.The LMC6442is designed for battery powered systems that require long service life through low supply current,such as smoke and gas detectors,and pager or personal communi-cations systems.Operation from single supply is enhanced by the wide com-mon mode input voltage range which includes the ground (or negative supply)for ground sensing applications.Very low (5fA,typical)input bias current and near constant supply cur-rent over supply voltage enhance the LMC6442’s perfor-mance near the end-of-life battery voltage.Designed for closed loop gains of greater than plus two (or minus one),the amplifier has typically 9.5KHz GBWP (Gain Bandwidth Product).Unity gain can be used with a simple compensation circuit,which also allows capacitive loads of up to 300pF to be driven,as described in the Application Notes section.For compact assembly the LMC6442is available in the MSOP 8pin package,about one half the size required by the SOIC 8pin package.8pin DIP and 8pin SOIC are also available.Key Specifications Features(Typical,V S =2.2V)n Output Swing to within 30mV of supply rail n High voltage gain 103dB n Gain Bandwidth Product 9.5KHz n Guaranteed for: 2.2V,5V,10V n Low Supply Current 0.95µA/Amplifier n Input Voltage Range −0.3V to V +-0.9V n Power consumption2.1µW/Amplifiern Stable for A V ≥+2or A V ≤−1Applicationsn Portable instrumentsn Smoke/gas/CO/fire detectors n Pagers/cell phones n Instrumentation n Thermostatsn Occupancy sensors n CamerasnActive badgesConnection DiagramOrdering InformationPackage Temperature RangeNSC Drawing Supplied AS Package MarkingIndustrial −40˚C to +85˚C Military −55˚C to +125˚C8-pin SO-8LMC6442AIM,LMC6442IM -M08A Rails LMC6442AIM LMC6442IMLMC6442AIMX,LMC6442IMX-M08A2.5KTape and ReelDS100064-40Top ViewSeptember 1997LMC6442Dual Micropower Rail-to-Rail Output Single Supply Operational Amplifier©1999National Semiconductor Corporation Ordering Information(Continued)Package Temperature RangeNSC Drawing Supplied AS Package MarkingIndustrial −40˚C to +85˚C Military −55˚C to +125˚CMSOPLMC6442AIMM,LMC6442IMM -MUA08A RailsA08ALMC6442AIMMX,LMC6442IMMX-MUA08A 3K Tapeand Reel 8-pin DIP LMC6442AIN,LMC6442IN-N08E Rails LMC6442AIN,LMC6442IN 8-pin CDIP -5962-9761301QPA J08A Rails LMC6442AMJ-QML 5962-976130IQPA 10-pin SO-5962-9761301QXAWG10ATraysLMC6442AMWG-Q 9761301QXA 2Absolute Maximum Ratings (Note 1)If Military/Aerospace specified devices are required,please contact the National Semiconductor Sales Office/Distributors for availability and specifications.ESD Tolerance (Note 2)2kVDifferential Input Voltage ±Supply VoltagesVoltage at Input/Output Pin (V +)+0.3V,(V −)−0.3VSupply Voltage (V +−V −):16VCurrent at Input Pin (Note 10)±5mA Current at Output Pin(Notes 3,7)±30mALead Temp.(soldering 10sec)260˚CStorage Temp.Range:−65˚C to +150˚CJunction Temp.(Note 4)150˚COperating Ratings (Note 1)Supply Voltage 1.8V ≤V S ≤11V Junction Temperature−40˚C <T J <+85˚CRange:LMC6442AI,LMC6442I Thermal Resistance (θJA )M Package,8-pin Surface Mount193˚C/W MSOP Package235˚C/W N Package,8-pin Molded DIP115˚C/W2.2V Electrical CharacteristicsUnless otherwise specified,all limits guaranteed for T J =25˚C,V +=2.2V,V −=0V,V CM =V O =V +/2,and R L =1M Ωto V +/2.Boldface limits apply at the temperature extremes.SymbolParameterConditionsTyp (Note 5)LMC6442AI Limit (Note 6)LMC6442ILimit (Note 6)UnitsDC Electrical Characteristics V OS Input Offset Voltage −0.75±3±4±7±8mV max TCV OS Temp.coefficient of inputoffset voltage 0.4µV/˚C I B Input Bias Current (Note 14)0.00544pA max I OS Input Offset Current (Note 14)0.002522pA max CMRR Common Mode Rejection Ratio−0.1V ≤V CM ≤0.5V9267676767dB min C IN Common Mode Input Capacitance4.7pF PSRR Power Supply Rejection Ratio V S =2.5V to 10V 9575757575dB min V CMInput Common-Mode Voltage RangeCMRR ≥50dB1.31.050.95 1.050.95V min −0.3−0.20−0.20V max A V Large Signal Voltage Gain Sourcing (Note 11)100dB min Sinking(Note 11)94V O =0.22V to 2V1038080V O Output Swing V ID =100mV (Note 13) 2.18 2.152.15 2.152.15V min V ID =−100mV (Note 13)2260606060mV max I SC Output Short Circuit CurrentSourcing,V ID =100mV (Notes 12,13)5018171817µA minSinking,V ID =−100mV (Notes 12,13)5020192019I S Supply Current (2amplifiers)R L =open1.902.43.02.63.2µA maxV +=1.8V,R L =open2.10AC Electrical Characteristics SRSlew Rate (Note 8)2.2V/ms32.2V Electrical Characteristics(Continued)Unless otherwise specified,all limits guaranteed for T J =25˚C,V +=2.2V,V −=0V,V CM =V O =V +/2,and R L =1M Ωto V +/2.Boldface limits apply at the temperature extremes.SymbolParameterConditionsTyp (Note 5)LMC6442AI Limit (Note 6)LMC6442ILimit (Note 6)UnitsAC Electrical Characteristics GBWP Gain-Bandwidth Product 9.5KHz φmPhase Margin(Note 15)63Degree5V Electrical CharacteristicsUnless otherwise specified,all limits guaranteed for T J =25˚C,V +=5V,V −=0V,V CM =V O =V +/2,and R L =1M Ωto V +/2.Boldface limits apply at the temperature extremes.SymbolParameterConditionsTyp (Note 5)LMC6442AILimit (Note 6)LMC6442I Limit (Note 6)UnitsDC Electrical Characteristics V OS Input Offset Voltage −0.75±3±4±7±8mV max TCV OS Temp.coefficient of input offset voltage 0.4µV/˚C I B Input Bias Current (Note 14)0.00544pA max I OS Input Offset Current (Note 14)0.002522pA max CMRR Common Mode Rejection Ratio−0.1V ≤V CM ≤3.5V10270707070dB min C IN Common Mode Input Capacitance4.1pF PSRR Power Supply Rejection Ratio V S =2.5V to 10V 9575757575dB min V CMInput Common-Mode Voltage RangeCMRR ≥50dB4.13.853.75 3.853.75V min −0.4−0.20−0.20V max A V Large Signal Voltage Gain Sourcing (Note 11)100dB min Sinking (Note 11)94V O =0.5V to 4.5V1038080V O Output SwingV ID =100mV (Note 13)4.99 4.954.95 4.954.95V min V ID =−100mV (Note13)2050505050mV max I SC Output Short Circuit CurrentSourcing,V ID =100mV (Notes 12,13)500300200300200µA min Sinking,V ID =−100mV (Notes 12,13)350200150200150I S Supply Current (2amplifiers)R L =open1.902.43.0 2.63.2µA max AC Electrical Characteristics SR Slew Rate (Note 8)4.1 2.52.5V/ms GBWP Gain-Bandwidth Product 10KHz φm Phase Margin(Note 15)64Degree THDTotal Harmonic DistortionA V =+2,f =100Hz,R L =10M Ω,V OUT =1Vpp0.08% 410V Electrical CharacteristicsUnless otherwise specified,all limits guaranteed for T J =25˚C,V +=10V,V −=0V,V CM =V O =V +/2,and R L =1M Ωto V +/2.Boldface limits apply at the temperature extremes.SymbolParameterConditionsTyp (Note 5)LMC6442AILimit (Note 6)LMC6442I Limit (Note 6)UnitsDC Electrical Characteristics V OS Input Offset Voltage −1.5±3±4±7±8mV max TCV OS Temp.coefficient of input offset voltage 0.4µV/˚C I B Input Bias Current (Note 14)0.00544pA max I OS Input Offset Current (Note 14)0.002522pA max CMRR Common Mode Rejection Ratio−0.1V ≤V CM ≤8.5V10570707070dB min C IN Common Mode Input Capacitance3.5pF PSRR Power Supply Rejection Ratio V S =2.5V to 10V 9575757575dB min V CMInput Common-Mode Voltage RangeCMRR ≥50dB9.18.858.758.858.75V min −0.4−0.20−0.20V max A V Large Signal Voltage Gain Sourcing (Note 11)120dB min Sinking (Note 11)100V O =0.5V to 9.5V1048080V O Output SwingV ID =100mV (Note 13)9.999.979.979.979.97V min V ID =−100mV(Note 13)2250505050mV max I SC Output Short Circuit CurrentSourcing,V ID =100mV (Notes 12,13)21001200100012001000µA min Sinking,V ID =−100mV (Notes 12,13)900600500600500I S Supply Current (2amplifiers)R L =open1.902.43.0 2.63.2µA max AC Electrical Characteristics SR Slew Rate(Note 8)4.1 2.52.5V/ms GBWP Gain-Bandwidth Product 10.5KHz φm Phase Margin(Note 15)68Degree e n Input-Referred Voltage Noise R L =open f =10Hz 170nV/√Hz i nInput-Referred Current Noise R L =open f =10Hz 0.0002pA/√Hz Crosstalk Rejection(Note 9)85dB5Electrical Characteristics (continued)Note 1:Absolute Maximum Ratings indicate limits beyond which damage to the device may occur.Operating Ratings indicate conditions for which the device is intended to be functional,but specific performance is not guaranteed.For guaranteed specifications and the test conditions,see the Electrical Characteristics.Note 2:Human body model,1.5k Ωin series with 100pF.Note 3:Applies to both single-supply and split-supply operation.Continuous short circuit operation at elevated ambient temperature can result in exceeding the maximum allowed junction temperature of 150˚C.Output currents in excess of ±30mA over long term may adversely affect reliability.Note 4:The maximum power dissipation is a function of T J(max),θJA ,and T A .The maximum allowable power dissipation at any ambient temperature is P D =(T J -(max)-T A )/θJA .All numbers apply for packages soldered directly into a PC board.Note 5:Typical Values represent the most likely parametric norm.Note 6:All limits are guaranteed by testing or statistical analysis unless otherwise specified.Note 7:Do not short circuit output to V +,when V +is greater than 13V or reliability will be adversely affected.Note 8:Slew rate is the slower of the rising and falling slew rates.Note 9:Input referred,V +=10V and R L =10M Ωconnected to 5V.Each amp excited in turn with 1KHz to produce about 10Vpp output.Note 10:Limiting input pin current is only necessary for input voltages that exceed absolute maximum input voltage ratings.Note 11:R L connected to V +/2.For Sourcing Test,V O >V +/2.For Sinking tests,V O <V +/2.Note 12:Output shorted to ground for sourcing,and shorted to V+for sinking short circuit current test.Note 13:V ID is differential input voltage referenced to inverting input.Note 14:Limits guaranteed by design.Note 15:See the Typical Performance Characteristics and Application Notes sections for more details.Typical Performance CharacteristicsV S =5V,Single Supply,T A =25˚C unless otherwise specifiedTotal Supply Current vs Supply VoltageDS100064-8Total Supply Current vs Supply Voltage(Negative Input Overdrive)DS100064-9Total Supply Current vs Supply Voltage(Positive Input Overdrive)DS100064-10Input Bias Current vs TemperatureDS100064-41Offset Voltage vsCommon Mode Voltage (V S =2.2V)DS100064-6Offset Voltage vsCommon Mode Voltage (V S =5V)DS100064-7 6Typical Performance Characteristics VS =5V,Single Supply,TA=25˚C unless otherwisespecified(Continued)Offset Voltage vsCommon Mode Voltage(V S=10V)DS100064-42Swing Towards V−vsSupply VoltageDS100064-3Swing Towards V+vsSupply VoltageDS100064-2Swing From Rail(s)vs TemperatureDS100064-1Output Source Currentvs Output VoltageDS100064-49Output Sink Currentvs Output VoltageDS100064-48Maximum Output Voltagevs Load ResistanceDS100064-24Large Signal VoltageGain vs Supply VoltageDS100064-52Open LoopGain/Phase vsFrequencyDS100064-19 7Typical Performance CharacteristicsV S =5V,Single Supply,T A =25˚C unless otherwisespecified (Continued)Open Loop Gain/Phase vsFrequency For Various C L (Z L =1M ΩII C L )DS100064-26Open Loop Gain/Phase vsFrequency For Various C L (Z L =100K ΩII C L )DS100064-25Gain Bandwidth Product vs Supply VoltageDS100064-21Phase Margin (Worst Case)vs Supply VoltageDS100064-23CMRR vs Frequency DS100064-34PSRR vs FrequencyDS100064-15Positive Slew Rate vs Supply Voltage DS100064-12Negative Slew Rate vs Supply Voltage DS100064-11Cross-Talk Rejection vs FrequencyDS100064-18 8Typical Performance Characteristics VS =5V,Single Supply,TA=25˚C unless otherwisespecified(Continued)Input Voltage Noisevs FrequencyDS100064-16Output Impedancevs FrequencyDS100064-33THD+N vs FrequencyDS100064-28THD+N vs AmplitudeDS100064-27Maximum OutputSwing vs FrequencyDS100064-53Small Signal StepResponse(A V=+2)(C L=12pF,100pF)DS100064-29Large Signal StepResponse(A V=+2)(C L=100pF)DS100064-30Small Signal StepResponse(A V=−1)(C L=1MΩII100pF,200pF)DS100064-51Small Signal StepResponse(A V=+1)For Various C LDS100064-31 9Typical Performance Characteristics VS=5V,Single Supply,TA=25˚C unless otherwise specified(Continued)Application NotesUsing LMC6442in unity gain applications:LMC6442isoptimized for maximum bandwidth and minimal externalcomponents when operating at a minimum closed loop gainof+2(or−1).However,it is also possible to operate the de-vice in a unity gain configuration by adding external compen-sation as shown in Figure1:Using this compensation technique it is possible to drive ca-pacitive loads of up to300pF without causing oscillations(see the Typical Performance Characteristics for step re-sponse plots).This compensation can also be used withother gain settings in order to improve stability,especiallywhen driving capacitive loads(for optimum performance,R cand C c may need to be adjusted).Using“T”Network:Compromises need to be made whenever high gain invert-ing stages need to achieve a high input impedance as well.This is especially important in low current applications whichtend to deal with high resistance ing a traditionalinverting amplifier,gain is inversely proportional to the resis-tor value tied between the inverting terminal and input whilethe input impedance is equal to this value.For example,inorder to build an inverting amplifier with an input impedanceof10MΩand a gain of100,one needs to come up with afeedback resistor of1000MΩ-an expensive task.An alternate solution is to use a“T”Network in the feedbackpath,as shown in Fig.2.Closed loop gain,A V is given by:It must be noted,however,that using this scheme,the real-izable bandwidth would be less than the theoretical maxi-mum.With feedback factor,β,defined as:BW(−3dB)≈GBWP•βIn this case,assuming a GBWP of about10KHz,the ex-pected BW would be around50Hz(vs100Hz with the con-ventional inverting amplifier).Looking at the problem from a different view,with R F definedby A V•Rin,one could select a value for R in the“T”Networkand then determine R1based on this selection: Large Signal StepResponse(A V=+1)(C L=200pF)DS100064-32DS100064-35FIGURE1.A V=+1Operation by adding C c and R cDS100064-36FIGURE2.“T”Network Used to Replace High ValueResistorDS100064-22FIGURE3.“T”Network Values for Various Values of R 10Application Notes(Continued)For convenience,Fig.3shows R1vs R F for different values of R.Design Considerations for Capacitive Loads:As with many other opamps,the LMC6442is more stable at higher closed loop gains when driving a capacitive load.Figure 4shows minimum closed loop gain versus load capacitance,to achieve less than 10%overshoot in the output small sig-nal response.In addition,the LMC6442is more stable when it provides more output current to the load and when its out-put voltage does not swing close to V −.The LMC6442is more tolerant to capacitive loads when the equivalent output load resistance is lowered or when output voltage is 1V or greater from the V −supply.The capacitive load drive capability is also improved by adding an isolating resistor in series with the load and the output of the device.Figure 5shows the value of this resistor for various capaci-tive loads (A V =−1),while limiting the output to less than 10%overshoot.Referring to the Typical Performance Characteristics plot of Phase Margin (Worst Case)vs Supply Voltage,note that Phase Margin increases as the equivalent output load resis-tance is lowered.This plot shows the expected Phase Mar-gin when the device output is very close to V −,which is the least stable condition of paring this Phase Margin value to the one read off the Open Loop Gain/Phase vs Frequency plot,one can predict the improvement in Phase Margin if the output does not swing close to V −.This dependence of Phase Margin on output voltage is minimized as long as the output load,R L ,is about 1M Ωor less.Output Phase Reversal:The LMC6442is immune against this behavior even when the input voltages exceed the com-mon mode voltage range.Output Time Delay:Due to the ultra low power consump-tion of the device,there could be as long as 2.5ms of time delay from when power is applied to when the device output reaches its final value.DS100064-47FIGURE 4.Minimum Operating Gain vs Capactive LoadDS100064-43FIGURE 5.Isolating Resistor Value vs Capactive Load11Application CircuitsMicropower Single Supply Voltage to Frequency ConverterDS100064-45 V+=5V:I S<10µA,f/V C=4.3(Hz/V)DS100064-4612Application Circuits(Continued)Gain Stage with Current BoostingDS100064-54Offset Nulling SchemesDS100064-4413Physical Dimensions inches(millimeters)unless otherwise noted8-Lead(0.150″Wide)Molded Small Outline Package,JEDECOrder Number LMC6442AIM or LMC6442IM or LMC6442AIMX or LMC6442IMXNS Package Number M08A8-Lead(0.300″Wide)Molded Dual-In-Line PackageOrder Number LMC6442AIN or LMC6442IN or LMC6442AINX or LMC6442INXNS Package Number N08E14Physical Dimensionsinches (millimeters)unless otherwise noted (Continued)LIFE SUPPORT POLICYNATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION.As used herein:1.Life support devices or systems are devices or systems which,(a)are intended for surgical implant into the body,or (b)support or sustain life,and whose failure to perform when properly used in accordance with instructions for use provided in the labeling,can be reasonably expected to result in a significant injury to the user.2.A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system,or to affect its safety or effectiveness.National Semiconductor Corporation AmericasTel:1-800-272-9959Fax:1-800-737-7018Email:support@National Semiconductor EuropeFax:+49(0)180-5308586Email:europe.support@Deutsch Tel:+49(0)180-5308585English Tel:+49(0)180-5327832Français Tel:+49(0)180-5329358Italiano Tel:+49(0)180-5341680National Semiconductor Asia Pacific Customer Response Group Tel:65-2544466Fax:65-2504466Email:sea.support@National Semiconductor Japan Ltd.Tel:81-3-5639-7560Fax:81-3-5639-75078-Lead (0.118″Wide)Molded Mini Small Outline PackageOrder Number LMC6442AIMM or LMC6442IMM or LMC6442AIMMX or LMC6442IMMXNS Package Number MUA08ALMC6442Dual Micropower Rail-to-Rail Output Single Supply Operational AmplifierNational does not assume any responsibility for use of any circuitry described,no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.。

2P4M中文资料(nec)中文数据手册「EasyDatasheet - 矽搜」

DRM,

Tj = 125°C

−

Tj = 25°C

−

Tj = 125°C

−

dV D/dt Tj = 125°C, V DM = 2/3 V DRM

10

−

VTM ITM = 4 A

−

IGT VDM = 6 V, R L = 100 Ω,

−

栅极触发电压

Note

VGT VDM = 6 V, R L = 100 Ω,

1985, 2006

The revised points can be easily searched by copying an "现场:修订部分可以通过在 PDF文件中复制一个 “R”,并在 “查找内容 ”指定它可以很容易地搜索 .

芯片中文手册,看全文,戳

2P4M,2P6M

最大额定值

Note

IH VDM = 24 V, I TM = 4 A

−

1

3

mA 参照图9

电路改判关断时间

tq

Tj = 125°C, I TM = 500毫安,

−

30

−

μs

−

diR / DT = 15 A /μs, V R ≥ 25 V,

VDM = 2/3 V DRM ,DV D / dt的= 10V μ/ s

特性

符号

非重复性峰值反向电压 非重复性峰值断态电压 重复峰值反向电压 重复峰值断态电压

Note Note Note Note

VRSM VDSM VRRM VDRM

通态电流

IT (AV)

有效的通态电流 浪涌不重复通态电流 熔断电流

IT (RMS)

IT S M

∫

i2

基于HC-SR04模块的时差法声速测量

基于HC-SR04模块的时差法声速测量张克声;隆昌喜【摘要】提出了一种基于超声波测距模块HC-SR04的时差法测量声速的软硬件实现方法,并介绍了相应的硬件模块信号处理流程和测量程序运行流程.本方法可通过精确测量已知距离的声传播时间计算声速.利用所设计的实验装置,实际测量了空气中不同温度下多组声传播速度,测量结果与理论值的最大相对误差仅为0.6%,从而证明了本方法的可行性和合理性.与传统的共振干涉法、相位比较法等声速测量方法相比,本文方法具有实时性高、成本低、结构简单和精度高等优点.%This paper proposes a time-difference method based on HC-SR04,an ultrasonic ranging module,to measure acoustic velocity,and introduces the signal process hardware module and the measuring program running process.The proposed method can calculate the speed of sound by accurately measuring the acoustic propagation time at a known distance.In the experiment,the propagation speeds of ultrasonic waves at different temperatures were obtained through the devices designed for this study.The maximum relative error between the measured results and the theoretical value was only 0.6%,which proved the feasibility and rationality of the proposed pared with the traditional measuring methods such as resonance interferometry and phase-comparison method,the proposed one is of high real-time performance,low cost,simple structure,and high precision.【期刊名称】《机械与电子》【年(卷),期】2018(036)002【总页数】4页(P54-57)【关键词】HC-SR04模块;声速测量;时差法;超声波测距模块【作者】张克声;隆昌喜【作者单位】贵州理工学院电气与信息工程学院,贵州贵阳550003;贵州理工学院电气与信息工程学院,贵州贵阳550003【正文语种】中文【中图分类】O422.10 引言超声波是一种在弹性的媒质中传播的纵波,其频率范围则在20 kHz和大约1 GHz之间。

IC Realtime MAX系列单通道DVR产品说明书

MAX-504D4C h a n n e l H.264E D1 1.5U S t a n d a l o n e D V RAffordable, small form factor Analog recorder for residential and small office use. The MAX series of DVRs is a compact digital video recorder available in 4, 8, and 16 channel offerings. Due to its small size, the MAX series DVR is perfect for installation on a desktop, or a rack mounted shelf.The latest generation of MAX series recorders will record and stream 960H resolution at 30 FPS (frames-per-second) on every input, giving it high-end features while maintaining a low price tag. This DVR is well suited for installations such as: retail stores, residences, small business/offices. This DVR also integrates with the full suite of supported IC Realtime A/V control system drivers.Like all IC Realtime series recorders, this device utilizes H.264E (Enhanced H.264) compression technology, enabling crisp image viewing with the least bandwidth consumption possible. This unit adopts an embedded system design, as well as a Linux Operating System, resulting in high levels of stability, performance, and most importantly: reliability. In addition, this unit is fully operational from remote locations (Search/Playback/Backup/Configuration) over standard Ethernet networks. Features∙Up to 32 TeraBytes (32,000G) Internal Storage∙Central management software for viewing/managing multiple DVRs∙1000M Network∙SmartPhone Access (iPhone/iPad, Android, Windows phone)∙Support two way audio∙Email Notification of Events∙USB 2.0 Mouse Interface for super easy operation∙HDMI, VGA, BNC Video Output∙Matrix video output for Spot monitor applications∙Loop back video output for every channel∙Smart Search∙4-channel simultaneous real-time playback∙Realtime Synchronized Audio/Video Recording on All Channels ∙All channel 960H(960x576/960x480)realtime recording∙Pentaplex Operation∙Embedded High-Speed DualCore Microprocessor & Linux OS ∙H.264E Compression with dual stream encoding∙ 1.5U Rack Mount Case SpecificationMAX-504D SpecificationsAccessoriesIntegration InformationIC Realtime LLC3050 N Andrews Avenue ExtensionPompano Beach, FL 33064(866) 997-9009Designs and specifications subject to change w ithout notice. Copyright © 2015 IC Realtime, LLC. All rights reserved.。

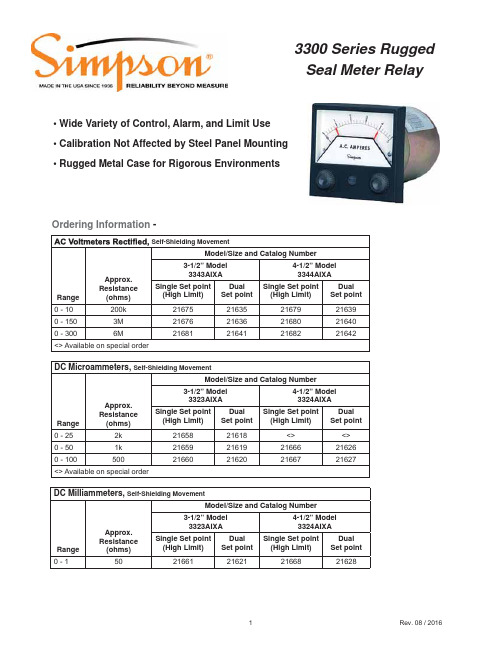

3300系列耐用封闭型磁电流表关闭阀门闸控制、警报和限位用途说明书