IC datasheet pdf-TLV5614Y,pdf(TLV5614IYE_ 2.7 V To 5.5V 12-Bit Quad DAC in Wafer Chip Scale Package)

74HC165_DataSheet

1Information furnished by Linear Technology Corporation is believed to be accurate and reliable.However, no responsibility is assumed for its use. Linear Technology Corporation makes no represen-tation that the interconnection of its circuits as described herein will not infringe on existing patent rights.2LTC1569-6A U G WA W U W A R BSOLUTEXI TI SW U UPACKAGE/ORDER I FOR ATIO(Note 1)Total Supply Voltage................................................11V Power Dissipation..............................................500mW Operating Temperature................................0°C to 70°C Storage Temperature............................–65°C to 150°C Lead Temperature (Soldering, 10 sec)..................300°CThe q denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T A = 25°C.V S = 3V (V + = 3V, V – = 0V), f CUTOFF = 64kHz, R LOAD = 10k unless otherwise specified.ELECTRICAL C C HARA TERISTICSConsult factory for Industrial and Military grade parts.PARAMETER CONDITIONSMIN TYP MAX UNITS Filter GainV S = 5V, f CLK = 4.096MHz,f IN = 1280Hz = 0.02 • f CUTOFF q –0.050.050.15dB f CUTOFF = 64kHz, V IN = 1.4V P-P ,f IN = 12.8kHz = 0.2 • f CUTOFF q –0.25–0.15–0.05dB R EXT = 10k, Pin 5 Shorted to Pin 4f IN = 32kHz = 0.5 • f CUTOFF q –0.65–0.55–0.4dB f IN = 51.2kHz = 0.8 • f CUTOFF q –1.3–1.0–0.7dB f IN = 64kHz = f CUTOFFq –5.3–3.8–2.4dB f IN = 97.5kHz = 1.5 • f CUTOFF q –60–48dB f IN = 128kHz = 2 • f CUTOFF q –62–50dB f IN = 192kHz = 3 • f CUTOFF q –71–60dB V S = 2.7V, f CLK = 1MHz,f IN = 312Hz = 0.02 • f CUTOFF q –0.120.050.16dB f CUTOFF = 15.625kHz, V IN = 1V P-P ,f IN = 3125kHz = 0.2 • f CUTOFF q –0.25–0.15–0.05dB Pin 6 Shorted to Pin 4, External Clockf IN = 7812kHz = 0.5 • f CUTOFF q –0.65–0.55–0.4dB f IN = 12.5kHz = 0.8 • f CUTOFF q –1.1–0.9–0.7dB f IN = 15.625kHz = f CUTOFF q –3.6–3.4–3.2dB f IN = 23.44kHz = 1.5 • f CUTOFF q –54–50dB f IN = 31.25kHz = 2 • f CUTOFF q –60–55dB f IN = 46.88kHz = 3 • f CUTOFF q –66–60dB Filter PhaseV S = 2.7V, f CLK = 4MHz,f IN = 1250Hz = 0.02 • f CUTOFF –11Deg f CUTOFF = 62.5kHz, Pin 6 Shorted to f IN = 12.5kHz = 0.2 • f CUTOFF q –114–111–108Deg Pin 4, External Clockf IN = 31.25kHz = 0.5 • f CUTOFF q 798285Deg f IN = 50kHz = 0.8 • f CUTOFF q –83–79–75Deg f IN = 62.5kHz = f CUTOFFq156162168Deg f IN = 93.75kHz = 1.5 • f CUTOFF–91DegFilter Cutoff Accuracy R EXT = 10.24k from Pin 6 to Pin 7,62.5kHz ±1%when Self-Clocked V S = 3V, Pin 5 Shorted to Pin 4Filter Output DC Swing V S = 3V, Pin 3 = 1.11V2.1V P-P (Note 6)q1.9V P-P V S = 5V, Pin 3 = 2V3.6V P-P q3.2V P-P V S = ±5V, Pin 5 Shorted to Pin 7, R LOAD = 20k8.5V P-P3LTC1569-6The q denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T A = 25°C.V S = 3V (V + = 3V, V – = 0V), f CLK = 4.096MHz, f CUTOFF = 64kHz, R LOAD = 10k unless otherwise specified.ELECTRICAL C C HARA TERISTICSPARAMETER CONDITIONSMIN TYP MAX UNITS Output DC Offset R EXT = 10k, Pin 5 Shorted to Pin 7V S = 3V ±2±5mV (Note 2)V S = 5V ±6±12mV V S = ±5V ±15mV Output DC Offset DriftR EXT = 10k, Pin 5 Shorted to Pin 7V S = 3V 25µV/°C V S = 5V 25µV/°C V S = ±5V 75µV/°CClock Pin Logic Thresholds V S = 3V Min Logical “1” 2.7V when Clocked ExternallyMax Logical “0”0.5V V S = 5V Min Logical “1” 4.0V Max Logical “0”0.5V V S = ±5VMin Logical “1” 4.0V Max Logical “0”0.5VPower Supply Current f CLK = 256kHz (40k from Pin 6 to Pin 7,V S = 3V34mA (Note 3)Pin 5 Open, ÷ 4), f CUTOFF = 4kHzq5mA V S = 5V3.55mA q6mA V S = 10V4.57mA q8mA f CLK = 4.096MHz (10k from Pin 6 to Pin 7,V S = 3V 8mA Pin 5 Shorted to Pin 4, ÷ 1), f CUTOFF = 64kHzq11mA V S = 5V9mA q13mA V S = 10V12mA q17mA Clock Feedthrough Pin 5 Open0.1mV RMS Wideband Noise Noise BW = DC to 2 • f CUTOFF 95µV RMSTHDf IN = 3kHz, 1.5V P-P , f CUTOFF = 32kHz80dBClock-to-Cutoff 64Frequency Ratio Max Clock Frequency V S = 3V 5MHz (Note 4)V S = 5V 5MHz V S = ±5V7MHz Min Clock Frequency V S = 3V, 5V, T A < 85°C 1.5kHz (Note 5)V S = ±5V3kHz Input Frequency RangeAliased Components <–65dB 0.9 • f CLKHzNote 1: Absolute maximum ratings are those values beyond which the life of a device may be impaired.Note 2: DC offset is measured with respect to Pin 3.Note 3: If the internal oscillator is used as the clock source and the divide-by-4 or divide-by-16 mode is enabled, the supply current is reduced as much as 40% relative to the divide-by-1 mode.Note 4: The maximum clock frequency is arbitrarily defined as thefrequency at which the filter AC response exhibits >1dB of gain peaking.Note 5: The minimum clock frequency is arbitrarily defined as the frequecy at which the filter DC offset changes by more than 5mV.Note 6: For more details refer to the Input and Output Voltage Range paragraph in the Applications Information section.4LTC1569-6TYPICAL PERFOR A CE CHARACTERISTICSU WTHD vs Input VoltageTHD vs Input FrequencyINPUT VOLTAGE (V P-P )0.51.0 1.52.0 2.53.0 3.54.0T H D (d B )1569-6 G02–50–55–60–65–70–75–80–85–90INPUT FREQUENCY (kHz)51015202530TH D (d B )1569-6 G01–60–65–70–75–80–85–90PI FU CTIO SU U UIN +/IN – (Pins 1, 2): Signals can be applied to either or both input pins. The DC gain from IN + (Pin 1) to OUT (Pin␣8) is 1.0, and the DC gain from Pin 2 to Pin 8 is –1. The input range, input resistance and output range are de-scribed in the Applications Information section. Input voltages which exceed the power supply voltages should be avoided. Transients will not cause latchup if the current into/out of the input pins is limited to 20mA.GND (Pin 3): The GND pin is the reference voltage for the filter and should be externally biased to 2V (1.11V) to maximize the dynamic range of the filter in applications using a single 5V (3V) supply. For single supply operation,the GND pin should be bypassed with a quality 1µF ceramic capacitor to V – (Pin 4). The impedance of the circuit biasing the GND pin should be less than 2k Ω as the GND pin generates a small amount of AC and DC current.For dual supply operation, connect Pin␣3 to a high quality DC ground. A ground plane should be used. A poor ground will increase DC offset, clock feedthrough, noise and distortion.V –/V + (Pins 4, 7): For 3V, 5V and ±5V applications a quality 1µF ceramic bypass capacitor is required from V +(Pin 7) to V – (Pin 4) to provide the transient energy for the internal clock drivers. The bypass should be as close aspossible to the IC. In dual supply applications (Pin 3 is grounded), an additional 0.1µF bypass from V + (Pin 7) to GND (Pin 3) and V – (Pin 4) to GND (Pin 3) is recom-mended.The maximum voltage difference between GND (Pin 3) and V + (Pin 7) should not exceed 5.5V.DIV/CLK (Pin 5): DIV/CLK serves two functions. When the internal oscillator is enabled, DIV/CLK can be used to engage an internal divider. The internal divider is set to 1:1when DIV/CLK is shorted to V – (Pin 4). The internal divider is set to 4:1 when DIV/CLK is allowed to float (a 100pF bypass to V – is recommended). The internal divider is set to 16:1 when DIV/CLK is shorted to V + (Pin 7). In the divide-by-4 and divide-by-16 modes the power supply current is reduced by as much as 40%.When the internal oscillator is disabled (R X shorted to V –) DIV/CLK becomes an input pin for applying an external clock signal. For proper filter operation, the clock waveform should be a squarewave with a duty cycle as close as possible to 50% and CMOS voltages levels (see Electrical Characteristics section for voltage levels). DIV/CLK pin voltages which exceed the power supply voltages should be avoided. Transients will not cause latchup if the fault current into/out of the DIV/CLK pin is limited to 40mA.LTC1569-656LTC1569-6Table1. f CUTOFF vs R EXT , V S = 3V, T A = 25°C, Divide-by-1 ModeR EXT Typical f CUTOFFTypical Variation of f CUTOFF3844Ω*N/A ±3.0%5010Ω*N/A ±2.5%10k 64kHz ±1%20.18k 32kHz ±2.0%40.2k16kHz±3.5%*REXT values less than 10k can be used only in the divide-by-16 mode.In the divide-by-4 and divide-by-16 modes, the cutoff frequencies in Table 1 will be lowered by 4 and 16respectively. When the LTC1569-6 is in the divide-by-4APPLICATIO S I FOR ATIO W UU U and divide-by-16 modes the power is automatically re-duced. This results in up to a 40% power savings with a single 5V supply.The power reduction in the divide-by-4 and divide-by-16modes, however, effects the fundamental oscillator fre-quency. Hence, the effective divide ratio will be slightly different from 4:1 or 16:1 depending on V S , T A and R EXT .Typically this error is less than 1% (Figures 4 and 6).The cutoff frequency is easily estimated from the equation in Figure 1. Examples 1 and 2 illustrate how to use the graphs in Figures 2 through 7 to get a more precise estimate of the cutoff frequency.Figure 4. Typical Divide Ratio in the Divide-by-4 Mode, T A = 25°CFigure 5. Filter Cutoff vs Temperature,Divide-by-4 Mode, R EXT = 10kFigure 3. Filter Cutoff vs Temperature,Divide-by-1 Mode, R EXT = 10kFigure 2. Filter Cutoff vs V SUPPLY ,Divide-by-1 Mode, T A = 25°CV SUPPLY (V)2D I V I D E R A T I O1569-6 F044.084.044.003.9646810TEMPERATURE (°C)–50N O R M A L I Z E D F I L T E R C U T O F F1569-6 F051.0101.0081.0061.0041.0021.0000.9980.9960.9940.9920.990–250255075100V SUPPLY (V)2N O R M A L I Z E D F I L T E R C U T O F F1569-6 F021.041.031.021.011.000.990.980.970.9646810TEMPERATURE (°C)–50N O R M A L I Z E D F I L T E R C U T O F F1569-6 F031.0101.0081.0061.0041.0021.0000.9980.9960.9940.9920.990–250255075100LTC1569-678LTC1569-6When driven with a complementary signal whose com-mon mode voltage is GND, the IN + input appears to have 125k to GND and the IN – input appears to have –125k to GND. To make the effective IN – impedance 125k when driven differentially, place a 62.5k resistor from IN – to GND. For other cutoff frequencies use 62.5k • (128kHz/f CUTOFF ), as shown in the Typical Applications section. The typical variation in dynamic input impedance for a given clock frequency is ±10%.Wideband NoiseThe wideband noise of the filter is the RMS value of the device’s output noise spectral density. The wideband noise data is used to determine the operating signal-to-noise at a given distortion level. The wideband noise is nearly independent of the value of the clock frequency and excludes the clock feedthrough. Most of the wideband noise is concentrated in the filter passband and cannot be removed with post filtering (Table 2). Table 3 lists the typical wideband noise for each supply.Table 2. Wideband Noise vs Supply Voltage, Single 3V SupplyBandwidth Total Integrated NoiseDC to f CUTOFF 80µV RMS DC to 2 • f CUTOFF 95µV RMS DC to f CLK110µV RMSTable 3. Wideband Noise vs Supply Voltage, f CUTOFF = 64kHzTotal Integrated Noise Power Supply DC to 2 • f CUTOFF3V 95µV RMS 5V 100µV RMS ±5V105µV RMSClock FeedthroughClock feedthrough is defined as the RMS value of the clock frequency and its harmonics that are present at the filter’s OUT pin (Pin 8). The clock feedthrough is measured with IN + and IN – (Pins 1 and 2) grounded and depends on the PC board layout and the power supply decoupling. Table␣4shows the clock feedthrough (the RMS sum of the first 11harmonics) when the LTC1569-7 is self-clocked with R EXT = 10k, DIV/CLK (Pin 5) open (divide-by-4 mode). The clock feedthrough can be reduced with a simple RC post filter.APPLICATIO S I FOR ATIO W UU U it reaches the typical limits V MAX and V MIN . The above voltage swings are for R LOAD = 10k for V S = 3V and 5V.R LOAD = 20k for V S = ±5V.To maximize the undistorted peak-to-peak signal swing of the filter, the GND (Pin 3) voltage should be set to 2V (1.11V) in single 5V (3V) supply applications.The LTC1569-6 can be driven with a single-ended or differential signal. When driven differentially, the voltage between IN + and IN – (Pin 1 and Pin 2) is filtered with a DC gain of 1. The single-ended output voltage OUT (Pin 8) is referenced to the voltage of the GND (Pin 3). The common mode voltage of IN + and IN – can be any voltage that keeps the input signals within the power supply range.For noninverting single-ended applications, connect IN –to GND or to a quiet DC reference voltage and apply the input signal to IN +. If the input is DC coupled then the DC gain from IN + to OUT will be 1. This is true given IN + and OUT are referenced to the same voltage, i.e., GND, V – or some other DC reference. To achieve the distortion levels shown in the Typical Performance Characteristics the input signal at IN + should be centered around the DC voltage at IN –. The input can also be AC coupled, as shown in the Typical Applications section.For inverting single-ended filtering, connect IN + to GND or to quiet DC reference voltage. Apply the signal to IN –. The DC gain from IN – to OUT is –1, assuming IN – is referenced to IN + and OUT is reference to GND.Refer to the Typical Performance Characteristics section to estimate the THD for a given input level.Dynamic Input ImpedanceThe unique input sampling structure of the LTC1569-6 has a dynamic input impedance which depends on the con-figuration, i.e., differential or single-ended, and the clock frequency. The equivalent circuit in Figure 8 illustrates the input impedance when the cutoff frequency is 64kHz. For other cutoff frequencies replace the 125k value with 125k • (64kHz/f CUTOFF ).When driven with a single-ended signal into IN – with IN +tied to GND, the input impedance is very high (~10M Ω).When driven with a single-ended signal into IN + with IN –tied to GND, the input impedance is a 125k resistor to GND.LTC1569-6910LTC1569-6Single 3V Operation, AC Coupled Input,64kHz Cutoff Frequencyf CUTOFF =n = 1, 4, 16 FOR PIN 5 ATGROUND, OPEN, V +64kHz n = 1()10k R EXT()n = 1, 4, 16 FOR PIN 5 ATGROUND, OPEN, V+n = 4R EXTSingle 3V Supply Operation, DC Coupled,16kHz Cutoff FrequencySingle 5V Operation, 50kHz Cutoff Frequency,DC Coupled Differential Inputs with Balanced Input Impedancef CUTOFF ~n = 1, 4, 16 FOR PIN 5 ATGROUND, OPEN, V +64kHz n = 1()10k 12.8k()µF±5V Supply Operation, DC Coupled Filter with External Clock SourceTYPICAL APPLICATIO SUFREQUENCY (Hz)G A I N (d B )GROUP DELAY 1569-6 TA02a0–10–20–30–40–50–60–70–80–90µs µsµs Single 3V, AC Coupled Input,64kHz Cutoff FrequencyLTC1569-61112LTC1569-6© Linear Technology Corporation1630 McCarthy Blvd., Milpitas, CA 95035-7417(408) 432-1900 q FAX : (408) 434-0507 q PART NUMBER DESCRIPTIONCOMMENTSLTC1064-3Linear Phase, Bessel 8th Order Filter f CLK /f CUTOFF = 75/1 or 150/1, Very Low Noise LTC1064-7Linear Phase, 8th Order Lowpass Filter f CLK /f CUTOFF = 50/1 or 100/1, f CUTOFF(MAX) = 100kHzLTC1068-x Universal, 8th Order Filterf CLK /f CUTOFF = 25/1, 50/1, 100/1 or 200/1, f CUTOFF(MAX) = 200kHz LTC1069-7Linear Phase, 8th Order Lowpass Filter f CLK /f CUTOFF = 25/1, f CUTOFF(MAX) = 200kHz, SO-8LTC1164-7Low Power, Linear Phase Lowpass Filter f CLK /f CUTOFF = 50/1 or 100/1, I S = 2.5mA, V S = 5V LTC1264-7Linear Phase, 8th Order Lowpass Filter f CLK /f CUTOFF = 25/1 or 50/1, f CUTOFF(MAX) = 200kHz LTC1562/LTC1562-2Universal, 8th Order Active RC Filterf CUTOFF(MAX) = 150kHz (LTC1562)f CUTOFF(MAX) = 300kHz (LTC1562-2)RELATED PARTSFf CUTOFF =n = 1, 4, 16 FOR PIN 5 ATGROUND, OPEN, V +n = 4()R EXT()Single 5V Supply Operation, DC Coupled Input,16kHz Cutoff Frequency0.5V /D I VINPUT 32ksps (OR 64kbps)1569-6 TA07TYPICAL APPLICATIO SU。

TLV5618中文数据手册

TLV5618A带掉电功能2.7V-5.5V低功耗双路12位数模转换器特点应用●双路12位电压输出DAC ●数字伺服控制回路●可编程调节转换时间●数字增益和增益调节- 快速模式 3μs ●工业过程控制- 低速模式 10μs ●机器和运动装置控制●兼容TMS320和SPI串行接口●大容量存储设备●典型微分非线性值<0.5LSB●单调的温度●直接替换TLC5618A(C和I后缀)●汽车类可用汽车上的应用高可靠性配置控制/打印支持汽车行业标准描述TLV5618A是一个带灵活的3线串行接口的双12位电压输出型的数模转换器。

串行接口兼容TMS320、SPI、QSPI和Microwire串行接口。

16位串行编程位包括4位控制和12位数据位。

电阻串输出电压是由一个2倍增益的轨到轨输出缓冲器。

缓冲区具有AB类输出级,以提高稳定性和减少建立时间。

可编程DAC的转换时间以允许设计师优化速度与功耗。

CMOS工艺制作,该设备支持2.7V-5.5V单一电源。

它可在标准的商业和工业温度范围内的8引脚SOIC封装。

TLV5618AC可工作温度范围为0℃到70℃,TLV5618AI可工作温度范围为-40℃到85℃,TLV5618AQ可工作温度范围为-40℃到125℃,TLV5618AM可工作温度范围为-55℃到125℃。

请注意,有关可用性,标准保修一个重要的通知,和使用的关键应用德州仪器产品和免责条款出现在此数据手册的末尾。

SPI和QSPI是摩托罗拉公司注册商标。

TLV5618A带掉电功能2.7V-5.5V低功耗双路12位数模转换器功能框图TLV5618A带掉电功能2.7V-5.5V低功耗双路12位数模转换器在空气中的温度范围中操作的最大额定值(除非另有说明)电源电压(VDD到GND) (7V)基准电压输入范围............................................ -0.3V到VDD+0.3V 数字电压输入范围............................................ -0.3V到VDD+0.3V 可工作温度范围,T A:TLV5618AC.......................................0℃到70℃TLV5618AI.................................... -40℃到85℃TLV5618AQ....................................-40℃到125℃TLV5618AM....................................-55℃到125℃储存温度范围,T stg................................................ -65℃到150℃*超出上述列表的“绝对最大值”,可能会对器件造成永久性的损伤。

tlv5614

IMPORTANT NOTICETexas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL APPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER’S RISK.In order to minimize risks associated with the customer’s applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI’s publication of information regarding any third party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.Copyright © 1999, Texas Instruments Incorporated。

FDD5614中文资料

ID = -4.5A VGS = -10V

ID = -2.3 A 0.3

0.2

TA = 125oC

0.1

TA = 25oC

125

150

175

0 2 4 6 8 10 -VGS, GATE TO SOURCE VOLTAGE (V)

TJ, JUNCTION TEMPERATURE ( C)

Figure 3. On-Resistance Variation with Temperature.

PD RDS(ON) 3. Maximum current is calculated as: where PD is maximum power dissipation at TC = 25°C and RDS(on) is at TJ(max) and VGS = 10V. Package current limitation is 21A

a) RθJA = 40°C/W when mounted on a 1in2 pad of 2 oz copper

b) RθJA = 96°C/W when mounted on a minimum pad.

Scale 1 : 1 on letter size paper 2. Pulse Test: Pulse Width < 300µs, Duty Cycle < 2.0%

元器件交易网

FDD5614P

February 2001

FDD5614P

60V P-Channel PowerTrench MOSFET

General Description

This 60V P-Channel MOSFET uses Fairchild’s high voltage PowerTrench process. It has been optimized for power management applications.

TLV5614

在实际的应用中,我们取参考电压REF为2.5V,DAC的供电为5V,由于TLV5614是满幅度输出,所以由式1可得,它的DAC输出电压范围将在0~5V之间。很显然,它的输出电压分辨率为1.22mV。在实际应用中,我们需要输出的精确电压值可能在0~12V之间,或是更高,这时,只需对DAC输出电压进行直流放大,放大倍数就是我们所需最高电压与5V的比值。相比TLV5614的1.22mV分辨率,对12V电压,最终输出电压的分辨率为2.93mV,它也能够满足大多数应用场合对电压变化精度的要求。

关键词:TLV5614;D/A转换器;SPI接口

概述

TLV5614是TI公司生产的四路12位电压输出型数模转换器(DAC),具有灵活的四线串行接口,可以与TMS320、SPI、QSPI和Microwire串行口实现无缝联接。TLV5614的编程控制由16位串行字组成,即2位DAC地址、2个独立的DAC控制位和12位的DAC输入值。器件采用双电源供电:一组为串行接口使用的数字电源,即DVDD和DGND;另一组为输出缓冲器使用的模拟电源,即AVDD和AGND。两组电源相互独立且可为2.7V至5.5V之间的任何值。双电源应用的好处是DAC使用5V电源工作,而DAC的数字部分使用2.7V~5.5V电源,所以可以和多种接口连接工作。

TLV5614数模转换器的原理及其与单片机的接口应用

The Principle and Application of TLV5614 Digital-Analog Converter

■ 武汉理工大学信息工程学院 陈伟 王桂琼

摘 要:本文介绍了TI公司生产的4通道12位D/A转换器TLV5614的功能特点和工作原理,结合开发实例,给出了TLV5614 与MCS-51系列单片机的应用接口电路和软件程序,最后对结果进行了分析并指出了其应用前景。

IC datasheet pdf-TL1431,pdf(Precision Programmable Reference)

(5) Maximum power dissipation is a function of TJ(max), θJC, and TC. The maximum allowable power dissipation at any allowable case temperature is PD = (TJ(max) – TC)/θJC. Operating at the absolute maximum TJ of 150°C can affect reliability.

2

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of the Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

FEATURES

1

•2 0.4% Initial Voltage Tolerance • 0.2-Ω Typical Output Impedance • Fast Turnon…500 ns

D PACKAGE (TOP VIEW)

CATHODE 1 ANODE 2 ANODE 3 NC 4

II(ref)

Reference input current range

θJA

AD转换芯片介绍

l???????ADS7812?低功耗串行12位采样模数转换器

l???????ADS7810?12位800kHz采样CMOS模数转换器

l???????ADS7800?12位3us采样模数转换器

l???????ADS574??兼容微处理器的采样CMOSA/D转换器?

l???????THS1007?10位6MSPS同步采样四路通道ADC;包含并行DSP/uPI/F通道自动扫描?

l???????ADS901??10位20MSPSADC,具有单端/差动输入、外部参考和可调节全范围?

l???????ADS900??10位20MSPSADC,具有单端/差动输入、内部基准和可调节全范围?

l???????ADS822?10位40MSPSADC,具有单端/差动输入、内/外基准和断电、引脚符合ADS823/6/8?

l???????ADS821?10位40MSPSADC,单端/差动输入具有内部基准和9.3位ENOB?

l???????ADS820?10位20MSPSADC,单端/差动输入具有内部基准和9.5位ENOB?

l???????TLC3545?14位200KSPSADC,具有串行输出、自动断电和伪差动输入?

l???????TLC3544?14位、5V、200KSPS、4通道单级性ADC

l???????TLC3541?14位200KSPSADC系列输出、自动断电、单端输入?

l???????THS1403?14位、3MSPSADC单通道、差动输入、DSP/uPIF、可编程增益放大器、内部S&H?

l???????TLC4541?16位200KSPSADC,具有串行输出、自动断电和单端输入

IC datasheet pdf-TLV2254-Q1,pdf(Advanced LinCMOS Rail-to-Rail Very Low Power Operational Amplifier)

TLV225xĆQ1,Advanced LinCMOS VERY LOWĆPOWER OPERATIONALTLV225xĆQ1, TLV225xAĆQ1Advanced LinCMOSVERY LOWĆPOWER OPERATIONAL AMPLIFIERSTLV225xĆQ1,Advanced LinCMOS VERY LOWĆPOWER OPERATIONALTLV225xĆQ1,Advanced LinCMOS VERY LOWĆPOWER OPERATIONALTLV225xĆQ1,Advanced LinCMOS VERY LOWĆPOWER OPERATIONALPACKAGING INFORMATIONOrderable Device Status(1)PackageType PackageDrawingPins PackageQtyEco Plan(2)Lead/Ball Finish MSL Peak Temp(3)TLV2252AQDRG4Q1ACTIVE SOIC D82500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2252AQDRQ1ACTIVE SOIC D82500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2252QDRG4Q1ACTIVE SOIC D82500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2252QDRQ1ACTIVE SOIC D82500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2254AQDRG4Q1ACTIVE SOIC D142500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2254AQDRQ1ACTIVE SOIC D142500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2254QDRG4Q1ACTIVE SOIC D142500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2254QDRQ1ACTIVE SOIC D142500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIM(1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan-The planned eco-friendly classification:Pb-Free(RoHS),Pb-Free(RoHS Exempt),or Green(RoHS&no Sb/Br)-please check /productcontent for the latest availability information and additional product content details.TBD:The Pb-Free/Green conversion plan has not been defined.Pb-Free(RoHS):TI's terms"Lead-Free"or"Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all6substances,including the requirement that lead not exceed0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Pb-Free(RoHS Exempt):This component has a RoHS exemption for either1)lead-based flip-chip solder bumps used between the die and package,or2)lead-based die adhesive used between the die and leadframe.The component is otherwise considered Pb-Free(RoHS compatible)as defined above.Green(RoHS&no Sb/Br):TI defines"Green"to mean Pb-Free(RoHS compatible),and free of Bromine(Br)and Antimony(Sb)based flame retardants(Br or Sb do not exceed0.1%by weight in homogeneous material)(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.OTHER QUALIFIED VERSIONS OF TLV2252-Q1,TLV2252A-Q1,TLV2254-Q1,TLV2254A-Q1:•Catalog:TLV2252,TLV2252A,TLV2254,TLV2254A•Enhanced Product:TLV2252-EP,TLV2252A-EP,TLV2254-EP,TLV2254A-EP•Military:TLV2252M,TLV2252AM,TLV2254M,TLV2254AMNOTE:Qualified Version Definitions:•Catalog-TI's standard catalog product•Enhanced Product-Supports Defense,Aerospace and Medical Applications •Military-QML certified for Military and Defense ApplicationsIMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,modifications,enhancements,improvements, and other changes to its products and services at any time and to discontinue any product or service without notice.Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by government requirements,testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design.Customers are responsible for their products and applications using TI components.To minimize the risks associated with customer products and applications,customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any TI patent right,copyright,mask work right, or other TI intellectual property right relating to any combination,machine,or process in which TI products or services are rmation published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.Reproduction of this information with alteration is an unfair and deceptive business practice.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements.TI products are not authorized for use in safety-critical applications(such as life support)where a failure of the TI product would reasonably be expected to cause severe personal injury or death,unless officers of the parties have executed an agreement specifically governing such use.Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications,and acknowledge and agree that they are solely responsible for all legal,regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications,notwithstanding any applications-related information or support that may be provided by TI.Further,Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or"enhanced plastic."Only products designated by TI as military-grade meet military specifications.Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk,and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use. TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS16949requirements.Buyers acknowledge and agree that,if they use any non-designated products in automotive applications,TI will not be responsible for any failure to meet such requirements.Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotiveDLP®Products Communications and /communicationsTelecomDSP Computers and /computersPeripheralsClocks and Timers /clocks Consumer Electronics /consumer-appsInterface Energy /energyLogic Industrial /industrialPower Mgmt Medical /medicalMicrocontrollers Security /securityRFID Space,Avionics&/space-avionics-defenseDefenseRF/IF and ZigBee®Solutions /lprf Video and Imaging /videoWireless /wireless-appsMailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2010,Texas Instruments Incorporated。

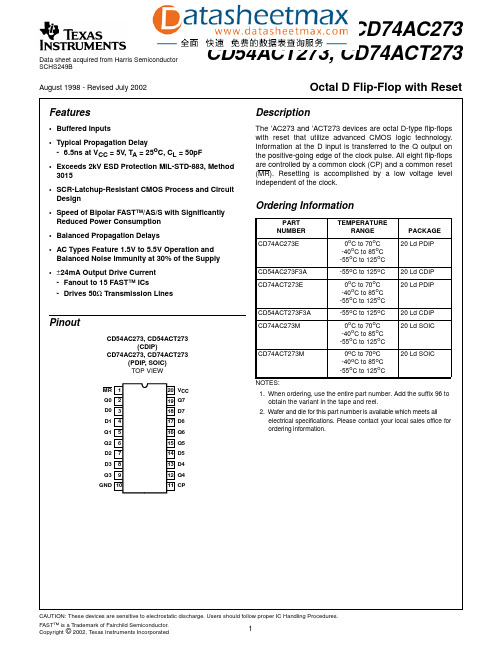

IC datasheet pdf-CD54AC273, CD74AC273,CD54ACT273, CD74ACT273,pdf(Octal D Flip-Flop)

Data sheet acquired from Harris SemiconductorSCHS249BFeatures•Buffered Inputs•Typical Propagation Delay- 6.5ns at V CC = 5V , T A = 25o C, C L = 50pF•Exceeds 2kV ESD Protection MIL-STD-883, Method 3015•SCR-Latchup-Resistant CMOS Process and Circuit Design •Speed of Bipolar FAST™/AS/S with Significantly Reduced Power Consumption •Balanced Propagation Delays•AC Types Feature 1.5V to 5.5V Operation and Balanced Noise Immunity at 30% of the Supply •±24mA Output Drive Current -Fanout to 15 FAST™ ICs-Drives 50Ω Transmission LinesPinoutCD54AC273, CD54ACT273(CDIP)CD74AC273, CD74ACT273(PDIP , SOIC)TOP VIEWDescriptionThe ’AC273and ’ACT273devices are octal D-type flip-flops with reset that utilize advanced CMOS logic rmation at the D input is transferred to the Q output on the positive-going edge of the clock pulse.All eight flip-flops are controlled by a common clock (CP)and a common reset (MR).Resetting is accomplished by a low voltage level independent of the clock.1112131415161718201910987654321MR Q0D0D1Q1Q2D3D2Q3GND V CC D7D6Q6Q7Q5D5D4Q4CPOrdering InformationPART NUMBER TEMPERATURERANGE PACKAGE CD74AC273E0o C to 70o C -40o C to 85o C -55o C to 125o C 20 Ld PDIPCD54AC273F3A -55o C to 125o C 20 Ld CDIP CD74ACT273E0o C to 70o C -40o C to 85o C -55o C to 125o C 20 Ld PDIPCD54ACT273F3A -55o C to 125o C 20 Ld CDIP CD74AC273M0o C to 70o C -40o C to 85o C -55o C to 125o C 20 Ld SOICCD74ACT273M 0o C to 70o C -40o C to 85o C -55o C to 125o C20 Ld SOICNOTES:1.When ordering,use the entire part number.Add the suffix 96to obtain the variant in the tape and reel.2.Wafer and die for this part number is available which meets allelectrical specifications.Please contact your local sales office for ordering information.August 1998 - Revised July 2002CD54AC273, CD74AC273CD54ACT273, CD74ACT273Octal D Flip-Flop with ResetFunctional DiagramTRUTH TABLE INPUTSOUTPUTSRESET (MR)CLOCK CP DATA Dn Qn L X X L H ↑H H H ↑L L HLXQ0H =High level (steady state),L =Low level (steady state),X =Irrel-evant,↑=Transition from Low to High level,Q0=The level of Q before the indicated steady-state input conditions were estab-lished.Q0Q1Q2Q3Q4Q5Q6Q7RESET MRD0D1D2D3D4D5D6D7CLOCKCPDATA INPUTSDATAOUTPUTSAbsolute Maximum Ratings Thermal InformationDC Supply Voltage, V CC. . . . . . . . . . . . . . . . . . . . . . . .-0.5V to 6V DC Input Diode Current, I IKFor V I < -0.5V or V I > V CC + 0.5V. . . . . . . . . . . . . . . . . . . . . .±20mA DC Output Diode Current, I OKFor V O < -0.5V or V O > V CC + 0.5V . . . . . . . . . . . . . . . . . . . .±50mA DC Output Source or Sink Current per Output Pin, I OFor V O > -0.5V or V O < V CC + 0.5V . . . . . . . . . . . . . . . . . . . .±50mA DC V CC or Ground Current, I CC or I GND (Note 3) . . . . . . . . .±100mA Operating ConditionsTemperature Range, T A . . . . . . . . . . . . . . . . . . . . . .-55o C to 125o C Supply Voltage Range, V CC (Note 4)AC T ypes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1.5V to 5.5V ACT T ypes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4.5V to 5.5V DC Input or Output Voltage, V I, V O . . . . . . . . . . . . . . . . .0V to V CC Input Rise and Fall Slew Rate, dt/dvAC T ypes, 1.5V to 3V . . . . . . . . . . . . . . . . . . . . . . . . .50ns (Max) AC T ypes, 3.6V to 5.5V. . . . . . . . . . . . . . . . . . . . . . . .20ns (Max) ACT T ypes, 4.5V to 5.5V. . . . . . . . . . . . . . . . . . . . . . .10ns (Max)Thermal Resistance,θJA(Typical, Note 5)E Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .69o C/W M Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .58o C/W Maximum Junction T emperature (Plastic Package) . . . . . . . . . .150o C Maximum Storage Temperature Range . . . . . . . . . .-65o C to 150o C Maximum Lead Temperature (Soldering 10s). . . . . . . . . . . . .300o CCAUTION:Stresses above those listed in“Absolute Maximum Ratings”may cause permanent damage to the device.This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.NOTES:3.For up to 4 outputs per device, add±25mA for each additional output.4.Unless otherwise specified, all voltages are referenced to ground.5.The package thermal impedance is calculated in accordance with JESD 51.DC Electrical SpecificationsPARAMETER SYMBOLTESTCONDITIONS VCC(V)25o C-40o C TO85o C-55o C TO125o CUNITS V I(V)I O(mA)MIN MAX MIN MAX MIN MAXAC TYPESHigh Level Input Voltage V IH-- 1.5 1.2- 1.2- 1.2-V3 2.1- 2.1- 2.1-V5.5 3.85- 3.85- 3.85-V Low Level Input Voltage V IL-- 1.5-0.3-0.3-0.3V3-0.9-0.9-0.9V5.5- 1.65- 1.65- 1.65V High Level Output Voltage V OH V IH or V IL-0.05 1.5 1.4- 1.4- 1.4-V-0.053 2.9- 2.9- 2.9-V-0.05 4.5 4.4- 4.4- 4.4-V-43 2.58- 2.48- 2.4-V-24 4.5 3.94- 3.8- 3.7-V-75(Note 6, 7)5.5-- 3.85---V-50(Note 6, 7)5.5---- 3.85-VLow Level Output VoltageV OLV IH or V IL0.05 1.5-0.1-0.1-0.1V 0.053-0.1-0.1-0.1V 0.05 4.5-0.1-0.1-0.1V 123-0.36-0.44-0.5V 24 4.5-0.36-0.44-0.5V 75(Note 6, 7) 5.5--- 1.65--V 50(Note 6, 7)5.5----- 1.65V Input Leakage Current I I V CC or GND - 5.5-±0.1-±1-±1µA Quiescent Supply Current MSI I CCV CC or GND5.5-8-80-160µAACT TYPESHigh Level Input Voltage V IH -- 4.5 to 5.52-2-2-V Low Level Input Voltage V IL -- 4.5 to 5.5-0.8-0.8-0.8V High Level Output VoltageV OHV IH or V IL-0.05 4.5 4.4- 4.4- 4.4-V -24 4.5 3.94- 3.8- 3.7-V -75(Note 6, 7) 5.5-- 3.85---V -50(Note 6, 7)5.5---- 3.85-V Low Level Output VoltageV OLV IH or V IL0.05 4.5-0.1-0.1-0.1V 24 4.5-0.36-0.44-0.5V 75(Note 6, 7) 5.5--- 1.65--V 50(Note 6, 7)5.5----- 1.65V Input Leakage Current I I V CC or GND - 5.5-±0.1-±1-±1µA Quiescent Supply Current MSII CC V CC or GND 0 5.5-8-80-160µA Additional Supply Current per Input Pin TTL Inputs High 1 Unit Load ∆I CCV CC -2.1- 4.5 to 5.5- 2.4- 2.8-3mANOTES:6.Test one output at a time for a 1-second maximum duration.Measurement is made by forcing current and measuring voltage to minimize power dissipation.7.Test verifies a minimum 50Ω transmission-line-drive capability at 85o C, 75Ω at 125o C.ACT Input Load TableINPUT UNIT LOADDn 0.5MR 0.57CP1NOTE:Unit load is ∆I CC limit specified in DC Electrical Specifications T able, e.g., 2.4mA max at 25o C.DC Electrical Specifications(Continued)PARAMETERSYMBOL TEST CONDITIONSV CC (V)25o C -40o C TO 85o C -55o C TO 125o C UNITS V I (V)I O (mA)MIN MAX MIN MAX MIN MAXPrerequisite For Switching FunctionPARAMETER SYMBOL V CC (V)-40o C TO 85o C-55o C TO 125o CUNITS MIN MAX MIN MAXAC TYPESData to CP Set-Up Time t SU 1.52-2-ns3.3(Note 9)2-2-ns5(Note 10)2-2-ns Hold Time t H 1.52-2-ns3.32-2-ns52-2-ns Removal Time,MR to CP t REM 1.52-2-ns3.32-2-ns52-2-ns MR Pulse Width t W 1.555-63-ns3.3 6.1-7-ns5 4.4-5-ns CP Pulse Width t W 1.555-63-ns3.3 6.1-7-ns5 4.4-5-ns CP Frequency f MAX 1.59-8-MHz3.381-71-MHz5114-100-MHz ACT TYPESData to CP Set-Up Time t SU5(Note 10)2-2-ns Hold Time t H52-2-ns Removal Time MR to CP t REM52-2-ns MR Pulse Width t W5 4.4-5-ns CP Pulse Width t W5 5.3-6-ns CP Frequency f MAX597-85-MHz Switching Specifications Input t r, t f = 3ns, C L= 50pF (Worst Case)PARAMETER SYMBOL V CC (V)-40o C TO 85o C-55o C TO 125o CUNITS MIN TYP MAX MIN TYP MAXAC TYPESPropagation Delay, CP to Qn t PLH, t PHL 1.5--154--169ns3.3(Note 9)4.9-17.2 4.7-18.9ns5(Note 10)3.5-12.3 3.4-13.5nsPropagation Delay,MR to Qnt PLH , t PHL1.5--154--169ns 3.3 4.9-17.2 4.7-18.9ns 53.5-12.3 3.4-13.5ns Input CapacitanceC I ---10--10pF Power Dissipation Capacitance C PD (Note 11)--45--45-pFACT TYPES Propagation Delay,CP to Qnt PLH , t PHL 5(Note 10)3.5-12.3 3.4-13.5ns Propagation Delay,MR to Qn t PLH , t PHL5 3.5-12.3 3.4-13.5ns Input CapacitanceC I ---10--10pF Power Dissipation Capacitance C PD (Note 11)--45--45-pFNOTES:8.Limits tested 100%.9.3.3V Min is at 3.6V, Max is at 3V.10.5V Min is at 5.5V, Max is at 4.5V.11.C PD is used to determine the dynamic power consumption per flip-flop.AC: P D = C PD V CC 2 f i =∑ (C L V CC 2 f o )ACT:P D =C PD V CC 2f i +∑(C L V CC 2f o )+V CC ∆I CC where f i =input frequency,f o =output frequency,C L =output load capacitance,V CC = supply voltage.FIGURE 1.PROPAGATION DELAY TIMES AND CLOCKPULSE WIDTH FIGURE 2.PREREQUISITE AND PROPAGATION DELAYTIMES FOR MASTER RESETSwitching Specifications Input t r , t f = 3ns, C L = 50pF (Worst Case)(Continued)PARAMETERSYMBOL V CC (V)-40o C TO 85o C-55o C TO 125o CUNITS MIN TYP MAX MIN TYP MAX 90%t f t r V SV S V SV SV St PLHt PHLt W 10%10%CP INPUT LEVEL QMR CPINPUT LEVELV SQV St REMV SV St PLHt WGNDINPUT(Q)FIGURE 3.PREREQUISITE FOR CLOCKDV S V S V SV S V S V St H (H)t SU (L)t H (L)t SU (H)CPOUTPUT LEVELDUT OUTPUTR L (NOTE)OUTPUT LOAD500ΩC L 50pFNOTE:For AC Series Only: When V CC = 1.5V , R L = 1k Ω.FIGURE 4.PROPAGATION DELAY TIMESACACT Input LevelV CC 3V Input Switching Voltage, V S 0.5 V CC 1.5V Output Switching Voltage, V S0.5 V CC0.5 V CCPACKAGING INFORMATIONOrderable Device Status(1)PackageType PackageDrawingPins PackageQtyEco Plan(2)Lead/Ball Finish MSL Peak Temp(3)CD54AC273F3A ACTIVE CDIP J201TBD A42N/A for Pkg Type CD54ACT273F3A ACTIVE CDIP J201TBD A42N/A for Pkg Type CD74AC273E ACTIVE PDIP N2020Pb-Free(RoHS)CU NIPDAU N/A for Pkg TypeCD74AC273EE4ACTIVE PDIP N2020Pb-Free(RoHS)CU NIPDAU N/A for Pkg TypeCD74AC273M ACTIVE SOIC DW2025Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD74AC273M96ACTIVE SOIC DW202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD74AC273M96E4ACTIVE SOIC DW202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD74AC273M96G4ACTIVE SOIC DW202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD74AC273ME4ACTIVE SOIC DW2025Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD74AC273MG4ACTIVE SOIC DW2025Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD74ACT273E ACTIVE PDIP N2020Pb-Free(RoHS)CU NIPDAU N/A for Pkg TypeCD74ACT273EE4ACTIVE PDIP N2020Pb-Free(RoHS)CU NIPDAU N/A for Pkg TypeCD74ACT273M ACTIVE SOIC DW2025Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD74ACT273M96ACTIVE SOIC DW202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD74ACT273M96E4ACTIVE SOIC DW202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD74ACT273M96G4ACTIVE SOIC DW202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD74ACT273ME4ACTIVE SOIC DW2025Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD74ACT273MG4ACTIVE SOIC DW2025Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD74ACT273PW ACTIVE TSSOP PW2070Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD74ACT273PWE4ACTIVE TSSOP PW2070Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD74ACT273PWG4ACTIVE TSSOP PW2070Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD74ACT273PWR ACTIVE TSSOP PW202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD74ACT273PWRE4ACTIVE TSSOP PW202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD74ACT273PWRG4ACTIVE TSSOP PW202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD74ACT273SM96ACTIVE SSOP DB202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD74ACT273SM96E4ACTIVE SSOP DB202000Green(RoHS&CU NIPDAU Level-1-260C-UNLIMOrderable Device Status(1)PackageType PackageDrawingPins PackageQtyEco Plan(2)Lead/Ball Finish MSL Peak Temp(3)no Sb/Br)CD74ACT273SM96G4ACTIVE SSOP DB202000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIM(1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan-The planned eco-friendly classification:Pb-Free(RoHS),Pb-Free(RoHS Exempt),or Green(RoHS&no Sb/Br)-please check /productcontent for the latest availability information and additional product content details.TBD:The Pb-Free/Green conversion plan has not been defined.Pb-Free(RoHS):TI's terms"Lead-Free"or"Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all6substances,including the requirement that lead not exceed0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Pb-Free(RoHS Exempt):This component has a RoHS exemption for either1)lead-based flip-chip solder bumps used between the die and package,or2)lead-based die adhesive used between the die and leadframe.The component is otherwise considered Pb-Free(RoHS compatible)as defined above.Green(RoHS&no Sb/Br):TI defines"Green"to mean Pb-Free(RoHS compatible),and free of Bromine(Br)and Antimony(Sb)based flame retardants(Br or Sb do not exceed0.1%by weight in homogeneous material)(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.TAPE AND REELINFORMATION*All dimensionsare nominalDevicePackage Type Package Drawing Pins SPQReel Diameter (mm)Reel Width W1(mm)A0(mm)B0(mm)K0(mm)P1(mm)W (mm)Pin1Quadrant CD74AC273M96SOIC DW 202000330.024.410.813.0 2.712.024.0Q1CD74ACT273M96SOIC DW 202000330.024.410.813.0 2.712.024.0Q1CD74ACT273PWR TSSOP PW 202000330.016.4 6.957.1 1.68.016.0Q1CD74ACT273SM96SSOPDB202000330.016.48.27.52.512.016.0Q1PACKAGE MATERIALS INFORMATION11-Mar-2008*Alldimensions are nominal DevicePackage Type Package Drawing Pins SPQ Length (mm)Width (mm)Height (mm)CD74AC273M96SOIC DW 202000346.0346.041.0CD74ACT273M96SOIC DW 202000346.0346.041.0CD74ACT273PWRTSSOP PW 202000346.0346.033.0CD74ACT273SM96SSOP DB 202000346.0346.033.0PACKAGE MATERIALS INFORMATION 11-Mar-2008Pack Materials-Page 2IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,modifications,enhancements,improvements, and other changes to its products and services at any time and to discontinue any product or service without notice.Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by government requirements,testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design.Customers are responsible for their products and applications using TI components.To minimize the risks associated with customer products and applications,customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any TI patent right,copyright,mask work right, or other TI intellectual property right relating to any combination,machine,or process in which TI products or services are rmation published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.Reproduction of this information with alteration is an unfair and deceptive business practice.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements.TI products are not authorized for use in safety-critical applications(such as life support)where a failure of the TI product would reasonably be expected to cause severe personal injury or death,unless officers of the parties have executed an agreement specifically governing such use.Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications,and acknowledge and agree that they are solely responsible for all legal,regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications,notwithstanding any applications-related information or support that may be provided by TI.Further,Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or"enhanced plastic."Only products designated by TI as military-grade meet military specifications.Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk,and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use. TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS16949requirements.Buyers acknowledge and agree that,if they use any non-designated products in automotive applications,TI will not be responsible for any failure to meet such requirements.Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers AudioData Converters AutomotiveDLP®Products BroadbandDSP Digital ControlClocks and Timers MedicalInterface MilitaryLogic Optical NetworkingPower Mgmt SecurityMicrocontrollers TelephonyRFID Video&ImagingRF/IF and ZigBee®Solutions WirelessMailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2009,Texas Instruments Incorporated。

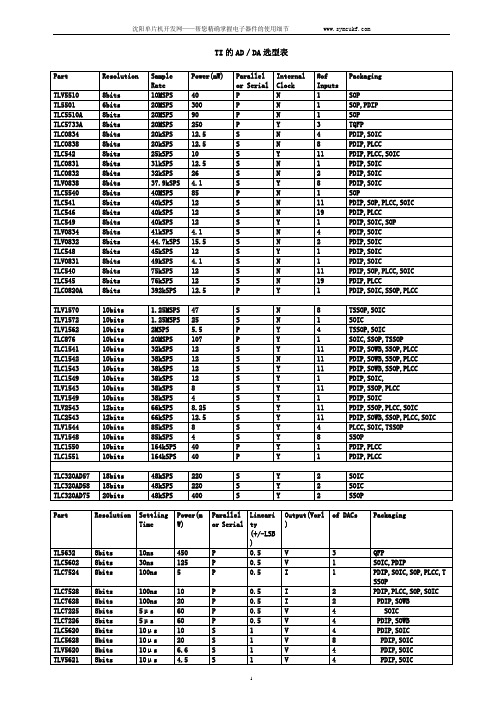

TI的AD、DA选型表

TI的AD/DA选型表Part Resolution SampleRate Power(mW) Parallelor SerialInternalClock#ofInputsPackagingTLV5510 8bits 10MSPS 40 P N 1 SOPTL5501 6bits 20MSPS 300 P N 1 SOP,PDIPTLC5510A 8bits 20MSPS 90 P N 1 SOPTLC5733A 8bits 20MSPS 250 P Y 3 TQFPTLC0834 8bits 20kSPS 12.5 S N 4 PDIP,SOICTLC0838 8bits 20kSPS 12.5 S N 8 PDIP,PLCCTLC542 8bits 25kSPS 10 S Y 11 PDIP,PLCC,SOICTLC0831 8bits 31kSPS 12.5 S N 1 PDIP,SOICTLC0832 8bits 32kSPS 26 S N 2 PDIP,SOICTLV0838 8bits 37.9kSPS 4.1 S Y 8 PDIP,SOICTLC5540 8bits 40MSPS 85 P N 1 SOPTLC541 8bits 40kSPS 12 S N 11 PDIP,SOP,PLCC,SOICTLC546 8bits 40kSPS 12 S N 19 PDIP,PLCCTLC549 8bits 40kSPS 12 S Y 1 PDIP,SOIC,SOPTLV0834 8bits 41kSPS 4.1 S N 4 PDIP,SOICTLV0832 8bits 44.7kSPS 15.5 S N 2 PDIP,SOICTLC548 8bits 45kSPS 12 S Y 1 PDIP,SOICTLV0831 8bits 49kSPS 4.1 S N 1 PDIP,SOICTLC540 8bits 75kSPS 12 S N 11 PDIP,SOP,PLCC,SOICTLC545 8bits 76kSPS 12 S N 19 PDIP,PLCCTLC0820A 8bits 392kSPS 12.5 P Y 1 PDIP,SOIC,SSOP,PLCCTLV1570 10bits 1.25MSPS 47 S N 8 TSSOP,SOICTLV1572 10bits 1.25MSPS 25 S N 1 SOICTLV1562 10bits 2MSPS 5.5 P Y 4 TSSOP,SOICTLC876 10bits 20MSPS 107 P Y 1 SOIC,SSOP,TSSOPTLC1541 10bits 32kSPS 12 S Y 11 PDIP,SOWB,SSOP,PLCCTLC1542 10bits 38kSPS 12 S N 11 PDIP,SOWB,SSOP,PLCCTLC1543 10bits 38kSPS 12 S Y 11 PDIP,SOWB,SSOP,PLCCTLC1549 10bits 38kSPS 12 S Y 1 PDIP,SOIC,TLV1543 10bits 38kSPS 8 S Y 11 PDIP,SSOP,PLCCTLV1549 10bits 38kSPS 4 S Y 1 PDIP,SOICTLV2543 12bits 66kSPS 8.25 S Y 11 PDIP,SSOP,PLCC,SOICTLC2543 12bits 66kSPS 12.5 S Y 11 PDIP,SOWB,SSOP,PLCC,SOIC TLV1544 10bits 85kSPS 8 S Y 4 PLCC,SOIC,TSSOPTLV1548 10bits 85kSPS 4 S Y 8 SSOPTLC1550 10bits 164kSPS 40 P Y 1 PDIP,PLCCTLC1551 10bits 164kSPS 40 P Y 1 PDIP,PLCCTLC320AD57 18bits 48kSPS 220 S Y 2 SOICTLC320AD58 18bits 48kSPS 220 S Y 2 SOICTLC320AD75 20bits 48kSPS 400 S Y 2 SSOPPart Resolution SettlingTime Power(mW)Parallelor SerialLinearity(+/-LSB)Output(Vorl)of DACs PackagingTL5632 8bits 10ns 450 P 0.5 V 3 QFPTLC5602 8bits 30ns 125 P 0.5 V 1 SOIC,PDIPTLC7524 8bits 100ns 5 P 0.5 I 1 PDIP,SOIC,SOP,PLCC,TSSOPTLC7528 8bits 100ns 10 P 0.5 I 2 PDIP,PLCC,SOP,SOIC TLC7628 8bits 100ns 20 P 0.5 I 2 PDIP,SOWBTLC7225 8bits 5μs 60 P 0.5 V 4 SOICTLC7226 8bits 5μs 60 P 0.5 V 4 PDIP,SOWBTLC5620 8bits 10μs 10 S 1 V 4 PDIP,SOICTLC5628 8bits 10μs 20 S 1 V 8 PDIP,SOICTLV5620 8bits 10μs 6.6 S 1 V 4 PDIP,SOICTLV5621 8bits 10μs 4.5 S 1 V 4 PDIP,SOIC1TLV5628 8bits 10μs 13.2 S 1 V 8 PDIP,SOIC TLV5613 10bits 1-3.5μs 1.2-4.2 P 1.5 V 1 SOIC,TSSOP TLC5617A 10bits 1.9-7.9μs3.5 S 0.5 V 2 SOICTLV5604 10bits 3-9μs 5.5 S 0.5 V 4 SOIC,TSSOP TLC5615 10bits 12.5μs 1.25 S 0.5 V 1 PDIP,SOIC TLV5619 12bits 1μs 4.3 P 1.5 V 1 SOIC,TSSOP TLC5618A 12bits 1.5-3μs 3.5 S 1 V 2 SOICTLV5614 12bits 3-9μs 3.6-8 S 1.5 V 4 SOIC,TSSOP TLV5616 12bits 3-9μs 2.1 S 1.9 V 1 SOICTLC320AD8 0 16bits-260 S-V 2 PLCCTMS57014A 18bits- 350 S-PWM 2 SOPAnalog Interface Circuits(AICs)Part Band PassFilter Low PassFilterSampling RateSin x/xCorrectionInternalVRefSupplyVoltagePowerDissipation(3dB)Hz (3dB) (max)8BitTLC32040 300-3400Hz 3400Hz 19.2kHz No Yes +/-5 120mW TLC32041 300-3400Hz 3400Hz 19.2k No No +/-5 120mW TLC32044 150-3600Hz 3600Hz 19.2k Yes Yes +/-5 125mW TLC32045 150-3600Hz 3600Hz 19.2k Yes Yes +/-5 125mW TLC32046 300-7300Hz 7300Hz 25k Yes Yes +/-5 125mW TLC32047 450-10.95kHz10.95k 25k Yes Yes +/-5 130mWTLC320AC0 1 up to10.8kHz10.8k 25k Yes Yes 5 100mWTLC320AC0 2 up to10.8kHz10.8k 25k Yes Yes 5 100mW16BitTLC320AD5 0 up to9.92kHz9.92k 22.05k No Yes 1.666666667120mWTLC320AD5 2 up to9.92kHz9.92k 22.05k No Yes 1.666666667120mWTLC320AD5 5 up to4.41kHz4.41k 11.025k No Yes 5 150mWTLC320AD5 6 up to8.82kHz8.82k 22.05k No Yes 1.666666667100mWTLC320AD5 35 up to4.96kHz4.96k 11.025k No Yes 5 240mWTLC320AD5 45 up to4.96kHz4.96k 11.025k No Yes 1.666666667120mWADC Resolution ConversionRate Power(mV)typ.ParallelOr SerialNo.ofInputsSupplyVoltage(V)TLC540 8bits 75kSPS 6 S 11 5TLC541 8bits 40kSPS 6 S 11 5TLC542 8bits 25kSPS 6 S 11 5TLC545 8bits 76kSPS 6 S 19 5TLC546 8bits 40kSPS 6 S 19 5TLC548 8bits 45kSPS 6 S 1 5TLC549 8bits 40kSPS 6 S 1 5TLC876 10bits 20MSPS 107 P 1 3月5日 TLC1540 10bits 32kSPS 6 S 11 5TLC1541 10bits 32kSPS 6 S 11 5TLC1542 10bits 38kSPS 4 S 11 5TLC1543 10bits 38kSPS 4 S 11 5TLC1549 10bits 38kSPS 4 S 11 5TLC1550 10bits 164kSPS 10 P 1 5TLC1551 10bits 164kSPS 10 P 1 5TLC2543 12bits 66kSPS 5 S 11 5TLC5510 8bits 20MkSPS 90 P 1 3.32TLC5540 8bits 40MSPS 85 P 1 5TLV1543 10bits 38kSPS 4 S 11 3.3*TLV1544 10bits 85kSPS 3 S 4 5*TLV1548 10bits 85kSPS 3 S 8 3月5日 *TLV1570 10bits 1.25kSPS 8 S 8 3月5日 *TLV1572 10bits 1.25kSPS 8 S 1 3月5日 *TLV2543 12bits 66kSPS 3.3 S 11 3.3*TLV5510 8bits 10kSPS 40 P 1 3.3 Analog-to-Digital Converters for the 'c3000*TLC876 10bits 20MSPS 107 P 1 5TLC1550 10bits 164kSPS 10 P 1 5TLC1551 10bits 164kSPS 10 P 1 5*TLC2543 12bits 66kSPS 5 S 11 5*TLC5510 8bits 20MkSPS 90 P 1 5*TLC5540 8bits 40MSPS 85 P 1 5*TLV1544/8 10bits 85kSPS 3 S 4 or 8 3月5日 *TLV1570 10bits 1.25kSPS 8 S 8 3月5日 *TLV1572 10bits 1.25kSPS 8 S 1 3月5日 *TLV2543 12bits 66kSPS 3.3 S 11 3.3*TLV5510 8bits 10kSPS 40 P 1 3.3 Analog-to-Digital Converters for the 'c54x*TLC876 10bits 20MSPS 107 P 1 5TLC1550 10bits 164kSPS 10 P 1 5TLC1551 10bits 164kSPS 10 P 1 5*TLC2543 12bits 66kSPS 5 S 11 5*TLC5510 8bits 20MkSPS 90 P 1 5*TLC5540 8bits 40MSPS 85 P 1 5*TLV1544/8 10bits 85kSPS 3 S 4 or 8 3月5日 *TLV1570 10bits 1.25kSPS 8 S 8 3月5日 *TLV1572 10bits 1.25kSPS 8 S 1 3月5日 *TLV2543 12bits 66kSPS 3.3 S 11 3.3*TLV5510 8bits 10kSPS 40 P 1 3.3 Analog-to-Digital Converters for the 'c6201*TLC876 10bits 20MSPS 107 P 1 5TLV1543 10bits 38kSPS 4 S 11 3.3*TLV1544/8 10bits 85kSPS 3 S 4 or 8 3月5日 *TLV1570 10bits 1.25kSPS 8 S 8 3月5日 *TLV1572 10bits 1.25kSPS 8 S 1 3月5日 *TLV2543 12bits 66kSPS 3.3 S 11 3.3*TLV5510 8bits 10kSPS 40 P 1 3.3 Digital-to-Analog Converters for the 'c2000DAC Resolution SettlingTime(μs) Power(mW)typ.ParallelOr SerialSupplyVoltage(V)Output(V or I)No.ofDACsTLC5615 10bits 12.5 1.3 S 5 V 1 TLC5617A 10bits 2.5-12.5 8.8 S 5 V 2 TLC5618A 12bits 2.5-12.5 8.8 S 5 V 2 TLC7225 8bits 5 75 P 5月15日 V 4 TLC7226 8bits 5 96 P 15 V 4 TLC7524 8bits 0.1 5 P 5月15日 I 1 TLC7528 8bits 0.1 10 P 5月15日 I 2 TLC7628 8bits 0.1 20 P 11月15日 I 2 TLV5604 10bits 3月9日 9 S 3月5日 V 4 TLV5613 12bits 1-3.5 4.2 P 3月5日 V 1 TLV5614 12bits 3.9 9.6 S 3月5日 V 4 TLV5616 12bits 3月9日 2.1 S 3月5日 V 1 TLV5619 12bits 1 4.5 P 3月5日 V 1 Digital-to-Analog Converters for the 'C3000TLC5617A 10bits 2.5-12.5 8.8 S 5 V 2 TLC5618A 12bits 2.5-12.5 8.8 S 5 V 2 TLC7225 8bits 5 75 P 5月15日 V 4 TLC7226 8bits 5 96 P 15 V 4 TLC7524 8bits 0.1 5 P 5月15日 I 13TLC7528 8bits 0.1 10 P 5月15日 I 2 TLC7628 8bits 0.1 20 P 11月15日 I 2 TLV5604 10bits 3.9 9 S 3月5日 V 4 TLV5613 12bits 1-3.5 4.2 P 3月5日 V 1 TLV5614 12bits 3月9日 9.6 S 3月5日 V 4 TLV5616 12bits 3月9日 2.1 S 3月5日 V 1 TLV5619 12bits 1 4.5 P 3月5日 V 1 Digital-to-Analog Converters for the 'C54XTLC5617A 10bits 2.5-12.5 8.8 S 5 V 2 TLC5618A 12bits 2.5-12.5 8.8 S 5 V 2 TLC7225 8bits 5 75 P 5月15日 V 4 TLC7226 8bits 5 96 P 15 V 4 TLC7524 8bits 0.1 5 P 5月15日 I 1 TLC7528 8bits 0.1 10 P 5月15日 I 2 TLC7628 8bits 0.1 20 P 11月15日 I 2 TLV5604 10bits 3.9 9 S 3月5日 V 4 TLV5614 12bits 3月9日 9.6 S 3月5日 V 4 TLV5616 12bits 3月9日 2.1 S 3月5日 V 1 TLV5613 12bits 1-3.5 4.2 P 3月5日 V 1 TLV5619 12bits 1 4.5 P 3月5日 V 1 Digital-to-Analog Converters for the 'C6201TLV5604 10bits 3.9 9 S 3月5日 V 4 TLV5613 12bits 1-3.5 4.2 P 3月5日 V 1 TLV5614 12bits 3月9日 9.6 S 3月5日 V 4 TLV5616 12bits 3月9日 2.1 S 3月5日 V 1 TLV5619 12bits 1 4.5 P 3月5日 V 14。

TLV5616中文资料

湖州职业技术学院应用电子技术专业课程设计信号处理资料学生姓名:沈惠娣毕业班级:应电0803指导教师:俞志根2010年1月8日信号处理资料一、绪论AD:模数转换,将模拟信号变成数字信号,便于数字设备处理。

DA:数模转换,将数字信号转换为模拟信号与外部世界接口。

AD转换器的分类有很多如:积分型、逐次逼近型、并行比较型/串并行型、∑-Δ调制型、电容阵列逐次比较型及压频变换型。

AD转换器的主要技术指标分辨率(Resolution)、转换速率(Conversion Rate)、量化误差(Quantizing Error)、偏移误差(Offset Error)、满刻度误差(Full Scale Error)、线性度(Linearity)、其他指标还有:绝对精度(Absolute Accuracy) ,相对精度(Relative Accuracy),微分非线性,单调性和无错码,总谐波失真(Total Harmonic Distotortion缩写THD)和积分非线性。

DA转换器有电压输出型、电流输出型、乘算型、一位DA转换器。

DA转换器的主要技术指标:分辩率(Resolution)、建立时间(Setting Time)、其他指标还有线性度(Linearity),转换精度,温度系数/漂移。

目前生产AD/DA的主要厂家有ADI、TI等。

1. ADI公司AD/DA器件1)带信号调理、1mW功耗、双通道16位AD转换器:AD7705AD7705是AD公司出品的适用于低频测量仪器的AD转换器。

它能将从传感器接收到的很弱的输入信号直接转换成串行数字信号输出,而无需外部仪表放大器。

采用Σ-Δ的ADC,实现16位无误码的良好性能,片内可编程放大器可设置输入信号增益。

通过片内控制寄存器调整内部数字滤波器的关闭时间和更新速率,可设置数字滤波器的第一个凹口。

在+3V电源和1MHz主时钟时,;AD7705功耗仅是1mW。

AD7705是基于微控制器(MCU)、数字信号处理器(DSP)系统的理想电路,能够进一步节省成本、缩小体积、减小系统的复杂性。

TLV5616资料总结

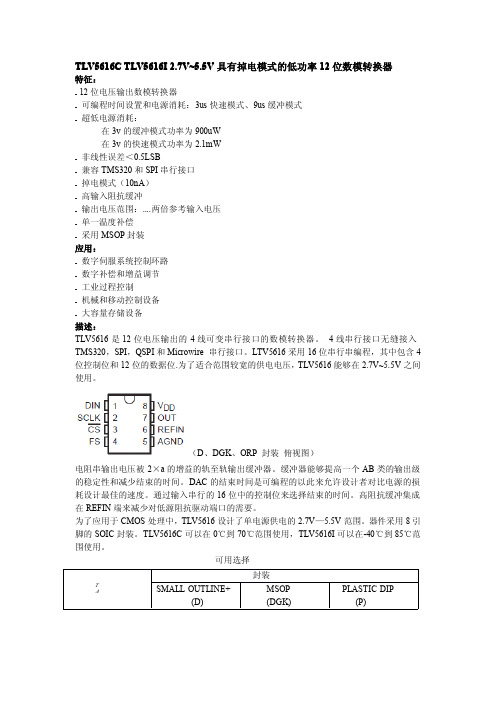

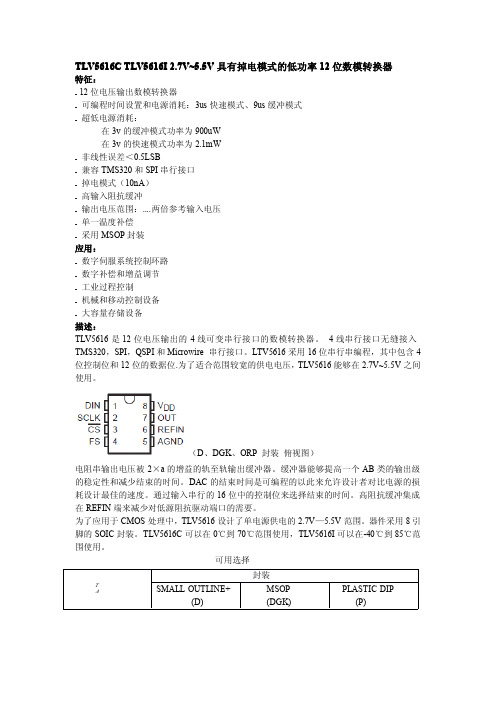

高精度D/A转换芯片—TLV5616TLV5616 是12 位电压输出的4 线可变串行接口的数模转换器。

4 线串行接口无缝接入TMS320,SPI,QSPI 和Microwire 串行接口。

电源供电电压范围2.7V~5.5V。

LTV5616 采用16 位串行串编程,其中包含4位控制位和12 位的数据位.为了适合范围较宽的供电电压。

1.TLV5616的引脚图及其说明:电阻串输出电压被2×a 的增益的轨至轨输出缓冲器。

缓冲器能够提高一个AB 类的输出级的稳定性和减少结束的时间。

DAC 的结束时间是可编程的以此来允许设计者对比电源的损耗设计最佳的速度。

通过输入串行的16 位中的控制位来选择结束的时间。

高阻抗缓冲集成在REFIN 端来减少对低源阻抗驱动端口的需要。

2.TLV5616的功能模块图:3. TLV5616的接口图当REF 是参考电压CODE 是在0x000~0xFFF 范围内的数字输入值时,上电复位初始复位外部触发器到一个固定的状态(全为0)。

串行接口说明数据的转换:首先器件必须设置/CS 为低电平时器件有效,然后在FS 的下降边缘开始一位一位转移数据(开始是高位有效位)在SCLK 的下降边缘转移到内部寄存器。

在16 位都被转换后或FS 上升时,转移寄存器的内容移到DAC 的触发器使其输出电压更新到一个新的电平。

TLV5616 串行接口可以采用两个基本模式:. 四线(包括片选). 三线(不包括片选)使用片选(四线模式)使得多个器件连接到串行口的数据源(DSP 或微控制器)成为可能。

接口是TMS320 类兼容的,下图给出了2 个TLV 5616 直接连接到TMS320DSP 上的例子。

如果串行总线上只有一个器件,那么/CS 可以接低电平,16 给出了TLV5616 如何在SPI 或图Microwire 接口三线引脚下连接到一个TMS320 上的例子。

注意SPI 和Microwire:在控制器开始转换数据之前软件必须在FS 连接的I/O 引脚上产生一个下降缘。

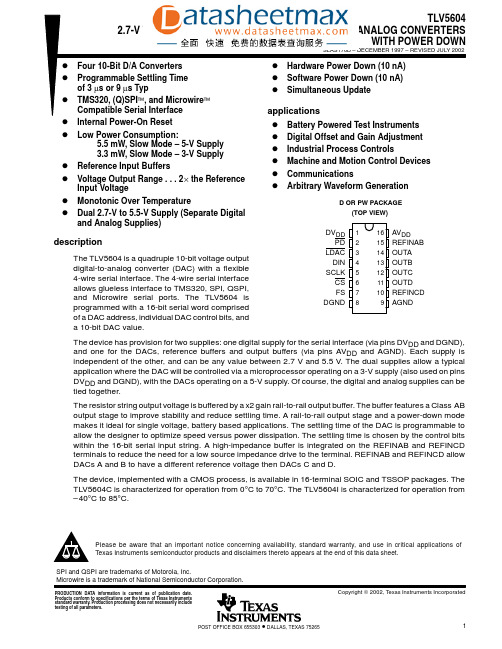

IC datasheet pdf-TLV5604,pdf(2.7-V to 5.5-V 10-Bit 3-uS Quadruple Digital-to-Analog Converters w_Pow

SLAS176B – DECEMBER 1997 – REVISED JULY 2002

AVAILABLE OPTIONS PACKAGE TA 0°C to 70°C – 40°C to 85°C SOIC (D) TLV5604CD TLV5604ID TSSOP (PW) TLV5604CPW TLV5604IPW

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. SPI and QSPI are trademarks of Motorola, Inc. Microwire is a trademark of National Semiconductor Corporation.

Four 10-Bit D/A Converters Programmable Settling Time of 3 µs or 9 µs Typ TMS320, (Q)SPI, and Microwire Compatible Serial Interface Internal Power-On Reset Low Power Consumption: 5.5 mW, Slow Mode – 5-V Supply 3.3 mW, Slow Mode – 3-V Supply Reference Input Buffers Voltage Output Range . . . 2 × the Reference Input Voltage Monotonic Over Temperature Dual 2.7-V to 5.5-V Supply (Separate Digital and Analog Supplies)

tlv5616中文

推荐使用的环境:

注意 1:为了满足×2 输出缓存,参考输入电压≥VDD/2 将引起转换功能消减。 在推荐的自由空间温度范围内的电气特征(除非特别的说明) 电源供电:

注意: 2、电源供电抑制比在零刻度的测量通过变化的 VDD 由下式求出: 3、电源供电抑制比在满刻度的测量通过变化的 VDD 有下式求出:

(D、DGK、ORP 封装 俯视图)

电阻串输出电压被 2×a 的增益的轨至轨输出缓冲器。缓冲器能够提高一个 AB 类的输出级 的稳定性和减少结束的时间。DAC 的结束时间是可编程的以此来允许设计者对比电源的损 耗设计最佳的速度。通过输入串行的 16 位中的控制位来选择结束的时间。高阻抗缓冲集成 在 REFIN 端来减少对低源阻抗驱动端口的需要。 为了应用于 CMOS 处理中,TLV5616 设计了单电源供电的 2.7V—5.5V 范围。器件采用 8 引 脚的 SOIC 封装。TLV5616C 可以在 0℃到 70℃范围使用,TLV5616I 可以在-40℃到 85℃范 围使用。

在推荐的自由空间温度范围内的电气特征(除非特别的说明)(续) 静态 DAC 规格 RL=10KΩ CL=100pF:

注意: 4、相对精度或集成非线性化(INL)有时候涉及到线性化的错误,是最大的输出偏 差来自线性的零刻度到满刻度除了零刻度和满刻度误差。

5、微分非线形化有时候设计到微分差,微分差是由于测量和任何毗邻码 1LSB 的幅 度改变的不同造成的,单调性表示输出电压随着输入的数字电压变化在相同的方向上变(或 者保持为一个常数)。

线性化、补偿、增益误差应用在单端供电中 当一个放大器采用单电源供电时,电源补偿仍然可正可负。正补偿时输出电压在第一个 码变化时放生变化,负补偿时,输出电压可能不会在第一个码处发生变化,它取决于补偿电 压的幅角。输出放大器趋向使输出为一个负的电压,然后绝大多数负的供电源端都是接地 的 , 输出不可能低于零,因此输出电压都固定在 0V。 输出电压保持为 0V 直到输入的码值产生一个有效的正输出电压来弥补负的补偿电压结 果产生了图 19 的转换功能。

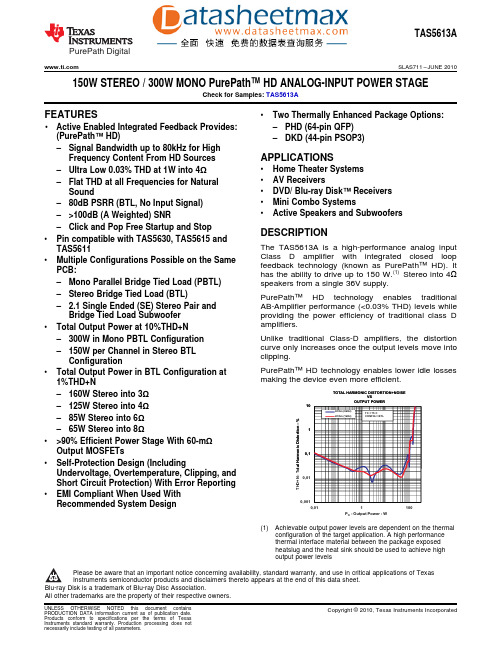

IC datasheet pdf-TAS5613,pdf(150W Stereo_300W Mono PurePath HD Analog-Input Power Stage)

•23 Active Enabled Integrated Feedback Provides: (PurePath™ HD) – Signal Bandwidth up to 80kHz for High Frequency Content From HD Sources – Ultra Low 0.03% THD at 1W into 4Ω – Flat THD at all Frequencies for Natural Sound – 80dB PSRR (BTL, No Input Signal) – >100dB (A Weighted) SNR – Click and Pop Free Startup and Stop

• EMI Compliant When Used With Recommended System Design

• Two Thermally Enhanced Package Options: – PHD (64-pin QFP) – DKD (44-pin PSOP3)

APPLICATIONS

• Home Theater Systems • AV Receivers • DVD/ Blu-ray Disk™ Receivers • Mini Combo Systems • Active Speakers and Subwoofers

PO - Output Power - W

IC datasheet pdf-TL1431-Q1,pdf(Precision Programmable Reference)

PRECISION PROGRAMMABLEPRECISION PROGRAMMABLEPACKAGING INFORMATION Orderable DeviceStatus (1)Package Type Package Drawing Pins Package Qty Eco Plan (2)Lead/Ball Finish MSL Peak Temp (3)TL1431QDRG4Q1ACTIVE SOIC D 82500Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM TL1431QDRQ1ACTIVE SOIC D 82500Pb-Free (RoHS)CU NIPDAU Level-2-250C-1YEAR/Level-1-235C-UNLIM (1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan -The planned eco-friendly classification:Pb-Free (RoHS),Pb-Free (RoHS Exempt),or Green (RoHS &no Sb/Br)-please check /productcontent for the latest availability information and additional product content details.TBD:The Pb-Free/Green conversion plan has not been defined.Pb-Free (RoHS):TI's terms "Lead-Free"or "Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all 6substances,including the requirement that lead not exceed 0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Pb-Free (RoHS Exempt):This component has a RoHS exemption for either 1)lead-based flip-chip solder bumps used between the die and package,or 2)lead-based die adhesive used between the die and leadframe.The component is otherwise considered Pb-Free (RoHS compatible)as defined above.Green (RoHS &no Sb/Br):TI defines "Green"to mean Pb-Free (RoHS compatible),and free of Bromine (Br)and Antimony (Sb)based flame retardants (Br or Sb do not exceed 0.1%by weight in homogeneous material)(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TIto Customer on an annual basis.OTHER QUALIFIED VERSIONS OF TL1431-Q1:•Catalog:TL1431•EnhancedProduct:TL1431-EP •Military:TL1431M •Space:TL1431-SP NOTE:Qualified Version Definitions:•Catalog-TI's standard catalog product •EnhancedProduct -Supports Defense,Aerospace and Medical Applications •Military -QML certified for Military and Defense Applications •Space -Radiation tolerant,ceramic packaging and qualified for use in Space-based application PACKAGE OPTION ADDENDUM 18-Sep-2008Addendum-Page 1IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,modifications,enhancements,improvements, and other changes to its products and services at any time and to discontinue any product or service without notice.Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by government requirements,testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design.Customers are responsible for their products and applications using TI components.To minimize the risks associated with customer products and applications,customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any TI patent right,copyright,mask work right, or other TI intellectual property right relating to any combination,machine,or process in which TI products or services are rmation published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.Reproduction of this information with alteration is an unfair and deceptive business practice.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements.TI products are not authorized for use in safety-critical applications(such as life support)where a failure of the TI product would reasonably be expected to cause severe personal injury or death,unless officers of the parties have executed an agreement specifically governing such use.Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications,and acknowledge and agree that they are solely responsible for all legal,regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications,notwithstanding any applications-related information or support that may be provided by TI.Further,Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or"enhanced plastic."Only products designated by TI as military-grade meet military specifications.Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk,and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use. TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS16949requirements.Buyers acknowledge and agree that,if they use any non-designated products in automotive applications,TI will not be responsible for any failure to meet such requirements.Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers AudioData Converters AutomotiveDLP®Products BroadbandDSP Digital ControlClocks and Timers MedicalInterface MilitaryLogic Optical NetworkingPower Mgmt SecurityMicrocontrollers TelephonyRFID Video&ImagingRF/IF and ZigBee®Solutions WirelessMailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2009,Texas Instruments Incorporated。

tlv5616中文

图 11

集成非线性化误差:

图 12

微分非线性误差:

图 13

图 14

应用信息: 总体功能 TLV5616 是一个基于寄存器串 12 位单电源数模转换器。器件由一个串行接口、加速器和 掉 电控制逻辑、参考输入缓冲期,串寄存器和一个轨至轨的输出缓存器构成。 输出电压(满刻度取决于外部参考电压)由下式给给出:

可用选择

封装

T A

SMALL OUTLINE+

MSOP

PLASTIC DIP

(D)

(DGK)

(P)

0℃~70℃

TLV5616CD

TLV5616CDGK

-40℃~85℃ TLV5616ID

TLV5616IDGK

+ 在磁带和卷轴中是 TLV5616CD 和 TLV5616IDR

功能模块图:

TLV5616CP TLV5616IP

13、转换速度取决于 DAC 输出由满刻度的 10%变到满刻度的 90%说花费的时间。

数字输入时间要求: 参数测定信息:

典型特征: 输出电压和负载电流:

图 1. 时序图

图4 图5

图6 供电电流和只有空间温度:

图6

图7 总谐波失真和频率:

图8

图9 总谐波失真和噪声与频率:

图 10

供电电流和时间(进入掉电模式)

当 REF 是参考电压 CODE 是在 0x000~0xFFF 范围内的数字输入值时,上电复位初始复位外 部触发器到一个固定的状态(全为 0)。 串行接口 说明数据的转换:首先器件必须设置 /CS 为低电平时器件有效,然后在 FS 的下降边缘开始 一位一位转移数据(开始是高位有效位)在 SCLK 的下降边缘转移到内部寄存器。在 16 位 都被转换后或 FS 上升时,转移寄存器的内容移到 DAC 的触发器使其输出电压更新到一个 新的电平。 TLV5616 串行接口可以采用两个基本模式: . 四线(包括片选) . 三线(不包括片选) 使用片选(四线模式)使得多个器件连接到串行口的数据源( DSP 或微控制器)成为可能。

TLV5616

2011-3-8

RL A DJNZ R0,SEND—HIBYTE MOV R0.#08H MOV A,R6 ;取命令字低字节 SEND—LOBYTE: M0V SD,ACC.7 ;送出数据位D7一D0 CLR SCK SETB SCK RL A DJNZ R0.SEND—LOBYTE SETB CS ;传输结束,关芯片接口 RET 在上例中,TLV5638采用+5V供电,使用片内基准源,片选信号CS#由微控制器 P1.0引脚提供;帧起始信号FS由P1.1引脚提供;串行通信时钟SCLK由P1.2引 脚提供;串行数据由P1.3输出。若串行总线上仅挂接TLV5636一个设备,则CS#可 以接低电平以节约一根口线。若TLV5636使用外接基准源,则每次系统上电后必须 向其写人命令字以关闭内部基准源的输出。在上面的程序段中,入口参数为16位的 TLV5636命令字,高字节存放在R7中,低字节存放在R6中。使用时将上述程序附在 主程序后,并在主程序中调用即可。

2011-3-8

TLV5636的内部结构及引脚功能 TLV5636的内部结构及引脚功能

引脚名称及功能

• 引脚号 名称 功能 • l DIN 串行数据输入 • 2 SCLK 串行时钟输入 • 3 CS# 片选 • 4 FS 帧起始 • 5 AGND 电源地 • 6 REF 基准输入或输出 • 7 0UT 转换输出引脚 • 8 VDD 电源

SPD为速度控制位,为0时电路工作于低速模式,为1时工作于高速模式。PWR为功耗 控制位,为1时电路进入掉电模式。当Ro、R1同时为1时,12位数据被写入DAc数据寄 存器。当R0、R1同时为0时,12位数据的最低两位(Dl,D0)被写入控制寄存器。如果控 制寄存器中数据为0或3时,片内基准源将被禁止,此时可以使用外接的电压基准。如果 此数据为1,片内基准输出为1.024V,此数据为2,则片内基准输出为2.048V。电路 模拟电压输出值Vout=2*Vref*Code/4096,此式中Vref即基准电压,Code础即DAC寄存器 中的12位数据。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

D D Low Power Consumption:

D D Voltage Output Range . . . 2 × the Reference D D Dual 2.7-V to 5.5-V Supply (Separate Digital

and Analog Supplies) Input Voltage Monotonic Over Temperature

APPLICATIONS D D D D D D

Battery Powered Test Instruments Digital Offset and Gain Adjustment Industrial Process Controls Machine and Motion Control Devices Communications Arbitrary Waveform Generation

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright 2003, Texas Instruments Incorporated

TLV5614IYE

SLAS391A − JULY 2003 − REVISED AUGUST 2003

These devices have limited built-in ESD protection. The device should be placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

9 µs Typ TMS320 DSP Family, (Q)SPI, and Microwire Compatible Serial Interface Internal Power-On Reset − 8 mW, Slow Mode − 5-V Supply − 3.6 mW, Slow Mode − 3-V Supply Reference Input Buffer

2 2 2-Bit Control Data Latch 2 Power-Down/ Speed Control

DIN

4

Serial Input Register 2

14

7 FS SCLK CS 5 6 DAC Select/ Control Logic DAC B 13 OUTB

DAC C

12

OUTC

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. TMS320 DSP is a trademark of Texas Instruments. SPI and QSPI are trademarks of Motorola, Inc. Microwire is a trademark of National Semiconductor Corporation.

LDAC

DIN

SCLK

CS

The TLV5614IYE is a quadruple 12-bit voltage output digital-to-analog converter (DAC) with a flexible 4-wire serial interface. The serial interface allows glueless interface to TMS320, SPI, QSPI, and Microwire serial ports. The TLV5614IYE is programmed with a 16-bit serial word comprised of a DAC address, individual DAC control bits, and a 12-bit DAC value. The device has provision for two supplies: one digital supply for the serial interface (via pins DVDD and DGND), and one for the DACs, reference buffers, and output buffers (via pins AVDD and AGND). Each supply is independent of the other, and can be any value between 2.7 V and 5.5 V. The dual supplies allow a typical application where the DAC is controlled via a microprocessor operating on a 3 V supply (also used on pins DVDD and DGND), with the DACs operating on a 5 V supply. Of course, the digital and analog supplies can be tied together. The resistor string output voltage is buffered by a x2 gain rail-to-rail output buffer. The buffer features a Class AB output stage to improve stability and reduce settling time. A rail-to-rail output stage and a power-down mode makes it ideal for single voltage, battery based applications. The settling time of the DAC is programmable to allow the designer to optimize speed versus power dissipation. The settling time is chosen by the control bits within the 16-bit serial input string. A high-impedance buffer is integrated on the REFINAB and REFINCD terminals to reduce the need for a low source impedance drive to the terminal. REFINAB and REFINCD allow DACs A and B to have a different reference voltage then DACs C and D. The TLV5614IYE is implemented with a CMOS process and is available in a 16-terminal WCS package. The TLV5614IYE is characterized for operation from −40°C to 85°C in a wire-bonded small outline (SOIC) package.

AVAILABLE OPTIONS

PACKAGE TA WCS(1) (YE)

−40°C to 85°C TLV5614IYE (1) Wafer chip scale package. See Figure 17.

FUNCTIONAL BLOCK DIAGRAM

AVDD REFINAB 15 16 DVDD 1 DAC A Power-On Reset 12 14-Bit Data and Control Register + _ + _ 12-Bit DAC Latch 10 14 OUTA

REFINCD

10

DAC D

11

OUTD

3 9 AGND 8 DGND LDAC

2 PD

2

TLV5614IYE

SLAS391A − JULY 2003 − REVISED AUGUST 2003

Terminal Functions

TERMINAL NAME AGND AVDD CS DGND DIN DVDD FS PD LDAC REFINAB REFINCD SCLK OUTA OUTB OUTC OUTD NO. 9 16 6 8 4 1 7 2 3 15 10 5 14 13 12 11 I I I I I I O O O O I I I/O Analog ground Analog supply Chip select. This terminal is active low. Digital ground Serial data input Digital supply Frame sync input. The falling edge of the frame sync pulse indicates the start of a serial data frame shifted out to the TLV5614IYE. Power down pin. Powers down all DACs (overriding their individual power down settings), and all output stages. This terminal is active low. Load DAC. When the LDAC signal is high, no DAC output updates occur when the input digital data is read into the serial interface. The DAC outputs are only updated when LDAC is low. Voltage reference input for DACs A and B. Voltage reference input for DACs C and D. Serial clock input DACA output DACB output DACC output DACD output DESCRIPTION