ApplicationNote-Negative Spike In Buck Converters_6 值得学习

Buck电源设计

* (Rx, Cy) 显示驱动极点及零点的组成部分。 详尽的公式登载在注释的一页内。

1-26

电压模式 ─ 误差信号放大器

VC ZF =− VOUT ZI

我们可以因应误差信号放大器的四周环境变化而调整所需补偿, 我们可以因应误差信号放大器的四周环境变化而调整所需补偿,这是最 容易为整个环路提供补偿的地方。此外,也有几个其他方法可以采用。 容易为整个环路提供补偿的地方。此外,也有几个其他方法可以采用。

R C2 = 1 ω P2C C3

CC3 =

1 ωZ2RFB2

C C2 =

C C1 =

ω Z2 R FB2 Cc 3 ω Z1R C1

RC1 = kRFB2

1 ω P1R C1

1-29

简单易用的电源产品

1-30

如何利用第 5 代 SIMPLE SWITCHER® 解决 这个问题?

完全无需考虑外部补偿的问题

1-27

电压模式 ─ 第 3 类 (Type III) 补偿

VOUT

ZF

CC2 CC3 CC1 RC1 RC2 VFB VREF

ZI

dB

60 40

(RFB2, Cc3)

RFB2

20 0

k

~ = Rc /RFB2

ωz 2 ~ = Rc1 /Rc2

ωP1

ωP 2

Hz

100,000 1,000,000

(Rc2, Cc3)

Buck电源设计

2011年8月

1-1

内容

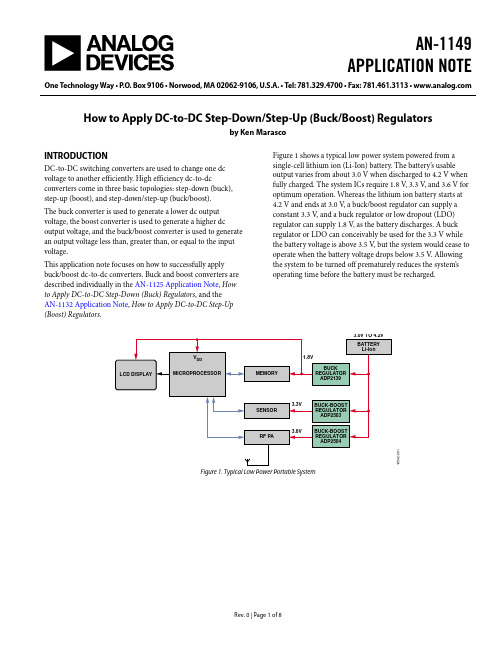

直流/直流转换器的基本原理 简单易用的电源产品

1-2

直流/直流转换器的基本原理

1-3

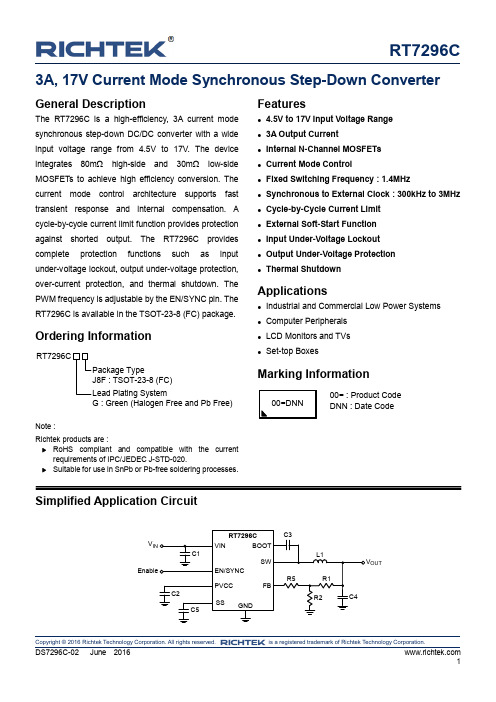

降压稳压器

控制开关 输入电容器

电感器 开关节点电压 输出电容器

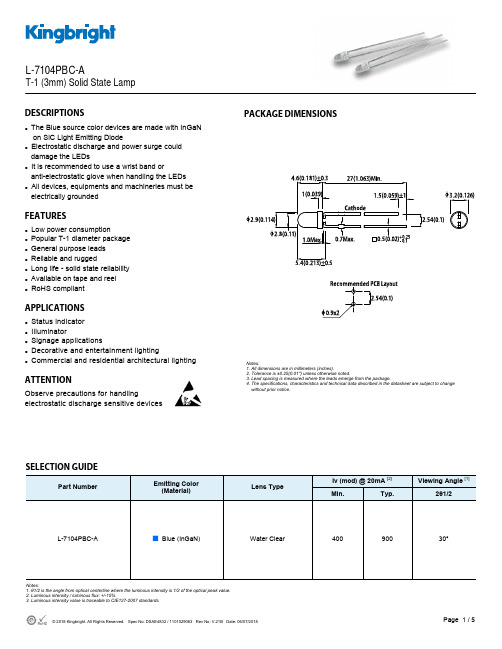

Kingbright 蓝色LED灯的数据手册说明书

Part NumberEmitting Color (Material)Lens TypeIv (mcd) @ 20mA [2] Viewing Angle [1]Min. Typ. 2θ1/2L-7104PBC-A■ Blue (InGaN)Water Clear 400 30°900DESCRIPTIONSzThe Blue source color devices are made with InGaN on SiC Light Emitting Diodez Electrostatic discharge and power surge could damage the LEDsz It is recommended to use a wrist band oranti-electrostatic glove when handling the LEDs z All devices, equipments and machineries must be electrically groundedFEATURESzLow power consumptionz Popular T-1 diameter package z General purpose leads z Reliable and ruggedz Long life - solid state reliability z Available on tape and reel z RoHS compliantAPPLICATIONSz Status indicator z Illuminatorz Signage applicationsz Decorative and entertainment lightingzCommercial and residential architectural lightingATTENTIONObserve precautions for handlingelectrostatic discharge sensitive devicesPACKAGE DIMENSIONSL-7104PBC-AT-1 (3mm) Solid State LampSELECTION GUIDENotes:1. θ1/2 is the angle from optical centerline where the luminous intensity is 1/2 of the optical peak value.2. Luminous intensity / luminous flux: +/-15%.3. Luminous intensity value is traceable to CIE127-2007 standards.Notes:1. All dimensions are in millimeters (inches).2. Tolerance is ±0.25(0.01") unless otherwise noted.3. Lead spacing is measured where the leads emerge from the package.4. The specifications, characteristics and technical data described in the datasheet are subject to change without prior notice.ABSOLUTE MAXIMUM RATINGS at T A =25°CELECTRICAL / OPTICAL CHARACTERISTICS at T A =25°CNotes:1. 1/10 Duty Cycle, 0.1ms Pulse Width.2. 2mm below package base.3. 5mm below package base.4. Relative humidity levels maintained between 40% and 60% in production area are recommended to avoid the build-up of static electricity – Ref JEDEC/JESD625-A and JEDEC/J-STD-033.Notes:1. The dominant wavelength (λd) above is the setup value of the sorting machine. (Tolerance λd : ±1nm. )2. Forward voltage: ±0.1V.3. Wavelength value is traceable to CIE127-2007 standards.4. Excess driving current and / or operating temperature higher than recommended conditions may result in severe light degradation or premature failure.ParameterSymbol Value Unit Power Dissipation P D 120 mW Reverse Voltage V R 5 V Junction Temperature T j 125 °C Operating Temperature T op -40 to +85 °C Storage Temperature T stg -40 to +85°C DC Forward Current I F 30 mA Peak Forward CurrentI FM [1]100 mA Electrostatic Discharge Threshold (HBM) -1000VLead Solder Temperature [2] 260°C For 3 Seconds Lead Solder Temperature [3]260°C For 5 SecondsParameterSymbol Emitting ColorValue Unit Typ. Max. Wavelength at Peak Emission I F = 20mA λpeak Blue 468 - nm Dominant Wavelength I F = 20mA λdom [1] Blue 465 - nm Spectral Bandwidth at 50% Φ REL MAX I F = 20mA Δλ Blue 21 - nm CapacitanceC Blue 100 - pF Forward Voltage I F = 20mA V F [2] Blue 3.2 4 V Reverse Current (V R = 5V)I RBlue-10uATECHNICAL DATABLUERECOMMENDED WAVE SOLDERING PROFILENotes:1. Recommend pre-heat temperature of 105°C or less (as measured with a thermocoupleattached to the LED pins) prior to immersion in the solder wave with a maximum solder bath temperature of 260°C2. Peak wave soldering temperature between 245°C ~ 255°C for 3 sec (5 sec max).3. Do not apply stress to the epoxy resin while the temperature is above 85°C.4. Fixtures should not incur stress on the component when mounting and during soldering process.5. SAC 305 solder alloy is recommended.6. No more than one wave soldering pass.PACKING & LABEL SPECIFICATIONSPRECAUTIONSStorage conditions1. Avoid continued exposure to the condensing moisture environment and keep the product away from rapid transitions in ambient temperature.2. LEDs should be stored with temperature ≤ 30°C and relative humidity < 60%.3. Product in the original sealed package is recommended to be assembled within 72 hours of opening. Product in opened package for more than a week should be baked for 30 (+10/-0) hours at 85 ~ 100°C.2. When soldering wires to the LED, each wire joint should be separately insulated with heat-shrink tube to prevent short-circuit contact. Do not bundle both wires in one heat shrink tube to avoid pinching the LED leads. Pinching stress on the LED leads may damage the internal structures and cause failure.3. Use stand-offs (Fig.1) or spacers (Fig.2) to securely position the LED above the PCB.4. Maintain a minimum of 3mm clearance between the base of the LED lens and the first lead bend (Fig. 3 ,Fig. 4).5. During lead forming, use tools or jigs to hold the leads securely so that the bending force will not be transmitted to the LED lens and its internal structures. Do not perform lead forming once the component has been mounted onto the PCB. (Fig. 5 )LED Mounting Method1. The lead pitch of the LED must match the pitch of the mounting holes on the PCB during component placement.Lead-forming may be required to insure the lead pitch matches the hole pitch.Refer to the figure below for proper lead forming procedures.Note 1-3: Do not route PCB trace in the contact area between the leadframe and the PCB to prevent short-circuits." ○" Correct mounting method " x " Incorrect mounting methodLead Forming Procedures1. Do not bend the leads more than twice. (Fig. 6 )2. During soldering, component covers and holders should leaveclearance to avoid placing damaging stress on the LED duringsoldering.(Fig. 7)3. The tip of the soldering iron should never touch the lens epoxy.4. Through-hole LEDs are incompatible with reflow soldering.5. If the LED will undergo multiple soldering passes or face otherprocesses where the part may be subjected to intense heat,please check with Kingbright for compatibility.PRECAUTIONARY NOTES1. The information included in this document reflects representative usage scenarios and is intended for technical reference only.2. The part number, type, and specifications mentioned in this document are subject to future change and improvement without notice. Before production usage customer should refer tothe latest datasheet for the updated specifications.3. When using the products referenced in this document, please make sure the product is being operated within the environmental and electrical limits specified in the datasheet. Ifcustomer usage exceeds the specified limits, Kingbright will not be responsible for any subsequent issues.4. The information in this document applies to typical usage in consumer electronics applications. If customer's application has special reliability requirements or have life-threateningliabilities, such as automotive or medical usage, please consult with Kingbright representative for further assistance.5. The contents and information of this document may not be reproduced or re-transmitted without permission by Kingbright.6. All design applications should refer to Kingbright application notes available at /application_notes。

Agilent 7700x 7800 ICP-MS application note说明书

Analysis of flue gas desulfurization wastewaters with the Agilent 7700x/7800 ICP-MS Application noteAuthorsRichard Burrows TestAmerica Laboratories, Inc. USASteve WilburAgilent TechnologiesUSAEnvironmentalIntroductionThe U.S. Environmental Protection Agency (US EPA) is in the processof revising effluent guidelines for the steam electric power generating industry, due to increases in wastewater discharges as a result of Phase 2 of the Clean Air Act amendments. These regulations require SO2scrubbing for most coal-fired plants resulting in ‘flue gas desulfurization’ (FGD) wastewaters. The revised effluent guidelines will apply to plants ‘primarily engaged in the generation of electricity for distribution and sale which results primarily from a process utilizing fossil-type fuel (coal, oil or gas) or nuclear fuel in conjunction with a thermal cycle employing the steam water system as the thermodynamic medium’[1]. This includes most large-scale power plants in the United States. Effluents from these plants, especially coal-fired plants, can contain several hundred to several thousand ppmof calcium, magnesium, manganese, sodium, boron, chloride, nitrate and sulfate. Measurement of low ppb levels of toxic metals (including As, Cd,Cr, Cu, Pb, Se, Tl, V and Zn) in this matrix presents a challenge for ICP-MS,Sample preparationThe samples were collected in HDPE containers and acidified with trace metal grade nitric acid to pH <2. Sample preparation was performed according to EPA 1638, Section 12.2 for total recoverable analytes by digestion with nitric and hydrochloric acid in a covered Griffin beaker on a hot plate. All calibrations wereprepared in 2% HNO 3/0.5% HCl v/v as described in the method.Analytical methodA standard Agilent 7700x ICP-MS with Micromist nebulizer and optional ISIS-DS was used. HMI aerosol dilution was set to medium, using the MassHunter ICP-MS software to automatically optimize the plasma parameters and robustness (CeO +/Ce + ratio ~0.2%). MassHunter uses HMI optimization algorithms that take into account the type of nebulizer used, to ensure reproducible conditions from run to run and from instrument to instrument. Operating parameters are shown in Table 1.Table 1. Instrument parameters used, illustrating simple, consistentHMI modeRobust plasma, medium aerosol dilutionForward RF power (W)1550Carrier gas flow (L/min)0.56Dilution gas flow (L/min)0.33Extraction lens 1 (V)0Kinetic energy discrimination (V)4Cell gas flow (mL/min) 4 (He)4 (H 2)Acquisition conditions Number of isotopes (including ISTDs)253Number of replicates 3Total acquisition time (s)80 (total for both ORS modes)ISIS parameters Sample loop volume (μL)600Online dilution factor1:2due to the very high dissolved solids levels and potential interferences from matrix-based polyatomic ions. Furthermore, FGD wastewater can vary significantly from plant to plant depending on the type and capacity of the boiler and scrubber, the type of FGD process used, and the composition of the coal, limestone and make-up water used. As a result, FGD wastewater represents the most challenging of samples for ICP-MS; it is very high in elements known to cause matrix interferences, and also highly variable. To address this difficult analytical challenge, in 2009 the EPA commissioned the development of a new ICP-MS method specifically for FGD wastewaters. This method was developed and validated at TestAmerica Laboratories, Inc. using an Agilent 7700x ICP-MS equipped with an Agilent ISIS-DS discrete sampling system.Methods and materialsInstrumentationThe Agilent 7700x ICP-MS with ISIS-DS is uniquely suited to the challenge of developing a simple, robust analytical method for the analysis of regulated metals in uncharacterized high-matrix FGD wastewaters. Three attributes of the 7700x system are particularly critical and work together to enable reliable, routine analysis of large batches of variable high-matrix samples:•Agilent’s unique High Matrix Introduction (HMI) system enables controlled, reproducible aerosol dilution, which increases plasma robustness and significantly reduces exposure of the interface and ion lenses to undissociated sample matrix.•The Octopole Reaction System (ORS 3) operating in helium collision mode eliminates matrix-based polyatomic interferences regardless of sample composition, without the need for time consuming sample-specific or analyte-specific optimization.•The optional ISIS-DS discrete sampling system significantly reduces run time, while further reducing both matrix exposure and carryover.The ORS 3 was operated in two modes: helium collision mode (He mode) for all analytes except selenium, which was measured in hydrogen reaction mode (H 2 mode). Twenty-five masses including internal standards were acquired, with typical integration times of 50 ms per replicate and three replicates per sample. Instrument detection limits (IDLs) were automatically calculated by the MassHunter software, based on the precision of the calibration blank measurement and the slope of the calibration plots (Table 2). Method detection limits (MDLs) (3σ) were calculated from 7 replicate analyses of a low-level spike of the synthetic FGD matrix solution.Cr 520.05He Sc 0.17-Mn 550.05He Sc 0.440.68Ni 600.05He Sc 0.170.45Cu 630.05He Sc 0.150.48Zn 660.05He Ge 0.94 2.04As 750.1He Ge 0.490.61Se 780.05H 2Ge 0.080.31Ag 1070.05He In 0.020.29Cd 1110.05He In 0.190.59Sb 1210.05He In 0.050.36Tl 2050.05He Ho 0.020.23Pb2080.05HeHo0.030.36* MDL calculated as 3σ of low-level spike into synthetic FGD matrix sample (n=7). MDL not calculated for chromium due to significant contamination in the synthetic FGD matrix solution. Additional isotopes were acquired for internal confirmation, but not reported.Quality controlThe quality control used for the new FGD wastewater method was based on the typical protocols used in other EPA methods. Prior to commissioning for routine operation, initial method validation requires determination of method detection limits, linear ranges, and analysis of multiple, single-element interference check solutions, to assess the effectiveness ofpolyatomic interference removal under the collision/reaction cell conditions used in the method. In routine use, daily quality control in a typical analytical sequence includes the analyses outlined in Table 3.The FGD wastewater method requires the analysis of two new QC samples: a synthetic FGD matrix sample and a fortified FGD matrix sample.Prior to preparing the synthetic FGD matrix samples, each potential matrix component was analyzed as a separate single-element standard, in order to determine the source and magnitude of any potential contaminants and the effectiveness of He mode atremoving matrix-based interferences. Results are shown in Table 4. Nearly all contaminants and interferences were sub-ppb. The most significant contaminants were Cr, Ni and Zn in the 10,000 ppm Ca solution, confirmed by measuring secondary or qualifier isotopes for the analytes. Approximately 2 ppb of V was detected in the 10% HCl solution. This was either due to contamination, a small residual interference from 35Cl 16O, or acombination of the two, but at less than 2 ppb it did not present a problem for this analysis.After each matrix component was characterized individually, a mixed synthetic FGD solution was prepared with the composition shown in Table 5, together with a second solution with the same matrix components but additionally spiked with all the analyte elements at 40 ppb. These new FGD matrix samples are analogous to the interference check solutionsICS-A and ICS-AB required by EPA method 6020, except the synthetic FGD samples are much higher in total dissolved solids (TDS) than the ICS-A and AB solutions, and contain those matrix elements that are commonly high in actual FGD samples. The detailed composition of the FGD matrix samples, which contain a total of >1% (10,000 ppm) TDS, is listed in Table 5, and results from the analysis of the synthetic FGD matrix blank and synthetic FGD matrix spike are shown in Table 6.Table 3. Typical FGD analytical sequence including all required quality control. ICV: Initial Calibration Verification, ICB: Initial Calibration Blank,CCV: Continuing Calibration Verification, CCB: Continuing Calibration Blank, LCS: Laboratory Control Sample, MS/MSD: Matrix Spike/Matrix Spike DuplicateTable 4. Initial demonstration of interference removal in single-element matrix solutions. Analyte concentrations (ppb) for each matrix (sum of analyte52 Cr0.7710.0000.17155 Mn0.0190.1370.64760 Ni 1.1150.7400.07863 Cu-0.0950.1870.17866 Zn 2.7060.160-0.12675 As0.689-0.1540.27178 Se0.0290.2130.320107 Ag0.0120.0400.002111 Cd-0.005-0.031-0.044121 Sb0.6560.0280.542205 Tl0.0620.013-0.003208 Pb0.0580.1350.037Table 5. Composition of synthetic FGD matrix sample. Laboratory fortified synthetic FGD sample is spiked with 40 ppb of each of the target elementsCalcium2000 mg/LMagnesium1000 mg/LSulfate2000 mg/LSodium1000 mg/LButanol 2 mL/LTable 6. Analysis of mixed matrix FGD interference check sample and spiked52 Cr12.699*96.6%0.01548.8510.11755 Mn-0.10194.3%-0.32848.4350.10060 Ni0.24788.4%-0.00948.5350.15463 Cu0.09491.6%0.09647.3160.11566 Zn 3.18186.1%-0.30249.8040.10075 As0.107110.0%-0.04348.2050.00978 Se0.538120.2%-0.14449.6050.186 107 Ag0.14594.3%0.01047.6320.003 111 Cd0.03998.9%-0.01748.6950.017 121 Sb0.18198.4%0.01550.8060.031 205 Tl0.02190.3%0.00048.1080.008 208 Pb0.43692.1%0.00348.3810.008* Cr contamination verified by secondary isotope.ResultsInitial performance verification indicated that the 7700x with HMI was able to analyze the very high matrix samples, and He mode successfully eliminated matrix-based spectroscopic interferences, while the use of ISIS-DS helped to minimize memory effects (Table 6). Accuracy, both in terms of calibration stability (CCV) and for spike recoveries in the matrix (spiked FGD solution), were well within the standard operating procedure (SOP) requirements (CCV ± 15%, matrix spike recoveries ± 30%).When running real FGD samples in a long sequence, continuing instrument performance must be monitored according to typical EPA criteria. Each group of 10 samples must include one laboratory control sample (LCS) of known concentration, and one matrix spike/ matrix spike duplicate (MS/MSD) pair in addition to 7 unknown samples.After each block of 10 samples, calibration and blank levels were verified through the analysis of a CCV and CCB standard (Figure 1). Additionally, internal standards were monitored for all samples and easily met the requirement to fall within 60 to 125% of the intensity measured in the calibration blank (Figure 2). Internal standard recoveries provide information on sample-specific matrix effects as well as longterm instrument drift.Figure 1. CCV recoveries over a sequence of 88 analyses including real FGD samples, all required QC samples and synthetic FGD matrix samples. Control limits (85–115%) are indicated in red.Internal standard recoveries for the 88 sample validation sequence are shown in Figure 2. All samples met the ISTD QC requirements of 60 to 125% recovery and total instrument drift over the course of the sequence was less than 10% as indicated by the ISTD response for the final CCV sample.In the complete sequence, a total of six MS/MSD pairs were analyzed and the relative percent difference (RPD) calculated for each pair is shown in Table 7. The method limit for RPD is < 20% which includes both measurement and sample preparation errors. Only silver proved to be problematic late in the sequence, most likely due to chemical stability/solubility problems in samples containing high and variable levels of chloride.Figure 2. Internal standard recoveries for entire 88 sample sequence. Control limits (60–125%) are indicated by red dashed lines.Table 7. Matrix spike (MS) and matrix spike duplicate (MSD) results and relative percent differences (RPD) for the sequence of 88 analyses. Spike concentrationwas 20 ppb except silver, which was 5 ppb.51 V21.4321.99 2.6%22.2021.85-1.6%21.3122.08 3.6%52 Cr20.0820.190.5%20.9519.55-6.7%20.4420.15-1.4%55 Mn5093.085097.500.1%5060.455121.08 1.2%5444.415340.90-1.9%60 Ni25.1720.08-20.2%19.0023.0721.4%20.5319.39-5.5%63 Cu19.2619.53 1.4%19.4518.73-3.7%19.2219.230.1%66 Zn21.4421.27-0.8%20.4721.73 6.1%21.0218.23-13.3%75 As25.7122.84-11.2%24.0724.080.0%24.1822.80-5.7%107 Ag 6.02 2.87-52.3% 5.758.3044.3% 5.22 6.0215.2%111 Cd17.6920.0613.4%17.4818.19 4.0%19.0018.71-1.5%121 Sb21.4222.69 5.9%21.6121.650.2%22.3821.82-2.5%205 Tl20.7920.45-1.7%20.4420.540.5%21.0820.53-2.6%208 Pb19.4019.62 1.1%19.4719.73 1.3%19.3019.27-0.2%ConclusionsFlue gas desulfurization (FGD) wastewater samples are extremely challenging due to their high and variable matrix composition and the fact that most of the required analytes can suffer from overlap from matrix-based polyatomic interferences. However, the new EPA method development and validation has demonstrated that these difficult sample matrices can be routinely analyzed for trace metal contaminants using the Agilent 7700x ICP-MS with optional ISIS-DS discrete sampling accessory.Based on extensive initial validation and strict ongoing EPA mandated quality control, the new method has been shown to be simple, robust, and reliable. Using the combined advantages of a highly robust plasma, HMI aerosol dilution, helium collision mode to eliminate interferences, and discrete sampling, this method has achieved performance comparable to that normally expected when analyzing much simpler samples such as waters and soil digests.References1. Technical Support Document for the Preliminary 2010 Effluent Guidelines Program Plan, 40 CFR Part 423.10, NoteResults presented in this document were obtained using the 7700x ICP-MS, but performance is also validated for the 7800 ICP-MS.Agilent shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance or use of this material.Information, descriptions, and specifications in this publication are subject to change without notice.© Agilent Technologies, Inc. 2015Published June 1, 2015Publication number: 5990-8114EN。

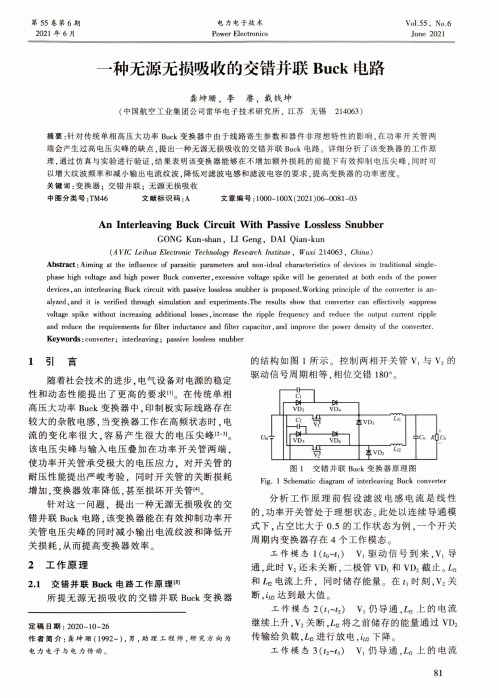

一种无源无损吸收的交错并联Buck电路

摘 要 :针 对 传 统 单 相 高 压 大 功 率 B uck 变 换 器 中 由 于 线 路 寄 生 参 数 和 器 件 非 理 想 特 性 的 影 响 ,在 功 率 开 关 管 两

端 会 产 生 过 高 电 压 尖 峰 的 缺 点 ,提 出 一 种 无 源 无 损 吸 收 的 交 错 并 联 B u c k 电 路 。详 细 分 析 了 该 变 换 器 的 工 作 原

分析工作原理前假设滤波电感电流是线性 的 ,功率开关管处于理想状态。此处以连续导通模 式 下 ,占空比 大 于0 . 5 的工作状态为例, 一 个开关 周期内变换器存在4 个工作模态。

工 作 模 态 V , 驱 动 信 号 到 来 ,V ,导 通 ,此 时 % 还 未 关 断 ,二 极 管 丫 0,和 V D 2截止 。Ln 和 电 流 上 升 ,同时储存能量。在 时 刻 ,乂2 关 断 ,k 达到最大值。

电力电子技术 Power Electronics

Vol.55, No.6 June 2021

继续 上 升,此 时 v 2 驱 动信号 到来,v 2 导通,L 储 存能量的同时电流上升。

工作 模 态 4(t3~f4) V , 关 断 ,电 感 电 流 。 通 过 V D ,传输给负载,Ln 放电,电流下降,% 仍 导 通 ,

由 图 3a 可 以 看 出 ,当变换器不加吸收电路

时 ,关断瞬间功率开关管承受一个极大的电压尖 峰 ,达 到 667.4 V ,在实际工作中极有可能损坏开 关 管 ,因此在设计过程中必须考虑增加吸收电路。

S G 3 5 2 5 输 出 的 驱 动 信 号 经 过 延 时 模 块 后 ,占 空比相等,与原驱动信号 交错 180°,如 图 3b 所示。 图 3c 为 其 中 一 个 M 0 S F E T 漏源电压与驱动信号

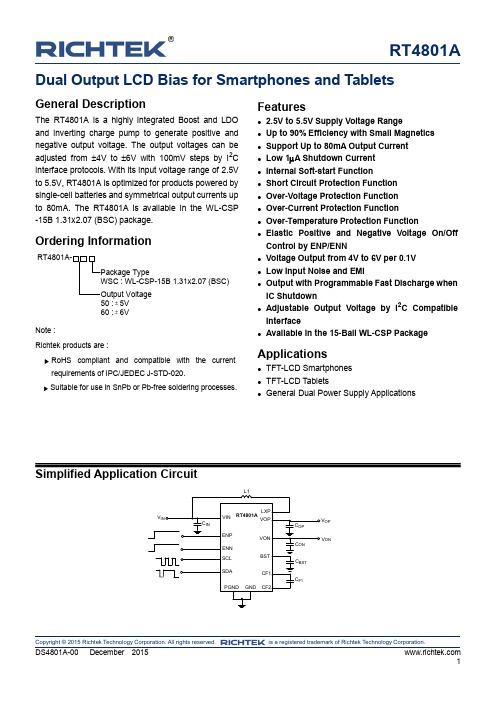

Richtek RT4801A 双输出LCD偏置电源说明书

RT4801ACopyright © 2015 Richtek Technology Corporation. All rights reserved. is a registered trademark of Richtek Technology Corporation.DS4801A-00 December 2015Dual Output LCD Bias for Smartphones and TabletsGeneral DescriptionThe RT4801A is a highly integrated Boost and LDO and inverting charge pump to generate positive and negative output voltage. The output voltages can be adjusted from ±4V to ±6V with 100mV steps by I 2C interface protocols. With its input voltage range of 2.5V to 5.5V, RT4801A is optimized for products powered by single-cell batteries and symmetrical output currents up to 80mA. The RT4801A is available in the WL-CSP -15B 1.31x2.07 (BSC) package.Ordering Information50 : 5V 60 : 6V±±Note :Richtek products are :④ RoHScompliant and compatible with the currentrequirements of IPC/JEDEC J-STD-020.④ Suitable for use in SnPb or Pb-free soldering processes.Features● 2.5V to 5.5V Supply Voltage Range● Up to 90% Efficiency with Small Magnetics ● Support Up to 80mA Output Current ● Low 1μA Shutdown Current ● Internal Soft-start Function● Short Circuit Protection Function ● Over-Voltage Protection Function ● Over-Current Protection Function● Over-Temperature Protection Function●Elastic Positive and Negative Voltage On/Off Control by ENP/ENN● Voltage Output from 4V to 6V per 0.1V● Low Input Noise and EMI●Output with Programmable Fast Discharge when IC Shutdown●Adjustable Output Voltage by I 2C Compatible Interface●Available in the 15-Ball WL-CSP PackageApplications● TFT-LCD Smartphones● TFT-LCD Tablets●General Dual Power Supply ApplicationsSimplified Application CircuitOP ONRT4801APin Configurations(TOP VIEW)VIN PGNDCF1BST VOPLXP VONGNDBSTENN CF2PGND ENPSCLSDAC1C2C3D3D1E1E2E3D2A1A2A3B3B1B2WL-SP-15B 1.31x2.07 (BSC)Marking Information3B : Product Code W : Date Code.Functional Pin DescriptionRT4801AFunction Block DiagramVOPCF2GNDVONCF1OperationThe RT4801A is a highly integrated Boost, LDO and inverting charge pump to generate positive and negative output voltages for LCD panel bias or consumer products. It can support input voltage range from 2.5V to 5.5V and the output current up to 80mA. Both positive and negative voltages can be programmed by a MCU through the dedicated I 2C interface. The RT4801A provides Over-Temperature Protection (OTP) and Short Circuit Protection (SCP) mechanisms to prevent the device from damage with abnormal operations. When the EN voltage is logic low for more than 375μs, the IC will be shut down with low input supply current less than 1μA.RT4801AAbsolute Maximum Ratings (Note 1)•Supply Input Voltage V IN Pin --------------------------------------------------------------------------------------- -0.3V to 6V●Output Voltage VOP Pins -------------------------------------------------------------------------------------------- -0.3V to 7V●Output Voltage VON Pins ------------------------------------------------------------------------------------------- -7V to 0.3V●Others Pin to GND ---------------------------------------------------------------------------------------------------- -0.3V to 6V●Power Dissipation, P D @ T A = 25°CWL-CSP-15B 1.31x2.07 (BSC) ----------------------------------------------------------------------------------- 2W●Package Thermal Resistance (Note 2)WL-CSP-15B 1.31x2.07 (BSC), θJA----------------------------------------------------------------------------- 49.8°C/W●Lead Temperature (Soldering, 10 sec.) ------------------------------------------------------------------------- 260︒C●Junction Temperature ----------------------------------------------------------------------------------------------- 150︒C●Storage Temperature Range -------------------------------------------------------------------------------------- -65︒C to 150︒C ●ESD Susceptibility (Note 3)HBM (Human Body Model) ---------------------------------------------------------------------------------------- 2kVMM (Machine Model) ----------------------------------------------------------------------------------------------- 200V Recommended Operating Conditions (Note 4)●Supply Input Voltage ------------------------------------------------------------------------------------------------- 2.5V to 5.5V●Ambient Temperature Range--------------------------------------------------------------------------------------- -40︒C to 85︒C ●Junction Temperature Range -------------------------------------------------------------------------------------- -40︒C to 125︒C Electrical Characteristics(V IN = 3.7V, C IN= C OP = C F1 = 4.7μF, C BST = C ON = 10μF, L1 = 2.2μH, T A = 25°C, unless otherwise specified.)Copyright © 2015 Richtek Technology Corporation. All rights reserved. is a registered trademark of Richtek Technology Corporation.DS4801A-00 December 2015RT4801ACopyright © 2015 Richtek Technology Corporation. All rights reserved. is a registered trademark of Richtek Technology Corporation.Note 1. Stresses beyond those listed “Absolute Maximum Ratings” may cause permanent damage to the device. These arestress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability. Note 2. θJA is measured at T A = 25︒C on a high effective thermal conductivity four-layer test board per JEDEC 51-7. Note 3. Devices are ESD sensitive. Handling precaution recommended. Note 4. The device is not guaranteed to function outside its operating conditions. Note 5. T OTP , T OTP_HYST are guaranteed by design.RT4801ACopyright © 2015 Richtek Technology Corporation. All rights reserved. is a registered trademark of Richtek Technology Corporation.DS4801A-00 December 2015Typical Application CircuitL1V OPV ONTable 1. Component List of Evaluation BoardRT4801ACopyright © 2015 Richtek Technology Corporation. All rights reserved. is a registered trademark of Richtek Technology Corporation.I 2C InterfaceSDASCL VV V VRT4801ACopyright © 2015 Richtek Technology Corporation. All rights reserved. is a registered trademark of Richtek Technology Corporation.DS4801A-00 December 2015I 2C CommandSlave AddressWrite Command(a) Write single byte of data to Register11111Slave ACK Slave AddressRegister AddressR7R6R3R5R4R2R1R0Slave ACKData From MasterStartSlave ACK StopD7D6D5D4D3D2D1D0(b) Write multiple bytes of data to Registers111110Slave ACK Slave AddressRegister Address n thSlave ACK n th Data From MasterStartD7D6D5D4D3D2D1D0SlaveACKSlave ACKStop(n + 1)th Data From MasterLast Data From MasterR7R6R3R5R4R2R1R0D7D6D5D4D3D2D1D0Slave ACK D7D6D5D4D3D2D1D0Read Command(a) Read single byte of data from Register111110Slave ACK Slave AddressRegister Address111111Slave ACK Slave AddressData From MasterRe-startStartSlaveACKD7D6D5D4D3D2D1D0Master NACKStop D7D6D5D4D3D2D1D0(b) Read multiple bytes of data from Registers11111Slave ACK 0111111Slave ACK Slave Addressn th Data From MasterMaster ACKRe-startStart Slave AddressRegister AddressMaster NACKStopLast Data From MasterD7D6D5D4D3D2D1D0Slave ACKD7D6D5D4D3D2D1D0D7D6D5D4D3D2D1D0Start : Start command R7 to R0 : Register Address. VOP : Register address = 0X00h VON : Register address = 0X01h DISP : Register address = 0x03h DISN : Register address = 0x03hR/W : Read active (R/W = H) or Write active (R/W = L)ACK : Acknowledge = L activeD7 to D0 : Write data when WRITE command or read data when READ command Stop : Stop commandRT4801ACopyright © 2015 Richtek Technology Corporation. All rights reserved. is a registered trademark of Richtek Technology Corporation.Registers MapTable 3. VON Voltage SelectionCopyright © 2015 Richtek Technology Corporation. All rights reserved. is a registered trademark of Richtek Technology Corporation.DS4801A-00 December 201511The Reserved bits are ignored when written and return either 0 or 1 when read.The Reserved bits are ignored when written and return either 0 or 1 when read.Factory Default Register ValueRT4801A-50WSC default VOP/VON DATA is 0Ah/0Ah. RT4801A-60WSC default VOPN/VON DATA is 14h/14h.Copyright © 2015 Richtek Technology Corporation. All rights reserved. is a registered trademark of Richtek Technology Corporation. DS4801A-00 December 201512Typical Operating CharacteristicsEfficiency vs. Output Current010203040506070809010000.020.040.060.08Output Current (A)E f f i c i e n c y (%)V OP vs. Output Current4.974.984.995.005.015.020.010.020.030.040.050.060.070.08Output Current (A)V O P(V )V ON vs. Output Current-5.02-5.01-5.00-4.99-4.98-4.970.010.020.030.040.050.060.070.08Output Current (A)V O N (V )V OP vs. Input Voltage4.974.984.995.005.015.02V O P (V )V ON vs. Input Voltage-5.02-5.01-5.00-4.99-4.98-4.972.533.544.555.5Input Voltage (V)V O N (V )0.000.020.040.060.080.100.120.140.160.180.20-40-2020406080100Temperature (°C)S h u t d o w n C u r r e n t (μA )Copyright © 2015 Richtek Technology Corporation. All rights reserved. is a registered trademark of Richtek Technology Corporation.DS4801A-00 December 201513Quiescent Current vs. Temperature0.40.50.60.70.80.91.01.11.2-40-2020406080100Temperature (°C)Q u i e s c e n t C u r r e n t (m A )Input Voltage vs. Temperature2.102.122.142.162.182.202.222.242.262.282.30-40-2020406080100Temperature (°C)I n p u t V o l t a g e (V )V IN = 3.7V, V OP = 5V, I OP = 0mA V OP (10mV/Div)Time (1ms/Div)V OP Ripple Voltage V OP(10mV/Div)Time (1ms/Div)V OP Ripple VoltageV IN = 3.7V, V OP = 5V, I OP = 20mAV OP(10mV/Div)Time (1ms/Div)V OP Ripple Voltage V IN = 3.7V, V OP = 5V, I OP = 40mA V OP (10mV/Div)Time (1ms/Div)V OP Ripple VoltageV IN = 3.7V, V OP = 5V, I OP = 80mACopyright © 2015 Richtek Technology Corporation. All rights reserved. is a registered trademark of Richtek Technology Corporation. DS4801A-00 December 201514V ON (20mV/Div)Time (1ms/Div)V ON Ripple VoltageV IN = 3.7V, V ON = 5V, I ON = 0mA V ON (20mV/Div)Time (10μs/Div)V ON Ripple VoltageV IN = 3.7V, V ON = 5V, I ON = 20mAV ON (20mV/Div)Time (10μs/Div)V ON Ripple Voltage V IN = 3.7V, V ON = 5V, I ON = 40mA V ON (20mV/Div)Time (10μs/Div)V ON Ripple VoltageV IN = 3.7V, V ON = 5V, I ON = 80mAV IN = 2.9V, V OP = 5V, V ON = -5V, T R = T F = 10μs, I OPN = 5m to 35mAV OP (50mV/Div)V ON (50mV/Div)I OP(20mA/Div)Time (100μs/Div)Load TransientV IN = 2.9V, V OP = 5V, V ON = -5V, T R = T F = 10μs, I OPN = 10m to 70mAV OP (50mV/Div)V ON (50mV/Div)I OP(50mA/Div)Time (100μs/Div)Load TransientCopyright © 2015 Richtek Technology Corporation. All rights reserved. is a registered trademark of Richtek Technology Corporation.DS4801A-00 December 201515V IN = 3.7V, V OP = 5V, V ON = -5V, T R = T F = 10μs, I OPN = 5m to 35mAV OP (50mV/Div)V ON (50mV/Div)I OP(20mA/Div)Time (100μs/Div)Load TransientV IN = 3.7V, V OP = 5V, V ON = -5V, T R = T F = 10μs, I OPN = 10m to 70mAV OP (50mV/Div)V ON (50mV/Div)I OP(50mA/Div)Time (100μs/Div)Load TransientV IN = 4.5V, V OP = 5V, V ON = -5V, T R = T F = 10μs, I OPN = 5m to 35mAV OP (50mV/Div)V ON (50mV/Div)I OP(20mA/Div)Time (100μs/Div)Load TransientV IN = 4.5V, V OP = 5V, V ON = -5V, T R = T F = 10μs, I OPN = 10m to 70mAV OP (50mV/Div)V ON (50mV/Div)I OP(50mA/Div)Time (100μs/Div)Load TransientV IN = 2.9V to 3.4V, V OP = 5V,V ON = -5V, I OPN = 5mAV IN (1V/Div)V OP (50mV/Div)V ON (50mV/Div)Time (500μs/Div)Line TransientV INV IN = 3.7V to 4.2V, V OP = 5V,V ON = -5V, I OPN = 5mAV OP (50mV/Div)V IN (1V/Div)V ON (50mV/Div)Time (500μs/Div)Line TransientV INCopyright © 2015 Richtek Technology Corporation. All rights reserved. is a registered trademark of Richtek Technology Corporation. DS4801A-00 December 201516V IN = 2.9V to 3.4V, V OP = 5V,V ON = -5V, I OPN = 40mAV OP (50mV/Div)V IN (1V/Div)V ON (50mV/Div)Time (500μs/Div)Line TransientV INV IN = 3.7V to 4.2V, V OP = 5V,V ON = -5V, I OPN = 40mAV OP (50mV/Div)V IN (1V/Div)V ON (50mV/Div)Time (500μs/Div)Line TransientV INV IN = 2.9V to 3.4V, V OP = 5V,V ON = -5V, I OPN = 80mAV OP (50mV/Div)V IN (1V/Div)V ON (50mV/Div)Time (500μs/Div)Line TransientV INV IN = 3.7V to 4.2V, V OP = 5V,V ON = -5V, I OPN = 80mAV OP (50mV/Div)V IN (1V/Div)V ON (50mV/Div)Time (500μs/Div)Line TransientV INV IN = 3.7V, V OP = 5V, V ON = -5V, No Load, ENP/ENN On simultaneouslyENP (5V/Div)ENN (5V/Div)(5V/Div)I IN(200mA/Div)Time (1ms/Div)Power OnV OP V ONV IN = 3.7V, V OP = 5V, V ON = -5V, No Load, ENP/ENN Off simultaneouslyENP (5V/Div)ENN (5V/Div)(5V/Div)I IN(200mA/Div)Time (1ms/Div)Power OffV OPV ONCopyright © 2015 Richtek Technology Corporation. All rights reserved. is a registered trademark of Richtek Technology Corporation.DS4801A-00 December 201517V IN = 3.7V, V OP = 5V, V ON = -5V,No Load, ENP prior ENN OnENP (5V/Div)ENN (5V/Div)(5V/Div)I IN(200mA/Div)Time (1ms/Div)Power OnV OP V ONV IN = 3.7V, V OP = 5V, V ON = -5V,No Load, ENP prior ENN OffENP (5V/Div)ENN (5V/Div)(5V/Div)I IN(200mA/Div)Time (1ms/Div)Power OffV OP V ONV IN = 3.7V, V OP = 5V, V ON = -5V,No Load, ENN prior ENP OnENP (5V/Div)ENN (5V/Div)(5V/Div)I IN(200mA/Div)Time (1ms/Div)Power OnV OPV ONV IN = 3.7V, V OP = 5V, V ON = -5V,No Load, ENN prior ENP OffENP (5V/Div)ENN (5V/Div)(5V/Div)I IN(200mA/Div)Time (1ms/Div)Power OffV OPV ONCopyright © 2015 Richtek Technology Corporation. All rights reserved. is a registered trademark of Richtek Technology Corporation. DS4801A-00 December 201518Application InformationThe RT4801A is a highly integrated Boost, LDO and inverting charge pump to generate positive and negative output voltages for LCD panel bias or consumer products. It can support input voltage range from 2.5V to 5.5V and the output current up to 80mA. The V OP positive output voltage is generated from the LDO supplied from a synchronous Boost converter, and V OP is set at a typical value of 6V. The Boost converter output also drives an inverting charge pump controller to generate V ON negative output voltage which is set at a typical value of -6V. Both positive and negative voltages can be programmed by a MCU through the dedicated I 2C interface and the available voltage range is from ±4V to ±6V with 100mV per step. Input Capacitor SelectionInput ceramic capacitor with 4.7μF capacitance is suggested for applications. For better voltage filtering, select ceramic capacitors with low ESR, X5R and X7R types are suitable because of their wider voltage and temperature ranges. Boost Inductor SelectionThe inductance depends on the maximum input current. As a general rule, the inductor ripple current range is 20% to 40% of the maximum input current. If 40% is selected as an example, the inductor ripple current can be calculated according to the following equations :OUT OUT(MAX)IN(MAX)IN RIPPLE IN(MAX)V I I =V I = 0.4I η⨯⨯⨯w here η is the efficiency of the VOP Boost converter, I IN(MAX) is the maximum input current, and ∆I L is the inductor ripple current. The input peak current can then be obtained by adding the maximum input current with half of the inductor ripple current as shown in the following equation : I PEAK = 1.2 x I IN(MAX)Note that the saturated current of the inductor must be greater than I PEAK .The inductance can eventually be determined according to the following equation :()()()22IN OUT IN OUT OUT(MAX)OSCηV V V L 0.4V I f ⨯⨯-=⨯⨯⨯where f OSC is the switching frequency. For better system performance, a shielded inductor is preferred to avoid EMI problems.Boost Output Capacitor SelectionThe output ripple voltage is an important index for estimating IC performance. This portion consists of two parts. One is the product of ripple current with the ESR of the output capacitor, while the other part is formed by the charging and discharging process of the output capacitor. As shown in Figure 1, ∆V OUT1 can be evaluated based on the ideal energy equalization. According to the definition of Q, the ∆V OUT1 value can be calculated as the following equation :OUT OUT OUT1SOC OUT OUT1SOC OUT1Q = I D = CV f I DV =f C ⨯⨯⨯∆⨯∆⨯where f OSC is the switching frequency and D is the duty cycle.Finally, taking ESR into consideration, the overall output ripple voltage can be determined by the following equation :OUT OUT ESR OUT1SER OSC OUTI DV = V + V = V + f C ⨯∆∆∆∆⨯where ∆V ESR = I Crms x R CESRThe output capacitor, C OUT , should be selected accordingly.Copyright © 2015 Richtek Technology Corporation. All rights reserved. is a registered trademark of Richtek Technology Corporation.DS4801A-00 December 201519Figure 1. The Output Ripple Voltage without theContribution of ESRUnder Voltage LockoutTo prevent abnormal operation of the IC in low voltage condition, an under voltage lockout is included which shuts down IC operation when input voltage is lower than the specified threshold voltage. Soft-StartThe RT4801A employs an internal soft-start feature to avoid high inrush current during start-up. The soft-start function is achieved by clamping the output voltage of the internal error amplifier with another voltage source that is increased slowly from zero to near VIN during the soft-start period. Output Voltage SettingThe output voltage can be programmed by a MCU through the dedicated I 2C interface according to the V OP /V ON Voltage Selection Table. Shutdown Delay and DischargeWhen the EN signal is logic low for more than 375μs, the IC function will be shut down. The output V OP /V ON can be actively discharged to GND via discharge selection bit enabled. In shutdown mode, the input supply current for the IC is less than 1μA.Over Current ProtectionThe RT4801A includes a cycle-by-cycle current limit function which monitors the inductor current during each ON period. The power switch will be forced off to avoid large current damage once the current is over the limit level.Short Circuit ProtectionThe RT4801A has an advanced output short-circuit protection mechanism which prevents the IC from damage by unexpected applications. When the output becomes shorted to ground, and the output voltage is under the limit level with 1ms (typ.) duration, the LCD bias function enters shutdown mode and can only re-start normal operation after triggering the ENP/ENN pin.Over Temperature ProtectionThe RT4801A equips an over temperature protection circuitry to prevent overheating due to excessive power dissipation. The OTP will shut down LCD bias operation when ambient temperature exceeds 140°C. Once the ambient temperature cools down by approximately 15°C, IC will automatically resume normal operation. To maintain continuous operation, the maximum junction temperature should be prevented from rising above 125°C.Thermal ConsiderationsFor continuous operation, do not exceed absolute maximum junction temperature. The maximum power dissipation depends on the thermal resistance of the IC package, PCB layout, rate of surrounding airflow, and difference between junction and ambient temperature. The maximum power dissipation can be calculated by the following formula : P D(MAX) = (T J(MAX) - T A ) / θJAwhere T J(MAX) is the maximum junction temperature, T A is the ambient temperature, and θJA is the junction to ambient thermal resistance.For recommended operating condition specifications, the maximum junction temperature is 125︒C. The junction to ambient thermal resistance, θJA , is layout dependent. For WL-CSP-15B 1.31x2.07 (BSC) package, the thermal resistance, θJA , is 49.8︒C/W on a standard JEDEC 51-7 four-layer thermal test board.Copyright © 2015 Richtek Technology Corporation. All rights reserved. is a registered trademark of Richtek Technology Corporation. DS4801A-00 December 201520The maximum power dissipation at T A = 25︒C can be calculated by the following formula :P D(MAX) = (125︒C - 25︒C) / (49.8︒C/W) = 2W for WL-CSP-15B 1.31x2.07 (BSC) packageThe maximum power dissipation depends on the operating ambient temperature for fixed T J(MAX) and thermal resistance, θJA . The derating curve in Figure 2 allows the designer to see the effect of rising ambient temperature on the maximum power dissipation.Figure 2. Derating Curve of Maximum PowerDissipationLayout ConsiderationsFor the best performance of RT4801A, the followingPCB layout guidelines should be strictly followed. ④ For good regulation, place the power components asclose to the IC as possible. The traces should be wide and short especially for the high current output loop.④ Theinput and output bypass capacitor should beplaced as close to the IC as possible and connected to the ground plane of the PCB.④ The flying capacitor should be placed as close to theCF1/CF2 pin as possible to avoid noise injection.④ Minimizethe size of the LXP node and keep thetraces wide and short. Care should be taken to avoid running traces that carry any noise-sensitive signals near LXP or high-current traces.④ Separate power ground (PGND) and analog ground(GND). Connect the GND and the PGND islands at a single end. Make sure that there are no other connections between these separate ground planes.Figure 3. PCB Layout Guide0.00.40.81.21.62.02.4255075100125Ambient Temperature (°C)M a x i m u m P o w e r D i s s i p a t i o n (W )RT4801ACopyright © 2015 Richtek Technology Corporation. All rights reserved. is a registered trademark of Richtek Technology Corporation.DS4801A-00 December 201521Outline DimensionWL-CSP-15B 1.31x2.07 (BSC)Richtek Technology Corporation14F, No. 8, Tai Yuen 1st Street, Chupei City Hsinchu, Taiwan, R.O.C. Tel: (8863)5526789Richtek products are sold by description only. Richtek reserves the right to change the circuitry and/or specifications without notice at any time. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.。

(重点)Emulated Current Mode Control for Buck Regulators Using Sample and Hold Technique

LM3495Emulated Current Mode Control for Buck Regulators Using Sample and Hold TechniqueLiterature Number: SNVA537EMULATED CURRENT MODE CONTROL FOR BUCK REGULATORS USING SAMPLE AND HOLD TECHNIQUE Small Signal Linear Analysis and Comparison to Peak and ValleyMethodsbyRobert SheehanPrincipal Applications EngineerNational Semiconductor CorporationSanta Clara, CAPES02Tuesday, October 24, 20068:30am – 9:30amPower Electronics Technology Exhibition and ConferenceOctober 24-26, 2006Long Beach Convention CenterLong Beach, CAEMULATED CURRENT MODE CONTROL FOR BUCK REGULATORS USINGSAMPLE AND HOLD TECHNIQUESmall Signal Linear Analysis and Comparison to Peak and Valley MethodsbyRobert SheehanPrincipal Applications EngineerNational Semiconductor CorporationSanta Clara, CAAbstract – While naturally sampled peak and valley current mode control methods have been widely used, other control architectures are possible using gated sampling techniques. Theory for an emulated peak current mode control method using a gated sample and hold of the valley current is developed. This gated sampling technique removes the duty cycle dependence of the slope compensating ramp, stabilizing the modulator gain over changes in line voltage. A general solution for current mode buck regulator small signal linear equations is presented. This allows the modulator gain for any control method to be introduced into the equations, including peak, valley, average and gated sampling methods. Comparison to peak and valley is made using switching, linear and LaPlace spice models. Sub-harmonic stability bounds are demonstrated using graphical spreadsheet calculators. Theory is verified with frequency response measurements of an actual circuit.Figure 1: Naturally sampled peak or valley current mode buck regulator.Figure 2: Emulated peak current mode buck regulator using valley sample and hold.1. IntroductionThere are a lot of misconceptions and misinformation about current mode control in the industry. Papers that have been written at the graduate or PhD level are hard to understand. Concepts are difficult to put into practical use. Basically, an ideal current mode converter is only dependent on the dc or average inductor current. The inner current loop turns the inductor into a voltage controlled current source, effectively removing the inductor from the outer voltage control loop at dc and low frequencies. The current loop gain splits the complex conjugate pole of the output filter into two real poles, so that the characteristic of the output filter is set by the capacitor and load resistor. Only when the impedance of the output inductor equals the current loop gain does the inductor pole reappear at higher frequencies.Whether the current mode converter is peak, valley, average, or sample and hold is secondary to the operation of the current loop. As long as the dc current is sampled, current mode operation is maintained. The modulator gain is dependent on the effective slope of the ramp presented to the modulating comparator input. Each operating mode will have a unique characteristic equation for the modulator gain. The requirement for slope compensation is dependent on the relationship of the average current to the value of current at the time when the sample is taken.To understand the theory and follow the derivations presented in this paper, a good working knowledge of the references is needed. For the practical designer, simplified transfer functions along with tabulated general gain parameters provide the basic tools for design analysis.The primary application for emulated current mode is high input voltage to low output voltage operating at a narrow duty cycle. In any practical design, device capacitance may cause a significant leading edge spike on the current sense waveform. By sampling the inductor current at the end of the switching cycle and adding an external ramp, the minimum on time can be significantly reduced, without the need for blanking or filtering which is normally required for peak current mode control.2. Linear ModelingFigure 3: Buck regulator linear models.Averaged ModelReference [1] has been one of the most popular papers covering current mode control. The analysis presented here refers the inductor current to the control voltage as the basis for writing the transfer functions.Starting with , write the transfer function in terms of voltages: O vˆLO OSW O Z Z Z v ˆvˆ+⋅= (1)d ˆV D v ˆv ˆIN IN SW ⋅+⋅= (2))K v ˆK v ˆR i ˆv ˆ(F d ˆO O I IN i L C m⋅+⋅−⋅−⋅= (3)OO L Z v ˆi ˆ= (4)Combining equations 1 through 4 yields:L O O O O I IN O i O C m IN IN O Z Z Z K v ˆK v ˆZ R v ˆv ˆF V D v ˆv ˆ+⋅⎥⎥⎦⎤⎢⎢⎣⎡⎟⎟⎠⎞⎜⎜⎝⎛⋅+⋅−⋅−⋅⋅+⋅= (5)Define K mp as:m IN mp F V K ⋅= (6)Setting to zero allows the control to output gain to be found: IN vˆ)Z K R (K Z Z Z K v ˆvˆO O i mp L O O mp C O ⋅−⋅++⋅=(7)Setting to zero allows the line to output gain to be found: C vˆ)Z K R (K Z Z Z )K K D (v ˆvˆO O i mp L O O I mp IN O ⋅−⋅++⋅⋅−=(8)Define Z O and Z L :)R R (C s 1)R C s 1(R R ||R C s 1Z C O O C O O O C O O +⋅⋅+⋅⋅+⋅=⎟⎟⎠⎞⎜⎜⎝⎛+⋅= (9)S L L R R L s Z ++⋅=(10)Equations 7 and 8 can be plotted without further analysis using MATHCAD, SPICE or other application. Define terms for: K mp Modulator gain coefficient K I Line to modulator gain block K O Output to modulator gain block R i Current sense amplifier gain = G I · R SDC Transfer FunctionsControl to OutputLet Z O =R O , Z L =R L +R S . From equation 7:)R K R (K R R R R K )dc (v ˆvˆO O i mp S L O O mp C O ⋅−⋅+++⋅=(11)By factoring this becomes:imp O mp O i mp SL iO C O R K K K 1R R K R R 11R R )dc (v ˆv ˆ⋅⋅−⋅+⋅++⋅= (12)Define K m as the modulator gain where:Ompm K K 11K −=(13)This allows the control to output gain to be expressed as:im O i mp S L iO C O R K R R K R R 11R R )dc (v ˆv ˆ⋅+⋅++⋅= (14)If R O >>R L +R S the simplified expression is:im O iO C O R K R 11R R )dc (v ˆv ˆ⋅+⋅≈(15)Line to OutputIn similar fashion:)R K R (K R R R R )K K D ()dc (v ˆvˆO O i mp S L O O I mp IN O ⋅−⋅+++⋅⋅−=(16)By factoring this becomes:imp O mp O i mp SL Imp iO IN O R K K K 1R R K R R 1DK K 1R DR )dc (v ˆv ˆ⋅⋅−⋅+⋅++−⋅⋅= (17)Define K n as the audio susceptibility coefficient:DK K 1K I mp n −=(18)This allows the line to output gain to be expressed as:im O i mp S L niO IN O R K R R K R R 1K R D R )dc (v ˆv ˆ⋅+⋅++⋅⋅= (19)If R O >>R L +R S the simplified expression is:im O niO IN O R K R 1K R D R )dc (v ˆv ˆ⋅+⋅⋅≈ (20)Continuous-Time ModelReferences [2] and [3] cover this model. The sampling gain is incorporated into the current loop as H e (s). Derivation of the gain blocks for the on voltage and off voltage requires differentiation of the inductor current with respect to each voltage. Here, a straightforward algebraic method is used to relate the continuous-time model to the averaged model. This provides a simple means to derive the equations for different control modes.Starting with , write the transfer function in terms of voltages: dˆ)K vˆK v ˆ)s (H R i ˆv ˆ(F d ˆr OFF f ON e i L C m ′⋅+′⋅+⋅⋅−⋅′= (21)Combining with equations 1, 2 and 4 for the power stage yields:L O O r OFF f ON O e i O C m IN IN O Z Z Z K v ˆK v ˆZ )s (H R v ˆv ˆF V D v ˆv ˆ+⋅⎥⎥⎦⎤⎢⎢⎣⎡⎟⎟⎠⎞⎜⎜⎝⎛′⋅+′⋅+⋅⋅−⋅′⋅+⋅= (22)Define K ′mp as:m IN mp F V K ′⋅=′ (23)Let , , Z O IN ON v ˆv ˆv ˆ−=O OFF v ˆv ˆ=O =R O , Z L =0, H e (s)=1. Solve for the dc gain equation.⎥⎥⎦⎤⎢⎢⎣⎡⎟⎟⎠⎞⎜⎜⎝⎛′⋅+′⋅−′⋅+⋅−⋅′+⋅≈r O f O f IN O iO C mp IN O K v ˆK v ˆK v ˆR R v ˆv ˆK D v ˆ)dc (v ˆ (24)Setting to zero allows the control to output gain to be found: IN vˆi mp rmp f mp O i O C O R K K K K K 1R 11R R )dc (v ˆv ˆ⋅′′⋅′−′⋅′+⋅+⋅≈(25)Setting to zero allows the line to output gain to be found: C vˆimp rmp f mp O fmp i OIN O R K K K K K 1R 1D K K 1R DR )dc (v ˆv ˆ⋅′′⋅′−′⋅′+⋅+′+′⋅⋅≈ (26)Define K ′m and K ′n where:rf mp m K K K 11K ′−′+′=′ D K K 1K f mp n ′+′=′ (27)Equate K m to K ′m and K n to K ′n . Solve for K ′f and K ′r .I mp mp f K K 1K 1D K −⎟⎟⎠⎞⎜⎜⎝⎛′−⋅=′ O f mpmp r K K K 1K 1K +′+−′=′ (28)Figure 4: Simplified continuous-time model using general gain parameters. This model is valid for control to output transfer functions of all operating modes. The line to output transfer function is valid at dc, but diverges from theactual response over frequency.⎟⎟⎠⎞⎜⎜⎝⎛−′⋅+=m mp i L e K 1K 1R Z )s (H )s (H (29) Where:2n 2z n e ωs Q ωs 1)s (H +⋅+= T πωn = π2Q z−= (30)Unified ModelThe unified model is presented in references [4] and [5]. This uses a single pole in series with the modulator to account for the sampling gain.Starting with , write the transfer function in terms of voltages: dˆ)K v ˆR i ˆv ˆ()s (F d ˆIN i L C m⋅−⋅−⋅= (31)Combining with equations 1, 2 and 4 for the power stage yields:L O O IN O i O C m IN IN O Z Z Z K v ˆZ Rv ˆv ˆ)s (F V D v ˆv ˆ+⋅⎥⎥⎦⎤⎢⎢⎣⎡⎟⎟⎠⎞⎜⎜⎝⎛⋅−⋅−⋅⋅+⋅= (32)Define:)s (H K )s (F V p m m IN ⋅=⋅ (33)Let Z O =R O , Z L =0, H p (s)=1. Solve for the dc gain equation.⎥⎥⎦⎤⎢⎢⎣⎡⎟⎟⎠⎞⎜⎜⎝⎛⋅−⋅−⋅+⋅≈K v ˆR R v ˆv ˆK D v ˆ)dc (v ˆIN O iO C m IN O (34)Setting to zero allows the control to output gain to be found: IN vˆim O iO C O R K R 11R R )dc (v ˆv ˆ⋅+⋅≈(35)Setting to zero allows the line to output gain to be found: C vˆim O m iO IN O R K R 1DK K 1R D R )dc (v ˆv ˆ⋅+−⋅⋅≈ (36)Comparing this to the averaged and continuous-time models:D KK 1K m n −= Therefore: ⎟⎟⎠⎞⎜⎜⎝⎛−⋅=n m K K 1D K (37)Figure 5: Unified model uses the high frequency asymptote for a single pole in series with the modulator. This accurately models the current loop and control to output transfer functions, but is limited to PCM1, VCM1 andVCM3 operating modes.Hpp ωs 11)s (H +=Where:Qωωn Hp = (38)Algebraic manipulation of the closed loop continuous-time expression for H(s) to find a general open loop expression for H p (s) would appear to be straightforward. For peak or valley current mode with a fixed slopecompensating ramp, ⎟⎟⎠⎞⎜⎜⎝⎛−′⋅−≅⋅m mpi L z n K 1K 1R Z Q ωs . H(s) reduces to 2n 2ωs 1+, which leads to the simplification of a single pole for H p (s). This is not the case for other operating modes. Further work is needed to develop a general expression for H p (s). Though the unified model shows the potential to accurately model the line to output transfer function, this has not been validated. Comparisons of line to output bode plots from the linear model to SPICE results from the switched model do not match over frequency.Simplified Transfer FunctionsThe simplified transfer functions assume poles that are well separated by the current loop gain. Expressions for the averaged model do not show the additional phase shift due to the sampling effect. The control to output gain of the continuous-time model accurately represents the circuit’s behavior to half the switching frequency. The line to output expressions for audio susceptibility are accurate at dc, but diverge from the actual response over frequency.Averaged Model:⎟⎟⎠⎞⎜⎜⎝⎛+⋅⎟⎟⎠⎞⎜⎜⎝⎛++⋅⋅+⋅≈L P Z i m O i O C O ωs 1ωs 1ωs 1R K R 11R R v ˆv ˆ (39) ⎟⎟⎠⎞⎜⎜⎝⎛+⋅⎟⎟⎠⎞⎜⎜⎝⎛++⋅⋅+⋅⋅≈L P Zim OniO IN O ωs 1ωs 1ωs 1R K R 1K R DR v ˆv ˆ (40)Continuous-Time Model:⎟⎟⎠⎞⎜⎜⎝⎛+⋅+⋅⎟⎟⎠⎞⎜⎜⎝⎛++⋅⋅+⋅≈2n 2n P Zim OiO C O ωs Qωs 1ωs 1ωs 1R K R 11R R v ˆvˆ(41)⎟⎟⎠⎞⎜⎜⎝⎛+⋅+⋅⎟⎟⎠⎞⎜⎜⎝⎛++⋅⋅+⋅⋅≈2n 2n P Z i m O ni O IN O ωs Q ωs 1ωs 1ωs 1R K R 1K R D R vˆv ˆ (42)Where: CO Z R C 1ω⋅=⎟⎟⎠⎞⎜⎜⎝⎛⋅+⋅≈i m O O P R K 1R1C 1ω LR K ωimp L ⋅≈Tπωn =(43)Figure 6: SIMPLIS SPICE schematic - emulated peak current mode synchronous buck.Figure 7: SIMPLIS SPICE results of control to output gain.Figure 8: SIMPLIS SPICE results of line to output gain.Figure 9: SIMPLIS SPICE results of current loop gain.TABLE 5Calculated General Gain ParametersV IN=10 V O=5 D=0.5R O=1 R i=0.1 T=5μ L=5μMODE V SLOPE K SL V SL K m K n m c QPCM1 V SL0.10 0.5020.00 0.025 2.000 0.637PCM2 V O·K SL0.10 --- 10.00 0.025 2.000 0.637VCM1 V SL0.10 0.5020.00 0.075 2.000 0.637VCM2 (V IN-V O)·K SL0.10 --- 10.00 0.175 2.000 0.637EPCM1 V SL0.10 1.0010.00 0.125 1.000 0.637EPCM2 V IN·K SL0.10 --- 10.00 0.025 1.000 0.637EVCM1 V SL0.10 1.0010.00 0.075 1.000 0.637EVCM2 V IN·K SL0.10 --- 10.00 0.175 1.000 0.637VCM3 V IN·K SL0.10 --- 10.00 0.225 3.000 0.318EPCM3 (V IN-V O)·K SL +V SL0.10 0.5020.00 0.025 1.000 0.637EPCM4 V IN·K SL +V SL0.05 0.5010.00 0.075 1.000 0.637PCM2 0.5·V O·K SL0.10 --- 20.00 0.000 1.250 2.546VCM2 0.5·(V IN-V O)·K SL0.10 --- 20.00 0.100 1.250 2.546Table Notation:PCM – Peak Current Mode VCM – Valley Current ModeEPCM – Emulated Peak Current Mode EVCM – Emulated Valley Current Mode1 – Fixed slope compensation V SL2 – Optimal slope compensation proportional to K SL3, 4 – Other fixed or proportional slope compensation implementationsIn the last section of Table 5 for PCM2, peak current mode with a slope compensating ramp equal to one half the down slope of the inductor current represents a special case. K n=0 which corresponds to infinite line rejection. This is difficult to achieve due to finite resistance and parasitic elements in a practical circuit. This is not optimal since sub-harmonic oscillation is possible at D>0.5 with feedback control. See section 4 on general slope compensation requirements.TABLE 6Calculated Values and Measured PSPICE Switching Circuit DataR O=1 R i=0.1 T=5μ L=5μV IN=6 V O=5 D=0.83MeasuredCalculatedMODE V SLOPE K SL V SL V O/V C V O/V IN V O/V C V O/V IN PCM1 V SL0.10 0.50 6.67 0.231 6.66 0.240 PCM2 V O·K SL0.10 --- 4.29 0.149 4.25 0.154 VCM1 V SL0.10 0.10 6.67 0.324 6.55 0.325 VCM2 (V IN-V O)·K SL0.10 --- 6.00 0.392 5.98 0.383 EPCM1 V SL0.10 0.60 4.29 0.506 4.24 0.502 EPCM2 V IN·K SL0.10 --- 4.29 0.149 4.25 0.148 EVCM1 V SL0.10 0.60 6.00 0.292 6.00 0.300 EVCM2 V IN·K SL0.10 --- 6.00 0.392 5.96 0.388 VCM3 V IN·K SL0.10 --- 4.29 0.577 4.23 0.571 EPCM3 (V IN-V O)·K SL +V SL0.10 0.50 6.67 0.231 6.61 0.231 EPCM4 V IN·K SL +V SL0.05 0.50 3.75 0.391 3.71 0.389TABLE 7Calculated Values and Measured PSPICE Switching Circuit DataV IN=10 V O=5 D=0.5R O=1 R i=0.1 T=5μ L=5μMeasuredCalculatedMODE V SLOPE K SL V SL V O/V C V O/V IN V O/V C V O/V INPCM1 V SL0.10 0.50 6.67 0.083 6.65 0.088 PCM2 V O·K SL0.10 --- 5.00 0.063 5.00 0.065 VCM1 V SL0.10 0.50 6.67 0.250 6.57 0.249 VCM2 (V IN-V O)·K SL0.10 --- 5.00 0.438 4.97 0.427 EPCM1 V SL0.10 1.00 5.00 0.313 5.00 0.313 EPCM2 V IN·K SL0.10 --- 5.00 0.063 5.00 0.063 EVCM1 V SL0.10 1.00 5.00 0.188 4.99 0.189 EVCM2 V IN·K SL0.10 --- 5.00 0.438 4.99 0.430 VCM3 V IN·K SL0.10 --- 5.00 0.563 4.98 0.550 EPCM3 (V IN-V O)·K SL +V SL0.10 0.50 6.67 0.083 6.56 0.085 EPCM4 V IN·K SL +V SL0.05 0.50 5.00 0.188 5.00 0.188TABLE 8Calculated Values and Measured PSPICE Switching Circuit DataV IN=50 V O=5 D=0.1R O=1 R i=0.1 T=5μ L=5μMeasuredCalculatedMODE V SLOPE K SL V SL V O/V C V O/V IN V O/V C V O/V INPCM1 V SL0.10 0.50 6.67 0.003 6.56 0.009 PCM2 V O·K SL0.10 --- 6.25 0.003 6.17 0.009 VCM1 V SL0.10 4.50 6.67 0.063 6.52 0.063 VCM2 (V IN-V O)·K SL0.10 --- 4.17 0.415 4.16 0.407 EPCM1 V SL0.10 5.00 6.25 0.066 6.19 0.066 EPCM2 V IN·K SL0.10 --- 6.25 0.003 6.14 0.005 EVCM1 V SL0.10 5.00 4.17 0.040 4.15 0.041 EVCM2 V IN·K SL0.10 --- 4.17 0.415 4.16 0.412 VCM3 V IN·K SL0.10 --- 6.25 0.628 6.21 0.618 EPCM3 (V IN-V O)·K SL +V SL0.10 0.50 6.67 0.003 6.53 0.005 EPCM4 V IN·K SL +V SL0.05 0.50 8.33 0.013 8.09 0.014EMULATED CURRENT MODE CONTROL FOR BUCK REGULATORS by Robert SheehanFigure 10: SIMPLIS SPICE results for EPCM2 with varying Q.3. Discrete Time Analysis for Slope Compensation(a) Peak current mode(b) Valley current modeFigure 11: Slope compensation for peak and valley current mode buck.Peak Current Mode Trailing Edge ModulationFor peak current mode control, the peak current must be accounted for in its relationship to the average current. By perturbing the duty cycle, we can see the effect on V C .Write the equation for the voltage at V C :C SLOPE i O IN i L v d V R LTd )v v (5.0R i =⋅+⋅⋅⋅−⋅+⋅ (44)V IN , V O , and V SLOPE are considered to be fixed with respect to the period T. The duty cycle is perturbed, whichshows the effect on the control voltage with respect to the inductor current. The quantity , and . )T (i ˆI LL=Δ)T (d ˆD =Δ)T (vˆV C C =ΔC SLOPE i O IN i L V D V R LTD )V V (5.0R I Δ=Δ⋅+⋅⋅Δ⋅−⋅+⋅Δ (45)To maintain constant average inductor current, the control voltage must change by ½ the ripple current times the current sense gain:i PK C R I 5.0V ⋅Δ⋅−=Δ (46)LTD V L T )D 1(V I O O PK ⋅Δ⋅−=⋅Δ−⋅=Δ (47)Combine equations and solve for ∆D/∆I L :INSLOPE i INi L V V LT R )D 5.0(1V R I D +⋅⋅−⋅−=ΔΔ (48)The term INSLOPE i V V LTR )D 5.0(1+⋅⋅− is equivalent to the peak current mode modulator gain K m with fixedV SLOPE .By factoring, this becomes:⎥⎥⎦⎤⎢⎢⎣⎡−−⋅⎟⎟⎠⎞⎜⎜⎝⎛⋅−+⋅⋅−=ΔΔ5.0)D 1(L /R )V V (T/V 1L T 1V 1I Di O IN SLOPE IN L (49)This can be expressed as:)5.0D m (LT1V 1I D c IN L −′⋅⋅⋅−=ΔΔ (50) Where:D 1D −=′n e c S S1m += Slope compensating ramp: T /V S SLOPE e =Positive current sense ramp:L /R )V V (S i O IN n ⋅−=Reviewing the equation for ∆D/∆I L , when D>0.5, the T/L term goes negative. V SLOPE must be large enough to compensate, or this will manifest itself in the time domain as a sub-harmonic oscillation of the current loop. If the condition is set such that:iIN SLOPE R V VL T D ⋅=⋅ (51)Then m C ·D ′ = 1, so the current loop will be stable for any duty cycle. To meet this condition, solve for V SLOPE :LTR V V i O SLOPE ⋅⋅= (52)Figure 12: Peak current mode sub-harmonic oscillation. For D<0.5, sub-harmonic oscillation is damped. For D>0.5,sub-harmonic oscillation builds with insufficient slope compensation.Valley Current Mode Leading Edge ModulationFor valley current mode control, the valley current must be accounted for in its relationship to the average current. By perturbing the duty cycle, we can see the effect on V C .Write the equation for the voltage at V C :C SLOPE i O i L v )d 1(V R LT)d 1(v 5.0R i =−⋅−⋅⋅−⋅⋅−⋅ (53)V IN , V O , and V SLOPE are considered to be fixed with respect to the period T. The duty cycle is perturbed, whichshows the effect on the control voltage with respect to the inductor current. The quantity , and . )T (i ˆI LL=Δ)T (d ˆD =Δ)T (vˆV C C =ΔC SLOPE i O i L VD V R LTD V 5.0R I Δ=Δ⋅+⋅⋅Δ⋅⋅+⋅Δ (54)To maintain constant average inductor current, the control voltage must change by ½ the ripple current:i PK C R I 5.0V ⋅Δ⋅=Δ(55)LTD )V V (I O IN PK ⋅Δ⋅−=Δ(56)Combine equations and solve for ∆D/∆I L :INSLOPE i INi L V V LT R )5.0D (1V R I D +⋅⋅−⋅−=ΔΔ (57)The term INSLOPE i V V LTR )5.0D (1+⋅⋅− is equivalent to the valley current mode modulator gain K m with fixedV SLOPE .By factoring, this becomes:⎥⎥⎦⎤⎢⎢⎣⎡−⋅⎟⎟⎠⎞⎜⎜⎝⎛⋅+⋅⋅−=ΔΔ5.0D L /R V T /V 1L T 1V 1I Di O SLOPE IN L (58)This can be expressed as:)5.0D m (LT1V 1I D c IN L −⋅⋅⋅−=ΔΔ (59) Where: ne c S S1m +=Slope compensating ramp:T /V S SLOPE e =Negative current sense ramp: L /R V S i O n ⋅=Reviewing the equation for ∆D/∆I L , when D<0.5, the T/L term goes negative. V SLOPE must be large enough to compensate, or this will manifest itself in the time domain as a sub-harmonic oscillation of the current loop. If the condition is set such that:iIN SLOPE R V VL T )D 1(⋅=⋅− (60)Then m C ·D = 1, so the current loop will be stable for any duty cycle. To meet this condition, solve for V SLOPE .LTR )V V (V i O IN SLOPE ⋅⋅−= (61)Figure 13: Valley current mode sub-harmonic oscillation. For D>0.5, sub-harmonic oscillation is damped. ForD<0.5, sub-harmonic oscillation builds with insufficient slope compensation.Emulated Peak Current Mode Valley Sample and HoldThe valley current is sampled on the down slope of the inductor current. This is used as the DC value of current to start the next cycle. A slope compensating ramp is added to produce V RAMP at the modulator input.Write the equation for the voltage at V C :C SLOPE i O IN i L v d V R LTd )v v (5.0R i =⋅+⋅⋅⋅−⋅−⋅ (62)V IN , V O , and V SLOPE are considered to be fixed with respect to the period T. The duty cycle is perturbed, whichshows the effect on the control voltage with respect to the inductor current. The quantity , and . )T (i ˆI LL=Δ)T (d ˆD =Δ)T (vˆV C C =ΔC SLOPE i O IN i L V D V R LTD )V V (5.0R I Δ=Δ⋅+⋅⋅Δ⋅−⋅−⋅Δ (63)To maintain constant average inductor current, the control voltage must change by ½ the ripple current:i PK C R I 5.0V ⋅Δ⋅−=Δ (64)LTD V L T )D 1(V I O O PK ⋅Δ⋅−=⋅Δ−⋅=Δ (65)Combine equations and solve for ∆D/∆I L :LT R 5.0V V 1V R I D i IN SLOPE INi L ⋅⋅−⋅−=ΔΔ (66)By factoring, this becomes:⎟⎟⎠⎞⎜⎜⎝⎛−⋅⋅⋅−=ΔΔ5.0L /R V T /V L T 1V 1I D i IN SLOPE IN L (67)This can also be written as:()5.0m LT 1V 1I D C IN L−⋅⋅−=ΔΔ (68)Where:ne C S S m = T /V S SLOPE e =L /R V S i IN n ⋅=Reviewing the equation for ∆D/∆I L , when m C <0.5, the T/L term goes negative. V SLOPE must be large enough to compensate, or this will manifest itself in the time domain as a sub-harmonic oscillation of the current loop. If the condition is set such that:LR V T V iIN SLOPE ⋅= (69)Then m C = 1, so the current loop will be unconditionally stable. Unlike peak or valley current mode, slope compensation is independent of duty cycle. To meet this condition, solve for V SLOPE .LTR V V i IN SLOPE ⋅⋅=(70)Figure 14: Emulated peak current mode sub-harmonic oscillation. Tendency for sub-harmonic oscillation isindependent of duty cycle. Even with minimal damping, it will eventually die out.Emulated Valley Current ModePeak Sample and HoldThe peak current is sampled on the positive slope of the inductor current. This is used as the DC value of current to start the next cycle. A slope compensating ramp is added to produce V RAMP at the modulator input.Write the equation for the voltage at V C :C SLOPE i O i L v )d 1(V R LT)d 1(v 5.0R i =−⋅−⋅⋅−⋅⋅+⋅ (71)V IN , V O , and V SLOPE are considered to be fixed with respect to the period T. The duty cycle is perturbed, whichshows the effect on the control voltage with respect to the inductor current. The quantity , and . )T (i ˆI LL=Δ)T (d ˆD =Δ)T (vˆV C C =ΔC SLOPE i O i L V D V R LTD V 5.0R I Δ=Δ⋅+⋅⋅Δ⋅⋅−⋅Δ (72)To maintain constant average inductor current, the control voltage must change by ½ the ripple current:i PK C R I 5.0V ⋅Δ⋅=Δ(73)LTD )V V (I O IN PK ⋅Δ⋅−=Δ(74)Combine equations and solve for ∆D/∆I L :LT R 5.0V V 1V R I Di IN SLOPE IN i L⋅⋅−⋅−=ΔΔ(75)By factoring, this becomes:⎟⎟⎠⎞⎜⎜⎝⎛−⋅⋅⋅−=ΔΔ5.0L /R V T /V L T 1V 1I D i IN SLOPE IN L (76)This can be expressed as:)5.0m (LT 1V 1I D c IN L−⋅⋅−=ΔΔ (77)Where: ne C S S m = T /V S SLOPE e =L /R V S i IN n ⋅=Reviewing the equation for ∆D/∆I L , when m C <0.5, the T/L term goes negative. V SLOPE must be large enough to compensate, or this will manifest itself in the time domain as a sub-harmonic oscillation of the current loop. If the condition is set such that:LR V T V iIN SLOPE ⋅= (78)Then m C = 1, so the current loop will be unconditionally stable. Unlike peak or valley current mode, slope compensation is independent of duty cycle. To meet this condition, solve for V SLOPE .LTR V V i IN SLOPE ⋅⋅= (79)4. General Slope Compensation RequirementsThe graphs in the preceding section were made by entering the discrete time expressions for the inductor current and slope compensating ramp into an Excel spreadsheet. The results are plotted on a cycle by cycle basis. This shows the current loop behavior without any feedback to the control voltage. Reference [6] discusses the voltage loop gain effect on the slope compensation requirement for peak current mode. Peaking of the closed loop gain due to insufficient slope compensation and ripple on the control voltage can cause sub-harmonic oscillation before the calculated limit, i.e. at duty cycles below 0.5 for peak current mode.For any mode of operation, when the sum of the sensed inductor current’s slope (times the current sense gain) plus the slope of the compensation ramp is proportional to V IN , any tendency toward sub-harmonic oscillation will damp in one switching cycle. This condition is represented by equations 52, 61, 70 and 79, which corresponds to a Q of 0.637. Operation is considered to be optimal, in that the effective sampled gain inductor pole is fixed in frequency with respect to changes in line voltage. This allows for the highest closed loop gain without any tendency toward sub-harmonic oscillation. Increasing the external ramp beyond this point will lower the modulator gain, consequently shifting toward a more voltage mode behavior.The effective sampled gain inductor pole frequency (45° phase shift) is given by:⎟⎠⎞⎜⎝⎛−⋅+⋅⋅⋅=1Q 41Q T 41)Q (f 2L(80)5. Correlation of Measured DataThe LM3495 standard reference design was chosen as a platform for correlation. It is an emulated peak current mode controller with MOSFET current sensing and internally generated slope compensation using mode EPCM4. Operating parameters:V IN =12 V O =1.2 T=2μs V SL =0.125 K SL =1/16 L=1μH R L =3m Ω G I =4 R S =3.4m Ω C O =200μF R C =1m Ω R O =1Ω and 0.2ΩMeasurement of control to output gain was made using an AP200 frequency response analyzer.The simplified transfer function using equation 41 was entered into SPICE as LaPlace for the calculated results. Nominal data sheet values were used for the components and operating parameters.Comparison of the results is shown in figure 15.Figure 15: LM3495 control to output gain.6. ConclusionThis analysis has focused on current mode buck regulators with continuous inductor current. Using the methodology outlined here, general expressions for the boost and buck-boost can be developed. Preliminary work has demonstrated good correlation between switching and linear models. Using the gain coefficients from reference [2], general expressions for discontinuous conduction mode can also be developed.Limitations of existing models have been identified, with direction for further work. Regardless of the limitations, the simplified transfer functions and general gain parameters allow accurate modeling of the control to output gain. This is the most important parameter from a design standpoint. Tools like SIMPLIS provide bode plots for any transfer function directly from the switching model.REFERENCES[1] R.D. Middlebrook, “Topics in Multi-Loop Regulators and Current-Mode Programming,” IEEE PESCRecord, pp. 716–732, 1985 (also in IEEE Transactions on Power Electronics, Volume 2, Issue 2, pp. 109–124, 1987).[2] R.B. Ridley, “A New Continuous-Time Model for Current-Mode Control with Constant Frequency,Constant On-Time, and Constant Off-Time, in CCM and DCM,” IEEE PESC Record, pp. 382–389, 1990.[3] R.B. Ridley, “A New, Continuous-Time Model for Current-Mode Control,” IEEE Transactions on PowerElectronics, Volume 6, Issue 2, pp. 271–280, 1991.[4] F.D. Tan, R.D. Middlebrook, “Unified Modeling and Measurement of Current-Programmed Converters,”IEEE PESC Record, pp. 380–387, 1993.[5] F.D. Tan, R.D. Middlebrook, “A Unified Model for Current-Programmed Converters,”IEEE Transactions on Power Electronics, Volume 10, Issue 4, pp. 397–408, 1995.“Modeling, Analysis and Compensation of the Current-Mode Converter,” Powercon 11 Holland,[6] BarneyProceedings, I-2, 1984.。

超特克(Supertex)高压DC DC转换器应用注解说明书