【专业文档】clocks(150字).doc

(完整word版)PEP人教版小学英语五年级下册课堂同步练习试题全册,推荐文档

五年级(下)第一单元第1课时学案Unit 1 My dayPart A Let’s talk【学习目标】1.能够听懂、会说句型:When do you finish class in the morning? We finish class at 1o’clock.并能在实际情景中运用。

能够正确使用usually这个频度副词。

2.能在Role play部分用本课时目标语言询问同学的作息时间,并能对结果做简单的反思。

【重点难点】重点:能够熟练使用句型:―When do you finish class in the morning? We finish class at 1o’clock.问答活动时间。

难点:能够在情境中熟练使用句型:―When do you …?问答活动时间。

【新知预习】写出下列单词或词组的意思。

1. finish class ______________2. after lunch_________3. start _____________4. Spain__________5. too late_____________【课堂探究】探究1 根据汉意写单词。

1. 吃午餐__________________2. 回学校_____________3. 吃晚餐________________4.什么时候_____________5. 或者________________探究2 翻译下列句子。

When do you finish class in the morning? ___________________________________Classes start at 3 o’clock. __________________________________【针对练习】单项选择。

1.---________ do you go to bed?--- At 9:00.A.WhatB. whenC. When2.I eat dinner _____ 6 o’clock.A. aB. atC. on【达标练习】Ⅰ. 选择正确答案。

LMK00101SQXNOPB;LMK00101SQNOPB;LMK00101SQENOPB;LMK00101BEVALNOPB;中文规格书,Datasheet资料

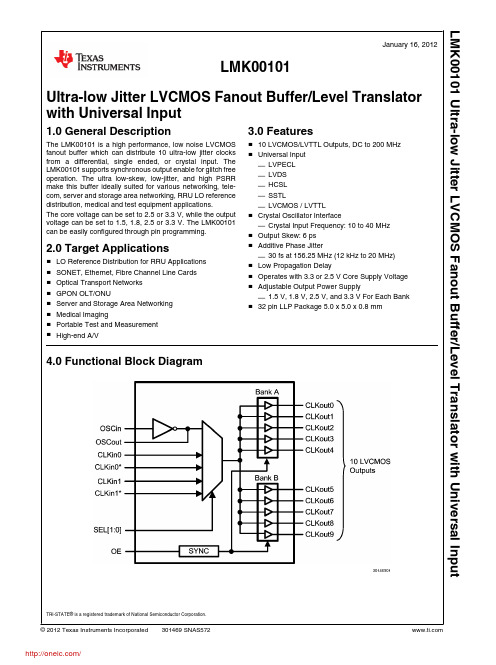

LMK00101January 16, 2012Ultra-low Jitter LVCMOS Fanout Buffer/Level Translator with Universal Input1.0 General DescriptionThe LMK00101 is a high performance, low noise LVCMOS fanout buffer which can distribute 10 ultra-low jitter clocks from a differential, single ended, or crystal input. The LMK00101 supports synchronous output enable for glitch free operation. The ultra low-skew, low-jitter, and high PSRR make this buffer ideally suited for various networking, tele-com, server and storage area networking, RRU LO reference distribution, medical and test equipment applications.The core voltage can be set to 2.5 or 3.3 V, while the output voltage can be set to 1.5, 1.8, 2.5 or 3.3 V. The LMK00101 can be easily configured through pin programming.2.0 Target Applications■LO Reference Distribution for RRU Applications■SONET, Ethernet, Fibre Channel Line Cards■Optical Transport Networks■GPON OLT/ONU■Server and Storage Area Networking■Medical Imaging■Portable Test and Measurement■High-end A/V 3.0 Features■10 LVCMOS/LVTTL Outputs, DC to 200 MHz ■Universal Input—LVPECL—LVDS—HCSL—SSTL—LVCMOS / LVTTL■Crystal Oscillator Interface—Crystal Input Frequency: 10 to 40 MHz■Output Skew: 6 ps■Additive Phase Jitter—30 fs at 156.25 MHz (12 kHz to 20 MHz)■Low Propagation Delay■Operates with 3.3 or 2.5 V Core Supply Voltage ■Adjustable Output Power Supply—1.5 V, 1.8 V, 2.5 V, and 3.3 V For Each Bank ■32 pin LLP Package 5.0 x 5.0 x 0.8 mm4.0 Functional Block Diagram30146901TRI-STATE® is a registered trademark of National Semiconductor Corporation.© 2012 Texas Instruments Incorporated301469 LMK00101 Ultra-low Jitter LVCMOS Fanout Buffer/Level Translator with Universal Input5.0 Connection Diagram32-Pin LLP Package301469026.0 Pin DescriptionsPin #Pin Name Type DescriptionDAP DAP -The DAP should be grounded1CLKout0Output LVCMOS Output2, 6Vddo Power Power Supply for Bank A (CLKout0 to CLKout4) CLKout pins.19,23Vddo Power Power Supply for Bank B (CLKout5 to CLKout9) CLKout pins.3CLKout1Output LVCMOS Output 4,9,15,16,21,25,26,32GND GND Ground5CLKout2Output LVCMOS Output 7CLKout3Output LVCMOS Output 8CLKout4Output LVCMOS Output10Vdd Power Supply for operating core and input buffer 11OSCin Input Input for Crystal 12OSCout Output Output for Crystal 13CLKin0Input Input Pin14CLKin0*Input Optional complimentary input pin 17CLKout5Output LVCMOS Output 18CLKout6Output LVCMOS Output 20CLKout7Output LVCMOS Output 22CLKout8Output LVCMOS Output 24CLKout9Output LVCMOS Output27CLKin1*Input Optional Complimentary Input Pin 28CLKin1Input Input Pin29SEL1Input MSB for Input Clock Selection. This pin has an internal pull-down resistor.30SEL0Input LSB for Input Clock Selection. This pin has an internal pull-down resistor.31OEInputOutput Enable. This pin has an internal pull-down resistor. 2L M K 00101 U l t r a -l o w J i t t e r L V C M O S F a n o u t B u f f e r /L e v e l T r a n s l a t o r w i t h U n i v e r s a l I n p u t7.0 Absolute Maximum Ratings (Note 1, Note 2)If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.Parameter Symbol Ratings Units Core Supply Voltage Vdd-0.3 to 3.6VOutput Supply Voltage Vddo-0.3 to 3.6V Input Voltage V IN-0.3 to Vdd + 0.3V Storage Temperature Range T STG-65 to 150°CLead Temperature (solder 4 s)T L+260°C Junction Temperature T J+125°C8.0 Recommended Operating ConditionsParameter Symbol Min Typ Max Units Ambient Temperature T A-402585°CCore Supply Voltage Vdd 2.375 3.3 3.45V Output Supply Voltage (Note 3)Vddo 1.425 3.3Vdd VNote 1:"Absolute Maximum Ratings" indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or other conditions beyond those indicated in the Recommended Operating Conditions is not implied. The Recommended Operating Conditions indicate conditions at which the device is functional and the device should not be operated beyond such conditions.Note 2:This device is a high performance integrated circuit with ESD handling precautions. Handling of this device should only be done at ESD protected work stations. The device is rated to a HBM-ESD of > 2.5 kV, a MM-ESD of > 250 V, and a CDM-ESD of > 1 kV.Note 3:Vddo should be less than or equal to Vdd(Vddo≤ Vdd)9.0 Package Thermal Resistance32-Lead LLPPackage Symbols Ratings UnitsThermal resistance from junction to ambienton 4-layer Jedec board (Note 4)θJA50° C/WThermal resistance from junction to case(Note 5)θJC (DAP)20° C/WNote 4:Specification assumes 5 thermal vias connect to die attach pad to the embedded copper plane on the 4-layer Jedec board. These vias play a key role in improving the thermal performance of the LLP. For best thermal dissipation it is recommended that the maximum number of vias be used on the board layout.Note 5:Case is defined as the DAP (die attach pad).LMK00101 Ultra-low Jitter LVCMOS Fanout Buffer/Level Translator with Universal Input10.0 Electrical Characteristics(2.375 V ≤ Vdd ≤ 3.45 V, 1.425 ≤ Vddo ≤ Vdd, -40 °C ≤ T A ≤ 85 °C, Differential inputs. Typical values represent most likely parametric norms at Vdd = Vddo = 3.3 V, T A = 25 °C, at the Recommended Operation Conditions at the time of product charac-terization and are not guaranteed). Test conditions are: F test = 100 MHz, Load = 5 pF in parallel with 50 Ω unless otherwise stated.SymbolParameterTest ConditionsMinTypMaxUnitsTotal Device CharacteristicsVddCore Supply Voltage2.3752.5 or3.33.45VVddo Output Supply Voltage 1.425 1.5,1.8,2.5, or3.3Vdd VI VddCore CurrentNo CLKin1625mAV ddo = 3.3 V, F test = 100 MHz 24 V ddo = 2.5 V, F test = 100 MHz 20 I Vddo[n]Current for Each OutputV ddo = 2.5 V,OE = High, F test = 100 MHz5 mAV ddo = 3.3 V,OE = High, F test = 100 MHz7 OE = Low 0.1 I Vdd + I VddoTotal Device Current with Loads onall outputsOE = High @ 100 MHz95 mAOE = Low16Power Supply Ripple Rejection (PSRR)PSRRRipple Induced Phase Spur Level100 kHz, 100 mVpp Ripple Injected on V dd , V ddo = 2.5 V-44dBcOutputs (Note 6)Skew Output Skew Measured between outputs,referenced to CLKout06 ps f CLKoutOutput Frequency(Note 7)DC 200MHzt Rise Rise/Fall Time V dd = 3.3 V, V ddo = 1.8 V, C L = 10 pF500 psV dd = 2.5 V, V ddo = 2.5 V, C L = 10 pF 300 V dd = 3.3 V, V ddo = 3.3 V, C L = 10 pF200 V CLKout Low Output Low Voltage 0.1V V CLKout High Output High Voltage Vddo-0.1 R CLKoutOutput Resistance50 ohm t jRMS Additive Jitterf CLKout = 156.25 MHz,CMOS input slew rate ≥ 2 V/ns C L = 5 pF, BW = 12 kHz to 20 MHz30fs 4L M K 00101 U l t r a -l o w J i t t e r L V C M O S F a n o u t B u f f e r /L e v e l T r a n s l a t o r w i t h U n i v e r s a l I n p u tSymbol Parameter Test ConditionsMin Typ Max UnitsDigital Inputs (OE, SEL0, SEL1)V Low Input Low Voltage Vdd = 2.5 V 0.4VV High Input High Voltage Vdd = 2.5 V 1.3 Vdd = 3.3 V1.6 I IH High Level Input Current 50uAI IL Low Level Input Current -5 5CLKin0/0* and CLKin1/1* Input Clock Specifications, (Note 9, Note 10)I IH High Level Input Current V CLKin = Vdd 20uA I IL Low Level Input Current(Note 8)V CLKin = 0 V-20 uA V IH Input High Voltage Vdd VV ILInput Low VoltageGND V CMDifferential InputCommon Mode Input Voltage(Note 12)V ID = 150 mV0.5 Vdd-1.2VV ID = 350 mV 0.5 Vdd-1.1V ID = 800 mV0.5 Vdd-0.9V ID Differential Input Voltage Swing CLKin driven differentially 0.15 1.5V OSCin/OSCout Pinsf OSCinInput Frequency (Note 7)Single-Ended Input, OSCout floatingDC200MHzf XTALCrystal Frequency Input Range Fundamental Mode Crystal ESR < 200 Ω ( f Xtal ≤ 30 MHz )ESR < 120 Ω ( f Xtal > 30 MHz )(Note 11, Note 7)10 40MHzC OSCinShunt Capacitance1 pFNote 6:AC Parameters for CMOS are dependent upon output capacitive loading Note 7:Guaranteed by characterization.Note 8:V IL should not go below -0.3 volts.Note 9:See Section 12.1 Differential Voltage Measurement Terminology for definition of V ID and V OD .Note 10:Refer to application note AN-912 Common Data Transmission Parameters and their Definitions for more information.Note 11:The ESR requirements stated are what is necessary in order to ensure that the Oscillator circuitry has no start up issues. However, lower ESR values for the crystal might be necessary in order to stay below the maximum power dissipation requirements for that crystal.Note 12:When using differential signals with V CM outside of the acceptable range for the specified V ID , the clock must be AC coupled.LMK00101 Ultra-low Jitter LVCMOS Fanout Buffer/Level Translator with Universal Input30146942Iddo per Output vs Frequency50100150200250051015C U R R E N T (m A )FREQUENCY (MHz)Cload = 10 pFVddo = 1.5 V Vddo = 1.8 V Vddo = 2.5 V Vddo = 3.3 V 30146976Note 13:Test conditions: LVCMOS Input, slew rate ≥ 2 V/ns, C L = 5 pF in parallel with 50 6L M K 00101 U l t r a -l o w J i t t e r L V C M O S F a n o u t B u f f e r /L e v e l T r a n s l a t o r w i t h U n i v e r s a l I n p u t12.0 Measurement Definitions12.1 Differential Voltage Measurement TerminologyThe differential voltage of a differential signal can be de-scribed by two different definitions causing confusion when reading datasheets or communicating with other engineers. This section will address the measurement and description of a differential signal so that the reader will be able to under-stand and discern between the two different definitions when used.The first definition used to describe a differential signal is the absolute value of the voltage potential between the inverting and non-inverting signal. The symbol for this first measure-ment is typically VID or VODdepending on if an input or outputvoltage is being described.The second definition used to describe a differential signal is to measure the potential of the non-inverting signal with re-spect to the inverting signal. The symbol for this second measurement is VSSand is a calculated parameter. Nowherein the IC does this signal exist with respect to ground, it onlyexists in reference to its differential pair. VSScan be measured directly by oscilloscopes with floating references, otherwisethis value can be calculated as twice the value of VODas de-scribed in the first sectionFigure 1 illustrates the two different definitions side-by-side for inputs and Figure 2 illustrates the two different definitionsside-by-side for outputs. The VIDand VODdefinitions showVAand VBDC levels that the non-inverting and inverting sig-nals toggle between with respect to ground. VSSinput and output definitions show that if the inverting signal is consid-ered the voltage potential reference, the non-inverting signal voltage potential is now increasing and decreasing above and below the non-inverting reference. Thus the peak-to-peak voltage of the differential signal can be measured.VIDand VODare often defined in volts (V) and VSSis oftendefined as volts peak-to-peak (VPP).30146912FIGURE 1. Two Different Definitions for Differential Input Signals30146913FIGURE 2. Two Different Definitions for Differential Output Signals LMK00101 Ultra-low Jitter LVCMOS Fanout Buffer/Level Translator with Universal Input13.0 Functional DescriptionThe LMK00101 is a 10 output LVCMOS clock fanout buffer with low additive jitter that can operate up to 200 MHz. It fea-tures a 3:1 input multiplexer with a crystal oscillator input,single supply or dual supply (lower power) operation, and pin-programmable device configuration. The device is offered in a 32-pin LLP package.13.1 V dd and V ddo Power Supplies (Note 14, Note 15)Separate core and output supplies allow the output buffers to operate at the same supply as the Vdd core supply (3.3 V or 2.5 V) or from a lower supply voltage (3.3 V, 2.5 V, 1.8 V, or 1.5 V). Compared to single-supply operation, dual supply op-eration enables lower power consumption and output-level compatibility.Bank A (CLKout0 to CLKout4) and Bank B (CLKout5 to CLK-out9) may also be operated at different V ddo voltages, provid-ed neither V ddo voltage exceeds V dd .Note 14:Care should be taken to ensure the V ddo voltage does not exceed the Vdd voltage to prevent turning-on the internal ESD protection circuitry.Note 15:DO NOT DISCONNECT OR GROUND ANY OF THE V ddo PINS as the V ddo pins are internally connected within an output bank.13.2 CLOCK INPUTSThe LMK00101 has three different inputs, CLKin0/CLKin0*,CLKin1/CLKin1*, and OSCin that can be driven in different manners that are described in the following sections.13.2.1 SELECTION OF CLOCK INPUTClock input selection is controlled using the SEL0 and SEL1pins as shown in Table 1. Refer to Section 14.1 Driving the Clock Inputs for clock input requirements. When CLKin0 or CLKin1 is selected, the crystal circuit is powered down. When OSCin is selected, the crystal oscillator will start-up and its clock will be distributed to all outputs. Refer to Section 14.2Crystal Interface for more information. Alternatively, OSCin may be driven by a single ended clock, up to 200 MHz, instead of a crystal.TABLE 1. Input SelectionSEL1SEL0Input 00CLKin0, CLKin0*01CLKin1, CLKin1*1XOSCin (Crystal Mode)13.2.1.1 CLKin/CLKin* PinsThe LMK00101 has two differential inputs (CLKin0/CLKin0*and CLKin1/CLKin1*) that can be driven single-ended or dif-ferentially. They can accept AC or DC coupled 3.3V/2.5V LVPECL, LVDS, or other differential and singled ended sig-nals that meet the input requirements under the “CLKin0/0*and CLKin1/1* Input Clock Specifications” portion of the Sec-tion 10.0 El ectrical Characteristics and (Note 12). Refer to Section 14.1 Driving the Clock Inputs for more details on driv-ing the LMK00101 inputs.In the event that a Crystal mode is not selected and the CLKin pins do not have an AC signal applied to them, Table 2 fol-lowing will be the state of the outputs.TABLE 2. CLKinX Input vs. Output States CLKinX CLKinX*Output State Open Open Logic Low Logic Low Logic Low Logic Low Logic High Logic Low Logic High Logic LowLogic HighLogic Low13.3 CLOCK OUTPUTSThe LMK00101 has 10 LVCMOS outputs.13.3.1 Output Enable PinWhen the output enable pin is held High, the outputs are en-abled. When it is held Low, the outputs are held in a Low state as shown in Table 3.TABLE 3. Output Enable Pin StatesOE Outputs Low Disabled (Hi-Z)HighEnabledThe OE pin is synchronized to the input clock to ensure that there are no runt pulses. When OE is changed from Low to High, the outputs will initially have an impedance of about 400 Ω to ground until the second falling edge of the input clock. Starting with the second falling edge of the input clock,the outputs will buffer the input. If the OE pin is taken from Low to High when there is no input clock present, the outputs will either go High or Low and stay a that state; they will not oscillate. When the OE pin is taken from High to Low the out-puts will become Low after the second falling edge of the clock input and then will go to a Disabled (Hi-Z) state starting after the next rising edge.13.3.2 Using Less than Ten OutputsAlthough the LMK00101 has 10 outputs, not all applications will require all of these. In this case, the unused outputs should be left floating with a minimum copper length (Note 16) to minimize capacitance. In this way, this output will con-sume minimal output current because it has no load.Note 16:For best soldering practices, the minimum trace length should extend to include the pin solder mask. This way during reflow, the solder has the same copper area as connected pins. This allows for good, uniform fillet solder joints helping to keep the IC level during reflow. 8L M K 00101 U l t r a -l o w J i t t e r L V C M O S F a n o u t B u f f e r /L e v e l T r a n s l a t o r w i t h U n i v e r s a l I n p u t14.0 Application Information14.1 Driving the Clock InputsThe LMK00101 has two differential inputs (CLKin0/CLKin0*and CLKin1/CLKin1*) that can accept AC or DC coupled 3.3V/2.5V LVPECL, LVDS, and other differential and single ended signals that meet the input requirements specified in Sec-tion 10.0 Electrical Characteristics . The device can accept a wide range of signals due to its wide input common mode voltage range (V CM ) and input voltage swing (V ID )/dynamic range. AC coupling may also be employed to shift the input signal to within the V CM range.To achieve the best possible phase noise and jitter perfor-mance, it is mandatory for the input to have a high slew rate of 2 V/ns (differential) or higher. Driving the input with a lower slew rate will degrade the noise floor and jitter. For this rea-son, a differential input signal is recommended over single-ended because it typically provides higher slew rate and common-mode noise rejection.While it is recommended to drive CLKin0 and CLKin1 with a differential signal input, it is possible to drive them with a sin-gle ended clock. The single-ended input slew rate should be as high as possible to minimize performance degradation.The CLKinX input has an internal bias voltage of about 1.4 V,so the input can be AC coupled as shown in Figure 3, Figure 4, or Figure 5 depending upon the application.30146938FIGURE 3. Single-Ended LVCMOS Input, AC Coupling,Near and Far End Termination30146943FIGURE 4. Single-Ended LVCMOS Input, AC Coupling,Near End Termination30146944FIGURE 5. Single-Ended LVCMOS Input, AC Coupling,Far End Termination A single ended clock may also be DC coupled to CLKinX as shown in Figure 6. If the DC coupled input swing has a com-mon mode level near the devices internal bias of 1.4 V, then only a 0.1 µF bypass cap is required on CLKinX*. Otherwise,if the input swing is not optimally centered near the internal bias voltage, then CLKinX* should be externally biased to the midpoint voltage of the input swing. This can be achieved us-ing external biasing resistors, R B1 and R B2, or another low-noise voltage reference. The external bias voltage should be within the specified input common voltage (VCM) range. This will ensure the input swing crosses the threshold voltage at a point where the input slew rate is the highest.30146939FIGURE 6. Single-Ended LVCMOS Input, DC Couplingwith Common Mode Biasing If the crystal oscillator circuit is not used, it is possible to drive the OSCin input with an single-ended external clock as shown in Figure 7. Configurations similar to Figure 4 or Figure 5 could also be used as long as the OSCout pin is left floating. The input clock should be AC coupled to the OSCin pin, which has an internally generated input bias voltage, and the OSCout pin should be left floating. While OSCin provides an alterna-tive input to multiplex an external clock, it is recommended to use either differential input (CLKinX) since it offers higher op-erating frequency, better common mode, improved power supply noise rejection, and greater performance over supply voltage and temperature variations.LMK00101 Ultra-low Jitter LVCMOS Fanout Buffer/Level Translator with Universal Input30146903FIGURE 7. Driving OSCin with a Single-Ended ExternalClock 14.2 Crystal InterfaceThe LMK00101 has an integrated crystal oscillator circuit that supports a fundamental mode, AT-cut crystal. The crystal in-terface is shown in Figure 8.30146904FIGURE 8. Crystal InterfaceThe load capacitance (C L ) is specific to the crystal, but usually on the order of 18 to 20 pF. While C L is specified for the crys-tal, the OSCin input capacitance (C IN = 1 pF typical) of the device and PCB stray capacitance (C STRAY ~ 1 to 3 pF) can affect the discrete load capacitor values, C 1 and C 2. For the parallel resonant circuit, the discrete capacitor values can be calculated as follows:C L = (C 1 * C 2) / (C 1 + C 2) + C IN + C STRAY(1)Typically, C 1 = C 2 for optimum symmetry, so Equation 1 can be rewritten in terms of C 1only:C L = C 12 / (2 * C 1 ) + C IN + C STRAY(2)Finally, solve for C 1:C 1 = (C L - C IN - C STRAY ) * 2(3)Section 10.0 Electrical Characteristics provides crystal inter-face specifications with conditions that ensure start-up of the crystal, but it does not specify crystal power dissipation. The designer will need to ensure the crystal power dissipation does not exceed the maximum drive level specified by the crystal manufacturer. Overdriving the crystal can cause pre-mature aging, frequency shift, and eventual failure. Drive level should be held at a sufficient level necessary to start-up and maintain steady-state operation.The power dissipated in the crystal, P XTAL , can be computed by:P XTAL = I RMS 2 * R ESR * (1 + C 0 / C L )2(4)Where:•I RMS is the RMS current through the crystal.•R ESR is the maximum equivalent series resistance specified for the crystal.•C L is the load capacitance specified for the crystal.•C 0 is the minimum shunt capacitance specified for the crystal.I RMS can be measured using a current probe (e.g. Tektronix CT-6 or equivalent) placed on the leg of the crystal connected to OSCout with the oscillation circuit active.As shown in Figure 8, an external resistor, R LIM , can be used to limit the crystal drive level if necessary. If the power dissi-pated in the selected crystal is higher than the drive level specified for the crystal with R LIM shorted, then a larger resis-tor value is mandatory to avoid overdriving the crystal. How-ever, if the power dissipated in the crystal is less than the drive level with R LIM shorted, then a zero value for R LIM can be used.As a starting point, a suggested value for R LIM is 1.5 k Ω14.3 Power Supply Ripple RejectionIn practical system applications, power supply noise (ripple)can be generated from switching power supplies, digital ASICs or FPGAs, etc. While power supply bypassing will help filter out some of this noise, it is important to understand the effect of power supply ripple on the device performance.When a single-tone sinusoidal signal is applied to the power supply of a clock distribution device, such as LMK00101, it can produce narrow-band phase modulation as well as am-plitude modulation on the clock output (carrier). In the single-side band phase noise spectrum, the ripple-induced phase modulation appears as a phase spur level relative to the car-rier (measured in dBc).For the LMK00101, power supply ripple rejection (PSRR),was measured as the single-sideband phase spur level (in dBc) modulated onto the clock output when a ripple signal was injected onto the V ddo supply. The PSRR test setup is shown in Figure 9.30146940FIGURE 9. PSRR Test SetupA signal generator was used to inject a sinusoidal signal onto the V ddo supply of the DUT board, and the peak-to-peak ripple amplitude was measured at the V ddo pins of the device. A lim-iting amplifier was used to remove amplitude modulation on the differential output clock and convert it to a single-ended signal for the phase noise analyzer. The phase spur level measurements were taken for clock frequencies of 100 MHz under the following power supply ripple conditions:•Ripple amplitude: 100 mVpp on V ddo = 2.5 V •Ripple frequency: 100 kHzAssuming no amplitude modulation effects and small index modulation, the peak-to-peak deterministic jitter (DJ) can be calculated using the measured single-sideband phase spur level (PSRR) as follows:10L M K 00101 U l t r a -l o w J i t t e r L V C M O S F a n o u t B u f f e r /L e v e l T r a n s l a t o r w i t h U n i v e r s a l I n p u t分销商库存信息:NATIONAL-SEMICONDUCTORLMK00101SQX/NOPB LMK00101SQ/NOPB LMK00101SQE/NOPB LMK00101BEVAL/NOPB。

我的大学生活英语作文150词

我的大学生活英语作文150词下面是小编精心整理提供的关于大学生活的英语,供大家阅读参考。

我的大学生活英语作文1:In my understanding, if we refer to an ideal college life as a formal western dinner, then a high GPA, that is, Grade Point Average, should be the main course, while an active part in activities, together with associations, means the appetizer. Some romances, of course, play the role as desserts. They are the 3 key elements for an ideal college life.Those, however, are not what college life is all about. As we all know, college is wildly different from middle school. It connects not only adolescence to adulthood, but also the ivory tower to the real society. Therefore, the ideal college life is that I become matured both physically and mentally, and that I obtain qualified academic knowledge and get well prepared for society at the same time.Under this circumstance, I never expect my college life to be too ideal, or you can call it too perfect. It is not realistic to make all things on my own way, with everyone liking me, winning the first prize all the time, and so on. Of course, I’d like to lead a carefree life. However, this does little good to my future. What really helps is hardships like failure, betrayal, and unjust treatment. Only after experiencing those can I know what society is like, and what life is like.To conclude my speech, I wanna say, some positive experiences are surely part of the ideal college life. But, I should not forget about the negative sides. They are not less necessary.我的大学生活英语作文2:With time goes by, it becomes a bit hard for me to remember everything about myself at the first day of my college life. However, there was one thing for sure that I did feel quite excited and curious about my university. There is no doubt that students like me have struggled for a long time so that can be permitted to enter the university.随着时间的流逝,记得在我的第一天大学生活对我来说变得有点困难了。

通信工程专业英语教案

Ancient systems and optical telegraphy

Early telecommunications included smoke signals and drums. Talking drums1 were used by natives in Africa, New Guinea and South America, and smoke signals in North America and China. Contrary to what one might think, these systems were often used to do more than merely announce the presence of a military camp.

Telephone

The electric telephone was invented in the 1870s; it was based on earlier work with harmonic (multi-signal) telegraphs. The first commercial telephone services were set up in 1878 and 1879 on both sides of the Atlantic in the cities of New Haven and London. Alexander Graham Bell held the master patent for the telephone that was needed for such services in both countries. All other patents for electric telephone devices and features flowed from this master patent.

UPC1862资料

The mark shows major revised points.©1991, 1996Document No. S11431EJ3V0DS00 (3rd edition)Date Published December 1997 N CP(K)Printed in Japan2BLOCK DIAGRAMSSICSO VSSIHDF HDOHKO SGND HSOF1HSOF2HSOF3AFCF SV CC BGPE NHSO CPO FIO VSO N/P SCOCV CC1TINTCINACCFCKOCKFCOUT APCF CGND SCOF1SCOF2SCOF3CV CC2CV CC3VCOO DIVS ESCIRemark AFC :Automatic Frequency ControlACC :Automatic Color saturation level Control APC :Automatic Phase ControlSelecting divide ratio by DIVS pinSelecting TV transmission by N/P pinDIVS Divide ratioN/P pinTV transmissionH 1/8H PAL Open EXT IN with pin 18LNTSCL1/4In PAL, only correspond 4f SC (DIVS = L).System Block DiagramApplication to Process of Digital Video SignalAnalog34PIN CONFIGURATION (Top View)36-pin plastic shrink SOP (300 mil)SSI CSO VSSI HDF HDO HKO SGND HSOF1HSOF2HSOF3AFCF SV CC BGPE NHSO CPO FIO VSO N/PCV CV CVACCF:Chroma ACC FilterAFCF:Horizontal Sync AFC FilterAPCF:Chroma APC FilterBGPE:Burst Gate Pulse from ExternalCGND:Chroma GNDCIN:Chroma InputCKF:Color Killer FilterCKO:Color Killer OutputCOUT:Chroma OutputCPO:Clamp Pulse OutputCSO:Composite Sync OutputCV CC1-CV CC3:Chroma V CCDIVS:Divider Setting InputESCI:External Subcarrier InputFIO:Field ID OutputHDF:Horizontal Sync Detect FilterHDO:Horizontal Sync Detect OutputHKO:Horizontal Sync Killer OutputHSOF1-HSOF3:32f H VCO FilterNHSO:Negative Horizontal Sync OutputN/P:NTSC/PAL Mode SelectSCO:Subcarrier OutputSCOF1-SCOF3:f SC VCO FilterSGND:Sync GNDSSI:Horizontal Sync Separation InputSV CC:Sync V CCTINT:Tint ControlVCOO:VCO OutputVSO:Vertical Sync OutputVSSI:Vertical Sync Separation Input5PIN FUNCTIONS(1/12)6Note Chroma burst amplitude from pin 4: 150 mV p-p7Note Chroma burst amplitude from pin 4: 150 mV p-p 8Note Chroma burst amplitude from pin 4: 150 mV p-p910Note When only 0.3 V p-p sync signal is input to pin 36Note When only 0.3 V p-p sync signal is input to pin 36ELECTRICAL SPECIFICATIONSABSOLUTE MAXIMUM RATINGS (T A = 25 °C, unless otherwise specified)Parameter Symbol Ratings UnitSupply voltage V CC7VInput signal voltage (Chroma signal)e i43V p-pInput signal voltage (H sync separation)e i363V p-pInput signal voltage (V sync separation)e i343V p-pInput signal voltage (EXT)e i18V CC V p-pTint control signal voltage e c3V CC V Output current I O–7mAPermissible package power dissipation P D570 (T A = 75°C)mW (when mounted on PCB)Operating ambient temperature T A–10 to +75°C Storage temperature T stg–40 to +125°CCaution Expose to Absolute Maximum Rating for extended periods may affect device reliability; exceeding the ratings could cause permanent damage. The parameters apply independently.The device should be operated within the limits specified under DC and AC Characteristics.RECOMMENDED OPERATING CONDITIONSParameter Symbol MIN.TYP.MAX.Unit Supply voltage V CC 4.5 5.0 5.5VInput signal voltage (Chroma signal)e i4150mV p-p Input signal voltage (H sync separation)e i36 1.0V p-pInput signal voltage (V sync separation)e i34 1.0V p-pInput signal voltage (EXT IN HIGH voltage)e iH18 2.0VInput signal voltage (EXT IN LOW voltage)e iL180.8V Divider selector voltage 1 (1/8)V17 (8) 4.8V Divider selector voltage 2 (1/4)V17 (4)0.2VTint control voltage V3 2.5VNTSC/PAL select voltage (PAL)V19P 4.5VNTSC/PAL select voltage (NTSC)V19N0.5VELECTRICAL CHARACTERISTICS (at T A = 25±3 °C, RH ≤ 70 %, V CC = 5 V, unless otherwise specified)Chroma sectionParameter Symbol Condition MIN.TYP.MAX.UnitSupply current I CC (C)V CC (C) = 5 V172125mAof chroma section No current on pin 2, 14 and 15ACC amplitude ACC1Fluctuation of chroma output level at +6 dB–2.00+2.0dB characteristic 1change of chroma input burst signal(0 dB = 150 mV p-p)ACC amplitude ACC2Fluctuation of chroma output level at –20 dB–5.0–1.0+1.0dB characteristic 2change of chroma input burst signal(0 dB = 150 mV p-p)Color killer set point e KS Input level at killer ON with chroma input burst–45–39–33dBsig. (0 dB = 150 mV p-p) being attenuatedColor residual of color killer e KR Residual level of chroma output in Killer ON--15mV p-pstate when chroma input burst signal of150 mV p-p is inputChroma output level E COUT Chroma output level when chroma input burst 1.1 1.3 1.5V p-psignal of 150 mV p-p is inputColor killer output E CKOH (1)High level of color killer output at color killer 2.7 3.5-V High level (1)OFFI OH = –400 µAColor killer output E CKOH (2)High level of color killer output at color killer 3.5 4.0-V High level (2)OFFI OH = –20 µAColor killer output E CKOL Low level of color killer output at color killer ON-0.20.4V Low level I OL = +2 mAAPC lock-in range f P Frequency pulled by APC with chroma input±400±600-Hzburst frequency changed (f SC conversion)VCO control sensitivityβP Rate of variation of frequency when APC filter8.010.012.0Hz/mVpin is changed from –0.025 V to +0.025 V(f SC conversion)Phase variable rangeθCONT Amount of phase shift when voltage of phase±40±55-degcontrol pin is set at 2.5 V + 1 VVCO output level e VCOO VCO output level when chroma input burst 1.0 1.3 1.6V p-psignal of 150 mV p-p is inputf SC output level e SCO f SCO output level when chroma input burst210300390mV p-psignal of 150 mV p-p is inputDivider select voltage VDIVSL1/4 freq. division if V DIVS < V DIVSL--0.5VV DIVSH EXT IN with V DIVS : OPEN4.5--V 1/8 freq. division if V DIVSH < V DIVSNTSC/PAL select voltage V N/PT f V = 60 Hz if V N/P < V N/PT 1.7 2.0 2.3Vf V = 50 Hz if V N/PT < V N/PSync sectionParameter Symbol Condition MIN.TYP.MAX.UnitSupply current I CC (1)V CC (1) = 5 V121518mA of Sync section No current on pin 25DC level of H sync V SSI Voltage of pin 36 when connected to GND via 1.9 2.2 2.5V separation input10 kΩ resistorDC level of V sync V VSSI Voltage of pin 34 when connected to GND via 1.9 2.2 2.5V separation input10 kΩ resistorSync separation output E CSOH1High level of sync separation output when only 2.7 3.8-V High level (1)0.3 V p-p sync signal is input to pin 36I OH = –400 µASync separation output E CSOH2High level of sync separation output when only 3.5 4.3-V High level (2)0.3 V p-p sync signal is input to pin 36I OH = –20 µASync separation output E CSOL Low level of sync separation output when only-0.10.4V Low level0.3 V p-p sync signal is input to pin 36I OL = +2 mAHD output E NHSOH1High level of synchronized HD output when 2.7 3.8-V High level (1)only 0.3 V p-p sync signal is input to pin 36I OH = –400 µAHD output E NHSOH2High level of synchronized HD output when 3.5 4.3-V High level (2)only 0.3 V p-p sync signal is input to pin 36I OH = –20 µAHD output E NHSOL High level of synchronized HD output when-0.10.4V Low level only 0.3 V p-p sync signal is input to pin 36I OL = +2 mAVD output E VSOH1High level of synchronized VD output when 2.7 3.8-V High level (1)only 0.3 V p-p sync signal is input to pin 36I OH = –400 µAVD output E VSOH2High level of synchronized VD output when 3.5 4.3-V High level (2)only 0.3 V p-p sync signal is input to pin 36I OH = –20µAVD output E VSOL High level of synchronized VD output when-0.10.4V Low level only 0.3 V p-p sync signal is input to pin 36I OL = +2 mAClamp output E CPOH1High level of synchronized Clamp output when 2.7 3.8-V High level (1)only 0.3 V p-p sync signal is input to pin 36I OH = –400 µAClamp output E CPOH2High level of synchronized Clamp output when 3.5 4.3-V High level (2)only 0.3 V p-p sync signal is input to pin 36I OH = –20 µAClamp output E CPOL High level of synchronized Clamp output when-0.10.4V Low level only 0.3 V p-p sync signal is input to pin 36I OL= +2 mAParameter Symbol Condition MIN.TYP.MAX.UnitField ident. output E FIOH1High level of synchronized Field ident. output 2.7 3.8-V High level (1)when only 0.3 V p-p sync signal is input to pin 36I OH = –400 µAField ident. output E FIOH2High level of synchronized Field ident. output 3.5 4.3-V High level (2)when only 0.3 V p-p sync signal is input to pin 36I OH = –20 µAField idnet. output E FIOL High level of synchronized Field ident. output-0.10.4V Low level when only 0.3 V p-p sync signal is input to pin 36I OL = +2 mAH detection output E FIOH1High level of asynchronized H detect output 2.7 3.8-V High level (1)without H sync inputI OH = –400 µAH detection output E FIOH2High level of asynchronized H detect output 3.5 4.3-V High level (2)without H sync inputI OH = –20 µAH detection output E FIOL High level of synchronized H detect output-0.10.4V Low level when only 0.3 V p-p sync signal is input to pin 36I OL= +2 mAH sync lock-in range f HP Frequency range that can be pulled when only±400±500-Hz0.3 V p-p sync signal is input to pin 36 and Hsync frequency is varied (f SC conversion)Horizontal VCO controlβH Rate of variation of frequency when APC filter–1.6–1.3–0.9Hz/mV sensitivity pin is changed form 3.0 V to 3.4 V without Hsync input (f SC conversion)Horizontal VCO free-run f HO Frequency difference of HD output from f H–100–25+50Hz frequency when H sync input is not appliedPulse width of HD output P WNHSO Pulse width of synchronized HD output when 3.8 4.0 4.2µsonly 0.3 V p-p sync signal is input to pin 36Pulse width of VD output P WVSO1Pulse width of synchronized VD ODD- 6.0-H NoteP WVSO2output when only 0.3 V p-p syncEVEN- 5.5-H Note signal is input to pin 36Pulse width of Clamp output P WCPO Pulse width of synchronized Clamp output when 3.4 3.6 3.8µsonly 0.3 V p-p sync signal is input to pin 36Oscillation start voltage of V ST Output voltage at HD when V CC is gradually-- 4.2V horizontal VCO increased from 0 V without H sync inputH killer output Low level E HKOL Low level of synchronized H killer output when--0.4Vonly 0.3 V p-p sync signal is input to pin 36Change value of Chroma outputBurst gate input V BGPE1Burst gate pulse input voltage when Clamp 1.6 1.9 2.0V Threshold level 1voltage begins Low level is gradually increasedfrom 0 V without signal inputNote H: Horizontal scanning period21Parameter Symbol Condition MIN.TYP.MAX.UnitBurst gate input V BGPE2Burst gate pulse input voltage when Clamp 3.8 4.0 4.2V Threshold level 2voltage begins High level is graduallyincreased from V BGPE1 without signal inputVertical free-running f V1 (50)Frequency ratio of HD output to VD output-f H/352-Hz frequency 1H sync input: No signalf V1 (60)Pin 33 input: V CC-f H/288-HzV sync input: V CCVertical free-running f V2 (50)Same as f V1 with the following exception-f H/288-Hz frequency 2f V2 (60)V sync input: GND-f H/240-Hz Vertical free-running f V3 (50)Same as f V1 with the following exception-f H/368-Hz frequency 3f V3 (60)Pin 33 input: GND-f H/296-Hz Vertical free-running f V4 (50)Same as f V1 with the following exception-f H/272-Hzfrequency 4f V4 (60)Pin 33 input: GND-f H/232-Hz V sync input: GND22TIMING CHARTS (Horizontal Period)Comp VideoInputComp SyncOutput(CSO)HD Output(NHSO)CLAMPOutput(CPO)23CAUTION AT DESIGNINGResonatorsNEC evaluates µPC1862 using resonators which are shown below in design and development process.If the different product is used as a resonator, electrical specification value described in this document is not assured.And when connecting resonator to external circuit, there is need to consider temperature specification, voltage fluctuation and product variation. In this case, normal operation is not assured in the application circuit including the different product.Use the resonators which are shown below when you design circuit.32 f H VCO resonator X1:in application example circuitX1(PAL):CSB500F2 (MURATA)(NTSC):CSB503F2 (MURATA)nf SC VCO resonator X2X2:HC-49/U (KINSEKI, µPC1860 adoption)Reference data of 4f SC, 8f SC VCO resonator (KINSEKI)Item NTSC for 4f SC NTSC for 8f SC PAL for 4f SCName HC-49/UFrequency14.31818 MHz28.63636 MHz17.34475 MHzOvertone Order Fundamental (AT cut)Fundamental (BT cut)Fundamental (AT cut)Operating Temperature–10 to +70°CFrequency Permitted±30 × 10–6±50 × 10–6±30 × 10–6 Tolerance (25±5°C)Frequency Temperature±30 × 10–6±100 × 10–6±30 × 10–6 Specification (to 25°C)Equivalent Serial Resistance50 Ω or lessParallel Capacitance7.0 pF or less3rd harmonic standard3rd harmonic frequency is over–3rd harmonic frequency is over3f O (42.95454 MHz) + 7.5 kHz3f O (53.203425 MHz) + 7.5 kHz25Recommended patternThe µPC1862 generates system clock for synchronous signal processing and clock generate processing.If the supply voltage, line placement and routing are not set appropriately that the µPC1862 cannot generate correct system clock.Though the recommended pattern is not shows in this document, note points shown below at designing.1.For synchronous section and chroma section, each power supply must be isolated.2.Lines to pin 9 to pin 13 should be as thick and short as possible.3.Connect resonator as near IC as possible. Don’t put GND line between resonator pins for parasitism capacitance. 2628Care Point for Planning of Application Circuit 1.Processing of V CC pinPlease isolate Chroma. V CC from Sync. V CC as follows. If you have external processing block of digital signal, don’t directly supply of the block’s V DD .2.Application of no using Chroma pinIf you don’t use Chroma pin but use Sync pin on µPC1862, you process pin 1 to pin 18 as follows.3.Application of no using Sync pinIf you don’t use Sync pin but use Chroma pin on µPC1862, you process pin 19 to pin 36 as follows. In this case, you need to input a pin 24 with burst gate pulse from external.In this application, you can’t use output of pin 20 to pin 23.F0.01 F µµinput29PACKAGE DRAWING36 PIN PLASTIC SHRINK SOP (300 mil)detail of lead end5°±5P36GM-80-300B-3ITEM MILLIMETERS INCHES A B C D E F G H I J K 15.54 MAX.0.8 (T.P.)1.8 MAX.1.557.7±0.30.97 MAX.0.612 MAX.0.005±0.0030.071 MAX.0.303±0.0120.2200.039 MAX.NOTEL M 0.100.6±0.21.15.60.0040.024+0.008–0.009Each lead centerline is located within 0.10mm (0.004 inch) of its true position (T .P.) at maximum material condition.0.0430.0610.031 (T.P.)0.20+0.10–0.050.008+0.004–0.002N0.100.0040.014+0.004–0.0030.350.125±0.075+0.10–0.05RECOMMENDED SOLDERING CONDITIONSWhen soldering this product, it is highly recommended to observe the conditions as shown below. If other soldering processes are used, or if the soldering is performed under different conditions, please make sure to consult with our sales offices.For more details, refer to our document “SEMICONDUCTOR DEVICE MOUNTING TECHNOLOGY MANUAL”(C10535E).Surface Mount DeviceµPC1862GS: 36-pin plastic shrink SOP (300 mil)Process Conditions SymbolInfrared ray reflow Peak temperature: 235 °C or below (Package surface temperature),IR35-00-2Reflow time: 30 seconds or less (at 210 °C or higher),Maximum number of reflow processes: 2 times.VPS Peak temperature: 215 °C or below (Package surface temperature),VP15-00-2Reflow time: 40 seconds or less (at 200 °C or higher),Maximum number of reflow processes: 2 times.Wave Soldering Solder temperature: 260 °C or below, Flow time: 10 seconds or less,WS60-00-1Maximum number of flow process: 1 time,Pre-heating temperature: 120 °C or below (Package surface temperature).Partial heating method Pin temperature: 300 °C or below,–Heat time: 3 seconds or less (Per each side of the device).Caution Apply only one kind of soldering condition to a device, except for “Partial heating method”, or the device will be damaged by heat stress.30[MEMO]31[MEMO]The application circuits and their parameters are for reference only and are not intended for use in actual design-ins.No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from useof such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customers must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.NEC devices are classified into the following three quality grades:"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications ofa device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.Standard:Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronicequipment and industrial robotsSpecial:Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designedfor life support)Specific:Aircrafts, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.The quality grade of NEC devices is "Standard" unless otherwise specified in NEC's Data Sheets or Data Books.If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact an NEC sales representative in advance.Anti-radioactive design is not implemented in this product.M4 96.5。

33389资料

Document Number: MC33389Rev. 5.0, 3/2007Freescale Semiconductor Advance Information* This document contains certain information on a new product.Specifications and information herein are subject to change without notice.© Freescale Semiconductor, Inc., 2007. All rights reserved.System Basis Chip with Low Speed Fault Tolerant CANThe 33389 is a monolithic integrated circuit combining manyfunctions frequently used by automotive Engine Control Units (ECUs). It incorporates a low speed fault tolerant CAN transceiver.Features•Dual Low Drop Voltage Regulators, with Respectively 100 mA and 200 mA Current Capabilities, Current Limitation, and Over Temperature Detection with Pre-warning • 5.0 V Output Voltage for V1 Regulator•Three Operational Modes (Normal, Stand-by, and Sleep Modes) Separated from the CAN Interface Operating Modes•Low Speed 125 kBaud Fault Tolerant CAN Interface, Compatible with 33388 Stand Alone Physical Interface •V1 Regulator Monitoring and Reset Function•Three External High Voltage Wake-Up Inputs, Associated with V3 V BAT Switch•100 mA Output Current Capability for V3 V BAT Switch Allowing Drive of External Switches or Relays•Low Stand-by and Sleep Current Consumption•V BAT Monitoring and V BAT Failure Detection Capabilities •DC Operating Voltage up to 27 V •40 V Maximum Transient Voltage•Programmable Software Window Watchdog and Reset•Wake-Up Capabilities (CAN Interface, Local Programmable Cycle Wake•INterface with the MCU through the SPI•Pb-Free Packaging Designated by Suffix Codes VW and EGFigure 1. 33389 Simplified Application DiagramSYSTEM BASIS CHIP33389ORDERING INFORMATIONDevice Temperature Range (T A )PackageMC33389CDH/R2-40 to 125°CHSOP-20MC33389CVW/R2MC33389CDW/R2SO-28MC33389DDW/R2Analog Integrated Circuit Device Data33389DEVICE VARIATIONSDEVICE VARIATIONSTable 1. Device VariationsFreescale Part No.V1 UndervoltageMC33389CDH MC33389CVW MC33389CDW In V1 undervoltage condition, device remains in permanent reset state until V1 returns to normal conditions. V1 is protected by overcurrent and overtemperature functions.MC33389DDWThe sole difference between the C version and the D version is V1 Reset Threshold. Reference V1 Reset Threshold on V1 on page 9.INTERNAL BLOCK DIAGRAMINTERNAL BLOCK DIAGRAMFigure 2. 33389 Simplified Internal Block Diagram33389 Analog Integrated Circuit Device DataAnalog Integrated Circuit Device Data33389PIN CONNECTIONSPIN CONNECTIONSFigure 3. 33389 Pin ConnectionsTable 1. 33389 Pin Definitions: HSOSP 20-LeadA functional description of each pin can be found in the Functional Pin Description section beginning on page 17.Pin NumberPin NameFormal Name Definition1TX Transmitter DataTransmitter input of the LS CAN interface2V1Voltage Regulator One This 5.0 V pin is a 3% low drop voltage regulator dedicated to the microcontroller supply.3RX Receiver DataReceiver output of the LS CAN interface 4RST Reset This is an Input/Output pin.5INT Interrupt Output This output is asserted LOW when an enabled interrupt condition occurs.6MISO Master In/Slave Out This pin is the tri-state output from the shift register. 7MOSI Master Out/Slave In This pin is for the input of serial instruction data. 8SCLK System Clock This pin clocks the internal shift registers.9CS Chip Select This pin communicates with the system MCU and enables SPI communication.10 - 12L0 - L2Level 0 - 2 inputs(L0: L2)Input interfaces to external circuitry. Levels at these pins can be read by SPI and input can be used as programmable wake-up input in Sleep or Stop mode.13RTH RTH Pin for the connection of the bus termination to CANH 14CANLCAN Low CAN low input/output15GND Ground This pin is the ground of the integrated circuit.16CANH CAN HighCAN high input/output17V2Voltage Regulator Two This 5.0 V pin is a low drop voltage regulator dedicated to the peripherals supply.18RTL RTL Pin for the connection of the bus termination to CANL 19VBAT Voltage Battery This pin is voltage supply from the battery.20V3Voltage RegulatorThreeThis pin is a 10 Ω switch to V BAT , used to supply external contacts or relays.Analog Integrated Circuit Device Data 33389PIN CONNECTIONSTable 2. 33389 Pin Definitions: SOICW 28-LeadA functional description of each pin can be found in the Functional Pin Description section beginning on page 17.Pin NumberPin Name Formal Name Definition1TXTransmitter Data Transmitter input of the LS CAN interface2V1Voltage Regulator OneThis 5.0 V pin is a 3% low drop voltage regulator dedicated to the microcontroller supply.3RXReceiver Data Receiver output of the LS CAN interface 4RST Reset This is an Input/Output pin.5INT Interrupt This output is asserted LOW when an enabled interrupt condition occurs.6 -9 20 - 23GND GroundThese device ground pins are internally connected to the package lead frame to provide a 33389-to-PCB thermal path.10MISO Master In/Slave OutThis pin is the tri-state output from the shift register. 11MOSIMaster Out/Slave In This pin is for the input of serial instruction data. 12SCLKSystem Clock This pin clocks the internal shift registers.13CS Chip Select This pin communicates with the system MCU and enables SPI communication.14, 15, 16L0: L2Wake-up Input (L0: L2)Input interfaces to external circuitry. Levels at these pins can be read by SPI and input can be used as programmable wake-up input in Sleep or Stop mode.17NCNo Connect This pin does not connect.18RTH Thermal Resistance High Pin for the connection of the bus termination to CANH 19CANLCAN Low CAN low input/output 24CANHCAN High CAN high input/output25V2Voltage Regulator TwoThis 5.0 V pin is a low drop voltage regulator dedicated to the peripherals supply.26RTL Thermal Resistance LowPin for the connection of the bus termination to CANL 27VBAT Voltage Battery This pin is voltage supply from the battery.28V3Voltage Regulator ThreeThis pin is a 10 Ω switch to V BAT , used to supply external contacts or relays.Analog Integrated Circuit Device Data33389ELECTRICAL CHARACTERISTICS MAXIMUM RATINGSELECTRICAL CHARACTERISTICSMAXIMUM RATINGSTable 3. Maximum RatingsAll voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.RatingsSymbol Value UnitELECTRICAL RATINGS DC Voltage at VBAT Pin V BAT -0.3 to 27V Transient Voltage at VBAT Pint < 500 ms (load dump)V BAT 40V DC Voltage at Pins CANH and CANL V BAT -20 to 27V Transient Voltage at Pins CANH and CANL 0.0 < V2 < 5.5, V BAT > 0.0, t < 500 msV BAT-40 to 40VCoupled Transient Voltage at Pins CANH and CANLWith 100 Ω Termination Resistors, Coupled Through 1.0 nF (1)V BAT-100 to 100 VDC Voltage at Pins V1 and V2V BAT -0.3 to 6.0V DC Current at Output Pins RX, MISO, RST, INT V BAT -20 to 20mA DC Voltage at Input Pins TX, MOSI, CS, RST V BAT -0.3 to 6.0V DC Voltage at Pins L0, L1, L20.0 < V BAT < 40 V V BAT-0.3 to 40VCurrent at Pins L0, L1, L2V BAT -15mA Transient Current at Pin V3V BAT -30 to 20mA DC Voltage at pins RTH and RTLV BAT -0.3 to 40V ESD Voltage on any Pin (HBM 100 pF, 1.5 K)V BAT -2.0 to 2.0kV ESD Voltage on L0, L1, L2, CANH, CANL, VBAT V BAT -2.0 to 2.0kV ESD Voltage on any Pin (MM 200 pF, 0 Ω)V BAT-150 to 150VTHERMAL RATINGSOperating Junction Temperature T J -40 to 150°C Ambient Temperature T A -40 to 125°C Storage TemperatureT S-55 to 165°CNotes1.Pulses 1, 2, 3a, and 3b according to ISO7637.Analog Integrated Circuit Device Data 33389ELECTRICAL CHARACTERISTICSMAXIMUM RATINGSTHERMAL RESISTANCERTH, RTL Termination ResistanceR RTHRTL 500 to 16 kΩJunction to Heatsink Thermal Resistance for HSOP-2033% Power on V1, 66% on V2 (including CAN) (2) R AJC3.1°C/WJunction to Pin Thermal Resistance for SO-28WD (3) R AS/P 17°C/W Thermal Shutdown TemperatureT SD 165°C Peak Package Reflow Temperature During Reflow (4), (5)T PPRTNote 5°CNotes2.Refer to thermal management in device description section.3.Refer to thermal management in device section. Ground pins 6, 7, 8, 9, 20, 21, 22, and 23 of SO28WB package.4.Pin soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits maycause malfunction or permanent damage to the device.5.Freescale’s Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For Peak Package ReflowTemperature and Moisture Sensitivity Levels (MSL),Go to , search by part number [e.g. remove prefixes/suffixes and enter the core ID to view all orderable parts. (i.e. MC33xxxD enter 33xxx), and review parametrics.Table 3. Maximum Ratings (continued)All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.RatingsSymbolValueUnitAnalog Integrated Circuit Device Data33389ELECTRICAL CHARACTERISTICSSTATIC ELECTRICAL CHARACTERISTICSSTATIC ELECTRICAL CHARACTERISTICSTable 4. Static Electrical CharacteristicsCharacteristics noted under conditions V BAT , - 40°C ≤ T A ≤ 125°C unless otherwise noted. Typical values noted reflect the approximate parameter means at T A = 25°C under nominal conditions unless otherwise noted.CharacteristicSymbol Min Typ Max UnitPOWER INPUT (VBAT)Nominal VBAT Operating Range V BAT 5.5—18V Functional VBAT Operating Range V BAT 5.5—27V V BAT Threshold for BAT FAIL Flag BAT FAIL2.0— 4.0V Delay for Signalling BAT FAIL TFAIL—150400µs Overvoltage V BAT Threshold BAT HIGH 182022V Delay for Setting BAT HIGH Flag T HIGH 4.01850µs Supply Current in Sleep ModeForced Wake-Up and Cyclic Sense Disabled V BAT = 12 V, T J = 25°C to 150°C I SLEEP1—75125µASupply Current in Sleep ModeForced Wake-Up and Cyclic Sense Disabled V BAT = 12 V, T J = -40°C to 25°C I SLEEP2——210µASupply Current in Sleep ModeForced Wake-Up and Cyclic Sense Enabled V BAT = 12 V, T J = 25°C to 150°C I SLEEP3—105155µASupply Current in Sleep ModeForced Wake-Up and Cyclic Sense Enabled V BAT = 12 V, T J = -40°C to 25°C I SLEEP4——250µASupply Current in Sleep ModeForced Wake-Up and Cyclic Sense Disabled V BAT = 12 V, T J = 25°C to 150°C I SLEEP5——300µASupply Current in Stand-by Mode I STB2—0.5 1.0mA Supply Current in Normal Mode Normal Mode with I(V1) = 1 I(V2) = 0Bus in Recessive State I NREC—3.57.0mAPOWER OUTPUT V1 Output Voltage 0 mA < I OUT < 100 mA 5.5 V < V BAT < 27 V V1NOM4.855.05.15VV1 Output Voltage I OUT =< 100 mA 27 V < V BAT < 40 V V14.85.05.2VV1 Drop Voltage I OUT =< 100 mA (6)V1DROP —0.350.5VNotes6.Measured when V1 has dropped 100mV below its nominal valueAnalog Integrated Circuit Device Data 33389ELECTRICAL CHARACTERISTICSSTATIC ELECTRICAL CHARACTERISTICSPOWER OUTPUT (CONTINUED) V1 Output Current Limitation V1NOM - 100 mVI1MAX130170200mAV1 Overtemperature Shut OFF Threshold Junction TemperatureTV1H 160—190°CV1 Pre-Warning Temperature Threshold Junction TemperatureTV1L 130—160°CV1 Temperature Threshold Difference TV1H-TV1L20—40°C V1 Reset Threshold on V15.5 V < V BAT < 27 V (C Version)(D Version)VR1 4.1V2 - 0.4 4.3V1 - 0.284.8V1 - 0.1VV1 Reset Active V1 RangeV1R 1.0VR1—V V1 Reverse Current from V1 to V BAT and GND V1 = 4.9 V, 0 < V BAT < 4.9 V IREV——1.0mAV2 Output Voltage0 mA < I OUT < 200 mA 5.5 V < V BAT < 40 V V2NOM 4.75 5.0 5.25 VV2 Drop Voltage I OUT = 200 mA (7)V2DROP —0.2 0.5VV2 Drop Voltage I OUT = 20 mA (7)V2DROP —0.050.15VV2 Output Current Limitation V2NOM -100 mVI1MAX220280350mAV2 Threshold on V2 to Report V2 OFF V2 Nominal V R24.14.554.75VV R2 Delay TimeV R220—70µs V2 Overtemperature Pre-Warning Threshold V2 Junction TemperatureT V2L130—160°CV2 Overtemperature Switch-OFF Threshold V2 Junction Temperature T V2H155—185°CV2 Line Regulation 9.0 V < V BAT < 16.5V2LR1-15—+15mVV2 Load Regulation 4.0 mA < I LOAD < 200 mA V2LR2-75—+75mVV2 Line Ripple Rejection 100 Hz, 1.0 V PP on V BAT (8)V2LRR3055—dBNotes7.Measured when V1 has dropped 100mV below its nominal value 8.Guaranteed by design; however, it is not production testedTable 4. Static Electrical Characteristics (continued)Characteristics noted under conditions V BAT , - 40°C ≤ T A ≤ 125°C unless otherwise noted. Typical values noted reflect the approximate parameter means at T A = 25°C under nominal conditions unless otherwise noted.CharacteristicSymbol Min Typ Max UnitAnalog Integrated Circuit Device Data33389ELECTRICAL CHARACTERISTICSSTATIC ELECTRICAL CHARACTERISTICSPOWER OUTPUT (CONTINUED) V2 Percentage Difference V2-V1V BAT > 9.0, I V1 = 20 mA, I V2 = 40 mA V2V2-V1-3.0—3.0%V3 High Level Voltage DropI V3 = -50 mA, 9.0 V < V BAT < 40 V V3DROP—0.41.0VV3 High Level Voltage DropI V3 = -50 mA, 6.0 V < V BAT < 9.0 V V3DROP——1.5VV3 Leakage Output Limitation 5.5 V < V BAT < 27 V I3LIM100150250mAV3 Leakage Current V3 = 0 (V3 OFF)I3LEAK——15µAV3 Overtemperature Detection Junction TemperatureT V3155—185°CV3 Voltage with -30 mA (negative current for Relay Switch OFF) No Functional Error Allowed for t < 100 msV V30.3—0.5VCAN Transceiver V2 for Forced Bus Stand-by Mode (Fail Safe) VRC2 3.0 3.9 4.7V CANH/L Differential Receiver, Threshold VoltageV CANTH -3.2—-2.5V CANH/L Differential Receiver, Dominant to Recessive Threshold (Bus Failures 1, 2, and 5)V CANDRTH-3.2—-2.5VCANH Recessive Output Voltage TX = High, R(RTH) < 4.0 k V CANH——0.2VCANL Recessive Output Voltage TX = High, R(RTH) < 4.0 k V CANLV2-0.2——VCANH Output Voltage, DominantTX = 0 V, BusNormal Mode, I CANH = - 40 mA V CANHV2-1.4——VCANL Output Voltage, DominantTX = 0 V, Bus Normal Mode, I CANL = - 40 mA V CANL——1.4VCANH Output Current Limit (V CANH = 0.0 V, TX = 0)I CANH5075100mACANL Output Current Limit (V CANL = 14 V, TX = 0)I CANL5095130mADetection Threshold for Short Circuit to Battery Voltage Bus Normal ModeV CANH -V CANL7.37.98.9VDetection Threshold for Short Circuit to Battery Voltage Bus Stand-by ModeV CANHV BAT /2+3—V BAT /2+5VCANH Output Current, Failure 3Bus Stand-by Mode V CANH = 12 V I CANHF3—5.010µACANL Output Current, Failure 4Bus Stand-by Mode, V CANL = 0.0 V, V BAT = 12 VI CANLF4—0.02.0µATable 4. Static Electrical Characteristics (continued)Characteristics noted under conditions V BAT , - 40°C ≤ T A ≤ 125°C unless otherwise noted. Typical values noted reflect the approximate parameter means at T A = 25°C under nominal conditions unless otherwise noted.CharacteristicSymbolMinTypMaxUnitELECTRICAL CHARACTERISTICSSTATIC ELECTRICAL CHARACTERISTICSPOWER OUTPUT (CONTINUED)CANL Wake-Up Voltage ThresholdBus Stand-by ModeV WAKEL 2.5 3.3 3.9VCANH Wake-Up Voltage ThresholdBus Stand-by ModeV WAKEH 1.2 2.0 2.7VWake-Up Threshold Difference V WAKEL -V WAKEH0.2——V CANH Single Ended Receiver ThresholdFailures 4, 6, and 7V CANH 1.5 1.85 2.15VCANL Single Ended Receiver ThresholdFailures 3 and 8V CANL 2.8 3.05 3.4VCANL Pull-Up CurrentBus Normal ModeI CANLPU457590µACANH Pull Down CurrentBus Normal ModeI CANLPD457590µA Receiver Differential Input Impedance CANH/CANL R DIFF100—180kΩDifferential Receiver Common Mode Voltage Range V COM-8.0—8.0V RTL to V2 Switch on ResistanceI OUT < -10 mA, Bus Normal Operating ModeR RTL102570ΩRTL to Battery Switch Series ResistanceBus Stand-by ModeR RTL8.012.520kΩRTH to Ground Switch on ResistanceI OUT < 10 mA, All ModesR RTH—2570ΩCONTROL INTERFACEHigh Level Input Voltage VIH0.7 V1—V1 + 0.3 V VCS Threshold for SPI Wake-UpSBC in Sleep Mode, V1 < 1.5 VV CSTH— 2.2—VCS Filter Time for SPI Wake-UpSBC in Sleep Mode, V1 < 1.0 Vt CSFT—— 3.0µsLow Level Input Voltage VIL-0.3—0.3 V1V High Level Input Current on CSV I = 4.0 VI CSH-100—-20µALow Level Input Current on CSV I = 1.0 VI CSL-100—-20µATX High Level Input CurrentV I = 4.0 VI TXH-200-80-25µATX Low Level Input CurrentV I = 1.0 VI TXL-800-320-100µASI, SCLK Input Current0 < V IN < V1I SISLK-10—+10µATable 4. Static Electrical Characteristics (continued)Characteristics noted under conditions V BAT, -40°C ≤ T A ≤ 125°C unless otherwise noted. Typical values noted reflect the approximate parameter means at T A = 25°C under nominal conditions unless otherwise noted.Characteristic Symbol Min Typ Max UnitELECTRICAL CHARACTERISTICSSTATIC ELECTRICAL CHARACTERISTICSCONTROL INTERFACE (CONTINUED)RX, INT, MISO High Level Output Voltage I 0 = -250 µAV OHV1 - 0.9—V1VRX, INT, MISO Low Level Output Voltage I 0 = -1.5 mAV OL0.0—0.9VRX, INT, MISO Tri-Stated SO Output Current 0 V < V SO < V1I Z-2.0—+2.0µARST High Level Input Voltage V IH 0.7 V1—V1 + 0.3 V —RST Low Level Input Voltage V IL -0.3—-0.3 V1V RST High Level Output Current 10.0 < V OUT < 0.5 V1I RSTH1-50-30-10µARST High Level Output Current 20.5 < V OUT < V1I RSTH2—-300—µARST Low Level Output Voltage (I 0 = 1.5 mA)1.0 V < V BAT < 27 VV RST0.0—0.9VLX/Wake-Up Positive Switching Threshold 6.0 V <V BAT < 16 VV WUP3.03.74.5VLX/Wake-Up Negative Switching Threshold 6.0 V <V BAT < 16 V V WUN2.53.03.8VLX/Wake-Up Hysteresis 6.0 V <V BAT < 16 VV HYS—700—mALX/Wake-Up Leakage Current 0 < V WU < V BAT I LXWU -5.0—+5.0µA LX Input Current at 40 VV IN—350600µATable 4. Static Electrical Characteristics (continued)Characteristics noted under conditions V BAT , - 40°C ≤ T A ≤ 125°C unless otherwise noted. Typical values noted reflect the approximate parameter means at T A = 25°C under nominal conditions unless otherwise noted.CharacteristicSymbolMinTypMaxUnitELECTRICAL CHARACTERISTICSDYNAMIC ELECTRICAL CHARACTERISTICSDYNAMIC ELECTRICAL CHARACTERISTICSTable 5. Dynamic Electrical CharacteristicsCharacteristics noted under conditions 7.0 V ≤ V SUP≤ 18 V, - 40°C ≤ T A ≤ 125°C, GND = 0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at T A = 25°C under nominal conditions unless otherwise noted.Characteristic Symbol Min Typ Max Unit MICROCONTROLLER INTERFACEAC CANL/CANH Slew Rates, Rising or Falling Edges, TX from Recessive toDominant StateC LOAD - 10 nF, 133 Ω Termination Resistorst CANRD 3.5 5.010V/µsAC CANL/CANH Slew Rates, Rising or Falling Edges, TX from Dominant toRecessive StateC LOAD - 10 nF, 133 Ω Termination Resistorst CANDR 2.0 3.510V/µsAC Propagation Delay TX to RX LowC LOAD - 10 nF, 133 Ω Termination Resistorst DH— 1.2 2.0µsAC Propagation Delay TX to RX HighC LOAD - 10 nF, 133 Ω Termination Resistorst DL— 2.0 3.0µsWake-Up Filter Time tWUFT8.02038µs RST Duration after V1 High t RES— 1.0—ms SCLK Clock Period t PSCLK500——ns SCLK Clock High Time t WSCLKH175——ns SCLK Clock Low Time t WSCLKL175——ns Falling Edge of CS to Rising Edge of SCLK t LEAD25050—ns Falling Edge of SCLK to Rising Edge of CS t LEAD25050—nsSI to Falling Edge of SCLK t SISU12525—ns Falling Edge of SCLK to SI t SI(HOLD)12525—nsSO Rise Time (C L = 200 pF)t RSO—2575nsSO Fall Time (C L = 200 pF)t FSO—2575ns SI, CS, SCLK Incoming Signal Rise Time t RSI——200ns SI, CS, SCLK Incoming Signal Fall Time t FSI——200—Time from Falling Edge of CS to SOLow Impedance High Impedance t SO(EN)t SO(DIS)——200200nsTime from Rising Edge of SCLK to SO Data Valid0.2 V1 or V2 < SO > 0.8 V1 or V2, C L = 200 pFt VALID—50125—Running Mode Oscillator Tolerance (Normal Request, Normal and Stand-byModes (9))RMOT-12—+12%Software Watchdog Timing 1 (9)tSW1 4.4 5.0 5.6msSoftware Watchdog Timing 2 (9)tSW28.81011.2msSoftware Watchdog Timing 3 (9)tSW317.62022.4msSoftware Watchdog Timing 4 (9)tSW4283236ms Notes9.Software watchdog timing accuracy is based on the running mode oscillator toleranceELECTRICAL CHARACTERISTICSDYNAMIC ELECTRICAL CHARACTERISTICSMICROCONTROLLER INTERFACE (CONTINUED)Software Watchdog Timing 5 (10)t SW544.85158ms Software Watchdog Timing 6 (10)t SW6657483ms Software Watchdog Timing 7 (10)t SW788100112ms Software Watchdog Timing 8 (10).t SW8167190213ms Sleep Mode Oscillator Tolerance (10)SMOT -30—+30%Cyclic Sense/FWU Timing 1 Sleep Mode (10)t CY122.43246.6ms Cyclic Sense/FWU Timing 2 Sleep Mode (10)t CY244.86483.2ms Cyclic Sense/FWU Timing 3 Sleep Mode (10)t CY389.6128166.4ms Cyclic Sense/FWU Timing 4 Sleep Mode (10)t CY4179256333ms Cyclic Sense/FWU Timing 5 Sleep Mode (10)t CY5358512665ms Cyclic Sense/FWU Timing 6 Sleep Mode (10).t CY671710241331ms Cyclic Sense/FWU Timing 7 Sleep Mode (10) t CY7143420482662ms Cyclic Sense/FWU Timing 8 Sleep Mode (10)t CY85734819210650ms Ground Shift Threshold 1 (11)CAN Transceiver Active in Two Wire Operation GS1-1.0-0.7-0.3VGround Shift Threshold 2 (11)CAN Transceiver Active in Two Wire Operation GS2-1.5-1.2-0.8VGround Shift Threshold 3 (11)CAN Transceiver Active in Two Wire Operation GS3-2.0-1.7-1.3VGround Shift Threshold 4 (11)CAN Transceiver Active in Two Wire Operation GS4-2.6-2.2-1.7VBUS TRANSMITTERAC Minimum Dominant Time for Wake-Up on CANL or CANH Bus Stand-by Mode, V BAT = 12 V t WAKE4.0—40µsAC Failure 3 Detection Time Bus Normal Mode t AC3D10—60µsAC Failure 3 Recovery Time Bus Normal Mode t AC3R10—60µsAC Failure 6 Detection Time Bus Normal Mode t AC6D50—400µsAC Failure 6 Recovery Time Bus Normal Modet AC6R150—1000µsAC Failure 4, 7, and 8 Detection Time Bus Normal Modet AC478D0.75—4.0msNotes10.Cyclic sense and forced wake-up timing accuracy are based on the Sleep mode oscillator tolerance.11.No overlap between two adjacent thresholds.Table 5. Dynamic Electrical Characteristics (continued)Characteristics noted under conditions 7.0 V ≤ V SUP ≤ 18 V, - 40°C ≤ T A ≤ 125°C, GND = 0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at T A = 25°C under nominal conditions unless otherwise noted.CharacteristicSymbolMinTypMaxUnitELECTRICAL CHARACTERISTICSDYNAMIC ELECTRICAL CHARACTERISTICSBUS TRANSMITTER (CONTINUED)AC Failure 4, 7, and 8 Recovery Time Bus Normal Modet AC478R10—60µsAC Failure 3, 4, and 7 Detection Time Bus Stand-by Mode, V BAT = 12 V t AC347D0.8—8.0msAC Failure 3, 4 and 7 Recovery Time Bus Stand-by Mode, V BAT = 12 Vt AC347R—2.5—msAC Edge Count Difference Between CANH/CANL for Failures 1, 2, 5 Detection Bus Normal ModeCAN 125D—3.0——AC Edge Count Difference Between CANH/CANL for Failures 1, 2, 5 Recovery Bus Normal ModeCAN 125R—3.0——TX Permanent Dominant Timer Disable Time Bus Normal and Failure Modes t TXD0.75—4.0msPOWER INPUT TIMING V1 Reset Delay Time t D 2.0—20µs V1 Line Regulation9.0 V < V BAT < 16.5, I LOAD = 10 mA t D -152.0+15mVV1 Line Regulation5.5 V < V BAT < 27 V I LOAD = 10 mA t D -5010+50mVV1 Load Regulation1.0 mA < I LOAD < 100 mA t D -50—+50mVV1 Line Ripple Rejection100 Hz, 1.0 V PP on V BAT = 12 V, I LOAD = 100 mA (12)t D 3055—dBV1 Line Transient ResponseV BAT from 12 V to 40 V in 1.0 µs, (10 µF, ESR = 3 Ω)t D —27—mVV1 Load Transient ResponseI LOAD from 10 µA to 100 mA in 1.0 µs (CLOAD = 10 µF, ESR = 3 Ω) (13)t D —400—mVV1 Load Transient ResponseI LOAD from 10 µA to 100 mA in 1.0 µs (CLOAD = 10 µF, ESR= 0.1 Ω)t D—16—mVNotes12.Guaranteed by design. Not production tested.13.This condition does not produce a resetTable 5. Dynamic Electrical Characteristics (continued)Characteristics noted under conditions 7.0 V ≤ V SUP ≤ 18 V, - 40°C ≤ T A ≤ 125°C, GND = 0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at T A = 25°C under nominal conditions unless otherwise noted.CharacteristicSymbolMinTypMaxUnitELECTRICAL CHARACTERISTICS TIMING DIAGRAMSTIMING DIAGRAMSFigure 4. Input Timing Switch CharacteristicsSISCLKCSDon’t Care Don’t CareDon’t CareValidValidt LEAD t WSCLKH t WSCLKLt R t F t LAGt SISUt SI(HOLD)FUNCTIONAL DESCRIPTIONINTRODUCTION FUNCTIONAL DESCRIPTIONINTRODUCTIONThe System Basis Chip (SBC) is an integrated circuit dedicated to car body applications. It includes three main blocks:1. A dual voltage regulator2.Reset, watchdog, wake-up inputs, cyclic wake-up3.CAN low speed fault tolerant physical interfaceSuppliesTwo low drop regulators and one switch to V BAT are provided to supply the ECU microcontroller or peripherals, with independent control and monitoring through SPI.FUNCTIONAL PIN DESCRIPTIONTRANSMIT AND RECEIVE DATA (TX AND RX) The RX and TX pins (receive data and transmit data pins, respectively) are connected to a microcontroller’s CAN protocol handler. TX is an input and controls the CANH and CANL line state (dominant when TX is LOW, recessive when TX is HIGH). RX is an output and reports the bus state.VOLTAGE REGULATOR ONE AND TWO(V1 AND V2)The V1 pin is a 3% low drop voltage regulator dedicated to the microcontroller supply (nominal 5V supply).The V2 pin is a low drop voltage regulator dedicated to the peripherals supply (nominal 5V supply).RESET (RST)The RST (reset) pin is an input/output pin. The typical reset duration from SBC to microcontroller is 1ms. If longer times are required, an external capacitor can be used. SBC provides two RST output pull-up currents. A typical 30µA pull up when Vreset is below 2.5V and a 300uA pull up when reset voltage is higher than 2.5V. RST is also an input for the SBC. It means the MC33389 is forced to Normal Request mode after RST is released by the microcontroller INTERRUPT (INT)The Interrupt pin INT is an output that is set LOW when an interrupt occurs. INT is enabled using the Interrupt Register (INTR). When an interrupt occurs, INT stays LOW until the interrupt source is cleared.INT output also reports a wake-up event.GROUND (GND)This pin is the ground of the integrated circuit.MASTER IN/ SLAVE OUT (MISO)MISO is the Master In Slave Out pin of the serial peripheral interface. Data is sent from the SBC to the microcontroller through the MISO pin.MASTER OUT/ SLAVE IN (MOSI)MOSI is the Master Out Slave In pin of the serial peripheral interface. Control data from a microcontroller is received through this pin.SYSTEM CLOCK (SCLK)This pin clocks the internal shift registers for SPI communication.CHIP SELECT (CS)CS is the Chip Select pin of the serial peripheral interface (SPI). When this pin is LOW, the SPI port of the device is selected.LEVEL 0-2 INPUTS (L0: L2)The L0: L2 pins can be connected to contact switches or the output of other ICs for external inputs. The input states can be read by the SPI. These inputs can be used as wake-up events for the SBC.NO CONNECT (NC)No pin connection.TERMINATION RESISTANCE (HIGH AND LOW?) (RTH AND RTL)External CAN bus high and low termination resistance pins are connected to these pins.CAN HIGH AND CAN LOW OUTPUTS(CANH AND CANL)The CAN High and CAN Low pins are the interfaces to the CAN bus lines. They are controlled by TX input level, and the state of CANH and CANL is reported through RX output. VOLTAGE BATTERY (VBAT)This pin is the voltage supply from the battery.VOLTAGE REGULATOR THREE (V3)This pin is a 10 Ω switch to VBAT, which is used to supply external contacts or relays.。

CDCE925 时钟芯片

Based on the PLL frequency and the divider settings, the internal loop filter components are automatically adjusted to achieve high stability and optimized jitter transfer characteristic of each PLL.

16 Xout 15 S1/SDA 14 S2/SCL 13 Y1 12 GND 11 Y2 10 Y3

9 Vddout

1

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. DaVinci, OMAP, Pro-Clock are trademarks of Texas Instruments.

国际贸易标准分类(简)

国际贸易标准分类(Standard International Trade Classification,简称:SITC)为用于国际贸易商品的统计和对比的标准分类方法。

现行“国际贸易标准分类”于1950年7月12日由联合国经济社会理事会正式通过,目前为世界各国政府普遍采纳的商品贸易分类体系。

到2006年为止,该标准分类经历了四次修改,最近的一次修改为第四次修订版,于2006年3月获联合国统计委员会第三十七届会议通过。

该分类法将商品分为为10大类、63章、223组、786个分组和1924个项目。

在它的编号中第一位数字表示类、第二位数字表示章、第三位数字表示组、第四位数字表示分组。

如果对分组再进行细分,五位数即表示品目,六位数字表示细目。

具体分类0 -食品和活畜00 -活的动物以外的其他动物的分裂00 - Live animals other than animals of division01 -肉及肉制品 01 - Meat and meat preparations02 -乳制品和鸟蛋 02 - Dairy products and birds' eggs03 -鱼(不是海洋哺乳动物),甲壳类,软体动物和水生无脊椎动物 03 - Fish (not marine mammals), crustaceans, molluscs and aquatic invertebrates, and preparations thereof04 -谷物和谷物制品 04 - Cereals and cereal preparations05 -蔬菜和水果 05 - Vegetables and fruit06 -糖,糖制品及蜂蜜 06 - Sugars, sugar preparations and honey07 -咖啡,茶,可可,香料,及其制造 07 - Coffee, tea, cocoa, spices, and manufactures thereof08 -喂养(不包括没有碾磨的谷物)08 - Feeding stuff for animals (not including unmilled cereals)09 -杂项食品产品和筹备工作09 - Miscellaneous edible products and preparations1 -饮料和烟草1 - Beverages and tobacco11 -饮料11 - Beverages12 -烟草及烟草制品 12 - Tobacco and tobacco manufactures2 -粗材料,不能食用,除燃料2 - Crude materials, inedible, except fuels21 -皮,表皮和毛皮,原料 21 - Hides, skins and furskins, raw22 -石油种子和含油果实 22 - Oil-seeds and oleaginous fruits23 -天然橡胶(包括合成和再生)23 - Crude rubber (including synthetic and reclaimed)24 -软木及木 24 - Cork and wood25 -纸浆及废纸 25 - Pulp and waste paper26 -纺织纤维(毛条除外和其他精梳羊毛)及其废料(不成纱或布料制造的)26 - Textile fibres (other than wool tops and other combed wool) and their wastes (not manufactured into yarn or fabric)27 -原油肥料,矿产和原油(不包括煤,石油和宝石)27 - Crude fertilizers, other than those of division 56, and crude minerals (excluding coal, petroleum and precious stones)28 -金属矿砂及金属废料 28 - Metalliferous ores and metal scrap29 -原油动物和植物材料制2 9 - Crude animal and vegetable materials, nes3 -矿物燃料,润滑剂和相关材料 3 - Mineral fuels, lubricants and related materials32 -煤,焦煤及煤球 32 - Coal, coke and briquettes33 -石油,石油产品及副产品 33 - Petroleum, petroleum products and related materials34 -天然气(天然和制造的) 34 - Gas, natural and manufactured35 -电流 35 - Electric current4 -动物和植物油,油脂和蜡 4 - Animal and vegetable oils, fats and waxes41 -动物油脂 41 - Animal oils and fats42 -固定油脂,原油,成品或分馏 42 - Fixed vegetable fats and oils, crude, refined or fractionated43 -动物或植物油脂,加工过的;不宜食的混合物或动物或植物脂肪或油类,不另说明 43 - Animal or vegetable fats and oils, processed; waxes of animal or vegetable origin; inedible mixtures or preparations of animal or vegetable fats or oils, n.e.s5 -化学品及有关产品,不另说明 5 -Chemicals and related products, n.e.s.51 -有机化工产品 51 - Organic chemicals52 -无机化学品 52 - Inorganic chemicals53 -染料,鞣革料 53 - Dyeing, tanning and colouring materials54 -医药产品 54 - Medicinal and pharmaceutical products55 -精油及香膏和香水原料;厕所,抛光和清洗的准备工具 55 - Essential oils and resinoids and perfume materials; toilet, polishing and cleansing preparations56 -肥料(除组272) 56 - Fertilizers (other than those of group 272)57 -初级形状塑料 57 - Plastics in primary forms58 -在非塑料,初级形状 58 - Plastics in non-primary forms59 -化学材料及制品,不另说明 59 - Chemical materials and products, n.e.s6 -主要以材料分类的制成品 6 - Manufactured goods classified chiefly by material61 -皮革,皮革制品,不另说明,并经处理的毛皮 61 - Leather, leather manufactures, nes, and dressed furskins62 -橡胶制品,不另说明 62 - Rubber manufactures, nes63 -软木及木制品(不包括家具) 63 - Cork and wood manufactures (excluding furniture)64 -纸,纸板和纸浆的文章,纸或纸板 64 - Paper, paperboard and articles of paper pulp, of paper or of paperboard65 -纺织纱线,织物,制成品,不另说明,以及相关产品 65 - Textile yarn, fabrics, made-up articles, nes, and related products66 -非金属矿产制品,不另说明 66 - Non-metallic mineral manufactures, nes67 -钢铁 67 - Iron and steel68 -有色金属 68 - Non-ferrous metals69 -金属制品 69 - Manufactures of metals, nes7 -机械和运输设备 7 - Machinery and transport equipment71 -发电机械设备 71 - Power-generating machinery and equipment72 -个别工业专用机械 72 - Machinery specialized for particular industries73 -金属加工机械 73 - Metalworking machinery74 -一般工业机械和设备和机器零件,不另说明 74 - General industrial machinery and equipment, nes, and machine parts, nes75 -办公室机器和自动资料处理仪器 75 - Office machines and automatic data-processing machines76 -电信和录音及音响设备和仪器 76 - Telecommunications andsound-recording and reproducing apparatus and equipment77 -电气机械,仪器和用具,巢,及零件(包括非电气同行,电家庭型设备) 77 - Electrical machinery, apparatus and appliances, nes, and electrical parts thereof (including non-electrical counterparts, nes, of electrical household-type equipment)78 -道路车辆(包括气垫车辆) 78 - Road vehicles (including air-cushion vehicles)79 -其他运输设备 79 - Other transport equipment8 -杂项制品 8 - Miscellaneous manufactured articles81 -预制建筑物,管道,发热及照明装置和设备,不另说明 81 - Prefabricated buildings; sanitary, plumbing, heating and lighting fixtures and fittings, nes82 -家具及其零件,床上用品,床垫,床垫,软座垫及类似的填充制品 82 - Furniture, and parts thereof; bedding, mattresses, mattress supports, cushions and similar stuffed furnishings83 -旅游用品,手袋及类似容器 83 - Travel goods, handbags and similar containers84 -服装及衣服配件 84 - Articles of apparel and clothing accessories85 -鞋子 85 - Footwear87 -专业,科学及控制用仪器及器具 87 - Professional, scientific and controlling instruments and apparatus, nes88 -摄影仪器,设备和供应品,光学产品;钟表 88 - Photographic apparatus, equipment and supplies and optical goods, nes; watches and clocks89 -杂项制品,不另说明 89 - Miscellaneous manufactured articles, nes9 -分类商品,而不是其他地方的贸易标准分类交易 9 - Commodities and transactions not classified elsewhere in the SITC91 -邮政包裹并无按实物 91 - Postal packages not classified according to kind93 -特殊交易和商品并无按实物 93 - Special transactions and commodities not classified according to kind96 -硬币(金币除外),没有法定货币 96 - Coin (other than gold coin), not being legal tender97 -金,非货币(不包括黄金矿砂及其精矿) 97 - Gold, non-monetary (excluding gold ores and concentrates)。

DS1302Z