MUSB-AB-S-RA-TSMT中文资料

EZ-USB_TRM第一章节中文版

EZ_USB技术参考手册 1.4版本塞普拉斯半导体公司198 Champion CourtSan Jose,CA 95134-1709Tel.:(800)858-1810(toll-free in the U.S.)(408)943-2600塞普拉斯公司免责声明协议本文文件所包含的信息可随时更改而不另行通知,不得解释为塞普拉斯半导体公司成立的承诺。

对于本文檔中出现的任何错误,即使采取了合理的预防措施,塞普拉斯半导休公司不承担任何责任。

如果没有塞普拉斯公司事先的书面同意,本文檔中的任何内容都不能以任何形式或方式被复制或转载。

塞普拉斯半导体产品并不适用、有意的、或者授权,作为组件在系统设计过程中强加于设计之中、或其它有意支持或维持生命的应用、或其它任何由塞普拉斯半导体产品应用的失败而导致的个人受伤或死亡。

买主购买或使用塞普拉斯半导体产品,用于任何无意或无授权的应用,买主应该保护并保挂塞普拉斯半导体和官员、雇员、下属公司、隶属机构及其经销商无害,反对所有因债权、损失、伤害、花费及其合理的律师费,由于直接或间接的任何意想不到或未经授权而引起的人身伤害或死亡的索赔,即使索赔诉讼是由于塞普拉斯公司设计或生产的产品疏忽所引起的。

接受此文檔将被解释为已经接受了以上条款。

EZ-USB技术参考手册,1.4版本版权@2000-2006.塞普拉斯半导体公司版权所有.商标名单Cypress,the Cypress Logo,EZ-USB,Making USB Universal,Xcelerator,and ReNumeration是塞普拉斯半导体公司的商标或注册商标。

Machintosh是苹果计算机公司的注册商标。

Windows是微软的注册商标。

I2C是飞利浦电子的注册商标。

SmartMedia是东芝公司的注册商标。

所有在本手册中使用的其它产品或公司名字可以是他们各自的商标、注册商标或服务商标。

第一章EZ-USB简介1.1简介通用串行总线(USB)作为计算机外设设备的连接方法已经获得了广泛接受。

ASUS A55BM-A USB3 ii T8663 第二版 2013 年 9 月发行手册说明书

SINUMERIKSINUMERIK Integrate for Production Valid for840D sl under Operate 4.7 SP3828D under Operate 4.7 SP3 Supplementary conditions and notes onreloading HMI archivesVersion Nov. 12, 2015Readme file© Siemens AG 2016DF MC TTI T&E 2Page 1 of 6 All rights reservedNotes for installation and useThese notes take priority over statements made in other documents.Please read the notes carefully because they contain important information for installation and use of SINUMERIK Integrate for Production.The SINUMERIK Integrate for Production software is called SIP in the following.Please read these notes before the installation.Activation and enabling of the SIP components under SINUMERIK Operate for 828D and 840D slAfter an Operate update of software version 4.5 SP3 (or higher) or a new installation of software version 4.7 SP3 for the 840D sl or software version 4.7 SP3 for the 828D, the required SIP components are already available in SINUMERIK Operate, but still have to be activated and enabled. Only then are the SIP functionalities available.Please read the SIP Installation Manual which describes how SIP is activated and enabled under SINUMERIK Operate.© Siemens AG 2016DF MC TTI T&E 2Page 2 of 6 All rights reservedNotes and supplementary conditions when reloading HMI archives for the 840D sl under LinuxUnder Linux during an update to software version 4.7 SP3Precondition: HMI archive has been created in a software version as of 4.5 SP3Assumption: Software update under Linux as of 4.5 SP3 to software version 4.7 SP3 has been performed. Reload of an HMI archive which has been created in a software version as of 4.5 SP3.Note: All SIP products, SIP Operate clients and SIP-specific softkeys are available again after reloading the HMI archive.1. After reloading the HMI archive, please restart the HMI.2. After this, settings in the er.xml, epsconfig.manufact.xml or epsconfig.individual.xmlmy have to be imported from the epsconfig.*.xml.invalid or be re-edited (parameters such asURLs, logging, etc.). This is only the case, however, if these files epsconfig.*.xml.invalid areavailable.3. BaseSetup should be reinstalled. (Uninstallation and installation).4. Finally, restart the HMI.Under Linux during a new installation of software version 4.7 SP3 using the "Full Restore"functionPrecondition: HMI archive has been created in a software version as of 4.5 SP3Assumption: New installation of software version 4.7 SP3 and subsequent reloading of the HMI archive. HMI restart has been performed after the reload.Note: If SIP products and SIP functionalities were activated when the HMI archive was created, they are available after the reload when the following adaptations have ben made.1. After reloading the HMI archive, please restart the HMI.2. After this, settings in the er.xml, epsconfig.manufact.xml or epsconfig.individual.xmlmy have to be imported from the epsconfig.*.xml.invalid or be re-edited (parameters such asURLs, logging, etc.). This is only the case, however, if these files epsconfig.*.xml.invalid areavailable.3. Then you must uninstall all clients (MMT, MMP, BaseSetup, etc.). HMI restarts are required inbetween. Uninstallation can be found under SoftKey App installation.4. Uninstall the "Installer.tar.gz" and restart the HMI again5. Install the "Installer.tar.gz" and install the "Basesetup.tar.gz" with the "App Installation" softkey6. Finally, restart the HMI.7. If necessary, install the Operate clients (e.g. for MMT, MMP & AMP) individually and restart theHMI after each Operate client installation.It is recommended that you create an HMI archive in software version 4.7 SP3 if further new installations based on 4.7 SP3 with customer-specific SIP adaptations are planned.© Siemens AG 2016DF MC TTI T&E 2Page 3 of 6All rights reservedNotes and supplementary conditions when reloading HMI archives for the 840D sl under WindowsUnder Windows during an update to software version 4.7 SP3Precondition: HMI archive has been created in a software version as of 4.5 SP3Assumption: Software update under Windows as of 4.5 SP3 to software version 4.7 SP3 has been performed. Reloading of an HMI archive which has been created in a software version 4.5 SP3 (or higher).Note: All SIP products, SIP Operate clients and SIP-specific customer adaptations and softkeys are available again after the reload.1. After reloading the HMI archive, please restart the HMI.2. After this, settings in the er.xml, epsconfig.manufact.xml or epsconfig.individual.xmlmy have to be imported from the epsconfig.*.xml.invalid or be re-edited (parameters such asURLs, logging, etc.). This is only the case, however, if these files epsconfig.*.xml.invalid areavailable.3. BaseSetup should be reinstalled. (Uninstallation and installation).4. Finally, restart the HMI.Under Windows during a new installation of software version 4.7 SP3Precondition: HMI archive has been created in a software version as of 4.5 SP3Assumption: New installation of software version 4.7 SP3 and subsequent reloading of the HMI archive. HMI restart has been performed after reloading the archive.Note: If SIP products and SIP functionalities were activated when the HMI archive was created, they are available again after the reload when the following adaptations have been made.1. After reloading the HMI archive, please restart the HMI.2. After this, settings in the er.xml, epsconfig.manufact.xml or epsconfig.individual.xml myhave to be imported from the epsconfig.*.xml.invalid or be re-edited (parameters such as URLs, logging, etc.). This is only the case, however, if these files epsconfig.*.xml.invalid are available.3. Then you must uninstall all clients (MMT, MMP, BaseSetup, etc.). HMI restarts are required inbetween. Uninstallation can be found under SoftKey App installation.4. Then uninstall "Installer.tar.gz". During the uninstallation the following error message appears,"Cannot remove file: F:/hmisl/addon/sinumerik/hmi/lng\installer_eng.qm".5. Restart the HMI and restart the uninstallation of the "Installer.tar.gz".6. Restart the HMI again7. Install "Installer.tar.gz"8. Select and install the "Basesetup.tar.gz" setup file with the "App Installation" softkey9. Restart the HMI again10. Install the Operate clients (e.g. for MMT, MMP & AMP) individually and restart the HMI after eachOperate client installation(Information on the installation of the Operate clients can be found in the SIP Installation Manual)It is recommended that you create an HMI archive in software version 4.7 SP3 if further new installations based on 4.7 SP3 with customer-specific SIP adaptations are planned.© Siemens AG 2016DF MC TTI T&E 2Page 4 of 6 All rights reserved© Siemens AG 2016DF MC TTI T&E 2Page 5 of 6All rights reservedNotes and supplementary conditions when reloading HMI archives for the 828D under LinuxUnder Linux during a new installation of software version 4.7 SP3 using the "Full Restore" functionPrecondition: HMI archive has been created in a software version as of 4.5 SP3Assumption: New installation of software version 4.7 SP3 and subsequent reloading of the HMI archive. HMI restart has been performed after reloading the archive.Note: The customer-specific SIP adaptations are available again after reloading the HMI archive under SINUMERIK Operate 4.7 SP3.Supplementary condition: ID Title Supplementary condition Description Workaround374835 Sporadic HMI crash with activated SlTrace of the ePSJsDialog module In the SlTrc (HMI trace), the options (trace bits) must not be activated for the ePSJsDialog module. If the options (trace bits) of the ePSJsDialog module are activated for the trace on the control in the SlTrc (HMI trace) for analysis purposes, the HMI Operate may crash if certain characters occur at a specific position in the trace output. As long as the ePSJsDialog module remains inactive, the SlTrace can be used as usual.In the SlTrc(HMI trace), the options (trace bits) must be deactivated for the ePSJsDialogmodule. In the initial state (after installation ofthe SINUMERIK Operate), these options are deactivated.430468 MMT 2.7 - HMI archive reloading on PCU after SinOp update is erroneous: Some files cannot be overwrittenWhen an HMI archive is reloaded, error messages must be acknowledge d manually. The reloading of an HMI archive on a PCU after a Sinumerik Operate Update is erroneous: Some files cannot be overwritten. After pressingSkip softkey, the reloading of the archive is carried out without errors.430089 "Backup data" softkey does not function after update from SINOP4711 to 4721 Backup data softkey only functions after the installer and base are re-installed."Backup data" softkey no longer functions after the update of Sinumerik Operate 4.7.1.1 to 4.7.2.1. Softkey exists but has no function. It will functionagain after you uninstall and re-install the installer/base setup.425374 SinInt - the SINint softkey is only active on Without an HMI restart, the If no connection exists from the PCU(Windows XP) to an NCU, the HMI must be restarted so that the SinumerikAfter the activation of the Sinumerik© Siemens AG 2016 DF MC TTI T&E 2Page 6 of 6All rights reservedWindows XP after an HMI restartSinumerik Integrate softkey is not available. Integrate softkey is available. Integrate via the machine data, the HMI must be restarted.425512If usage is blocked, the user can assign but not resign in the "User menu".If the use of Sinumerik Integrate is deactivated ("Block usage"softkey), then the "User menu" dialog should not be used.User menu dialog cannot be used when Sinumerik Integrate is deactivated, because it is no longer possible to exit this dialog. A changeover outside of Sinumerik Integrate is possible, however.If the User menu is nevertheless activated when usage is blocked, the machine dialog can be re-activated with F10 + F1. Sinumerik Integrate can only beactivated and used after an HMI restart.430907AMB - HMI archive cannot be read-in by SinIntClientOccasionally, large IBN archives are notcompletely transferred from the SIP server to a machine.Large IBN archives (approx. > 1 MB) occasionally cannot be downloaded from the server via the Sinumerik Integrate client and installed without errors.Download of an IBN archive from the SIP server directly to a USB stick. Thisarchive can then be installed directly on a machine via Sinumerik Operate.。

微斯米微波式芯片公司2014年产品说明书

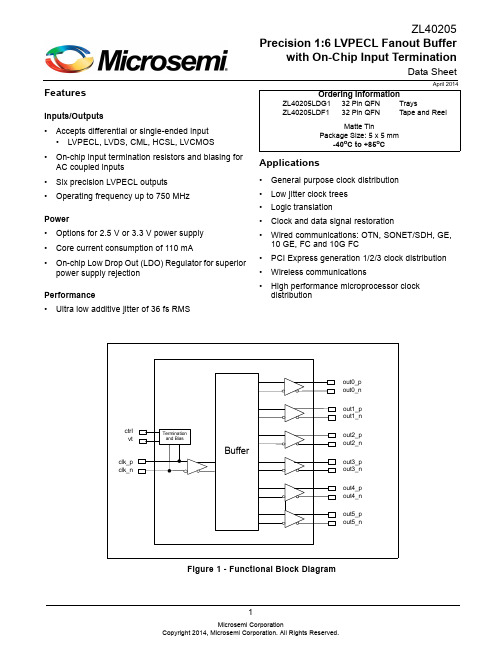

1FeaturesInputs/Outputs •Accepts differential or single-ended input •LVPECL, LVDS, CML, HCSL, LVCMOS •On-chip input termination resistors and biasing for AC coupled inputs•Six precision LVPECL outputs •Operating frequency up to 750 MHzPower •Options for 2.5 V or 3.3 V power supply •Core current consumption of 110 mA•On-chip Low Drop Out (LDO) Regulator for superior power supply rejectionPerformance •Ultra low additive jitter of 36 fs RMSApplications•General purpose clock distribution •Low jitter clock trees •Logic translation•Clock and data signal restoration•Wired communications: OTN, SONET/SDH, GE,10 GE, FC and 10G FC•PCI Express generation 1/2/3 clock distribution •Wireless communications•High performance microprocessor clock distributionApril 2014Figure 1 - Functional Block DiagramZL40205Precision 1:6 LVPECL Fanout Bufferwith On-Chip Input TerminationData SheetOrdering InformationZL40205LDG1 32 Pin QFN TraysZL40205LDF132 Pin QFNTape and ReelMatte TinPackage Size: 5 x 5 mm-40o C to +85o CTable of ContentsFeatures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Inputs/Outputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1 Power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1 Performance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1 Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Change Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41.0 Package Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .52.0 Pin Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63.0 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73.1 Clock Inputs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73.2 Clock Outputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .123.3 Device Additive Jitter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .153.4 Power Supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .163.4.1 Sensitivity to power supply noise. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .163.4.2 Power supply filtering. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .163.4.3 PCB layout considerations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .164.0 AC and DC Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .175.0 Performance Characterization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .206.0 Typical Behavior . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .217.0 Package Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .238.0 Mechanical Drawing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24List of FiguresFigure 1 - Functional Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Figure 2 - Pin Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 Figure 3 - Simplified Diagram of Input Stage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 Figure 4 - Clock Input - LVPECL - DC Coupled. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 Figure 5 - Clock Input - LVPECL - AC Coupled. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 Figure 6 - Clock Input - LVDS - DC Coupled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Figure 7 - Clock Input - LVDS - AC Coupled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Figure 8 - Clock Input - CML- AC Coupled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 Figure 9 - Clock Input - HCSL- AC Coupled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 Figure 10 - Clock Input - AC-coupled Single-Ended . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Figure 11 - Clock Input - DC-coupled 3.3V CMOS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Figure 12 - Simplified Output Driver. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Figure 13 - LVPECL Basic Output Termination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Figure 14 - LVPECL Parallel Output Termination. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Figure 15 - LVPECL Parallel Thevenin-Equivalent Output Termination. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Figure 16 - LVPECL AC Output Termination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 Figure 17 - LVPECL AC Output Termination for CML Inputs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 Figure 18 - Additive Jitter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 Figure 19 - Decoupling Connections for Power Pins. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 Figure 20 - Differential and Single-Ended Output Voltages Parameter Definitions . . . . . . . . . . . . . . . . . . . . . . . . 18 Figure 21 - Input To Output Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19Change SummaryPage Item Change1Applications Added PCI Express clock distribution.6Pin Description Added exposed pad to Pin Description.8Figure 4 and Figure 5Removed 22 ohm series resistors from Figure 4 and 5. These resistor are not required; however there is no impact to performance if the resistors are included.16Power supply filtering 18Figure 20Clarification of V ID and V OD .Below are the changes from the February 2013 issue to the April 2014 issue:Page Item Change8Figure 4Changed text to indicate the circuit is not recommended for VDD_driver=2.5V.Below are the changes from the November 2012 issue to the February 2013 issue:Corrected typo of 0.3 Ohm to 0.15 Ohm.1.0 Package DescriptionThe device is packaged in a 32 pin QFNFigure 2 - Pin Connections2.0 Pin DescriptionPin # Name Description3, 6clk_p, clk_n,Differential Input (Analog Input). Differential (or single ended) input signals.For all input configurations see “Clock Inputs” on page 728, 27, 26, 25, 24, 23, 18, 17, 16, 15, 14, 13out0_p, out0_nout1_p, out1_nout2_p, out2_nout3_p, out3_nout4_p, out4_nout5_p, out5_nDifferential Output (Analog Output). Differential outputs.9, 19,22, 32vdd Positive Supply Voltage. 2.5 V DC or 3.3 V DC nominal.1, 8vdd_core Positive Supply Voltage. 2.5 V DC or 3.3 V DC nominal.2, 7,20, 21gnd Ground. 0 V.4vt On-Chip Input Termination Node (Analog). Center tap between internal 50 Ohmtermination resistors.The use of this pin is detailed in section 3.1, “Clock Inputs“, for various input signal types.5ctrl Digital Control for On-Chip Input Termination (Input). Selects differential input mode;0: DC coupled LVPECL or LVDS modes1: AC coupled differential modesThis pin are internally pulled down to GND. The use of this pin is detailed in section 3.1,“Clock Inputs“, for various input signal types.10, 11,12, 29,30, 31NC No Connection. Leave unconnected.Exposed Pad Device GND.3.0 Functional DescriptionThe ZL40205 is an LVPECL clock fan out buffer with six output clock drivers capable of operating at frequencies up to 750MHz.The ZL40205 provides an internal input termination network for DC and AC coupled inputs; optional input biasing for AC coupled inputs is also provided. The ZL40205 can accept DC or AC coupled LVPECL and LVDS input signals, AC coupled CML or HCSL input signals, and single ended signals. A pin compatible device with external termination is also available.The ZL40205 is designed to fan out low-jitter reference clocks for wired or optical communications applications while adding minimal jitter to the clock signal. An internal linear power supply regulator and bulk capacitors minimize additive jitter due to power supply noise. The device operates from 2.5V+/-5% or 3.3V+/-5% supply. Its operation is guaranteed over the industrial temperature range -40°C to +85°C.The device block diagram is shown in Figure 1; its operation is described in the following sections.3.1 Clock InputsThe device has a differential input equipped with two on-chip 50 Ohm termination resistors arranged in series with a center tap. The input can accept many differential and single-ended signals with AC or DC coupling as appropriate. A control pin is available to enable internal biasing for AC coupled inputs. A block diagram of the input stage is in Figure 3.Receiverclk_n 50clk_pVt 50BiasctrlFigure 3 - Simplified Diagram of Input StageThis following figures give the components values and configuration for the various circuits compatible with the input stage and the use of the Vt and ctrl pins in each case.In the following diagrams where the ctrl pin is logically one and the Vt pin is not connected, the Vt pin can be instead connected to VDD with a capacitor. A capacitor can also help in Figure 4 between Vt and VDD. This capacitor will minimize the noise at the point between the two internal termination resistors and improve the overall performance of the device.Figure 4 - Clock Input - LVPECL - DC CoupledFigure 5 - Clock Input - LVPECL - AC CoupledFigure 6 - Clock Input - LVDS - DC CoupledFigure 7 - Clock Input - LVDS - AC CoupledFigure 8 - Clock Input - CML- AC CoupledFigure 9 - Clock Input - HCSL- AC CoupledFigure 10 - Clock Input - AC-coupled Single-EndedFigure 11 - Clock Input - DC-coupled 3.3V CMOS3.2 Clock OutputsLVPECL has a very low output impedance and a differential signal swing between 1V and 1.6 V. A simplified diagram for the output stage is shown in Figure 12.The LVPECL to LVDS output termination is not shown since there is a different device with the same inputs and LVDS outputs.out_pout_nFigure 12 - Simplified Output DriverThe methods to terminate the ZL40205 LVPECL drivers are shown in the following figures.Figure 15 - LVPECL Parallel Thevenin-Equivalent Output TerminationFigure 16 - LVPECL AC Output TerminationFigure 17 - LVPECL AC Output Termination for CML Inputs3.3 Device Additive JitterThe ZL40205 clock fanout buffer is not intended to filter clock jitter. The jitter performance of this type of device is characterized by its additive jitter. Additive jitter is the jitter the device would add to a hypothetical jitter-free clock as it passes through the device. The additive jitter of the ZL40205 is random and as such it is not correlated to the jitter of the input clock signal.The square of the resultant random RMS jitter at the output of the ZL40205 is equal to the sum of the squares of the various random RMS jitter sources including: input clock jitter; additive jitter of the buffer; and additive random jitter due to power supply noise. There may be additional deterministic jitter sources, but they are not shown in Figure 18.Figure 18 - Additive Jitter3.4 Power SupplyThis device operates employing either a 2.5V supply or 3.3V supply.3.4.1 Sensitivity to power supply noisePower supply noise from sources such as switching power supplies and high-power digital components such as FPGAs can induce additive jitter on clock buffer outputs. The ZL40205 is equipped with a low drop out (LDO) regulator and on-chip bulk capacitors to minimize additive jitter due to power supply noise. The on-chip regulation, recommended power supply filtering, and good PCB layout all work together to minimize the additive jitter from power supply noise.3.4.2 Power supply filteringJitter levels may increase when noise is present on the power pins. For optimal jitter performance, the device should be isolated from the power planes connected to its power supply pins as shown in Figure 19. •10 µF capacitors should be size 0603 or size 0805 X5R or X7R ceramic, 6.3 V minimum rating •0.1 µF capacitors should be size 0402 X5R ceramic, 6.3 V minimum rating •Capacitors should be placed next to the connected device power pins •A 0.15 Ohm resistor is recommended3.4.3 PCB layout considerationsThe power nets in Figure 19 can be implemented either as a plane island or routed power topology without changing the overall jitter performance of the device.ZL402051891922320.1 µF 0.1 µFvdd_core10 µF 0.1 µF0.15 Ωvdd0.1 µF 10 µFFigure 19 - Decoupling Connections for Power PinsAbsolute Maximum Ratings*Parameter Sym.Min.Max.Units 1Supply voltage V DD_R-0.5 4.6V 2Voltage on any digital pin V PIN-0.5VDD V 4LVPECL output current I out30mA 5Soldering temperature T260 °C 6Storage temperature T ST-55125 °C 7Junction temperature T j125 °C 8Voltage on input pin V input VDD V 9Input capacitance each pin C p500fF 4.0 AC and DC Electrical Characteristics* Exceeding these values may cause permanent damage. Functional operation under these conditions is not implied.* Voltages are with respect to ground (GND) unless otherwise statedRecommended Operating Conditions*Characteristics Sym.Min.Typ.Max.Units1Supply voltage 2.5 V mode V DD25 2.375 2.5 2.625V2Supply voltage 3.3 V mode V DD33 3.135 3.3 3.465V3Operating temperature T A-402585°C* Voltages are with respect to ground (GND) unless otherwise statedDC Electrical Characteristics - Current ConsumptionCharacteristics Sym.Min.Typ.Max.Units Notes 1Supply current LVPECL drivers -unloadedI dd_unload110mA Unloaded2Supply current LVPECL drivers - loaded (all outputs are active)I dd_load209mA Including powerto R L = 50DC Electrical Characteristics - Inputs and Outputs - for 3.3 V SupplyCharacteristics Sym.Min.Typ.Max.Units Notes1CMOS control logic high-level inputvoltageV CIH0.7*V DD V2CMOS control logic low-level inputvoltageV CIL0.3*V DD V3CMOS control logic Input leakagecurrentI IL1µA V I = V DD or 0 V4Differential input common modevoltageV CM 1.1 2.0V5Differential input voltage difference V ID0.251V6Differential input resistance V IR80100120ohm* This parameter was measured from 125 MHz to 750 MHz.* This parameter was measured from 125 MHz to 750 MHz.Figure 20 - Differential and Single-Ended Output Voltages Parameter Definitions7LVPECL output high voltage V OH V DD -1.40V 8LVPECL output low voltage V OL V DD - 1.62V 9LVPECL output differential voltage*V OD0.50.9VDC Electrical Characteristics - Inputs and Outputs - for 2.5 V SupplyCharacteristicsSym.Min.Typ.Max.Units Notes1Differential input common mode voltageV CM 1.1 1.6V 2Differential input voltage difference V ID 0.251V 3Differential input resistance V IR 80100120ohm 4LVPECL output high voltage V OH V DD -1.40V 5LVPECL output low voltage V OL V DD - 1.62V 6LVPECL output differential voltage*V OD0.40.9VDC Electrical Characteristics - Inputs and Outputs - for 3.3 V SupplyCharacteristicsSym.Min.Typ.Max.Units NotesAC Electrical Characteristics* - Inputs and Outputs (see Figure 21) - for 2.5/3.3 V supply.Characteristics Sym.Min.Typ.Max.Units Notes 1Maximum Operating Frequency1/t p750MHz2Input to output clock propagation delay t pd012ns3Output to output skew t out2out50100ps4Part to part output skew t part2part80300ps5Output clock Duty Cycle degradation t PWH/ t PWL-202Percent6LVPECL Output clock slew rate r SL0.75 1.2V/ns* Supply voltage and operating temperature are as per Recommended Operating ConditionsInputt Pt PWL t pdt PWHOutputFigure 21 - Input To Output TimingAdditive Jitter at 2.5 V*Output Frequency (MHz)Jitter MeasurementFilterTypical RMS (fs)Notes112512 kHz - 20 MHz 1392212.512 kHz - 20 MHz 1093311.0412 kHz - 20 MHz 85442512 kHz - 20 MHz 57550012 kHz - 20 MHz 506622.0812 kHz - 20 MHz 40775012 kHz - 20 MHz36Additive Jitter at 3.3 V*Output Frequency (MHz)Jitter MeasurementFilterTypical RMS (fs)Notes112512 kHz - 20 MHz 1152212.512 kHz - 20 MHz 853311.0412 kHz - 20 MHz 72442512 kHz - 20 MHz 55550012 kHz - 20 MHz 486622.0812 kHz - 20 MHz 41775012 kHz - 20 MHz395.0 Performance Characterization*The values in this table were taken with an approximate slew rate of 0.8 V/ns.*The values in this table were taken with an approximate slew rate of 0.8 V/ns.Additive Jitter from a Power Supply Tone*Carrier frequencyParameterTypicalUnitsNotes125MHz 25 mV at 100 kHz 115fs RMS 750MHz25 mV at 100 kHz59fs RMS* The values in this table are the additive periodic jitter caused by an interfering tone typically caused by a switching power supply. For this test, measurements were taken over the full temperature and voltage range for V DD = 2.5 V. The magnitude of the interfering tone is measured at the DUT.6.0 Typical BehaviorTypical Phase Noise at 622.08 MHzTypical Waveformat 155.52 MHzV OD versus FrequencyPropagation Delay versus TemperatureNote:This is for a single device. For more details see thePower Supply Tone Frequency (at 25 mV) versus PSRR at 125 MHz Power Supply Tone Frequency (at 25 mV) versus Additive Jitter at 125 MHzPower Supply Tone Magnitude (at 100 kHz) versus PSRR at 125 MHz Power Supply Tone Magnitude (at 100 kHz) versus Additive Jitter at 125 MHz7.0 Package CharacteristicsThermal DataParameter Symbol Test Condition Value UnitJunction to Ambient Thermal Resistance ΘJA Still Air1 m/s2 m/s 37.433.131.5o C/WJunction to Case Thermal Resistance ΘJC24.4o C/W Junction to Board Thermal Resistance ΘJB19.5o C/W Maximum Junction Temperature*T jmax125o C Maximum Ambient Temperature T A85o C© 2014 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.Microsemi Corporation (NASDAQ: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense and security, aerospace and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world’s standard for time; voice processing devices; RF solutions; discrete components; security technologies and scalable anti-tamper products; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif. and has approximately 3,400 employees globally. Learn more at .Microsemi Corporate Headquarters One One Enterprise, Aliso Viejo CA 92656 USA Within the USA: +1 (800) 713-4113Outside the USA: +1 (949) 380-6100Sales: +1 (949) 380-6136Fax: +1 (949) 215-4996E-mail: ***************************Information relating to products and services furnished herein by Microsemi Corporation or its subsidiaries (collectively “Microsemi”) is believed to be reliable. However, Microsemi assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Microsemi or licensed from third parties by Microsemi, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Microsemi, or non-Microsemi furnished goods or services may infringe patents or other intellectual property rights owned by Microsemi.This publication is issued to provide information only and (unless agreed by Microsemi in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Microsemi without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user’s responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical and other products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Microsemi’s conditions of sale which are available on request.For more information about all Microsemi productsvisit our website at TECHNICAL DOCUMENTATION – NOT FOR RESALE。

商斯达射频微波光电产品目录说明书

SUNSTAR 商斯达微波光电公司 射频、微波、光纤、光电、通讯产品目 录更多产品请看本公司产品专用销售网站:欢迎来电查询购买商斯达产品或索取免费详细资料、设计指南和光盘;产品繁多,未能尽录,欢迎来电查询。

商斯达射频微波光电产品网:/商斯达中国传感器科技信息网:/商斯达工控安防网:/商斯达电子元器件网:/商斯达军工产品网:hrrp:///商斯达消费电子产品网:///商斯达实业研制科技产品网:/// 射频微波光电元器件销售热线:地址:深圳市福田区福华路福庆街鸿图大厦1602室电话:0755-******** 83397033 83398585 82884100MSN:邮编:518033 E-mail:QQ: 195847376深圳赛格展销部:深圳华强北路赛格电子市场2583号 电话:0755-******** 25059422 技术支持: 0755-******** 135********北京分公司:北京海淀区知春路132号中发电子大厦3097号TEL:82615020 FAX:上海分公司:上海市北京东路668号上海賽格电子市场D125号TEL:56703037 FAX:西安分公司:西安高新开发区20所(中国电子科技集团导航技术研究所)西安劳动南路88号电子商城二楼D23号TEL:Aavid ThermalloyABRACON CorporationAEPAeroflex INMETAeroflex KDI Resistor ProductsAmerican Tech Ceramics (ATC)AmphenolANADIGICSAnarenAnaren/RF PowerArcotronicsAvago TechnologiesBOMAR Interconnect Products, Inc.Cornell DubilierCrystek CorporationCTS CorporationDynex SemiconductorElectronic Devices, Inc.Emerson Network Power (formerly Johnson Components) Empower RF Systems, Inc.EPCOS F.W. BellFractusfree2moveFreescale Semiconductor, Inc. General ElectricGoreHoneywellHuber+SuhnerHVVIIllinois Capacitor, Inc.Infineon TechnologiesIQD Frequency ProductsJohanson ManufacturingLaird TechnologiesM/A-COM Technology Solutions Maxwell TechnologiesMicrosemiMicrosemi (Santa Clara)Mimix Broadband (formerly Celeritek) Mitsubishi ElectronicsNational ElectronicsNDKNEC Compound Semiconductors NitronexOhmitePacific MonolithicsPCTEL (Maxrad, Inc.)Peregrine Semiconductor PolyPhaser Corporation PowerexRadiallRadiotronixRaltronRES - IngeniumRF IndustriesRichardson Component Solutions Richardson Power Solutions Richardson System Solutions RiedonSDP Components, Inc. SemeLab, PlcSemikron Spectrum Advanced Specialty Products Spectrum MicrowaveST MicroelectronicsSV MicrowaveTeledyne CoaxTeledyne RelaysTensolite CDI/QMIToko AmericaTyco ElectronicsUnited Chemi-con, Inc.United Monolithic Semiconductors (UMS) Valpey FisherVincotechVishayWakefield Thermal SolutionsWanTcomWavecomWestcode Semiconductors, Inc.WJ CommunicationsMTI MilanoPacific MonolithicsMini-Circuits公司是1969年由 Harvey Kaylie先生创立的。

泰尔斯特极限移动宽带USB模块说明书

Removing the Modem 1. Exit the Connection Manager software. 2. Remove the modem by pulling it straight out from

the USB port.

Troubleshooting For a more complete listing of errors and possible solutions, please see the User Guide or Connection Manager online Help.

Starting the Mac Software If the Connection Manager software has not started automatically: Click the program’s icon in the dock. -orIn Finder™, select Go > Applications > Telstra Connection Manager and then double-click Telstra Connection Manager.

Problem/Error Solution

The device has no power— the LED in‑ dicator is off.

Ensure the following: • The device is properly inserted. • The computer is turned on and

Viewing the User Guide The User Guide provides additional operating informa‑ tion and specifications for the modem.

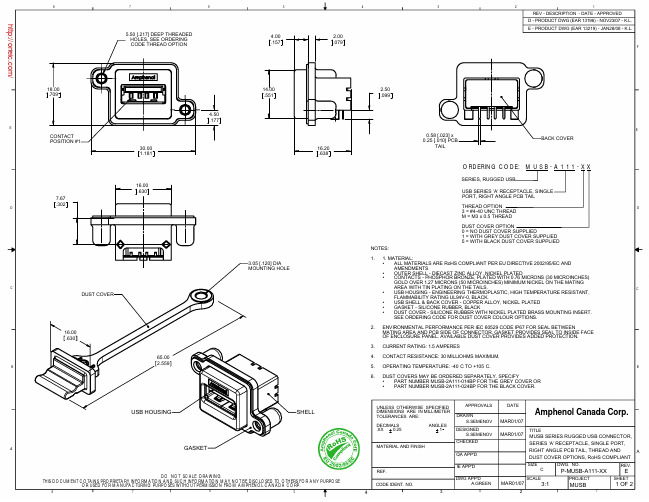

MUSB-A111-30;中文规格书,Datasheet资料

APPROVALS DRAWN S.SEMENOV DESIGNED S.SEMENOV CHECKED

DATE

Amphenol Canada Corp.

MAR01/07 MAR01/07

TITLE

A

MATERIAL AND FINISH QA APP'D IE APP'D

MUSB SERIES RUGGED USB CONNECTOR, SERIES 'A' RECEPTACLE, SINGLE PORT, RIGHT ANGLE PCB TAIL, THREAD AND A DUST COVER OPTIONS, RoHS COMPLIANT

RECOMMENDED PCB LAYOUT

COMPONENT SIDE OF BOARD

RECOMMENDED PANEL CUTOUT

C C

B

B

UNLESS OTHERWISE SPECIFIED DIMENSIONS ARE IN MILLIMETER TOLERANCES ARE: DECIMALS 0.25 .XX ANGLES 1

APPROVALS DRAWN S.SEMENOV DESIGNED S.SEMENOV CHECKED

DATE

Amphenol Canada Corp.

MAR01/07 MAR01/07

TITLE

A

GASKET

MATERIAL AND FINISH QA APP'D IE APP'D

MUSB SERIES RUGGED USB CONNECTOR, SERIES 'A' RECEPTACLE, SINGLE PORT, RIGHT ANGLE PCB TAIL, THREAD AND A DUST COVER OPTIONS, RoHS COMPLIANT

M5A78L-M USB3 使用手冊 ii T8017 第二版(V2) 2013年1月发行说明书

diiT8017第二版(V2)2013 年 1 月發行Offer to Provide Source Code of Certain SoftwareThis product may contain copyrighted software that is licensed under the General Public License (“GPL”) and under the Lesser General Public License Version (“LGPL”). The GPL and LGPL licensed code in this product is distributed without any warranty. Copies of these licenses are included in this product.You may obtain the complete corresponding source code (as defined in the GPL) for the GPL Software, and/or the complete corresponding source code of the LGPL Software (with the complete machine-readable “work that uses the Library”) for a period of three years after our last shipment of the product including the GPL Software and/or LGPL Software, which will be no earlier than December 1, 2011, either(1) for free by downloading it from /download;or (2) for the cost of reproduction and shipment, which is dependent on the preferred carrier and the location where you want to have it shipped to, by sending a request to:ASUSTeK Computer Inc.Legal Compliance Dept.15 Li Te Rd.,Beitou, Taipei 112Taiwan In your request please provide the name, model number and version, as stated in the About Box of the product for which you wish to obtain the corresponding source code and your contact details so that we can coordinate the terms and cost of shipment with you.The source code will be distributed WITHOUT ANY WARRANTY and licensed under the same license as the corresponding binary/object code.This offer is valid to anyone in receipt of this information.ASUSTeK is eager to duly provide complete source code as required under various Free Open Source Software licenses. If however you encounter any problems in obtaining the full corresponding source code *************************************************************************,statingthe product and describing the problem (please do NOT send large attachments such as source code archives etc to this email address).版權說明©ASUSTeK Computer Inc. All rights reserved. 華碩電腦股份有限公司保留所有權利本使用手冊包括但不限於其所包含的所有資訊皆受到著作權法之保護,未經華碩電腦股份有限公司(以下簡稱「華碩」)許可,不得任意地仿製、拷貝、謄抄、轉譯或為其他利用。

RAM..G Relay Datasheet说明书

1-pole, solid state relay with LED and built-in Varistor, VDE certifiedMain features• AC switching Solid State Relay• Direct copper bonding (DCB) technology • Back to Back thyristor output• VDE certified for Glow wire test according to IEC/EN 60335-1• 100,000 cycles UL endurance test*• Integrated overvoltage protection • LED for control presence indication • Clip-on IP20 protection cover • Self-lifting terminals•65 kA UL short circuit current rating* selected modelsThe industrial, 1-phase relay with antiparallel thyristor output is the most widely used industrial SSR due to its multiple application possibilities. The relay can be used for resistive, inductive and capacitive loads. The zero switching relay switches ON when the sinusoidal curve crosses zero and switches OFF when the current crosses zero. The built-in varistor secures transient protection. The LED indicates the status of the control input. The clipon cover secures touch protection (IP 20). Protected output terminals can handle cables up to 16 mm².Specifications are at a surrounding temperature of 25°C unless otherwise specified.RAM1A..GApplicationsPlastic injection machines, Extrusion machines, Blow moulding machines, Thermoformers, Dryers, Electrical ovens, Fryers, Shrink tunnels, Air handling units, Sterilisation equipment, Climatic chambers, Ovens and furnaces, Ambient heating.Main functions• 1-pole, zero cross switching• Rated output voltage up to 660 VAC • Rated output current up to 125 AAC•3(4)-32 VDC or 20-280 VAC/22-48 VDC control voltage rangeOrder codeEnter the code option instead of . Refer to the Selection guide section for valid part numbers.Selection guideCarlo Gavazzi compatible componentsCarlo Gavazzi further readingStructureFeaturesGeneral dataPerformanceOutput specifications1. Refer to Heatsink selection section2. UL requirement for General Use Endurance Testing is 6,000 cyclesOutput voltage specificationsMotor ratings*: HP (UL508)* With suitable heatsink.InputsOutput power dissipationHeatsink selectionThermal resistance [°C/W] of RAM1A..25Thermal resistance [°C/W] of RAM1A..50, 51Thermal resistance [°C/W] of RAM1A..100Thermal resistance [°C/W] of RAM1A..125'nh' means no heatsink necessary. The SSR should still be tightened to a surface to ensure optimal thermal dissipation.Thermal data3. Thermal resistance case to heatsink values are applicable upon application of a fine layer of silicon based thermal paste HTS02S from Electrolube between SSR and heatsinkCompatibility and conformanceEN 60947-4-3 / EE: BS EN 60947-4-3EN 60947-4-3 / EMC: BS EN 60947-4-3UL508 Recognised (E80573), NRNT2, NRNT8C22.2 No.14, (204075)Note:• Control input lines must be installed together to maintain products’ susceptibility to Radio Frequency interference.• The control terminals A1, A2 (RAM1A..A..G) shall be supplied by a secondary circuit where power is limited by a transformer, rectifier, voltage divider, or similar device that derives power from a primary circuit, and where the short-circuit limit between conductors of the secondary circuit or between conductors and ground is 1500 VA or less. The short-circuit volt ampere limit is the product of the open circuit voltage and the short circuit ampere.• Performance Criteria 1 (PC1): No degradation of performance or loss of function is allowed when the product is operated as intended.• Performance Criteria 2 (PC2): During the test, degradation of performance or partial loss of function is allowed. However when the test iscomplete the product should return operating as intended by itself.• Performance Criteria 3 (PC3): Temporary loss of function is allowed, provided the function can be restored by manual operation of the controls.The declaration in this section is prepared in compliance with People’s Republic of China Electronic Industry Standard SJ/T11364-2014: Marking for the Restricted Use of Hazardous Substances in Electronic and Electrical Products.这份申明根据中华人民共和国电子工业标准SJ/T11364-2014:标注在电子电气产品中限定使用的有害物质Protection Co-ordination, Type 1 vs Type 2:Type 1 protection implies that after a short circuit, the device under test will no longer be in a functioning state. In Type 2 co-ordination the device under test will still be functional after the short circuit. In both cases, however the short circuit has to be interrupted. The fuse between enclosure and supply shall not open. The door or cover of the enclosure shall not be blown open. There shall be no damage to conductors or terminals and the conductors shall not separate from terminals. there shall be no breakage or cracking of insulating bases to the extent that the integrity of the mounting of live parts is impaired. Discharge of parts or any risk of fire shall not occur.The product variants listed in the table hereunder are suitable for use on a circuit capable of delivering not more than 65,000 Arms Symmetrical Amperes, 600Volts maximum when protected by fuses. Tests at 65,000A were performed with Class J, fast acting: please refer to the table below for maximum allowed ampere rating of the fuse. Use fuses only.zz = 00, without fuse trip indication,zz = 21, with fuse trip indication.4. Between MCB and Load (including return path which goes back to the mains).Note: A prospective current of 6 kA and a 230 / 400 V power supply is assumed for the above suggested specifications. For cables with different cross section than those mentioned above please consult Carlo Gavazzi's Technical Support Group.S201 models refer to 1-pole M.C.B., S202 models refer to 2-poles M.C.B.DimensionsAPPLY HEATSINK COMPOUNDDimensions in mm.Tolerances ±0.5 mm.Control InputL1L2/NFunctional diagram* Varistor across input applies to AC control versions only.Connection diagramA1(A2()+~L1-~Connection SpecificationsCOPYRIGHT ©2022Content subject to change.Download the PDF: https://。

MEMORY存储芯片MT29F64G08CBABBWPRB中文规格书

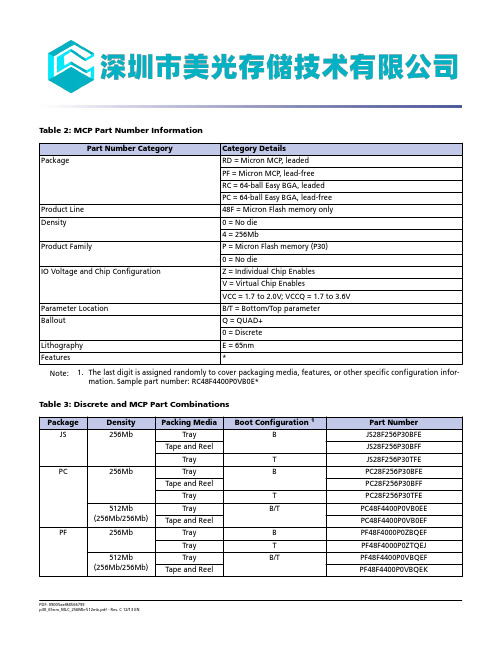

Table 2: MCP Part Number InformationNote: 1.The last digit is assigned randomly to cover packaging media, features, or other specific configuration infor-mation. Sample part number: RC48F4400P0VB0E*Table 3: Discrete and MCP Part CombinationsSignal DescriptionsTable 7: TSOP and Easy BGA Signal DescriptionsTable 7: TSOP and Easy BGA Signal Descriptions (Continued)Table 8: QUAD+ SCSP Signal DescriptionsTable 8: QUAD+ SCSP Signal Descriptions (Continued)One-Time Programmable RegistersRead OTP RegistersThe device contains 17 OTP registers that can be used to implement system security measures and/or device identification. Each OTP register can be individually locked.The first 128-bit OTP register is comprised of two 64-bit (8-word) segments. The lower 64-bit segment is preprogrammed at the Micron factory with a unique 64-bit number.The upper 64-bit segment, as well as the other sixteen 128-bit OTP registers, are ers can program them as needed. Once programmed, users can also lock the OTP register(s) to prevent additional bit programming (see the OTP Register Map figure be-low).The OTP registers contain OTP bits; when programmed, PR bits cannot be erased. Each OTP register can be accessed multiple times to program individual bits, as long as the register remains unlocked.Each OTP register has an associated lock register bit. When a lock register bit is pro-grammed, the associated OTP register can only be read; it can no longer be program-med. Additionally, because the lock register bits themselves are OTP , when program-med, they cannot be erased. Therefore, when an OTP register is locked, it cannot be un-locked.The OTP registers can be read from an OTP-RA address. To read the OTP register, a READ DEVICE IDENTIFIER command is issued at an OTP-RA address to place the de-vice in the read device identifier state. Next, a READ operation is performed using the address offset corresponding to the register to be read. The Device Identifier Informa-tion table shows the address offsets of the OTP registers and lock registers. PR data is read 16 bits at a time.256Mb and 512Mb (256Mb/256Mb), P30-65nm One-Time Programmable Registers。

MEMORY存储芯片TUSB212RWBR中文规格书

I/O

INTERNAL PULLUP/PULLDOWN

DESCRIPTION

I/O

N/A

I/O

N/A

I/O

RSTN asserted: 500 kΩ PD

I/O

RSTN asserted: 500 kΩ PD

I

500 kΩ PU

I

N/A

I/O

N/A

I/O

N/A

I/O

P

N/A

O

N/A

P

N/A

USB High Speed negative port..

6.2 ESD Ratings

V(ESD)

Electrostatic discharge

Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins(1) Charged device model (CDM), per JEDEC specification JESD22-C101, all pins(2)

channel Cable Length – Four Selectable AC Boost Settings Via

External Pulldown Resistor – DC Boost Along With AC Boost for Best Signal

Integrity

2 Applications

In addition, TUSB212 is compatible with the USB OnThe-Go (OTG) and Battery Charging (BC) protocols.

Device Information (1)

外置mos管同步整流芯片

外置mos管同步整流芯片英文回答:Introduction to External MOSFET Synchronous Rectifier ICs.External MOSFET synchronous rectifier ICs are used in a wide variety of power conversion applications to improve efficiency and reduce power loss. They are typically usedin place of traditional diodes in synchronous rectification circuits, which can significantly reduce conduction losses and improve overall system efficiency.Operation of External MOSFET Synchronous Rectifier ICs.External MOSFET synchronous rectifier ICs are typically implemented using a low-side N-channel MOSFET as the main switching device. The MOSFET is driven by a control circuit that generates a complementary gate drive signal to the MOSFET, which turns on the MOSFET when the output voltageis below the input voltage and turns it off when the output voltage is above the input voltage. This allows the MOSFETto act as a synchronous rectifier, conducting current only when the output voltage is lower than the input voltage.Advantages of External MOSFET Synchronous Rectifier ICs.External MOSFET synchronous rectifier ICs offer several advantages over traditional diodes, including:Lower conduction losses: MOSFETs have much lower on-resistance than diodes, which reduces conduction losses and improves overall system efficiency.Higher switching speeds: MOSFETs can be switched onand off much faster than diodes, which reduces switching losses and improves transient response.Lower voltage drop: MOSFETs have a lower forward voltage drop than diodes, which further reduces power loss and improves system efficiency.Selection of External MOSFET Synchronous Rectifier ICs.When selecting an external MOSFET synchronous rectifier IC, several factors should be considered, including:Input voltage range: The input voltage range of the IC should be compatible with the expected range of input voltages in the application.Output current rating: The output current rating of the IC should be sufficient to handle the expected load current in the application.Switching speed: The switching speed of the IC should be fast enough to minimize switching losses and improve transient response.Conduction losses: The conduction losses of the IC should be minimized to improve overall system efficiency.Applications of External MOSFET Synchronous Rectifier ICs.External MOSFET synchronous rectifier ICs are used in a wide variety of power conversion applications, including:DC-DC converters: External MOSFET synchronousrectifier ICs can be used in both buck and boost DC-DC converters to improve efficiency and reduce power loss.AC-DC converters: External MOSFET synchronousrectifier ICs can be used in AC-DC converters to rectify the AC input voltage and provide a DC output voltage.Inverters: External MOSFET synchronous rectifier ICs can be used in inverters to generate an AC output voltage from a DC input voltage.中文回答:外置MOS管同步整流芯片介绍。

MEMORY存储芯片MAX813LESA+中文规格书

Manual Reset Input Many μP-based products require manual reset capabil -ity, allowing the operator, a test technician, or external logic circuitry to initiate a reset. A logic low on MR asserts reset. Reset remains asserted while MR is low, and for the Reset Active Timeout Period (t RP ) after MR returns high. This input has an internal 20kΩ pull-up resistor, so it can be left open if it is not used. MR can be driven with TTL or CMOS-logic levels, or with open-drain/collector outputs. Connect a normally open momentary switch from MR to GND to create a manual-reset function; external debounce circuitry is not required. If MR is driven from long cables or if the device is used in a noisy environment, connecting a 0.1μF capacitor from MR to ground provides additional noise immunity.Reset Threshold Accuracy The MAX811/MAX812 are ideal for systems using a 5V ±5% or 3V ±5% power supply with ICs specified for 5V ±10% or 3V ±10%, respectively. They are designed to meet worst-case specifications over temperature. The reset is guaranteed to assert after the power supplyfalls out of regulation, but before power drops below theminimum specified operating voltage range for the systemICs. The thresholds are pre-trimmed and exhibit tight dis -tribution, reducing the range over which an undesirable reset may occur.PINNAME FUNCTION MAX811MAX81211GND Ground 2—RESET Active-Low Reset Output. RESET remains low while V CC is below the reset threshold or while MR is held low. RESET remains low for the Reset Active Timeout Period (t RP ) after the reset conditions are terminated.—2RESET Active-High Reset Output. RESET remains high while V CC is below the reset threshold or while MR is held low. RESET remains high for Reset Active Timeout Period (t RP ) after the reset conditions are terminated.33MR Manual Reset Input. A logic low on MR asserts reset. Reset remains asserted as long as MR is low and for 180ms after MR returns high. This active-low input has an internal 20kΩ pull-up resistor. It can be driven from a TTL or CMOS-logic line, or shorted to ground with a switch. Leave open if unused.44V CC +5V, +3.3V, or +3V Supply Voltage Detailed DescriptionReset OutputA microprocessor’s (μP’s) reset input starts the μP in aknown state. These μP supervisory circuits assert resetto prevent code execution errors during power-up, power-down, or brownout conditions.RESET is guaranteed to be a logic low for V CC > 1V.Once V CC exceeds the reset threshold, an internal timerkeeps RESET low for the reset timeout period; after thisinterval, RESET goes high.If a brownout condition occurs (V CC dips below the resetthreshold), RESET goes low. Any time V CC goes belowthe reset threshold, the internal timer resets to zero, andRESET goes low. The internal timer starts after V CC returns above the reset threshold, and RESET remainslow for the reset timeout period.The manual reset input (MR ) can also initiate a reset. See the Manual Reset Input section.The MAX812 has an active-high RESET output that is theinverse of the MAX811’s RESET output.MAX811/MAX8124-Pin μP Voltage Monitorswith Manual Reset InputPin DescriptionPACKAGE TYPEPACKAGE CODE OUTLINE ND PATTERN NO.4 SOT143U4+121-005290-0183MAX811/MAX8124-Pin μP Voltage Monitorswith Manual Reset InputPackage InformationFor the latest package outline information and land patterns (footprints), go to . Note that a “+”, “#”, or “-” in the package code indicates RoHS status only. Package drawings may show a different suffixcharacter, but the drawing pertains to the package regardless of RoHS status.。

无锡英斯特微电子有限公司 A825 游戏鼠标芯片 数据手册说明书

A825游戏鼠标芯片数据手册版本V1.04无锡英斯特微电子有限公司目录1. 总体描述 (1)2. 特性 (1)3. 引脚排列 (2)4. 引脚说明 (2)5. 模块框图 (3)6. 应用说明 (3)6.1 按键阵列定义 (3)6.2 自定义按键说明 (3)6.3 CPI设置 (4)6.3.1 档位与数值设置 (4)6.3.2 档位的LED指示 (4)6.4 背光LED (4)6.4.1 同步背光效果 (4)6.4.2 流水背光效果 (4)6.4.3 反应模式 (5)6.4.4 背光灯操控方法 (5)6.5 配置存储功能 (5)6.6 宏配置 (6)7. 典型应用电路 (6)7.1 应用电路方案1 (6)7.2 应用电路方案2 (6)8. 电气特性 (7)8.1 极限参数 (7)8.2 推荐的应用条件 (7)8.3 直流电气参数(电压VDD = 5.0V, 温度Temperature = 25 ºC ) (8)8.4 交流电气参数(电压VDD = 5.0V, 温度Temperature = 25 ºC) (8)9. 封装规格 (8)10. 产品装配图 (9)11. 修订记录 (10)1.总体描述A825是一款搭配全速USB接口的CMOS传感器工艺的高性能游戏鼠标芯片,采用全新光学导航引擎,使用高精度图像识别算法技术,定位精准,CPI可达12800,最大帧率7000fps,最大速度60inch/s,最大加速度20g。

A825内置32Kb的超大容量存储器,用户可通过烧录/驱动程序设置按键、CPI档位与分辨率、背光模式与颜色等等功能,此设置可保存于存储器中。

其中,CPI档位数量用户可设置(最多6档),CPI档位对应的分辨率用户可设(范围200~12800,共23级可选);支持9个物理按键,按键和滚轮可设置成鼠标、键盘、多媒体按键,也可设置成宏按键(一种快捷方式,是鼠标按键、鼠标位移、键盘按键、多媒体按键等等的任意组合功能);背光有14种模式可供选择,部分模式可自定义颜色。

MITSUBISHI ELECTRIC RD07MUS2B TETRA 说明书

Date : 16th Feb. 2010Rev. Date :22th Jun. 2010Prepared : Y.TakaseS.KametaniConfirmed :T.Okawa(Taking charge of Silicon RF byMIYOSHI Electronics) SUBJECT: RD07MUS2B TETRA single-stage amplifier at f=350-400MHz,Vdd=7.2VSUMMARY:This application note shows the TETRA data .-Sample history :RD07MUS2B: Lot number “08XXA-G”, Sample No. “5”-Evaluate conditions :@ f=350MHz, 375MHz, 400MHz, Vdd=7.2V, Idq=250mAπ/4DQPSK, Filter (α=0.35), Symbol rate=18ksps, Band Width=18kHz- Results :Page 2. shows the summary data.Page 3. shows the Pout characteristics data.Page 4. shows the Pin characteristics data.Page 5-7. shows the characteristics data.Page 8. shows the Input / Output impedance vs. Frequency characteristics.Page 9. shows the equivalent circuit.1. Summary* ACP_1L ; ACP Low @Channel Spacing = 25kHzACP_1H ; ACP High @Channel Spacing = 25kHzConditions@ Modulation type ; π/4DQPSK, Filter (α=0.35, Current filter response ; Root cosine), Band Width=18kHz, Symbol rate=18ksps, PRBS9 (PN9)Setting ; Spectrum AnalyzerResolution BW ; 300Hz, Video BW ; 3kHz, Sweep Time ; 1.5s,Channel Spacing=25kHz (Band Width=18kHz),Detector ; RMS, Average sweep count “8”2. RF characteristics2-1. Pout vs.@ Vdd=7.2V,Idq=250mA, f=350MHz, 375MHz, 400MHz2-2. Pin vs., f=350MHz, 375MHz, 400MHz3. RF characteristics data*ACP_1L ; ACP Low @Channel Spacing = 25kHz ACP_1H ; ACP High @Channel Spacing = 25kHz*ACP_1L ; ACP Low @Channel Spacing = 25kHz ACP_1H ; ACP High @Channel Spacing = 25kHz*ACP_1L ; ACP Low @Channel Spacing = 25kHz ACP_1H ; ACP High @Channel Spacing = 25kHz4. Input / Output Impedance vs. Frequency characteristicsZout* (f=350,375,400MHz)@Po=4W, Vdd=7.2V, Idq=: Complex conjugate of Output impedance.---------------------------------------------------------------------------------------------------------------------------------------------- Zin* (f=350,375,400MHz)@ Po=4W, Vdd=7.2V,Zin* : Complex conjugate of Iutput impedance.Zo=10ohmf=350MHzZo=10ohm f=350MHzf=375MHzf=400MHz5. Equivalent circuit (@f=350 to 400MHz)Vgg VddGNDGNDRF-in RF-out。

M-System产品说明书.pdf_1693882024.9156795

BEFORE USE ....Thank you for choosing M-System. Before use, please check contents of the package you received as outlined below .If you have any problems or questions with the product, please contact M-System’s Sales Office or representatives. ■PACKAGE INCLUDES:DC alarm (body + base socket + input resistor) ................(1)Input resistor is provided only with current input type. ■MODEL NO.Confirm Model N o. marking on the product to be exactly what you ordered.■INSTRUCTION MANUALThis manual describes necessary points of caution when you use this product, including installation, connection and basic maintenance procedures.POINTS OF CAUTION■POWER INPUT RATING & OPERATIONAL RANGE• Locate the power input rating marked on the product and confirm its operational range as indicated below: AC power : Rating ±10%, 50/60 ±2 Hz, approx. 2VA DC power : R ating ±10%, approx. 2Wor 85 – 150V , approx. 2W for 110V rating ■GENERAL PRECAUTIONS• Before you remove the unit from its base socket or mount it, turn off the power supply and input signal for safety . ■ENVIRONMENT • Indoor use.• When heavy dust or metal particles are present in the air, install the unit inside proper housing with sufficient ventilation.• Do not install the unit where it is subjected to continuous vibration. Do not subject the unit to physical impact.• Environmental temperature must be within -5 to +60°C (23 to 140°F) with relative humidity within 30 to 90% RH in order to ensure adequate life span and operation. ■WIRING• Do not install cables close to noise sources (relay drive cable, high frequency line, etc.).• Do not bind these cables together with those in which noises are present. Do not install them in the same duct. ■AND ....• The unit is designed to function as soon as power is supplied, however, a warm up for 10 minutes is required for satisfying complete performance described in the data sheet.COMPONENT IDENTIFICATION■FRONT PANEL CONFIGURATION• ExplanationsHi and Lo setpoint rotary switches are used to set the alarm setpoints.The Hi and Lo LED, turn on when the coil for each relay is energized.• ExamplesFor setting the relay to trip above 80% of the full-scale input signal, set the Hi rotary switch (×10) to “8”, while the switch (×1) to “0”.INSTALLATIONDetach the yellow clamps located at the top and bottom of Shape and size of the base socket are slightly different with varioussocket types. ■DIN RAIL MOUNTINGSet the base socket so that its DIN rail adaptor is at the bot-tom. Position the upper hook at the rear side of base socket on the DIN rail and push in the lower. When removing the socket, push down the DIN rail adaptor utilizing a minus screwdriver and pull.■WALL MOUNTING Refer to “EXTERN AL DI-MENSIONS.”TERMINAL CONNECTIONSConnect the unit as in the diagram below or refer to the connection diagram on the front of the unit.When an input resistor is provided with the module, attach it together with input wiring to the input screw terminals.■EXTERNAL DIMENSIONS unit: mm (inch)CLAMP• When mounting, no extra space is needed between units.■CONNECTION DIAGRAM*Input shunt resistor attached for current input.■ N.O. (make) Relay■ N.C. (break) Relay■TERMINAL ASSIGNMENTS unit: mm (inch)INPUT RESISTORInput shunt resistor attachedfor current input.CHECKING1) Terminal wiring: Check that all cables are correctly con-nected according to the connection diagram.2) Power input voltage: Check voltage across the terminal 7 – 8 with a multimeter.3) Input: Check that the input signal is within 0 – 100% of the full-scale.4) Alarm operations: Check the alarm operations referring to the figure below.5) Output load: Check that the output load is 380V AC/120VA or 125V DC/30W at the maximum. For maxi-mum relay life with inductive load, external protection is recommended.MAINTENANCERegular calibration procedure is explained below:■CALIBRATIONWarm up the unit for at least 10 minutes.• Hi SetpointI ncrease the input signal from a value lower than the set-point and check that the trip point remains within the accuracy described in the data sheet.• Lo SetpointD ecrease the input signal from a value higher than the setpoint and check that the trip point remains within the accuracy described in the data sheet.When the setpoints are shifted, please contact M-System’s Sales Office or representatives.LIGHTNING SURGE PROTECTIONM-System offers a series of lightning surge protector for protection against induced lightning surges. Please contact M-System to choose appropriate models.。

MEMORY存储芯片MT25QU128ABA1ESE-0SIT中文规格书

Features•SPI-compatible serial bus interface•Single and double transfer rate (STR/DTR)•Clock frequency–166 MHz (MAX) for all protocols in STR –90 MHz (MAX) for all protocols in DTR•Dual/quad I/O commands for increased through-put up to 90 MB/s•Supported protocols in both STR and DTR –Extended I/O protocol –Dual I/O protocol –Quad I/O protocol •Execute-in-place (XIP)•PROGRAM/ERASE SUSPEND operations•Volatile and nonvolatile configuration settings •Software reset•Additional reset pin for selected part numbers•Dedicated 64-byte OTP area outside main memory –Readable and user-lockable–Permanent lock with PROGRAM OTP command •Erase capability –Bulk erase–Sector erase 64KB uniform granularity –Subsector erase 4KB, 32KB granularity •Security and write protection–Volatile and nonvolatile locking and software write protection for each 64KB sector –Nonvolatile configuration locking –Password protection–Hardware write protection: nonvolatile bits (BP[3:0] and TB) define protected area size –Program/erase protection during power-up –CRC detects accidental changes to raw data •Electronic signature–JEDEC-standard 3-byte signature (BB18h)–Extended device ID: two additional bytes identify device factory options •JESD47H-compliant–Minimum 100,000 ERASE cycles per sector –Data retention: 20 years (TYP)OptionsMarking•Voltage – 1.7–2.0V U •Density –128Mb128•Device stacking –MonolithicA •Device generationB •Die revisionA •Pin configuration–RESET# and HOLD#8•Sector Size –64KBE •Packages – JEDEC-standard, RoHS-compliant–24-ball T-PBGA, 05/6mm x 8mm (5 x 5 array)12–24-ball T-PBGA 05/6mm x 8mm (4 x 6 array)14–Wafer level chip-scale package,15balls , 9 active balls (XFWLBGA 0.5P)54–8-pin SOP2, 208 mils body width (SO8W)SE –16-pin SOP2, 300 mils body width (SO16W)SF –W-PDFN-8 6mm x 5mm (MLP8 6mm x 5mm)W7–W-PDFN-8 8mm x 6mm (MLP8 8mm x 6mm)W9•Standard security 0•Special options –Standard S –AutomotiveA •Operating temperature range –From –40°C to +85°C IT –From –40°C to +105°CAT找Memory 、FPGA 、二三极管、连接器、模块、光耦、电容电阻、单片机、处理器、晶振、传感器、 滤波器,上深圳市美光存储技术有限公司Signal Assignments – Package Code: SE, W7, W9Figure 7: 8-Pin, SOP2 or W-PDFN (Top View)12348765S#DQ1W#/DQ2V SS1MT25QXXXXXXX 3EXX-XXXXS#DQ1W#/DQ2V SSV CC DQ3/HOLD#C DQ0V CC DQ3/RESET#C DQ0Notes:1.RESET# or HOLD# signals can share pin 7 with DQ3, depending on the selected device(see Part Numbering Ordering Information). When using single and dual I/O commands on these parts, DQ3 must be driven HIGH by the host, or an external pull-up resistor must be placed on the PCB, in order to avoid allowing the HOLD# or RESET# input to float.2.On the underside of the W-PDFN package, there is an exposed central pad that is pulledinternally to V SS . It can be left floating or can be connected to V SS . It must not be con-nected to any other voltage or signal line on the PCB.3.MT25QXXXXXXX8EXX-XXXX not available in 8-pin package.Signal Assignments – Package Code: SFFigure 8: 16-Pin, Plastic Small Outline – SO16 (Top View)12345678161514131211109C DQ0V SS W#/DQ2DQ3/HOLD#V CC RESET#DNU DNU DNU DNU DNU DNU DNU C DQ0V SS W#/DQ2DNU DNU DNU DNU C DQ0V SS W#/DQ2DNU DNU DNU DNU S#DQ1DQ3/HOLD#V CC DNUDNU DNUDNU S#DQ1DQ3/RESET#V CC DNU DNUDNU DNU S#DQ18MT25QXXXXXXX 3EXX-XXXXMT25QXXXXXXX 1EXX-XXXX Notes:1.RESET# or HOLD# signals can share pin 1 with DQ3, depending on the selected device(see Part Numbering Ordering Information). When using single and dual I/O commands on these parts, DQ3 must be driven HIGH by the host, or an external pull-up resistor must be placed on the PCB, in order to avoid allowing the HOLD# or RESET# input to float.128Mb, 1.8V Multiple I/O Serial Flash Memory Signal Assignments – Package Code: SE, W7, W9128Mb, 1.8V Multiple I/O Serial Flash Memory Signal Assignments – Package Code: SF128Mb, 1.8V Multiple I/O Serial Flash MemorySignal Descriptions128Mb, 1.8V Multiple I/O Serial Flash Memory Package Dimensions – Package Code: 12Notes: 1.All dimensions are in millimeters.。

台积电bq20z655-R1电源管理芯片应用 说明书

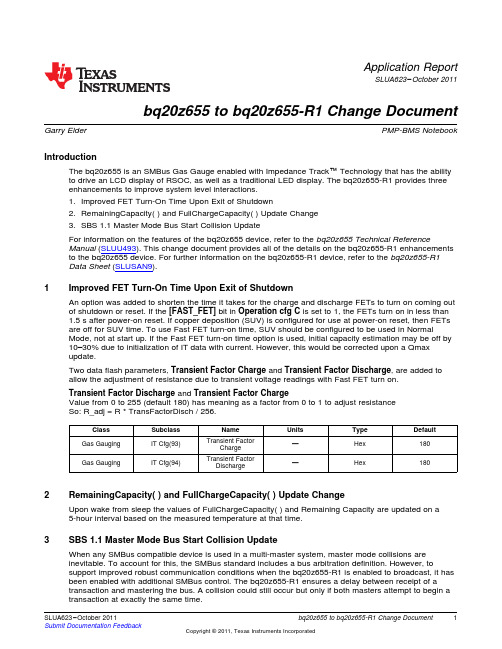

Application ReportSLUA623–October2011bq20z655to bq20z655-R1Change Document Garry Elder PMP-BMS NotebookIntroductionThe bq20z655is an SMBus Gas Gauge enabled with Impedance Track™Technology that has the ability to drive an LCD display of RSOC,as well as a traditional LED display.The bq20z655-R1provides three enhancements to improve system level interactions.1.Improved FET Turn-On Time Upon Exit of Shutdown2.RemainingCapacity()and FullChargeCapacity()Update Change3.SBS1.1Master Mode Bus Start Collision UpdateFor information on the features of the bq20z655device,refer to the bq20z655Technical ReferenceManual(SLUU493).This change document provides all of the details on the bq20z655-R1enhancements to the bq20z655device.For further information on the bq20z655-R1device,refer to the bq20z655-R1Data Sheet(SLUSAN9).1Improved FET Turn-On Time Upon Exit of ShutdownAn option was added to shorten the time it takes for the charge and discharge FETs to turn on coming out of shutdown or reset.If the[FAST_FET]bit in Operation cfg C is set to1,the FETs turn on in less than1.5s after power-on reset.If copper deposition(SUV)is configured for use at power-on reset,then FETsare off for SUV time.To use Fast FET turn-on time,SUV should be configured to be used in NormalMode,not at start up.If the Fast FET turn-on time option is used,initial capacity estimation may be off by 10–30%due to initialization of IT data with current.However,this would be corrected upon a Qmaxupdate.Two data flash parameters,Transient Factor Charge and Transient Factor Discharge,are added to allow the adjustment of resistance due to transient voltage readings with Fast FET turn on.Transient Factor Discharge and Transient Factor ChargeValue from0to255(default180)has meaning as a factor from0to1to adjust resistanceSo:R_adj=R*TransFactorDisch/256.Class Subclass Name Units Type DefaultTransient FactorGas Gauging IT Cfg(93)—Hex180ChargeTransient FactorGas Gauging IT Cfg(94)—Hex180Discharge2RemainingCapacity()and FullChargeCapacity()Update ChangeUpon wake from sleep the values of FullChargeCapacity()and Remaining Capacity are updated on a5-hour interval based on the measured temperature at that time.3SBS1.1Master Mode Bus Start Collision UpdateWhen any SMBus compatible device is used in a multi-master system,master mode collisions areinevitable.To account for this,the SMBus standard includes a bus arbitration definition.However,tosupport improved robust communication conditions when the bq20z655-R1is enabled to broadcast,it has been enabled with additional SMBus control.The bq20z655-R1ensures a delay between receipt of atransaction and mastering the bus.A collision could still occur but only if both masters attempt to begin a transaction at exactly the same time.1 SLUA623–October2011bq20z655to bq20z655-R1Change Document Submit Documentation FeedbackCopyright©2011,Texas Instruments IncorporatedSBS1.1Master Mode Bus Start Collision Update The bq20z655-R1introduces a delay between the selected host command and the gas gauge mastertransaction.An internal timer is started at the end of the selected SMBus host transaction(SMB SyncCommand),generating an interrupt when the timer reaches the end of the delay time.This interrupt sets up the SMBus hardware to generate the master transaction.The start occurs only if there is a mastertransaction request pending,which means the device must be configured for broadcast and SMBussynchronization,and there must be an alarm condition or charger update pending.SMB Sync Delay sets the duration of the delay.Units are488µs,which is the low-frequency oscillator input divided by16.There is an additional delay of about700µs for the execution of the end of SMBus handling and timer setup.This means the units are488+700µs.Such precision is unlikely to benecessary,since there should be a reliable"dead time"after a given command.Setting the delay time to zero disables SMBus synchronization and returns the gauge to the previouscompletely asynchronous operation.SMB Sync Command sets the host command which will trigger the delay to the subsequent SMBusmaster transaction.Setting the command to0xff will enable triggering after any command.Selecting a useful command will require monitoring the host communication to determine its repeatable patterns.A command will need to be determined which is used somewhat frequently in all operationalmodes and is followed by a predictable"dead time."If communication is particularly sparse,it is advisable to use the"any command"setting of0xff.3.1Features Removed to Support This ChangeWhere present,the SMBus command and associated data flash of Manufacturer Block Command4was removed to recover data flash space necessary for the new configuration constants.Class Subclass Name Units Type Default0123456789ABCDE System Data Manufacturer Info Manuf Block4—StringF0123.2Additional Data Flash Configuration ConstantsClass Subclass Name Units Type DefaultSBM SyncConfiguration AFE Hex Uchar0xffCommandConfiguration AFE SBM Sync Delay488µs Uchar502bq20z655to bq20z655-R1Change Document SLUA623–October2011Submit Documentation FeedbackCopyright©2011,Texas Instruments IncorporatedIMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,modifications,enhancements,improvements, and other changes to its products and services at any time and to discontinue any product or service without notice.Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by government requirements,testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design.Customers are responsible for their products and applications using TI components.To minimize the risks associated with customer products and applications,customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any TI patent right,copyright,mask work right, or other TI intellectual property right relating to any combination,machine,or process in which TI products or services are rmation published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.Reproduction of this information with alteration is an unfair and deceptive business practice.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements.TI products are not authorized for use in safety-critical applications(such as life support)where a failure of the TI product would reasonably be expected to cause severe personal injury or death,unless officers of the parties have executed an agreement specifically governing such use.Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications,and acknowledge and agree that they are solely responsible for all legal,regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications,notwithstanding any applications-related information or support that may be provided by TI.Further,Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or"enhanced plastic."Only products designated by TI as military-grade meet military specifications.Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk,and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use. TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS16949requirements.Buyers acknowledge and agree that,if they use any non-designated products in automotive applications,TI will not be responsible for any failure to meet such requirements.Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAudio /audio Communications and Telecom /communicationsAmplifiers Computers and Peripherals /computersData Converters Consumer Electronics /consumer-appsDLP®Products Energy and Lighting /energyDSP Industrial /industrialClocks and Timers /clocks Medical /medicalInterface Security /securityLogic Space,Avionics and Defense /space-avionics-defense Power Mgmt Transportation and Automotive /automotiveMicrocontrollers Video and Imaging /videoRFID OMAP Mobile Processors /omapWireless Connectivity /wirelessconnectivityTI E2E Community Home Page Mailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2011,Texas Instruments Incorporated。