CY7C1069DV33-10ZXI中文资料

CY7C64713资料

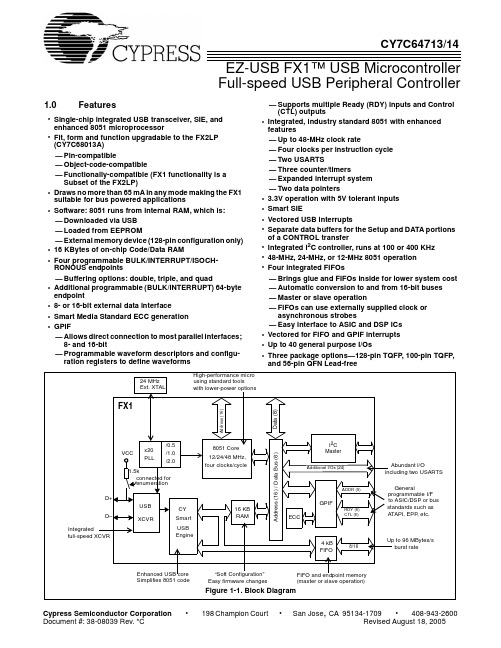

The 8051 microprocessor embedded in the FX1 family has 256 bytes of register RAM, an expanded interrupt system, three timer/counters, and two USARTs. 4.2.1 8051 Clock Frequency

24 MHz Ext. XTAL High-performance micro using standard tools with lower-power options

• • • • • • •

• • •

— Supports multiple Ready (RDY) inputs and Control (CTL) outputs Integrated, industry standard 8051 with enhanced features — Up to 48-MHz clock rate — Four clocks per instruction cycle — Two USARTS — Three counter/timers — Expanded interrupt system — Two data pointers 3.3V operation with 5V tolerant inputs Smart SIE Vectored USB interrupts Separate data buffers for the Setup and DATA portions of a CONTROL transfer Integrated I2C controller, runs at 100 or 400 KHz 48-MHz, 24-MHz, or 12-MHz 8051 operation Four integrated FIFOs — Brings glue and FIFOs inside for lower system cost — Automatic conversion to and from 16-bit buses — Master or slave operation — FIFOs can use externally supplied clock or asynchronous strobes — Easy interface to ASIC and DSP ICs Vectored for FIFO and GPIF interrupts Up to 40 general purpose I/Os Three package options—128-pin TQFP, 100-pin TQFP, and 56-pin QFN Lead-free

NZX33B,133;NZX9V1C,133;NZX7V5C,133;NZX3V9B,133;NZX3V9A,133;中文规格书,Datasheet资料

4 of 13

/

NXP Semiconductors

NZX series

Single Zener diodes

Table 8. Characteristics per type; NZX2V1B to NZX18C …continued Tj = 25 C unless otherwise specified. NZXxxx Sel Working voltage VZ (V) IZ = 5 mA Min 7V5 A B C D X 8V2 A B C D 9V1 A B C D E 10 A B C D 11 A B C D 12 A B C D X 13 A B C 14 A B C 7.0 7.2 7.3 7.5 7.07 7.7 7.9 8.1 8.3 8.5 8.7 8.9 9.1 9.3 9.5 9.7 9.9 10.2 10.4 10.7 10.9 11.1 11.4 11.6 11.9 12.2 11.44 12.4 12.6 12.9 13.2 13.5 13.8 Max 7.3 7.6 7.7 7.9 7.45 8.1 8.3 8.5 8.7 8.9 9.1 9.3 9.5 9.7 9.9 10.1 10.3 10.6 10.8 11.1 11.3 11.6 11.9 12.1 12.4 12.7 12.03 12.9 13.1 13.4 13.7 14.0 14.3 35 0.05 9.8 35 0.1 8 35 0.1 8 25 0.1 8 25 0.2 7 20 0.5 6 20 0.7 5 Differential resistance rdif () IZ = 5 mA Max 15 Max 1 VR (V) 5 Reverse current IR (A)

CY7C1051DV33芯片手册

PRELIMINARY 8-Mbit (512K x 16) Static RAMCY7C1051DV33Features•High speed —t AA = 10 ns •Low active power—I CC = 110 mA @ 10 ns •Low CMOS standby power —I SB2 = 20 mA •2.0V data retention•Automatic power-down when deselected •TTL-compatible inputs and outputs•Easy memory expansion with CE and OE features•Available in lead-free 48-ball FBGA and 44-pin TSOP II packagesFunctional Description [1]The CY7C1051DV33 is a high-performance CMOS Static RAM organized as 512K words by 16 bits.Write to the device by taking Chip Enable (CE) and Write Enable (WE) inputs LOW. If Byte LOW Enable (BLE) is LOW,then data from IO pins (IO 0–IO 7), is written into the location specified on the address pins (A 0–A 18). If Byte HIGH Enable (BHE) is LOW, then data from IO pins (IO 8–IO 15) is written into the location specified on the address pins (A 0–A 18).Read from the device by taking Chip Enable (CE) and Output Enable (OE) LOW while forcing the Write Enable (WE) HIGH.If Byte LOW Enable (BLE) is LOW, then data from the memory location specified by the address pins will appear on IO 0–IO 7.If Byte HIGH Enable (BHE) is LOW, then data from memory will appear on IO 8 to IO 15. See the “Truth Table” on page 8 for a complete description of Read and Write modes.The input/output pins (IO 0–IO 15) are placed in a high-impedance state when the device is deselected (CE HIGH), the outputs are disabled (OE HIGH), the BHE and BLE are disabled (BHE, BLE HIGH), or a Write operation (CE LOW,and WE LOW) is in progress.The CY7C1051DV33 is available in a 44-pin TSOP II package with center power and ground (revolutionary) pinout, as well as a 48-ball fine-pitch ball grid array (FBGA) package.Note1.For guidelines on SRAM system design, please refer to the “System Design Guidelines” Cypress application note, available on the internet at .1415Logic Block DiagramA 1A 2A 3A 4A 5A 6A 7A 8COLUMN DECODERR O W D E C O D E RS E N S E A M P SINPUT BUFFER512K × 16ARRAYA 0A 11A 13A 12A A A 16A 17A 18A 9A 10IO 0–IO 7OE IO 8–IO 15CE WE BLEBHEPRELIMINARY CY7C1051DV33Selection Guide–10Unit Maximum Access Time 10ns Maximum Operating Current 110mA Maximum CMOS Standby Current20mAPin Configurations [2]48-ball Mini FBGAWE V CC A 11A 10NC A 6A 0A 3CE IO 10IO 8IO 9A 4A 5IO 11IO 13IO 12IO 14IO 15V SS A 9A 8OE V SS A 7IO 0BHE NC A 17A 2A 1BLE V CC IO 2IO 1IO 3IO 4IO 5IO 6IO 7A 15A 14A 13A 12NC A 18NC326541D E B A C F G HA 16(Top View)TSOP IIWE 1234567891011143132363534333740393812134144434216152930V CC A 5A 6A 7A 8A 0A 1OE V SS A 17IO 15A 2CE IO 2IO 0IO 1BHE A 3A 418172019IO 32728252622212324V SS IO 6IO 4IO 5IO 7A 16A 15BLE V CC IO 14IO 13IO 12IO 11IO 10IO 9IO 8A 14A 13A 12A 11A 9A 10A 18(Top View)Note2.NC pins are not connected on the diePRELIMINARY CY7C1051DV33Maximum Ratings(Exceeding the maximum ratings may impair the useful life of the device. These are for user guidelines, they are not tested.)Storage Temperature .................................–65°C to +150°C Ambient Temperature withPower Applied.............................................–55°C to +125°C Supply Voltage on V CC to Relative GND [3]....–0.5V to +4.6V DC Voltage Applied to Outputsin High-Z State [3]....................................–0.3V to V CC + 0.3V DC Input Voltage [3].................................–0.3V to V CC + 0.3VCurrent into Outputs (LOW).........................................20 mA Static Discharge Voltage............................................>2001V (per MIL-STD-883, Method 3015)Latch-up Current......................................................>200 mAOperating RangeRange Ambient Temperature V CC Industrial–40°C to +85°C3.3V ± 0.3VDC Electrical Characteristics Over the Operating RangeParameter DescriptionTest Conditions–10Unit Min MaxV OH Output HIGH Voltage V CC = Min, I OH = –4.0 mA 2.4V V OL Output LOW Voltage V CC = Min, I OL = 8.0 mA0.4V V IH Input HIGH Voltage 2.0V CC + 0.3V V IL [3]Input LOW Voltage –0.30.8V I IX Input Leakage Current GND < V I < V CC–1+1μA I OZ Output Leakage Current GND < V OUT < V CC , Output Disabled –1+1μA I CCV CC Operating Supply CurrentV CC = Max, f = f MAX = 1/t RC100 MHz 110mA83 MHz 100 66 MHz 9040 MHz80I SB1Automatic CE Power Down Current —TTL Inputs Max V CC , CE > V IH V IN > V IH or V IN < V IL , f = f MAX 40mA I SB2Automatic CE Power Down Current —CMOS Inputs Max V CC , CE > V CC – 0.3V,V IN > V CC – 0.3V or V IN < 0.3V, f = 020mACapacitance [4]Parameter DescriptionTest ConditionsMax.Unit C IN Input Capacitance T A = 25°C, f = 1 MHz, V CC = 3.3V12pF C OUTIO Capacitance12pFNotes3.V IL (min) = –2.0V and V IH (max) = V CC + 2.0V for pulse durations of less than 20 ns.4.Tested initially and after any design or process changes that may affect these parametersThermal Resistance [4]ParameterDescription Test ConditionsFBGA PackageTSOP II PackageUnit ΘJA Thermal Resistance (Junction to Ambient)Still Air, soldered on a 3 × 4.5 inch, four-layer printed circuit board28.3151.43°C/W ΘJCThermal Resistance (Junction to Case)11.415.8°C/WPRELIMINARYCY7C1051DV33AC Test Loads and Waveforms [5]AC Switching Characteristics [6] Over the Operating RangeParameterDescription–10UnitMinMaxRead Cycle t power [7]V CC (typical) to the first access 100μs t RC Read Cycle Time 10ns t AA Address to Data Valid10ns t OHA Data Hold from Address Change 3ns t ACE CE LOW to Data Valid 10ns t DOE OE LOW to Data Valid 5ns t LZOE OE LOW to Low-Z 0ns t HZOE OE HIGH to High-Z [8, 9]5ns t LZCE CE LOW to Low-Z [9]3ns t HZCE CE HIGH to High-Z [8, 9]5ns t PU CE LOW to Power Up 0ns t PD CE HIGH to Power Down 10ns t DBE Byte Enable to Data Valid 5ns t LZBE Byte Enable to Low-Z 0ns t HZBEByte Disable to High-Z6nsNotes5.AC characteristics (except High-Z) are tested using the load conditions shown in Figure (a). High-Z characteristics are tested for all speeds using the test loadshown in Figure (c).6.Test conditions assume signal transition time of 3 ns or less, timing reference levels of 1.5V, input pulse levels of 0 to 3.0V.7.t POWER gives the minimum amount of time that the power supply should be at typical V CC values until the first memory access can be performed.8.t HZOE , t HZCE , t HZBE and t HZWE are specified with a load capacitance of 5 pF as in part (d) of AC Test Loads.Transition is measured when the outputs enter ahigh impedance state.9.At any given temperature and voltage condition, t HZCE is less than t LZCE , t HZOE is less than t LZOE , t HZBE is less than t LZBE , and t HZWE is less than t LZWE for anygiven device.90%10%3.0VGND90%10%ALL INPUT PULSES * CAPACITIVE LOAD CONSISTS OF ALL COMPONENTS OF THE TEST ENVIRONMENTRise Time: 1 V/nsFall Time: 1 V/ns30 pF*OUTPUTZ = 50Ω50Ω1.5V (a)3.3V OUTPUT5 pF(c)R 317ΩR2351ΩHigh-Z Characteristics(b)PRELIMINARY CY7C1051DV33Data Retention WaveformWrite Cycle [10, 11]t WC Write Cycle Time 10ns t SCE CE LOW to Write End 7ns t AW Address Setup to Write End 7ns t HA Address Hold from Write End 0ns t SA Address Setup to Write Start 0ns t PWE WE Pulse Width 7ns t SD Data Setup to Write End 5ns t HD Data Hold from Write End 0ns t LZWE WE HIGH to Low-Z [9]3ns t HZWE WE LOW to High-Z [8, 9]5ns t BWByte Enable to End of Write7nsData Retention Characteristics Over the Operating RangeParameter DescriptionConditions [12]Min MaxUnit V DR V CC for Data Retention 2.0V I CCDR Data Retention CurrentV CC = V DR = 2.0V , CE > V CC – 0.3V , V IN > V CC – 0.3V or V IN < 0.3V20mA t CDR [4]Chip Deselect to Data Retention Time 0ns t R [13]Operation Recovery Timet RCnsAC Switching Characteristics [6] Over the Operating Range (continued)ParameterDescription–10UnitMinMax3.0V 3.0V t CDRV DR > 2VDATA RETENTION MODEt RCEV CC Notes10.The internal Write time of the memory is defined by the overlap of CE LOW, and WE LOW. CE and WE must be LOW to initiate a Write, and the transition ofeither of these signals can terminate the Write. The input data setup and hold timing should be referenced to the leading edge of the signal that terminates the Write.11.The minimum Write cycle time for Write Cycle No. 3 (WE controlled, OE LOW) is the sum of t HZWE and t SD .12.No inputs may exceed V CC + 0.3V13.Full device operation requires linear V CC ramp from V DR to V CC (min) > 50 μs or stable at V CC (min) > 50 μs.PRELIMINARY CY7C1051DV33Switching WaveformsRead Cycle No. 1[14, 15]Read Cycle No. 2 (OE Controlled)[15, 16]Notes14.Device is continuously selected. OE, CE, BHE or BHE or both= V IL .15.WE is HIGH for Read cycle.16.Address valid prior to or coincident with CE transition LOW.PREVIOUS DATA VALIDDATA VALIDt RCt AAt OHAADDRESSDATA OUT50%50%DATA VALIDt RCt ACEt DOE t LZOE t LZCE t PUHIGH IMPEDANCEt HZOEt HZBEt PDHIGHOE CEICC ISB IMPEDANCEADDRESSDATA OUT V CC SUPPLY t DBE t LZBEt HZCE BHE,BLECURRENTI CCI SBPRELIMINARY CY7C1051DV33Write Cycle No. 1 (CE Controlled)[17, 18]Write Cycle No. 2 (BLE or BHE Controlled)Notes17.Data I/O is high-impedance if OE or BHE or BLE or both = V IH .18.If CE goes HIGH simultaneously with WE going HIGH, the output remains in a high-impedance state.Switching Waveforms (continued)t HDt SDt SCEt SA t HAt AWt PWEt WCBWDATAI/OADDRESSCEWEBHE,BLEt t HDt SDt BWt SA t HAt AWt PWEt WCt SCEDATAI/OADDRESSBHE,BLEWECEPRELIMINARY CY7C1051DV33Write Cycle No. 3 (WE Controlled, OE LOW)Switching Waveforms (continued)t HDt SDt SCEt HAt AWt PWEt WCt BWDATA I/OADDRESSCEWEBHE,BLEt SAt LZWEt HZWETruth TableCE OE WE BLE BHE I/O 0–I/O 7I/O 8–I/O 15ModePower H X X X X High-Z High-Z Power-down Standby (I SB )L L H L L Data Out Data Out Read All Bits Active (I CC )L L H L H Data Out High-Z Read Lower Bits Only Active (I CC )L L H H L High-Z Data Out Read Upper Bits Only Active (I CC )L X L L L Data In Data In Write All Bits Active (I CC )L X L L H Data In High-Z Write Lower Bits Only Active (I CC )L X L H L High-Z Data In Write Upper Bits Only Active (I CC )LHHXXHigh-ZHigh-ZSelected, Outputs DisabledActive (I CC )Ordering InformationSpeed (ns)Ordering Code Package Diagram Package TypeOperating Range 10CY7C1051DV33-10BAXI 51-8510648-ball FBGA (Pb-Free)IndustrialCY7C1051DV33-10ZSXI51-8508744-pin TSOP II (Pb-Free)Please contact your local Cypress sales representative for availability of these parts.PRELIMINARY CY7C1051DV33 Package DiagramsPRELIMINARY CY7C1051DV33Document #: 001-00063 Rev. *C Page 10 of 11© Cypress Semiconductor Corporation, 2006-2007. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the All products and company names mentioned in this document may be the trademarks of their respective holders.Figure 2. 44-pin TSOP II (51-85087)Package Diagrams (continued)51-85087-*APRELIMINARY CY7C1051DV33Document #: 001-00063 Rev. *C Page 11 of 11Document History Page Document Title: CY7C1051DV33 8-Mbit (512K x 16) Static RAM Document Number: 001-00063REV.ECN NO.Issue Date Orig. of Change Description of Change **342195See ECN PCI New Data Sheet *A 380574See ECN SYT Redefined I CC values for Com’l and Ind’l temperature rangesI CC (Com’l): Changed from 110, 90 and 80 mA to 110, 100 and 95 mA for 8, 10and 12 ns speed bins respectivelyI CC (Ind’l): Changed from 110, 90 and 80 mA to 120, 110 and 105 mA for 8, 10and 12 ns speed bins respectivelyChanged the Capacitance values from 8 pF to 10 pF on Page # 3*B 485796See ECN NXR Changed address of Cypress Semiconductor Corporation on Page# 1 from“3901 North First Street” to “198 Champion Court”Removed -8 and -12 Speed bins from product offering,Removed Commercial Operating Range option,Modified Maximum Ratings for DC input voltage from -0.5V to -0.3V andV CC + 0.5V to V CC + 0.3VChanged the Description of I IX from Input Load Current toInput Leakage Current.Changed t HZBE from 5 ns to 6 nsUpdated footnote #7 on High-Z parameter measurementAdded footnote #11Updated the Ordering Information table and Replaced Package Name columnwith Package Diagram.*C 866000See ECN NXRChanged ball E3 from V SS to NC in FBGA pin configuration [+] FeedbThis datasheet has been downloaded from:Free DownloadDaily Updated Database100% Free Datasheet Search Site100% Free IC Replacement Search SiteConvenient Electronic DictionaryFast Search SystemAll Datasheets Cannot Be Modified Without PermissionCopyright © Each Manufacturing Company。

USB控制芯片cy7c68013中文手册

■ CY7C68013A:适合非电池供电应用 ❐ 挂起电流:300 μA (typ)

■ 有五种无铅封装供选择,可包含多达 40 个 GPIO ❐ 128 引脚 TQFP (40 个 GPIO)、 100 引脚 TQFP (40 个 GPIO)、 56 引脚 QFN (24 个 GPIO)、 56 引脚 SSOP (24 个 GPIO)和 56 引脚 VFBGA (24 个 GPIO)

注 1. 以 115 KBaud 的速率运行也是可能的,只要分别针对 UART0、 UART1 或针对二者将 8051 SMOD0 或 SMOD1 位编程为 “1” 即可。

文件编号:001-50431 修订版 **

第 3 页,共 61 页

[+] Feedback

CY7C68013A, CY7C68014A CY7C68015A, CY7C68016A

■ 有商业和工业温度等级供选择 (除 VFBGA 外的所有封装)

Cypress Semiconductor Corporation • 198 Champion Court 文件编号:001-50431 修订版 **

• San Jose, CA 95134-1709 • 408-943-2600

修订时间 2008 年 12 月 11 日

1.2 特色 (仅限 CY7C68015A/16A)

■ CY7C68016A:适合电池供电应用 ❐ 挂起电流:100 μA (typ)

■ CY7C68015A:适合非电池供电应用 ❐ 挂起电流:300 μA (typ)

■ 采用无铅 56 引脚 QFN 封装 (26 个 GPIO) ❐ 比 CY7C68013A/14A 多 2 个 GPIO,可在同样的空间内实现 额外的功能

CY7C1041CV33-10ZXI中文资料

Industrial

100

95

Automotive-A

100

Automotive-E

Commercial/

10

10

Industrial

Automotive-A

10

Automotive-E

48-ball FBGA

(Top View)

12

3

4

5

6

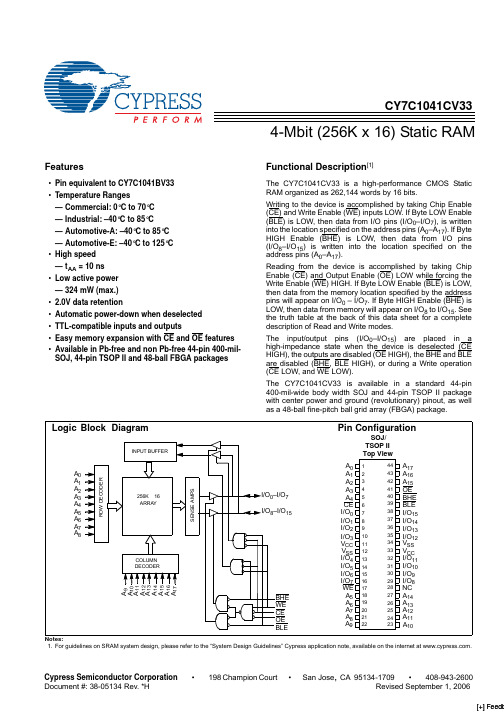

CY7C1041CV33

-15

-20

Unit

15

20

ns

80

28

A6, E3, G2, H1, No Connect No Connects. This pin is not connected to the die

H6

17

G5

Input/Control Write Enable Input, active LOW. When selected LOW, a

A5 18 A6 19 A7 20 A8 21 A9 22

44 A17 43 A16 42 A15 41 OE

40 BHE 39 BLE

38 I/O15 37 I/O14 36 I/O13 35 I/O12 34 VSS 33 VCC 32 I/O11 31 I/O10 30 I/O9 29 I/O8 28 NC

WRITE is conducted. When selected HIGH, a READ is

conducted.

6

ห้องสมุดไป่ตู้B5

Input/Control Chip Enable Input, active LOW. When LOW, selects the chip.

When HIGH, deselects the chip.

CY7C63723-PC中文资料

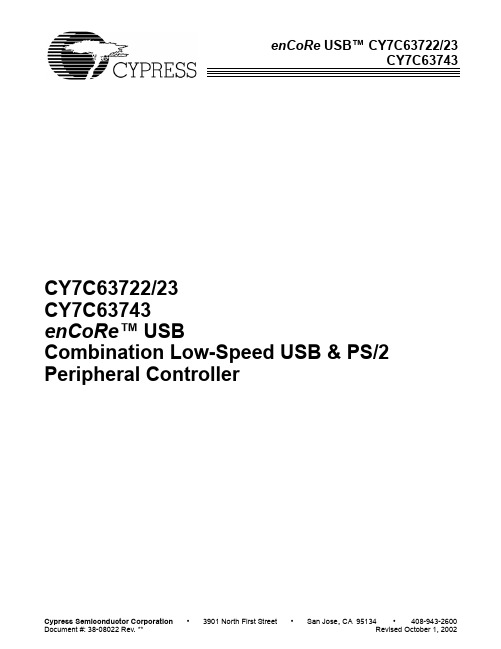

元器件交易网CY7C63743CY7C63722/23CY7C63743enCoRe™ USBCombination Low-Speed USB & PS/2Peripheral ControllerTABLE OF CONTENTS1.0 FEATURES (5)2.0 FUNCTIONAL OVERVIEW (6)2.1 enCoRe USB - The New USB Standard (6)3.0 LOGIC BLOCK DIAGRAM (7)4.0 PIN CONFIGURATIONS (7)5.0 PIN ASSIGNMENTS (7)6.0 PROGRAMMING MODEL (8)6.1 Program Counter (PC) (8)6.2 8-bit Accumulator (A) (8)6.3 8-bit Index Register (X) (8)6.4 8-bit Program Stack Pointer (PSP) (8)6.5 8-bit Data Stack Pointer (DSP) (9)6.6 Address Modes (9)6.6.1 Data (9)6.6.2 Direct (9)6.6.3 Indexed (9)7.0 INSTRUCTION SET SUMMARY (10)8.0 MEMORY ORGANIZATION (11)8.1 Program Memory Organization (11)8.2 Data Memory Organization (12)8.3 I/O Register Summary (13)9.0 CLOCKING (14)9.1 Internal/External Oscillator Operation (15)9.2 External Oscillator (16)10.0 RESET (16)10.1 Low-voltage Reset (LVR) (16)10.2 Brown Out Reset (BOR) (16)10.3 Watchdog Reset (WDR) (17)11.0 SUSPEND MODE (17)11.1 Clocking Mode on Wake-up from Suspend (18)11.2 Wake-up Timer (18)12.0 GENERAL PURPOSE I/O PORTS (18)12.1 Auxiliary Input Port (21)13.0 USB SERIAL INTERFACE ENGINE (SIE) (22)13.1 USB Enumeration (22)13.2 USB Port Status and Control (22)14.0 USB DEVICE (24)14.1 USB Address Register (24)14.2 USB Control Endpoint (24)14.3 USB Non-control Endpoints (25)14.4 USB Endpoint Counter Registers (26)15.0 USB REGULATOR OUTPUT (27)16.0 PS/2 OPERATION (27)17.0 SERIAL PERIPHERAL INTERFACE (SPI) (28)17.1 Operation as an SPI Master (29)17.2 Master SCK Selection (29)17.3 Operation as an SPI Slave (29)17.4 SPI Status and Control (30)17.5 SPI Interrupt (31)17.6 SPI Modes for GPIO Pins (31)18.0 12-BIT FREE-RUNNING TIMER (31)19.0 TIMER CAPTURE REGISTERS (32)20.0 PROCESSOR STATUS AND CONTROL REGISTER (35)21.0 INTERRUPTS (36)21.1 Interrupt Vectors (37)21.2 Interrupt Latency (37)21.3 Interrupt Sources (37)22.0 USB MODE TABLES (42)23.0 REGISTER SUMMARY (47)24.0 ABSOLUTE MAXIMUM RATINGS (48)25.0 DC CHARACTERISTICS (48)26.0 SWITCHING CHARACTERISTICS (50)27.0 ORDERING INFORMATION (55)28.0 PACKAGE DIAGRAMS (55)LIST OF FIGURESFigure 8-1. Program Memory Space with Interrupt Vector Table (11)Figure 8-2. Data Memory Organization (12)Figure 9-1. Clock Oscillator On-chip Circuit (14)Figure 9-2. Clock Configuration Register (Address 0xF8) (14)Figure 10-1. Watchdog Reset (WDR, Address 0x26) (17)Figure 12-1. Block Diagram of GPIO Port (one pin shown) (19)Figure 12-2. Port 0 Data (Address 0x00) (19)Figure 12-3. Port 1 Data (Address 0x01) (19)Figure 12-4. GPIO Port 0 Mode0 Register (Address 0x0A) (20)Figure 12-5. GPIO Port 0 Mode1 Register (Address 0x0B) (20)Figure 12-6. GPIO Port 1 Mode0 Register (Address 0x0C) (20)Figure 12-7. GPIO Port 1 Mode1 Register (Address 0x0D) (20)Figure 12-8. Port 2 Data Register (Address 0x02) (21)Figure 13-1. USB Status and Control Register (Address 0x1F) (23)Figure 14-1. USB Device Address Register (Address 0x10) (24)Figure 14-2. Endpoint 0 Mode Register (Address 0x12) (25)Figure 14-3. USB Endpoint EP1, EP2 Mode Registers (Addresses 0x14 and 0x16) (26)Figure 14-4. Endpoint 0,1,2 Counter Registers (Addresses 0x11, 0x13 and 0x15) (26)Figure 17-1. SPI Block Diagram (28)Figure 16-1. Diagram of USB-PS/2 System Connections (28)Figure 17-2. SPI Data Register (Address 0x60) (29)Figure 17-3. SPI Control Register (Address 0x61) (30)Figure 17-4. SPI Data Timing (31)Figure 18-1. Timer LSB Register (Address 0x24) (31)Figure 18-2. Timer MSB Register (Address 0x25) (32)Figure 18-3. Timer Block Diagram (32)Figure 19-1. Capture Timers Block Diagram (33)Figure 19-2. Capture Timer A-Rising, Data Register (Address 0x40) (33)Figure 19-3. Capture Timer A-Falling, Data Register (Address 0x41) (34)Figure 19-4. Capture Timer B-Rising, Data Register (Address 0x42) (34)Figure 19-5. Capture Timer B-Falling, Data Register (Address 0x43) (34)Figure 19-6. Capture Timer Status Register (Address 0x45) (34)Figure 19-7. Capture Timer Configuration Register (Address 0x44) (34)Figure 20-1. Processor Status and Control Register (Address 0xFF) (35)Figure 21-1. Global Interrupt Enable Register (Address 0x20) (38)Figure 21-2. Endpoint Interrupt Enable Register (Address 0x21) (39)Figure 21-3. Interrupt Controller Logic Block Diagram (40)Figure 21-4. Port 0 Interrupt Enable Register (Address 0x04) (40)Figure 21-5. Port 1 Interrupt Enable Register (Address 0x05) (40)Figure 21-6. Port 0 Interrupt Polarity Register (Address 0x06) (41)Figure 21-7. Port 1 Interrupt Polarity Register (Address 0x07) (41)Figure 21-8. GPIO Interrupt Diagram (41)Figure 26-1. Clock Timing (51)Figure 26-2. USB Data Signal Timing (51)Figure 26-3. Receiver Jitter Tolerance (52)Figure 26-4. Differential to EOP Transition Skew and EOP Width (52)Figure 26-5. Differential Data Jitter (52)Figure 26-7. SPI Slave Timing, CPHA = 0 (53)Figure 26-6. SPI Master Timing, CPHA = 0 (53)Figure 26-8. SPI Master Timing, CPHA = 1 (54)Figure 26-9. SPI Slave Timing, CPHA = 1 (54)LIST OF TABLESTable 8-1. I/O Register Summary (13)Table 11-1. Wake-up Timer Adjust Settings (18)Table 12-1. Ports 0 and 1 Output Control Truth Table (21)Table 13-1. Control Modes to Force D+/D– Outputs (24)Table 17-1. SPI Pin Assignments (31)Table 19-1. Capture Timer Prescalar Settings (Step size and range for FCLK = 6 MHz) (35)Table 21-1. Interrupt Vector Assignments (37)Table 22-1. USB Register Mode Encoding for Control and Non-Control Endpoints (42)Table 22-2. Decode table for Table 22-3: “Details of Modes for Differing Traffic Conditions” (44)Table 22-3. Details of Modes for Differing Traffic Conditions (45)Table 28-1. CY7C63722-XC Probe Pad Coordinates in microns ((0,0) to bond pad centers) (57)1.0 Features•enCoRe™ USB - enhanced Component Reduction—Internal oscillator eliminates the need for an external crystal or resonator—Interface can auto-configure to operate as PS/2 or USB without the need for external components to switch between modes (no GPIO pins needed to manage dual mode capability)—Internal 3.3V regulator for USB pull-up resistor—Configurable GPIO for real-world interface without external components•Flexible, cost-effective solution for applications that combine PS/2 and low-speed USB, such as mice, gamepads, joysticks, and many others.•USB Specification Compliance—Conforms to USB Specification, Version 2.0—Conforms to USB HID Specification, Version 1.1—Supports 1 Low-Speed USB device address and 3 data endpoints—Integrated USB transceiver—3.3V regulated output for USB pull-up resistor•8-bit RISC microcontroller—Harvard architecture—6-MHz external ceramic resonator or internal clock mode—12-MHz internal CPU clock—Internal memory—256 bytes of RAM—8 Kbytes of EPROM—Interface can auto-configure to operate as PS/2 or USB—No external components for switching between PS/2 and USB modes—No GPIO pins needed to manage dual mode capability•I/O ports—Up to 16 versatile General Purpose I/O (GPIO) pins, individually configurable—High current drive on any GPIO pin: 50 mA/pin current sink—Each GPIO pin supports high-impedance inputs, internal pull-ups, open drain outputs or traditional CMOS outputs —Maskable interrupts on all I/O pins•SPI serial communication block—Master or slave operation—2 Mbit/s transfers•Four 8-bit Input Capture registers—Two registers each for two input pins—Capture timer setting with 5 prescaler settings—Separate registers for rising and falling edge capture—Simplifies interface to RF inputs for wireless applications•Internal low-power wake-up timer during suspend mode—Periodic wake-up with no external components•Optional 6-MHz internal oscillator mode—Allows fast start-up from suspend mode•Watchdog Reset (WDR)•Low-voltage Reset at 3.75V•Internal brown-out reset for suspend mode•Improved output drivers to reduce EMI•Operating voltage from 4.0V to 5.5VDC•Operating temperature from 0 to 70 degrees Celsius•CY7C63723 available in 18-pin SOIC, 18-pin PDIP•CY7C63743 available in 24-pin SOIC, 24-pin PDIP•CY7C63722 available in DIE form•Industry standard programmer support2.0 Functional Overview2.1enCoRe USB - The New USB StandardCypress has re-invented its leadership position in the low-speed USB market with a new family of innovative microcontrollers. Introducing...enCoRe USB—“enhanced Component Reduction.” Cypress has leveraged its design expertise in USB solutions to create a new family of low-speed USB microcontrollers that enables peripheral developers to design new products with a minimum number of components. At the heart of the enCoRe USB technology is the breakthrough design of a crystal-less oscillator. By integrating the oscillator into our chip, an external crystal or resonator is no longer needed. We have also integrated other external components commonly found in low-speed USB applications such as pull-up resistors, wake-up circuitry, and a 3.3V regulator. All of this adds up to a lower system cost.The CY7C637xx is an 8-bit RISC One Time Programmable (OTP) microcontroller. The instruction set has been optimized specif-ically for USB and PS/2 operations, although the microcontrollers can be used for a variety of other embedded applications. The CY7C637xx features up to 16 general purpose I/O (GPIO) pins to support USB, PS/2 and other applications. The I/O pins are grouped into two ports (Port 0 to 1) where each pin can be individually configured as inputs with internal pull-ups, open drain outputs, or traditional CMOS outputs with programmable drive strength of up to 50 mA output drive. Additionally, each I/O pin can be used to generate a GPIO interrupt to the microcontroller. Note the GPIO interrupts all share the same “GPIO” interrupt vector. The CY7C637xx microcontrollers feature an internal oscillator. With the presence of USB traffic, the internal oscillator can be set to precisely tune to USB timing requirements (6 MHz ±1.5%). Optionally, an external 6-MHz ceramic resonator can be used to provide a higher precision reference for USB operation. This clock generator reduces the clock-related noise emissions (EMI). The clock generator provides the 6- and 12-MHz clocks that remain internal to the microcontroller.The CY7C637xx has 8 Kbytes of EPROM and 256 bytes of data RAM for stack space, user variables, and USB FIFOs.These parts include low-voltage reset logic, a watchdog timer, a vectored interrupt controller, a 12-bit free-running timer, and capture timers. The low-voltage reset (LVR) logic detects when power is applied to the device, resets the logic to a known state, and begins executing instructions at EPROM address 0x0000. LVR will also reset the part when V CC drops below the operating voltage range. The watchdog timer can be used to ensure the firmware never gets stalled for more than approximately 8 ms. The microcontroller supports 10 maskable interrupts in the vectored interrupt controller. Interrupt sources include the USB Bus-Reset, the 128-µs and 1.024-ms outputs from the free-running timer, three USB endpoints, two capture timers, an internal wake-up timer and the GPIO ports. The timers bits cause periodic interrupts when enabled. The USB endpoints interrupt after USB transactions complete on the bus. The capture timers interrupt whenever a new timer value is saved due to a selected GPIO edge event. The GPIO ports have a level of masking to select which GPIO inputs can cause a GPIO interrupt. For additional flexibility, the input transition polarity that causes an interrupt is programmable for each GPIO pin. The interrupt polarity can be either rising or falling edge.The free-running 12-bit timer clocked at 1 MHz provides two interrupt sources as noted above (128 µs and 1.024 ms). The timer can be used to measure the duration of an event under firmware control by reading the timer at the start and end of an event, and subtracting the two values. The four capture timers save a programmable 8 bit range of the free-running timer when a GPIO edge occurs on the two capture pins (P0.0, P0.1).The CY7C637xx includes an integrated USB serial interface engine (SIE) that supports the integrated peripherals. The hardware supports one USB device address with three endpoints. The SIE allows the USB host to communicate with the function integrated into the microcontroller. A 3.3V regulated output pin provides a pull-up source for the external USB resistor on the D– pin.The USB D+ and D– USB pins can alternately be used as PS/2 SCLK and SDATA signals, so that products can be designed to respond to either USB or PS/2 modes of operation. PS/2 operation is supported with internal pull-up resistors on SCLK and SDATA, the ability to disable the regulator output pin, and an interrupt to signal the start of PS/2 activity. No external components are necessary for dual USB and PS/2 systems, and no GPIO pins need to be dedicated to switching between modes. Slow edge rates operate in both modes to reduce EMI.3.0 Logic Block Diagram4.0 Pin Configurations5.0 Pin AssignmentsNameI/O CY7C63723CY7C63743CY7C63722Description18-Pin 24-Pin 25-Pad D–/SDATA,D+/SCLK I/O 121315161617USB differential data lines (D– and D+), or PS/2 clock and data signals (SDATA and SCLK)P0[7:0]I/O1, 2, 3, 4,15, 16, 17, 181, 2, 3, 4,21, 22, 23, 241, 2, 3, 4,22, 23, 24, 25GPIO Port 0 capable of sinking up to 50 mA/pin, or sinking controlled low or high programmable current.Can also source 2 mA current, provide a resistive pull-up, or serve as a high-impedance input. P0.0 and P0.1 provide inputs to Capture Timers A and B, respec-tively.P1[7:0]I/O5, 145, 6, 7, 8,17, 18, 19, 205, 6, 7, 8,18, 19, 20, 21IO Port 1 capable of sinking up to 50 mA/pin, or sinking controlled low or high programmable current. Can alsosource 2 mA current, provide a resistive pull-up, or serve as a high-impedance input.Wake-Up 12-bit Timer USB &D+,D–P1.0–P1.7Interrupt ControllerPort 0P0.0–P0.7GPIO8-bit RISC Xtal RAM 256 Byte EPROM 8K ByteCoreBrown-out Reset XcvrWatch Timer Dog 3.3V Port 1GPIO Capture TimersUSB Engine PS/2Internal Oscillator Oscillator Low ResetVoltage RegulatorTimerSPIXTALOUTXTALIN/P2.1VREG/P2.01234569111516171819202221P0.0P0.1P0.2P0.3P1.0P1.2VSS VREG/P2.0P0.6P1.5P1.1P1.3D+/SCLK P1.7D–/SDATA VCC14P0.710VPPXTALIN/P2.1XTALOUT121378P1.4P1.62423P0.4P0.524-pin SOIC/PDIPCY7C6374312346781011121315161817P0.0P0.1P0.2P0.3VSS VREG/P2.0P0.4P0.6P0.7D+/SCLK D–/SDATA VCC18-pin SOIC/PDIPP0.59VPPXTALIN/P2.1XTALOUTCY7C63723514P1.0P1.1Top View4 5 6 7 8 93 P 0.21 P 0.0 2 P 0.125 P 0.4 24 P 0.523 P 0.622 21 20 19 1811121314151617P0.3P1.0P1.2P1.4P1.6 VSS VSS V P P X T A L I N /P 2.1V R E G X T A L O U T V C C D -/S D A T A D+/SCLK P0.7P1.1P1.3P1.5P1.7CY7C63722-XCDIE106.0 Programming ModelRefer to the CYASM Assembler User’s Guide for more details on firmware operation with the CY7C637xx microcontrollers.6.1Program Counter (PC)The 14-bit program counter (PC) allows access for up to 8 Kbytes of EPROM using the CY7C637xx architecture. The program counter is cleared during reset, such that the first instruction executed after a reset is at address 0x0000. This instruction is typically a jump instruction to a reset handler that initializes the application.The lower 8 bits of the program counter are incremented as instructions are loaded and executed. The upper 6 bits of the program counter are incremented by executing an XPAGE instruction. As a result, the last instruction executed within a 256-byte “page”of sequential code should be an XPAGE instruction. The assembler directive “XPAGEON” will cause the assembler to insert XPAGE instructions automatically. As instructions can be either one or two bytes long, the assembler may occasionally need to insert a NOP followed by an XPAGE for correct execution.The program counter of the next instruction to be executed, carry flag, and zero flag are saved as two bytes on the program stack during an interrupt acknowledge or a CALL instruction. The program counter, carry flag, and zero flag are restored from the program stack only during a RETI instruction.Please note the program counter cannot be accessed directly by the firmware. The program stack can be examined by reading SRAM from location 0x00 and up.6.28-bit Accumulator (A)The accumulator is the general-purpose, do everything register in the architecture where results are usually calculated.6.38-bit Index Register (X)The index register “X” is available to the firmware as an auxiliary accumulator. The X register also allows the processor to perform indexed operations by loading an index value into X.6.48-bit Program Stack Pointer (PSP)During a reset, the program stack pointer (PSP) is set to zero. This means the program “stack” starts at RAM address 0x00 and “grows” upward from there. Note that the program stack pointer is directly addressable under firmware control, using the MOV PSP ,A instruction. The PSP supports interrupt service under hardware control and CALL, RET, and RETI instructions under firmware control.During an interrupt acknowledge, interrupts are disabled and the program counter, carry flag, and zero flag are written as two bytes of data memory. The first byte is stored in the memory addressed by the program stack pointer, then the PSP is incremented.The second byte is stored in memory addressed by the program stack pointer and the PSP is incremented again. The net effect is to store the program counter and flags on the program “stack” and increment the program stack pointer by two.The return from interrupt (RETI) instruction decrements the program stack pointer, then restores the second byte from memory addressed by the PSP . The program stack pointer is decremented again and the first byte is restored from memory addressed by the PSP . After the program counter and flags have been restored from stack, the interrupts are enabled. The effect is to restore the program counter and flags from the program stack, decrement the program stack pointer by two, and re-enable interrupts.The call subroutine (CALL) instruction stores the program counter and flags on the program stack and increments the PSP by two.XTALIN/P2.1IN 912136-MHz ceramic resonator or external clock input, or P2.1 inputXTALOUT OUT1013146-MHz ceramic resonator return pin or internal oscillator outputV PP 71011Programming voltage supply, ground for normal operation V CC111415Voltage supplyVREG/P2.0 81112Voltage supply for 1.3-k Ω USB pull-up resistor (3.3V nominal). Also serves as P2.0 input.V SS699, 10Ground5.0 Pin Assignments (continued)NameI/O CY7C63723CY7C63743CY7C63722Description18-Pin 24-Pin 25-PadThe return from subroutine (RET) instruction restores the program counter, but not the flags, from program stack and decrements the PSP by two.Note that there are restrictions in using the JMP, CALL, and INDEX instructions across the 4-KB boundary of the program memory. Refer to the CYASM Assembler User’s Guide for a detailed description.6.58-bit Data Stack Pointer (DSP)The data stack pointer (DSP) supports PUSH and POP instructions that use the data stack for temporary storage. A PUSH instruction will pre-decrement the DSP, then write data to the memory location addressed by the DSP. A POP instruction will read data from the memory location addressed by the DSP, then post-increment the DSP.During a reset, the Data Stack Pointer will be set to zero. A PUSH instruction when DSP equals zero will write data at the top of the data RAM (address 0xFF). This would write data to the memory area reserved for a FIFO for USB endpoint 0. In non-USB applications, this works fine and is not a problem.For USB applications, the firmware should set the DSP to an appropriate location to avoid a memory conflict with RAM dedicated to USB FIFOs. The memory requirements for the USB endpoints are shown in Section 8.2. For example, assembly instructions to set the DSP to 20h (giving 32 bytes for program and data stack combined) are shown below:MOV A,20h; Move 20 hex into Accumulator (must be D8h or less to avoid USB FIFOs)SWAP A,DSP; swap accumulator value into DSP register6.6Address ModesThe CY7C637xx microcontrollers support three addressing modes for instructions that require data operands: data, direct, and indexed.6.6.1DataThe “Data” address mode refers to a data operand that is actually a constant encoded in the instruction. As an example, consider the instruction that loads A with the constant 0x30:•MOV A, 30hThis instruction will require two bytes of code where the first byte identifies the “MOV A” instruction with a data operand as the second byte. The second byte of the instruction will be the constant “0xE8h”. A constant may be referred to by name if a prior “EQU” statement assigns the constant value to the name. For example, the following code is equivalent to the example shown above:•DSPINIT: EQU 30h•MOV A,DSPINIT6.6.2Direct“Direct” address mode is used when the data operand is a variable stored in SRAM. In that case, the one byte address of the variable is encoded in the instruction. As an example, consider an instruction that loads A with the contents of memory address location 0x10h:•MOV A, [10h]In normal usage, variable names are assigned to variable addresses using “EQU” statements to improve the readability of the assembler source code. As an example, the following code is equivalent to the example shown above:•buttons: EQU 10h•MOV A,[buttons]6.6.3Indexed“Indexed” address mode allows the firmware to manipulate arrays of data stored in SRAM. The address of the data operand is the sum of a constant encoded in the instruction and the contents of the “X” register. In normal usage, the constant will be the “base” address of an array of data and the X register will contain an index that indicates which element of the array is actually addressed:•array: EQU 10h•MOV X,3•MOV A,[x+array]This would have the effect of loading A with the fourth element of the SRAM “array” that begins at address 0x10h. The fourth element would be at address 0x13h.7.0 Instruction Set SummaryRefer to the CYASM Assembler User’s Guide for detailed information on these instructions. Note that conditional jump instructions (i.e., JC, JNC, JZ, JNZ) take 5 cycles if jump is taken, 4 cycles if no jump.MNEMONIC Operand Opcode Cycles MNEMONIC Operand Opcode Cycles HALT 007NOP 204ADD A,expr data014INC A acc214ADD A,[expr] direct026INC X x224ADD A,[X+expr] index037INC [expr] direct237ADC A,expr data044INC [X+expr] index248ADC A,[expr] direct056DEC A acc254ADC A,[X+expr] index067DEC X x264SUB A,expr data074DEC [expr] direct277SUB A,[expr] direct086DEC [X+expr] index288SUB A,[X+expr] index097IORD expr address295SBB A,expr data0A4IOWR expr address2A5SBB A,[expr] direct0B6POP A2B4SBB A,[X+expr] index0C7POP X2C4OR A,expr data0D4PUSH A2D5OR A,[expr] direct0E6PUSH X2E5OR A,[X+expr] index0F7SWAP A,X2F5AND A,expr data104SWAP A,DSP305AND A,[expr] direct116MOV [expr],A direct315AND A,[X+expr] index127MOV [X+expr],A index326XOR A,expr data134OR [expr],A direct337XOR A,[expr] direct146OR [X+expr],A index348XOR A,[X+expr] index157AND [expr],A direct357CMP A,expr data165AND [X+expr],A index368CMP A,[expr] direct177XOR [expr],A direct377CMP A,[X+expr] index188XOR [X+expr],A index388MOV A,expr data194IOWX [X+expr] index396MOV A,[expr] direct1A5CPL 3A4MOV A,[X+expr] index1B6ASL 3B4MOV X,expr data1C4ASR 3C4MOV X,[expr] direct1D5RLC 3D4reserved 1E RRC 3E4XPAGE 1F4RET 3F8MOV A,X404DI 704MOV X,A414EI 724MOV PSP,A604RETI 738CALL addr50 - 5F10JMP addr80-8F5JC addr C0-CF 5 (or 4) CALL addr90-9F10JNC addr D0-DF 5 (or 4)JZ addr A0-AF 5 (or 4)JACC addr E0-EF7JNZ addr B0-BF 5 (or 4)INDEX addr F0-FF148.0 Memory Organization8.1Program Memory Organization[1]After reset Address14 -bit PC0x0000Program execution begins here after a reset.0x0002USB Bus Reset interrupt vector0x0004128-µs timer interrupt vector0x0006 1.024-ms timer interrupt vector0x0008USB endpoint 0 interrupt vector0x000A USB endpoint 1 interrupt vector0x000C USB endpoint 2 interrupt vector0x000E SPI interrupt vector0x0010Capture timer A interrupt Vector0x0012Capture timer B interrupt vector0x0014GPIO interrupt vector0x0016Wake-up interrupt vector0x0018Program Memory begins here0x1FDF8 KB PROM ends here (8K - 32 bytes). See Note below Figure 8-1. Program Memory Space with Interrupt Vector TableNote:1.The upper 32 bytes of the 8K PROM are reserved. Therefore, the user’s program must not overwrite this space.8.2Data Memory OrganizationThe CY7C637xx microcontrollers provide 256 bytes of data RAM. In normal usage, the SRAM is partitioned into four areas: program stack, data stack, user variables and USB endpoint FIFOs as shown below:After reset Address8-bit DSP8-bit PSP0x00Program Stack Growth(User’s firmware movesDSP)8-bit DSP User Selected Data Stack GrowthUser Variables0xE8USB FIFO for Address A endpoint 20xF0USB FIFO for Address A endpoint 10xF8USB FIFO for Address A endpoint 0Top of RAM Memory0xFFFigure 8-2. Data Memory Organization8.3I/O Register SummaryI/O registers are accessed via the I/O Read (IORD) and I/O Write (IOWR, IOWX) instructions. IORD reads the selected port into the accumulator. IOWR writes data from the accumulator to the selected port. Indexed I/O Write (IOWX) adds the contents of X to the address in the instruction to form the port address and writes data from the accumulator to the specified port. Note that specifying address 0 with IOWX (e.g., IOWX 0h) means the I/O port is selected solely by the contents of X.Note:All bits of all registers are cleared to all zeros on reset, except the Processor Status and Control Register (Figure20-1). All registers not listed are reserved, and should never be written by firmware. All bits marked as reserved should always be written as 0 and be treated as undefined by reads.Table 8-1. I/O Register SummaryRegister Name I/O Address Read/Write Function Fig. Port 0 Data0x00R/W GPIO Port 012-2 Port 1 Data0x01R/W GPIO Port 112-3 Port 2 Data0x02R Auxiliary input register for D+, D–, VREG, XTALIN 12-8 Port 0 Interrupt Enable0x04W Interrupt enable for pins in Port 021-4 Port 1 Interrupt Enable0x05W Interrupt enable for pins in Port 121-5 Port 0 Interrupt Polarity 0x06W Interrupt polarity for pins in Port 021-6 Port 1 Interrupt Polarity 0x07W Interrupt polarity for pins in Port 121-7 Port 0 Mode0 0x0A W Controls output configuration for Port 012-4 Port 0 Mode10x0B W12-5 Port 1 Mode00x0C W Controls output configuration for Port 112-6 Port 1 Mode10x0D W12-7 USB Device Address0x10R/W USB Device Address register14-1 EP0 Counter Register0x11R/W USB Endpoint 0 counter register14-4 EP0 Mode Register0x12R/W USB Endpoint 0 configuration register14-2 EP1 Counter Register0x13R/W USB Endpoint 1 counter register14-4 EP1 Mode Register0x14R/W USB Endpoint 1 configuration register14-3 EP2 Counter Register0x15R/W USB Endpoint 2 counter register14-4 EP2 Mode Register0x16R/W USB Endpoint 2 configuration register14-3 USB Status & Control0x1F R/W USB status and control register13-1 Global Interrupt Enable0x20R/W Global interrupt enable register21-1 Endpoint Interrupt Enable0x21R/W USB endpoint interrupt enables21-2 Timer (LSB)0x24R Lower 8 bits of free-running timer (1 MHz)18-1 Timer (MSB)0x25R Upper 4 bits of free-running timer18-2 WDR Clear0x26W Watchdog Reset clear-Capture Timer A Rising0x40R Rising edge Capture Timer A data register19-2 Capture Timer A Falling0x41R Falling edge Capture Timer A data register19-3 Capture Timer B Rising0x42R Rising edge Capture Timer B data register19-4 Capture Timer B Falling0x43R Falling edge Capture Timer B data register19-5 Capture TImer Configuration0x44R/W Capture Timer configuration register19-7 Capture Timer Status0x45R Capture Timer status register19-6 SPI Data0x60R/W SPI read and write data register17-2 SPI Control0x61R/W SPI status and control register17-3 Clock Configuration0xF8R/W Internal / External Clock configuration register9-2 Processor Status & Control0xFF R/W Processor status and control20-1。

cy7c68000中文翻译

CY7C68000TX2™ USB 2.0 UTMI 收发器Jude 译2009.111.0 EZ-USB TX2性能EZ-USB TX2 是一个符合usb2.0的收发器,把串行的解串成30M的16位或者60M的8位的并行接口。

EZ-USB TX2 提供一个高速的物理层接口,可以工作在usb2.0 允许的最大带宽。

这允许设计者把复杂的高速模拟的usb 部分放在数字ASIC的外面,以减少开发时间和关联两部分的风险。

它提供一个被usb2.0鉴定过的标准的接口,这个接口符合UTMI 1.05(dated 3/29/01)版本的协议。

图1-1 为功能模块,EZ-USB TX2的特性:●作为设备符合usb2.0 UTMI的标准●可作业在usb高速480MBIT/S, 和全速12MBIT/S●串到并,并到串转化●8位单向或者8位双向,或者16位双向外部数据接口●在接受包是检测同步场和EOP●在发送包的时候产生同步场和EOP●从usb 串行数据流恢复数据和时钟●位填充/不填充,为填充错误检测●分段运输寄存器,用来管理在位填充/不填充期间数据速率变化●16位30M ,8位60M的并行接口●全速和高速之间终止和发送信号的转换能力(Ability to switch between FS and HSterminations andsignaling翻译的不准,自己领会)●支持对usb 复位,挂起,回复的检测●支持usb2.0定义的高速的识别和检测●支持恢复信号的发射● 3.3v 工作●两种封装选择56脚QFN,56脚SSOP●所有必要的终止,包括DPLUS上的1.5k 的上拉,都在片内●支持usb2.0测试模式2.0 应用• DSL modems数字模拟语言模型• ATA interface ATA接口• Memory card readers存储卡读卡器• Legacy conversion devices遗产转化设备☺• Cameras照相机• Scanners扫描仪• Home PNA☹• Wireless LAN无线局域网• MP3 players mp3 播放器• Networking网络3.0 功能概述3.1 usb 发信号的速度TX2 工作在两种速率:全速:位时间为12Mbps高速:位时间为480Mbps不支持低速速率1.5Mbps3.2 收发器时钟频率TX2 有一个片上的可用24M晶振的振荡器电路,有以下特性:并行振荡基波模型500uw驱动级27-33pf负载电容片上的pll 把24M的时钟倍频为30M或者60M,作为并行数据传输的时钟,DataBus16_8 引脚决定clk 的频率。

CY7C0831AV资料

Revised May 10, 2006

Logic Block Diagram[1]

OEL R/WL B0L B1L

CE0L CE1L

CY7C0837AV CY7C0830AV/CY7C0831AV CY7C0832AV/CY7C0833AV

OER R/WR

B0R B1R

CE0R CE1R

DQ9L–DQ17L

True Dual-Ported RAM Array

Address Decode

Address Decode

Interrupt Logic

MRST

Reset Logic

TMS TDI TCK

JTAG

Addr. Read Back

Mask Register

Counter/ Address Register Mirror Reg

1-Mbit (64K x 18)

CY7C0830AV

167

4.0

225

120 TQFP 144 FBGA

2-Mbit (128K x 18)

CY7C0831AV

167

4.0

225

120 TQFP 144 FBGA

4-Mbit (256K 18)

CY7C0832AV

167

4.0

225

120 TQFP 144 FBGA

CY7C093794V CY7C093894V CY7C09289V CY7C09369V CY7C09379V CY7C09389VFLEx18™ 3.3V 64K/128K x 36 and 128K/256K x 18 Synchronous Dual-Port RAM

CY7C0837AV CY7C0830AV/CY7C0831AV CY7C0832AV/CY7C0833AV

CY7C67300-100AI资料

CY7C67300 EZ-Host™ Programmable EmbeddedUSB Host/Peripheral ControllerTABLE OF CONTENTS1.0 INTRODUCTION (10)1.1 EZ-Host Features (10)2.0 TYPICAL APPLICATIONS (11)3.0 FUNCTIONAL OVERVIEW (11)3.1 Processor Core (11)3.1.1 Processor (11)3.1.2 Clocking (11)3.1.3 Memory (11)3.1.4 Interrupts (11)3.1.5 General Timers and Watchdog Timer (11)3.1.6 Power Management (11)4.0 INTERFACE DESCRIPTIONS (11)4.1 USB Interface (13)4.1.1 USB Features (13)4.1.2 USB Pins. (14)4.2 OTG Interface (14)4.2.1 OTG Features (14)4.2.2 OTG Pins. (14)4.3 External Memory Interface (14)4.3.1 External Memory Interface Features (14)4.3.2 External Memory Access Strobes (14)4.3.3 Page Registers (15)4.3.4 Merge Mode (15)4.3.5 Program Memory Hole Description (15)4.3.6 DMA to External Memory Prohibited (15)4.3.7 External Memory Interface Pins (16)4.3.8 External Memory Interface Block Diagrams (17)4.4 General Purpose I/O Interface (GPIO) (18)4.4.1 GPIO Description (18)4.4.2 Unused Pin Descriptions (18)4.5 UART Interface (18)4.5.1 UART Features (18)4.5.2 UART Pins. (18)4.6 I2C EEPROM Interface (18)4.6.1 I2C EEPROM Features (18)4.6.2 I2C EEPROM Pins. (18)4.7 Serial Peripheral Interface (18)4.7.1 SPI Features (19)4.7.2 SPI Pins (19)4.8 High-speed Serial Interface (19)4.8.1 HSS Features (19)4.8.2 HSS Pins (20)4.9 Programmable Pulse/PWM Interface (20)4.9.1 Programmable Pulse/PWM Features (20)4.9.2 Programmable Pulse/PWM Pins. (20)4.10 Host Port Interface (20)4.10.1 HPI Features (20)4.10.2 HPI Pins. (21)TABLE OF CONTENTS (continued)4.11 IDE Interface (21)4.11.1 IDE Features (22)4.11.2 IDE Pins (22)4.12 Charge Pump Interface (22)4.12.1 Charge Pump Features (23)4.12.2 Charge Pump Pins. (23)4.13 Booster Interface (23)4.13.1 Booster Pins. (24)4.14 Crystal Interface (25)4.14.1 Crystal Pins (25)4.15 Boot Configuration Interface (25)4.16 Operational Modes (26)4.16.1 Coprocessor Mode (26)4.16.2 Standalone Mode (26)5.0 POWER-SAVINGS AND RESET DESCRIPTION (27)5.1 Power-Savings Mode Description (27)5.2 Sleep (27)5.3 External (Remote) wakeup Source (27)5.4 Power-On-Reset Description (27)5.5 Reset Pin (27)5.6 USB Reset (27)6.0 MEMORY MAP (28)6.1 Mapping (28)6.1.1 Internal Memory (28)6.1.2 External Memory (28)7.0 REGISTERS (30)7.1 Processor Control Registers (30)7.1.1 CPU Flags Register [0xC000] [R] (30)7.1.2 Bank Register [0xC002] [R/W] (31)7.1.3 Hardware Revision Register [0xC004] [R] (31)7.1.4 CPU Speed Register [0xC008] [R/W] (32)7.1.5 Power Control Register [0xC00A] [R/W] (33)7.1.6 Interrupt Enable Register [0xC00E] [R/W] (35)7.1.7 Breakpoint Register [0xC014] [R/W] (36)7.1.8 USB Diagnostic Register [0xC03C] [R/W] (37)7.1.9 Memory Diagnostic Register [0xC03E] [W] (38)7.2 External Memory Registers (39)7.2.1 Extended Page n Map Register [R/W] (39)7.2.2 Upper Address Enable Register [0xC038] [R/W] (39)7.2.3 External Memory Control Register [0xC03A] [R/W] (40)7.3 Timer Registers (41)7.3.1 Watchdog Timer Register [0xC00C] [R/W] (41)7.3.2 Timer n Register [R/W] (42)7.4 General USB Registers (42)7.4.1 USB n Control Register [R/W] (42)7.5 USB Host Only Registers (45)7.5.1 Host n Control Register [R/W] (45)7.5.2 Host n Address Register [R/W] (46)TABLE OF CONTENTS (continued)7.5.3 Host n Count Register [R/W] (46)7.5.4 Host n Endpoint Status Register [R] (47)7.5.5 Host n PID Register [W] (48)7.5.6 Host n Count Result Register [R] (49)7.5.7 Host n Device Address Register [W] (50)7.5.8 Host n Interrupt Enable Register [R/W] (50)7.5.9 Host n Status Register [R/W] (52)7.5.10 Host n SOF/EOP Count Register [R/W] (53)7.5.11 Host n SOF/EOP Counter Register [R] (53)7.5.12 Host n Frame Register [R] (54)7.6 USB Device Only Registers (54)7.6.1 Device n Endpoint n Control Register [R/W] (55)7.6.2 Device n Endpoint n Address Register [R/W] (56)7.6.3 Device n Endpoint n Count Register [R/W] (57)7.6.4 Device n Endpoint n Status Register [R/W] (57)7.6.5 Device n Endpoint n Count Result Register [R/W] (59)7.6.6 Device n Port Select Register [R/W] (60)7.6.7 Device n Interrupt Enable Register [R/W] (60)7.6.8 Device n Address Register [W] (63)7.6.9 Device n Status Register [R/W] (63)7.6.10 Device n Frame Number Register [R] (65)7.6.11 Device n SOF/EOP Count Register [W] (66)7.7 OTG Control Registers (66)7.7.1 OTG Control Register [0xC098] [R/W] (66)7.8 GPIO Registers (68)7.8.1 GPIO Control Register [0xC006] [R/W] (68)7.8.2 GPIO n Output Data Register [R/W] (70)7.8.3 GPIO n Input Data Register [R] (70)7.8.4 GPIO n Direction Register [R/W] (71)7.9 IDE Registers (71)7.9.1 IDE Mode Register [0xC048] [R/W] (71)7.9.2 IDE Start Address Register [0xC04A] [R/W] (72)7.9.3 IDE Stop Address Register [0xC04C] [R/W] (72)7.9.4 IDE Control Register [0xC04E] [R/W] (73)7.9.5 IDE PIO Port Registers [0xC050 - 0xC06F] [R/W] (74)7.10 HSS Registers (74)7.10.1 HSS Control Register [0xC070] [R/W] (75)7.10.2 HSS Baud Rate Register [0xC072] [R/W] (77)7.10.3 HSS Transmit Gap Register [0xC074] [R/W] (77)7.10.4 HSS Data Register [0xC076] [R/W] (78)7.10.5 HSS Receive Address Register [0xC078] [R/W] (78)7.10.6 HSS Receive Counter Register [0xC07A] [R/W] (79)7.10.7 HSS Transmit Address Register [0xC07C] [R/W] (79)7.10.8 HSS Transmit Counter Register [0xC07E] [R/W] (79)7.11 HPI Registers (80)7.11.1 HPI Breakpoint Register [0x0140] [R] (80)7.11.2 Interrupt Routing Register [0x0142] [R] (81)7.11.3 SIEXmsg Register [W] (82)7.11.4 HPI Mailbox Register [0xC0C6] [R/W] (83)7.11.5 HPI Status Port [] [HPI: R] (83)TABLE OF CONTENTS (continued)7.12 SPI Registers (85)7.12.1 SPI Configuration Register [0xC0C8] [R/W] (86)7.12.2 SPI Control Register [0xC0CA] [R/W] (87)7.12.3 SPI Interrupt Enable Register [0xC0CC] [R/W] (89)7.12.4 SPI Status Register [0xC0CE] [R] (89)7.12.5 SPI Interrupt Clear Register [0xC0D0] [W] (90)7.12.6 SPI CRC Control Register [0xC0D2] [R/W] (91)7.12.7 SPI CRC Value Register [0xC0D4] [R/W] (92)7.12.8 SPI Data Register [0xC0D6] [R/W] (92)7.12.9 SPI Transmit Address Register [0xC0D8] [R/W] (93)7.12.10 SPI Transmit Count Register [0xC0DA] [R/W] (93)7.12.11 SPI Receive Address Register [0xC0DC [R/W] (93)7.12.12 SPI Receive Count Register [0xC0DE] [R/W] (94)7.13 UART Registers (94)7.13.1 UART Control Register [0xC0E0] [R/W] (94)7.13.2 UART Status Register [0xC0E2] [R] (95)7.13.3 UART Data Register [0xC0E4] [R/W] (96)7.14 PWM Registers (96)7.14.1 PWM Control Register [0xC0E6] [R/W] (97)7.14.2 PWM Maximum Count Register [0xC0E8] [R/W] (98)7.14.3 PWM n Start Register [R/W] (99)7.14.4 PWM n Stop Register [R/W] (99)7.14.5 PWM Cycle Count Register [0xC0FA] [R/W] (100)8.0 PIN DIAGRAM (101)9.0 PIN DESCRIPTIONS (101)10.0 ABSOLUTE MAXIMUM RATINGS (105)11.0 OPERATING CONDITIONS (105)12.0 CRYSTAL REQUIREMENTS (XTALIN, XTALOUT) (105)13.0 DC CHARACTERISTICS (105)13.1 USB Transceiver (106)14.0 AC TIMING CHARACTERISTICS (107)14.1 Reset Timing (107)14.2 Clock Timing (107)14.3 SRAM Read Cycle (108)14.4 SRAM Write Cycle (109)14.5 I2C EEPROM Timing (110)14.6 HPI (Host Port Interface) Write Cycle Timing (111)14.7 HPI (Host Port Interface) Read Cycle Timing (112)14.8 IDE Timing (113)14.9 HSS BYTE Mode Transmit (113)14.10 HSS Block Mode Transmit (113)14.11 HSS BYTE and BLOCK Mode Receive (113)14.12 Hardware CTS/RTS Handshake (114)15.0 REGISTERS SUMMARY (114)16.0 ORDERING INFORMATION (118)17.0 PACKAGE DIAGRAMS (118)LIST OF FIGURESFigure 1-1. Block Diagram (10)Figure 4-1. Page n Registers External Address Pins Logic (15)Figure 4-2. Interfacing to 64k × 8 Memory Array (17)Figure 4-3. Interfacing up to 256k × 16 for External Code/Data (17)Figure 4-4. Interfacing up to 512k × 8 for External Code/Data (17)Figure 4-5. Charge Pump (23)Figure 4-6. Power Supply Connection With Booster (24)Figure 4-7. Power Supply Connection Without Booster (24)Figure 4-8. Crystal Interface (25)Figure 4-9. Minimum Standalone Hardware Configuration – Peripheral Only (26)Figure 6-1. Memory Map (29)Figure 7-1. Processor Control Registers (30)Figure 7-2. CPU Flags Register (30)Figure 7-3. Bank Register (31)Figure 7-4. Revision Register (31)Figure 7-5. CPU Speed Register (32)Figure 7-6. Power Control Register (33)Figure 7-7. Interrupt Enable Register (35)Figure 7-8. Breakpoint Register (36)Figure 7-9. USB Diagnostic Register (37)Figure 7-10. Memory Diagnostic Register (38)Figure 7-11. External Memory Control Registers (39)Figure 7-12. Extended Page n Map Register (39)Figure 7-13. External Memory Control Register (39)Figure 7-14. External Memory Control Register (40)Figure 7-15. Timer Registers (41)Figure 7-16. Watchdog Timer Register (41)Figure 7-17. Timer n Register (42)Figure 7-18. General USB Registers (42)Figure 7-19. USB n Control Register (43)Figure 7-20. USB Host Only Register (45)Figure 7-21. Host n Control Register (45)Figure 7-22. Host n Address Register (46)Figure 7-23. Host n Count Register (46)Figure 7-24. Host n Endpoint Status Register (47)Figure 7-25. Host n PID Register (49)Figure 7-26. Host n Count Result Register (49)Figure 7-27. Host n Device Address Register (50)Figure 7-28. Host n Interrupt Enable Register (50)Figure 7-29. Host n Status Register (52)Figure 7-30. Host n SOF/EOP Count Register (53)Figure 7-31. Host n SOF/EOP Counter Register (54)Figure 7-32. Host n Frame Register (54)Figure 7-33. USB Device Only Registers (55)Figure 7-34. Device n Endpoint n Control Register (55)Figure 7-35. Device n Endpoint n Address Register (57)Figure 7-36. Device n Endpoint n Count Register (57)Figure 7-37. Device n Endpoint n Status Register (58)Figure 7-38. Device n Endpoint n Count Result Register (60)LIST OF FIGURES (continued)Figure 7-39. Device n Port Select Register (60)Figure 7-40. Device n Interrupt Enable Register (61)Figure 7-41. Device n Address Register (63)Figure 7-42. Device n Status Register (63)Figure 7-43. Device n Frame Number Register (65)Figure 7-44. Device n SOF/EOP Count Register (66)Figure 7-45. OTG Registers (66)Figure 7-46. OTG Control Register (66)Figure 7-47. GPIO Registers (68)Figure 7-48. GPIO Control Register (68)Figure 7-49. GPIO n Output Data Register (70)Figure 7-50. GPIO n Input Data Register (70)Figure 7-51. GPIO n Direction Register (71)Figure 7-52. IDE Registers (71)Figure 7-53. IDE Mode Register (71)Figure 7-54. IDE Start Address Register (72)Figure 7-55. IDE Stop Address Register (72)Figure 7-56. IDE Control Register (73)Figure 7-57. HSS Registers (74)Figure 7-58. HSS Control Register (75)Figure 7-59. HSS Baud Rate Register (77)Figure 7-60. HSS Transmit Gap Register (77)Figure 7-61. HSS Data Register (78)Figure 7-62. HSS Receive Address Register (78)Figure 7-63. HSS Receive Counter Register (79)Figure 7-64. HSS Transmit Address Register (79)Figure 7-65. HSS Transmit Counter Register (79)Figure 7-66. HPI Registers (80)Figure 7-67. HPI Breakpoint Register (80)Figure 7-68. Interrupt Routing Register (81)Figure 7-69. SIEXmsg Register (82)Figure 7-70. HPI Mailbox Register (83)Figure 7-71. HPI Status Port (83)Figure 7-72. SPI Registers (85)Figure 7-73. SPI Configuration Register (86)Figure 7-74. SPI Control Register (87)Figure 7-75. SPI Interrupt Enable Register (89)Figure 7-76. SPI Status Register (89)Figure 7-77. SPI Interrupt Clear Register (90)Figure 7-78. SPI CRC Control Register (91)Figure 7-79. SPI CRC Value Register (92)Figure 7-80. SPI Data Register (92)Figure 7-81. SPI Transmit Address Register (93)Figure 7-82. SPI Transmit Count Register (93)Figure 7-83. SPI Receive Address Register (93)Figure 7-84. SPI Receive Count Register (94)Figure 7-85. UART Registers (94)Figure 7-86. UART Control Register (94)Figure 7-87. UART Status Register (95)LIST OF FIGURES (continued)Figure 7-88. UART Data Register (96)Figure 7-89. PWM Registers (96)Figure 7-90. PWM Control Register (97)Figure 7-91. PWM Maximum Count Register (98)Figure 7-92. PWM n Start Register (99)Figure 7-93. PWM n Stop Register (99)Figure 7-94. PWM Cycle Count Register (100)Figure 8-1. EZ-Host Pin Diagram (101)LIST OF TABLESTable 4-1. Interface Options for GPIO Pins (12)Table 4-2. Interface Options for External Memory Bus Pins (12)Table 4-3. USB Port Configuration Options (13)Table 4-4. USB Interface Pins (14)Table 4-5. OTG Interface Pins (14)Table 4-6. External Memory Interface Pins (16)Table 4-7. UART Interface Pins (18)Table 4-8. I2C EEPROM Interface Pins (18)Table 4-9. SPI Interface Pins (19)Table 4-10. HSS Interface Pins (20)Table 4-11. PWM Interface Pins (20)Table 4-12. HPI Interface Pins (21)Table 4-13. HPI Addressing (21)Table 4-14. IDE Throughput (22)Table 4-15. IDE Interface Pins (22)Table 4-16. Charge Pump Interface Pins (23)Table 4-17. Charge Pump Interface Pins (24)Table 4-18. Crystal Pins (25)Table 4-19. Boot Configuration Interface (25)Table 5-1. Wakeup Sources (27)Table 7-1. Bank Register Example (31)Table 7-2. CPU Speed Definition (32)Table 7-3. Force Select Definition (38)Table 7-4. Memory Arbitration Select (38)Table 7-5. Period Select Definition (41)Table 7-6. USB Data Line Pull-up and Pull-down Resistors (44)Table 7-7. Port A/B Force D± State (44)Table 7-8. Port Select Definition (47)Table 7-9. PID Select Definition (49)Table 7-10. Mode Select Definition (69)Table 7-11. Mode Select Definition (72)Table 7-12. IDE PIO Port Registers (74)Table 7-13. Scale Select Field Definition for SCK Frequency (86)Table 7-14. CRC Mode Definition (91)Table 7-15. UART Baud Select Definition (95)Table 7-16. Prescaler Select Definition (97)Table 9-1. Pin Descriptions (101)Table 12-1. Crystal Requirements (105)Table 13-1. DC Characteristics (105)Table 13-2. DC Characteristics: Charge Pump (106)Table 15-1. Register Summary (114)Table 16-1. Ordering Information (118)1.0 INTRODUCTIONEZ-Host™ (CY7C67300) is Cypress Semiconductor’s first full-speed, low-cost multiport host/peripheral controller. EZ-Host is designed to easily interface to most high-performance CPUs to add USB host functionality. EZ-Host has its own 16-bit RISC processor to act as a coprocessor or operate in standalone mode. EZ-Host also has a programmable I/O interface block allowing a wide range of interface options.Figure 1-1. Block Diagram1.1EZ-Host Features•Single-chip programmable USB dual-role (Host/Peripheral) controller with two configurable Serial Interface Engines (SIEs) and four USB ports•Support for USB On-The-Go (OTG) protocol•On-chip 48-MHz 16-bit processor with dynamically switchable clock speed•Configurable I/O block supporting a variety of I/O options or up to 32 bits of General Purpose I/O (GPIO)•4K x 16 internal masked ROM containing built-in BIOS that supports a communication ready state with access to I2C EEPROM Interface, external ROM, UART, or USB•8K x 16 internal RAM for code and data buffering•Extended memory interface port for external SRAM and ROM•16-bit parallel Host Port Interface (HPI) with a DMA/Mailbox data path for an external processor to directly access all of the on-chip memory and control on-chip SIEs•Fast serial port supports from 9600 baud to 2.0 Mbaud•SPI support in both master and slave•On-chip 16-bit DMA/Mailbox data path interface•Supports 12-MHz external crystal or clock•3.3V operation•Package option — 100-pin TQFP2.0 Typical ApplicationsEZ-Host is a very powerful and flexible dual role USB controller that supports a wide variety of applications. It is primarily intended to enable host capability in applications such as:•Set-top boxes•Printers•KVM switches•Kiosks•Automotive applications•Wireless access points.3.0 Functional Overview3.1Processor Core3.1.1ProcessorEZ-Host has a general-purpose 16-bit embedded RISC processor that runs at 48 MHz.3.1.2ClockingEZ-Host requires a 12-MHz source for clocking. Either an external crystal or TTL level oscillator may be used. EZ-Host has an internal PLL that produces a 48-MHz internal clock from the 12-MHz source.3.1.3MemoryEZ-Host has a built-in 4K × 16 masked ROM and an 8K × 16 internal RAM. The masked ROM contains the EZ-Host BIOS. The internal RAM can be used for program code or data.3.1.4InterruptsEZ-Host provides 128 interrupt vectors. The first 48 vectors are hardware interrupts and the following 80 vectors are software interrupts.3.1.5General Timers and Watchdog TimerEZ-Host has two built-in programmable timers and a Watchdog timer. All three timers can generate an interrupt to the EZ-Host.3.1.6Power ManagementEZ-Host has one main power saving mode, Sleep. Sleep mode pauses all operations and provides the lowest power state.4.0 Interface DescriptionsEZ-Host has a wide variety of interface options for connectivity. With several interface options available, EZ-Host can act as a seamless data transport between many different types of devices.See Table4-1 and Table4-2 to understand how the interfaces share pins and which can coexist. It should be noted that some interfaces have more then one possible port location selectable through the GPIO Control Register [0xC006]. Below are some general guidelines:•HPI and IDE interfaces are mutually exclusive.•If 16-bit external memory is required, then HSS and SPI default locations must be used.•I2C EEPROM and OTG do not conflict with any interfaces.Notes:1.Default interface location.2.Alternate interface location.Table 4-1. Interface Options for GPIO Pins GPIO Pins HPIIDEPWMHSSSPIUARTI2C OTGGPIO31SCL/SDA GPIO30SCL/SDAGPIO29OTGIDGPIO28TX [1]GPIO27RX [1]GPIO26PWM3CTS [1]GPIO25GPIO24INT IOREADY GPIO23nRD IOR GPIO22nWR IOW GPIO21nCS GPIO20A1CS1GPIO19A0CS0GPIO18A2PWM2RTS [1]GPIO17A1PWM1RXD [1]GPIO16A0PWM0TXD [1]GPIO15D15D15GPIO14D14D14GPIO13D13D13GPIO12D12D12GPIO11D11D11MOSI [1]GPIO10D10D10SCK [1]GPIO9D9D9nSSI [1]GPIO8D8D8MISO [1]GPIO7D7D7TX [2]GPIO6D6D6RX [2]GPIO5D5D5GPIO4D4D4GPIO3D3D3GPIO2D2D2GPIO1D1D1GPIO0D0D0Table 4-2. Interface Options for External Memory Bus Pins MEM Pins HPIIDEPWMHSS SPIUARTI2COTGD15CTS [2]D14RTS [2]D13RXD [2]D12TXD [2]D11MOSI [2]D10SCK [2]D9nSSI [2]D8MISO [2]D[7:0]A[18:0]CONTROL4.1USB InterfaceEZ-Host has two built-in Host/Peripheral SIEs and four USB transceivers that meet the USB 2.0 specification requirements for full and low speed (high speed is not supported). In Host mode, EZ-Host supports four downstream ports, each support control, interrupt, bulk, and isochronous transfers. In Peripheral mode, EZ-Host supports one peripheral port with eight endpoints for each of the two SIEs. Endpoint 0 is dedicated as the control endpoint and only supports control transfers. Endpoints 1 though 7 support Interrupt, Bulk (up to 64 Bytes/packet), or Isochronous transfers (up to 1023 Bytes/packet size). EZ-Host also supports a combi-nation of Host and Peripheral ports simultaneously as shown in Table4-3.Table 4-3. USB Port Configuration OptionsPort Configurations Port 1A Port 1B Port 2A Port 2BOTG OTG–––OTG + 2 Hosts OTG–Host HostOTG + 1 Host OTG–Host–OTG + 1 Host OTG––HostOTG + 1 Peripheral OTG–Peripheral–OTG + 1 Peripheral OTG––Peripheral4 Hosts Host Host Host Host3 Hosts Any Combination of Ports2 Hosts Any Combination of Ports1 Host Any Port2 Hosts + 1 Peripheral Host Host Peripheral–2 Hosts + 1 Peripheral Host Host–Peripheral2 Hosts + 1 Peripheral Peripheral–Host Host2 Hosts + 1 Peripheral–Peripheral Host Host1 Host + 1 Peripheral Host–Peripheral–1 Host + 1 Peripheral Host––Peripheral1 Host + 1 Peripheral–Host–Peripheral1 Host + 1 Peripheral–Host Peripheral–1 Host + 1 Peripheral Peripheral–Host–1 Host + 1 Peripheral Peripheral––Host1 Host + 1 Peripheral–Peripheral–Host1 Host + 1 Peripheral–Peripheral Host–2 Peripherals Peripheral–Peripheral–2 Peripherals Peripheral––Peripheral2 Peripherals–Peripheral–Peripheral2 Peripherals–Peripheral Peripheral–1 Peripheral Any Port4.1.1USB Features•USB 2.0-compliant for full and low speed•Up to four downstream USB host ports•Up to two upstream USB peripheral ports•Configurable endpoint buffers (pointer and length), must reside in internal RAM•Up to eight available peripheral endpoints (one control endpoint)•Supports Control, Interrupt, Bulk, and Isochronous transfers•Internal DMA channels for each endpoint•Internal pull-up and pull-down resistors•Internal Series termination resistors on USB data lines4.1.2USB Pins.Table 4-4. USB Interface PinsPin Name Pin NumberDM1A22DP1A23DM1B18DP1B19DM2A9DP2A10DM2B4DP2B54.2OTG InterfaceEZ-Host has one USB port that is compatible with the USB On-The-Go supplement to the USB 2.0 specification. The USB OTG port has a various hardware features to support Session Request Protocol (SRP) and Host Negotiation Protocol (HNP). OTG is only supported on USB PORT 1A.4.2.1OTG Features•Internal Charge Pump to supply and control VBUS•VBUS Valid Status (above 4.4V)•VBUS Status for 2.4V< VBUS <0.8V•ID Pin Status•Switchable 2KΩ internal discharge resistor on VBUS•Switchable 500Ω internal Pull-up resistor on VBUS•Individually switchable internal Pull-up and Pull-down resistors on the USB Data Lines4.2.2OTG Pins.Table 4-5. OTG Interface PinsPin Name Pin NumberDM1A22DP1A23OTGVBUS11OTGID41CSwitchA13CSwitchB124.3External Memory InterfaceEZ-Host provides a robust interface to a wide variety of external memory arrays. All available external memory array locations can contain either code or data. The CY16 RISC processor directly addresses a flat memory space from 0x0000 to 0xFFFF. 4.3.1External Memory Interface Features•Supports 8-bit or 16-bit SRAM or ROM•SRAM or ROM can be used for code or data space•Direct addressing of SRAM or ROM•Two external memory mapped page registers4.3.2External Memory Access StrobesAccess to external memory is sampled asynchronously on the rising edge of strobes with a minimum of one wait state cycle. Up to seven wait state cycles may be inserted for external memory access. Each additional wait state cycle stretches the external memory access time by 21 nsec. An external memory device with 12-nsec access time is necessary to support 48-MHz code execution.4.3.3Page RegistersEZ-Host allows extended data or program code to be stored in external SRAM, or ROM. The total size of extended memory can be up to 512K bytes. The CY16 processor can access extended memory via two address regions of 0x8000-0x9FFF and 0xA000-0xBFFF. The page register 0xC018 can be used to control the address region 0x8000-0x9FFF and the page register 0xC01A controls the address region of 0xA000-0xBFFF.Figure4-1 illustrates that when the nXMEMSEL pin is asserted the upper CPU address pins are driven by the contents of the Page x Registers.Figure 4-1. Page n Registers External Address Pins Logic4.3.4Merge ModeMerge modes enabled through the External Memory Control Register [0xC03] allow combining of external memory regions in accordance with the following:•nXMEMSEL is active from 0x8000 to 0xBFFF•nXRAMSEL is active from 0x4000 to 0x7FFF when RAM Merge is disabled; nXRAMSEL is active from 0x4000 to 0xBFFF when RAM Merge is enabled•nXROMSEL is active from 0xC100 to 0xDFFF when ROM Merge is disabled; nXROMSEL is active from 0x8000 to 0xDFFF (excluding the 0xC000 to 0xC0FF area) when ROM Merge is enabled4.3.5Program Memory Hole DescriptionCode residing in the 0xC000-0xC0FF address space is not accessible by the cpu.4.3.6DMA to External Memory ProhibitedEZ-Host supports an internal DMA engine to rapidly move data between different functional blocks within the chip. This DMA engine is used for SIE1, SIE2, HPI, SPI, HSS, and IDE but it can only transfer data between the specified block and internal RAM or ROM. Setting up the DMA engine to transfer to or from an external memory space might result in internal RAM data corruption because the hardware (i.e HSS/HPI/SIE1/SIE2/IDE) does not explicitly check the address range. For example, setting up a DMA transfer to external address 0x8000 might result in a DMA transfer into address 0x0000.External Memory Related Resource Considerations:•By default A[18:15] are not available for general addressing and are driven high on power up. The Upper Address Enable Register must be written appropriately to enable A[18:15] for general addressing purposes.•47k ohm external pull-up on A15-pin for 12-MHz crystal operation.•During the 3-msec BIOS boot procedure the CPU external memory bus is active.•ROM boot load value 0xC3B6 located at 0xC100.•HPI, HSS, SPI, SIE1, SIE2, and IDE can't DMA to external memory arrays.•Page 1 banking is always enabled and is in effect from 0x8000 to 0x9FFF.•Page 2 banking is always enabled and is in effect from 0xA000 to 0xBFFF.•CPU memory bus strobes may wiggle when chip selects are inactive.4.3.7External Memory Interface PinsTable 4-6. External Memory Interface PinsPin Name Pin Number nWR64nRD62 nXMEMSEL (optional nCS)34nXROMSEL (ROM nCS)35nXRAMSEL (RAM nCS)36A1896A1795A1697A1538A1433A1332A1231A1130A1027A925A824A720A617A58A47A33A22A11nBEL/A099nBEH98D1567D1468D1369D1270D1171D1072D973D874D776D677D578D479D380D281D182D0834.3.8External Memory Interface Block DiagramsFigure4-2 illustrates how to connect a 64k × 8 memory array (SRAM/ROM) to the EZ-Host external memory interface.Figure 4-2. Interfacing to 64k × 8 Memory ArrayFigure4-3 illustrates the interface for connecting a 16-bit ROM or 16-bit RAM to the EZ-Host external memory interface. In 16-bit mode, up to 256K words of external ROM or RAM are supported. Note that the Address lines do not map directly.Figure 4-3. Interfacing up to 256k × 16 for External Code/DataFigure4-4 illustrates the interface for connecting an 8-bit ROM or 8-bit RAM to the EZ-Host external memory interface. In 8-bit mode, up to 512K bytes of external ROM or RAM are supported.Figure 4-4. Interfacing up to 512k × 8 for External Code/Data4.4General Purpose I/O Interface (GPIO)EZ-Host has up to 32 GPIO signals available. Several other optional interfaces use GPIO pins as well and may reduce the overall number of available GPIOs.4.4.1GPIO DescriptionAll Inputs are sampled asynchronously with state changes occurring at a rate of up to two 48-MHZ clock cycles. GPIO pins are latched directly into registers, a single flip-flop.4.4.2Unused Pin DescriptionsUnused USB pins should be three-stated with the D+ line pulled high through the internal pull-up resistor and the D- line pulled low through the internal pull-down resistor.Unused GPIO pins should be configured as outputs and driven low.4.5UART InterfaceEZ-Host has a built-in UART interface. The UART interface supports data rates from 900 to 115.2K baud. It can be used as a development port or for other interface requirements. The UART interface is exposed through GPIO pins.4.5.1UART Features•Supports baud rates of 900 to 115.2K•8-N-14.5.2UART Pins.Table 4-7. UART Interface PinsPin Name Pin NumberTX42RX434.6I2C EEPROM InterfaceEZ-Host provides a master only I2C interface for external serial EEPROMs. The serial EEPROM can be used to store application specific code and data. This I2C interface is only to be used for loading code out of EEPROM, it is not a general I2C interface. The I2C EEPROM interface is a BIOS implementation and is exposed through GPIO pins. Please refer to the BIOS documentation for additional details on this interface.4.6.1I2C EEPROM Features•Supports EEPROMs up to 64KB (512K bit)•Auto-detection of EEPROM size4.6.2I2C EEPROM Pins.Table 4-8. I2C EEPROM Interface PinsPin Name Pin NumberSMALL EEPROMSCK39SDA40LARGE EEPROMSCK40SDA394.7Serial Peripheral InterfaceEZ-Host provides a SPI interface for added connectivity. EZ-Host may be configured as either an SPI master or SPI slave. The SPI interface can be exposed through GPIO pins or the External Memory port.。

CY7C1061AV33-10ZXI中文资料

Logic Block Diagram

Functional Description

The CY7C1061AV33 is a high performance CMOS Static RAM organized as 1,048,576 words by 16 bits.

Commercial/Industrial

50

Pin Configurations [1, 2]

60-ball FBGA Top View

1

2

3

4

5

NC NC

NC

6

NC NC NC

BLE OE A0 A1 A2 CE2

A

IO 8 BHE A3 A4 CE1 IO 0

B

IO 9 IO 10 A5

A6 IO 1 IO 2

To write to the device, enable the chip (CE1 LOW and CE2 HIGH) while forcing the Write Enable (WE) input LOW. If Byte Low Enable (BLE) is LOW, then data from IO pins (IO0 through IO7), is written into the location specified on the address pins (A0 through A19). If Byte High Enable (BHE) is LOW, then data from IO pins (IO8 through IO15) is written into the location specified on the address pins (A0 through A19).

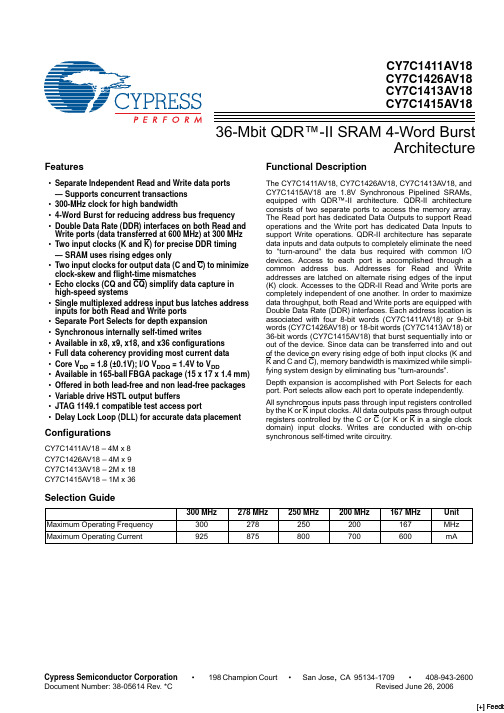

CY7C1417AV18资料