LOC112中文资料

ABB传感器PFEA111-112中英文手册

hapter 1 - Introduction第一章绪论1.1About this manual1.1 关于此手册This User Manual describes your new Measure Web Tension System. When you have read the manual, you will have the necessary knowledge for mechanical and electrical installation, commissioning, operation, preventive maintenance and basic fault tracing of your measurement system.。

该手册介绍新型幅面材料的张力测量系统,阅读该手册须具备对测量系统的认知,包括机械和电气安装、调试、操作、定期检修和基本故障查寻。

注:对于不同产业来说,幅面材料所指不同。

幅面在钢铁工业中是指带钢;纺织工业是指布匹;造纸工业是指纸张;塑料工业是指塑料薄膜……To get the best reliability and precision out of your measurement system, study this User Manual first.阅读用户手册可使你的测量系统获得最佳的可靠性和精密度。

1.2How to use this manual1.2 怎么使用手册This user manual comprises two main parts.此用户手册有两个主要部分。

rmation about the Tension Electronics:1. 张力传感器的信息。

-System and safety information (chapter 1)-系统和安全信息(第一章)-Installation, commissioning, maintenance, operation and fault tracing (chapters 2-6)-安装,试车,维护,操作和故障查寻(2-6章)-Technical data (appendix A)-技术数据(附录A)rmation about Designing the Load Cell Installation:压头的安装-Vertical-force sensing load cell PFCL 301E (Appendix B)微型垂直力压头PFCL 301E (附录 B)-Horizontal-force sensing load cell PFTL 301E (Appendix C)微型水平力压头PFTL 301E (附录 C)-Radial-force Tensiometer PFRL 101 (Appendix径向张力计PFRL 101(附录D)-Horizontal-force sensing load cell PFTL 101 (Appendix水平力压头PFTL 101 (附录 E)Each appendix contains detailed information about one of the above load cell types when used in web tension systems with Tension Electronics PFEA111/112.每个附录均包括上述幅面张力系统使用到的PFEA111/112测量装置的详细信息。

汽车零部件中英文缩略写对照表

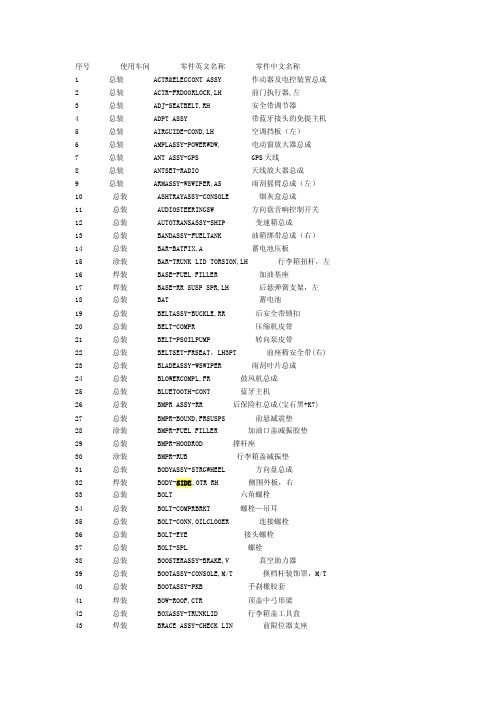

序号使用车间零件英文名称零件中文名称1 总装 ACTR&ELECCO NT ASSY 作动器及电控装置总成2 总装 ACTR-FRDOOR LOCK,LH 前门执行器,左3 总装 ADJ-SEATBE LT,RH 安全带调节器4 总装 ADPT ASSY 带蓝牙接头的免提主机5 总装 AIRGUI DE-COND,LH 空调挡板(左)6 总装 AMPLAS SY-POWERW DW, 电动窗放大器总成7 总装 ANT ASSY-GPS GPS天线8 总装 ANTSET-RADIO天线放大器总成9 总装 ARMASS Y-WSWIPE R,AS 雨刮摇臂总成(左)10 总装 ASHTRA YASSY-CONSOL E 烟灰盒总成11 总装 AUDIOS TEERI NGSW方向盘音响控制开关12 总装 AUTOTR ANSAS SY-SHIP 变速箱总成13 总装 BANDAS SY-FUELTA NK 油箱绑带总成(右)14 总装 BAR-BATFIX,A 蓄电池压板15 涂装 BAR-TRUNKLID TORSIO N,LH 行李箱扭杆,左16 焊装 BASE-FUEL FILLER加油基座17 焊装 BASE-RR SUSP SPR,LH 后悬弹簧支架,左18 总装 BAT 蓄电池19 总装 BELTAS SY-BUCKLE,RR 后安全带锁扣20 总装 BELT-COMPR压缩机皮带21 总装 BELT-PSOILP UMP 转向泵皮带22 总装 BELTSE T-FRSEAT,LH3PT前座椅安全带(右)23 总装 BLADEA SSY-WSWIPE R 雨刮叶片总成24 总装 BLOWER COMPL,FR 鼓风机总成25 总装 BLUETO OTH-CONT 蓝牙主机26 总装 BMPR ASSY-RR 后保险杠总成(宝石黑+K7)27 总装 BMPR-BOUND,FRSUSP S 前悬减震垫28 涂装 BMPR-FUEL FILLER加油口盖减振胶垫29 总装 BMPR-HOODRO D 撑杆座30 涂装 BMPR-RUB 行李箱盖减振垫31 总装 BODYAS SY-STRGWH EEL 方向盘总成32 焊装 BODY-SIDE,OTR RH 侧围外板,右33 总装 BOLT 六角螺栓34 总装 BOLT-COMPRB RKT 螺栓—吊耳35 总装 BOLT-CONN,OILCLO OER 连接螺栓36 总装 BOLT-EYE 接头螺栓37 总装 BOLT-SPL 螺栓38 总装 BOOSTE RASSY-BRAKE,V 真空助力器39 总装 BOOTAS SY-CONSOL E,M/T 换档杆装饰罩,M/T40 总装 BOOTAS SY-PKB 手刹橡胶套41 焊装 BOW-ROOF,CTR 顶盖中弓形梁42 总装 BOXASS Y-TRUNKL ID 行李箱盖工具盒43 焊装 BRACEASSY-CHECKLIN 前限位器支座44 焊装 BRACEASSY-FR PLR LW 前柱下铰链支座总成45 焊装 BRACE-COWL TOP,SIDE顶罩侧板,右46 总装 BRGASS Y-WHEEL轴承总成47 总装BRKT支架48 焊装BRKT ASSY-BLOWER风机支架49 焊装BRKT ASSY-CLUTCH PED 离合器踏板支架总成50 焊装BRKT ASSY-EXH MTG 排气管支架51 总装BRKT ASSY-FR BMPR,LH 前保险杠支架,左52 焊装BRKT ASSY-FR SEAT MT 前座椅安装支架,左53 焊装BRKT ASSY-HEATER,A 加热器支架总成,A54 焊装BRKT ASSY-JACK MTG 千斤顶支架总成55 焊装BRKT ASSY-MFLR MTG 消音器安装支架56 焊装BRKT ASSY-PKB CONT 焊接前地板手刹车支架57 焊装BRKT ASSY-RR TOWING后挂钩支架总成58 焊装BRKT ASSY-SPAREWHEE 备胎支架59 总装BRKT-ACCELW IRE 油门线支架60 总装BRKT-ADJBOL T 支架61 总装BRKT-ASSTGR IP 拉手支架62 总装 BRKTAS SY-BATMTG电瓶支架总成63 总装 BRKTAS SY-BRAKET UBE 制动阀支架总成64 总装 BRKTAS SY-CANIST ER 碳罐支架65 总装 BRKTAS SY-INSTST AY 仪表板支架66 总装 BRKTAS SY-LIQUID TAN 干燥瓶支架67 总装 BRKTAS SY-PSTANK动力转向油罐支架总成68 总装 BRKTAS SY-RADMTG散热器支架(右)69 总装 BRKTAS SY-SEATRA ILINR MTG,RH 座椅支架,右70 总装 BRKTAS SY-SENMTG传感器安装支架总成71 总装 BRKTAS SY-STABMT G,L 稳定杆夹箍72 总装 BRKTAS SY-SUNROO F 支架73 总装 BRKTAS SY-SUPTBR G 支架总成74 总装BRKT-BRAKEH OSE,RRR 制动管支架(右)75 总装BRKT-CABLEM TG 拉索支架76 总装BRKT-CABLEP KB,RR 驻车钢索支架77 总装BRKT-CLIP 支架—线夹78 总装BRKT-CLUTCH TUBE离合器管支架79 总装BRKT-COMPR压缩机支架80 焊装BRKT-CONN 四通支架81 总装BRKT-CONSOL E,FR 杂物盒支架,前82 总装BRKT-CONTUN IT 电脑板支架83 总装BRKT-ENG COVER发动机装饰盖支架84 焊装BRKT-ENG MTG 发动机安装支架85 总装BRKT-ENGMTG,RR 发动机后悬置托架86 总装BRKT-ENGMTG BLOCK,C 发动机安装支架87 总装BRKT-EXHMTG排气管安装支架,后88 焊装BRKT-FDR,LH 前翼子板支架,左89 焊装BRKT-FILLER TUBE PRO 加油管固定支座90 焊装BRKT-FOOT REST 搁脚板支架91 总装BRKT-FRSPEA KER,RH 前扬声器支架(右)92 总装BRKT-FUELPU MP,A 油泵支架93 总装BRKT-FUELTA NKMTG,F 燃油箱安装支架,前94 总装BRKT-FUSEBL OCK 保险丝盒支架95 总装BRKT-HORN 防盗喇叭支架96 总装BRKT-HOSE 管夹支架97 总装BRKT-INSTSI DE,RH 仪表板骨架支架,右98 焊装BRKT-JACK MTG 千斤顶支架99 总装BRKT-MAPLAM P 地图灯支架100 总装BRKT-PSTUBE动力转向管支架101 总装BRKT-PULLHA NDLE把手支架102 总装BRKT-RADIOLH 音响支架,左103 总装BRKT-RADRES VRTAN K 贮液罐支架总成104 总装BRKT-RESONA TOR 谐振器支架105 焊装BRKT-RR BMPR SIDE,A 后保险杠侧支架,A 106 焊装BRKT-RR BMPR STAY 后保险杠固定支架107 焊装BRKT-RR SEAT BACK 后排座椅靠背支架108 焊装BRKT-RR TIE DOWN HOOK RH 后挂钩支架,右109 总装BRKT-RRBMPR SIDE保险杠侧支架110 总装BRKT-RRBMPR SIDE后保险杠侧支架111 总装BRKT-RRSTAB MTG,RH 后稳定杆支架(右)112 总装BRKT-SEN,AMB 传感器支架113 焊装BRKT-STRG POST,OTR 方向柱支架,外114 焊装BRKT-TRUNKTRIM,A 行李箱装饰板支架,A115 总装 BUSH-FRSTAB前连接杆衬套116 总装 BUSH-LINK 橡胶套117 总装 BUSH-STAB 稳定杆衬套118 总装 BUZZER ASSY蜂鸣器119 总装 CABLE,BATTOE NG 电缆120 总装 CABLEA SSY-ACCEL油门拉索总成121 总装 CABLEA SSY-AUTOTR AN 自动变速箱拉索122 总装 CABLEA SSY-HOODLO CK 机仓盖拉索123 总装 CABLEA SSY-TRUNK&F 行李箱盖拉索总成124 总装 CALIPE RASSY-RRBRAK后制动钳总成,左125 总装 CAMERA ASSY-BACK VIEW 倒车摄像头总成126 总装 CANIST ERASS Y-VAPO,W 碳罐127 总装 CAPASS Y-DISCWH ELL 轮辋装饰罩128 总装 CAPASS Y-FILLER加油口盖总成129 总装 CAPCOM PL 散热器盖130 总装 CAP-HUB 轮骰盖131 总装 CAP-PULLHA NDLE拉手盖132 总装 CARPET ASSY-FLOOR地毯总成133 总装 CARPET ASSY-TRUNKF LOOR行李箱地毯总成134 总装 CD CHANGE R ASSY CD转换器总成135 总装 CHECKL INKAS SY-FRD 门限位器总成136 总装 CHMBRA SSY-FUELTA NK 燃油室总成137 总装 CIRCUI TBREA KER 断路保护器138 总装 CLAMPH OSE 管夹139 总装 CLAMP-RODHOO D 撑杆支座140 总装 CLAMP-RODHOO D 机仓撑杆总成141 总装 CLANKA SSY-BELLTR UNKLI D 行李舱锁曲柄连杆142 总装 CLIP 卡扣143 总装 CLNRAS SY-AIR 空气滤清器总成144 总装 CLOCKA SSY-ANALOG时钟总成145 焊装 CLOSIN G PLATE-FR SIDE MBR LH 前边梁盖板,左146 焊装 CLOSIN G PLATE-SILL,R 门槛连接板,右147 总装 CLPASS Y-SPARET IRE 备胎夹总成148 总装 CLP-CHECKV ALVE单向阀夹149 总装 CLP-COMPRR OD,LH 加强板(左)150 总装 COLASS Y-STRG 转向柱总成151 总装 COLLAR-INSUL套管152 总装 COLLAR-STRUTM T 定位管153 总装 COMPRC OMPL空调压缩机总成154 总装 CONDAS SY 冷凝器155 总装 CONN-DRAINH OSE,CANI 三通接头156 总装 CONSOL E ASSY RR 后杂物盒总成157 总装 CONT ASSY-CCD CCD后视主机158 总装 CONT ASSY-NAVI NAVI主机总成159 总装 CONTAS SY-AIRCON D,AUTO 空调控制器160 总装 CONTAS SY-BACKSO NAR 倒车雷达控制器161 总装 CONTAS SY-SHIFTL OCK 档位锁控制器162 总装 CONT-LTG 自动点灯控制器163 总装 CONTRO LLER-AV 遥控器--NAVI164 总装 CONT-TIME 延时控制器165 总装 CONTUN IT 控制单元-防盗166 总装 CONVAS SY-MAINCA T 催化转化器总成167 焊装 CORNER-RR FDR,LH 后翼子板角板,左168 总装 COVERASSY-INST LWR RH 下安装板罩,右169 总装 COVER-ACCELS TOPPE R 加速踏板限位器170 总装 COVER-AIRINT进气口盖171 总装 COVERA SSY-HOLE 转向柱护罩172 总装 COVERA SSY-TRANSH OL 变速器孔罩总成173 总装 COVER-BATTCO NN 电池罩174 总装 COVER-BELTAN CH 安全带螺扣175 总装 COVER-BLOWER MOTOR鼓风机罩176 总装 COVERC LUTCH-HOLE 离合器口罩177 总装 COVERC OMPL-STRGCO L 泡棉178 总装 COVERC OMPL-STRGCO L 组合开关罩总成179 总装 COVER-FRDOOR CORNE R 右前窗三角框180 总装 COVER-FRDOOR CORNE R,INRARH前门拐角罩(右)181 总装 COVER-FRDOOR CORNE R,INRBRH外后视罩饰板(右)182 总装 COVER-FRUNDE R,LH 防溅板(左)183 总装 COVER-FUSIBL ELINK,H 保险丝盒盖184 总装 COVER-HOLE 孔罩185 焊装 COVER-INSP HOLE 检修孔罩186 涂装 COVER-LOCATE HOLE 定位孔盖,A型φ25m m187 总装 COVER-OELTOP,RH 顶罩板,右188 总装 COVER-RELAYB OX 继电器盒罩总成189 总装 COVER-RRPLAT E 孔盖190 总装 COVER-SEATHO LE 胶贴191 总装 COVER-SEATSL IDE,RRINRL H 座椅滑轨盖,后内左192 总装 COVER-SPARET IRE 备胎盖板193 总装 COVER-STRGCO L,LWR 转向柱罩外194 总装 COVER-STRUTM TG,RR 后减震器罩195 总装 COVER-TRUNKL IDLOC K 行李箱撞锁盖196 总装 COVER-WIPERA RM 雨刮摇臂罩197 焊装 COWL TOP 顶罩板198 焊装 COWL TOP ASSY-SIDE,L 顶罩板侧板总成,左199 总装 CRP-HOSE,THDWIR E 管箍200 总装 CUSHAS SY-RRSEAT后座椅坐垫总成201 总装 CYLASS Y-BRAKEM ASTE制动总泵202 总装 CYLASS Y-CLUTCH MAST离合器主缸总成203 总装 CYLASS Y-CLUTCH OPER离合器分泵总成204 总装 DAMPER,A 减震套205 总装 DAM-SEALAN T,RRRUB减震条206 焊装 DASH-LWR 前围下板207 焊装 DASH-UPR 上仪表板208 总装 DISC-FRBRAK E 前制动盘209 总装 DISPLA Y ASSY-NAVIGA TION音响主机210 焊装 DOOR ASSY-FR,LH 前门总成,左211 总装 DOORPR OTECT OR 车门护块212 总装 DRAFTE RASSY-AIR,LH 通风器总成213 焊装 DRIP-FDR,RR LH 后翼子板滴水檐214 焊装 DRIP-FR PLR,RH 前立柱滴水槽215 焊装 DRIP-ROOF SIDE,CTR R 顶盖滴水檐216 总装 DUCT-ASPIRA TOR 进气管217 总装 DUCTAS SY-AIR,DUSTS进气管总成218 总装 DUCT-CTRVEN T,FR 中部通气管219 总装 DUCT-SIDEDE F,FRASST侧通风管220 总装 DUCT-SIDEVE NT,FRAS 侧通风管海棉221 总装 DUCT-SIDEVE NT,FRDR 通风管222 总装 DVCASS Y-PKB 驻车装置总成223 总装 DVCCOM PL-A/TCONT变速操纵杆总成224 总装 DVD-ROM,MAP DVD地图光盘225 总装 EAR PHONEJACK 耳机座总成226 总装 EMBLEM-SIM SIM卡座操作说明标贴227 总装 ENG ASSY 发动机总成228 总装 ENG ASSY 发动机总成229 总装 ESCUTC HEONASSY-F/DO 前门外拉手总成,右(宝石黑) 230 总装 ESCUT-FRDOOR INSID EHAND LE,LH 前门内把手饰盖(左)231 总装 ESCUT-STRGLO CK 点火锁饰罩232 总装 ESCUT-TELMIC ROPHO NE 话筒饰盖233 焊装 EXT ASSY-FR SIDE MBR LH 前边梁总成延长件,左234 焊装 EXT-DASH UPR,LH 仪表板上板加强件235 焊装 EXT-FR SIDE MBR,CTR 前纵梁加长件236 焊装 EXT-RR WH OTR,RH 后轮罩外板加长件,右237 总装 FASTEN ER 内饰扣238 总装 FASTEN ERASS Y-BAFFLE卡扣239 总装 FASTEN ERASS Y-BAFFLE散热器防溅板卡扣240 总装 FASTEN ER-MLDG,BACKW后挡风玻璃上嵌条241 总装 FASTEN ER-MLDG,WS 前挡风玻璃上嵌条242 总装 FASTNE RASSY-FRMUD前保险杠卡扣总成243 焊装 FDR-FR,LH 前翼子板,左244 总装 FEEDER-ANT 天线馈线245 总装 FIN ASSY-CONSOL E,RR 后杂物盒总成饰件246 总装 FIN ASSY-TRUNKLID 行李箱盖饰板总成(宝石黑)247 总装 FINASS Y-CONSOL E,A/TCONT换档杆装饰罩,A/T248 总装 FINASS Y-FRDOOR,LH 左前车门护板总成249 总装 FINASS Y-POWERW DWSW,FRLH 控制面板总成,后左250 总装 FINASS Y-RRDOOR,LH 左后车门护板总成251 总装 FINASS Y-RRPLR,LH 立柱装饰板,左后252 总装 FINASS Y-RRPSHE LF(W/WOOFER) 衣帽架搁板253 总装 FIN-DASHSI DE,LH 仪表板左下饰板254 总装 FIN-HUD 饰板总成-抬头显示器255 总装 FIN-INST,A 仪表板饰板,左256 总装 FIN-TRUNKS IDE,RH 行李箱右饰板257 总装 FIXER-STRGLO CK 点火锁固定板258 总装 FLASHE RUNIT-COMB 闪烁灯控制器259 焊装 FLG-AIR INT 进气法兰260 焊装 FLOORSIDE ASSY-RR,L 后地板侧板,左261 焊装 FLOOR-FR 前地板262 总装 FLTRAS SY-FUEL 燃油滤清器263 总装 FOAM-WS 前风窗玻璃海绵块264 焊装 FR FDR,RH 前翼子板,右265 总装 FRCOOL INGUN ITCOM PL 蒸发器总成266 总装 FRHEAT ERASS Y 暖风机总成267 总装 GARNAS SY-FRPLR,LH 前立柱饰板,左268 总装 GARNAS SY-FRPLR,LWRLH中立柱下饰板(左)269 总装 GARN-TRUNK,RRUPR行李箱上饰板270 总装 GAUGEA SSY-OILLEV EL 机油标尺杆总成271 总装 GEAR&LNKGAS SY-PS 动力转向机总成272 总装 GLASSASSY-FRDOOR,LH 前门玻璃总成(左)273 总装 GLASSA SSY-WS 前风窗玻璃总成274 总装 GLASS-BACKWD WW/OD 后挡风玻璃275 总装 GLASS-RRDOOR PTN,LH 三角玻璃(左)276 总装 GLASSR UN-FRDOOR WD 前门玻璃密封胶条(右)277 总装 GRILLE ASSY-RAD 散热器格栅总成278 总装 GRILL-FRDEF,LH 前除霜器格栅,左279 总装 GRILL-SIDEDE F,RH 前除霜器格栅,右侧280 总装 GRIPAS SY-ASST 拉手总成281 总装 GROM 垫圈282 总装 GSKT-BRAKEH OSE 制动管衬垫284 总装 GSM-ANT 手机天线285 总装 GUARDA SSY-DRAFTE R,L 通风器护板总成286 总装 GUARDA SSY-SPLASH,RA 散热器防溅板总成287 总装 GUARD-SPLASH,FRBRAK前制动防溅板288 总装 GUIDE-AIR,ENGMTG导气板289 总装 GUSS-COMPR,FR 压缩机角撑290 总装 HANDLE ASSY-FRDOOR内拉手(右)291 总装 HANDLE ASSY-TRUNK&行李箱盖拉手总成292 总装 HANDLE-PULL,FRDOOR LH 前门把手,左293 总装 HANDSE T 听筒294 焊装 HANGER-SEAT BACK 支架—座椅背部295 总装 HARN-BODY 车身线束296 总装 HARN-ENGROO M 发动机舱线束297 总装 HARN-H/F CDCHAN GER CABLEASSY CD转换器电缆线束298 总装 HARN-MAIN 主线束299 总装 HARN-ROOMLA MP 室灯线束300 总装 HARN-SUB 防滑控制线束301 总装 HARN-TAIL 车尾线束302 总装 HDLNGA SSY-ROOF 顶蓬布303 总装 HEADUP DISPL AYUNI T 抬头显示装置304 焊装 HINGEASSY-FR DOOR,U 前门上铰链总成,右305 焊装 HINGEASSY-HOOD,LH 发动机罩铰链总成306 焊装 HINGEASSY-TRUNKLID 行李箱盖铰链总成307 总装 HLDR-ROD 拉杆保持架308 总装 HLDR-RRDOOR PTN,LH 后门角窗框卡板(左)309 总装 HLDR-RRDOOR SUNSH ADE 后门窗遮阳罩保持架310 总装 HLDR-SUNVIS OR 遮阳板固定挂钩311 总装 HOLDER-FUELFI LTER滤清器支架312 焊装 HOOD ASSY 发动机舱盖总成313 焊装 HOODLE DGE ASSY,LH 挡泥板总成,左314 总装 HOODSW报警开关315 总装 HOOK-FR TIE DOWN,LH 前挂钩316 总装 HOOK-RRWDWS HADE后遮阳廉挂钩317 总装 HORN ALARM防盗喇叭318 总装 HORNAS SY-HIGH 高音喇叭319 总装 HORNAS SY-LOW 低音喇叭320 总装 HOSE&TUBEAS SY-RTN 回油管总成321 总装 HOSE&TUBESE T-PS 动力转向油管322 总装 HOSE-AIR 进气管总成323 总装 HOSE-AIR 空气软管324 总装 HOSEAS SY-BLOWBY通风管总成366 总装 LAMPAS SY-ROOM 室灯总成367 总装 LAMPAS SY-RRCOMB,LH 后组合灯总成,右368 总装 LAMPAS SY-SIDETU RN 侧转向灯369 总装 LAMPAS SY-STEP,FRDOOR,LH 左前门侧灯370 总装 LAMPAS SY-TRUNKR OOM 行李舱灯总成371 总装 LEVERC OMPL-ACCELP E 油门踏板总成372 焊装 LID ASSY-TRUNK行李箱盖总成373 总装 LIDASS Y-CLUSTE R,C 仪表盘总成,C374 总装 LIDASS Y-FUSEBL OCK 保险丝盒盖总成375 总装 LIDASS Y-GLOVEB OX 资料盒盖总成376 总装 LIDASS Y-SUNROO F 天窗盖377 焊装 LID-FUEL FILLER加油口盖378 总装 LID-GLOVEB OX 资料盒盖379 总装 LID-LUCSID E 千斤顶饰罩380 总装 LID-STRG,LH 转向罩,左381 总装 LIGHTE RASSY-CIGARE T 点烟器382 总装 LINKAS SY-TRANSC ONT 换档杆总成383 总装 LINKCO MPL-TRANSV,RH 下摆臂(右)384 总装 LNKGAS SY-WSWIPE R 雨刮连杆总成385 总装 LOCK&RCASSY-FRDO 前门锁机构(右)386 总装 LOCKAS SY-HOOD 机仓盖锁387 总装 LOCKAS SY-TRUNKL ID 行李箱盖撞锁总成388 总装 MAGAZI NE-VCD VCD转换器碟盒389 总装 MASK-DASHSI DEFIN(PK30) 饰盖390 总装 MASK-R/F SENSOR开关饰盖391 总装 MATCUT杯垫392 焊装MBR ASSY-CROSS,2ND 第二横梁393 焊装MBR ASSY-RR CROSS,CT 后横梁总成394 焊装MBR ASSY-RR SEAT CRO 后排座横梁总成395 总装 MBRASS Y-ENGMTG发动机悬置下横梁总成396 总装 MBRASS Y-STRG 转向梁总成397 总装 MBRCOM PL-FRSUSP前悬架横梁装置总成398 焊装MBR-DASH UPR CROSS前围上板横梁399 焊装MBR-SIDE RR L 后边梁,左400 总装 METERA SSY-AIRMAS S 空气流量传感器401 总装 METERA SSY-COMB 组合仪表402 总装 MFLRAS SY-EXH,SUB 副消声器总成403 总装 MICROP HONEU NIT-TEL 话筒404 总装 MIRROR ASSY-DOOR,LH 后视镜总成,左(宝石黑)405 总装 MIRROR ASSY-INSIDE车内后视镜总成406 总装 MIRROR SW 后视镜控制器407 总装 MLDG ASSY-FR DOOR LH 前门防撞饰条,左(浅灰)408 总装 MLDGAS SY-FRDOOR OU 右前窗下嵌条409 总装 MLDGAS SY-WSSIDE,LH 前挡风压板(左)410 总装 MLDGAS SY-WSUPR前挡风上饰条总成411 总装 MLDG-BACKWD W,UPR 后挡风嵌条412 总装 MLDG-RRDOOR SASH,FR 左后窗上嵌条413 总装 MLFRAS SY-EXH,FR 排气管总成(前)414 总装 MLFRAS SY-EXH,MAI 主消音器总成415 总装 MODULE ASSY-AIRBAG,ASSY 气囊总成416 总装 MODUNI T-ENGCON T 发动机控制模板417 总装 MOTORA SSY-STARTE R 起动电机418 总装 MOTORC OMPL-WSWIPE R 雨刮电机总成419 总装 MTGASS Y-EXH,RUB 排气管吊耳420 总装 MTG-COND,LWR 冷凝器支座下421 总装 MTG-EXH,RUB 排气管吊耳422 总装 MTG-RAD,LWR 散热器胶垫(下)423 总装 MUDGUA RD-CTR,FR LH 下裙摆,前左(浅灰)424 总装 NOZZLE COMPL-WSWASH前雨刮喷嘴(左)425 总装 NOZZLE-DEF,WS 除霜器导管426 总装 NOZZLE-SIDEDE F,FRASST侧除霜器管道(右)427 焊装 NUT WELD 焊接螺母428 总装 ORNAMASSY-ENG COVER发动机装饰盖总成429 总装 P/HC/RMACHI NESCR EW 天窗开关螺钉430 总装 PACK-BRAKEB OOSTE R 垫片431 总装 PACK-FUELGA UGE 密封圈432 总装 PACK-MASTER CYL 胶垫433 总装 PAD-FR 发动机前减震垫434 总装 PANEL&PADASS Y 仪表板总成435 总装 PANELC LIPAS SY 夹板总成(左)436 总装 PANEL-INSTLW R,DR 转向柱下饰板437 焊装 PATCH-DASH LWR,LH 前围板衬片,左438 焊装 PATCH-TRUNKLID LOCK 行李箱盖锁辅助板439 总装 PEDALC OMPL-BRAKE,W/ 制动踏板,带支架总成440 总装 PIN-CLEVIS定位销轴441 总装 PIN-COTTER,SPLIT开口销442 总装 PINION ASSY-SPEEDO,W 速度传感器443 总装 PIPEAS SY-COOLER,CONDTO TANK空调高压管(干—冷)444 总装 PIPEAS SY-OILCHA RGI 加油管总成445 总装 PIPECO MPL-FRCOOL ER,HIGH 空调高压管(蒸—干)446 总装 PIPECO MPL-FRCOOL ER,LOW 前低压空调管447 焊装 PLATE-ANCH,C 加强件448 总装 PLATE-CABLEL OCK 弹簧锁片449 总装 PLATE-KICKIN G,FRLH LED门槛踏板(左前)450 总装 PLATE-LOCK,FUELGA UG 油表锁定板451 总装 PLATE-LOCKH/BCONT卡簧452 总装 PLATE-MODELN O 铭牌(整车)453 焊装 PLATE-NUT(R)螺母板454 总装 PLATE-TUBE,FUELTA NK 油箱管护板455 焊装 PLR ASSY-CTR,INR LH 中柱内板总成456 焊装 PLR ASSY-FR,INR UPR 前立柱内上板,左457 总装 PLUG 堵塞458 涂装 PLUG-WAIST&PSHELF行李架及中板堵盖(35×25×t2)459 总装 PROTEC TOR-FLATWI RE 排水管护垫460 总装 PROTR-BACKWD WHARN后挡风线束护夹461 总装 PROTR-FLATWI RE 胶贴462 总装 PROTR-FRFDR,LH 前翼子板防溅板总成,左463 总装 PROTR-FUELTA NK 油箱护板464 总装 PROTR-HARN 胶贴465 总装 PROTR-TRUNKL IDFIN行李箱盖护板466 焊装 PSHELF行李搁板467 总装 PULLER-FUSE 保险丝夹468 总装 PUMPAS SY-FUELIN TA 油泵总成469 总装 PUMPAS SY-PS 动力转向泵总成470 总装 RADASS Y 散热器总成471 总装 RADASS Y,W/OILCOO LE 散热器总成472 焊装 RAIL ASSY-ROOF SIDE, 顶盖侧内柱总成473 总装 RAILCO MPL-SUNROO F 天窗滑轨组件474 焊装 RAIL-ROOF,FR 前顶梁475 焊装 RAIL-ROOF,RR 顶盖后横梁476 总装 RECEIV ER 接收器477 总装 RECEIV ER ASSY-3 ZONE 按摩座椅接收器478 总装 REFLEC TORAS SY-WARNIN G 三角警示牌479 总装 REGCOM PL-FRDOOR,LH 前门窗升降机总成(左)480 焊装 REINFASSY-ANCH BELT 安全带加强件481 焊装 REINFASSY-BELT ANCH,RR OTR 安全带加强件482 焊装 REINFASSY-DASH LWR 前围下板加强板483 焊装 REINFASSY-FR PLR,LW 前立柱内下加强件,右484 焊装 REINFASSY-FR SIDE MBR,RH 前边梁总成加强件,右485 焊装 REINFASSY-HOODLE DGE 挡泥板加强件总成486 焊装 REINFASSY-PKB 驻车安装支架487 焊装 REINFASSY-ROOF 顶盖天窗加强框488 焊装 REINFASSY-RR PLR,LH 后立柱加强件总成,左489 焊装 REINFASSY-RR SIDE MBR,LH 后边梁加强件490 焊装 REINFASSY-RR SUSP MTG L 后悬挂安装加强件总成,左491 焊装 REINFASSY-SEAT BELT 安全带加强件总成492 焊装 REINFASSY-WIPERMOT 雨刮电机加强件总成493 焊装 REINFPSHELF行李箱隔板加强板494 焊装 REINF-FR ROOF RAIL 前顶梁加强件495 总装 REINF-KNEEPR OTR,RH 加强件496 焊装 REINF-ROOF SIDE RAIL 顶盖侧梁加强件497 焊装 REINF-RR PANELUPR 后围上板加强板498 焊装 REINF-WIPERPIVOT雨刮枢轴加强件499 总装 RELAY继电器500 总装 RELAY-HORN 喇叭继电器501 总装 REMOTE ASSY-3 ZONE CONTRC按摩座椅遥控器502 总装 RESETS W 复位开关503 总装 RESONA TORAS SY 谐振器504 焊装 RET ASSY-STRIKE R,LH 撞锁卡扣总成505 总装 RET -FR BMPR 前保险杠保持架506 总装 RET-SNAP 定位销507 总装 RING-CIGARE TTELI GHT 点烟器护圈508 总装 RING-SNAP,BRG 内卡环509 总装 RIVET-SPL 铆钉510 总装 ROD-BATFIX蓄电池固定拉杆511 总装 RODCOM PL-RADIUS半径杆512 总装 ROD-CONN,STAB 后稳定杆连接杆513 总装 ROD-KEYLOC K,RH 锁芯连杆514 总装 ROD-TRUNKL IDLOC K 行李舱撞锁杆515 焊装 ROOF 顶盖516 焊装 RR PANEL-UPR 后围上板517 涂装 RUB BMPR 发动机减振垫518 总装 RUB-BMPR 缓冲块519 总装 SASHAS SY-FRDOOR LW 前窗玻璃导轨(右后)520 总装 SASHCO MPL-RRDOOR P 后门窗框(右)521 总装 SCREEN ASSY-SEALIN G,FRDOOR LH 前门防水胶膜(左)522 总装 SCREW-TAPPIN GP/HTYPE2后门窗遮阳罩螺钉523 总装 SCR-FIX,STRGLO CK 点火锁螺钉524 总装 SCR-TAPTRH DTYPE阅读灯螺钉525 总装 SEAL ASSY-COWL TOP 顶罩板密封条526 总装 SEALAS SY-RADCOR E 机仓散热密封条右527 总装 SEAL-FRDOOR PARTI NG 左前门外密封条528 总装 SEAL-GREASE,FRHUB油封529 总装 SEAL-INSPHO LECOV ER 检修孔罩密封条530 总装 SEAL-ORING(18S) O型圈531 总装 SEAL-RRDOOR PARTI NG 后门右外密封条532 总装 SEAL-STOPPE R 密封挡块533 总装 SEATAS SY-FR,LH 前座椅总成(左)534 总装 SEATAS SY-FRSPR,UPR 前弹簧座总成535 总装 SEATAS SY-RRBACK后座椅靠背总成536 总装 SEATAS SY-RRSPR,UPR 后弹簧座总成,左537 总装 SEATBE LTASS Y-TONGUE,RRLH 后安全带总成(左) 538 总装 SEN ASSY-NAVIGA TION遥控接收头539 总装 SEN&DIAGNO SISAS SY 气囊传感器&诊断器总成540 总装 SEN-AMB 传感器541 总装 SENASS Y-ANTISK ID,FR 前防抱死感应器,右542 总装 SENDER UNIT-FUELGA U 燃油表传感器543 总装 SEN-INCAR传感器544 总装 SEN-ROTOR,ANTISK IDR 后防抱感应器转子545 总装 SENSAO NARSS Y-BACKSO NAR,RH 雷达传感器(浅灰)546 总装 SEN-SUN 传感器547 总装 SFTASS Y-FRDRIV E 驱动轴总成548 总装 SHADEA SSY-SUNROO F 天窗遮阳板549 总装 SHIM-DOORLO CK 调整垫片550 总装 SHIM-LID 垫片551 总装 SHROUD ASSY,W/MOTOR风扇及电机总成552 焊装 SILL ASSY-INR,LH 门槛内板总成,左553 总装 SIM SIM卡座+连线554 总装 SPACER垫片555 焊装 SPACER-C PEDALBRKT C型踏板支架556 总装 SPACER-RRSTRU TINSU垫片557 总装 SPARETIRE ASSY 备胎总成558 总装 SPCR-BACKGL ASS 后挡风玻璃垫片559 总装 SPCR-FRBMPR SIDE,LH 前保险杠左侧护垫560 总装 SPCR-GLASS前挡风玻璃定位扣561 总装 SPCR-HDLNG减震器垫块562 总装 SPCR-PSHELF SIDE,RR 海绵垫(铰链)563 总装 SPCR-RRBMPR SIDE,LH 后保险杠左侧护垫564 总装 SPDL-RR 后心轴565 总装 SPEAKE R ASSY-NAVI NAVI扬声器总成566 总装 SPEAKE RUNIT6.5FR 前扬声器567 总装 SPLASH GUARD-AIRDUC T 通风口防溅泡棉568 总装 SPLASH GUARD-HOODLE D 防溅板(右)569 总装 SPR-FR 弹簧、前570 总装 SPR-FUELFI LLER加油口弹簧571 总装 SPRING NUTM5螺母夹572 总装 STAB-FR 前稳定杆573 焊装 STAY ASSY-FR BMPR,LH 前保险杠支架总成,左574 焊装 STAY ASSY-FR FDR,RH 前翼子板支撑板总成,右575 总装 STAYAS SY-INST,ASST 仪表板支架总成,右576 总装 STAY-KEYCYL,RH 锁芯支撑架(右)577 焊装 STFNR-RR FDR, LH 后翼子板加强件578 涂装 STOPPE R RUB-DOOR 发动机盖减振垫579 总装 STOPPE R-DIFFMT G,LWR 挡块580 总装 STOPPE R-INSUL,REBOUN弹性加强板(左)581 总装 STOPPE R-REBOUN D,FRS 挡块582 总装 STRIKE RASSY-DOOR 车门撞锁总成583 总装 STRIKE RASSY-TRUNKL行李箱撞锁座总成584 总装 STRIKE R-GLOVEB OXLI资料盒撞锁585 总装 STRUTA SSY-FRSUSP,L 前悬支柱总成(左)586 总装 SUBWOO FER 压缩式重低音喇叭587 总装 SUNSHA DEASS Y-RRDOOR,RRLH 后门窗遮阳罩左588 总装 SUNVIS ORASS Y,RH 遮阳板总成,右589 焊装 SUPT ASSY-RAD CORE 散热器芯支架总成590 总装 SUPT-ENGMTG,LH 发动机支架(左)591 总装 SUPT-INSUL隔热垫支架592 总装 SUPT-INTMAN IF 进气歧管支架593 焊装 SUPT-RR SEAT BA 后排座靠背支架总成594 焊装 SUPT-TRUNKLID LOCK 行李箱锁板595 总装 SW ASSY-RR FOG 后雾灯开关总成596 总装 SWASSY-DOOR 车门灯开关597 总装 SWASSY-HAZARD危险警告开关598 总装 SWASSY-STOPLA MP 制动灯开关599 总装 SWASSY-SUNROO F 天窗开关总成600 总装 SWASSY-TEL 电话开关601 总装 SWCOMP L-COMB 组合开关总成602 总装 SW-HUD 抬头显示开关603 总装 SWUNIT-POWERW DW,AS 电动窗开关(右)604 总装 SWUNIT-POWERW DW,RR 后门电动窗开关605 总装 TAG-CAUTIO N,SELECT OR 换挡警示标贴606 总装 TANKAS SY-FUEL 燃油箱总成607 总装 TANKAS SY-LIQUID,W/SW 干燥瓶总成608 总装 TANKAS SY-PS 动力转向罐609 总装 TANKAS SY-WSWASH清洗罐总成610 总装 TANKCO MPL-RADRES VR 贮液罐总成611 涂装 TAPE-FRDOOR OUTSI DE 前门窗框外侧胶条,右612 风神物流 TIRE 备胎613 总装 TIRE ASSY 轮胎总成614 风神物流 TIRE-TBLS205/60R1591H 轮胎615 总装 TOOLSE T 随车工具616 总装 TRANSA XLEAS SY 变速器总成617 总装 TRAY-BAT 蓄电池托盘618 总装 TRIM-SUNROO FSIDE,LH 天窗装饰板,左619 总装 TUBEAS SYBRA KE 制动管路总成,后右620 总装 TUBEAS SY-BRAKE,FRL 前制动管(左)621 总装 TUBEAS SY-BRAKE,FRR 制动管路总成,前右622 总装 TUBEAS SY-BRAKEA CTR 制动管路总成,作动器623 总装 TUBEAS SY-CLUTCH,B 离合器管路总成624 总装 TUBEAS SY-FILLER加油管总成625 总装 TUBEAS SY-OILCOO LER 油冷却管总成626 总装 TUBEAS SY-PS 转向油散热器627 总装 TUBEAS SY-RTN,PS 动力转向油管机仓右后628 总装 TUBEAS SY-WSWASH前雨刮水管629 总装 TUBE-BRTHR,B 呼吸器管630 总装 TUBECO MPL-FUEL,BRAKE&EVAP 管路总成631 总装 TUBE-FUELTA NKOUT LE 供油管632 总装 TUBE-FUELTA NKRTN回油管633 总装 TUBE-VAC,BRAKEB OOST真空管634 总装 TUBE-VENT 溢气软管Ⅰ635 总装 UNIT-HUDDIS PLAY抬头显示器636 风神物流 VALVE-AIR 气嘴637 总装 VALVEA SSY-BRTHR阀总成638 总装 VALVEA SSY-CHECK单向阀总成639 总装 VALVEA SSY-DUALPR OP 阀总成640 总装 VALVEA SSY-FUELCH EC 单向阀总成641 总装 VCD CHANGE R ASSY VCD转换器总成642 涂装 WAIST&PSHELF ASSY 门槛堵盖,小(35×25×t2)643 焊装 WAIST-RR 后腰梁644 总装 WASHER-LOCK,SPR 弹簧垫圈645 总装 WASH-OTR,SHOCKA BS 前连接杆垫圈646 总装 WASH-PLAIN垫圈647 风神物流 WEIGHT WHEEL BALAN CE,10G 平衡块648 焊装 WELD BOLT 焊接螺栓649 总装 WELT-BODYSI DE,FRLH 车身侧围密封条,前左650 风神物流 WHEEL-DISC,AL 轮辋651 焊装 WH-RR,INR RH 后轮罩内板,右652 总装 WIREAS SY-STRG 转向线总成653 总装 WIRE-BONDIN G,RES 搭铁线654 总装 WSTRIP ASSY-RRDOOR, 后门胶条总成(左)655 总装 WSTRIP-DRIP,LH 滴水檐胶条,左656 总装 WSTRIP-RRDOOR PTNG后门角窗胶条(左)657 总装 WSTRIP-TRUNKL ID 行李舱胶条。

FLOELINE LU12 13 14手册(新版)

FLOWLINE超声波液位计型号:LU05/12/11/13 使用说明书如果您的产品出现损坏和故障,请与当地经销商联系,并明确以下事项:1.产品型号及出厂编号2.使用人联系电话及姓名3.大致描述故障现象4.大致说明使用状况之后您会收到一份返修通知单,请按通知地址寄出损坏的仪表。

经销商:(中文说明书仅供参考,阅读时,请参照英文说明)技术参数测量范围:LU05: 0.16英尺-4英尺 ( 5cm-1.2m) LU11: 0.16英尺-10英尺 ( 10cm-5.0m) LU12: 0.16英尺-10英尺 ( 5cm-3.0m) LU13: 0.33英尺-25英尺 (10cm-8m) 精度:空气满量程的±0.2% 分辨率:0.125(3mm ) 发射角度:LU05 / LU12 2直径LU13 / 3直径死区:LU05 / LU12 0.16英尺(5cm )LU13 0.33英尺(10cm )LED 指标:电源、标定、诊断状况 存 储 器:断电保存功能 电源电压:14-28VDC 信号输出:4-20mA 、二线制 失效诊断:恢复到22mA 温度范围:-40~+70℃ 压力级别:0~2bar@ 25℃ 外壳级别:NEMA6X(IP67)传感器材料: PVDF (聚偏氟乙烯) 电缆外套材料:PP (聚丙席) 电缆长度:标准10英尺(3m )单独订购:25英尺(7.6m )或50英尺(15.2m ) 安装螺纹:LU05 / LU12 1NPT (1G ) LU13 2NPT (2G ) 安装垫片:氟化橡胶 等 级:普通C E 认证:EN50082-2immunity一:安全注意事项※关于本说明书在安装和使用产品之前,请仔细阅读本说明书,本说明书适宜于超声波液位计:LULU12/LU11/13/14, 阅读本说明书之前,确定您所订购产品的型号。

※用户的安全责任FLOWLINE公司可提供多种液位计供用户选择,所以,您必须根据应用状况选择完全满足要求的仪表,否则仪表可能无法达到使用要求或造成损坏。

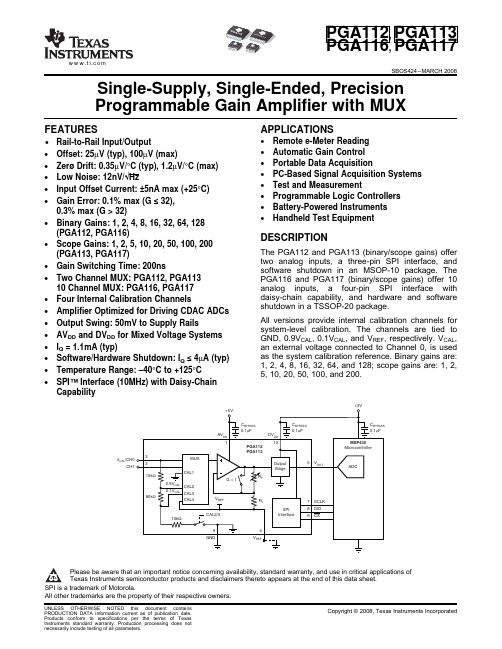

PGA112资料

• Binary Gains: 1, 2, 4, 8, 16, 32, 64, 128 (PGA112, PGA116)

• Scope Gains: 1, 2, 5, 10, 20, 50, 100, 200 (PGA113, PGA117)

• Gain Switching Time: 200ns • Two Channel MUX: PGA112, PGA113

DESCRIPTION

The PGA112 and PGA113 (binary/scope gains) offer two analog inputs, a three-pin SPI interface, and software shutdown in an MSOP-10 package. The PGA116 and PGA117 (binary/scope gains) offer 10 analog inputs, a four-pin SPI interface with daisy-chain capability, and hardware and software shutdown in a TSSOP-20 package.

PACKAGE-LEAD MSOP-10 MSOP-10 TSSOP-20 TSSOP-20

PACKAGE DESIGNATOR

DGS DGS PW PW

PACKAGE MARKING

P112 P113 PGA116 PGA117

(1) For the most current package and ordering information see the Package Option Addendum at the end of this document, or see the TI web site at .

电源管理芯片DK112中文资料

电源管理芯⽚DK112中⽂资料功能描述DK112芯⽚是专⽤⼩功率开关电源控制芯⽚,⼴泛⽤于电源适配器、LED电源、电磁炉、空调、DVD等⼩家电产品。

⼀、产品特点采⽤双芯⽚设计,⾼压开关管采⽤双极型晶体管设计,以降低产品成本;控制电路采⽤⼤规模MOS数字电路设计,并采⽤E极驱动⽅式驱动双极型晶体芯⽚,以提⾼⾼压开关管的安全耐压值。

内建⾃供电电路,不需要外部给芯⽚提供电源,有效的降低外部元件的数量及成本。

芯⽚内集成了⾼压恒流启动电路,⽆需外部加启动电阻。

内置过流保护电路,防过载保护电路,输出短路保护电路,温度保护电路及光藕失效保护电路。

内置斜坡补偿电路,保证在低电压及⼤功率输出时的电路稳定。

内置PWM振荡电路,并设有抖频功能,保证了良好的EMC特性。

内置变频功能,待机时⾃动降低⼯作频率,在满⾜欧洲绿⾊能源标准(<0.3W)同时,降低了输出电压的纹波。

内置⾼压保护,当输⼊母线电压⾼于保护电压时,芯⽚将⾃动关闭并进⾏延时重启。

内建斜坡电流驱动电路,降低了芯⽚的功耗并提⾼了电路的效率。

4KV防静电ESD测试。

⼆、功率范围输⼊电压(85~264V ac)(85~145V ac)(180~264V ac)最⼤输出功率12W18W18W三、封装与引脚定义引脚符号功能描述1Gnd接地引脚。

2Gnd接地引脚。

3Fb反馈控制端。

4Vcc供电引脚。

5678Collector输出引脚,连接芯⽚内⾼压开关管Collector端,与开关变压器相连。

四、内部电路框图五、极限参数供电电压Vcc...........................................-0.3V--9V供电电流Vcc...........................................100mA引脚电压...........................................-0.3V--Vcc+0.3V 开关管耐压...........................................-0.3V--780V 峰值电流...........................................800mA总耗散功率...........................................1000mW⼯作温度...........................................0℃--125℃储存温度...........................................-55℃--+150℃焊接温度...........................................+280℃/5S六、电⽓参数项⽬测试条件最⼩典型最⼤单位电源电压Vcc AC输⼊85V-----265V456V启动电压AC输⼊85V-----265V 4.85 5.2V关闭电压AC输⼊85V-----265V 3.64 4.2V电源电流Vcc=5V,Fb=2.2V203040mA 启动时间AC输⼊85V------500mS Collector保护电压L=1.2mH460480500V开关管耐压Ioc=1mA700------V开关管电流Vcc=5V,Fb=1.6V----3.6V600650700mA 峰值电流保护Vcc=5V,Fb=1.6V----3.6V650720800mA 振荡频率Vcc=5V,Fb=1.6V----2.8V606570KHz 变频频率Vcc=4.6V,Fb=2.8V----3.6V0.5--65KHz 抖频步进频率Vcc=4.6V,Fb=1.6V----2.8V0.81 1.2KHz 温度保护Vcc=4.6V,Fb=1.6V----3.6V120125130℃占空⽐Vcc=4.6V,Fb=1.6V----3.6V5---50%控制电压Fb AC输⼊85V-----265V 1.6--- 3.6V七、⼯作原理上电启动:当外部电源上电时,直流⾼压经开关变压器传⾄芯⽚的COLLECTOR端(5678引脚),后经内建⾼压恒流启动电路将启动电流送⾄开关管Q1的B极,通过开关管Q1的电流放⼤(约为20倍放⼤)进⼊电源管理电路经D1为Vcc外部电容C1充电,同时为Fb预提供⼀个3.6V电压(Fb引脚对地应接⼊⼀只滤波电容),当Vcc的电压逐步上升⾄5V时,振荡器起振,电路开始⼯作,控制器为Fb开启⼀个约为25uA的对地电流源,电路进⼊正常⼯作。

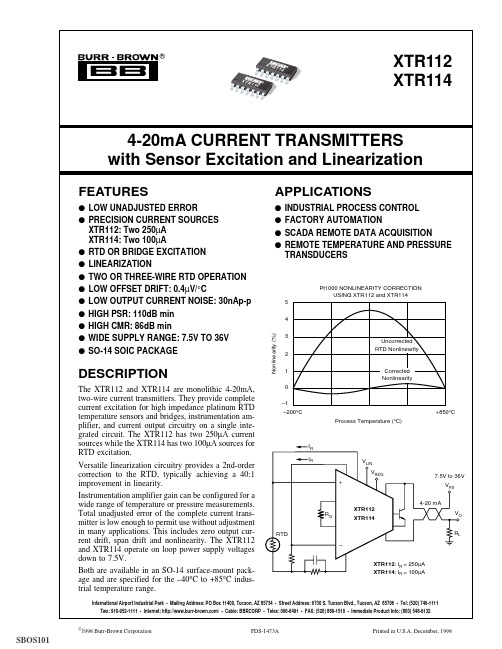

XTR112中文资料

APPLICATIONS

q q q q INDUSTRIAL PROCESS CONTROL FACTORY AUTOMATION SCADA REMOTE DATA ACQUISITION REMOTE TEMPERATURE AND PRESSURE TRANSDUCERS

Pt1000 NONLINEARITY CORRECTION USING XTR112 and XTR114 5 4 Nonlinearity (%) 3 2 1 0 –1 –200°C Process Temperature (°C) +850°C

±0.2 ±25 0.01 ±100 ±1.5 ±3 ±50 3.5 25 ±3

±0.4 T T ±250 ±3 T ±100 T 50 ±10

5 20 ±0.2 5 0.1 || 1 5 || 10 0.6 VO = 2V(6) 250 100 ±0.05 ±15 ±10 ±0.02 ±3 1 (V+) –2.5 –0.2 500 1.2 0.001 0.0004 5.1 ±0.02 ±0.2 1 –1, +2.1 –1, +2.4 75 1 ±0.2 ±25 +24 +7.5 –40 –55

®

©

1998 Burr-Brown Corporation

PDS-1473A 1

SBOS101

Printed in U.S.A. December, 1998 XTR112, XTR114

元器件交易网

SPECIFICATIONS

At TA = +25°C, V+ = 24V, and TIP29C external transistor, unless otherwise noted. XTR112U XTR114U PARAMETER OUTPUT Output Current Equation Output Current, Specified Range Over-Scale Limit Under-Scale Limit: XTR112 XTR114 ZERO OUTPUT(1) Initial Error vs Temperature vs Supply Voltage, V+ vs Common-Mode Voltage vs VREG Output Current Noise: 0.1Hz to 10Hz SPAN Span Equation (transconductance) Initial Error (3) vs Temperature(3) Nonlinearity: Ideal Input (4) INPUT(5) Offset Voltage vs Temperature vs Supply Voltage, V+ vs Common-Mode Voltage, RTI (CMRR) Common-Mode Input Range(2) Input Bias Current vs Temperature Input Offset Current vs Temperature Impedance: Differential Common-Mode Noise: 0.1Hz to 10Hz CURRENT SOURCES Current: XTR112 XTR114 Accuracy vs Temperature vs Power Supply, V+ Matching vs Temperature vs Power Supply, V+ Compliance Voltage, Positive Negative(2) Output Impedance: XTR112 XTR114 Noise: 0.1Hz to 10Hz: XTR112 XTR114 VREG(2) Accuracy vs Temperature vs Supply Voltage, V+ Output Current: XTR112 XTR114 Output Impedance LINEARIZATION RLIN (internal) Accuracy vs Temperature POWER SUPPLY Specified Voltage Operating Voltage Range TEMPERATURE RANGE Specification, TMIN to TMAX Operating /Storage Range Thermal Resistance, θJA SO-14 Surface-Mount T Specification same as XTR112U, XTR114U. NOTES: (1) Describes accuracy of the 4mA low-scale offset current. Does not include input amplifier effects. Can be trimmed to zero. (2) Voltage measured with respect to IRET pin. (3) Does not include initial error or TCR of gain-setting resistor, RG. (4) Increasing the full-scale input range improves nonlinearity. (5) Does not include Zero Output initial error. (6) Current source output voltage with respect to IRET pin.

洛迦诺分类号

洛迦诺分类号

Locarno中文是洛迦诺分类(LOC)一种工业品外观设计注册用国际分类,由《洛迦诺协定》(1968年)建立。

洛迦诺分类第十版于2014年1月1日生效。

国际上所采用的设计专利系统为根据Locarno分类表(Locarno Classification,洛迦诺分类表)所建立,其中该分类制度源于1968年所签署之Locarno Agreement(罗卡诺协定,亦译为洛迦诺协定)而来,而我国亦于90年10月24日所修正之专利法中采用该分类系统。

用国际专利分类法分类专利文献(说明书)而得到的分类号,称为国际专利分类号,通常缩写为IPC。

洛迦诺分类是一种工业品外观设计注册用国际分类,通常缩写为LOC。

IPC和洛迦诺分类号是判定专利预审申请是否符合保护中心受理条件的重要依据之一。

112F1中文资料

H

N4 7 N3 5 N2 3 N1 1 8 6 4 2

8

6

4 3

Par t No.

10.5max.

7

5

1

DATE CODE

TDK

2

ø0.5

Weight: 2g Dimensions in mm

ELECTRICAL CHARACTERISTICS

Part No. 123G∗1E 124H1E 133G1E 134H1E

ET constant (V-µs) min. 25 25 25 15 15 15 12 12 12

Refer to Winding form and pin numberings.

Specifications which provide more details for the proper and safe use of the described product are available upon request. All specifications are subject to change without notice.

KP Series KP-27, -35, -51, -148 Types

SHAPES AND DIMENSIONS

7.3max. 6 4 2 7.1max. 8min. ø0.5 5±0.2

WINDING FORM AND PIN NUMBERINGS

A

N2 5 3 6±0.2 6 4 2

B

N3 5 N2 3 N1 1 6 4 2

KP Series KP-27, -35, -51, -148 Types

SHAPES AND DIMENSIONS

10.5max. 12max. 4±0.6 7.5±0.25

TFS112资料

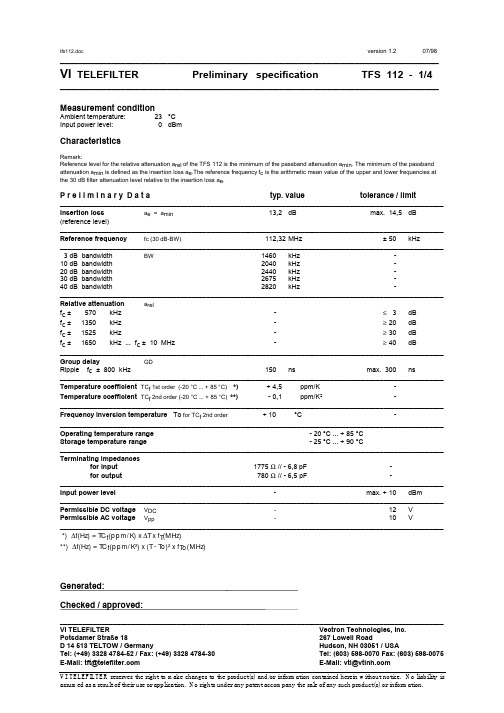

tfs112.docversion 1.2 07/98_________________________________________________________________________________VI TELEFILTERPreliminary specification TFS 112 - 1/4_________________________________________________________________________________Measurement conditionAmbient temperature: 23 °C Input power level: 0 dBmCharacteristicsRemark:Reference level for the relative attenuation a rel of the TFS 112 is the minimum of the passband attenuation a min . The minimum of the passband attenuation a min is defined as the insertion loss a e .The reference frequency f c is the arithmetic mean value of the upper and lower frequencies at the 30 dB filter attenuation level relative to the insertion loss a e .P r e l i m i n a r y D a t a typ. value tolerance / limit______________________________________________________________________________________________________Insertion lossa e = a min 13,2 dB max. 14,5 dB (reference level)______________________________________________________________________________________________________Reference frequencyf c (30 dB-BW) 112,32 MHz ± 50 kHz ______________________________________________________________________________________________________3 dB bandwidth BW 1460kHz - 10 dB bandwidth 2040 kHz - 20 dB bandwidth 2440 kHz - 30 dB bandwidth 2675 kHz - 40 dB bandwidth 2820 kHz -______________________________________________________________________________________________________ Relative attenuation a rel f c ± 570 kHz - ≤ 3 dB f c ± 1350 kHz - ≥ 20 dB f c ± 1525 kHz - ≥ 30 dB f c ± 1650 kHz ... f c ± 10 MHz - ≥ 40 dB______________________________________________________________________________________________________ Group delay GD Ripple f c ± 800 kHz 150 ns max. 300 ns______________________________________________________________________________________________________Temperature coefficient TC f 1st order (-20 °C ... + 85 °C) *) + 4,5 ppm/K - Temperature coefficient TC f 2nd order (-20 °C ... + 85 °C) **) -0,1 ppm/K² - ______________________________________________________________________________________________________Frequency inversion temperature To for TC f 2nd order+ 10 °C - ______________________________________________________________________________________________________Operating temperature range- 20 °C ... + 85 °C Storage temperature range- 25 °C ... + 90 °C ______________________________________________________________________________________________________ Terminating impedance s for input 1775 Ω // - 6,8 pF - for output 780 Ω // - 6,5 pF -______________________________________________________________________________________________________ Input power level - max. + 10 dBm______________________________________________________________________________________________________Permissible DC voltage V DC -12 V Permissible AC voltage V pp -10 V ______________________________________________________________________________________________________ *) ∆f(Hz) = TC f (ppm/K) x ∆T x f T (MHz)**) ∆f(Hz) = TC f (ppm/K²) x (T - To)² x f To (MHz)Generated:Checked / approved:______________________________________________________________________________________________________ VI TELEFILTER Vectron Technologies, Inc. Potsdamer Straße 18 267 Lowell Road D 14 513 TELTOW / Germany Hudson, NH 03051 / USA Tel: (+49) 3328 4784-52 / Fax: (+49) 3328 4784-30 Tel: (603) 598-0070 Fax: (603) 598-0075 E-Mail: tft@ E-Mail: vti@tfs112.doc version 1.2 07/98 _________________________________________________________________________________VI TELEFILTER Preliminary specification TFS 112 - 2/4 _________________________________________________________________________________Construction and pin configuration(All dimensions in mm)TFS 112tft K7Single-ended 50 Ohm matching circuitT.B.D.______________________________________________________________________________________________________ VI TELEFILTER Vectron Technologies, Inc. Potsdamer Straße 18 267 Lowell RoadD 14 513 TELTOW / Germany Hudson, NH 03051 / USATel: (+49) 3328 4784-52 / Fax: (+49) 3328 4784-30 Tel: (603) 598-0070 Fax: (603) 598-0075 E-Mail: tft@ E-Mail: vti@tfs112.doc version 1.2 07/98 _________________________________________________________________________________VI TELEFILTERPreliminary specification TFS 112 - 3/4_________________________________________________________________________________Stability characteristicsAfter the following tests the filter shall meet the whole specification:1. Shock: 100g, 18 ms, half sine wave, 3 shocks each plane;DIN IEC 68 T2 - 272. Vibration: 10 Hz to 500 Hz, 0,075 mm or 1g respectively, 1 octave per min, 10 cycles per plan, 3 plans;DIN IEC 68 T2 - 63. Damp heat: 90 % to 95 % rel. humidity, 40 °C, 10 days; (steady state)DIN IEC 68 - 2 - 34. Resistance tosolder heat (reflow): max. 2 times reflow process;for temperature conditions refer to the attached "Air reflow temperature conditions" on sheet 4;PackingTape & Reel: DIN IEC 286 - 3, with exception of value for N and minimum bending radius; tape type II , embossed carrier tape with top cover tape on the upper side; max. pieces of filters per reel: 1700COVER TAPETape (all dimensions in mm)W : 24 ± 0,3Po : 4 ± 0,1Do : 1,5 + 0,5 E : 1,75 ± 0,1F : 11,5 ± 0,1G (min) : 0,75P2 : 2 ± 0,1P1 : 12 ± 0,1D1(min) : 1,5Ao : 7,1 ± 0,2Bo : 13,9 ± 0,2D1 : 1,5 + 0,5NW 1W 2Reel (all dimensions in mm):A : 330W1 : 24,4 +2W2 (max) : 30,4N (min) : >= 90C : 13 ± 0,25The minimum bending radius is 45 mm. The mounting surface of the filters faces the bottom side of the embossed carrier tape. The marking of the filters is able to read if the view is directed on the upper side of the carrier tape with the sprocket holes on the right side of the tape.______________________________________________________________________________________________________ VI TELEFILTER Vectron Technologies, Inc. Potsdamer Straße 18 267 Lowell Road D 14 513 TELTOW / Germany Hudson, NH 03051 / USA Tel: (+49) 3328 4784-52 / Fax: (+49) 3328 4784-30 Tel: (603) 598-0070 Fax: (603) 598-0075 E-Mail: tft@ E-Mail: vti@tfs112.docversion 1.2 07/98_________________________________________________________________________________VI TELEFILTERPreliminary specification TFS 112 - 4/4_________________________________________________________________________________Air reflow temperature conditions1st and 2nd air reflow profileName:pre-heating periods main-heating periods peak temperatureTemperature:150 °C - 170 °C over 200 °C 255 °C ± 5 °CTime:60 sec. - 90 sec. 20 sec. - 25 sec.5±°CTolerancetemperatures:oftime / sec. temperature / °C time / sec. temperature / °C160 023 14016134 1501046 160164 2060 170170 3018080 18040205103 19050230121 19560134 200255 70143 205230 80205150 21090154 215180 100156 220165 110140158 230120120 130159 240______________________________________________________________________________________________________VI TELEFILTER Vectron Technologies, Inc.Potsdamer Straße 18 267 Lowell RoadD 14 513 TELTOW / Germany Hudson, NH 03051 / USATel: (+49) 3328 4784-52 / Fax: (+49) 3328 4784-30 Tel: (603) 598-0070 Fax: (603) 598-0075E-Mail: tft@ E-Mail: vti@。

DDC112中文资料

Protected by US Patent #5841310

AVDD CAP1A CAP1A IN1 CAP1B CAP1B CAP2A CAP2A IN2 CAP2B CAP2B Dual Switched Integrator Dual Switched Integrator AGND

CHANNEL 1

No Missing Codes Input Bias Current Range Error Range Error Match(5) Range Sensห้องสมุดไป่ตู้tivity to VREF Offset Error Offset Error Match(5) DC Bias Voltage(6) (Input VOS) Power Supply Rejection Ratio Internal Test Signal Internal Test Accuracy

CEXT = 250pF 47.5 95 142.5 190 237.5 285 332.5 –0.4%

1000 50 52.5 100 105 150 157.5 200 210 250 262.5 300 315 350 367.5 of Positive FS 2 1,000,000 10 12 12 T T T T T T T T T T T T T T T

TA = +25°C Range 5 (250pC) All Ranges VREF = 4.096 ±0.1V Range 5, (250pC)

3.2 3.8 4.2 6.0 ±0.005% Reading ±0.5ppm FSR, max ±0.005% Reading ±0.5ppm FSR, typ ±0.025% Reading ±1.0ppm FSR, max 20 0.1 10 5 0.1 0.5 1:1 ±200 ±100 ±0.05 ±2 ±25 ±200 13 ±10 ±0.5 ±0.2 3 0.01 2 25 ±0.05 4.000 4.096 150

OMIF-S-112LM中文资料

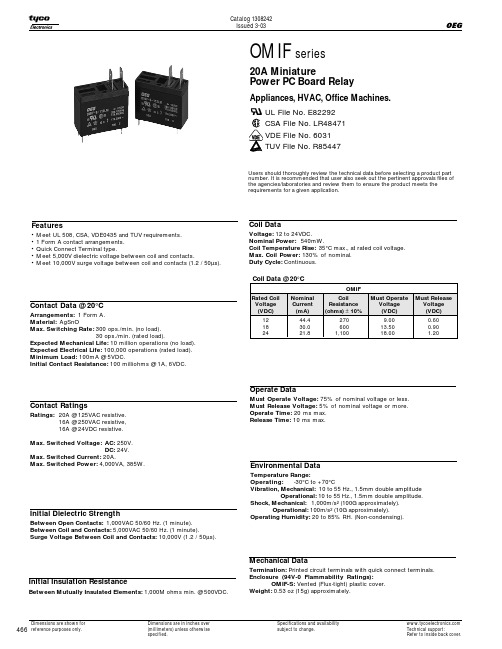

466Dimensions are shown forreference purposes only.Dimensions are in inches over(millimeters) unless otherwisespecified.Specifications and availabilitysubject to change.Technical support:Refer to inside back cover. Features•Meet UL 508, CSA, VDE0435 and TUV requirements.• 1 Form A contact arrangements.•Quick Connect Terminal type.•Meet 5,000V dielectric voltage between coil and contacts.•Meet 10,000V surge voltage between coil and contacts (1.2 / 50µs).OMIF series20A MiniaturePower PC Board RelayAppliances, HVAC, Office Machines.UL File No. E82292CSA File No. LR48471VDE File No. 6031TUV File No. R85447Initial Insulation ResistanceBetween Mutually Insulated Elements: 1,000M ohms min. @ 500VDC.Mechanical DataTermination: Printed circuit terminals with quick connect terminals.Enclosure (94V-0 Flammability Ratings):OMIF-S: Vented (Flux-tight) plastic cover.Weight: 0.53 oz (15g) approximately.Operate DataMust Operate Voltage: 75% of nominal voltage or less.Must Release Voltage: 5% of nominal voltage or more.Operate Time: 20 ms max.Release Time: 10 ms max.Environmental DataTemperature Range:Operating:-30°C to +70°CVibration, Mechanical: 10 to 55 Hz., 1.5mm double amplitudeOperational: 10 to 55 Hz., 1.5mm double amplitude.Shock, Mechanical: 1,000m/s2 (100G approximately).Operational: 100m/s2 (10G approximately).Operating Humidity: 20 to 85% RH. (Non-condensing).Initial Dielectric StrengthBetween Open Contacts:1,000VAC 50/60 Hz. (1 minute).Between Coil and Contacts: 5,000VAC 50/60 Hz. (1 minute).Surge Voltage Between Coil and Contacts: 10,000V (1.2 / 50µs).Contact Data @ 20°CArrangements: 1 Form A.Material:AgSnOMax. Switching Rate:300 ops./min. (no load).30 ops./min. (rated load).Expected Mechanical Life: 10 million operations (no load).Expected Electrical Life:100,000 operations (rated load).Minimum Load: 100mA @ 5VDC.Initial Contact Resistance: 100 milliohms @ 1A, 6VDC.Contact RatingsRatings:20A @ 125VAC resistive.16A @ 250VAC resistive,16A @ 24VDC resistive.Max. Switched Voltage:AC: 250V.DC: 24V.Max. Switched Current: 20A.Max. Switched Power: 4,000VA, 385W.Coil DataVoltage: 12 to 24VDC.Nominal Power:540mW.Coil Temperature Rise:35°C max., at rated coil voltage.Max. Coil Power: 130% of nominal.Duty Cycle: Continuous.Users should thoroughly review the technical data before selecting a product partnumber. It is recommended that user also seek out the pertinent approvals files ofthe agencies/laboratories and review them to ensure the product meets therequirements for a given application.467Dimensions are shown for reference purposes only.Dimensions are in inches over (millimeters) unless otherwise specified.Specifications and availability subject to change. Technical support:Refer to inside back cover.Note: This data is based on the max. allowable temperature for E type insulation coil (115°C).。

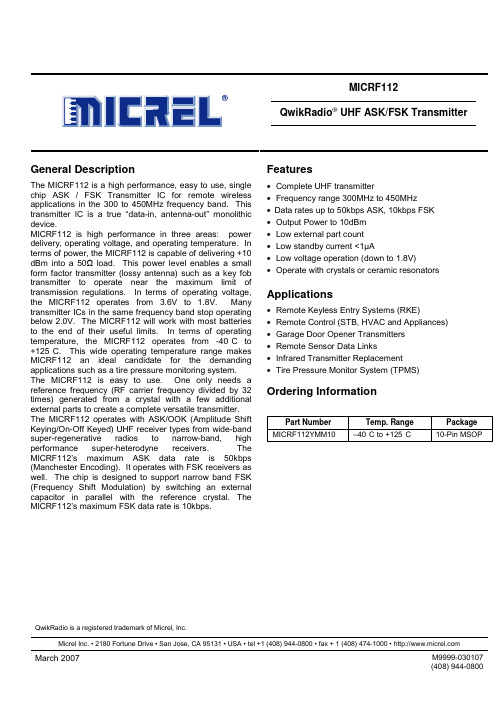

MICRF112中文资料

MICRF112QwikRadio ® UHF ASK/FSK TransmitterQwikRadio is a registered trademark of Micrel, Inc.Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000 • General DescriptionThe MICRF112 is a high performance, easy to use, single chip ASK / FSK Transmitter IC for remote wireless applications in the 300 to 450MHz frequency band. Thistransmitter IC is a true “data-in, antenna-out” monolithicdevice.MICRF112 is high performance in three areas: power delivery, operating voltage, and operating temperature. In terms of power, the MICRF112 is capable of delivering +10dBm into a 50Ω load. This power level enables a smallform factor transmitter (lossy antenna) such as a key fob transmitter to operate near the maximum limit of transmission regulations. In terms of operating voltage, the MICRF112 operates from 3.6V to 1.8V. Manytransmitter ICs in the same frequency band stop operating below 2.0V. The MICRF112 will work with most batteries to the end of their useful limits. In terms of operating temperature, the MICRF112 operates from -40°C to+125°C. This wide operating temperature range makesMICRF112 an ideal candidate for the demanding applications such as a tire pressure monitoring system.The MICRF112 is easy to use. One only needs a reference frequency (RF carrier frequency divided by 32 times) generated from a crystal with a few additional external parts to create a complete versatile transmitter. The MICRF112 operates with ASK/OOK (Amplitude Shift Keying/On-Off Keyed) UHF receiver types from wide-bandsuper-regenerative radios to narrow-band, high performance super-heterodyne receivers. The MICRF112’s maximum ASK data rate is 50kbps (Manchester Encoding). It operates with FSK receivers as well. The chip is designed to support narrow band FSK (Frequency Shift Modulation) by switching an external capacitor in parallel with the reference crystal. The MICRF112’s maximum FSK data rate is 10kbps. Features• Complete UHF transmitter• Frequency range 300MHz to 450MHz • Data rates up to 50kbps ASK, 10kbps FSK• Output Power to 10dBm • Low external part count • Low standby current <1µA • Low voltage operation (down to 1.8V)• Operate with crystals or ceramic resonatorsApplications • Remote Keyless Entry Systems (RKE)• Remote Control (STB, HVAC and Appliances) • Garage Door Opener Transmitters • Remote Sensor Data Links• Infrared Transmitter Replacement• Tire Pressure Monitor System (TPMS)Ordering InformationPart Number Temp. Range Package MICRF112YMM10–40°C to +125°C 10-Pin MSOPMicrel, Inc. MICRF112 Typical ApplicationFigure 1. MICRF112 ASK Key Fob DesignNote: Values in parenthesis are for 315MHzMicrel, Inc. MICRF112Pin ConfigurationXTAL_MODFSKASK XTLIN XTLOUTVSSVDD PAOUT VSSPA EN10-Pin MSOP (M)Pin DescriptionPin Number MSOP-10Pin Name Pin Function 1 ASK ASK DATA Input2 XLIN Reference oscillator input connection.3 XTLOUT Reference oscillator output connection.4 VSS Ground5 XTAL_MODReference oscillation modulation port for FSK operation. 6 FSK FSK Data Input 7 EN Chip enable, active high 8 VSSPA PA Ground 9 PA_OUT PA output10VDDPositive Power SupplyMicrel, Inc. MICRF112Absolute Maximum Ratings (Note 1)Supply Voltage VDD...................................................+5.0V Voltage on PAOUT.....................................................+7.2V Voltage on I/O Pins.............................VSS–0.3 to VDD+0.3 Storage Temperature Range....................-65°C to + 150°C Lead Temperature (soldering, 10 seconds)............+ 300°C ESD Rating................................................................Note 3 Operating Ratings (Note 2)Supply Voltage VDD.........................................1.8V to 3.6V Ambient Operating Temperature (TA).......–40°C to +125°C Programmable Transmitter Frequency Range: .......................................................300MHzto450MHzElectrical Characteristics(Note 4)Specifications apply for VDD = 3.0V, TA = 25°C, Freq REFOSC = 13.560MHz, EN = VDD. Bold values indicate –40°C to 125°C unlessotherwise noted. 1kbps data rate 50% duty cycle. RL 50ohm load (matched)Parameter Condition Min Typ Max UnitsPower SupplyStandby supply current, Iq EN = V SS .05 1µA µA@ 315MHz, P OUT = +10dBm 12.3 mAMark Supply Current I ON@ 433.92MHz, P OUT = +10dBm 12.5 mA@ 315MHz 2 mASPACE supply current, I OFF@ 433.92 MHz 2 mARF Output Section and Modulation Limits:@315MHz, Note 4 10dBm Output power level, P OUTFSK or ASK "mark" @433.92MHz, Note 410 dBm@ 630MHz, Note 4 2nd harm. -39 dBcHarmonics output for 315MHz @945MHz, Note 4 3rd harm. -53 dBc@ 867.84MHz, Note 4 2nd harm. -55 dBcHarmonics output for433.92 MHz @1301.76MHz, Note 4 3rd harm. -55 dBcExtinction ratio for ASK 70 dBcFSK ModulationFrequency Deviation load capacitor = 10pF, crystal type = HC49/U 22 kHzData Rate 10 kbpsASK ModulationData Rate 50 kbps@315MHz, Note 6 <700 kHzOccupied Bandwidth@433.92MHz, Note 6 <1000 kHzVCO Section@ 100kHz from Carrier -76 dBc/Hz315 MHz Single Side BandPhase Noise @ 1000kHz from Carrier -79 dBc/Hz@ 100kHz from Carrier -72 dBc/Hz433.92 MHz Single SideBand Phase Noise @ 1000kHz from Carrier -81 dBc/HzReference Oscillator SectionXTLIN, XTLOUT, XTLMOD Pin capacitance 2 pFExternal Capacitance See Schematic C17 & C18 18 pFOscillator Startup Time Note 5Crystal: HC49S 300 µsDigital / Control SectionOutput Blanking STDBY transition from LOW to HIGH 500 µsMicrel, Inc. MICRF112Electrical Characteristics (cont.)Parameter Condition Min Typ Max UnitsHigh (V IH ) 0.8×V DDVDigital Input (EN, ASK and FSK)Low (V IL )0.2×V DDVHigh (V IH ) 0.05 µADigital Input Leakage Current(EN, ASK and FSK Pins) Low (V IL )0.05 µA Under Voltage Lock Out (UVLO)1.6 VNote 1. Exceeding the absolute maximum rating may damage the device. Note 2. The device is not guaranteed to function outside its operating rating.Note 3. Devices are ESD sensitive. Handling precautions recommended. Human body model, 1.5k in series with 100pF. Note 4. Measured using Test Circuit in Figure 2. Note 5. Dependent on crystalNote 6. RBW = 100kHz, OBW measured at -20dBc.Micrel, Inc. MICRF112 Test CircuitFigure 2. MICRF112 Test Circuit with 50Ω OutputNote 1. Values without parenthesis are for 433.92 MHz and values in parenthesis are for 315MHzNote 2. C9 = 100pF for external REF-OSCNote 3. For FSK R1 = 0Ω, R2 = NP, R6 = 100k, and R5 = NPMicrel, Inc. MICRF112Assembly Drawing MICRF112 50 Ohm Test BoardTop LayerMICRF112 50 Ohm Test BoardBottom LayerMICRF112 50 Ohm Test BoardMicrel, Inc. MICRF112Typical Characteristics Using MICRF112, 50Ω test Board315MHz OBW, ASK = 1kHz315Mhz OBW, ASK = 50kHzCW Max Power @ 3V, 315MHz,ASK = 1kHz, Note 1RF Spectrum 2ndHarmonic;Fundamental at 315 MHzRF Spectrum 3rdHarmonic;Fundamental at 315 MHz315MHz, Power Level at Space,VDD = 3.0V, ASK = 1kHzNote 1. 1.2dB cable loss.Micrel, Inc. MICRF112315MHz, Zero Span , ASK = 1kHz315MHz, Zero Span, ASK = 50kHz315MHz, Phase Noise, ASK = 1kHz,100kHz Offset, –75.59dBc/Hz315MHz, Phase Noise, ASK = 1khz,1MHz Offset, –78.99dBc/Hz315MHz, Phase Noise, ASK = CW,100kHz Offset, –74.39dBc/Hz315MHz, Phase Noise, ASK = CW,1MHz Offset, –77.28dBc/HzMicrel, Inc. MICRF112433.92MHz OBW, ASK = 1kHz433.92MHz OBW, ASK = 50kHz433.92MHz, CW Max Power @ 3V,ASK = 1kHz, Note 1RF Spectrum 2ndHarmonic;Fundamental at 433.92 MHzRF Spectrum 3rdHarmonic;Fundamental at 433.92 MHz433.92MHz Power Level at Space,VDD = 3.0V, ASK = 1kHzNote 1. 1.3dB cable loss.Micrel, Inc. MICRF112433.92MHz Zero Span, 1kHz433.92ASK Zero Span at 50kHz433.92MHz Phase Noise, ASK = CW,100kHz Offset, –81.04dBc/Hz433.92MHz Phase Noise, ASK = CW,1MHz Offset, –78.76dBc/Hz433.92MHz Phase Noise, ASK = 1kHz,100kHz Offset, –71.73dBc/Hz433.92MHz Phase Noise, ASK = 1kHz,1MHz Offset, –81.04dBc/HzMicrel, Inc. MICRF112 Functional DiagramFigure 3. Functional Block Diagram MICRF112 10 Pin ASK / FSK VersionFunctional DescriptionFigure 3 shows a functional block diagram of the MICRF112 transmitter. The MICRF112 can be best described as a phase locked transmitter. The system can be partitioned into six functional blocks; crystal oscillator, PLL×32, power amplifier, enable control, under voltage detect and open drain switch for FSK operation.Crystal OscillatorThe reference oscillator is crystal-based Pierce configuration. It is designed to accept crystals with frequency from 9.375MHz to 14.0625MHz.Crystal Oscillator Parameters for ASK Operation Figure 4 shows a reference oscillator circuit configuration for ASK operation. The reference oscillator is capable of driving crystals with ESR range from 20Ωto 300Ω.When the ESR of crystal is at 20Ω, the crystal parameter limits are:ESR 20ΩC PAR 2 to 10pFC MO10 to 40fFFigure 4. Reference Oscillator ASK OperationWhen the ESR of crystal is at 300Ω, the crystal parameter limits are:ESR 300ΩC PAR 2 to 5pFC MO10 to 40fFC LOAD10 to 30pFMicrel, Inc. MICRF112Crystal Oscillator for FSK OperationFigure 5 shows reference oscillator circuit configuration for FSK operation. To operate the MICRF112 in FSK mode, one additional capacitor is needed between XTALOUT pin and XTALMOD pin. Crystal parameters for FSK operation are the same as ASK operation except:•When the ESR of crystal is at 20Ω, C FSK + C LOAD not to exceed 70pF.•When the ESR of crystal is at 300Ω, C FSK +C LOAD not to exceed 30pFFigure 5. Reference Oscillator FSK OperationPLL ×32The function of PLL×32 is to provide a stable carrier frequency for transmission. It is a “divided by 32” phase locked oscillator. Power AmplifierThe power amplifier serves two purposes: 1) to buffer the VCO from external elements and 2) to amplify the phase locked signal. The power amplifier can produce +10dBm at 3V (typical).Enable ControlEnable control gates the ASK data. It only allows transmission when Lock, Amplitude and Under Voltage Detect conditions are valid.Under Voltage Detect“Under voltage detect” block senses operating voltage. If the operating voltage falls below 1.6V, “under voltage detect” block will send a signal to “enable control” block to disable the PA.Open Drain SwitchOpen drain switch is used for FSK operation. FSK data is fed into the FSK pin. The FSK pin is connected to the gate of the open drain switch. The open collector is connected to the XTALMOD pin. In Figure 4, a capacitor is shown connected from XTALMOD pin to XTALOUT. When FSK pin goes high, the capacitor between XTALMOD and XTALOUT pulls the frequency of REFOSC low .Micrel, Inc. MICRF112Application InformationFigure 6. ASK 433.92MHz and 315MHzNote: Values in parenthesis are for 315MHzThe MICRF112 is well suited to drive a 50 ohms source, monopole or a loop antenna. Figure 6 is an example of a loop antenna configuration. Figure 6 also shows both 315MHz and 433.92MHz ASK configurations for a loop antenna. Besides using a different crystal, Table 1 lists modified values needed for the listed frequencies.Frequency (MHz) L1 (nH)C5 (pF)L4 (nH)C7 (pF)Y1 (MHz)315.0470 10 150 6.8 9.84375433.92 680 10 82 4.7 13.5600Table 1The reference design shown in Figure 6 has an antenna optimized for using the matching network as described in Table 1.Power Control Using External ResistorR7 is used to adjust the RF output levels which may be needed to meet compliance. As an example, the following tables list typical values of conducted RF output levels and corresponding R7 resistor values for the 50Ω test board shown in Figure 2. R7 of the TX112 Demo board using the loop antenna can be adjusted for the appropriate radiated field allowed by FCC or ETSI compliance. Contact Micrel for suggested values to meet FCC and ETSI compliances.R7, ΩOutput Power, dBmIDD, mA 0 10 6.7 75 8.5 6.3 100 8.0 6.2 500 1.6 4.13 1000 -3.84.87Output Power Versus External Resistor at 315MHzR7, ΩOutput Power, dBmIDD, mA 0 8.68 7.5 75 8.34 7.33 100 8.02 7.3 500 4.34 6.3 1000 0.425.5Output Power Versus External Resistor at 433.92 MHzMicrel, Inc. MICRF112Output Matching NetworkPart of the function of the output network is to attenuate the second and third harmonics. When matching to a transmit frequency, care must be taken not only to optimize for maximum output power but to attenuate unwanted harmonics.Layout IssuesPCB Layout is of primary concern to achieve optimum performance and consistent manufacturing results. Care must used on orientation of components to ensure they do not couple or decouple the RF signal. PCB trace length should be short to minimize parasitic inductance, (1 inch ~ 20nH). For example, depending on inductance values, a 0.5 inch trace can change the inductance by as much as 10%. To reduce parasitic inductance, the use of wide traces and a ground plane under signal traces is recommended. Vias with low value inductance should be used for components requiring a connection-to-ground. Antenna LayoutDirectivity is affected by antenna trace layout. No ground plane should be under the antenna trace. For consistent performance, components should not be placed inside the loop of the antenna. Gerbers for Figure 7, with a suggested layout, can be obtained on the Micrel web site at: .Micrel, Inc. MICRF112 PCB BoardAssembly Drawing MICRF112 Demo BoardTop Layer MICRF112 Demo BoardBottom LayerMICRF112 Demo BoardFigure 7. Demo Board PCBMicrel, Inc. MICRF112Figure 8. TX112-1 Demo Board SchematicNote: Configuration is for ASK operation. Values in parenthesis are for 315MHzMicrel, Inc. MICRF112Functional Description of TX112-1 Evaluation Board.Figure 7 shows the TX112-1 Demo Board PCB. Figure 8 is a detailed schematic of the TX112-1. Note that components labeled as NP are to obtain different configurations including FSK Mode of operation. Table 2 describes each header pin connector used in the demo board.Pin Function Name Functional DescriptionJ1-1 VDD 1.8Vto3.6VJ1-2 Ground VSSJ1-3 ASK INPUT Modulating Data Input, ASK or FSKJ2-1 REF-OSC External Reference InputJ2-2 GROUND VSSJ2-3 ENABLE Enable Input, Active HighTX112-1-433.92 ASK Bill of MaterialsItem Quantity Ref PartPCBFootprint Mfg P/N Manufacturer1 1 C1 10µF 0805 GRM21BR60J106KE01L muRata2 1 C2 100pF 0603GRM1885C1H101JA01D muRata 3 1 C5 10pF 0603GRM1885C1H100JA01D muRata4 3 R1,R4,R6 (np)5 5 C6,C8,C11,C12,C15 (np)6 1 C7 4.7pF 0603GRM1885C1H4R7JA01D muRata 7 1 C10 0.1µF 0603GRM188F51H104ZA01D muRata 8 2 C13,C14 18pF 0603GRM1885C1H180JA01D muRata9 2 J1,J2 CON3 TSHR-114-S-02-A-GT10 1 L1 680nH 0805 0805CS-680XJB Coilcraft11 1 L4 82nH 0603 0603CS-082NXJB Coilcraft12 1 L5 ANTENNA ANTENNA LOOP, Part ofPCB13 1 R2 100kΩ 0603CRCW0603100KFKEAVishay14 6R3,R5,R7R8,JPR1,JPR2 0Ω 0603CRC06030000Z0EAVishay13 1 U1 MICRF112YMM10MICRF112YM Micrel14 1 Y1 13.560MHZ XTAL SA-13.5600-F-10-C-3-3 HIBTable 2Micrel, Inc. MICRF112 Tx112-1-315MHz ASK Bill of MaterialsItem Quantity Ref PartPCBFootprint Mfg P/N Manufacturer1 1 C1 10µF 0805 GRM21BR60J106KE01L muRata2 1 C2 100pF 0603 GRM1885C1H101JA01D muRata3 1 C5 10pF 0603GRM1885C1H1000JA01D muRata4 3 R1,R4,R6 (np)5 5 C6,C8,C11,C12,C15 (np)6 1 C7 4.7pF 0603GRM1885C1H6R8JA01D muRata7 1 C10 0.1µF 0603 GRM188F51H104ZA01D muRata8 2 C13,C14 18pF 0603 GRM1885C1H180JA01D muRata9 2 J1,J2 CON3 TSHR-114-S-02-A-GT10 1 L1 470nH 0805 0805CS-470XJB Coilcraft11 1 L4 150nH 0603 0603CS-R15XJB Coilcraft12 1 L5 ANTENNA ANTENNA LOOP, Part ofPCB13 1 R2 100kΩ 0603CRCW0603100KFKEAVishay14 6R3,R5,R7R8,JPR1,JPR2 0Ω 0603CRC06030000Z0EAVishay13 1 U1 MICRF112YMM10MICRF112YM Micrel14 1 Y1 9.84375MHZXTALSA-9.84375-F-10-C-3-3HIB Table 3FSK OperationTable 2 and 3 describe the ASK operation for 433.92MHz and 315MHz.Table 4 lists the component values that change between ASK or FSK operation. Please note that use of a high FSK data rate may excite parasitic resonant modes with some crystal types. Recommended crystals from Table 2 and 3 are good for both ASK and FSK.ModeR1 R2 R5 R6 JPR1JPR2 C8ASK NP 100kΩ0Ω NP 0Ω NP NPFSK 0ΩNP NP 100kΩ NP 0Ω (1)3.3pF(2)10pFNotes:1. C8 = 3.3pF for 1kHz using HC49/U or HC49US type crystals.2. C8= 10pF for 10kHz using HC49/U, (high profile) only.Table 4: ASK and FSK SettingsR3 R4Constant ON 0Ω NPExternal Standby Control NP 100kΩTable 5: Enable Control (Shutdown)Micrel, Inc. MICRF112 Package Information10-Pin MSOP Package Type (YMM10)。

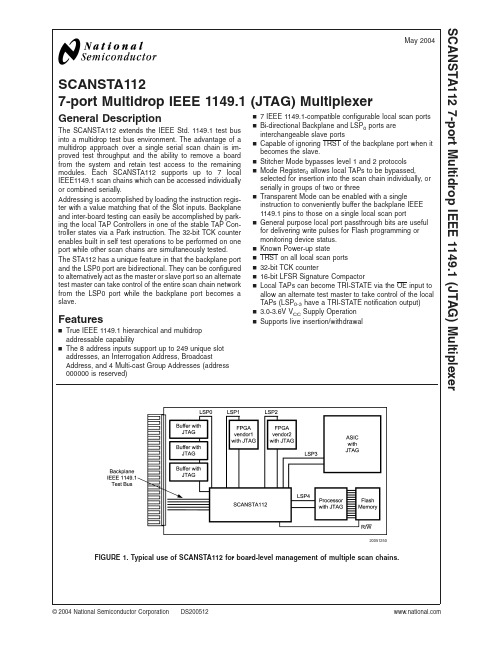

SCANSTA112中文资料

SCANSTA1127-port Multidrop IEEE 1149.1(JTAG)MultiplexerGeneral DescriptionThe SCANSTA112extends the IEEE Std.1149.1test bus into a multidrop test bus environment.The advantage of a multidrop approach over a single serial scan chain is im-proved test throughput and the ability to remove a board from the system and retain test access to the remaining modules.Each SCANSTA112supports up to 7local IEEE1149.1scan chains which can be accessed individually or combined serially.Addressing is accomplished by loading the instruction regis-ter with a value matching that of the Slot inputs.Backplane and inter-board testing can easily be accomplished by park-ing the local TAP Controllers in one of the stable TAP Con-troller states via a Park instruction.The 32-bit TCK counter enables built in self test operations to be performed on one port while other scan chains are simultaneously tested.The STA112has a unique feature in that the backplane port and the LSP0port are bidirectional.They can be configured to alternatively act as the master or slave port so an alternate test master can take control of the entire scan chain network from the LSP0port while the backplane port becomes a slave.Featuresn True IEEE 1149.1hierarchical and multidrop addressable capabilityn The 8address inputs support up to 249unique slot addresses,an Interrogation Address,BroadcastAddress,and 4Multi-cast Group Addresses (address 000000is reserved)n 7IEEE 1149.1-compatible configurable local scan ports n Bi-directional Backplane and LSP 0ports are interchangeable slave portsn Capable of ignoring TRST of the backplane port when it becomes the slave.n Stitcher Mode bypasses level 1and 2protocols n Mode Register 0allows local TAPs to be bypassed,selected for insertion into the scan chain individually,or serially in groups of two or threen Transparent Mode can be enabled with a singleinstruction to conveniently buffer the backplane IEEE 1149.1pins to those on a single local scan portn General purpose local port passthrough bits are useful for delivering write pulses for Flash programming or monitoring device status.n Known Power-up staten TRST on all local scan ports n 32-bit TCK countern 16-bit LFSR Signature Compactorn Local TAPs can become TRI-STATE via the OE input to allow an alternate test master to take control of the local TAPs (LSP 0-3have a TRI-STATE notification output)n 3.0-3.6V V CC Supply Operation n Supports live insertion/withdrawal20051250FIGURE 1.Typical use of SCANSTA112for board-level management of multiple scan chains.May 2004SCANSTA1127-port Multidrop IEEE 1149.1(JTAG)Multiplexer©2004National Semiconductor Corporation IntroductionThe SCANSTA112is the third device in a series that enable multi-drop address and multiplexing of IEEE-1149.1scan chains.The SCANSTA112is a superset of its predecessors -the SCANPSC110and the SCANSTA111.The STA112has all features and functionality of these two previous devices.The STA112is essentially a support device for the IEEE 1149.1standard.It is primarily used to partition scan chains into managable sizes,or to isolate specific devices onto a seperate chain (Figure 1).The benefits of multiple scan chains are improved fault isolation,faster test times,faster programiing times,and smaller vector sets.In addition to scan chain partitioning,the device is also addressable for use in a multidrop backplane environment (Figure 2).In this configuration,multiple IEEE-1149.1acces-sible cards with an STA112on board can utilize the same backplane test bus for system-level IEEE-1149.1access.This approach facilitates a system-wide commitment to structural test and programming throughout the entire sys-tem life sycle.ArchitectureFigure 3shows the basic architecture of the ’STA112.The device’s major functional blocks are illustrated here.The TAP Controller,a 16-state state machine,is the central control for the device.The instruction register and various test data registers can be scanned to exercise the various functions of the ’STA112(these registers behave as defined in IEEE Std.1149.1).The ’STA112selection controller provides the functionality that allows the 1149.1protocol to be used in a multi-drop environment.It primarily compares the address input to the slot identification and enables the ’STA112for subsequent scan operations.The Local Scan Port Network (LSPN)contains multiplexing logic used to select different port configurations.The LSPN control block contains the Local Scan Port Controllers (LSPC)for each Local Scan Port (LSP 0,LSP 1...LSP n ).This control block receives input from the ’STA112instruction register,mode registers,and the TAP controller.Each local port contains all four boundary scan signals needed to inter-face with the local TAPs plus the optional Test Reset signal (TRST).The TDI/TDO Crossover Master/Slave logic is used to define the bidirectional B0and B1ports in a Master/Slave configuration.20051251FIGURE 2.Example of SCANSTA112in a multidrop addressable backplane.S C A N S T A 112 2SCANSTA112 Array20051202FIGURE3.SCANSTA112Block Diagram3Connection Diagrams20051201(BGA Top view)S C A N S T A 112 4SCANSTA112 Connection Diagrams(Continued)20051260TQFP pinout5TABLE 1.Pin DescriptionsPin Name DescriptionNo.Pins I/O VCC 10N/A Power GND 10N/A GroundRESET 1I RESET Input:will force a reset of the device regardless of the current state.ADDMASK 1I ADDRESS MASK input:Allows masking of lower slot input pins.MPsel B1/B01I MASTER PORT SELECTION:Controls selection of LSP B0or LSP B1as the backplane port.The unselected port becomes LSP 00.A value of "0"will select LSP B0as the master port.SB/S 1I Selects ScanBridge or Stitcher Mode.LSPsel (0-6)7I In Stitcher Mode these inputs define which LSP’s are to be included in the scan chain TRANS1ITransparent Mode enable input:The value of this pin is loaded into the TRANSENABLE bit of the control register at power-up.This value is used to control the presence of registers and pad-bits in the scan chain while in the stitcher mode.TLR_TRST 1ISets the driven value of TRST 0-5when LSP TAPs are in TLR and the device is not being reset.During RESET ="0"or TRST B ="0"(IgnoreReset ="0")TRST n ="0".This pin is to be tied low to match the function of the SCANSTA111TLR_TRST 61I This pin affects TRST of LSP 6only.This pin is to be tied low to match the function of the SCANSTA111TDI B0,TDI B12IBACKPLANE TEST DATA INPUT:All backplane scan data is supplied to the ’STA112through this input pin.MPsel B1/B0determines which port is the master backplane port and which is LSP 00.This input has a 25K Ωinternal pull-up resistor and no ESD clamp diode (ESD is controlled with an alternate method).When the device is power-off (V DD floating),this input appears to be a capacitive load to ground (Note 1).When V DD =0V (i.e.;notfloating but tied to V SS )this input appears to be a capacitive load with the pull-up to ground.TMS B0,TMS B12I/OBACKPLANE TEST MODE SELECT:Controls sequencing through the TAP Controller of the ’STA112.Also controls sequencing of the TAPs which are on the local scan chains.MPsel B1/B0determines which port is the master backplane port and which is LSP 00.This bidirectional TRISTATE pin has 24mA of drive current,with a 25K Ωinternal pull-up resistor and no ESD clamp diode (ESD is controlled with an alternate method).When the device is power-off (V DD floating),this input appears to be a capacitive load to ground (Note 1).When V DD =0V (i.e.;not floating but tied to V SS )this input appears to be a capacitive load with the pull-up to ground.TDO B0,TDO B12I/OBACKPLANE TEST DATA OUTPUT:This output drives test data from the ’STA112and the local TAPs,back toward the scan master controller.This bidirectional TRISTATE pin has 12mA of drive current.MPsel B1/B0determines which port is the master backplane port and which is LSP 00.Output is sampled during interrogation addressing.When the device is power-off (V DD =0V or floating),this output appears to be a capacitive load (Note 1).TCK B0,TCK B12I/OTEST CLOCK INPUT FROM THE BACKPLANE:This is the master clock signal that controls all scan operations of the ’STA112and of the local scan ports.MPsel B1/B0determines which port is the master backplane port and which is LSP 00.These bidirectional TRISTATE pins have 24mA of drive current with hysterisis.This input has no pull-up resistor and no ESD clamp diode (ESD is controlled with an alternate method).When the device is power-off (V DD floating),this input appears to be a capacitive load to ground (Note 1).When V DD =0V (i.e.;not floating but tied to V SS )this input appears to be a capacitive load to ground.TRST B0,TRST B12I/OTEST RESET:An asynchronous reset signal (active low)which initializes the ’STA112logic.MPsel B1/B0determines which port is the master backplane port and which is LSP 00.This bidirectional TRISTATE pin has 24mA of drive current,with a 25K Ωinternal pull-up resistor and no ESD clamp diode (ESD is controlled with an alternate method).When the device is power-off (V DD floating),this pin appears to be a capacitive load to ground (Note 1).When V DD =0V (i.e.;not floating but tied to V SS )this input appears to be a capacitive load with the pull-up to ground.S C A N S T A 112 6TABLE 1.Pin Descriptions(Continued)Pin Name DescriptionNo.Pins I/O TRIST B0,TRIST B12OBACKPLANE TRI-STATE NOTIFICATION OUTPUT:This signal is high when the backplane scan port is TRI-STATEd.This pin is used for backplane physical layer changes (i.e.;TTL to LVDS).This TRISTATE output has 12mA of drive current.MPsel B1/B0determines which port is the master backplane port and which is LSP 00.A0B0,A1B0,A0B1,A1B14IBACKPLANE PASS-THROUGH INPUT:A general purpose input which is driven to the Y n of a single selected LSP.(Not available when multiple LSPs are selected).This input has a 25K Ωinternal pull-up resistor.MPsel B1/B0determines which port is the master backplane port and which is LSP 00.Y0B0,Y1B0,Y0B1,Y1B14OBACKPLANE PASS-THROUGH OUTPUT:A general purpose output which is driven from the A n of a single selected LSP.(Not available when multiple LSPs are selected).ThisTRISTATE output has 12mA of drive current.MPsel B1/B0determines which port is the master backplane port and which is LSP 00.S (0-7)8I SLOT IDENTIFICATION:The configuration of these pins is used to identify (assign a unique address to)each ’STA112on the system backplaneOE1IOUTPUT ENABLE for the Local Scan Ports,active low.When high,this active-low control signal TRI-STATEs all local scan ports on the ’STA112,to enable an alternate resource to access one or more of the local scan chains.TDO (01-06)6O TEST DATA OUTPUTS:Individual output for each of the local scan ports .These TRISTATE outputs have 12mA of drive current.TDI (01-06)6I TEST DATA INPUTS:Individual scan data input for each of the local scan ports.This input has a 25K Ωinternal pull-up resistor.TMS (01-06)6OTEST MODE SELECT OUTPUTS:Individual output for each of the local scan ports.TMS n does not provide a pull-up resistor (which is assumed to be present on a connected TMS input,per the IEEE 1149.1requirement).These TRISTATE outputs have 24mA of drive current.TCK (01-06)6O LOCAL TEST CLOCK OUTPUTS:Individual output for each of the local scan ports.These are buffered versions of TCK B .These TRISTATE outputs have 24mA of drive current.TRST (01-06)6O LOCAL TEST RESETS:A gated version of TRST B .These TRISTATE outputs have 24mA of drive current.A001,A1012ILOCAL PASS-THROUGH INPUTS:General purpose inputs which can be driven to thebackplane pin Y B .(Only on LSP 0and LSP 1.Only available when a single LSP is selected).These inputs have a 25K Ωinternal pull-up resistor.Y001,Y1012OLOCAL PASS-THROUGH OUTPUT:General purpose outputs which can be driven from the backplane pin A B .(Only on LSP 0and LSP 1.Only available when a single LSP is selected).These TRISTATE outputs have 12mA of drive current.TRIST (01-03)3OLOCAL TRI-STATE NOTIFICATION OUTPUTS:This signal is high when the local scan ports are TRI-STATEd .These pins are used for backplane physical layer changes (i.e.;TTL to LVDS).These TRISTATE outputs have 12mA of drive current.Note 1:Refer to the IBIS model on our website for I/O characteristics.Application OverviewADDRESSING SCHEME -The SCANSTA112architecture extends the functionality of the IEEE 1149.1Standard by supplementing that protocol with an addressing scheme which allows a test controller to communicate with specific ’STA112s within a network of ’STA112s.That network can include both multi-drop and hierarchical connectivity.In ef-fect,the ’STA112architecture allows a test controller to dynamically select specific portions of such a network for participation in scan operations.This allows a complex sys-tem to be partitioned into smaller blocks for testing purposes.The ’STA112provides two levels of test-network partitioningcapability.First,a test controller can select individual ’STA112s,specific sets of ’STA112s (multi-cast groups),or all ’STA112s (broadcast).This ’STA112-selection process is supported by a Level-1communication protocol.Second,within each selected ’STA112,a test controller can select one or more of the chip’s seven local scan-ports.That is,individual local ports can be selected for inclusion in the (single)scan-chain which a ’STA112presents to the test controller.This mechanism allows a controller to select spe-cific scan-chains within the overall scan network.The port-selection process is supported by a Level-2protocol.HIERARCHICAL SUPPORT -Multiple SCANSTA112’s can be used to assemble a hierarchical boundary-scan tree.InSCANSTA1127Application Overview(Continued)such a configuration,the system tester can configure the local ports of a set of ’STA112s so as to connect a specific set of local scan-chains to the active scan ing this capability,the tester can selectively communicate with spe-cific portions of a target system.The tester’s scan port is connected to the backplane scan port of a root layer of ’STA112s,each of which can be selected using multi-drop addressing.A second tier of ’STA112s can be connected to this root layer,by connecting a local port (LSP)of a root-layer ’STA112to the backplane port of a second-tier ’STA112.This process can be continued to construct a multi-level scan hierarchy.’STA112local ports which are not cas-caded into higher-level ’STA112s can be thought of as the terminal leaves of a scan tree.The test master can select one or more target leaves by selecting and configuring the local ports of an appropriate set of ’STA112s in the test tree.STANDARD SCANBRIDGE MODE -ScanBridge mode re-fers to functionality and protocol that has been used by National since the introduction of the PSC110in 1993.This functionality consists of a multidrop addressable IEEE1149.1switch.This enables one (or more)device to be selected from many that are connected to a parallel IEEE1149.1bus or backplane.The second function that ScanBridge mode accomplishes is to act as a mux for multiple IEEE1149.1local scan chains.The Local Scan Ports (LSP)of the device creates a connection between one or more of the local scan chains to the backplane bus.To accomplish this functionality the ScanBridge has two levels of protocol and an operational mode.Level 1protocolrefers to the required actions to address/select the desired ScanBridge.Level 2protocol is required to configuring the mux’ing function and enable the connection (UNPARK)be-tween the local scan chain and the backplane bus via an LSP .Upon completion of level 1and 2protocols the Scan-Bridge is prepared for its operational mode.This is where scan vectors are moved from the backplane bus to the desired local scan chain(s).STITCHER MODE -Stitcher Mode is a method of skipping level 1and 2protocol of the ScanBridge mode of operation.This is accomplished via external pins.When in stitcher mode the SCANSTA112will go directly to the operational mode.TRANSPARENT MODE -Transparent mode refers to a condition of operation in which there are no pad-bits or SCANSTA112registers in the scan chain.The Transparent mode of operation is available in both ScanBridge and Stitcher modes.Only the activation method differs.Once transparent mode has been activated there is no difference in operation.Transparent mode allows for the use of vectors that have been generated for a chain where these bits were not included.Check with your ATPG tool vendor to ensure support of these features.For details regarding the internal operation of the SCAN-STA112device,refer to applications note AN-1259SCAN-STA112Designers Reference.S C A N S T A 112 8Absolute Maximum Ratings(Note2) Supply Voltage(V CC)−0.3V to+4.0V DC Input Diode Current(I IK)V I=−0.5V−20mA DC Input Voltage(V I)−0.5V to+3.9V DC Output Diode Current(I OK)V O=−0.5V−20mA DC Output Voltage(V O)−0.3V to+3.9V DC Output Source/Sink Current(I O)±50mA DC V CC or Ground Current±50mA per Output PinDC Latchup Source or Sink Current±300mA Junction Temperature(Plastic)+150˚C Storage Temperature−65˚C to+150˚C Lead Temperature(Solder,4sec)100L FBGA220˚C 100L TQFP220˚C Max Package Power Capacity@25˚C100L FBGA 3.57W 100L TQFP 2.11W Thermal Resistance(θJA)100L FBGA35˚C/W 100L TQFP59.1˚C/W Package Derating above+25˚C100L FBGA28.57mW/˚C 100L TQFP16.92mW/˚C ESD Last Passing Voltage(HBM Min)2500V Recommended Operating ConditionsSupply Voltage(V CC)’STA112 3.0V to3.6V Input Voltage(V I)0V to V CC Output Voltage(V O)0V to V CC Operating Temperature(T A)Industrial−40˚C to+85˚C Note2:Absolute maximum ratings are those values beyond which damage to the device may occur.The databook specifications should be met,without exception,to ensure that the system design is reliable over its power supply, temperature,and output/input loading variables.National does not recom-mend operation of SCAN STA products outside of recommended operation conditions.DC Electrical CharacteristicsOver recommended operating supply voltage and temperature ranges unless otherwise specifiedSymbol Parameter Conditions Min Max UnitsV IH Minimum High Input Voltage V OUT=0.1V or 2.1VV CC−0.1VV IL Maximum Low Input Voltage V OUT=0.1V or0.8VV CC−0.1VV OH Minimum High Output Voltage I OUT=−100µA V CC-0.2v V All Outputs and I/O Pins V IN=V IH or V ILV OH Minimum High Output Voltage I OUT=−12mA 2.4V TDO B0,TDO B1,TRIST B0,TRIST B1,Y0B0,Y1B0,Y0B1,Y1B1,TDO(01-06),Y001,Y101,TRIST(01-03)All Outputs LoadedV OH Minimum High Output Voltage I OUT=−24mA 2.2V TMS B0,TMS B1,TCK B0,TCK B1,TRST B0,TRST B1,TMS(01-06),TCK(01-06),TRST(01-06)V OL Maximum Low Output Voltage I OUT=+100µA0.2V All Outputs and I/O Pins V IN=V IH or V ILV OL Maximum Low Output Voltage I OUT=+12mA0.4V TDO B0,TDO B1,TRIST B0,TRIST B1,Y0B0,Y1B0,Y0B1,Y1B1,TDO(01-06),Y001,Y101,TRIST(01-03)V OL Maximum Low Output Voltage I OUT=+24mA0.55V TMS B0,TMS B1,TCK B0,TCK B1,TRST B0,TRST B1,TMS(01-06),TCK(01-06),TRST(01-06)VIKL Maximum Input Clamp Diode Voltage IIK=-18mA-1.2VI IN Maximum Input Leakage Current V IN=V CC or GND±5.0µA(non-resistor input pins)SCANSTA1129DC Electrical Characteristics(Continued)Over recommended operating supply voltage and temperature ranges unless otherwise specifiedSymbol ParameterConditionsMin Max Units I ILRInput Current LowV IN =GND-45-200µA(Input and I/O pins with pull-up resistors:TDI B0,TDI B1,TMS B0,TMS B1,TRST B0,TRST B1,A0B0,A1B0,A0B1,A1B1,TDI (01-06),A001,A101)I IHInput High Current(Input and I/O pins with pull-up resistors:TDI B0,TDI B1,TMS B0,TMS B1,TRST B0,TRST B1,A0B0,A1B0,A0B1,A1B1,TDI (01-06),A001,A101)V IN =V CC5.0µAI OFFPower-off Leakage CurrentOutputs and I/O pins without pull-up resistors V CC =0V,V IN =3.6V (Note 3)±5.0µA Outputs and I/O pins with pull-up resistors±200µA I OZ Maximum TRI-STATE Leakage Current ±5.0µAOutputs and I/O pins without pull-up resistors I CC Maximum Quiescent Supply Current V IN =V CC or GND 3.8mA I CCDMaximum Dynamic Supply CurrentV IN =V CC or GND,Input Freq =25MHz68mANote 3:Guaranteed by equivalent test method.AC Electrical Characteristics:Scan Bridge ModeOver recommended operating supply voltage and temperature ranges unless otherwise specified (Note 5).Symbol Parameter Conditions Typ Max Units t PHL ,Propagation Delay 8.513.5ns t PLH TCK B0to TDO B0or TDO B1t PHL ,Propagation Delay 8.514.0ns t PLH TCK B1to TDO B0or TDO B1t PHL ,Propagation Delay 7.512.5ns t PLH TCK B0to TDO (01-06)t PHL ,Propagation Delay 7.513.0ns t PLH TCK B1to TDO (01-06)t PHL ,Propagation Delay 8.012.0ns t PLH TMS B0to TMS B1t PHL ,Propagation Delay 8.012.0ns t PLH TMS B1to TMS B0t PHL ,Propagation Delay 8.012.0ns t PLH TMS B0to TMS (01-06)t PHL ,Propagation Delay 8.012.0ns t PLH TMS B1to TMS (01-06)t PHL ,Propagation Delay 8.012.0ns t PLH TCK B0to TCK B1t PHL ,Propagation Delay 8.012.0ns t PLH TCK B1to TCK B0t PHL ,Propagation Delay 7.512.0ns t PLH TCK B0to TCK (01-06)t PHL ,Propagation Delay 7.512.0ns t PLH TCK B1to TCK (01-06)t PHL ,Propagation Delay 11.518.0ns t PLH TCK B0to TRST B1t PHL ,Propagation Delay 11.518.0nst PLHTCK B1to TRST B0S C A N S T A 11210SCANSTA112 AC Electrical Characteristics:Scan Bridge Mode(Continued)Over recommended operating supply voltage and temperature ranges unless otherwise specified(Note5).Symbol Parameter Conditions Typ Max Unitst PHL,Propagation Delay12.018.5nst PLH TCK B0to TRST(01-06)t PHL,Propagation Delay12.018.5nst PLH TCK B1to TRST(01-06)t PHL Propagation Delay8.512.5ns TCK Bn to TRIST Bnt PHL Propagation Delay8.012.0ns TCK Bn to TRIST(01-03)t PZL,Propagation Delay9.014.5nst PZH TCK Bn to TDO Bn or TDO(01-06)t PHL,Propagation Delay 6.09.0nst PLH An to YnAC Timing Characteristics:Scan Bridge ModeOver recommended operating supply voltage and temperature ranges unless otherwise specified(Notes4,5).Symbol Parameter Conditions Min Max Unitst S Setup Time 2.5ns TMS Bn to TCK Bnt H Hold Time 1.5ns TMS Bn to TCK Bnt S Setup Time 3.0ns TDI Bn to TCK Bnt H Hold Time 2.0ns TDI Bn to TCK Bnt S Setup Time 1.0ns TDI(01-06)to TCK Bnt H Hold Time 3.5ns TDI(01-06)to TCK Bnt REC Recovery Time 1.0ns TCK Bn from TRST Bnt W Clock Pulse Width t R/t F=1.0ns10.0ns TCK Bn(H or L)t W L Reset Pulse Width t R/t F=1.0ns 2.5ns TRST Bn(L)F MAX Maximum Clock Frequency(Note6)t R/t F=1.0ns25MHzNote4:Guaranteed by Design(GBD)by statistical analysisNote5:R L=500Ωto GND,C L=50pF to GND,t R/t F=2.5ns,Frequency=25MHz,V M=1.5VNote6:When sending vectors one-way to a target device on an LSP(such as in FPGA/PLD configuration/programming),the clock frequency may be increased above this specification.In Scan Mode(expecting to capture returning data at the LSP),the F MAX must be limited to the above specification.11AC Electrical Characteristics:Stitcher Transparent ModeOver recommended operating supply voltage and temperature ranges unless otherwise specified (Note 5).Symbol ParameterConditionsTypMax Units t PHL ,Propagation Delay12.5nst PLH TDI B0to TDO B1,TDI B1to TDO B0t PHL ,Propagation Delay12.5nst PLH TDI B0to TDO 01,TDI B1to TDO 01t PHL ,Propagation Delay 12.5nst PLH TDI LSPn to TDO LSPn+1t PHL ,Propagation Delay12.5nst PLH TMS B0to TMS B1,TMS B1to TMS B0t PHL ,Propagation Delay12.5nst PLH TMS B0to TMS (01-06),TMS B1to TMS (01-06)t PHL ,Propagation Delay12.5nst PLH TRST B0to TRST B1,TRST B1to TRST B0t PHL ,Propagation Delay12.5nst PLHTRST B0to TRST (01-06),TRST B1to TRST (01-06)Timing Diagrams20051236Waveforms for an Unparked STA112in the Shift-DR (IR)TAP Controller StateS C A N S T A 112 12Timing Diagrams(Continued)20051238Reset Waveforms20051239Output Enable WaveformsCapacitance &I/O CharacteristicsRefer to National’s website for IBIS models at /scanSCANSTA11213Physical Dimensionsinches (millimeters)unless otherwise noted100-Pin BGANS Package Number SLC100a Ordering Code SCANSTA112SM100-Pin TQFPNS Package Number VJD100a Ordering Code SCANSTA112VSS C A N S T A 112 14NotesLIFE SUPPORT POLICYNATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION.As used herein:1.Life support devices or systems are devices orsystems which,(a)are intended for surgical implant into the body,or(b)support or sustain life,and whose failure to perform when properly used in accordance with instructions for use provided in the labeling,can be reasonably expected to result in a significant injury to the user.2.A critical component is any component of a lifesupport device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system,or to affect its safety or effectiveness.BANNED SUBSTANCE COMPLIANCENational Semiconductor certifies that the products and packing materials meet the provisions of the Customer Products Stewardship Specification(CSP-9-111C2)and the Banned Substances and Materials of Interest Specification (CSP-9-111S2)and contain no‘‘Banned Substances’’as defined in CSP-9-111S2.National Semiconductor Americas CustomerSupport CenterEmail:new.feedback@ Tel:1-800-272-9959National SemiconductorEurope Customer Support CenterFax:+49(0)180-5308586Email:europe.support@Deutsch Tel:+49(0)6995086208English Tel:+44(0)8702402171Français Tel:+33(0)141918790National SemiconductorAsia Pacific CustomerSupport CenterEmail:ap.support@National SemiconductorJapan Customer Support CenterFax:81-3-5639-7507Email:jpn.feedback@Tel:81-3-5639-7560 SCANSTA112 7-port Multidrop IEEE 1149.1 (JTAG) MultiplexerNational does not assume any responsibility for use of any circuitry described,no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.。

TP112中文资料