基于DM642的以太网通信接口设计

DM642嵌入式网络接口开发设计

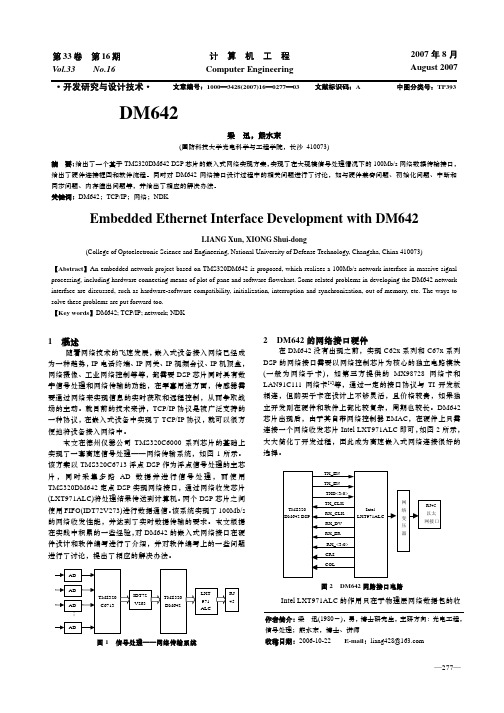

—277—DM642嵌入式网络接口开发设计梁 迅,熊水东(国防科技大学光电科学与工程学院,长沙 410073)摘 要:给出了一个基于TMS320DM642 DSP 芯片的嵌入式网络实现方案,实现了在大规模信号处理情况下的100Mb/s 网络数据传输接口,给出了硬件连接框图和软件流程。

同时对DM642网络接口设计过程中的相关问题进行了讨论,如与硬件兼容问题、初始化问题、中断和同步问题、内存溢出问题等,并给出了相应的解决办法。

关键词:DM642;TCP/IP ;网络;NDKEmbedded Ethernet Interface Development with DM642LIANG Xun, XIONG Shui-dong(College of Optoelectronic Science and Engineering, National University of Defense Technology, Changsha, China 410073)【Abstract 】An embedded network project based on TMS320DM642 is proposed, which realizes a 100Mb/s network interface in massive signal processing, including hardware connecting means of plot of pane and software flowchart. Some related problems in developing the DM642 network interface are discussed, such as hardware-software compatibility, initialization, interruption and synchronization, out of memory, etc. The ways to solve these problems are put forward too. 【Key words 】DM642; TCP/IP; network; NDK计 算 机 工 程Computer Engineering 第33卷 第16期Vol.33 No.16 2007年8月August 2007·开发研究与设计技术·文章编号:1000—3428(2007)16—0277—03文献标识码:A中图分类号:TP3931 概述随着网络技术的飞速发展,嵌入式设备接入网络已经成为一种趋势,IP 电话终端、IP 网关、IP 视频会议、IP 机顶盒,网络摄像、工业网络控制等等,都需要DSP 芯片同时具有数字信号处理和网络传输的功能,在军事用途方面,传感器需要通过网络来实现信息的实时获取和远程控制,从而争取战场的主动。

基于DM642的视频编码与网络传输

基于DM642的视频编码与网络传输近年来,随着互联网的普及和宽带网络的发展,视频成为了人们获取信息和娱乐的重要途径。

视频编码和网络传输技术的发展,对于提高视频质量和传输效率起到了关键作用。

基于DM642的视频编码与网络传输技术,成为了当前研究的热点之一。

首先,DM642是德州仪器公司推出的一款高性能数字信号处理器。

它具备强大的处理能力和丰富的外设接口,适用于各种复杂的视频编码和解码应用。

通过利用DM642的优势,可以实现高效率的视频编码和解码,从而提高视频质量和传输效率。

其次,视频编码是将原始视频信号进行压缩编码,以减少数据量的技术。

常见的视频编码标准有H.264、MPEG-4和VC-1等。

基于DM642的视频编码技术,可以利用其强大的处理能力和高效的算法实现实时的高质量视频编码。

通过有效地压缩视频数据,可以减少网络传输所需的带宽和存储空间。

再次,网络传输是将编码后的视频数据通过网络传输到接收端的过程。

网络传输中的延迟和丢包会对视频质量产生不可忽视的影响。

基于DM642的网络传输技术,可以利用其高性能的网络接口和流控制算法,实现稳定、高效的视频传输。

通过合理的网络传输策略,可以减少传输延迟和丢包率,从而保证视频的连续性和稳定性。

最后,基于DM642的视频编码与网络传输技术在实际应用中具有广泛的应用前景。

例如,在视频监控领域,基于DM642的视频编码与网络传输技术可以实现高清晰度的视频监控和实时传输;在视频会议领域,可以实现高质量的远程会议和协作;在网络直播领域,可以实现高效的视频直播和点播等。

综上所述,基于DM642的视频编码与网络传输技术在提高视频质量和传输效率方面具有重要意义。

通过充分利用DM642的处理能力和优化算法,可以实现高效的视频编码和解码;通过合理的网络传输策略,可以实现稳定、高效的视频传输。

基于DM642的视频编码与网络传输技术必将在未来的视频应用领域发挥重要作用。

基于DM642的视频处理系统硬件设计分析

基于DM642的视频处理系统硬件设计分析杨兴泉摘㊀要:随着现代经济的飞速发展,互联网技术㊁计算机技术也进入人们的视野,视频处理系统在人们的日常生活中的应用也逐渐多元化,并且逐渐走进军事㊁医疗㊁科研等诸多领域㊂近几年来,基于DM642的视频处理系统逐渐成为人们研究的重点㊂在视频处理系统中,编解码的硬件是实现视频处理的重要前提,只有通过该视频处理硬件,才能实现是数字视频的处理和网络传输,具有非常重要的研究意义㊂关键词:TMS320;视频处理;视频接口一㊁引言随着视频处理系统的迅速发展,视频处理系统也逐渐进入人们的视野㊂同时,随着对视频技术的研究的逐渐深入,在此基础上出现了很多的新的技术和研究方向,拓宽了它在其他领域的应用,比如医疗设备中的机器影像,交通路口㊁小区的监控装置,军事武器装备中的成像技术等㊂所以,设计一种视频处理系统对于人民和社会有着重要意义㊂二㊁基于TMS320的视频处理系统硬件设计在TI公司推出的C64系列中,TMS320DM642是专用视频接口的高性能定点DSP㊂性能方面,最大具有4800MIPS的数字处理能力;配置方面,具有二级缓存结构,3个视频接口,64位扩展内存接口(EMIF)(可扩展存储空间),64独立通道EDMA控制器,可(实现片内/外的数据传送和复制)㊂(一)系统的硬件结构视频处理系统的硬件设计的核心装置是DM642,相较于市面上普通的视频处理系统,它具有高性能和高运算速度,可以满足对于视频处理所需的大部分复杂算法的处理要求㊂在视频信号的采集方面,可以使用较为获得的CCD摄像头进行采集㊂当视频信号被采集完以后,系统利用解码芯片将模拟信号进行转换,使其变为数字信号,再传递给DSP进行运算处理㊂在DM642的3个视频接口中,VP0和VP1可以用于视频输入和音频输入,而VP2口分为两路视频输入㊂因此,这一硬件结构的工作就是,经CCD采集视频信号后,通过DM642的VP0口输入,解码芯片将模拟信号进行转换㊂此后,数字视频信号再经过DM642的软件编码器,被其编码压缩处理,并将生成的视频码流数据进行打包整理,再经过RJ-45接口利用太网传送到上位机,因此上位机就可以作为该系统的监控装置㊂此外,DM642的EMIF接口连接SDRAM和Flash存储器㊂系统内的DSP仅仅几乎不能满足系统的要求,因此当系统需要对视频进行实时处理时,必须在系统中配置高性能SDRAM㊂当它在运行程序和进行数据处理,可以减少数据流动过程中的时间消耗,在一定程度上提高了视频处理系统的所需的处理时间;Flash可以用来存放系统软件,也可以配置参数㊂(二)存储器模块设计在视频处理系统系统的数据处理模块中,存储器的核心模块电路芯片包括DSP芯片㊁SDRAM芯片和Flash芯片㊂存储器模块,顾名思义,它可以程序存储器的程序读写㊂此外,它还可以实现内部数据与外部数据存储器的数据传输㊂在仿真调试阶段,它可以与仿真器相连,与主机进行数据交换,进行仿真调试㊂(三)JTAG接口设计在进行调试时,JTAG接口也是必不可少的设计㊂它可以连接目标板,方便开发者对目标板的开发,并且开发者在修改的同时不用改变其系统结构,在一定程度上减轻了开发和测试系统的难度㊂此外,在连接调试设备时,JTAG接口将XDS510仿真器与系统板和电脑相连,方便开发者在统一的公司集成化开发环境中进行调试,极大限度的减轻了调试难度,避免了系统不匹配的问题㊂(四)电源模块的设计电源模块是给系统提供动力的模块㊂在一般的视频处理系统中,系统内的不同模块会利用不同的电压,所以在电源模块中必须设计电源管理芯片,其作用是进行电压变换,将相应的电阻和电容值进行修改,满足各部分模块所需的电压,如3.3V㊁1.8V及1.4V等不同大小的电压㊂在本系统设计中,为了减少在调试过程中的麻烦,决定采用TPS54310,它也是属于TI公司生产产品,属于电源调节芯片㊂需要说明的是,它虽然能够实现低电压输入和高电流输出,但是其调节范围是有限的,一般的调节范围为输入电压为3 6V,输出电压为0.9 3.3V之间㊂不同的电压用于不同的模块,例如3.3V的电源可以用于核心芯片如视频解码芯片㊁视频编码芯片㊁SDRAM芯片等的供给电源㊂三㊁系统调试由于系统的复杂性,为了尽量减少系统调试的难度,用到的系统模块多为TI公司的生产产品,在一定程度上提高了系统的可靠性㊂此外,为了避免单个模块出现问题的情况,决定对各个模块分别调试,后将各模块进行联调,最后整体调试系统的性能,缩短了调试时间㊂在调试中尽量选择最优的方案进行调试,方便系统工作时处于最佳状态㊂四㊁结语文章基于DM642这一核心装置,通过对系统硬件机构的选择,了解其不同的功能和用途,后文经过存储器模块㊁JTAG接口和电源模块的不同设计,最终进行系统调试,在理论和选材上完成了对DM642视频处理系统的设计㊂下一步研究的方向应该是对不同模块设计具体的程序,对其中的不同的模块设计电路图,进行组装,并对最后的系统进行进一步的完善㊂最后,可以在此系统上研究不同的算法,方便他用于不同的场景,比如通过研发新的视频压缩算法,方便它应用于军事㊁医疗㊁教育等诸多领域㊂参考文献:[1]刘丹,孙丽云,胡伟,等.基于DM642的视频处理系统设计[J].微计算机信息,2007,23(17):157-159.[2]圣冬冬.基于DM642的视频处理系统硬件设计[J].电子设计工程,2019,19(2):168-173.[3]刘琼,安涛,金钢,等.基于DM642视频采集处理系统硬件设计[J].微计算机信息,2007,23(32):180-182.作者简介:杨兴泉,南京优视互联科技有限公司㊂681。

基于DM642的网络视频系统的设计与实现

_ ] -4 22o:: _ r {::t42q

me t e n e s f i d f e - mes r el n es s m. e s h e d n so a t u v i a c y t t ok rl i l e

Ke r s ra—mevd o ew r o e ;DM6 2 ma ec mp eso y wo d : e t ie ;n tok n d s l i 4 ;i g o rsin;MJ EG P

收 稿 日期 : 0 2 0 一 4 2 1 — l 1 稿 件 编 号 :0 2 16 2 10 0 0

2 网络 视 频 节 点 软 件 设 计

2 1 整 体 流 程 .

r 公 司 的 D P开发 软 件 包 括 集 成 开 发 环 境 ( C )实 时 I 1 I S CS、 操 作 系 统 ( S / IS 、 三 方 算 法 库 标 准 (X rsD P 。 本 D PB O )第 e pes S )

种 多 媒 体 信 号 处 理 标 准 , 成 通 用 的 软 件 平 台 , 此 得 到 越 构 因

来 越 广 泛 的应 用 嘲 。

1 网络 视 频 节 点 硬 件 设 计

系 统 视 频 节 点 的硬 件 结 构 如 图 1 示 , C D摄 像 头 输 所 由 C

石

入 的视 频 信 号 首 先 通 过 视 频 编 码 器 S A 15 进 行 数 字 化 A 71H

作 者 简 介 : 佚 (9 9 )女 , 南 株 洲人 , 士 , 师 。 研 究方 向 : 子 仪 器 设 计 。 潘 1 7一 , 湖 博 讲 电

-

15 3-

《 电子设计 工程 )02年 第 5期 21

基于DM642的视频处理系统硬件设计

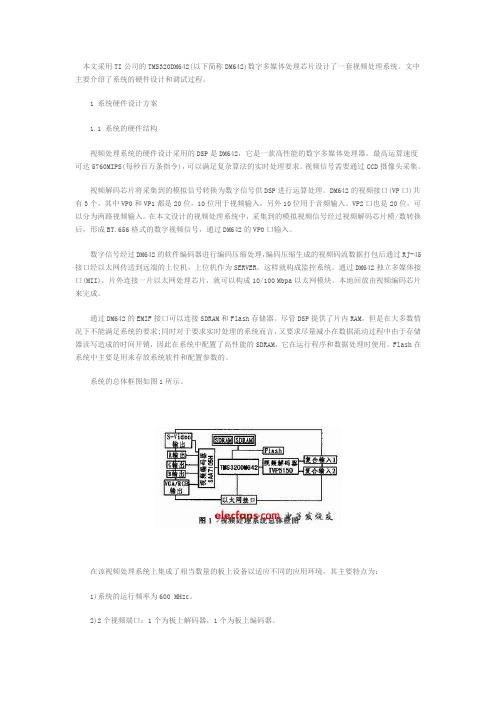

本文采用TI公司的TMS320DM642(以下简称DM642)数字多媒体处理芯片设计了一套视频处理系统。

文中主要介绍了系统的硬件设计和调试过程。

1 系统硬件设计方案1.1 系统的硬件结构视频处理系统的硬件设计采用的DSP是DM642,它是一款高性能的数字多媒体处理器,最高运算速度可达5760MIPS(每秒百万条指令),可以满足复杂算法的实时处理要求。

视频信号需要通过CCD摄像头采集。

视频解码芯片将采集到的模拟信号转换为数字信号供DSP进行运算处理。

DM642的视频接口(VP口)共有3个,其中VP0和VP1都是20位,10位用于视频输入,另外10位用于音频输入。

VP2口也是20位,可以分为两路视频输入。

在本文设计的视频处理系统中,采集到的模拟视频信号经过视频解码芯片模/数转换后,形成BT.656格式的数字视频信号,通过DM642的VP0口输入。

数字信号经过DM642的软件编码器进行编码压缩处理,编码压缩生成的视频码流数据打包后通过RJ-45接口经以太网传送到远端的上位机,上位机作为SERVER,这样就构成监控系统。

通过DM642独立多媒体接口(MII),片外连接一片以太网处理芯片,就可以构成10/100 Mbpa以太网模块。

本地回放由视频编码芯片来完成。

通过DM642的EMIF接口可以连接SDRAM和Flash存储器。

尽管DSP提供了片内RAM,但是在大多数情况下不能满足系统的要求;同时对于要求实时处理的系统而言,又要求尽量减小在数据流动过程中由于存储器读写造成的时间开销,因此在系统中配置了高性能的SDRAM,它在运行程序和数据处理时使用。

Flash在系统中主要是用来存放系统软件和配置参数的。

系统的总体框图如图1所示。

在该视频处理系统上集成了相当数量的板上设备以适应不同的应用环境,其主要特点为:1)系统的运行频率为600 MHzc。

2)2个视频端口:1个为板上解码器,1个为板上编码器。

3)32 MB的同步DRAM空间。

基于DM642以太网模块的数据加密传输

文 章 编 号 :1 7—1 6 2 0 ) 50 8 —4 6 359 (0 7 0 -0 10

基于 D 4 M6 2以太 网模块 的数据加 密传输

郝晓 弘,柏 璐

( 兰州理工大学 电气工程 与信息工程 学院 , 甘肃 兰州 705 ) 300

摘要 : 针对 数据采集系统 中的数据加 密传 输需求 , 出一种 基于 T 公 司的 TMS 2 D 4 提 I 3 0 M6 2芯 片 的以太 网接 入模 块 的数据传输方法 , 并且对传输 的数据进行加 密. 该模块 通过 D 4 有的 E M62特 MAC功能模块 对数据进 行传 输, 只 要对相应 的寄存器进行 配置就 能达到传输数据 的 目的, 还可 以利用 TI 提供 的函数对数 据包进行 处理. 过加 密算 通 法对数据进行加解 密传输 , 以达到数据 安全传 输的 目的. 后介 绍 了这个 模块 的物理 连接 实现 方法和 编程 实现方 最

p ro ma c n d t r n m iso . e f r n e i a a t a s s i n

K e r s DM 6 2;e h r e ;e cy t n ag rt m y wo d : 4 t en t n r p i lo ih o

网络安全问题 逐渐受 到各个企业 的重视 , 多 很 公司为了重要数据 的保密经常采用 的办法是将工作 机 和连接 Itre 的 机器 分 离 开来 , 加 了很 多需 nent 增 要在互联网上完成 的工作 的难度. 而连接内外 网的

HAO a - o g,B Xio h n AILu

( ol geo etia n nor to g n e n C l fElcrc la d I f ma in En i e r g,I n h u U nv fTe h e i m z o i.o c .,I z ou 7 0 0,Chn ) mn h 3 05 ia

基于DM642的实时多协议转换器设计

基于DM642的实时多协议转换器设计黄敬礼;钱进【摘要】A multi-protocol converter was designed to solve the problem of real-time interconnection between all the subsystems in virtual testing systems which have different type buses. DM642 + FPGA structure is adopted in the hardware design according to the principle of hardware resource allocation that the priority level of protocols is considered first. FPGA is used for real-time prior matching of the protocol with higher priority level. The different interrupt information is classified and returned to DM642. In the software design, the protocols are stored according to the address blocks in order to improve the search efficiency of the protocol. In accordance with the characteristics of various types of threads in DSP/BIOS, the tasks are assigned reasonably and triggered according to their classification to speed up the data processing velocity and to ensure the real-time performance of high-priority protocol.%为了解决虚拟试验系统中具有不同总线类型的各实物子系统互联的实时性问题,设计了一种多协议转换器.按协议高低优先级分配软硬件资源,硬件设计采用DM642+ FPGA的结构,使用FPGA实时匹配高优先级协议,并对DM642分类返回不同中断信息;软件设计时,按地址分块存储协议以提高的协议的查找效率,并根据DSP/BIOS中各类线程的特点,合理分配任务并分类触发不同任务,以加快数据处理速度并保证高优先级协议实时性.【期刊名称】《现代电子技术》【年(卷),期】2011(034)022【总页数】4页(P147-149,161)【关键词】多协议转换器;实时性;DM642;DSP/BIOS【作者】黄敬礼;钱进【作者单位】哈尔滨工业大学自动化测试与控制系,黑龙江哈尔滨 150001;海军驻北京航天三院军事代表室,北京100074【正文语种】中文【中图分类】TN919-340 引言在虚拟试验系统中,需要将不同总线类型和不同传输协议的各实物子系统进行互联,实物设备子系统常采用1553B,ARINC429,RS 232等总线,协议转换的实时性对整个虚拟试验系统试验结果的真实性具有重要的影响,因此设计了基于DM642的实时多协议转换器。

基于DM642的嵌入式网络视频服务器的设计

基于DM642的嵌入式网络视频服务器的设计很好的一个实例目前的安防监控领域的主流产品是DVR(数字硬盘录像机),它的主要特点是适合监控点集中的局域监控应用。

但是,随着对于远程分布式监控需求的增长,嵌人式网络视频服务器以其可靠性高,组网方便等优点越来越受到安防领域厂商和客户的重视。

视频服务器的解决方案有多种选择,但是市场产品的主流一般选择两种方案(I)CPU十ASIC。

该方案选择以ARM为核的CPU和专用媒体处理芯片搭建。

优点是开发时间相对较短,但由于采用ASIC,灵活性较差,产品一旦定型,很难更改。

(2)采用面向媒体处理的专用DSP。

其开发时间不长,优点是由于算法是软件代码,所以可以不断对产品性能进行升级,重复开发成本较低。

基于以上几点,本系统采用第二种方案设计。

一、系统的硬件设计视频服务器最主要的功能是完成图像和声音的采集、压缩及传输的功能。

视频服务器用到的核心技术一般包括视频压缩算法,音频压缩算法,网络传输协议。

目前市场上的主流技术主要是MPEG4或H26x视频压缩算法、AAC音频压缩算法、G.72x语音压缩算法(或AAC音频压缩算法),TCP/IP协议等。

DM642是TI公司推出的一款针对多媒体处理领域应用的DSP,它是在C64x的基础上,增加了很多外围设备和接口。

该DSP为548脚BGA封装,高度集成化。

主要外围设备包括:三个可配置的视频接口,可以和视频输人,输出或传输流输人无缝连接。

VCXO内插控制端口(VIC)10/100Mbps以太网口(EMAC)。

数据管理输人输出模块(MDIO)。

多通道音频串行端口(McASP)o 12C总线模块。

两个多通道有缓存的串口(McBSPs)。

三个32- bit 通用定时器。

用户可配置的16- bit或32- bit的主端口接口(HPI16/HPI32)o 6Mhz32- bit的PCI 接口。

通用1/0端口(GPIO)o 64- bit的外部存储单元接口,支持和同步或异步存储单元的连接。

TMS320DM642和TLV230AIC23B通信的接口设计

【 y w r s MS 2 D 4 2 L 2 O I2 B Ke od 】T 30 M6 ;T V 3 A C 3 ;Mc S ;F ;iia zt n A P C ntl ai ii o

1 引 言

DM6 2是 T 3 0 6 x系 列 的 D P, 于 C 4 4 MS 2 C 4 S 基 6 x内

2 硬 件 连 接 设 计

T 3 0 4 2 的 Mc P‘ T V 3 AI 2 Bi有 MS 2 DM6 AS [和 L 2 0 C 3 1 2 ]

核 ,扩 展 了 V l iI 术 的 V I 结 构 ( eoiI-) e cI 技 0r ’ LW V l T1 , c 2 包 含 了许 多 新 的指 令 , 加 了 额外 的数 据 通道 , 增 寄存 器

DM6 2 i ra ie . T r u 4 s el d z ho te u d rtn i g o h u c in o 4 2 a d AI 2 B, h n e a d n t e f n t DM6 n C 3 s f o f te c n e t n b t e n te h o n ci e w e h o

文 章 编号 : 0 2 8 8 2 1 1 - 0 5 0 1 0 — 6 4( 0 0) 1 0 4 - 3

T S 2 DM6 2和 T V2 0 C 3 .品 计 M 30 4 L 3 AI 2 B 产设 .

通信 的接 口设计

李倩然 , 南 周

( 子 科 技 大 学 电子 工程 学 院 ,四 川 成都 6 0 5 ) 电 104

【 bt c]A crigt tecaat i i f S hpo M 30 M6 2 h o mu i t no L 2 0 I2 B ad A s a t co n o h hrce sc o Pc i f T S 2 D 4 ,tecm nc i f V 3 A C 3 n r d rts D ao T

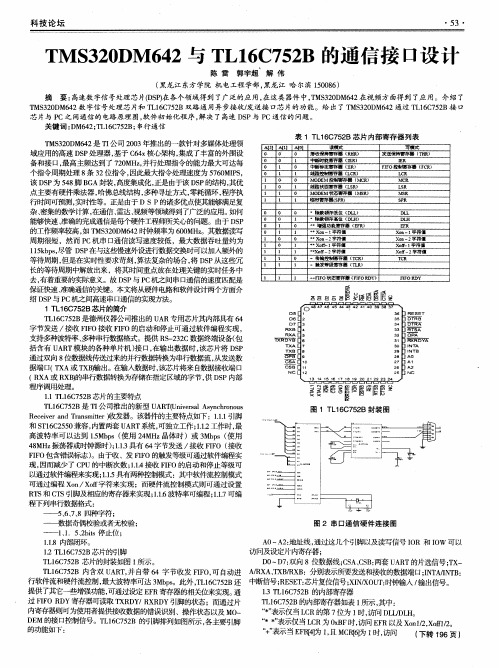

TMS320DM642与TL16C752B的通信接口设计

・ 3・ 5

T 3 0 M6 2与 T 1 C 5 B 的通信接 口设 计 MS 2 D 4 L 6 72

陈 雷 郭宇超 解 伟

( 黑龙 江东方 学院 机 电工程 学部 , 黑龙 江 哈 尔滨 10 8 片(S ) D P在各个领域得到 了广泛的应 用, 在这类器件 中,MS 2 D 4 T 3 0 M6 2在视 频方面得 到 了应 用。介 绍 了 T 3 0 M6 2 字信号 处理芯 片和 T 1 C 5 B双路通 用异步接收/ 送接 口芯片的功能。给 出了 T 3 0 M6 2通过 T 1 C 5 B接 口 MS 2 D 4 数 L6 72 发 MS 2D 4 L6 72 芯 片与 P C之 间通信的电路 原理图, 软件初 始化程序 , 解决 了高速 D P与 P S C通信的 问题 。 关 键 词 : M6 2 T 1 C 5 B 串行 通 信 D 4 ;L 6 7 2 ; 表 1T 1 C7 2 L 5 B芯片 内部 寄 存 器 列 表 6 T 30 M6 2 T 公 司 2 0 年 推 出 的一 款针 对多 媒 体处 理 领 MS 2 D 4 是 I 03 A2 Al A锄 f】 fl £ 诿 橇 建 写 鬣 式 0 O 0 攘 收 保持 蔫硼 (H ) R R 发 邂保 持鬻 释 嚣 ( H ) T R 域应用的高速 D P处理器 , S 基于 C 4 核心架构 , 6x 集成了丰富的外 围设 0 O l 中断耐 能 寄存 嚣 (E ) I R 匿R 备和接口, 最高主频达到了 70 z并行处理指令 的能力最大可达每 2 MH , n B 中断橱 蒋离 嚣 tI ) 事 l R FF /O控 彀帮 存嚣 ( C I F R) 个指令周期处理 8 3 位指令 , 条 2 因此最大指令处理速度为 56 M P , 7 0 IS 0 l t 耋 路燕嘲 璃R 器 《 , 差 事 i LR c l 8 0 M D E 控 制窬 箨器 ( R D MC ) MC , R 该 D P为 5 8 B A封装 , S 4脚 G 高度集成化 , 正是由于该 D P的结构 , S 其优 l 0 l 缝 路麟 悉暂 蒂 嚣 ( S ) LR LR S I t 0 MO E 犍慈 葡 器 ( s D M 筝 R 矾 点主要有硬件乘法器 , 哈佛总线结构 , 多种寻址方式, 零耗循环 , 程序执 l l I 临 时寄 存嚣 《P sR SR p 行时间可预测 , 实时胜等。正是由于 D SP的诸多优点使其能够满足复 杂、 密集的数学计算, 在通信、 、 雷达 视频等领域得到了广泛的应用。 如何 0 O 0 除 数辨 萍眠 位 《 工》 揽 D u l O O j 除 披钍 存 南位 ( 蠊{ D 》 D 悄 能够 陕速 、 准确的完成通信是每个硬件工程师所 的问题。由于 D P S 0 l 料 墙强 功 娩寄 群器 ‘ F ) ER 的工作频率较高, T S 2 D 4 时钟频率为 6 0 z 如 M 3 0 M6 2 0 MH 。其数据读写 0 l l ¨ 0 一1字符 德 嫩 一l 符 镰 字 l 0 0 一Xn o 一2 字得 僵 X 一 字 符 癯 ∞ 2 周期很短 ,然而 P C机串口通信读写速度较低 ,最大数据吞吐量约为 l l ” X  ̄-l 符 糠 t f 字 X f 字 符 德 o -t 1 l l D 一 字 符组 f 2 X f一 睾 掰越 o 2 15 b s kp, 1 尽管 D P S 在与这些慢速外谢 亍 数据交换时可以加入额外的 l l 0 一 棒 鞴控 嘲璃蒋 器 ( C ) T R TR C 等待周期 , 但是在实时f要求苛刻 , 生 算法复杂 的场合 , D P从这些冗 将 S l l l + 艘 捷 簪缀 臀襻 嚣 (Z ) TR 长的等待周期中解放出来 ,将其时间重点放在处理关键的实时任务 中 l 1 i +F 一 捧。状 卷寄 佯鬻 ‘ IOR Y) F F D FF R Io DY 去, 有着重要的实际意义。故 D P与 P S C机之间串口通信的速度匹配是 保 瘟、 准确通信的关键。本文将从硬件电路和软件 悯 个方面介 绍 D P与 P S C机之间高速串 口 通信的实现方法。 1T 1 C 5 B芯片的简介 L 7 2 6 T 1C 5 B是德州仪器公司推 出的 U R专用芯片其内部具有 6 L 6 72 A 4 字节发送 / 接收 FF IO接收 FF IO的启动和停止可通过软件编程实现, 支持多种波特率、 多种串行数据格式 。提供 R 一 3 C数据终端设备( S22 包 括含有 U R A T模块的各种单片机 ) 口, 接 在输出数据时, 该芯片将 D P S 通过双向 8 位数据线传送过来的并行数据转换为串行数据流, 从发送数 据端 口 T A或 T B ̄ 。在输 A数据时, (X X) 该芯片将来 自数据接收端 口 ( X R A或 R B的串行数据转换为存储在指定区域的字节, D P内部 X) 供 S 程 序调用 处理 。 1 L 6 7 2 片的 主要特点 . T 1C 5 B芯 1 T 1C 5 B是 T 公 司推 出 的新 型 U R (nvra A yc rnu L6 72 I A TU ie l snhoos s 图 1T 1 C 5 B封装 图 L 6 72 R ci r n rnm tr) ee e dTa s ie 收发器。该器件的主要特点如下 :1 .引脚 v a t .1 1 和 S 1C 5 0 T 6 2 5 兼容, 内置两套 U R A T系统, 可独立工作;. 1 2工作时, 1 最 E } 巷 高波特率可以达到 1 Mb s( . p 使用 2 MH 晶体时 )或 3 p 使用 5 4 z Mb s( 4 MH 振荡器或时钟源时)1 .具有 6 字节发送 /接收 FF ( 8 z ;.3 1 4 IO 接收 FF IO包含错误标志 ) 。由于收、发 FF IO的触发等级可通过软件编程实 — = — F L 现, 因而减 少 了 C U 的中断 次数 ;.4 收 FF P 1 .接 1 IO的启 动 和停止 等级 可 以通过软件编程来实现 ; 1 1 5具有两种控制模式 :其中软件流控制模式 . 可通 过 编程 X n X f o / o  ̄ 来 实 现 ;而硬 件 流控 制模 式 则可 通过 设 置 I … R S和 C S引脚及相应的寄存器来实现 ; 1 T T 1. .6波特率可编程;.7可编 1. 1 程下列串行数据格式: _ 678四种字符 ; 5 … 数据奇偶校验或者无校验 ; 图 2 串 口通 信 硬 件 连 接 图 11 、bt 、.52 i s停止 位 ; A 一 2地址线 , 0 A : 通过这几个引脚以及读写信号 I R和 I W 可以 O O 1. .8内部 闭环 。 1 1 L6 72 2 T 1C 5 B芯片的引脚 访问及设定片内寄有 器; T 1C 5 B芯片的封装如图 1 L6 72 所示。 D ~ 7双向 8位数据线 ;S 、S : U R 的片选信号;x 0 D: CA C B两套 A T T— T I C 5 B内含双 U R , 自带 6 L6 72 A T并 4字节收发 FF 可 自动进 AR A、X / X :分别表示所要发送和接收的数据端口; T / T : IO, /X T BR B I AI B N N 行软件流和硬件流控制 , 最大波特率可达 3 p。此外 ,L 6 7 2 Mb s T 1 C 5 B还 中 断信号;E E : R s T芯片复位信号;I/O T时钟输入 / 信号。 XNX U : 输出 提供了其它一些增强功能, 可通过设定 E R寄存器的相关位来实现。 F 通 1 L 6 7 2 的内部寄存器 .T 1C5B 3 过 FF D IO R Y寄存器可读取 T D / X D XR Y R R Y引脚的状态 ;而通过片 T 1C 5B的内部寄存器如表 1 L 67 2 所示 , 其中: 内寄存器则可为使用者提供接收数据的错误识别、操作状态以及 MO — “’ 表示仅当 L R的第 7 C 位为 1 访问 D UD H 时, L L。 D M 的接 口控制信号。T 1C 5 B的引脚排列如图所示 , E L6 72 各主要引脚 “ 表示仅当 L R为 0B 时, E R以 X n/ Xf / C xF 访问 F 及 o1 ,ol 。 2 2

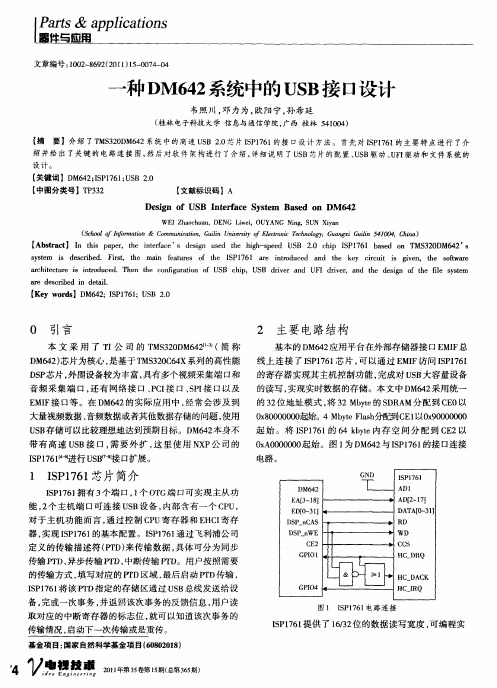

一种DM642系统中的USB接口设计

【 要】介绍 了T S2D 62 摘 M 30 M 4 系统中的高速 U B 2 芯片I 16 的接 口设计;法。首先对IP7 1 S . 0 S 71 P h - S 1 的主要特点进行 了介 6

绍 并给 出 了关键 的 电路 连接 图, 后 对软件 架构进 行 了介 绍 , 细说 明了U B芯 片的配置 、 S 然 详 S U B驱 动 、 F 驱 动和文件 系统 的 UI

【 y w r s M6 2 S 16 ;U B 2 Ke od 】D 4 ;IP 7 1 S . 0

踟

2 主要 电路结构

基本 的D 6 2 M 4 应用平 台在外部存储器接 口E F MI 总 线上 连接 了 IP 7 1 S 16 芯片 , 以通 过 E F访问 IP 7 1 可 MI S 16 的寄存器实现其 主机控 制功能 , 完成对 U B 容量设备 S大 的读写 , 实现实时数据的存储 。本文中 D 6 2 M 4 采用统一 的 3 位 地址模 式 , 3 bt 的 S R M分配 到 C O 2 将 2M y e DA E 以 。4Mbt Fah 冽 C x 00 0 0 y l 分酉 e s E 以0 9 00 0 1

基于DM642和TCP%2fIP协议的声纳信息传输系统的设计与实现

TMS320C64X为定点系列,而TMS320C67X为浮点系列“‘。

DM642是T1公司2003年推出的一款针对多媒体处理领域应用的高速DSP处理器,基于C64x核心架构,集成了丰富的外围设备和接口,最高主频可达720MHz。

并图2.3网络平台的版图行处理指令的能力最大可达每个指令周期处理8条32位指令,因此最大指令处理速度为5760MIPS。

该DSP为548脚BGA封装,高度集成化。

其功能模决图如图2.4所示。

主要外部设备包括:◆三个可配置的视频接口,可以和视频输入,输出或传输流输入无缝连接。

VCXO内插控制端口(VtC)◆10/100Mbps以太网D(EMAC),8个发送通道和8个接收通道◆数据管理输入输出模块(MDl01◆多通道音频串行端I](MeASP)◆12C总线模块◆两个多通道有缓存的串I](MeBSPs)◆三个32-bit通用定时器◆用户可配置的16-b“或32-bit的主端口接[21(HPll6/HPl32)◆66Mhz32.bit的PCI接口◆PW:程序地址访问等待;◆PR:程序取指包接收。

图2.5DM642内核结构图图2,6DM642取指组成图罔瓶…畦匪三雕三'寥恢二忡埘l雕兰:…[sk一节;Ⅱ—<囱垡霞巨;Lg!卜一匪琏土篇甲一罐匪*|要献l!!}掣.图2.7DM642数据通道图指令的读入是通过数据通道完成的,DM642有两个数据通道A和B,~一■●■■●■■■■■■●_I——I__●■●■●■■■■■■_■●_●■■I●__-■l_●__●■■_■■_l哈尔滨工程大学硕士学位论文也支持差分对驱动。

2.3硬件平台各个模块的设计与实现根据剖面声纳数据处理的需要,网络信息传输系统硬件平台必须完成两片DSP(TMS320DM642)的并行,因此系统的互连主要分为两部分,如图2.13所示,即两片DM642的互连以及主DSP与外部网络的互联。

Array图2.13系统互联框图2.3.1两片DM642并行的设计与实现2.3.1.1硬件配置从DM642处理器通过HPI口向主DM642处理器提供数据,以完成网络发送等操作。

一种DM642系统中的USB接口设计

一种DM642系统中的USB接口设计韦照川;邓力为;欧阳宁;孙希延【期刊名称】《电视技术》【年(卷),期】2011(35)15【摘要】In this paper, the interface's design used the high-speed USB 2.0 chip ISP 1761 based on TMS320DM642' s system is described. First, the main features of the ISP 1761 are introduced and the key circuit is given, the software architecture is introduced. Then the configuration of USB chip, USB driver and UFI driver, and the design of the file system are described in detail.%介绍了TMS320DM642系统中的高速USB 2.0芯片ISP1761的接口设计方法.首先对ISP1761的主要特点进行了介绍并给出了关键的电路连接图,然后对软件架构进行了介绍,详细说明了USB芯片的配置、USB驱动、UFI驱动和文件系统的设计.【总页数】5页(P74-77,80)【作者】韦照川;邓力为;欧阳宁;孙希延【作者单位】桂林电子科技大学信息与通信学院,广西桂林541004;桂林电子科技大学信息与通信学院,广西桂林541004;桂林电子科技大学信息与通信学院,广西桂林541004;桂林电子科技大学信息与通信学院,广西桂林541004【正文语种】中文【中图分类】TP332【相关文献】1.MP3系统中USB接口设计 [J], 徐强;宋依青2.一种声呐仿真系统中的高速USB接口设计 [J], 白汉斌;庞凌;贺富强;张明敏3.光缆检测系统中的USB设备接口设计 [J], 刘杰;郑翔;张文强4.大容量多通道数据采集系统中的USB接口设计 [J], 王岱钏5.高速数据采集系统中USB3.0数据传输接口设计 [J], 杨少博;裴东兴;岳孝忠因版权原因,仅展示原文概要,查看原文内容请购买。

基于DM642的以太网通信接口设计

基于DM642的以太网通信接口设计

冯琛华;别红霞

【期刊名称】《信号处理》

【年(卷),期】2007(023)005

【摘要】基于TI公司数字媒体DSP芯片DM642,设计并实现了以太网通信软硬件接口.采用DM642片内集成的以太网接口模块EMAC/MDI0,结合片外Intel LXT971 PHY芯片,在嵌入式操作系统DSP/BI0S架构上,运用网络开发包NDK提供的TCP/IP协议栈,实现了底层硬件驱动程序的编制及其协议栈接口,完成了视频信息的以太网传输.

【总页数】3页(P783-785)

【作者】冯琛华;别红霞

【作者单位】北京邮电大学信息工程学院,北京,100876;北京邮电大学信息工程学院,北京,100876

【正文语种】中文

【中图分类】TN91

【相关文献】

1.基于多核DSP的以太网通信接口设计 [J], 焦淑红;焦壮

2.基于DSP的以太网通信接口设计 [J], 肖波

3.基于ENC28J60的TMS320F2812以太网通信接口设计 [J], 高吉星;赵强;佟为明

4.基于ARM和W5100的嵌入式以太网通信接口设计 [J], 王广维;张浩然

5.一种基于C64系列DSP的千兆以太网通信接口设计 [J], 刘小刚;周建烨;铁奎因版权原因,仅展示原文概要,查看原文内容请购买。

基于dm642的温度采集与以太网传输系统设计

基于dm642的温度采集与以太网传输系统设计

高雪飞;安永丽;张晓杰

【期刊名称】《科技传播》

【年(卷),期】2012(0)9

【摘要】目前,DSP芯片在自动化控制领域已经得到了越来越广泛地应用,本文基于C64x系列DSP芯片TMS320DM642对多点温度采集与以太网传输系统进行了设计.测温元件采用单总线数字温度传感器DS18B20,以太网物理层收发器采用Intel 公司的LXT971A.系统可靠性高、实时性好,可广泛应用于远距离温度数据监测的场合,具有很高的实际应用价值.

【总页数】3页(P206-207,210)

【作者】高雪飞;安永丽;张晓杰

【作者单位】河北联合大学信息工程学院,河北唐山 063009;河北联合大学信息工程学院,河北唐山 063009;华升富士达电梯有限公司,河北廊坊 065001

【正文语种】中文

【中图分类】TP2

【相关文献】

1.基于ARM的温度采集与以太网传输系统的设计 [J], 徐萍;卿粼波;李金平;何小海

2.基于DM642的低成本视频采集与传输系统设计 [J], 李坤贺;卢峥;向昱丞;吴昌昊

3.基于DM642的桥梁缆索表面缺陷图像采集及传输系统设计 [J], 周忆;王生治;张军伟

4.基于DM642 DSP技术视频图像采集与传输系统设计 [J], 王东霞;程亚维

5.基于DM642的视频采集与传输系统设计 [J], 张龙;李霁野

因版权原因,仅展示原文概要,查看原文内容请购买。

基于DM642的多通道视频网络传输系统的硬件设计

基于DM642的多通道视频网络传输系统的硬件设计谢晶【期刊名称】《微型机与应用》【年(卷),期】2012(31)14【摘要】Tl's TMS320DM642 is a specialized high-performance DSP for image processing, which has a powerful instruction sets and high-speed computing speed. The stability and efficiency are poor for the traditional PC-based network video transmission system. In this paper, a multi-channel video network transmission system a based DM642 is design to meet the need. The images photographed hy CCD camera are transmitted to the video input port real-time. With high-speed computing power for image pro- eessing. The DM642 finishes the relevant images processing and transmits images to the PC to achieve the purpose of video surveil- lance through the EMAC (Ethernet).%TMS320DM642是TI公司推出的一种专门用于图像处理的高性能DSP,它具有强大的指令集和高速的运算速度。

,针对传统基于PC网络摄像传输系统的稳定性差、执行效率低的特点,提出了基于DM642的多通道视频网络传输系统。

TMS320DM642和TLV230AIC23B通信的接口设计

TMS320DM642和TLV230AIC23B通信的接口设计李倩然;周南

【期刊名称】《电声技术》

【年(卷),期】2010(034)011

【摘要】根据DSP芯片TMS320DM642的特点,搭建了音频编解码芯片

TLV230AIC23B和DSP之间的串口通信的软硬件系统.通过对AIC23B和DSP芯片功能的了解,设计AIC23B和DSP之问的硬件电路的连接,设置了

TLV230AIC23B和TMS320DM642的相关的寄存器.实现了TLV230AIC23B和TMS320DM642之间的通信,并给出了I2C写入TLV230AIC23B和初始化McASP的操作代码.这种接口设计具有广泛的通用性,可应用于各种相关的音频处理设备,进行音频信号的处理.

【总页数】3页(P45-47)

【作者】李倩然;周南

【作者单位】电子科技大学电子工程学院,四川成都610054;电子科技大学电子工程学院,四川成都610054

【正文语种】中文

【中图分类】TN912

【相关文献】

1.TLV320AIC23B与TMS320DM642的接口设计 [J], 胡涛;陈超

2.TMS320DM642与音频编解码器的接口设计 [J], 涂水林;薛正明

3.基于TMS320DM642实现网络通信功能的研究 [J], 吴皓;朱沛

4.一种FPGA和TMS320DM642的通信方案 [J], 任勇屹;张祺;韦忠正

5.TMS320DM642与TL16C752B的通信接口设计 [J], 陈雷;郭宇超;解伟

因版权原因,仅展示原文概要,查看原文内容请购买。

DM642嵌入式网络接口开发设计

DM642嵌入式网络接口开发设计

梁迅;熊水东

【期刊名称】《计算机工程》

【年(卷),期】2007(033)016

【摘要】给出了一个基于TMS320DM642 DSP芯片的嵌入式网络实现方案,实现了在大规模信号处理情况下的100Mb/s网络数据传输接口,给出了硬件连接框图和软件流程.同时对DM642网络接口设计过程中的相关问题进行了讨论,如与硬件兼容问题、初始化问题、中断和同步问题、内存溢出问题等,并给出了相应的解决办法.

【总页数】3页(P277-279)

【作者】梁迅;熊水东

【作者单位】国防科技大学光电科学与工程学院,长沙,410073;国防科技大学光电科学与工程学院,长沙,410073

【正文语种】中文

【中图分类】TP393

【相关文献】

1.基于DM642嵌入式图像融合处理系统硬件设计 [J], 王旭东;王晓卫;李明哲

2.基于DM642的嵌入式车牌识别系统设计与实现 [J], 陈存弟;刘金清;刘引;蔡淑宽;何世强;周晓童;邓淑敏;吴庆祥

3.基于DM642的嵌入式车牌识别系统设计与实现 [J], 陈存弟;刘金清;刘引;蔡淑宽;何世强;周晓童;邓淑敏;吴庆祥;

4.基于NDK的DSP网络接口移植开发设计 [J], 张枫;郑力新;周凯汀

5.DM642嵌入式图像融合处理系统硬件设计研究 [J], 郝雅婷;马立新

因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

ቤተ መጻሕፍቲ ባይዱ

Ke y wor s: DS d P;E h r e o t en t mmu i ain I t r c ;T P I r tc l c n c t n e a e C / P p oo o o f

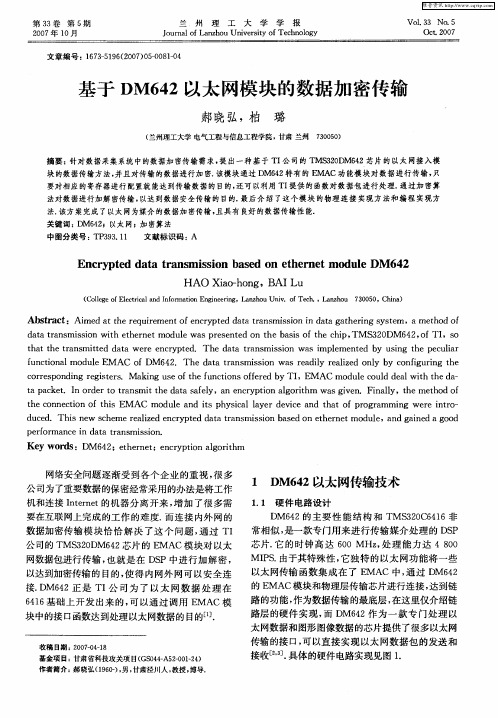

本文通信接 口的设 计方案 主要 用于 以 T 公 司 的数 字媒 I

体 D P芯 片 D 4 S M6 2为核心处理器 的系统 扩展 。针 对 D 4 M62

芯片的特 点和资源 , 扩展 了以太 网通信 接 口。主要 完成 了接

口电路的设 计 、 通信 接 口软件 的 总体架 构 、 底层 驱 动程 序及

D P BO n e I e o ee pn i ( D , ecm u i tnsf ae i ldn ad aedi r a dte C /Ppo cl S / I Sadt t r dvl igkt N K) t o m nc i ot r , cuighrw r r es n P I rt a hTN w k o h ao w n v hT o

1 引言

基于 D P的嵌 入式智 能信 息终端 系统 日渐普 及… , S 如实 时多媒体监控终 端 、 全数 字 广播终 端等 。同时 , 着 网络技 随

接 口等。本 文 利 用 D 62片 内的 以 太 网接 口模 块 E C M4 MA / MD O, I 结合片外 的 P Y芯片 Itl X 9 1以及简单 的外 围电 H ne L T 7 路, 扩展 了系统的以太 网网络通信接 口, 实现 系统的网络化 。

Th r wa e wa a e n e ha d r s b s d o EM AC /M DI m o u e n e rt d o DM 6 n he n t r hp ntlLX' O d l si t ga e n 42 a d t e wo k c i I e I 1 97 PHY.I c r r tng wih n o pea i t

( col f nom t nE g er g B F ,e ig 10 7 ,hn ) S ho o Ifr a o n i ei , U FB in ,0 8 6 C ia i n n j

A src : T eEhre cmm nct ns taea dh rw r b sdo I it m daD P ci D 4 eei pe etd b t t h tent o uiao ow r n ad ae ae nT g  ̄ ei S h M6 2w r m l ne . a i f di p m

关键词 :D P;以太网通信接 口;T P I S C /P协议栈

I lme t t n o t e n tCo mp e n a i fE h r e mm u ia in It r c s d o o nc t n e f e Ba e n DM6 2 o a 4

F ENG e ・ u BI Ho g・i Ch n・ a h E n ・ a x

维普资讯

第2 3卷

第 5期

信 号 处 理

S GNAL P I ROC S I E S NG

Vo _ 3. No. l2 5 0c . 0 t 2 07

20 o 7年 1 月 0

基于 D 4 M6 2的 以 太 网 通 信 接 口设 计

冯琛华 别 红 霞

( 京 邮 电 大 学 信 息 工 程 学 院 ,北 京 10 7 ) 北 0 8 6

摘

要 :基 于 T 公 司数字媒 体 D P芯 片 D 6 2 I S M 4 ,设计并实现 了以太 网通 信软硬件 接 1 。采用 D 6 2片内集成 的 以太 2 1 M4

网接 1模块 E C MD O,结合片外 It XI7 H 2 1 MA / I ne L ' 1P Y芯片 ,在嵌入式操作系统 D P BO 架构上 ,运用 网络开 发包 N K提 l 9 S/ IS D 供 的 T PI C /P协议栈 ,实 现了底层硬件驱动程序 的编制及其协议栈 接 口,完成了视频 信息的以太网传输 。

2 1 DM62片 内 以 太 网 接 口模 块 . 4

术 的发展 , 这些 D P嵌入式系统也需要 与外部系统进 行实 时 S

通信 , 以实现 信息 管 理 、 源共 享和 远程 监 控等 网络功 能。 资

E C模块是 D P处 理器 内核 与片 外 的网络 物理 层数 MA S 据传输 的接 口, 责 以太 网数 据 的接 收 和发 送 。它实 现 了 负 IE 0 . 准的以太 网 MA E E8 23标 C层协 议 功能 : 将从 上层 协议 栈传递来 的数据打包成 符合 8 2 3标准 的以太网数据 包 , 0. 并 从收到 的以太 网数据包 中剥离 出载荷 数据 , 提供给上 层协议 栈进行分析和处理 。 此外 , MA E C模块提供 了介质 无关 接 口 MI( daId— I Mei n e pn etne ae , e dn It c ) 能够与符 合 8 2 3标 准的 片外 P Y芯片 r f 0. H

无缝连接 。 MD O模 块 负 责 管 理 与 E C相 连 的 所 有 P I MA HY芯 片 , 包

因此 , 针对不 同嵌 入式 系统 的开 发环境 和具 体要 求 , 计性 设

价 比高 、 于实现 的网络通信 接 口已成 为 目前嵌 入式 系统开 易

发 中不 可 或 缺 的 一 部 分 J 。