dsp8

DSP集成开发环境CCS开发指南_部分8

64 o function 软中断激活时运行processing 函数,见5.2节。

o mailbox mailbox 域的值可控制何时运行软中断。

有几种API 调用会影响mailbox 的值,并且所产生的值将决定是否登记软中断。

当软中断被登记时,具有最高优先级的软中断或硬中断服务例程将运行。

o arg0, arg1 传递给processing 函数的inp_buffer 和 out_buffer 的地址。

11. 不作任何改变仅点击Cancel 关闭Properties 对话窗口,。

12. 由于processing 函数不再在主函数中运行,那什么事件将导致SWI 对象运行其函数?在源程序volume.c 中, SWI_dec 被dataIO 函数调用,它递减mailbox 域中的值,当mailbox 域中的值为0时,则登记软中断。

所以,data_CLK 对象运行dataIO 函数10次,SWI 对象就运行其函数一次。

13. 选择File→Close,将询问是否保存修改过的volume.cdb 文件。

点击Yes 保存,保存时将产生volumecfg.cmd、volumecfg.s54和volumecfg.h54。

14. 点击工具栏按钮或选择Project→Build。

655.4 用Execution Graph 查看任务执行情况当在processing 函数中设置探测点并使用图形方式观察输入输出结果时(见前一章),你已经完成了信号处理算法的测试。

本阶段注意的焦点应该是明确任务可以满足实时期限的要求。

1. 选择File→Load 并选取volume.out,然后点击OK。

2. 选择Debug→Go Main,程序运行到主函数的第一条语句。

3. 选择Tools→DSP/BIOS→RTA Control Panel,在CCS窗口底部将出现几个可选项。

4. 在几个可选项所在窗口区域内点击鼠标右键,取消Allow Docking 显示方式或选择Float in MainWindows 方式显示RTA Control Panel。

8路dsp最佳方案

8路DSP最佳方案1. 简介在音频处理和信号处理领域,数字信号处理器(Digital Signal Processor,简称DSP)的应用非常广泛。

在处理音频信号的应用中,8路DSP的方案能够实现对多通道音频信号进行高效处理与控制。

本文将介绍8路DSP的最佳方案,包括硬件和软件的选择、功能特点以及应用场景。

2. 硬件选择选择适合的硬件平台对于实现最佳8路DSP方案至关重要。

以下是几个常见的硬件选择:2.1 DSP芯片DSP芯片是实现音频信号处理的关键组件。

市场上有多种DSP芯片可供选择,如德州仪器(TI)的TMS320系列、安森美半导体(Analog Devices)的SHARC系列等。

选择DSP芯片时需要考虑其处理能力、功耗、接口支持等因素,以满足项目需求。

2.2 信号采集与输出模块为了处理8路音频信号,需要选择适配的信号采集与输出模块。

常见的选择是音频编解码模块,如PCM290x系列,可提供高质量的音频采集与解码功能。

此外,还要考虑模块的接口类型(如I2S、SPDIF等)与DSP芯片的兼容性。

2.3 存储器存储器是DSP系统中不可或缺的组成部分,用于存储程序代码、数据和中间结果。

可以选择外部闪存、RAM等存储设备,通常需要根据实际需求评估存储器大小与速度。

3. 软件选择选择适合的软件平台可以帮助开发人员更方便地进行DSP程序的开发与调试。

以下是几个常见的软件选择:3.1 DSP开发环境DSP开发环境通常由集成开发环境(Integrated Development Environment,简称IDE)和相关的编译器、调试器组成。

TI提供了Code Composer Studio(CCS)等DSP开发环境,用于开发TMS320系列DSP芯片。

选择开发环境时需要考虑其易用性、调试功能以及与硬件平台的兼容性。

3.2 DSP算法库DSP算法库提供了大量的音频处理算法,如滤波、均衡器、混响等,可以加速DSP应用程序的开发。

DSP芯片介绍(精)

DSP 芯片介绍1 什么是DSP 芯片DSP 芯片,也称数字信号处理器,是一种具有特殊结构的微处理器。

DSP芯片的内部采用程序和数据分开的哈佛结构,具有专门的硬件乘法器,广泛采用流水线操作,提供特殊的DSP 指令,可以用来快速地实现各种数字信号处理算法。

根据数字信号处理的要求,DSP芯片一般具有如下的一些主要特点:(1)在一个指令周期内可完成一次乘法和一次加法。

(2)程序和数据空间分开,可以同时访问指令和数据。

(3)片内具有快速RAM,通常可通过独立的数据总线在两块中同时访问。

(4)具有低开销或无开销循环及跳转的硬件支持。

(5)快速的中断处理和硬件I/O支持。

(6)具有在单周期内操作的多个硬件地址产生器。

(7)可以并行执行多个操作。

(8)支持流水线操作,使取指、译码和执行等操作可以重叠执行。

与通用微处理器相比,DSP芯片的其他通用功能相对较弱些。

2 DSP芯片的发展世界上第一个单片DSP 芯片是1978年AMI 公司宣布的S2811,1979年美国Iintel 公司发布的商用可编程期间2920是DSP 芯片的一个主要里程碑。

这两种芯片内部都没有现代DSP 芯片所必须的单周期芯片。

1980年。

日本NEC 公司推出的μPD7720是第一个具有乘法器的商用DSP 芯片。

第一个采用CMOS 工艺生产浮点DSP 芯片的是日本的Hitachi 公司,它于1982年推出了浮点DSP 芯片。

1983年,日本的Fujitsu 公司推出的MB8764,其指令周期为120ns ,且具有双内部总线,从而处理的吞吐量发生了一个大的飞跃。

而第一个高性能的浮点DSP 芯片应是AT&T公司于1984年推出的DSP32。

在这么多的DSP 芯片种类中,最成功的是美国德克萨斯仪器公司(Texas Instruments,简称TI)的一系列产品。

TI公司灾982年成功推出启迪一代DSP 芯片TMS32010及其系列产品TMS32011、TMS32C10/C14/C15/C16/C17等,之后相继推出了第二代DSP 芯片TMS32020、TMS320C25/C26/C28,第三代DSP 芯片TMS32C30/C31/C32,第四代DSP 芯片TMS32C40/C44,第五代DSP 芯片TMS32C50/C51/C52/C53以及集多个DSP 于一体的高性能DSP 芯片TMS32C80/C82等。

第8节 DSP应用系统设计

重视元器件焊接过程的监控。

先从电源模块开始焊接。然后,依次完成音频电路、

FLASH、SRAM、CPLD以及相关外围电路的焊接及调试 。

DSP软件系统设计与调试

§8.3 DSP系统软件设计与调试

程序开始

§8.3.1 DSP最小系统软件调试

D10

系统初始化 定时器初始化 开中断

定时开始 N

中断产生? Y 中断服务程序运行 D10状态改变 中断服务程序结束

TPS3307-33-EP

SENSE2

图8-7 TPS3307-33-EP内部结构图

1.6V

R

R

2

1

3.3V

5

V

G

N

D

0.1uF

4

3

2

1

TPS3307-33-EP

G

SENSE3

SENSE2

SENSE1

G

DSP最小系统设计

N

N

D

D

RESET

RESET

V

M

D

R

D

5

6

7

8

图8-8 复位电路原理图

RESET G N D

DECODER DECODER

256K 256K x x 16 16 MEMORY MEMORY ARRAY ARRAY

I/O I/O DATA DATA CIRCUIT CIRCUIT

COLUMN COLUMN I/O I/O

CE OE WE UB LB

CONTROL CONTROL CIRCUIT CIRCUIT

Control Control Logic Logic

I/O I/O Buffers Buffers and and Data Data Latches Latches DQ15-DQ0 VDDQ

DCP680 八通道汽车DSP音频处理器说明书

DCP680 主机

1台

ห้องสมุดไป่ตู้

线控器

1个

用户手册/保修卡

1 本/1 张

5 米 USB3.0 连接线

1条

光盘

2张

蓝牙天线

1只

Wifi 天线

1只

目录

用户手册

一、 注意事项 .................................................................1 二、 产品简介 .................................................................2

目录

用户手册

⑴ 加载机器预置场景 .............................................33 ⑵ 另存为机器预置场景 ...........................................34 ⑶ 删除机器预置场景 .............................................35 ⑷ 加载电脑上场景文件 ...........................................36 ⑸ 另存为电脑上场景文件 .........................................36 ⑹ 加载整机场景.................................................37 ⑺ 保存整机场景.................................................37 7.8.2、选项菜单 .....................................................37 ⑴ 中英文切换设置...............................................37 ⑵ 高级设置.....................................................38

dsp课件

在代码实现完成后,进行代码调试,确保程序的正确性和稳定性。

调试与测试结果分析总结

调试过程

在代码调试完成后,进行系统调试,确保各个模块之间的协调和正 常运行。

测试结果分析

对测试结果进行分析,包括性能测试、功能测试等,找出可能存在 的问题和不足。

总结

根据调试和测试结果,对项目进行总结,包括经验教训、改进方向等 ,为后续的项目提供参考和借鉴。

DSP课件

目录

• DSP概述 • DSP硬件结构与工作原理 • DSP软件编程与开发环境 • 典型应用案例分析 • DSP发展趋势与挑战 • 实践项目设计与实现

01 DSP概述

定义与发展

定义

数字信号处理(Digital Signal Processing,简称DSP)是一门涉及多个学科 的交叉学科,主要研究将模拟信号转换为数字信号,并对数字信号进行各种处 理。

通信信号处理应用

总结词

通信信号处理是数字信号处理的另一个重要应用领域,涉及信号的调制、传输和解调等环节。

详细描述

在通信信号处理中,数字信号处理技术可以用于信号的调制、编码、解调和解码等环节,同时还可以 进行信号特征提取、分类和识别等任务。具体的应用包括移动通信、卫星通信、数字电视和雷达信号 处理等。

未来DSP将进一步提高处理速度和效率,满足更 多复杂应用的需求。

更低的功耗

通过不断优化技术,降低DSP的功耗,延长设备 的使用寿命。

更广泛的应用领域

DSP将在更多领域得到应用,如智能家居、自动 驾驶、医疗保健等。

06 实践项目设计与 实现

项目需求分析与设计思路

明确项目目标

01

在开始实践项目之前,需要明确项目的目标,包括要实现的功

DSP各种知识点总结

1 DSP芯片的特点:(1).哈佛结构(程序空间和数据空间分开)(2).多总线结构.(3)流水线结构(取指、译码、译码、寻址、读数、执行)(4)多处理单元. (5)特殊的DSP指令(6).指令周期短. (7)运算精度高.(8)硬件配置强.(9)DSP最重要的特点:特殊的内部结构、强大的信息处理能力及较高的运行速度。

2 三类TMS320:(1)TMS320C2000适用于控制领域(2)TMS320C5000应用于通信领域(3)TMS320C6000应用于图像处理3 DSP总线结构:C54x片内有8条16位主总线:4条程序/数据总线和4条对应的地址总线。

1条程序总线(PB):传送自程序储存器的指令代码和立即操作数。

3条数据总线(CB、DB、EB):CB和EB传送从数据存储器读出的操作数;EB传送写到存储器中的数据。

4条地址总线(PAB、CAB、DAB、EAB)传送相应指令所需要的代码4存储器的分类:64k字的程序存储空间、64K字的数据存储空间和64K字的I/O空间(执行4次存储器操作、1次取指、2次读操作数和一次写操作数。

5存储器空间分配片内存储器的形式有DARAM、SARAM、ROM 。

RAM安排到数据存储空间、ROM构成程序存储空间。

(1)程序空间:MP/MC=1 40000H~FFFFH 片外MP/MC=0 4000H~EDDDH 片外FF00H~FFFFH 片内OVL Y=1 0000H~007FH 保留0080H~007FH 片内OVL Y=0 0000H~3FFFH片外(2)数据空间:DROM=1 F000H~F3FFH 只读空间FF00H~FFFH保留DROM=0 F000H~FEFFH 片外6数据寻址方式(1)立即寻址(2)绝对寻址<两位>(3)累加器寻址(4)直接寻址@<包换数据存储器地址的低7位>优点:每条指令只需一个字(5)间接寻址*按照存放某个辅助寄存器中的16位地址寻址的AR0~AR7(7)储存器映像寄存器寻址(8)堆栈寻址7寻址缩写语Smem:16位单寻址操作数Xmem Ymem 16位双dmad pmad PA16位立即数(0-65535)scr源累加器dst目的累加器lk 16位长立即数8状态寄存器ST0 15~13ARP辅助寄存器指针12TC测试标志位11C进位位10累积起A 的一出标志位OV A 9OVB 8~0DP数据存储器页指针9状态寄存器ST1 CPL:直接寻址编辑方式INTM =0开放全部可屏蔽中断=1关闭C16 双16位算数运算方式10定点DSP 浮点DSP:定点DSP能直接进行浮点运算,一次完成是用硬件完成的,而浮点需要程序辅助。

soundmagus dsp t8说明书

soundmagus dsp t8 说明书

1、功放机的输出功率要和音箱的功率匹配,不要用过大功率的功放机去推过小功率的音箱或用过小功率的功放机去推过大功率的音箱。

2、开机前检查,主音量控制旋钮是否处于关的位置,高低音控制旋钮是否调到较小位置,如果不是那就要调回,这样可以防止因开机产生的脉冲信号,使功放机过载,烧毁功放机或音箱喇叭。

3、开机时,先开启其他音响设备,然后翻开功放机。

关机时,先关闭功放机,后关闭其他音响设备,这样可以防止因开、关其他音响设备产生脉冲信号,使功放机过载。

4、功放机工作时•,音量要由关调到大,直到适中。

关闭时、音量由大调到关,然后关闭功放机电源。

dsp概述

DSP概述[转]默认分类2006-11-12 12:12:12 阅读44 评论1 字号:大中小订阅引言:DSP(digital singnal processor)是一种微处理器,它接收模拟信号,转换为0或1的数字信号,再对数字信号进行修改、删除、强化,并在其他系统芯片中把数字数据解译回模拟数据或实际环境格式。

DSP最突出的两大特色是强大数据处理能力和高运行速度,加上具有可编程性,实时运行速度可达每秒数以千万条复杂指令程序,远远超过通用微处理器,有业内人士预言,DSP将是未来集成电路中发展最快的电子产品,并成为电子产品更新换代的决定因素。

DSP的发展历程:在DSP出现之前,MPU(微处理器)承担着数字信号处理的任务,但它的处理速度较低,无法满足高速实时的要求。

70年代时, DSP的理论和算法基础被提出。

但当时DSP仅仅局限于在教科书,即使是研制出来的DSP系统也是由分立组件组成的,其应用领域仅限于军事、航空航大部门。

到了20世纪60年代,计算机和信息技术的飞速发展为DSP提供了长足进步的机会。

1982年美国德州仪器公司(TI公司)生产出了第一代数字信号处理器(DSP)TMS320C10,这种DSP器件采用微米工艺NMOS技术制作,虽功耗和尺寸稍大,但运算速度却是MPU的几十倍,这种数字信号处理器一面世就在语音合成和编码解码器中得到了广泛应用。

接下来,随着CMOS技术的进步与发展,第二代基于CMOS工艺的DSP芯片应运而生,其存储容量和运算速度成倍提高,成为语音处理、图像硬件处理技术的基础。

80年代后期,第三代DSP芯片问世,运算速度得到进一步提高,这使其应用范围逐步扩大到了通信和计算机领域。

90年代是DSP发展的重要时期,在这段时间第四代和第五代DSP器件相继出现。

目前的DSP属于第五代产品,与第四代相比,第五代DSP系统集成度更高,它已经成功地将DSP芯核及外围组件综合集成在单一芯片上。

这种高集成度的DSP芯片在通信、计算机领域大行其道,近年来已经逐渐渗透到人们日常消费领域,前景十分看好。

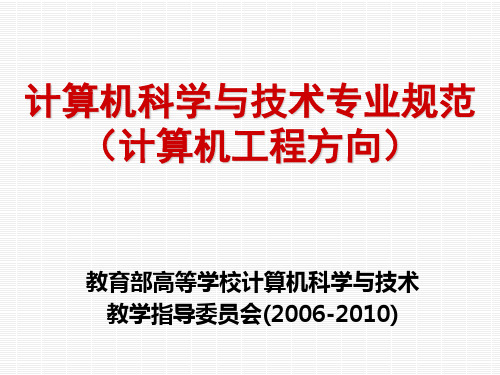

教育部高等学校计算机科学与技术教学指导委员会(200646;46;46;

DSP7 离散时间信号 DSP8 窗口函数 DSP9 卷积 DSP10 音频处理 DSP11 图象处理

ELE11 数据转换电路 ELE12 电压和电流来源 ELE(20)

CE-HCI 人机交互 (13)

ESY0 历史与概述[1] ESY1 嵌入式微控制器 [6] ESY2 嵌入式程序[3] ESY3 实时操作系统[3] ESY4 低功耗计算 [2] ESY5 可靠系统设计 [2] ESY6 设计方法 [3]

教育部高等学校计算机科学与技术教学指导委员会(2006-2010)

表3-1 知识领域和知识单元

知识领域

知识单元(551核心学时)

知识单元(选修)

CE-ALG 算 ALG0 历史与概述[1] 法与复杂 ALG1 基本算法分析[9] 度 (35) ALG2 算法策略 [8]

ALG3 计算算法 [12] ALG4 分布式算法 [3] ALG5 算法复杂性 [2]

1、CE方向特点、人才培养的基本定位

计算机工程学是计算机科学和电子工 程的交叉学科。

计算机工程涉及了计算机、航空航天、 通信、能源、制造业、国防和电子工业等 绝大多数工业领域,设计从细小的微电子 集成电路芯片到芯片的集成系统以及高效 通信系统等高科技产品。

教育部高等学校计算机科学与技术教学指导委员会(2006-2010)

教育部高等学校计算机科学与技术教学指导委员会(2006-2010)

3、知识结构

CE-HCI 人机交互 CE-NWK 计算机网络 CE-OPS 操作系统 CE-PRF 程序设计基础 CE-SPR 社会和职业问题 CE-SWE 软件工程 CE-VLS VLSI设计与构造 CE-DSC 离散结构 CE-PRS 概率和统计

应用技术

DSP-8章数字IO

MCRA0—7定义A口, MCRA8—15定义B口 1:引脚定义为基本功能 0:引脚定义为I/O

I/O口复用控制寄存器A(MCRA)配置 位 0

1 2 3

位的名称

MCRA. 0 MCRA. 1 MCRA. 2 MCRA. 3

基本功能(MCRA.n=1) SCITXD SCIRXD XINT1 CAP1/QEP1

IOSFT_REG .usect .include .def .text CALL LDP LACL AND SACL LACL AND SACL LACL OR SACL LDP SPLK “.data0”,1 “F2407REGS.H” _c_int0

_c_int0 SYSINIT #DP_PF2 MCRA #000FFH MCRA MCRC #0FBFFH MCRC PBDATDIR #0FF00H PBDATDIR #5H #01,IOSFT_REG

引脚

与数字I/O有关的寄存器共有9个,这些寄存器被映射到存储器空间, 地址从7090H到709FH其中保留位是无效的,读时为0,写对它无影响。 数字I/O控制寄存器

地

址

存储寄存器

MCRA MCRB MCRC PADATDIR PBDATDIR PCDATDIR PDDATDIR PEDATDIR PFDATDIR

C7 DIR IOPC 7 C6 DIR IOPC 6 C5 DIR IOPC 5 C4 DIR IOPC 4 C3 DIR IOPC 3 C2 DIR IOPC 2 C1 DIR IOPC 1 C0 DIR IOPC 0

7. 端口D数据和方向控制寄存器(PDDATDIR)---地址709Eh

保留位 保留位

A7 DIR IOPA 7 A6 DIR IOPA 6 A5 DIR IOPA 5 A4 DIR IOPA 4 A3 DIR IOPA 3 A2 DIR IOPA 2 A1 DIR IOPA 1 A0 DIR IOPA 0

TH-DSP-8H 电容投切状态指示器 说明书

TH-DSP-8H电容投切状态指示器安 装 使 用 说 明 书辽宁天昊电力有限公司地址:辽宁省沈阳市和平区南五马路228号 电话:024-******** 83250088 传真:024-********邮编:110000一、 概述本产品为我公司最新研制,与本公司综合模块配套使用,替代传统的电容指示灯。

该产品集成化程度高,外型美观大方,通用仪表尺寸,安装方便,接线极为简单,能大大提高整柜生产效率,减少出错几率,整体提升产品质量。

本说明书适用产品型号及配套模块类型见下表(型号参见产品名牌或合格证)。

注:在选用指示器时应遵循以下原则,在同一R S 485总线上, 如果全是共补模块,则应选用共补方式的指示器; 如果全是分补模块,则应选用分补方式的指示器;如果是混合补偿方式,若共补模块数量没有超过23只,分补模块的数量没有超过9只,则可选用混补方式的指示器;若共补模块的数量超过23只或者分补模块的数量超过9只,则必须选用共补方式及分补方式的指示器。

二、 功能特点1) 显示面板上集成72只高亮L E D 指示灯,功耗小,亮度高。

混补方式的指示器:指示23只共补模块和9只分补模块; 共补方式的指示器:仅指示32只共补模块; 分补方式的指示器:仅指示24只分补模块。

注意:指示灯顺序对应机号顺序,不一定对应安装顺序。

2) 采用数字通讯方式,与综合模块交换信息,自动采集电容状态信号并快速刷新显示。

3) 自带通讯故障检测,当通讯总线故障或无通讯时,故障灯亮起,提示检查通讯线路。

三、 使用环境海拔高度≤3000m ,湿度≤90%(20℃),环境温度为—20℃~60℃,大气压力为79.5~106.0k p a ,无易燃易爆的介质存在,无导电尘埃及腐蚀性气体存在。

四、 技术参数额定电压:交流50H Z ,380V ±20%; 额定功耗:不大于3V A ;五、 机械安装和电气接线机械安装:在屏柜上开一113×113m m 的方孔,将本产品从屏前推入方孔内,把配给的紧固件插入安装槽中,上紧螺丝即可固定在屏上。

DSP与智能化系统------第8章 dsp硬件设计基础

二、DSP系统的设计思路

输

输

入 抗混

DSP

平滑 出

叠滤 A/D 芯片 D/A 滤波

波器

器

典型的DSP系统

20

1.总体方案设计

DSP应用

DSP系统设计前:

定义系统性能指标

•明确设计任务 •给出设计任务书

选择DSP芯片

功能描述准确

软件编程

硬件设计

功能描述清楚 描述的方式

软件调试

硬件调试

人工语言

系统集成

29

器件的选型原则 4

逻辑控制

先 确 定 所 用 器 件 , 如 PLD 、 EPLD或FPGA;

再根据自己的特长和公司芯片 的特点决定采用哪家公司的哪一 系列产品;

最 后 根 据 DSP 芯 片 的 频 率 决 定 芯片的工作频率,并以此来确定 使用的芯片。

30

器件的选型原则 5

通信接口

根据与其他系 统通信的速率 决定采用的通 信方式: 串口 并口 总线

INTEL&AD 的新DSP CORE 15

选择芯片考虑的因素

1.DSP芯片的运算速度 MAC时间:一次乘法和一次加法的时间。大部分 DSP芯片可在一个指令周期内完成一次乘法和一次 加法操作。 FFT执行时间:运行一个N点FFT程序所需时间。 由于FFT运算在数字信号处理中很有代表性,因此 FFT运算时间常作为衡量DSP芯片运算能力的一个指 标。 MIPS:每秒执行百万条指令。 MOPS:每秒执行百万次操作。 MFLOPS:每秒执行百万次浮点操作。 BOPS:每秒执行十亿次操作。

Target Application (目标应用)

» Digital Cres (双核心)

DSP厂商及选型参考

DSP厂商1.德州仪器公司众所周知,美国德州仪器(Texas Instruments,TI)是世界上最知名的DSP芯片生产厂商,其产品应用也最广泛,TI公司生产的丁MS320系列DSP芯片广泛应用于各个领域。

TI公司在1982年成功推出了其第一代DSP芯片TMS32010,这是DSP应用历史上的一个里程碑,从此,DSP芯片开始得到真正的广泛应用。

由于TMS320系列DSP芯片具有价格低廉、简单易用功能强大等特点,所以逐渐成为目前最有影响、最为成功的DSP系列处理器。

目前,TI公司在市场上主要有三大系列产品:(1)面向数字控制、运动控制的TMS320C2000系列,主要包括TMS320C24x/F24x、TMS320LC240x/LF240x、TMS320C24xA/LF240xA、TMS320C28xx等。

(2)面向低功耗、手持设备、无线终端应用的TMS320C5000系列,主要包括TMS320C54x,TMS320C54xx,TMS320C55x等。

(3)面向高性能、多功能、复杂应用领域的TMS320C6000系列,主要包括TMS320C62xx、TMS320C64xx、TMS320C67xx等。

2.美国模拟器件公司ADI公司在DSP芯片市场上也占有一定的份额,相继推出了一系列具有自己特点的DSP芯片,其定点DSP芯片有ADSP2101/2103/2105、ADSP2111/2115、ADSP2126/2162/2164、ADSP2127/2181、ADSP-BF532以及Blackfin系列,浮点DSP芯片有ADSP21000/21020、ADSP21060/21062,以及虎鲨TS101、TS201S。

Motorola公司Motorola公司推出的DSP芯片比较晚。

1986年该公司推出了定点DSP处理器MC56001;1990年,又推出了与IEEE浮点格式兼容的的浮点DSP芯片MC96002。

DSP工作原理

DSP工作原理DSP(数字信号处理)是一种通过数字计算来处理和分析信号的技术。

它广泛应用于通信、音频、视频、雷达、医学图象处理等领域。

本文将详细介绍DSP的工作原理,包括信号采样、数字滤波、快速傅里叶变换等关键概念和算法。

1. 信号采样信号采样是将连续的摹拟信号转换为离散的数字信号的过程。

在DSP中,采样频率是一个重要参数,它决定了信号的频率范围和分辨率。

采样定理规定,采样频率必须大于信号最高频率的两倍,以避免采样失真。

常用的采样定理包括奈奎斯特采样定理和香农采样定理。

2. 数字滤波数字滤波是DSP中常用的一种信号处理方法,用于去除信号中的噪声、干扰和不需要的频率成份。

常见的数字滤波器包括低通滤波器、高通滤波器、带通滤波器和带阻滤波器。

数字滤波器可以通过差分方程、频域变换或者滤波器系数等方式实现。

3. 快速傅里叶变换(FFT)快速傅里叶变换是一种高效的算法,用于将时域信号转换为频域信号。

它可以快速计算出信号的频谱信息,包括频率和幅度。

FFT算法的核心思想是将信号分解为多个频率分量,并通过递归计算来提高计算效率。

FFT广泛应用于频谱分析、信号合成、滤波器设计等领域。

4. 数字信号处理器(DSP芯片)DSP芯片是专门设计用于执行数字信号处理任务的集成电路。

它具有高性能、低功耗和丰富的外设接口等特点,适合于实时信号处理和嵌入式系统。

常见的DSP芯片包括TI的TMS320系列、ADI的Blackfin系列和Freescale的DSP56800系列等。

5. 应用案例DSP在通信领域的应用非常广泛。

例如,手机中的语音信号经过DSP处理后可以实现降噪、回声抑制和语音编解码等功能。

在音频领域,DSP可以实现音频信号的均衡、混响和音效处理等。

此外,DSP还被广泛应用于雷达信号处理、医学图象处理和视频编码等领域。

总结:DSP工作原理涉及信号采样、数字滤波、快速傅里叶变换和DSP芯片等关键概念和算法。

通过采样将连续的摹拟信号转换为离散的数字信号,然后利用数字滤波器去除噪声和不需要的频率成份,最后通过快速傅里叶变换将信号转换为频域信号。

DSP-定点和浮点数格式

0.0625 0.125 0.25

0.5 1

3)动态范围

动态范围:数据表示格式中可以表示的最大值与最小值之比

N位定点数的动态范围:

DR

=

fix

(2N

1

1

1) / 2n

/

2n

2N 1 1

用分贝表示为:

DRfix=20 log10 2N1 1 6.02(N 1) dB

00001000b - 00000110b 商数:00001101 余数:00000010b

⑥ ⑦

00000100b - 00000110b 余数(丢弃):11111110b 商数:00011010 余数:00000100b

00001000b - 00000110b 商数: 00110101 余数:00000010b

① 小数乘小数(n、m≠0,m≤ n)

例:两个相乘数分别为Q7和Q6格式,8位字长

两个定点小数作乘法运算,结果左移一位,保存高位得到 运算结果,结果为Qm(m≤ n)格式

0.1000000b(0.5 Q7 )

01.100000b(1.5 Q6 )

000.1100000000000b(0.75 Q13)

对于负数(最高位MSB为1),要先把它转化为无符号二进制数,再进 行计算,最后加上负号

位

7 MSB

6

5

4

3

2

1

0 LSB

二进制补码 0

1

0

1

0

0

1

1

Q0

符号 26

252423源自222120

Q4

符号 22

21

20

DSP 880

DSP8808进8出信号处理器DSP-880为8进8出DSP音频处理器,整机配置有24位AD/DA转换器、40位浮点DSP 和96KHz采样率,以此来保证高音质输出。

输入端各通道配备有650ms延时、31段图示均衡、8个参量均衡、全功能滤波器(最大48dB)和压限器。

输出端各通道配置为650ms延时、8个参量均衡、全功能滤波器(最大48dB)和峰值限幅器。

DSP-880可以单独控制,亦可通过随机附送电脑软件进行操作。

电脑连机方式多样化,可通过RS232、USB或网络端口连接,亦可使用无线路由器扩展无线应用;同一网络内,最多可容纳16台处理器互联。

综上所述,DSP-880实为专业安装和流动演出市场物美价宜之首选。

输入/输出输入阻抗>10KΩ输出阻抗50Ω最大声压级+20dBu模式电子均衡模拟音频功效频响+/-0.1dB(20至30kHz)动态范围115dB typical(unweighted)共模抑制比>100dB(50至10kHz)串扰<-100dB失真0.002%(1kHz@+4dBu)数字音频功效DSP40位浮点运算单元采样率96kHzADC/DAC24位高效能芯片传输延时 1.5ms音频调节参数增益-40至+15dB,0.25dB/级相位+/-延时最大650ms输入/输出均衡均衡8个输入/输出均衡模式参量均衡、高通、低通、Phase-1和Phase-2EQ增益-30至+15dB,0.25dB/级EQ带宽0.02to2.50Oct(Q=0.5至72)图示均衡每输入配有31段图示均衡,1/3Oct每级分频参数模式Butterworth,Linkwitz Riley,Bessel波峰6-48dB/Octave压限/限幅器阈值-20至+20dBu响应时间0.3至100ms释放时间为响应时间的2至32倍比率1:1至1:40(仅对压限器生效)接口模拟输入/输出Euro/Phoenix数字接口25针DB-25(AES/EBU)母头RS-232DB-9母头USB B类接头以太网RJ45(可通过无线路由器扩展无线连接)电源标准IEC插口总体规格电源90-265VAC(50/60Hz)–20VA尺寸19"x1.75"x9"(483x44x229mm)重量 4.6kg注意:规格参数如有变更,恕不另行通知。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

ey (n) 也是具有白噪声特性的随机信号。 也是具有白噪声特性的随机信号。

有限字长定点乘积运算过程: 有限字长定点乘积运算过程:

x(n)

ax(n)

y(n)

ˆ y(n)

ey (n)

制作: 制作:常军

第7页 2011-11-26 11:21

的统计特性: 有限字长误差 e y (n) 的统计特性 : 位定长数据, 采取舍入截尾处理) (采取舍入截尾处理 。 假定乘积结果为 L 位定长数据 , 采取舍入截尾处理 ) ( q 2 (2 − L ) 2 2 = 均值 mey = 0 , 方差 σ ey = 。 12 12

制作: 制作:常军

第5页 2011-11-26 11:21

8.2.2 量化噪声通过线性时不变(LTI)系统 量化噪声通过线性时不变( )

量化信号通过 LTI 系统: 系统: ˆ ˆ y(n) = x(n) ∗ h(n) = [ x(n) + e(n)] ∗ h(n) = y(n) + f (n) 其中, 为量化噪声输出。 其中, f (n) = e(n) ∗ h(n) 为量化噪声输出。 根据随机信号分析方法,量化噪声输出信号的统计特性参数为: 根据随机信号分析方法,量化噪声输出信号的统计特性参数为:

制作: 制作:常军

第3页 2011-11-26 11:21

A/D变换的量化效应 8.2 A/D变换的量化效应

8.2.1 A/D变换的量化效应分析 变换的量化效应分析

1、 A/D 变 换 过 程 数 学 描 述 : 、 A/D 变 换 用 于 对 采 样 信 号 进 行 数 字 化 。 其 数 学 描 述 为 : ˆ x ( n ) = Q [ x a ( nT )] = x ( n ) + e ( n ) , ˆ 有限精度) 其中 x ( n ) 为量化后的数字信号 ( 有限精度 ) x (n ) 为采样得到的离散 , 信 号 ( 无 限 精 度 ) e (n ) 为 量 化 误 差 信 号 ( 无 限 精 度 ) , 。

说明: 说明: 数字处理系统中数据的表示:定点制,浮点制。定点制便于硬件实现; 数字处理系统中数据的表示:定点制,浮点制。定点制便于硬件实现; 浮点制主要用于软件实现。 浮点制主要用于软件实现。 定点制精度有限,需要对数字信号处理过程进行特别处理( 定点制精度有限,需要对数字信号处理过程进行特别处理(有限字长效 )。浮点制处理精度高 基本可以看成无限精度(特别是在32bit , 浮点制处理精度高, 应)。浮点制处理精度高,基本可以看成无限精度(特别是在 双精度情况下),可以不考虑有限字长效应。 ),可以不考虑有限字长效应 双精度情况下),可以不考虑有限字长效应。所以本章讨论的有限字长 效应只针对定点制。 效应只针对定点制。 A/D变换器一般都是输出定点编码数据(如定点补码),相当于对理想 变换器一般都是输出定点编码数据( ),相当于对理想 变换器一般都是输出定点编码数据 如定点补码), 数据进行截尾和舍入后的值。所以和实际采样值有一定的误差, 数据进行截尾和舍入后的值。所以和实际采样值有一定的误差,并且会 产生一种量化噪声。是数字信号系统的一种主要误差。 产生一种量化噪声。是数字信号系统的一种主要误差。

定点数据的乘积运算数学描述: 定点数据的乘积运算数学描述: ˆ y(n) = Q[ax(n)] = ax(n) + ey (n) = y(n) + ey (n) ,

ˆ 为有限字长的数字信号(有限精度) 其中 y(n) 为有限字长的数字信号(有限精度) 。 根据定点数的运算规则, 位的定点数, 根据定点数的运算规则,若 x(n) 为 Lx 位的定点数,a 为 La 位定点 位数据 假如结果存储器长度小于 Lx+La, 数, 则乘积 ax(n) 应为 Lx+La 位数据。 就需要对结果进行截尾处理。 就需要对结果进行截尾处理。这样就引入误差 ey (n) 。与量化误差类似

制作: 制作:常军

第2页 2011-11-26 11:21

q2

) (3)

中间计算结果的有限字长误差: 中间计算结果的有限字长误差:由于机器的数据都是有限字长表

示在迭代计算过程中,该误差会积累,使系统输出逐渐偏离正常范围。 示在迭代计算过程中,该误差会积累,使系统输出逐渐偏离正常范围。 特别是定点制运算时误差影响更明显。 特别是定点制运算时误差影响更明显。 在系统中尽量采用较高精度的 浮点数表示; 改变计算过程减小误差积累; 计算过程中进行误差修正等 浮点数表示; 改变计算过程减小误差积累; 都是常用的方法。 都是常用的方法。

数字信号处理基础

第8章 有限字长效应

1 2011-11-26 11:21

8.1 引 言

用有限位二进制数表示序列数值形成的误差,称为量化误差。 用有限位二进制数表示序列数值形成的误差,称为量化误差。 量化误差 因量化误差引起的各种效应称为有限字长效应 有限字长效应。 因量化误差引起的各种效应称为有限字长效应。 在数字系统的数值化运算中,主要有三种计算和量化误差: 在数字系统的数值化运算中,主要有三种计算和量化误差: A/D变换的量化误差、计算系数的量化误差和中间结果的有限 变换的量化误差、 变换的量化误差 字长效应。 字长效应。

2 σx σ x2 SNR = 10 log10 ( 2 ) = 10 log10 ( 2 ) σe q 12 2 2 = 10 log10 (12 × 22 L ⋅ σ x ) = 6.02L + 10.79 + 10 log10 (σ x ) dB 可知, ,信噪比可提高约 可知,A/D 量化字长每增加 1 位(L+1) 信噪比可提高约 6dB。 ) ,

制作: 制作:常军

第9页 2011-11-26 11:21

讨论: 讨论:

讨论: 讨论: IIR滤波器中乘积运算的有限字长效应对输出的影响,可通过在乘积环 滤波器中乘积运算的有限字长效应对输出的影响, 滤波器中乘积运算的有限字长效应对输出的影响 节引入误差噪声信号,然后计算输出。 节引入误差噪声信号,然后计算输出。 由上例可以看出,有限字长效应误差噪声信号对输出的影响与IIR滤波 由上例可以看出,有限字长效应误差噪声信号对输出的影响与 滤波 器的运算过程(实现结构)有关。 器的运算过程(实现结构)有关。所以需要分析不同的实现结构下的有 限字长效应。 限字长效应。 乘积运算的有限字长效应与IIR滤波器的结构的关系: 滤波器的结构的关系: 乘积运算的有限字长效应与 滤波器的结构的关系 (1)直接型:乘积运算的舍入误差都要经过全部的反馈环节 , 所以有较 直接型: 直接型 乘积运算的舍入误差都要经过全部的反馈环节, 大的误差积累。 大的误差积累。 (2)级联型:舍入误差只经过其后的反馈环节 , 而不通过前面的反馈环 级联型: 级联型 舍入误差只经过其后的反馈环节, 因而误差比直接型的小。 节,因而误差比直接型的小。 (3)并联型:每个并联子网络的舍入误差只经过本子网络的反馈环节 , 并联型: 并联型 每个并联子网络的舍入误差只经过本子网络的反馈环节, 与其他并联子网络无关,因此误差的积累最小。 与其他并联子网络无关,因此误差的积累最小。 另外,对于级联型结构中不同的级联次序, 另外,对于级联型结构中不同的级联次序,乘积运算的舍入误差所引 起的输出噪声功率大小会不同。 起的输出噪声功率大小会不同。一般把级联子网络按反馈系数和增益由 大到小排列次序,效果较好。 大到小排列次序,效果较好。

( 1) A/D 变 换 的 量 化 误 差 : ) 相当于在信 号中 加入了均值为 0 , 方差 为 0, ( q 为量化等级 ) 12 的量化噪音 。其频谱 具有非常宽的频带 ,所以 不容易滤出 。通过 提 高 量 化 精 度 , 减 小 q 可 减 小 A/D 变 换 的 量 化 误 差 。

( 2) 计算系数的量化误差: 滤波器和其他运算中的系数( 常量 )的表 ) 计算系数的量化误差:滤波器和其他运算中的系数( 常量) 示有一定的误差。该误差与机器的字长有关。 示有一定的误差 。该误差与机器的字长有关 。这一误差会改变系统 特性,甚至可能引起系统不稳定。 特性 ,甚至可能引起系统不稳定 。如 IIR 波器中系数误差可能使靠 近单位圆的极点变化到单位圆上或圆外,引起系统不稳定。 近单位圆的极点变化到单位圆上或圆外 ,引起系统不稳定。所以在 系统 设 计 过 程中 , 就 应 考虑 允 许 的 系数 误 差 。

制作: 制作:常军

第4页 2011-11-26 11:21

的统计特性可知量化误差为一白噪声随机信号, 、 3、根据 e(n) 的统计特性可知量化误差为一白噪声随机信号,其特性可以 用均值和方差来描述: 用均值和方差来描述: q2 2 量化舍入处理: 量化舍入处理:均值 me = 0 ,方差 σ e = 。 12 q2 q 量化截尾处理: 量化截尾处理:均值 me = − ,方差 σ e2 = 12 2 其中 q = 2 − L 为 A/D 变换器的量化间距,L 为 A/D 字长(L 位)。 变换器的量化间距, 字长 。 量化噪声的信噪比(信号和噪声功率比 率比) 量化噪声的信噪比(信号和噪声功率比)为:

ˆ 则输出为 y ( n) = y ( n) + f ( n) ,

其中误差噪声信号的输出: 其中误差噪声信号的输出 : f ( n) = af ( n − 1) + e( n) ,

q2 −L σ2 = 为乘积运算结果字长位数。 其中 q = 2 , L 为乘积运算结果字长位数 。 f 2 12(1 − a )

第8页 2011-11-26 11:21

8.3.1 IIR滤波器的有限字长效应 滤波器的有限字长效应

IIR滤波器的实现是一个输入序列和输出序列的有反馈叠代运算。如果 波器的实现是一个输入序列和输出序列的有反馈叠代运算。 滤波器的实现是一个输入序列和输出序列的有反馈叠代运算 是采用有限字长定点运算,那么在计算过程会有截尾误差。 是采用有限字长定点运算,那么在计算过程会有截尾误差。根据上面的 分析相当于在系统中引入了误差噪声信号。 分析相当于在系统中引入了误差噪声信号。