PCI总线接口学习心得

PCI小结

PCI小结展开全文几个基本的问题:1)注册函数的问题:因为编写的PCI设备驱动,是为某一具体设备服务,而这一具体设备,虽为PCI设备,但其本质仍可划分为,字符设备,网络设备等。

因此在驱动程序初始化的时候,仍应该调用相应类型设备的驱动注册函数,对驱动进行注册,如,register_chrdev().register_sound_mixer,register_sound_midi,register_netdev等。

一定要区别pci_register_driver()函数。

参考:《嵌入式设计及linux驱动开发指南》及中国linux论谈-linux高级应用-linux内核技术版中的文章《PCI Device Driver编写》2)关于pci_register_driver()的问题:原以为这是一个注册PCI 设备的函数,但实际上,这是一个用于探测设备的函数。

以下为引用一文章中关于这一问题的描述:探测设备顾名思义探测设备就是要找到驱动需要控制的设备随着内核的不断升级目前主要有两种风格的设备探测方式两种方式的区别在于老的风格是手工探测而新的方式则把探测的任务交给系统中的PCI层由它来自动完成这样一来可以支持设备的热插拔因此非常的方便和灵活一般在内核中开发驱动程序建议使用新的也就是自动探测方式如果出于向后兼容的需要则仍然需要采用老的手工方式进行探测下面分别对这两种方式进行介绍(1) 新的探测方式:在驱动初始化代码中通过调用内核提供的一个函数pci_register_driver完成探测任务该函数的原型如下:int pci_register_driver(struct pci_driver *)struct pci_driver结构是个关键通过填写该结构的成员我们通知了PCI层需要被探测的设备的相关信息该结构包含如下成员:name:描述该驱动程序的名字id_table:指向设备驱动程序感兴趣的设备ID的一个列表Probe:指向一个函数对于每一个与id_table中的项匹配的且未被其他驱动程序处理的设备在执行pci_register_driver时候调用此函数或者如果是以后插入的一个新设备的话,只要满足上述条件也调用此函数Remove: 指向一个函数当该驱动程序卸载或者被该驱动程序管理的设备被卸下的时候将调用此函数Save_state:用于在设备被挂起之前保存设备的相关状态Suspend:挂起设备使之处于节能状态Resume:唤醒处于挂起态的设备enable_wake:使设备能够从挂起态产生唤醒事件(2) 老的探测设备方式相对来说这种方式已经应用比较广泛了主要是利用pcibios_xxx类型的函数来实现手工探测可以利用厂商id和设备id,或者设备分类代码,或者是厂商id设备id系统厂商id子系统设备id 四者联合这三种方式进行探测相应的函数分别使用pci_find_device(VENDOR_ID, DEVICE_ID, dev)pci_find_class(CLASS_ID, dev)pci_find_subsys(VENDOR_ID, DEVICE_ID, SUBSYS_VENDOR_ID, SUBSYS_DEVICE_ID, dev)可见,只是两种探测方法。

plc学习心得体会

plc学习心得体会plc学习心得体会(优秀8篇)plc学习心得体会要怎么写,才更标准规范?根据多年的文秘写作经验,参考优秀的plc学习心得体会样本能让你事半功倍,下面分享【plc学习心得体会(优秀8篇)】,供你选择借鉴。

plc学习心得体会篇1短短的四周实训过的很快,我们在老师的精心的教导下,更加进一步的了解PLC。

我不得不说的是,我为自己拥有这样的老师而自豪,首先他很有耐心,不管我们是什么小问题还是大问题,或其他问他,他都会慢慢的跟我们讲解,有时候我们还么理解,又反复去问孙老师,他总是面带微笑仔细的跟我们讲解。

PLC实训我们这是第二次了,不需要老师手把手的教,我们自己也会学着去做一点点,反正遇到问题还是的找老师来解决,我们要学着自己独立完成,完成每一个实训项目,其次我们也必须要通过实训与理论相结合,这样才能事半功倍。

plc实训心得体会5篇心得体会,学习心得在此实习中充分了解PLC操作程序,增强感性认识,并可从中进一步了解、巩固与深化已经学过的理论知识了解运作方式,将我们所学到的专业知识和具体实践相结合,以提高我们的专业综合素质和能力,当然也为了让我们对进入企业做好铺垫,,增强我们对所学专业的认识,提高学习专业知识的兴趣,切身体会到工作中不同当事人面临的具体工作与他们之间的互动关系,对针对这些操作每天都有不同的心得体会,而且发现了不同的问题,使我们在实习中充分发挥主观能动性,真正理解并吸收课堂中所学到的知识,为将来走上工作岗位打下良好基础。

今天我们有机会在实训课上接处PLC,有关的知识紧密的接合了起来,这让我们深刻明白学习是一个环环相扣的环节。

以便即将迈入社会的我们能够更好的适应以后的学习和工作。

plc学习心得体会篇2经过4周的实训已经结束了,在老师的带领下,收获颇为丰富,我又增加了许多PLC的专业知识。

最为突出的是,我学会了根据工程控制的要求设计流程图,并用顺序控制指令编写出正确的程序。

老师讲解之后,我初步了解了传送指令、七段译码指令、加一指令的使用。

pci卡设计心得

{

DWORD io_cf8;

DWORD io_cfc;

int i;

PCIE调试心得

PCIE 调试总结(2)配置空间和设备寄放器PCI总线支持三个独立的物理地址空间:存储器空间、IO空间和配置空间。

在每一个PCI设备中的每一个功能都有一个PCI配置空间,最大为256B。

各PCI功能的配置空间不是统一编址的,而是采纳一种ID的寻址方式,用总线号、设备号、功能号和寄放器号来唯一标识一个功能中的配置空间。

配置空间只能由处置器通过HOST桥来访问。

X86CPU能访问存储器或IO地址空间,但不支持直接访问配置地址空间。

PCI标准规定了X86CPU间接访问PCI配置空间的方式,通过HOST桥中映射为I/O的一个地址端口和一个数据端口来索引和访问。

在运算机上电的时候PCI设备列举[29],配置空间被PCIBIOS访问。

从中读取PCI设备的配置信息。

然后在系统的存储器和I/O地址空间内为其分派一片独立的存储器或I/O地址空间,并将所分派空间的起始地址写入每一个BAR,此地址确信了该设备作为完成者(目标)能够响应的地址范围。

在运算机上电以后运算机(或驱动程序)能够采纳两种方式访问设备寄放器:通过CPU专用的I/O指令或通过标准内存引用指令。

图4描述了这两种方式,下面对这些方式进行简单说明。

图3 CPU访问I/O与内存寄放器1)、I/O空间寄放器:一些CPU体系结构(尤其是Intel X86)在引用设备驱动程序时利用I/O机械指令。

这些特殊指令引用CPU上一个特定的引脚集合,因此为I/O设备概念了一个单独的总线和地址空间。

在此总线上的地址也被称作端口,而且与任何内存地址完全隔离。

在Intel X86体系结构中,I/O地址空间是64KB大小(16位),汇编语言概念两个指令用于此地址空间读取和写入端口:IN和OUT。

2)、内存映射寄放器:并非所有的CPU结构都需要一个独立的I/O地址空间,在这种情形下,设备寄放器的地址直接映射到CPU的内存空间。

暴露大量数据缓冲区的设备往往映射到内存空间(如视频卡和数据搜集卡),如此就使得高级语言能够更快更直接对他们进行访问。

pic学习心得

5.定时器

定时器是单片机的一个很重要的部分,用它可以产生很多不同的定时时间,来满足程序设计的不同需求.PIC16F616有三个定时器,分别是Timer0、Timer1、Timer2.它们的用法不是很相同,下面来分别谈谈这三个定时器的用法和设置问题.

(1)Timer0

Timer0是一个八位的计数器,它有一个八位的计数寄存器TMR0,八位的预分频器(与看门狗共用),可以选择内部或者是外部时钟源,有计数器溢出中断的功能.

Timer0可以作为一个定时器或者计数器来使用,与Timer0有关的寄存器有:TMR0,INTCON,OPTION_REG,TRISA.

2.PIC单片机的概述

PIC16F616是一款14引脚、8位的CMOS单片机.采用精简指令集,仅有35条指令,由于采用了数据总线和指令总线分离的哈佛总线结构,使得除少量指令不是单周期之外,大部分的指令都是单周期指令.这样有利于提高单片机的运行速度和执行效率.

PIC16F616 这款单片机供电电压可以在2V到5.5V之间,内部集成了一个RC振荡器,频率可以配置成8MHZ或者4MHZ,也可以用外部晶振提供时钟.内部集成有 AD转换、比较器等硬件模块,还具有上电复位、欠压复位、看门狗、代码保护等功能.三个定时器、PWM发生器等可以由用户编程.下面我来一一介绍关于 PIC单片机的这些模块和功能.

以 下是T1CON每个位的具体功能:bit1:Timer1是否开启位,当此位设为1时,Timer1开启,设为0时,Timer1关闭;bit2:时钟源 选择位,置1时,选择外部时钟(T1CK1引脚的上升沿),此位置0时,选择的是内部时钟,并且和T1ACS(寄存器CM2CON1中)配合,当 T1ACS位为0时,时钟为FOSC/4,当T1ACS位为1时,时钟为FOSC.bit2:T1SYNC:定时器1的外部时钟输入同步位,当 TMR1CS位为1、T1SYNC位为1,定时器1被设置成与外部时钟不同步,T1SYNC位为0时,定时器1被设置成与外部时钟同步模式.Bit3: T1OSCEN:此位为1时Timer1的时钟选择LP,为0时LP晶体被关闭.Bit5-4:T1CKPS:Timer1时钟的预分频系数设置,通过这 两位的是指,可以讲Timer1设置成1:1、1:2、1:4、1:8几种分频值.Bit6:TMR1GE:只有当TMR1ON位为1时才有效,当此位为 1时,Timer1计数被Timer1的门限控制,此位为0时,Timer1正常计数.Bit7:T1GINV:此位为1时,Timer1在门限为高时计 数,此位为0时,Timer1在门限为低时计数.

PCIe的原理及体系架构_学习笔记

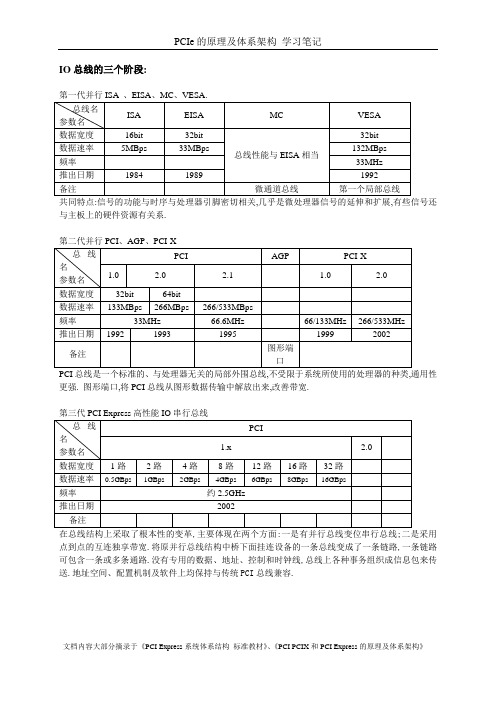

IO总线的三个阶段:第一代并行ISA 、EISA、MC、VESA.共同特点:信号的功能与时序与处理器引脚密切相关,几乎是微处理器信号的延伸和扩展,有些信号还与主板上的硬件资源有关系.第二代并行PCI、AGP、PCI-XPCI总线是一个标准的、与处理器无关的局部外围总线,不受限于系统所使用的处理器的种类,通用性更强. 图形端口,将PCI总线从图形数据传输中解放出来,改善带宽.第三代PCI Express高性能IO串行总线在总线结构上采取了根本性的变革,主要体现在两个方面:一是有并行总线变位串行总线;二是采用点到点的互连独享带宽.将原并行总线结构中桥下面挂连设备的一条总线变成了一条链路,一条链路可包含一条或多条通路.没有专用的数据、地址、控制和时钟线,总线上各种事务组织成信息包来传送.地址空间、配置机制及软件上均保持与传统PCI总线兼容.第一代和第二代都是并行总线,有多条地址线、数据线和控制线,挂接多个设备,称为下挂式总线(Multi-Drop),总线带宽由多个设备共享.通过提高数据宽度和频率来改善带宽的代价是挂接的电器负载减少(由于功耗增加和静态定时减少).PCIx与PCI相比:由于采用了PLL,频率更高性能更好;在地址和数据的基础上增加属性,从而可以高效管理缓冲区;分离事务协议相对延迟事务协议来说,提高了总线利用效率;可不需要中断引脚,改用消息信号中断(带内)体系结构,中断效率更高.基于PCI总线的结构最基本的PCI总线平台包含三级总线:FSB(Front-Side Bus)、PCI和ISA,FSB是处理器子系统的总线(Host总线),总线定义完全取决于系统所用的处理器;PCI局部总线是一个完全与处理器无关的总线,不受限微处理器的种类;ISA总线(IO扩展总线),也有采用EISA或MC总线的.不同的总线之间通过相应的桥芯片来连接.平台中两极桥是必须的,一是Host到PCI的(常称为主桥——Host桥),即北桥;另一个是PCI总线的桥(常称为扩展总线桥),即南桥.最基本的基于PCI总线的平台PCI地址空间映射x86 CPU的内存与I/O独立编址,I/O对应寄存器,内存对应RAM.因此,访问IO空间用IO读写指令,访问内存空间用内存读写指令.IO读写一般用于低速传输一些状态、控制寄存器的读写等。

pci-can总线互连技术学习总结

pci-can总线互连技术学习总结CAN是一种现场总线,串行通信网络,一种串行通信协议。

在CAN总线通信接口中集成了CAN协议的物理层和数据链路层,可完成对通信数据的成帧处理。

PCI-CAN总线适配器作为CAN总线与PCI总线的接口是完成PC 机与总线节点的数据通信的桥梁。

CAN报文有五种不同类型的帧:数据帧、远程帧、错误帧、超载帧、帧间隔。

数据帧和远程帧借助帧间隔同当前帧分离开,构成数据帧和远程帧的帧起始、仲裁场、控制场、数据场和CRC序列则借助位填充规则进行编码,其余位场采用固定格式不需要进行填充。

错误帧和超载帧同样是固定格式,不需要位填充的方法进行编码。

PCI总线信号(待细看)总线互连原理总线互连顾名思义,是用于连接多种总线数据传输协议,涉及到两种及两种以上的总线规范,协调几种规范间物理电气等几方面的问题,已完成数据通信。

无论是复杂的还是简单的总线协议都会规定一下四方面:物理、电气、逻辑、过程。

物理方面,指出连接器的硬件构成;电气方面,确定了接口电路信号的电压、宽度和他们的时间关系;逻辑方面,说明了如何把数据或字符变换成字段,以及说明传输控制字符的功能使用;过程方面,说明了通信控制字符的法定顺序、各种字段的法定内容以及控制数据流穿越接口的命令和应答。

PCI-CAN总线互连技术PCI总线用于典型的PC环境中是当前PC总线的主导,CAN总线则是典型的现场总线协议。

PCI-CAN总线互连由三大部分组成,CAN总线接口、PCI总线接口、CAN总线PCI总线间的I/O接口,每一部分需要一个或多个软件以支持正常工作。

软件如何实现?应完成哪些功能?由总线互连的具体功能决定。

(1)与CAN总线控制节点的数据传输,并完成对节点数据请求、节点参数修改、节点状态查询、实时报警等功能;(2)通过PCI总线实现与PC机的数据传输,PC机访问PCI-CAN适配卡,实现对总线节点的控制。

对于一个功能简单的PCI设备,不需要支持所有总线操作,在满足总线的安全性和稳定性的前提下,选择适当的PCI总线操作即可。

pci学习笔记

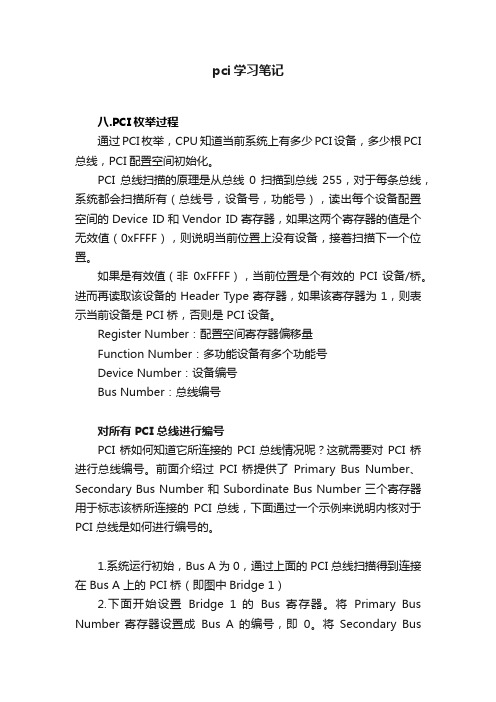

pci学习笔记八.PCI枚举过程通过PCI枚举,CPU知道当前系统上有多少PCI设备,多少根PCI 总线,PCI配置空间初始化。

PCI 总线扫描的原理是从总线0 扫描到总线255,对于每条总线,系统都会扫描所有(总线号,设备号,功能号),读出每个设备配置空间的Device ID和Vendor ID寄存器,如果这两个寄存器的值是个无效值(0xFFFF),则说明当前位置上没有设备,接着扫描下一个位置。

如果是有效值(非0xFFFF),当前位置是个有效的PCI 设备/桥。

进而再读取该设备的 Header Type 寄存器,如果该寄存器为 1,则表示当前设备是 PCI 桥,否则是 PCI 设备。

Register Number:配置空间寄存器偏移量Function Number:多功能设备有多个功能号Device Number:设备编号Bus Number:总线编号对所有 PCI 总线进行编号PCI 桥如何知道它所连接的 PCI 总线情况呢?这就需要对 PCI 桥进行总线编号。

前面介绍过PCI 桥提供了Primary Bus Number、Secondary Bus Number 和 Subordinate Bus Number 三个寄存器用于标志该桥所连接的PCI 总线,下面通过一个示例来说明内核对于PCI 总线是如何进行编号的。

1.系统运行初始,Bus A 为 0,通过上面的 PCI 总线扫描得到连接在 Bus A 上的 PCI 桥(即图中Bridge 1)2.下面开始设置Bridge 1 的Bus 寄存器。

将Primary Bus Number 寄存器设置成Bus A 的编号,即0。

将Secondary BusNumber 寄存器设置成 Bus B 的编号,它的值等于(Bus A + 1),也就是1。

由于暂时无法知道该桥所能访问的所有下行总线数目,Subordinate Bus Number 寄存器暂时设置成 0xFF。

PCIE基础知识总结

.PCIe总线概括跟着现代办理器技术的发展,在互连领域中,使用高速差分总线代替并行总线是大势所趋。

与单端并行信号对比,高速差分信号能够使用更高的时钟频次,进而使用更少的信号线,达成以前需要很多单端并行数据信号才能达到的总线带宽。

PCI总线使用并行总线构造,在同一条总线上的全部外面设施共享总线带宽,而PCIe总线使用了高速差分总线,并采纳端到端的连结方式,所以在每一条PCIe链路中只好连结两个设施。

这使得PCIe与PCI总线采纳的拓扑构造有所不一样。

PCIe总线除了在连结方式上与PCI总线不一样以外,还使用了一些在网络通讯中使用的技术,如支持多种数据路由方式,鉴于多通路的数据传达方式,和鉴于报文的数据传递方式,并充足考虑了在数据传递中出现服务质量QoS(QualityofService)问题。

PCIe总线的基础知识与PCI总线不一样,PCIe总线使用端到端的连结方式,在一条PCIe链路的两头只好各连结一个设施,这两个设施互为是数据发送端和数据接收端。

PCIe总线除了总线链路外,还拥有多个层次,发送端发送数据时将经过这些层次,而接收端接收数据时也使用这些层次。

PCIe总线使用的层次构造与网络协议栈较为近似。

端到端的数据传达PCIe链路使用“端到端的数据传递方式”,发送端和接收端中都含有TX(发送逻辑)和RX(接收逻辑),其构造如图4-1所示。

..由上图所示,在PCIe总线的物理链路的一个数据通路(Lane)中,由两组差分信号,共4根信号线构成。

此中发送端的TX零件与接收端的RX零件使用一组差分信号连结,该链路也被称为发送端的发送链路,也是接收端的接收链路;而发送端的RX零件与接收端的TX零件使用另一组差分信号连结,该链路也被称为发送端的接收链路,也是接收端的发送链路。

一个PCIe链路能够由多个Lane构成。

高速差分信号电气规范要求其发送端串接一个电容,以进行AC耦合。

该电容也被称为AC耦合电容。

PCIe链路使用差分信号进行数据传递,一个差分信号由D+和D-两根信号构成,信号接收端经过比较这两个信号的差值,判断发送端发送的是逻辑“1”仍是逻辑“0”。

关于总线接口学习心得

关于总线接口学习心得这几天一直在学习总线接口问题,使我在这些总线接口的理论学习上有了很大的提高,虽说现在还没有自己的思想,只能按着书本上的理论照搬,但我感觉还是学习到很多以前上课没有学习到的(主要是上课不认真吧,把老师教的都还给老师了)。

在此感谢艾德才所编著的《微机原理与接口技术》。

GPIO原理与结构GPIO是I/O的最基本形式,它是一组输入引脚或输出引脚,通常有两个控制器:数据方向寄存器和数据寄存器。

数据方向寄存器设置端口的方向,如果引脚设置为输出,那么数据寄存器控制着引脚状态,若引脚设置为输入,则此引脚由引脚上的逻辑店里层来实现对它的控制。

以sumsung公司的S3C2410嵌入式微处理器为列,S3C2410因其数据只能顺序访问linux字符设备,设备的file_operation结构定义如下:Struct file_operation S3C2410_gpio_fops={Read: S3C2410_gpio_read,Write: S3C2410_gpio_write,Open: S3C2410_gpio_open,Release: S3C2410_gpio_release,Ioctl: S3C2410_gpio_ioctl,Close: S3C2410_gpio_close,}键盘接口键盘的两种形式:线性键盘和矩阵键盘。

识别键盘上的比克键盘通常有两种方法:行扫描和行反转法。

行扫描法是矩阵最常见的方法:分两步操作。

1.识别键盘上哪一列的键被按下,让所有行线均为低电平,查询各列线电平是否为低,如果有列线为低,则说明该列有键按下,否则,没有键按下2.如果某列按键列下,识别哪一行按下,逐行置低电平,并置其余各行为高电平,查询各列的变化,如果列电平为低电平,则可确定此行此列处按键被按下。

键盘作为输入接口,实际上是用的非常多的,认真弄懂键盘接口,是非常有必要的!!!!串行接口(1)串行通信是指使数据一位一位地进行出书而实现的通信,与并行通信相比,串行通信具有传输线烧,成本低,特别适合远距离传输。

PCIE3.0标准学习总结

PCIE3.0标准学习总结11.介绍本章介绍了在PCI Express架构和关键概念的概述。

PCI Express是⼀种为多种类未来计算和通信平台互连⽽定义的⾼性能,通⽤I/ O。

关键的PCI属性,如它的使⽤模式,负载存储体系结构,软件接⼝,维持不变,⽽它的并⾏总线实施由⼀个⾼度可扩展的,完全串⾏接⼝取代。

利⽤PCI Express利⽤最新的点到点互连,基于交换机的技术,与分组交换协议,在性能和功能上提⾼到⼀个新⽔平。

PCI Express⽀持电源管理,服务质量(QoS),Hot-Plug/Hot-Swap ⽀持,数据完整性,可信的配置质量和错误处理等⾼级功能。

1.1第三代I/O互连第三代I/ O互连的⾼级别要求如下:⽀持多种细分市场和新兴的应⽤:统⼀桌⾯,移动,⼯作站,服务器,通信平台的I / O架构和嵌⼊式设备能够提供低成本,⾼容量的解决⽅案:结构在系统级等于或低于PCI成本⽀持多平台互联⽤途:芯⽚到芯⽚,板对板连接器或电缆通过新的机械形式的因素:易于移动的,PCI般的外形和模块化,盒外形PCI兼容的软件模型:能够使⽤不需要修改的PCI系统配置软件实现枚举和配置PCI Express硬件能够不需要修改引导现有的操作系统,能够不需要修改⽀持现有的任何的I / O设备驱动程序能够采⽤PCI配置范例配置/启⽤新的PCI Express功能性能:低开销,低延迟的通信带宽和有效载荷应⽤最⼤化链路效率每个针脚⾼带宽,以减少设备和连接器接⼝的针脚数通过聚合Lane和信号频率可扩展的性能⾼级功能:理解不同的数据类型和排序规则电源管理和预算能够识别电源管理能⼒通过⼀个给定的函数能够过渡到⼀个功能当进⼊特定的电源状态能够接收当前电源状态通知功能能够产⽣⼀个请求,唤醒从主电源断电状态能够为设备按照相应的平台电源预算策略顺序上电。

⽀持区分服务的能⼒,如:不同的服务质量(QoS)每个QoS数据流能有专⽤的链路资源,提⾼fabric效率和应⽤程序级的头⾯对队头阻塞的处理效率能够为每个组件配置fibric QoS仲裁策略能够为每个数据包端到端的QoS打上标记能够创建端到端的同步(基于时间,注⼊速率控制)解决⽅案可信配置⽀持能够⽀持受保护的从可信软件环境到可信配置空间的访问热插拔和热交换⽀持能够⽀持现有的PCI热插拔和热交换解决⽅案能够⽀持原⽣热插拔和热交换解决⽅案(没有边带信号需要)能够为所有形式因素⽀持统⼀的软件模型数据完整性能够⽀持所有的交易类型和数据链路链路数据包级别的数据完整性能够⽀持终端到终端的⾼可⽤性解决⽅案的数据完整性错误处理能够⽀持PCI -级的错误处理能够⽀持先进的错误报告和处理,以改善故障隔离和恢复解决⽅案独⽴⼯艺技术能够⽀持在发射器和接收器不同的直流共模电压易于测试能够通过简单的连接测试来测试设备电⽓规范1.2PCI Express链路⼀个链接表⽰两个组件之间的双-单⼯通信通道。

PIC学习心得

PIC学习⼼得PIC学习⼼得本次⼼得为PIC18F25K22上的代码零、配置CPU 的特殊功能,地址从300000开始,如以下,有晶振选择,复位功能,看门狗配置,调试⼝rb7-rb6的配置,因为RB6-RB7为串⼝2的端⼝,需要对应为位=1才能使得他们可以⽤于普通io,其实单⽚机默认也是1.对于已经⽤于特殊功能的引脚,⽐如已经配置了引脚为I2C功能,如果要配置为普通IO时,需要将I2C失能掉,SSPXCON1=0X00;这样才能正常使⽤这2个IO⼝了如果要使单⽚机使⽤内部晶振,就需要将对应的OSCCON位置1IRCF<2:0>:内部RC 振荡器频率选择位(2)IRCF<2:0>=111 = HFINTOSC – (16 MHz)OSTS=0 = 器件依靠内部振荡器(HFINTOSC、MFINTOSC 或LFINTOSC)运⾏OSCCON2默认使⽤内部晶振时,频率会随温度漂移,使⽤波特率的时候要注意了,最好使⽤外部晶振PWDX默认,使外围功能使能#pragma romdata CONFIG1H=0x300001 //晶振const rom unsigned char config1H = 0x0a; //setting for HS oscillator中档功耗#pragma romdata CONFIG2L=0x300002 //复位const rom unsigned char config2L = 0x00;#pragma romdata CONFIG2H=0x300003const rom unsigned char config2H = 0x1e; //WDT#pragma romdata CONFIG3H=0x300005//配置⼀些端⼝的映射const rom unsigned char config3H = 0x00; //禁⽤复位脚,开始为CPU提供时钟⽽⽆需等待#pragma romdata CONFIG4L=0x300006//最⾼位为1,RB6 和RB7⽤于普通IO ⼝const rom unsigned char config4L = 0x80; //RB6 和RB7专⽤于在线调试#pragma romdata⼀、中断配置,PIC只有⾼低2个优先级,对应的函数有2个,函数地址为0X08和0X18中断配置,⼀下为⾼低优先级配置RCONbits.IPEN=1;//使能中断优先级,如果IPEN配置为0,没有中断优先级,所有优先级都为⾼,调到0x08地址的中断INTCONbits.GIE=1;//=允许所有⾼优先级中断INTCONbits.PEIE=1;//=允许所有低优先级的中断2、中断函数写法⾼优先级地址为0X08#pragma code InterruptVectorHigh = 0x08void InterruptVectorHigh (void){_asmgoto InterruptHandlerHigh //jump to interrupt routine,goto之后的InterruptHandlerHigh函数名可以⾃⼰取名_endasm}// High priority interrupt routine#pragma code#pragma interrupt InterruptHandlerHigh //InterruptHandlerHigh函数名可以⾃⼰取名void InterruptHandlerHigh()//中断函数内容低优先级函数地址为0X18#pragma code InterruptVectorLow= 0x18void InterruptVectorLow (void){_asmgoto InterruptHandlerLow //jump to interrupt routine,goto之后的InterruptHandlerHigh函数名可以⾃⼰取名_endasm}// High priority interrupt routine#pragma code#pragma interruptlow InterruptHandlerLow //InterruptHandlerHigh函数名可以⾃⼰取名void InterruptHandlerLow(void) //中断函数内容3、例如串⼝中断配置:IPR1bits.RC1IP=0; //设为低优先级,让他跳⼊低优先级中断函数,为1将跳⼊⾼优先级函数PIR1bits.RC1IF=0; //清中断标志PIE1bits.RC1IE=1; //接收中断允许PIE1bits.TX1IE=0; //发送中断禁⽌4、这样配置完成后,如果串⼝其他寄存器配置⽆误,接收到数据后就会跳⼊低优先级函数InterruptHandlerLow中⼆、ADC1、ADC采集为了不浪费MCU资源,不⽤中断函数来采集配置如下,(1)先将要⽤于ADC采集的IO⼝配置为输⼊(2)将对应IO扣配置为ADC输⼊(3)配置ADCON0-3寄存器TRISA|=0x01;//引脚⽅向寄存器,1输⼊,0输出。

pcie学习计划

pcie学习计划一、入门阶段1. 了解PCIe的基本概念和原理在入门阶段,首先要对PCIe(Peripheral Component Interconnect Express)的基本概念和原理进行了解。

PCIe是一种用于连接扩展卡和主板的高速接口标准,它是PCI总线的后继者,在传输速度、带宽和功耗方面都有了显著的提升。

了解PCIe的发展历程、工作原理和技术特点,对后续的学习和应用都有很大的帮助。

2. 学习PCIe的物理层和数据链路层PCIe接口包括物理层和数据链路层两个部分,这两个部分是理解PCIe技术的关键。

在学习物理层时,要掌握信号传输的基本原理、组成部分和接口规范;在学习数据链路层时,要了解数据传输的机制、连接管理和控制流程。

对PCIe接口的物理层和数据链路层有深入的理解,有助于后续的应用和故障排除。

3. 学习PCIe的架构和规范PCIe接口有多个版本和规范,每个版本都有其特定的架构和规范。

在入门阶段,要学习PCIe的各个版本的架构和规范,包括连接类型、带宽规格、电气特性等。

对PCIe的各个版本的架构和规范有全面的了解,有助于选择合适的接口版本和了解其应用场景。

4. 学习PCIe的设备驱动开发PCIe接口的设备驱动开发是PCIe学习的重要内容之一。

在入门阶段,要学习PCIe设备驱动的基本概念、开发流程和调试技巧。

了解设备驱动的开发原理和方法,对后续的应用和系统优化都有很大的帮助。

二、进阶阶段1. 深入学习PCIe的协议和传输层PCIe接口的协议和传输层是PCIe学习的进阶内容,包括数据传输协议、报文格式、序列管理和错误控制等。

在进阶阶段,要深入学习PCIe接口的协议和传输层,包括数据包的格式、传输流程和错误检测与纠正等。

对PCIe接口的协议和传输层有深入的了解,有助于应用和系统性能的提升。

2. 学习PCIe的性能优化和调试技巧PCIe接口的性能优化和调试技巧是PCIe学习的重要内容之一。

在进阶阶段,要学习PCIe 接口的性能优化技巧,包括传输速度、带宽利用和延迟控制等。

2018年PCI心得

2018年PCI心得在研讨小组的观摩课上,有个家长说过一席话,我至今常常回味。

那家长说“刚开始,我们真的不明白怎么说说笑笑就一节课了呢?那么贵的学费啊。

直到孩子在生活中越来越快乐,越来越会玩游戏,主动性也越来越高时,我们才真正明白了其实说说笑笑一节课,远远比坐在那里教认知要难的多了。

”2017年六月,小鱼在儿童医院被诊断为“轻微自闭症”。

七月,在中山三院,医生问我儿童医院是怎么诊断的,我说轻微自闭症。

医生当时就尖声说道“就你这,还轻微自闭症,我看最少都是中度自闭症。

”是的,那时的小鱼,已经三岁了,却如一张白纸,没有语言,什么都不会。

八月,在三院参加家长培训会,第一次听到“RDI”时,我就感觉这套理念很好。

后来,我在“以琳自闭症论坛”上了解到杨教授。

当知道杨教授九月会来广州开讲座时,我如获至宝,马上报名。

第一次听杨教授的讲座,我恍然大悟。

我明白了原来我们可以这样去介入的。

我感觉自己找到了一个方向,不再懵懵懂懂。

2018年一月,我们非常荣幸的被选为研讨小组个案,由赖老师来小鱼。

这时的小鱼,开始有点点功能性语言,会表达我要什么。

但是在社会性上,小鱼还是一片空白,还依然沉浸在自我的世界里,对外界没有关注。

接下来的半年时间,我和赖老师不断的在失败中总结经验,对于我们来说,失败就像吃饭那么平常。

小鱼在上课时,很少有乐趣,基本抱着配合我们完成任务的心态。

此时的我,还抱着侥幸的心理,总是依赖着老师。

杨教授八月一对一点评小鱼的时候,赖老师生病没来,我完全无法介入小鱼。

从来都没有批评过家长的杨教授终于忍不住了,他委婉的说“妈妈做的很不够,最多只能评80分。

”我心里清楚,杨教授还是给我留了面子了。

到底该怎么做呢?我一筹莫展,焦虑绝望不断的纠缠着我。

我的情绪非常低落,又开始天天哭,甚至在路上也会一边走一边哭。

这段时间,小鱼似乎感应到了我的坏心情,状态也非常的低迷。

这时,guolan给我一条短信“其实,我可是杨教授的粉丝,真的想走南闯北的跟着他听讲座。

小强PCI6221阅读心得

1、NI_数据采集卡使用说明.pdf模拟输入的信号类型,一个电压源分为两类:接地信号和浮地信号。

三种测量方式:差分(DIFF);参考单端(RSE);非参考单端(NRSE)一般的,接地信号的测量,可以用差分或非参考单端方式;浮地信号的测量以上三种都行。

信号源必须有参考地AIGND(模拟地),若没有连接电阻,信号源浮地会导致读数不准。

信号源阻抗小于或大于100欧时有不同连线方式。

模拟输出,将输出正端接AOx,负端接AOGNDx。

这里给出部分采集卡的模拟输出的连接方法。

数字I/O,将输出正端接DIOx,负端接任意一个DGND。

这有部分关于数字I/O应用的连接方式。

计数器,测量和产生数字信号,常用于测量信号频率或者信号周期。

要明确指定节点执行的先后次序,就必须使用顺序结构来明确执行次序。

只要被调用VI程序定义了图标和连接器端口,就可以在任意一个VI程序的框图窗口里作为子程序调用。

数据采集VI程序的调用方法在数据采集子模板下,有六部分:模拟输入、模拟输出、数字I/O、计数器、校准和配置以及信号调理。

模拟输入与输出:在数据采集子模板下的模拟输入子模板程序执行模/数转换操作,模拟输出程序库执行数/模转换或多重转换。

扫描多个模拟输入通道,从多个输入通道以指定的采样率采集指定的采样点数,并将采样结果数据送回到计算机。

Channels控制栏制定要采样的多个通道的编号,各个通道号间以逗号隔开;控制栏Numbers of samples/ch是每个通道要采集的采样点数;Scan rate是每个通道没面中的采样点数即采样率。

Waveform是一个二维数组,包含模拟输入信号电压数值;Actual scan period是实际采样率的倒数。

连续数据采集:或者二说实时数据采集,是在不中断数据采集过程的情况下不断向计算机返回采集数据。

开始数据采集后,DAQ卡不断采集数据并将它们存储在指定的缓冲区中,LabVIEW每隔一段时间将一批数据送入计算机进行处理,如果缓冲区放满了,DAQ卡就会重新从内存起始位置写入新数据,覆盖原来的数据。

总线基本实验的实验心得

总线基本实验的实验心得

总线基本实验的实验心得

在进行总线基本实验的过程中,我学到了许多关于计算机硬件组成和数据传输的知识。

总线是计算机内部各个组件之间进行数据传输的通道,了解总线的原理对于理解计算机的工作原理至关重要。

在实验中,我们使用了一块开发板和一些简单的电路元件来模拟计算机内部的总线系统。

首先,我们学习了总线的基本分类,包括地址总线、数据总线和控制总线。

地址总线用于传输内存和外设的地址信息,数据总线用于传输实际的数据,控制总线用于传输控制信号。

我们进行了一些基本的实验,比如向特定地址写入数据、从特定地址读取数据等。

通过这些实验,我更加深入地了解了总线的工作原理。

我发现,当我们向特定地址写入数据时,数据会通过数据总线被传输到指定的地址;而当我们从特定地址读取数据时,数据会通过数据总线被传输到我们指定的接收器。

在实验过程中,我也遇到了一些问题。

比如,我在写入数据时经常会出现错误,导致数据传输不成功。

后来我发现,在编程时需要设置正确的地址和数据,同时还要确保总线的连接没有问题。

另外,我还发现,总线的传输速率也会影响数据传输的成功与否,因此在写入或读

取数据时需要根据总线的特性来设置合适的传输速率。

总的来说,总线基本实验是一个非常有趣和实用的实验。

通过这个实验,我不仅加深了对总线的理解,还提高了解决问题的能力。

我相信这些知识和经验对我今后的学习和工作都会有很大的帮助。

pcl课程设计心得体会400字

pcl课程设计心得体会400字通过此次pcl课程设计,使我更加扎实的掌握了有关高频电子线路方面的知识,在设计过程中虽然遇到了一些问题,但经过一次又一次的思考,一遍又一遍的检查终于找出了原因所在,也暴露出了前期我在这方面的知识欠缺和经验不足。

实践出真知,通过亲自动手制作,使我们掌握的知识不再是纸上谈兵。

过而能改,善莫大焉。

在课程设计过程中,我们不断发现错误,不断改正,不断领悟,不断获龋最终的检测调试环节,本身就是在践行“过而能改,善莫大焉”的知行观。

这次课程设计终于顺利完成了,在设计中遇到了很多问题,最后在老师的指导下,终于游逆而解。

在今后社会的发展和学习实践过程中,一定要不懈努力,不能遇到问题就想到要退缩,一定要不厌其烦的发现问题所在,然后一一进行解决,只有这样,才能成功的做成想做的事,才能在今后的道路上劈荆斩棘,而不是知难而退,那样永远不可能收获成功,收获喜悦,也永远不可能得到社会及他人对你的认可!课程设计诚然是一门专业课,给我很多专业知识以及专业技能上的提升,同时又是一门讲道课,一门辩思课,给了我许多道,给了我很多思,给了我莫大的空间。

同时,设计让我感触很深。

使我对抽象的理论有了具体的认识。

通过这次课程设计,我掌握了常用元件的识别和测试;熟悉了常用仪器、仪表;了解了电路的连线方法;以及如何提高电路的性能等等,掌握了焊接的方法和技术,通过查询资料,也了解了收音机的构造及原理。

我认为,在这学期的实验中,不仅培养了独立思考、动手操作的能力,在各种其它能力上也都有了提高。

更重要的是,在实验课上,我们学会了很多学习的方法。

而这是日后最实用的,真的是受益匪浅。

要面对社会的挑战,只有不断的学习、实践,再学习、再实践。

这对于我们的将来也有很大的帮助。

以后,不管有多苦,我想我们都能变苦为乐,找寻有趣的事情,发现其中珍贵的事情。

就像中国提倡的艰苦奋斗一样,我们都可以在实验结束之后变的更加成熟,会面对需要面对的事情。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

PCI总线接口学习心得

PCI总线概述

PCI 总线是一种时分复用的双向应答总线,属于公用时钟同步信号传输模式,工作频率一般为33MHz,也有使用66MHz的,其中传输发起方称为主设备,接收方称为从设备。

在PCI总线上最多可以支持10个外设。

一般POWERPC CPU可以带5个PCI从设备。

其主要接口信号图1所示,信号说明见表1。

图1 PCI接口主要信号示意图

PCI总线设计原则

表1 PCI接口信号描述

1、33M时钟频率的PCI总线在布线时,各PCI设备公用信号线的布线应该按照菊花链方式来进行约束和走线,第一个从设备和最后一个从设备到主设备之间的距离差不应超过5ns;从时钟驱动芯片到各PCI设备的时钟线应该保持等长,长度差范围在0.1ns以内。

当时钟频率为66MHz,可以参考33M时的布线原则,在约束上应根据频率作相应的修改。

PCI的公用信号线包括:AD[31:0],C/BE[3:0],DEVSEL#,FRAME#,IRDY#,LOCK#,PAR,SERR#,STOP#,TRDY#。

所谓菊花链走线方式,是指信号线先从PCI主设备连接到第一个PCI 从设备,再从第一个从设备连接到第二个从设备,依次直到连接到最后一个PCI从设备。

2、PCI设备的IDSEL,GNT#和REQ#信号,为PCI主设备和从设备点对点连接的方式,在走线上与PCI主设备到各PCI从设备的数据线保持等长。

3、由于PCI总线是利用信号反射来进行工作的,当时钟频率是33或者66MHz,为了降低布线难度,提高单板的生产直通率, PCI设备的信号线上可以不加串联匹配电阻。

为了防止PCI 设备的误操作,DEVSEL#,FRAME#,IRDY#,LOCK#,PAR,SERR#,STOP#,TRDY#一般要做上拉处理。

4、公用信号线不允许做终端端接处理。

5、PCI设备的RST#信号,在连接时要进行仿真,确保RST#的信号完整性,避免在RST#信号上有毛刺,产生误操作。

最好采用独立的复位信号连接到各PCI设备。