TLV2460中文文档

2460M产品简介

BAYER Desmodur 2460M用途介绍:(TDI替代品)

广泛用于制造聚氨酯合成革、人造革涂层、聚氨酯软泡、弹性纤维(即氨纶)、聚氨酯涂料、聚氨酯粘合剂,绝热、保温、保冷、轻工装潢、人造木材、建筑、防水堵墙等。作为异氰酸酯组份主要用于生产胶粘剂、密封剂、弹性铺装材料、鞋底及实心轮胎、涂料的预聚体,该产品也可用于制备聚氨酯塑胶跑道、喷涂聚脲弹性体、电器灌封胶、防水材料、弹性体、高回弹泡沫、半硬泡、汽车保险杠、挡泥板、减震器、阻流板等产品。

贮存温度:Desmodur 2460M随贮存时间的延长可生成二聚体不溶物,请在25℃~35

℃范围内贮存。

熔化条件:如果Desmodur 2460M的贮存温度低于17℃,将会出现结晶现象。必须立即在最短的时间内将结晶加热熔化。严禁局部过热,因为该产品在超过230℃会分解并产生气体。建议采用装有滚桶装置的热风烘箱于60℃烘化。烘化完成后,必须将桶内物料混合均匀。在滚桶烘化过程中,应严密注意料桶支撑点,以防出现磨损碰撞导致泄漏。

理化性能

项目

指标

执行标准号

纯度

≥99.6%

GB/T 13941

色数≤30(铂钴)号Fra bibliotekGB 3143

环己烷不溶物

≤0.3%

GB/T 13941

2,4异构体含量

45~55%

Model 2460 快速入门指南说明书

通过速度和简化重新设计测试和测量安全注意事项在使用本产品和任何相关仪器之前,请先阅读以下安全注意事项。

虽然一些仪器和附件通常在无害电压下使用,但是也可能出现对人体有害的情况。

本产品应由能辨别电击危险且熟悉避免潜在伤害的必要安全注意事项的合格人员使用。

使用此产品之前请仔细阅读并遵守所有的安装、操作和维护信息。

有关完整的产品规格,请参阅用户文档。

若以没有指定的方式使用产品,可能丧失产品保修所提供的保障。

产品的用户类型有:责任主体,是负责使用和维护机器,确保在设备规格和运行限制范围内使用设备,并确保操作人员经过充分培训的个人或小组。

操作人员,是负责使用产品特定功能的人员。

他们必须接受过电气安全流程和正确操作仪器方面的培训。

应当采取保护措施,防止他们遭到电击和触碰到危险的带电电路。

维护人员,负责产品日常维护以保持仪器运转正常,例如,设置线路电压或更换耗材。

用户文档中描述了维护步骤。

这些步骤都清楚描述了操作人员是否能够执行它们。

如果不能,那么只能由服务人员来执行这些操作。

服务人员,接受过培训,可操作带电电路,执行安全安装并修理产品。

只有受过正确训练的服务人员才能执行安装和服务流程。

美国吉时利仪器(Keithley Instruments) 公司的产品专门设计用于测量、控制和数据输入/输出连接等电气信号,而且不能直接连接到电网电压或具有瞬时高电压的电压源上。

Measurement Category II(引自IEC 60664 标准)连接要求针对本地交流电网连接经常发生的高瞬时电压采取保护措施。

某些吉时利测量仪器可以连接到电网上。

这些仪器将会标记为Category II 或更高级别。

除非在仪器规格、操作手册和仪器标签中明示允许,否则不要将任何仪器连接到电网上。

存在电击危险时,一定要小心谨慎。

电缆连接器插头或测试装置上可能存在致命电压。

美国国家标准学会(ANSI) 规定,超过30 V RMS、42.4V峰值或60 V DC 的电压水平存在电击的危险。

TLV320AC40资料

VBAP is a trademark of Texas Instruments Incorporated.PRODUCTION DATA information is current as of publication date.Products conform to specifications per the terms of Texas Instrumentsstandard warranty. Production processing does not necessarily includetesting of all parameters.元器件交易网IMPORTANT NOTICETexas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinueany product or service without notice, and advise customers to obtain the latest version of relevant informationto verify, before placing orders, that information being relied on is current and complete. All products are soldsubject to the terms and conditions of sale supplied at the time of order acknowledgement, including thosepertaining to warranty, patent infringement, and limitation of liability.TI warrants performance of its semiconductor products to the specifications applicable at the time of sale inaccordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extentTI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarilyperformed, except those mandated by government requirements.CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OFDEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICALAPPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, ORWARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHERCRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TOBE FULLY AT THE CUSTOMER’S RISK.In order to minimize risks associated with the customer’s applications, adequate design and operatingsafeguards must be provided by the customer to minimize inherent or procedural hazards.TI assumes no liability for applications assistance or customer product design. TI does not warrant or representthat any license, either express or implied, is granted under any patent right, copyright, mask work right, or otherintellectual property right of TI covering or relating to any combination, machine, or process in which suchsemiconductor products or services might be or are used. TI’s publication of information regarding any thirdparty’s products or services does not constitute TI’s approval, warranty or endorsement thereof.Copyright © 1998, Texas Instruments Incorporated。

TLV2262ID中文资料

1

元器件交易网

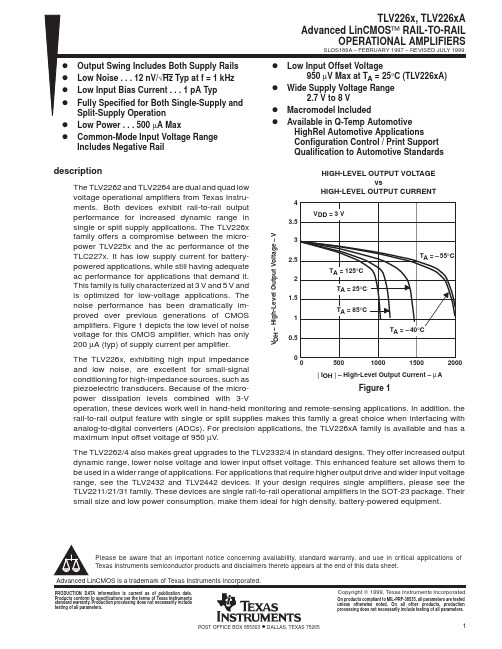

TLV226x, TLV226xA Advanced LinCMOS™ RAIL-TO-RAIL OPERATIONAL AMPLIFIERS

TLV2262 AVAILABLE OPTIONS PACKAGED DEVICES TA VIOmax AT 25°C 2.5 mV 950 µV µ 2.5 mV 950 µV µ 2.5 mV 950 µV 2.5 mV SMALL OUTLINE (D) TLV2262CD TLV2262AID TLV2262ID TLV2262AQD TLV2262QD — — CHIP CARRIER (FK) — — — — — TLV2262AMFK TLV2262MFK CERAMIC DIP (JG) — — — — — TLV2262AMJG TLV2262MJG PLASTIC DIP (P) TLV2262CP TLV2262AIP TLV2262IP — — — — TSSOP (PW) TLV2262CPWLE TLV2262AIPWLE — — — — — CERAMIC FLATPACK (U) — — — — — TLV2262AMU TLV2262MU

元器件交易网

TLV226x, TLV226xA Advanced LinCMOS™ RAIL-TO-RAIL OPERATIONAL AMPLIFIERS

SLOS186A – FEBRUARY 1997 – REVISED JULY 1999

D D D D D D

Output Swing Includes Both Supply Rails Low Noise . . . 12 nV/√Hz Typ at f = 1 kHz Low Input Bias Current . . . 1 pA Typ Fully Specified for Both Single-Supply and Split-Supply Operation Low Power . . . 500 µA Max Common-Mode Input Voltage Range Includes Negative Rail

TLV2460中文文档

增益带宽积(MHz)

电源电压(V) 温度(℃)

大信号波动(V)

小信号波动(V)

反向大信号波动(V)

反向小信号波动(V)

参数的测量方法

TLV246X家族系列运算放大器的应用

1.驱动容性负载

输出失调电压是输入失调电压和输入偏置电流乘以相应的增益的和,下面的原理图和公式可以用来计算输出失调电压。

2.一般的连接电路

温馨提示:买家在使用该款芯片的时候最好要去当地的经销商去实地查看一下元器件的焊接掩膜封装,放置由于厂家生产的时候改动了一些实际的封装而导致该封装与实际样板上面的封装不匹配。

该图片是向消费者展示该贴片封装的芯片的实物图从不同角度观察的视图

左上角:该芯片从左下角到左上角逆时针旋转依次对应该芯片的1——8脚,芯片体的长度在工业生产中对应4.30mm到4.50mm之间,在样板上芯片整体的长度为6.20mm到6.60mm之间,芯片引脚所占的空间为0.19mm到0.30mm之间,引脚与引脚之间的间距为0.65mm,故顾客在购买该款芯片的时候有较大的考虑余地也给实际制版带来了一定的方便

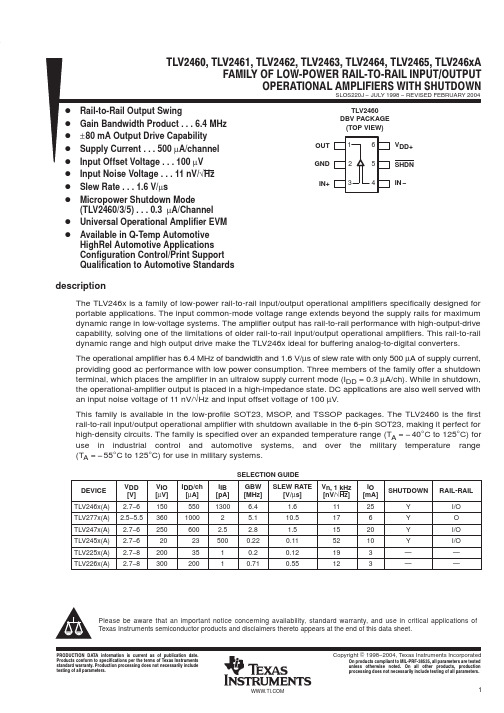

TLV2460/3/5为节省电池寿命有一个关断功能的便携式应用,电源电流降低至0.3μA/通道被禁用,放大器和输出置于高阻抗模式。为了使放大器,关闭终端可以悬空或拉到高。当关闭终端悬空,护理应采取措施,确保在关闭终端,寄生漏电流不不经意的地方进入关断的运算放大器。关闭终端的门槛总是引用到VDD / 2。因此,经营分割电源电压的设备(如:± 2.5 V)时,关闭终端需要拉至VDD(不接地)禁用运算放大器。

TLV5604中文资料

元器件交易网IMPORTANT NOTICETexas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinueany product or service without notice, and advise customers to obtain the latest version of relevant informationto verify, before placing orders, that information being relied on is current and complete. All products are soldsubject to the terms and conditions of sale supplied at the time of order acknowledgement, including thosepertaining to warranty, patent infringement, and limitation of liability.TI warrants performance of its semiconductor products to the specifications applicable at the time of sale inaccordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extentTI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarilyperformed, except those mandated by government requirements.CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OFDEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICALAPPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, ORWARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHERCRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TOBE FULLY AT THE CUSTOMER’S RISK.In order to minimize risks associated with the customer’s applications, adequate design and operatingsafeguards must be provided by the customer to minimize inherent or procedural hazards.TI assumes no liability for applications assistance or customer product design. TI does not warrant or representthat any license, either express or implied, is granted under any patent right, copyright, mask work right, or otherintellectual property right of TI covering or relating to any combination, machine, or process in which suchsemiconductor products or services might be or are used. TI’s publication of information regarding any thirdparty’s products or services does not constitute TI’s approval, warranty or endorsement thereof.Copyright © 1999, Texas Instruments Incorporated。

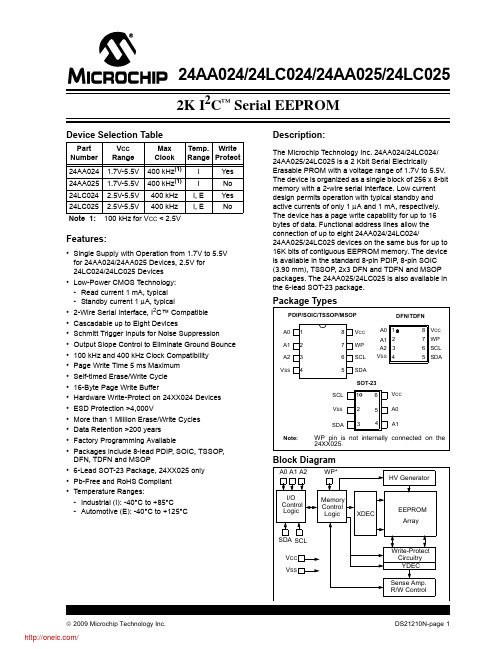

CAT24WC16WITE13F中文资料

V A2A0A1CAT24WC01/02/04/08/16ABSOLUTE MAXIMUM RATINGS*Temperature Under Bias .................–55°C to +125°C Storage Temperature.......................–65°C to +150°C Voltage on Any Pin withRespect to Ground (1)...........–2.0V to +V CC + 2.0V V CC with Respect to Ground ...............–2.0V to +7.0V Package Power DissipationCapability (Ta = 25°C)...................................1.0W Lead Soldering Temperature (10 secs)............300°C Output Short Circuit Current (2)........................100mA *COMMENTStresses above those listed under “Absolute Maximum Ratings ” may cause permanent damage to the device.These are stress ratings only, and functional operation of the device at these or any other conditions outside of those listed in the operational sections of this specification is not implied. Exposure to any absolute maximum rating for extended periods may affect device performance and reliability.RELIABILITY CHARACTERISTICS Symbol ParameterMin.Max.Units N END (3)Endurance 1,000,000Cycles/Byte T DR (3)Data Retention 100Years V ZAP (3)ESD Susceptibility 2000Volts I LTH (3)(4)Latch-up100mAD.C. OPERATING CHARACTERISTICSV CC = +1.8V to +5.5V, unless otherwise specified.Limits Symbol ParameterMin.Typ.Max.Units Test Conditions I CC Power Supply Current 3mA f SCL = 100 KHz I SB (5)Standby Current (V CC = 5.0V)1µA V IN = GND or V CC I LI Input Leakage Current 10µA V IN = GND to V CC I LO Output Leakage Current 10µA V OUT = GND to V CCV IL Input Low Voltage –1V CC x 0.3V V IH Input High VoltageV CC x 0.7V CC + 0.5V V OL1Output Low Voltage (V CC = 3.0V)0.4V I OL = 3 mA V OL2Output Low Voltage (V CC = 1.8V)0.5VI OL = 1.5 mA Note:(1)The minimum DC input voltage is –0.5V. During transitions, inputs may undershoot to –2.0V for periods of less than 20 ns. Maximum DCvoltage on output pins is V CC +0.5V, which may overshoot to V CC + 2.0V for periods of less than 20ns.(2)Output shorted for no more than one second. No more than one output shorted at a time.(3)These parameters are tested initially and after a design or process change that affects the parameter according to appropriate AEC-Q100and JEDEC test methods.(4)Latch-up protection is provided for stresses up to 100 mA on address and data pins from –1V to V CC +1V.(5)Maximum standby current (I SB ) = 10µA for the Automotive and Extended Automotive temperature range.CAPACITANCE T A = 25°C, f = 1.0 MHz, V CC = 5V Symbol TestMax.Units Conditions C I/O (3)Input/Output Capacitance (SDA)8pF V I/O = 0V C IN (3)Input Capacitance (A0, A1, A2, SCL, WP)6pFV IN = 0VCAT24WC01/02/04/08/16Note:(1)This parameter is tested initially and after a design or process change that affects the parameter.(2)t PUR and t PUW are the delays required from the time V CC is stable until the specified operation can be initiated.The write cycle time is the time from a valid stop condition of a write sequence to the end of the internal program/erase cycle. During the write cycle, the bus interface circuits are disabled, SDA is allowed to remain high, and the device does not respond to its slave address.Write Cycle Limits Symbol Parameter Min.Typ.Max Units t WRWrite Cycle Time10msPower-Up Timing(1)(2)Symbol ParameterMax.Units t PUR Power-up to Read Operation 1ms t PUWPower-up to Write Operation1msA.C. CHARACTERISTICSV CC = +1.8V to +5.5V, unless otherwise specified.Read & Write Cycle Limitsl o b m y S r e t e m a r a P 8.1-X X C W 42T A C XX C W 42T A C s t i n U V5.5-V 8.1V 5.5-V 5.2V 5.5-V 5.4.n i M .x a M .n i M .x a M .n i M .x a M F L C S yc n e u q e r F k c o l C 001001004z H k T I)1(t a t n a t s n o C e m i T n o i s s e r p p u S e s i o N st u p n I A D S ,L C S 002002002s n t A A K C A d n a t u O a t a D A D S o t w o L L C S tu O 5.35.31µs t FU B )1(e r o f e B e e r F e b t s u M s u B e h t e m i T t r a t S n a C n o i s s i m s n a r T w e N a 7.47.42.1µs t A T S :D H e m i T d l o H n o i t i d n o C t r a t S 446.0µs t W O L d o i r e P w o L k c o l C 7.47.42.1µs t H G I H do i r e P h g i H k c o l C 446.0µs t A T S :U S em i T p u t e S n o i t i d n o C t r a t S )n o i t i d n o C t r a t S d e t a e p e R a r o f (7.47.46.0µs t T A D :D H e m i T d l o H n I a t a D 000s n t T A D :U S e m i T p u t e S n I a t a D 050505s n t R )1(e m i T e s i R L C S d n a A D S 113.0µs t F)1(e m i T l l a F L C S d n a A D S 003003003s n t O T S :U S e m i T p u t e S n o i t i d n o C p o t S 446.0µs t HD em i T d l o H t u O a t a D 001001001snCAT24WC01/02/04/08/16FUNCTIONAL DESCRIPTIONThe CAT24WC01/02/04/08/16 supports the I 2C Bus data transmission protocol. This Inter-Integrated Circuit Bus protocol defines any device that sends data to the bus to be a transmitter and any device receiving data to be a receiver. Data transfer is controlled by the Master device which generates the serial clock and all START and STOP conditions for bus access. The CAT24WC01/02/04/08/16 operates as a Slave device. Both the Mas-ter and Slave devices can operate as either transmitter or receiver, but the Master device controls which mode is activated. A maximum of 8 devices (CAT24WC01 and CAT24WC02), 4 devices (CAT24WC04), 2 devices (CAT24WC08) and 1 device (CAT24WC16) may be connected to the bus as determined by the device address inputs A0, A1, and A2.PIN DESCRIPTIONSSCL: Serial ClockThe CAT24WC01/02/04/08/16 serial clock input pin is used to clock all data transfers into or out of the device.This is an input pin.SDA: Serial Data/AddressThe CAT24WC01/02/04/08/16 bidirectional serial data/address pin is used to transfer data into and out of the device. The SDA pin is an open drain output and can be wire-ORed with other open drain or open collector outputs.A0, A1, A2: Device Address InputsThese inputs set device address when cascading mul-tiple devices. When these pins are left floating the default values are zeros.A maximum of eight devices can be cascaded whenFigure 3. Start/Stop Timing5020 FHD F055020 FHD F03SCLSDA INSDA OUTSTART BITSDASTOP BITSCLCAT24WC01/02/04/08/16using either CAT24WC01 or CAT24WC02 device. All three address pins are used for these densities. If only one CAT24WC01 or CAT24WC02 is addressed on the bus, all three address pins (A0, A1and A2) can be left floating or connected to V SS .A total of four devices can be addressed on a single bus when using CAT24WC04 device. Only A1 and A2address pins are used with this device. The A0 address pin is a no connect pin and can be tied to V SS or left floating. If only one CAT24WC04 is being addressed on the bus, the address pins (A1 and A2) can be left floating or connected to V SS .Only two devices can be cascaded when using CAT24WC08. The only address pin used with this device is A2. The A0 and A1 address pins are no connect pins and can be tied to V SS or left floating. If only one CAT24WC08 is being addressed on the bus, the address pin (A2) can be left floating or connected to V SS .The CAT24WC16 is a stand alone device. In this case,all address pins (A0, A1and A2) are no connect pins and can be tied to V SS or left floating.WP: Write ProtectIf the WP pin is tied to V CC the entire memory array becomes Write Protected (READ only). When the WP pin is tied to V SS or left floating normal read/write operations are allowed to the device.I 2C Bus ProtocolThe following defines the features of the I 2C bus protocol:(1)Data transfer may be initiated only when the bus isnot busy.(2)During a data transfer, the data line must remain stable whenever the clock line is high. Any changes in the data line while the clock line is high will be interpreted as a START or STOP condition.START ConditionThe START Condition precedes all commands to the device, and is defined as a HIGH to LOW transition of SDA when SCL is HIG H. The CAT24WC01/02/04/08/16monitor the SDA and SCL lines and will not respond until this condition is met.STOP ConditionA LOW to HIGH transition of SDA when SCL is HIGH determines the STOP condition. All operations must end with a STOP condition.DEVICE ADDRESSINGThe bus Master begins a transmission by sending a START condition. The Master then sends the address of the particular slave device it is requesting. The four most significant bits of the 8-bit slave address are fixed as 1010 for the CAT24WC01/02/04/08/16 (see Fig. 5).The next three significant bits (A2, A1, A0) are the device address bits and define which device or which part of the device the Master is accessing. Up to eight CAT24WC01/02, four CAT24WC04, two CAT24WC08, and one CAT24WC16 may be individually addressed by the system. The last bit of the slave address specifies whether a Read or Write operation is to be performed.When this bit is set to 1, a Read operation is selected,and when set to 0, a Write operation is selected.After the Master sends a START condition and the slave address byte, the CAT24WC01/02/04/08/16 monitors the bus and responds with an acknowledge (on the SDA line) when its address matches the transmitted slaveFigure 4. Acknowledge Timing5020 FHD F06ACKNOWLEDGESTARTSCL FROM MASTERDATA OUTPUTFROM TRANSMITTERDATA OUTPUT FROM RECEIVERCAT24WC01/02/04/08/16address. The CAT24WC01/02/04/08/16 then performs a Read or Write operation depending on the state of the R/W bit.AcknowledgeAfter a successful data transfer, each receiving device is required to generate an acknowledge. The Acknowledg-ing device pulls down the SDA line during the ninth clock cycle, signaling that it received the 8 bits of data.The CAT24WC01/02/04/08/16 responds with an ac-knowledge after receiving a START condition and its slave address. If the device has been selected along with a write operation, it responds with an acknowledge after receiving each 8-bit byte.When the CAT24WC01/02/04/08/16 is in a READ mode it transmits 8 bits of data, releases the SDA line, and monitors the line for an acknowledge. Once it receives this acknowledge, the CAT24WC01/02/04/08/16 will continue to transmit data. If no acknowledge is sent by the Master, the device terminates data transmission and waits for a STOP condition.WRITE OPERATIONSByte WriteIn the Byte Write mode, the Master device sends the START condition and the slave address information (with the R/W bit set to zero) to the Slave device. After the Slave generates an acknowledge, the Master sends the byte address that is to be written into the address pointer of the CAT24WC01/02/04/08/16. After receiving another acknowledge from the Slave, the Master device transmits the data byte to be written into the addressed memory location. The CAT24WC01/02/04/08/16 ac-knowledge once more and the Master generates the STOP condition, at which time the device begins its internal programming cycle to nonvolatile memory. While this internal cycle is in progress, the device will not respond to any request from the Master device.Page WriteThe CAT24WC01/02/04/08/16 writes up to 16 bytes of data in a single write cycle, using the Page Write operation. The Page Write operation is initiated in the same manner as the Byte Write operation, however instead of terminating after the initial word is transmitted,Figure 5. Slave Address Bits*A0, A1 and A2 correspond to pin 1, pin 2 and pin 3 of the device.**a8, a9 and a10 correspond to the address of the memory array address word.***A0, A1 and A2 must compare to its corresponding hard wired input pins (pins 1, 2 and 3).1010A2 A1 A0R/W1010A2A1a8R/W1010A2a9 a8R/W1010a10a9a8R/WCAT24WC01/02CAT24WC04CAT24WC08CAT24WC16CAT24WC01/02/04/08/1624WCXX F09Figure 7. Page Write Timing5020 FHD F08Figure 6. Byte Write Timing*P=7 for CAT24WC01 and P=15 for CAT24WC02/04/08/16* = Don't care for CAT24WC01BUS ACTIVITY:MASTERSDA LINEBYTE C KC KC KS T O C KC KS T A R SLAVE NOTE: IN THIS EXAMPLE n = XXXX 0000(B); X = 1 or 0WRITE PROTECTIONThe Write Protection feature allows the user to protect against inadvertent programming of the memory array.If the WP pin is tied to V CC , the entire memory array is protected and becomes read only. The CAT24WC01/02/04/08/16 will accept both slave and byte addresses,but the memory location accessed is protected from programming by the device ’s failure to send an acknowledge after the first byte of data is received.READ OPERATIONSThe READ operation for the CAT24WC01/02/04/08/16is initiated in the same manner as the write operation with the one exception that the R/W bit is set to a one.Three different READ operations are possible: Immediate Address READ, Selective READ and Sequential READ.Immediate Address ReadThe CAT24WC01/02/04/08/16’s address counter contains the address of the last byte accessed,incremented by one. In other words, if the last READ or WRITE access was to address N, the READ immediately following would access data from address N+1. If N=E (where E = 255 for 24WC02, 511 for 24WC04, 1023 for 24WC08, and 2047 for 24WC16), then the counter will 'wrap around' to address 0 and continue to clock out data. If N = E (where E = 127 for the CAT24WC01) the counter will not 'wrap around'.BYTE ADDRESSSLAVE ADDRESSSA C KA C KDATAA C K S T O P PBUS ACTIVITY:MASTERSDA LINES T A R T the Master is allowed to send up to fifteen additional bytes. After each byte has been transmitted the CAT24WC01/02/04/08/16 will respond with an acknowledge, and internally increment the low order address bits by one. The high order bits remain unchanged.If the Master transmits more than sixteen bytes prior to sending the STOP condition, the address counter ‘wraps around ’, and previously transmitted data will be overwritten.Once all sixteen bytes are received and the STOP condition has been sent by the Master, the internal programming cycle begins. At this point all received data is written to the CAT24WC01/02/04/08/16 in a single write cycle.Acknowledge PollingThe disabling of the inputs can be used to take advantage of the typical write cycle time. Once the stop condition is issued to indicate the end of the host ’s write operation,the CAT24WC01/02/04/08/16 initiates the internal write cycle. ACK polling can be initiated immediately. This involves issuing the start condition followed by the slave address for a write operation. If the CAT24WC01/02/04/08/16 is still busy with the write operation, no ACK will be returned. If the CAT24WC01/02/04/08/16 has completed the write operation, an ACK will be returned and the host can then proceed with the next read or write operation.CAT24WC01/02/04/08/165020 FHD F10Figure 8. Immediate Address Read TimingSCL SDA 8TH BIT STOPNO ACKDATA OUT89SLAVE ADDRESSSA C KDATAN O A C KS T O P PBUS ACTIVITY:MASTERSDA LINES T A R T Selective ReadSelective READ operations allow the Master device to select at random any memory location for a READ operation. The Master device first performs a ‘dummy ’write operation by sending the START condition, slave address and byte address of the location it wishes to read. After the CAT24WC01/02/04/08/16 acknowledge the word address, the Master device resends the START condition and the slave address, this time with the R/W bit set to one. The CAT24WC01/02/04/08/16 then responds with its acknowledge and sends the 8-bit byte requested. The master device does not send an acknowledge but will generate a STOP condition.Sequential ReadThe Sequential READ operation can be initiated by either the immediate Address READ or Selective READoperations. After the 24WC01/02/04/08/16 sends initial 8-bit byte requested, the Master will respond with an acknowledge which tells the device it requires more data. The CAT24WC01/02/04/08/16 will continue to output an 8-bit byte for each acknowledge sent by the Master. The operation is terminated when the Master fails to respond with an acknowledge, thus sending the STOP condition.The data being transmitted from the CAT24WC01/02/04/08/16 is outputted sequentially with data from address N followed by data from address N+1. The READ operation address counter increments all of the CAT24WC01/02/04/08/16 address bits so that the entire memory array can be read during one operation. If more than the E (where E = 255 for 24WC02, 511 for 24WC04,1023 for 24WC08, and 2047 for 24WC16) bytes are read out, the counter will “wrap around ” and continue to clock out data bytes. If N = E (where E = 127 for the CAT24WC01) the counter will not 'wrap around'.CAT24WC01/02/04/08/165020 FHD F12Figure 10. Sequential Read Timing24WCXX F11Figure 9. Selective Read TimingSLAVE ADDRESSSA C KN O A C K S T O P PBUS ACTIVITY:MASTERSDA LINES T A R T BYTE ADDRESS (n)S A C KDATA nSLAVE ADDRESSA C KS T AR T *BUS ACTIVITY:MASTERSDA LINEDATA n+xDATA nC KC KDATA n+1C KS T O O A C KDATA n+2C KSLAVE ADDRESSCAT24WC01/02/04/08/16Notes:plies with JEDEC Publication 95 MS001 dimensions; however, some of the dimensions may be more stringent.2.All linear dimensions are in inches and parenthetically in millimeters.0.100 (2.54)BSC8-LEAD 300 MIL WIDE PLASTIC DIP (P, L, GL)8-LEAD 150 MIL WIDE SOIC (J, W, GW)Notes:plies with JEDEC publication 95 MS-012 dimensions; however, some dimensions may be more stringent.2.All linear dimensions are in inches and parenthetically in millimeters.CAT24WC01/02/04/08/1611Doc. No. 1022, Rev. N© 2005 by Catalyst Semiconductor, Inc.Characteristics subject to change without noticeSECTION A - ANotes:(1)All dimensions are in mm Angles in degrees.2Does not include Mold Flash, Protrusion or Gate Burrs. Mold Flash, Protrusions or Gate Burrs shall not exceed 0.15 mm. per side. 3Does not include Interlead Flash orProtrusion. Interlead Flash or Protrusion shall not exceed 0.25 mm per side. 4Does not include Dambar Protrusion, allowable Dambar Protrusion shall be 0.08 mm.(5)This part is compliant with JEDEC Specification MO-187 Variations AA.(6) Lead span/stand off height/coplanarity are considered as special characteristics. (S)(7) Controlling dimensions in inches. [mm]CAT24WC01/02/04/08/1612Doc. No. 1022, Rev. N© 2005 by Catalyst Semiconductor, Inc.Characteristics subject to change without notice8-LEAD TSSOP (U, Y, GY)CAT24WC01/02/04/08/1613Doc. No. 1022, Rev. N© 2005 by Catalyst Semiconductor, Inc.Characteristics subject to change without noticeORDERING INFORMATIONNotes:(1) The device used in the above example is a CAT24WC02JI-1.8TE13REV-E (SOIC, Industrial Temperature, 1.8 Volt to 5.5 VoltOperating Voltage, Tape & Reel, Die Revision E)** Available for CAT24WC01, CAT24WC02 and CAT24WC04Catalyst Semiconductor, Inc.Corporate Headquarters 1250 Borregas Avenue Sunnyvale, CA 94089Phone: 408.542.1000Fax: 408.542.1200Publication #:1022Revison:NIssue date:08/12/05Copyrights, Trademarks and PatentsTrademarks and registered trademarks of Catalyst Semiconductor include each of the following:DPP ™AE 2 ™Catalyst Semiconductor has been issued U.S. and foreign patents and has patent applications pending that protect its products. For a complete list of patents issued to Catalyst Semiconductor contact the Company’s corporate office at 408.542.1000.CATALYST SEMICONDUCTOR MAKES NO WARRANTY, REPRESENTATION OR GUARANTEE, EXPRESS OR IMPLIED, REGARDING THE SUITABILITY OF ITS PRODUCTS FOR ANY PARTICULAR PURPOSE, NOR THAT THE USE OF ITS PRODUCTS WILL NOT INFRINGE ITS INTELLECTUAL PROPERTY RIGHTS OR THE RIGHTS OF THIRD PARTIES WITH RESPECT TO ANY PARTICULAR USE OR APPLICATION AND SPECIFICALLY DISCLAIMS ANY AND ALL LIABILITY ARISING OUT OF ANY SUCH USE OR APPLICATION, INCLUDING BUT NOT LIMITED TO, CONSEQUENTIAL OR INCIDENTAL DAMAGES.Catalyst Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Catalyst Semiconductor product could create a situation where personal injury or death may occur.Catalyst Semiconductor reserves the right to make changes to or discontinue any product or service described herein without notice. Products with data sheets labeled "Advance Information" or "Preliminary" and other products described herein may not be in production or offered for sale.Catalyst Semiconductor advises customers to obtain the current version of the relevant product information before placing orders. Circuit diagrams illustrate typical semiconductor applications and may not be complete.REVISION HISTORYDate Rev.Reason2/3/2004HAdded: CAT24WC01/02/16 not recommended for new designs. See CAT24FC01, CAT24FC02 and CAT24FC16 data sheets5/28/2004I Added Die Revision to ordering information 7/28/2004J Update DC operating characteristics and notes 1/27/2005K Added Die Revision E to ordering information 2/28/2005L Edit Ordering Information 3/18/2005M Edit Features08/12/05NEdit FeaturesEdit Pin FunctionsEdit Reliability CharacteristicsEdit D.C. Operating Characteristics Edit A.C. Characteristics Add Package Dimensions Edit Ordering Information。

TLV2462AQPWR资料

TLV2460 DBV PACKAGE (TOP VIEW) OUT GND IN+ 1 2 3 6 5 4 VDD+ SHDN IN −

description

The TLV246x is a family of low-power rail-to-rail input/output operational amplifiers specifically designed for portable applications. The input common-mode voltage range extends beyond the supply rails for maximum dynamic range in low-voltage systems. The amplifier output has rail-to-rail performance with high-output-drive capability, solving one of the limitations of older rail-to-rail input/output operational amplifiers. This rail-to-rail dynamic range and high output drive make the TLV246x ideal for buffering analog-to-digital converters. The operational amplifier has 6.4 MHz of bandwidth and 1.6 V/µs of slew rate with only 500 µA of supply current, providing good ac performance with low power consumption. Three members of the family offer a shutdown terminal, which places the amplifier in an ultralow supply current mode (IDD = 0.3 µA/ch). While in shutdown, the operational-amplifier output is placed in a high-impedance state. DC applications are also well served with an input noise voltage of 11 nV/√Hz and input offset voltage of 100 µV. This family is available in the low-profile SOT23, MSOP, and TSSOP packages. The TLV2460 is the first rail-to-rail input/output operational amplifier with shutdown available in the 6-pin SOT23, making it perfect for high-density circuits. The family is specified over an expanded temperature range (TA = − 40°C to 125°C) for use in industrial control and automotive systems, and over the military temperature range (TA = −55°C to 125°C) for use in military systems.

TLC0820A中文资料

2008年北京市大学生电子设计竞赛芯片资料TLC372 双路通用LinCMOSTM 差动比较器∙单电源或双电源供电∙宽电源范围供电2V~18V∙5V电源时低漏电流150μA∙TTL输入电平时快速响应时间200ns∙内置ESD保护∙高输入阻抗典型值1012Ω∙外部低输入偏置电流典型值5PA∙超稳定的低输入偏置电压∙输入失调电压在最恶劣的输入条件下变化0.23μV/月,包括第一个30天∙共模输入电压包括地∙输出兼容TTL MOS CMOS∙引脚兼容LM393引脚功能∙1IN - 1路比较器反相输入∙1IN+ 1路比较器通向输入∙1OUT 1路比较器输出∙2IN - 2路比较器反相输入∙2IN+ 2路比较器同相输入∙2OUT 2路比较器输出∙GND 电源地∙VCC 电源正∙NC 空脚,不连接这个器件由两个独立电压比较器,使用LinCMOSTM工艺制造的,支持单电源。

输出是N 沟道漏极开路,实现正逻辑连接。

完全最大的测定值运行环境范围(除非另行注释)支持电压VDD(注释1)...............................................................+18V差分输入电压VID(注释2)...........................................................±18V输入电压范围.....................................................................-0.3~18V输出电压VO (18V)输入电流II ......................................................................±5mA输出电流IO.......................................................................20mA输出短路到地持续电流.............................................................无限制注释:1、差分电压除外,全部电压相对于地。

中国电信EVDO终端需求规范-Rev A数据终端AT命令接口分册-V1.0

保密等级:公开发放EVDO终端需求规范数据终端AT命令接口分册Teminal Requirement Specification of China Telecom Rev A Data Equipment AT Command Interface Fascicule(V1.0)××-××发布中国电信集团公司发布目 录目录 (I)前言 (IX)1适用范围 (10)2参考资料 (10)3缩略语 (10)4定义 (11)4.1 要求等级 (11)4.2 名词 (11)5数据卡客户端软件接口概述 (12)5.1 接口的设计原则 (12)5.2 接口的改动准则 (13)6基本命令 (14)6.1 回显命令E (14)6.1.1语法结构 (14)6.1.2接口描述 (14)6.1.3取值说明 (14)6.2 命令行结束符S3 (14)6.2.1语法结构 (14)6.2.2接口描述 (15)6.2.3取值说明 (15)6.3 响应格式字符S4 (15)6.3.1语法结构 (15)6.3.2接口描述 (15)6.3.3取值说明 (15)6.4 退格字符S5 (15)6.4.1语法结构 (15)6.4.2接口描述 (15)6.4.3取值说明 (16)6.5 ME响应格式命令V (16)6.5.1语法结构 (16)6.5.2接口描述 (16)6.5.3取值说明 (16)6.6 查询MS的所有ID信息I (16)I6.6.2接口描述 (16)6.6.3取值说明 (16)6.6.4举例说明 (17)6.7 查询MS当前所支持的传输能力域+GCAP (17)6.7.1语法结构 (17)6.7.2接口描述 (17)6.7.3取值说明 (17)6.7.4举例说明 (17)6.8 厂商信息查询命令+CGMI (17)6.8.1语法结构 (17)6.8.2接口描述 (17)6.8.3取值说明 (17)6.8.4举例说明 (18)6.9 产品名称查询命令+CGMM (18)6.9.1语法结构 (18)6.9.2接口描述 (18)6.9.3取值说明 (18)6.9.4举例说明 (18)6.10 软件版本号查询命令+CGMR (18)6.10.1语法结构 (18)6.10.2接口描述 (18)6.10.3取值说明 (18)6.11 ESN查询命令+GSN (19)6.11.1语法结构 (19)6.11.2接口说明 (19)6.11.3取值说明 (19)6.12 IMSI查询命令+CIMI (19)6.12.1语法结构 (19)6.12.2接口说明 (19)6.12.3取值说明 (19)6.12.4举例说明 (19)7分组域业务命令 (20)7.1 拨号呼叫发起命令D (20)7.1.1语法结构 (20)7.1.2接口说明 (20)7.1.3取值说明 (20)7.2 拨号挂断命令H (20)7.2.1语法结构 (20)7.2.2接口描述 (20)7.2.3取值说明 (20)8呼叫控制命令与方法 (20)II8.1.1语法结构 (20)8.1.2接口说明 (20)8.1.3取值说明 (21)8.2 接听命令A (21)8.2.1语法结构 (21)8.2.2接口说明 (21)8.3 呼叫挂断命令+CHV (21)8.3.1语法结构 (21)8.3.2接口说明 (21)8.4 来电指示RING (21)8.4.1语法结构 (21)8.4.2接口说明 (21)9网络服务相关命令 (21)9.1 PIN使能与查询功能命令+CLCK (21)9.1.1语法结构 (21)9.1.2接口描述 (22)9.1.3取值说明 (22)9.2 PIN修改密码命令+CPWD (23)9.2.1语法结构 (23)9.2.2接口描述 (23)9.2.3取值说明 (23)9.3 来电号码显示指示+CLIP (23)9.3.1语法结构 (23)9.3.2接口说明 (23)9.3.3取值说明 (23)9.3.4使用举例 (24)9.4 呼叫状态查询命令+CLCC (24)9.4.1语法结构 (24)9.4.2接口说明 (24)9.4.3取值说明 (24)10移动终端控制与状态命令 (25)10.1 操作模式设置命令+CFUN (25)10.1.1语法结构 (25)10.1.2接口描述 (25)10.1.3取值说明 (25)10.2 PIN管理命令+CPIN (26)10.2.1语法结构 (26)10.2.2接口描述 (26)10.2.3取值说明 (26)10.3 RSSI查询功能命令+CSQ (26)10.3.1语法结构 (26)III10.3.3取值说明 (27)10.4 HDR模式下信号格数查询命令^HDRCSQ (27)10.4.1语法结构 (27)10.4.2接口描述 (27)10.4.3取值说明 (27)10.5 耳机音量设置命令+CLVL (28)10.5.1语法结构 (28)10.5.2接口描述 (28)10.5.3取值说明 (28)10.6 麦克静音设置命令+CMUT (28)10.6.1语法结构 (28)10.6.2接口描述 (28)10.6.3取值说明 (28)10.7 电话本内存选择命令+CPBS (29)10.7.1语法结构 (29)10.7.2接口描述 (29)10.7.3取值说明 (29)11移动终端报错命令 (29)11.1 终端报错命令+CMEE (29)11.1.1语法结构 (29)11.1.2接口描述 (29)11.1.3取值说明 (30)12短信文本模式命令 (30)12.1 短信存储选择命令+CPMS (30)12.1.1语法结构 (30)12.1.2接口描述 (30)12.1.3取值说明 (30)12.2 设置短信格式命令+CMGF (31)12.2.1语法结构 (31)12.2.2接口描述 (31)12.2.3取值说明 (31)12.3 新短信通知设置命令+CNMI (32)12.3.1语法结构 (32)12.3.2接口描述 (32)12.3.3取值说明 (32)12.3.4应用举例 (34)12.4 短信到达指示+CMTI (34)12.4.1语法结构 (34)12.4.2接口描述 (34)12.4.3取值说明 (34)12.5 新收到的短信状态报告+CDSI (35)IV12.5.2接口描述 (35)12.5.3取值说明 (35)12.6 删除短信命令+CMGD (35)12.6.1语法结构 (35)12.6.2接口描述 (35)12.6.3取值说明 (35)12.7 新短信确认命令+CNMA (36)12.7.1语法结构 (36)12.7.2接口描述 (36)13移动终端控制和状态扩展接口 (36)13.1 硬件版本号查询功能命令^HWVER (36)13.1.1语法结构 (36)13.1.2接口描述 (36)13.1.3取值说明 (36)13.2 PIN管理命令^CPIN (37)13.2.1语法结构 (37)13.2.2接口描述 (37)13.2.3取值说明 (37)14语音呼叫扩展接口 (38)14.1 呼叫发起指示^ORIG (38)14.1.1语法结构 (38)14.1.2接口说明 (38)14.1.3取值说明 (38)14.1.4举例 (38)14.2 呼叫接通指示^CONN (38)14.2.1语法结构 (38)14.2.2接口说明 (38)14.2.3取值说明 (38)14.3 通话结束指示^CEND (39)14.3.1语法结构 (39)14.3.2接口说明 (39)14.3.3取值说明 (39)14.4 二次拨号命令^DTMF (41)14.4.1语法结构 (41)14.4.2接口说明 (42)14.4.3取值说明 (43)14.5 语音模式切换命令^CVOICE (43)14.5.1语法结构 (43)14.5.2接口描述 (43)14.5.3取值说明 (43)14.6 设置语音输出端口命令^DDSETEX (44)V14.6.2接口描述 (44)14.6.3取值说明 (44)15短信业务扩展接口 (44)15.1 短信存储介质满上报^SMMEMFULL (44)15.1.1语法结构 (44)15.1.2接口描述 (44)15.1.3取值说明 (44)15.2 新短信直接上报指示^HCMT (45)15.2.1语法结构 (45)15.2.2接口描述 (45)15.2.3取值说明 (45)15.3 新短信状态报告直接上报指示^HCDS (45)15.3.1语法结构 (45)15.3.2接口描述 (45)15.3.3取值说明 (45)15.4 选择短信参数命令^HSMSSS (46)15.4.1语法结构 (46)15.4.2接口描述 (46)15.4.3取值说明 (46)15.5 短信发送命令^HCMGS (46)15.5.1语法结构 (46)15.5.2接口说明 (47)15.5.3取值说明 (47)15.6 短信存储命令^HCMGW (47)15.6.1语法结构 (47)15.6.2接口说明 (47)15.6.3取值说明 (48)15.7 短信列表命令^HCMGL (49)15.7.1语法结构 (49)15.7.2接口描述 (50)15.7.3取值说明 (50)15.8 读取一条短信命令^HCMGR (50)15.8.1语法结构 (50)15.8.2接口描述 (50)15.8.3取值说明 (51)15.9 短信发送成功上报指示^HCMGSS (51)15.9.1语法结构 (51)15.9.2接口描述 (51)15.9.3取值说明 (52)15.10 短信发送失败上报指示^HCMGSF (52)15.10.1语法结构 (52)15.10.2接口描述 (52)VI16电话本业务扩展接口 (53)16.1 电话本读取命令^CPBR (53)16.1.1语法结构 (53)16.1.2接口描述 (53)16.1.3取值说明 (53)16.2 电话本写命令^CPBW (54)16.2.1语法结构 (54)16.2.2接口描述 (54)16.2.3取值说明 (54)16.2.4举例说明 (55)17网络服务相关扩展接口 (55)17.1 HDR RSSI格数变化指示^HRSSILVL (55)17.1.1语法结构 (55)17.1.2接口描述 (55)17.1.3取值说明 (55)17.2 系统模式变化事件指示^MODE (56)17.2.1语法结构 (56)17.2.2接口说明 (56)17.2.3取值说明 (56)17.3 UIM状态变化指示^SIMST (56)17.3.1语法结构 (56)17.3.2接口说明 (56)17.3.3取值说明 (56)17.4 系统的信息查询命令^SYSINFO (56)17.4.1语法结构 (56)17.4.2接口说明 (57)17.4.3取值说明 (57)17.5 网络模式选择^PREFMODE (58)17.5.1语法结构 (58)17.5.2接口说明 (58)17.5.3取值说明 (58)17.6 重启命令^RESET (58)17.6.1语法结构 (58)17.6.2接口描述 (58)17.6.3取值说明 (58)17.7 电压查询^VOLT (58)17.7.1语法结构 (58)17.7.2接口描述 (59)17.7.3取值说明 (59)17.8 MEID查询命令^MEID (59)17.8.1语法结构 (59)VII17.8.3取值说明 (59)17.9 进入休眠态指示^DSDORMANT (59)17.9.1语法结构 (59)17.9.2接口说明 (59)17.9.3取值说明 (59)17.10 发送F LASH/F LASH WITH I NFORMATION命令^FLASH (60)17.10.1语法结构 (60)17.10.2接口说明 (60)17.10.3取值说明 (60)18附录 (60)18.1 AT命令描述 (60)18.1.1基本命令 (60)18.1.2S寄存器命令 (60)18.1.3扩展命令和厂商定义命令 (61)18.1.4Abort属性: (62)18.2 CME ERROR列表 (62)18.3 CMS ERROR列表 (65)18.4 F INAL R ESULT C ODE汇总 (66)18.5 MT重启后命令参数初始值列表 (67)18.6 客户端的AT命令超时机制: (67)18.7 客户端查找设备机制: (67)18.8 客户端设备使用机制 (68)18.8.1设备先插入: (68)18.8.2客户端先启动: (68)18.8.3客户端启动时发送的AT命令顺序: (68)19详细更新历史 (69)图目录图 5-1 AT命令接口示意图 (12)VIIIIX 前 言客户端软件采用的AT 命令提出规定,中国电信内部和厂商共同使用,用于在业务及设备开发上为集团公司和省公司提供技术依据;适用于以数据卡为代表的移动终端产品。

YAV P无线ZigBee通信采集卡技术手册YAV7222P

YAV P压力传感器专用采集卡技术手册V1801武汉亚为电子科技有限公司YAV7222P关于本手册为亚为推出的YAV P压力传感器专用采集卡的用户手册,主要内容包括功能概述、1路压力传感器信号采集功能、2路数字量输入功能、2路数字量输出功能、串口RS232通信、应用实例、性能测试、注意事项及故障排除等。

另外部分DI采集包含需要定制的特殊功能:PWM功能输入,编码器输入,AO输出匹配输入。

说明序号版本号编写人编写日期支持对象应用时间特别说明1 1.0齐非2014.01YAV P采集卡2016.012 2.0樊春晖2016.01YAV P采集卡2017.013 3.0郑先科2017.01YAV P采集卡2017.084 4.0郑冉2017.08YAV P采集卡2017.08目录0.快速上手 (1)产品包装内容 (1)应用软件 (1)接口定义 (1)⏹端子描述 (1)⏹通信 (2)1.产品概述 (2)技术指标 (2)⏹模拟信号输入 (3)⏹数字信号输入 (3)⏹数字信号输出 (3)⏹通信总线 (4)⏹温度参数 (4)硬件特点 (4)原理框图 (5)机械规格 (6)2.模拟量输入功能 (7)输入采样原理 (7)输入接线 (7)采样值计算 (8)⏹无符号整型 (9)⏹ADC数据类型 (9)⏹模拟量值 (9)3.数字量输入功能 (9)数字输入原理 (9)DI高低电平/无源触点输入 (10)4.数字量输出功能 (11)输出原理 (11)DO高低电平输出 (11)5.通信协议 (12)无线Zigbee通信,亚为WSN无线采集卡IOT通信协议 (12)6.应用实例 (13)采集卡连接 (13)发现硬件 (13)软件功能 (14)软件应用 (15)⏹LabVIEW (15)⏹其它 (15)7.性能测试 (15)安全规范 (15)耐电压范围测试 (16)环境适应性测试 (16)电气参数 (17)通信 (18)采集卡指示灯 (18)8.注意事项及故障排除 (19)注意事项 (19)⏹存储说明 (19)⏹出货清单 (19)⏹质保及售后 (19)⏹特别说明 (19)故障排除 (19)⏹无法正常连接至上位机 (19)⏹多卡数据相同 (20)⏹采集速度不够 (20)⏹软件弹出错误 (20)9.文档权利及免责声明 (20)10.联系方式.......................................................................................................................错误!未定义书签。

rfc2460

Network Working Group S. Deering Request for Comments: 2460 Cisco Obsoletes: 1883 R. Hinden Category: Standards Track Nokia December 1998 Internet Protocol, Version 6 (IPv6)SpecificationStatus of this MemoThis document specifies an Internet standards track protocol for the Internet community, and requests discussion and suggestions forimprovements. Please refer to the current edition of the "InternetOfficial Protocol Standards" (STD 1) for the standardization stateand status of this protocol. Distribution of this memo is unlimited. Copyright NoticeCopyright (C) The Internet Society (1998). All Rights Reserved. AbstractThis document specifies version 6 of the Internet Protocol (IPv6),also sometimes referred to as IP Next Generation or IPng.Table of Contents1. Introduction (2)2. Terminology (3)3. IPv6 Header Format (4)4. IPv6 Extension Headers (6)4.1 Extension Header Order (7)4.2 Options (9)4.3 Hop-by-Hop Options Header (11)4.4 Routing Header (12)4.5 Fragment Header (18)4.6 Destination Options Header (23)4.7 No Next Header (24)5. Packet Size Issues (24)6. Flow Labels (25)7. Traffic Classes (25)8. Upper-Layer Protocol Issues (27)8.1 Upper-Layer Checksums (27)8.2 Maximum Packet Lifetime (28)8.3 Maximum Upper-Layer Payload Size (28)8.4 Responding to Packets Carrying Routing Headers (29)Deering & Hinden Standards Track [Page 1]RFC 2460 IPv6 Specification December 1998 Appendix A. Semantics and Usage of the Flow Label Field (30)Appendix B. Formatting Guidelines for Options (32)Security Considerations (35)Acknowledgments (35)Authors’ Addresses (35)References (35)Changes Since RFC-1883 (36)Full Copyright Statement (39)1. IntroductionIP version 6 (IPv6) is a new version of the Internet Protocol,designed as the successor to IP version 4 (IPv4) [RFC-791]. Thechanges from IPv4 to IPv6 fall primarily into the followingcategories:o Expanded Addressing CapabilitiesIPv6 increases the IP address size from 32 bits to 128 bits, to support more levels of addressing hierarchy, a much greaternumber of addressable nodes, and simpler auto-configuration of addresses. The scalability of multicast routing is improved by adding a "scope" field to multicast addresses. And a new type of address called an "anycast address" is defined, used to send a packet to any one of a group of nodes.o Header Format SimplificationSome IPv4 header fields have been dropped or made optional, to reduce the common-case processing cost of packet handling andto limit the bandwidth cost of the IPv6 header.o Improved Support for Extensions and OptionsChanges in the way IP header options are encoded allows formore efficient forwarding, less stringent limits on the length of options, and greater flexibility for introducing new options in the future.o Flow Labeling CapabilityA new capability is added to enable the labeling of packetsbelonging to particular traffic "flows" for which the senderrequests special handling, such as non-default quality ofservice or "real-time" service.Deering & Hinden Standards Track [Page 2]RFC 2460 IPv6 Specification December 1998 o Authentication and Privacy CapabilitiesExtensions to support authentication, data integrity, and(optional) data confidentiality are specified for IPv6.This document specifies the basic IPv6 header and the initially-defined IPv6 extension headers and options. It also discusses packet size issues, the semantics of flow labels and traffic classes, andthe effects of IPv6 on upper-layer protocols. The format andsemantics of IPv6 addresses are specified separately in [ADDRARCH].The IPv6 version of ICMP, which all IPv6 implementations are required to include, is specified in [ICMPv6].2. Terminologynode - a device that implements IPv6.router - a node that forwards IPv6 packets not explicitlyaddressed to itself. [See Note below].host - any node that is not a router. [See Note below].upper layer - a protocol layer immediately above IPv6. Examples are transport protocols such as TCP and UDP, controlprotocols such as ICMP, routing protocols such as OSPF, and internet or lower-layer protocols being "tunneled" over (i.e., encapsulated in) IPv6 such as IPX,AppleTalk, or IPv6 itself.link - a communication facility or medium over which nodes can communicate at the link layer, i.e., the layerimmediately below IPv6. Examples are Ethernets (simple or bridged); PPP links; X.25, Frame Relay, or ATMnetworks; and internet (or higher) layer "tunnels",such as tunnels over IPv4 or IPv6 itself.neighbors - nodes attached to the same link.interface - a node’s attachment to a link.address - an IPv6-layer identifier for an interface or a set ofinterfaces.packet - an IPv6 header plus payload.link MTU - the maximum transmission unit, i.e., maximum packetsize in octets, that can be conveyed over a link. Deering & Hinden Standards Track [Page 3]RFC 2460 IPv6 Specification December 1998 path MTU - the minimum link MTU of all the links in a path between a source node and a destination node.Note: it is possible, though unusual, for a device with multipleinterfaces to be configured to forward non-self-destined packetsarriving from some set (fewer than all) of its interfaces, and todiscard non-self-destined packets arriving from its other interfaces. Such a device must obey the protocol requirements for routers whenreceiving packets from, and interacting with neighbors over, theformer (forwarding) interfaces. It must obey the protocolrequirements for hosts when receiving packets from, and interactingwith neighbors over, the latter (non-forwarding) interfaces.3. IPv6 Header Format+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+|Version| Traffic Class | Flow Label |+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+| Payload Length | Next Header | Hop Limit |+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+| |+ +| |+ Source Address +| |+ +| |+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+| |+ +| |+ Destination Address +| |+ +| |+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+Version 4-bit Internet Protocol version number = 6.Traffic Class 8-bit traffic class field. See section 7.Flow Label 20-bit flow label. See section 6.Payload Length 16-bit unsigned integer. Length of the IPv6payload, i.e., the rest of the packet following this IPv6 header, in octets. (Note that any Deering & Hinden Standards Track [Page 4]RFC 2460 IPv6 Specification December 1998 extension headers [section 4] present areconsidered part of the payload, i.e., includedin the length count.)Next Header 8-bit selector. Identifies the type of headerimmediately following the IPv6 header. Uses the same values as the IPv4 Protocol field [RFC-1700 et seq.].Hop Limit 8-bit unsigned integer. Decremented by 1 byeach node that forwards the packet. The packetis discarded if Hop Limit is decremented tozero.Source Address 128-bit address of the originator of the packet. See [ADDRARCH].Destination Address 128-bit address of the intended recipient of the packet (possibly not the ultimate recipient, if a Routing header is present). See [ADDRARCH]and section 4.4.Deering & Hinden Standards Track [Page 5]RFC 2460 IPv6 Specification December 1998 4. IPv6 Extension HeadersIn IPv6, optional internet-layer information is encoded in separateheaders that may be placed between the IPv6 header and the upper-layer header in a packet. There are a small number of such extension headers, each identified by a distinct Next Header value. Asillustrated in these examples, an IPv6 packet may carry zero, one, or more extension headers, each identified by the Next Header field ofthe preceding header:+---------------+------------------------| IPv6 header | TCP header + data| || Next Header = || TCP |+---------------+------------------------+---------------+----------------+------------------------| IPv6 header | Routing header | TCP header + data| | || Next Header = | Next Header = || Routing | TCP |+---------------+----------------+------------------------+---------------+----------------+-----------------+----------------- | IPv6 header | Routing header | Fragment header | fragment of TCP | | | | header + data| Next Header = | Next Header = | Next Header = || Routing | Fragment | TCP |+---------------+----------------+-----------------+----------------- With one exception, extension headers are not examined or processedby any node along a packet’s delivery path, until the packet reaches the node (or each of the set of nodes, in the case of multicast)identified in the Destination Address field of the IPv6 header.There, normal demultiplexing on the Next Header field of the IPv6header invokes the module to process the first extension header, orthe upper-layer header if no extension header is present. Thecontents and semantics of each extension header determine whether or not to proceed to the next header. Therefore, extension headers must be processed strictly in the order they appear in the packet; areceiver must not, for example, scan through a packet looking for aparticular kind of extension header and process that header prior to processing all preceding ones.Deering & Hinden Standards Track [Page 6]RFC 2460 IPv6 Specification December 1998 The exception referred to in the preceding paragraph is the Hop-by-Hop Options header, which carries information that must be examinedand processed by every node along a packet’s delivery path, including the source and destination nodes. The Hop-by-Hop Options header,when present, must immediately follow the IPv6 header. Its presence is indicated by the value zero in the Next Header field of the IPv6header.If, as a result of processing a header, a node is required to proceed to the next header but the Next Header value in the current header is unrecognized by the node, it should discard the packet and send anICMP Parameter Problem message to the source of the packet, with anICMP Code value of 1 ("unrecognized Next Header type encountered")and the ICMP Pointer field containing the offset of the unrecognized value within the original packet. The same action should be taken if a node encounters a Next Header value of zero in any header otherthan an IPv6 header.Each extension header is an integer multiple of 8 octets long, inorder to retain 8-octet alignment for subsequent headers. Multi-octet fields within each extension header are aligned on theirnatural boundaries, i.e., fields of width n octets are placed at aninteger multiple of n octets from the start of the header, for n = 1, 2, 4, or 8.A full implementation of IPv6 includes implementation of thefollowing extension headers:Hop-by-Hop OptionsRouting (Type 0)FragmentDestination OptionsAuthenticationEncapsulating Security PayloadThe first four are specified in this document; the last two arespecified in [RFC-2402] and [RFC-2406], respectively.4.1 Extension Header OrderWhen more than one extension header is used in the same packet, it is recommended that those headers appear in the following order:IPv6 headerHop-by-Hop Options headerDestination Options header (note 1)Routing headerFragment headerDeering & Hinden Standards Track [Page 7]RFC 2460 IPv6 Specification December 1998 Authentication header (note 2)Encapsulating Security Payload header (note 2)Destination Options header (note 3)upper-layer headernote 1: for options to be processed by the first destination that appears in the IPv6 Destination Address fieldplus subsequent destinations listed in the Routingheader.note 2: additional recommendations regarding the relativeorder of the Authentication and EncapsulatingSecurity Payload headers are given in [RFC-2406].note 3: for options to be processed only by the finaldestination of the packet.Each extension header should occur at most once, except for theDestination Options header which should occur at most twice (oncebefore a Routing header and once before the upper-layer header).If the upper-layer header is another IPv6 header (in the case of IPv6 being tunneled over or encapsulated in IPv6), it may be followed byits own extension headers, which are separately subject to the sameordering recommendations.If and when other extension headers are defined, their orderingconstraints relative to the above listed headers must be specified.IPv6 nodes must accept and attempt to process extension headers inany order and occurring any number of times in the same packet,except for the Hop-by-Hop Options header which is restricted toappear immediately after an IPv6 header only. Nonetheless, it isstrongly advised that sources of IPv6 packets adhere to the aboverecommended order until and unless subsequent specifications revisethat recommendation.Deering & Hinden Standards Track [Page 8]RFC 2460 IPv6 Specification December 1998 4.2 OptionsTwo of the currently-defined extension headers -- the Hop-by-HopOptions header and the Destination Options header -- carry a variable number of type-length-value (TLV) encoded "options", of the following format:+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+- - - - - - - - -| Option Type | Opt Data Len | Option Data+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+- - - - - - - - -Option Type 8-bit identifier of the type of option.Opt Data Len 8-bit unsigned integer. Length of the Option Data field of this option, in octets.Option Data Variable-length field. Option-Type-specific data.The sequence of options within a header must be processed strictly in the order they appear in the header; a receiver must not, forexample, scan through the header looking for a particular kind ofoption and process that option prior to processing all precedingones.The Option Type identifiers are internally encoded such that theirhighest-order two bits specify the action that must be taken if theprocessing IPv6 node does not recognize the Option Type:00 - skip over this option and continue processing the header.01 - discard the packet.10 - discard the packet and, regardless of whether or not thepacket’s Destination Address was a multicast address, send an ICMP Parameter Problem, Code 2, message to the packet’sSource Address, pointing to the unrecognized Option Type.11 - discard the packet and, only if the packet’s DestinationAddress was not a multicast address, send an ICMP ParameterProblem, Code 2, message to the packet’s Source Address,pointing to the unrecognized Option Type.The third-highest-order bit of the Option Type specifies whether ornot the Option Data of that option can change en-route to thepacket’s final destination. When an Authentication header is present Deering & Hinden Standards Track [Page 9]RFC 2460 IPv6 Specification December 1998 in the packet, for any option whose data may change en-route, itsentire Option Data field must be treated as zero-valued octets whencomputing or verifying the packet’s authenticating value.0 - Option Data does not change en-route1 - Option Data may change en-routeThe three high-order bits described above are to be treated as partof the Option Type, not independent of the Option Type. That is, aparticular option is identified by a full 8-bit Option Type, not just the low-order 5 bits of an Option Type.The same Option Type numbering space is used for both the Hop-by-Hop Options header and the Destination Options header. However, thespecification of a particular option may restrict its use to only one of those two headers.Individual options may have specific alignment requirements, toensure that multi-octet values within Option Data fields fall onnatural boundaries. The alignment requirement of an option isspecified using the notation xn+y, meaning the Option Type mustappear at an integer multiple of x octets from the start of theheader, plus y octets. For example:2n means any 2-octet offset from the start of the header.8n+2 means any 8-octet offset from the start of the header,plus 2 octets.There are two padding options which are used when necessary to align subsequent options and to pad out the containing header to a multiple of 8 octets in length. These padding options must be recognized byall IPv6 implementations:Pad1 option (alignment requirement: none)+-+-+-+-+-+-+-+-+| 0 |+-+-+-+-+-+-+-+-+NOTE! the format of the Pad1 option is a special case -- it doesnot have length and value fields.The Pad1 option is used to insert one octet of padding into theOptions area of a header. If more than one octet of padding isrequired, the PadN option, described next, should be used, rather than multiple Pad1 options.Deering & Hinden Standards Track [Page 10]RFC 2460 IPv6 Specification December 1998 PadN option (alignment requirement: none)+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+- - - - - - - - -| 1 | Opt Data Len | Option Data+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+- - - - - - - - -The PadN option is used to insert two or more octets of paddinginto the Options area of a header. For N octets of padding, theOpt Data Len field contains the value N-2, and the Option Dataconsists of N-2 zero-valued octets.Appendix B contains formatting guidelines for designing new options.4.3 Hop-by-Hop Options HeaderThe Hop-by-Hop Options header is used to carry optional informationthat must be examined by every node along a packet’s delivery path.The Hop-by-Hop Options header is identified by a Next Header value of 0 in the IPv6 header, and has the following format:+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+| Next Header | Hdr Ext Len | |+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+ +| |. .. Options .. .| |+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+Next Header 8-bit selector. Identifies the type of headerimmediately following the Hop-by-Hop Optionsheader. Uses the same values as the IPv4Protocol field [RFC-1700 et seq.].Hdr Ext Len 8-bit unsigned integer. Length of the Hop-by-Hop Options header in 8-octet units, notincluding the first 8 octets.Options Variable-length field, of length such that thecomplete Hop-by-Hop Options header is an integer multiple of 8 octets long. Contains one or more TLV-encoded options, as described in section4.2.The only hop-by-hop options defined in this document are the Pad1 and PadN options specified in section 4.2.Deering & Hinden Standards Track [Page 11]RFC 2460 IPv6 Specification December 1998 4.4 Routing HeaderThe Routing header is used by an IPv6 source to list one or moreintermediate nodes to be "visited" on the way to a packet’sdestination. This function is very similar to IPv4’s Loose Sourceand Record Route option. The Routing header is identified by a Next Header value of 43 in the immediately preceding header, and has thefollowing format:+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+| Next Header | Hdr Ext Len | Routing Type | Segments Left |+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+| |. .. type-specific data .. .| |+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+Next Header 8-bit selector. Identifies the type of headerimmediately following the Routing header. Uses the same values as the IPv4 Protocol field[RFC-1700 et seq.].Hdr Ext Len 8-bit unsigned integer. Length of the Routingheader in 8-octet units, not including the first 8 octets.Routing Type 8-bit identifier of a particular Routing header variant.Segments Left 8-bit unsigned integer. Number of routesegments remaining, i.e., number of explicitlylisted intermediate nodes still to be visitedbefore reaching the final destination.type-specific data Variable-length field, of format determined bythe Routing Type, and of length such that thecomplete Routing header is an integer multipleof 8 octets long.If, while processing a received packet, a node encounters a Routingheader with an unrecognized Routing Type value, the required behavior of the node depends on the value of the Segments Left field, asfollows:Deering & Hinden Standards Track [Page 12]RFC 2460 IPv6 Specification December 1998 If Segments Left is zero, the node must ignore the Routing header and proceed to process the next header in the packet, whose typeis identified by the Next Header field in the Routing header.If Segments Left is non-zero, the node must discard the packet and send an ICMP Parameter Problem, Code 0, message to the packet’sSource Address, pointing to the unrecognized Routing Type.If, after processing a Routing header of a received packet, anintermediate node determines that the packet is to be forwarded onto a link whose link MTU is less than the size of the packet, the nodemust discard the packet and send an ICMP Packet Too Big message tothe packet’s Source Address.Deering & Hinden Standards Track [Page 13]RFC 2460 IPv6 Specification December 1998 The Type 0 Routing header has the following format:+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+| Next Header | Hdr Ext Len | Routing Type=0| Segments Left |+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+| Reserved |+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+| |+ +| |+ Address[1] +| |+ +| |+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+| |+ +| |+ Address[2] +| |+ +| |+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+. . .. . .. . .+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+| |+ +| |+ Address[n] +| |+ +| |+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+Next Header 8-bit selector. Identifies the type of headerimmediately following the Routing header. Uses the same values as the IPv4 Protocol field[RFC-1700 et seq.].Hdr Ext Len 8-bit unsigned integer. Length of the Routingheader in 8-octet units, not including the first 8 octets. For the Type 0 Routing header, HdrExt Len is equal to two times the number ofaddresses in the header.Routing Type 0.Deering & Hinden Standards Track [Page 14]RFC 2460 IPv6 Specification December 1998 Segments Left 8-bit unsigned integer. Number of routesegments remaining, i.e., number of explicitlylisted intermediate nodes still to be visitedbefore reaching the final destination.Reserved 32-bit reserved field. Initialized to zero for transmission; ignored on reception.Address[1..n] Vector of 128-bit addresses, numbered 1 to n.Multicast addresses must not appear in a Routing header of Type 0, or in the IPv6 Destination Address field of a packet carrying a Routing header of Type 0.A Routing header is not examined or processed until it reaches thenode identified in the Destination Address field of the IPv6 header. In that node, dispatching on the Next Header field of the immediately preceding header causes the Routing header module to be invoked,which, in the case of Routing Type 0, performs the followingalgorithm:Deering & Hinden Standards Track [Page 15]RFC 2460 IPv6 Specification December 1998 if Segments Left = 0 {proceed to process the next header in the packet, whose type isidentified by the Next Header field in the Routing header}else if Hdr Ext Len is odd {send an ICMP Parameter Problem, Code 0, message to the SourceAddress, pointing to the Hdr Ext Len field, and discard thepacket}else {compute n, the number of addresses in the Routing header, bydividing Hdr Ext Len by 2if Segments Left is greater than n {send an ICMP Parameter Problem, Code 0, message to the SourceAddress, pointing to the Segments Left field, and discard thepacket}else {decrement Segments Left by 1;compute i, the index of the next address to be visited inthe address vector, by subtracting Segments Left from nif Address [i] or the IPv6 Destination Address is multicast {discard the packet}else {swap the IPv6 Destination Address and Address[i]if the IPv6 Hop Limit is less than or equal to 1 {send an ICMP Time Exceeded -- Hop Limit Exceeded inTransit message to the Source Address and discard thepacket}else {decrement the Hop Limit by 1resubmit the packet to the IPv6 module for transmissionto the new destination}}}}Deering & Hinden Standards Track [Page 16]RFC 2460 IPv6 Specification December 1998 As an example of the effects of the above algorithm, consider thecase of a source node S sending a packet to destination node D, using a Routing header to cause the packet to be routed via intermediatenodes I1, I2, and I3. The values of the relevant IPv6 header andRouting header fields on each segment of the delivery path would beas follows:As the packet travels from S to I1:Source Address = S Hdr Ext Len = 6Destination Address = I1 Segments Left = 3Address[1] = I2Address[2] = I3Address[3] = DAs the packet travels from I1 to I2:Source Address = S Hdr Ext Len = 6Destination Address = I2 Segments Left = 2Address[1] = I1Address[2] = I3Address[3] = DAs the packet travels from I2 to I3:Source Address = S Hdr Ext Len = 6Destination Address = I3 Segments Left = 1Address[1] = I1Address[2] = I2Address[3] = DAs the packet travels from I3 to D:Source Address = S Hdr Ext Len = 6Destination Address = D Segments Left = 0Address[1] = I1Address[2] = I2Address[3] = I3Deering & Hinden Standards Track [Page 17]RFC 2460 IPv6 Specification December 1998 4.5 Fragment HeaderThe Fragment header is used by an IPv6 source to send a packet larger than would fit in the path MTU to its destination. (Note: unlikeIPv4, fragmentation in IPv6 is performed only by source nodes, not by routers along a packet’s delivery path -- see section 5.) TheFragment header is identified by a Next Header value of 44 in theimmediately preceding header, and has the following format:+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+| Next Header | Reserved | Fragment Offset |Res|M|+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+| Identification |+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+Next Header 8-bit selector. Identifies the initial headertype of the Fragmentable Part of the originalpacket (defined below). Uses the same values as the IPv4 Protocol field [RFC-1700 et seq.].Reserved 8-bit reserved field. Initialized to zero fortransmission; ignored on reception.Fragment Offset 13-bit unsigned integer. The offset, in 8-octet units, of the data following this header,relative to the start of the Fragmentable Partof the original packet.Res 2-bit reserved field. Initialized to zero fortransmission; ignored on reception.M flag 1 = more fragments; 0 = last fragment.Identification 32 bits. See description below.In order to send a packet that is too large to fit in the MTU of the path to its destination, a source node may divide the packet intofragments and send each fragment as a separate packet, to bereassembled at the receiver.For every packet that is to be fragmented, the source node generates an Identification value. The Identification must be different thanthat of any other fragmented packet sent recently* with the sameSource Address and Destination Address. If a Routing header ispresent, the Destination Address of concern is that of the finaldestination.Deering & Hinden Standards Track [Page 18]。

TLV1504ID;TLV1504IPW;TLV1508IPW;TLV1508IDW;TLV1504IPWR;中文规格书,Datasheet资料

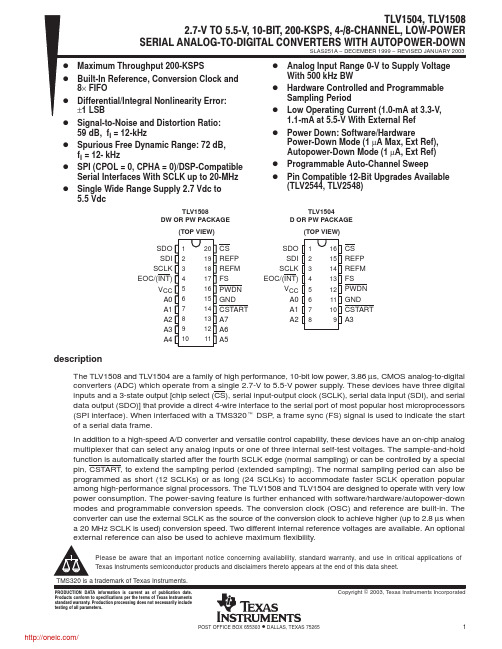

Terminal Functions

TERMINAL NAME A0 A1 A2 A3 A0 A1 A2 A3 A4 A5 A6 A7 NO. TLV1504 6 7 8 9 TLV1508 6 7 8 9 10 11 12 13 20 I Analog signal inputs. The analog inputs are applied to these terminals and are internally multiplexed. The driving source impedance should be less than or equal to 1 kΩ. For a source impedance greater than 1 kΩ, use the asynchronous conversion start signal CSTART (CSTART low time controls the sampling period) or program long sampling period to increase the sampling time. I/O DESCRIPTION

2

POST OFFICE BOX 655303

• DALLAS, TEXAS 75265

/

TLV1504, TLV1508 2.7ĆV TO 5.5ĆV, 10ĆBIT, 200ĆKSPS, 4Ć/8ĆCHANNEL, LOWĆPOWER SERIAL ANALOGĆTOĆDIGITAL CONVERTERS WITH AUTOPOWERĆDOWN

TLV1508 DW OR PW PACKAGE (TOP VIEW)

TLV2462