xilinx V6 DDR3调试成功经验分享

DDR3测试读写

DDR3测试读写(1)今天是重阳节,所以提前祝福重阳节快乐。

因为DDR3讲解内容比较多,所以分解成3节进行讲解。

一个做FPGA的人如果不懂DDR3,Serdes,那基本等于没学习fpga。

所以必须掌握ddr控制器才能深入fpga具体功能。

注意以后基本工具都是用的vivado2014.02版本。

用ise导致不一样,不要问我。

该工程参考的xilinx的文档xtp225。

首先是打开vivado,建完工程以后,然后点击IP catalog,打开ip库。

找到Memory Interface Generator IP核。

然后会出现图1.2页面图1.1图1.2的显示信息是当前工程设置的器件信息。

vivado不像以前的ISE,分离IP工程。

现在都是一个工程。

所以要注意观察该页面显示的器件是否正确。

经常有人选错速度等级而导致无法通过后期时序仿真。

图1.2图1.3是选择创建一个设计。

图1.3图1.4选择ddr3芯片。

图1.4图1.5显示的是兼容引脚。

选择next。

图1.5图1.6是选择选择DDR的时钟,记住,DDR是双边沿。

所以上面写的400MHz,也就是DDR 800M。

选额内存类型是SODIMMs。

内存类型是MT6JTF12864HZ-1G6类型。

Data Mask 数据掩码,可以选择或者不选择,类似于sdram的dqm信号。

有人问这有啥作用。

就等于内存中,你要改变其中几个bit而不是改变全部bit。

所以用掩码方式更好的。

否则你要读出来,然后再写入,这种方法太消耗时间。

图1.6图1.7是表示选择整个IP输入时钟多少,基本DDR3寄存器控制。

基本IP输入时钟在SPARTAN6的MIG核是没有选择,需要手动修改时钟文件。

这里有提供输入时钟选择。

读写burst的方式,一个顺序读取还有个strict 跳跃式读取。

除非你有特殊的要求,一般都是顺序读取。

输出驱动电阻控制RZQ/7和RTT电阻,这个电阻是从datasheet手册得到的。

飞思卡尔i.MX6平台DRAM接口高阶应用指导-DDR3篇

飞思卡尔i.MX6平台DRAM接⼝⾼阶应⽤指导-DDR3篇飞思卡尔i.MX6平台DRAM接⼝⾼阶应⽤指导-DDR3篇本⽂意于介绍基于i.MX6平台如何使⽤官⽅⼯具调试DDR3.以下内容会在本⽂中涉及:原理图及PCB版图设计规则,DDR3初始化代码⽣成⼯具,DDR3⾃校准和压⼒测试⼯具。

Contents1DRAM Design Consideration (2)2DDR3 initialization Script Generation Aid (3)3DDR Stress Test Tool (10)4Further Reading (19)1 设计DRAM 的注意事项飞思卡尔的硬件应⽤团队总结了⼀个名为 “HW Design Checking List for i.Mx6” 的⽂档来分享i.MX6硬件设计经验。

请通过以下链接来获得该⽂档: https:///doc/5cb1ce021eb91a37f0115c67.html /docs/DOC-938191.1 原理图和布线设计规则下表中的内容摘⾃“HW Design Checking List for i.Mx6”。

使⽤i.MX6平台进⾏设计时务必遵循⾥⾯的规则。

设计者应当逐条予以确认。

如有任何疑问或不确定之处,请寻求飞思卡尔的技术⽀持本们的帮助。

原理图检查清单 1i.Mx6和DDR 芯⽚的ZQ 管脚需要分别外加⼀个1%精度的240欧姆电阻到地 2提供⼀路低噪声并且等于50%NVCC_DRAM 电压值的电源给DRAM_VREF 管脚(更多细节请参考原⽂档) 3DRAM_RESET 管脚需要外接⼀个10 K 欧姆的电阻到地(更多细节请参考原⽂档) 4差分时钟端接设计规则(更多细节请参考原⽂档) 5 如果DDR3颗粒的数量少于等于四颗-PCB 顶⾯两颗底⾯两颗,建议使⽤T 拓扑结构。

如果PCB 单⾯需要部多于两颗DDR3颗粒,建议使⽤Fly-by 拓扑结构。

CLV63x调试介绍

中文

说明

英文 Trigger Source Sensor1,Sensor2 External Input1 External Input2 Command Timer/Tracking Good Read Condition Match1 Condition MultCodes1 Condition TeachIn1

一般不修改 会影响扫描周期,一般不修改

: Daniel Zhao 16

单台条码阅读器参数设置及调试

在Output Control下:(一般要修改,根据实际需要选择)

英文 End of Trigger As soon as possible

End of Label New Label

Single

中文 触发结束 立即输出 标签结束 新标签 单次输出 多次输出 读到条码 满足条件Match1 满足条件 TeachIn1 满足条件 TeachIn2

扫描器与PC连接电缆示意图

•确认电缆连接无误后,通过SOPAS_ET软件(可以通过SICK网站或者SICK公司获

得最新版本)通过RS232串口连通扫描器,当连接正确时软件下方会显示扫描 器型号以及通讯方式和当前状态,如下图所示:

这时就表示扫描器与PC建立了正确 的连接可以进行设置和调试工作。

SICK China : Confidential : Daniel Zhao 9

Start配置 要求传感器为PNP型输出,输出 传感器输入,高电平 触发,激光打开 为高电平是触发。 指令触发 自动触发 CAN网触发 总线触发 自动触发 通常为串口指令 周期性的打开激光,一般用于诊 断 CAN网中其它站提供触发信号 命令通过总线触发扫描头 激光常亮,监测到条码后读码

中文 Stop 配置 触发源条件变化 同Start配置中一致

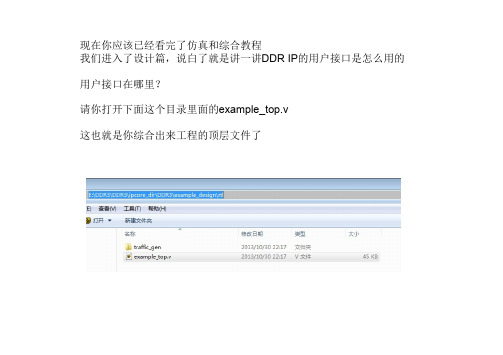

xilinx平台DDR3设计教程之综合篇_中文版教程

你已经看过我写的仿真教程,并且按照步骤都做成功了吧?现在要做综合?来个一图流就行了——看明白了吗?编译已经成功,bit文件生成了。

什么?没看明白?下面分开讲吧~之前仿真教程里面讲过过traffic_gen,现在派用场了看这个工程里面的顶层文件,不是我写的其实这工程里面所有的文件都不是我写的只要你生成好了IP core,管脚分配好(你也可以让core gen自动分配,用默认值就行,还是参见仿真教程)你要做的事,就是这么区区几步:1,建立一个ISE工程,FPGA型号和封装选对就可以了2,加入example_design/rtl下面的 example_top.v 以及其他所有.v文件(什么,你写VHDL的?乖乖,不知道现在写VHDL的很难找工作?)3,加入user_design/rtl下面的rtl下面的所有.v文件4,加入example_design/par 下面的example_top.ucf文件然后你就开始跑编译吧~文件全部加完了之后就是这样的,都是绝对路径显示多展开几级,来个壮观点儿的其实就是把这两个目录下的*.v都加进去,最后别忘了加上example_design/par 下面的example_top.ucf文件,就可以了只要你在core gen的时候分配好了管脚,就不可能编译不成功。

这张图还记得吗?万一做板子的人把按键和LED灯的管脚给你分配到了这里不能选的地方,你就得留意下一页的内容了。

/support/documentation/ip_documentation/mig_7series/v1_5/ug586_7Series_MIS.pdf 在上面这个文档,也就是xilinx MIG的用户手册里面的132页,有这么一段:管脚电平可以用planAhead来设置。

推荐你综合完了之后用post-synthesis(综合后)的选项来重设管脚属性,这个比pre-synthesis(综合前)有说服力,行不行还是得看你综合完了之后不是?但是实际上你打开了之后会发现不是那么回事儿这为啥LVCMOS都是2.5V,SSTL都是1.35V,编译也通过了?可能待会儿上电了下载还正常跑。

基于FPGA的DDR3用户接口设计技术详解

基于FPGA的DDR3用户接口设计技术详解

本文详细介绍了在Xilinx Virtex-6系列FPGA中使用MIG3.7 IP核实现高速率DDR3芯片控制的设计思想和设计方案。

针对高速实时数字信号处理中大容量采样数据通过DDR3存储和读取的应用背景,设计和实现了适用于该背景的控制状态机,并对控制时序作了详尽的分析。

系统测试结果表明,该设计满足大容量数据的高速率存储和读取要求。

一、引言

随着软件无线电[1]思想的提出和FPGA技术[2]的不断发展,高速实时数字信号处理[3]已经成为FPGA的一个重要课题,高速的采样频率带来的是大容量的存储数据。

在存储芯片领域,DDR3以较低的功耗,较快的存储速度,较高的存储容量和较低的价格迅速占领市场;同时在绘制PCB板图时,DDR2对信号完整性[4]的要求比较高,在很多地方都要求T型连接;而DDR3引入了write leveling的模块[5],专门用于各个模块间时钟的对齐,因此可以采用菊花链的连接方式,大大方便了PCB互联设计[6]。

因此,在FPGA中使用DDR3进行大容量数据的存储是一种趋势。

本文基于Xilinx 公司的Virtex-6芯片,针对高速实时数字信号处理中大容量采样数据通过DDR3存储和读取的应用背景,利用官方提供的IP核完成了用户接口设计,并在该芯片上完成了验证和实现。

目前,该方案已经在某。

xilinx平台DDR3设计教程之仿真篇_中文版教程

想做个DDR设计不?想还是不想?你要知道FPGA这种东西,片内存储资源终究有限,实在谈不上海量存储。

万一哪天你想要海量存储数据了咋办?你是不是得用DRAM条子啊?什么?你还想用SRAM?今年已经2013年了童鞋~关于DRAM,或许是SDRAM,或许是DDR1(再次提醒你,2013年了已经),或许是DDR2或者DDR3。

这些条子都有一套控制协议,这套协议对不同的条子大同小异,但是里面又有各种细节的区别,这些你都搞懂了吗?没搞懂?其实,你不需要搞懂。

现在的EDA设计不需要你从基础知识开始研究。

这个时代,你要生存要发展,最佳的办法是站在巨人的肩膀上,而不是亲自长成个巨人。

DDR设计太常用了,只要你在搞FPGA,自然有人给你搞定一套IP,免费的给你用。

你不会还想自己从底层写起吧?多花些时间在没有免费IP用的协议合算法上吧。

现在进入正题:我刚刚讲的免费IP,在哪里?怎么用的?(小白问题,IP是什么,IP地址吗?)这里的IP就是Intelligence Property说白了就是xilinx里的core gen(对应于altera里面的mega wizard)这个文档就举一个例子来讲,选哪家呢?本人是xilinx和altera都来一个?条子选啥?SDR?DDR1? 各种条子全都写一套?(你以为写这个文档容易吗,是不是要连chipscope怎么用也一起出个文档啊?全部都写一套可以,先往我账户上打五千块钱,然后我再考虑考虑。

记住这个世界上没有白吃的午餐,你要看白痴都能看会的DDR教程,你就得听我在这里唠叨)本教程选择一个例子来讲,那就是xilinx平台下用DDR3(常见的笔记本内存条)接下来是你玩转这个教程所必须要准备的工具:xilinx ISE 14.1或者更高版本(不好意思,比14.1还低的版本我没试过。

vivado当然也可以,不过我是用的ISE)modelsim SE 6.6a或者更高版本(更低版本我负责的告诉你不可以,因为无法正常生成编译库,所以,6.5版本或者更低的你干脆就别装了)有鉴于这个文档的面相对象设定为连chiscope都不太会用的人,就是那种刚毕业不到一两年甚至还在校的,我必须郑重的告诉你一下这两个工具上哪里去下载:网上下载,百度股沟搜索会不会?什么?你告诉我搜不到?我给你跪了,菜鸟兄XILINX ISE 14.4这里下载http://simplecd.me/entry/L1a0enD2/破解文件:/f/62469961.htmlmodelsim 6.6这里下载(要注册和花积分的):/viewthread.php?tid=232457破解文件:/f/34760037.html(注意,时间长了以后这几个链接是可能失效的,比如你可能在2015年看到这个2013年11月写的文档,到时候可能只能自己找下载了)PPT翻了一页了,工具都装完了吗亲?已经装完了啊?很好哦,那我们就开始吧!你知道用ISE做DDR设计的第一步是啥吗?当然是打开工具了——我估计这你肯定知道打开工具之后做啥?当然是生成一个IP,对xilinx来说也就是core gen了我估计你即便是新手上路,这个也是知道的——因为我前面刚刚讲过了嘛那么core gen生成完了之后呢?是不是要仿真啊?仿真需要什么?当然是modelsim了——我还是刚刚讲过,哈哈那你知道用modelsim仿真DDR的core gen,是需要xilinx仿真库的吗?什么?你不知道啥叫仿真库?乖乖隆地洞,我还是给你讲讲啥叫仿真库吧先关于FPGA的仿真库本人不是学校里的学究,本人是工程师所以用工程师的语言告诉你啥叫仿真库FPGA本身是一种特定的芯片,这个芯片里有很多特定的基本电路单元。

xilinx平台DDR3设计教程之仿真篇

想做个DDR设计不?想还是不想?你要知道FPGA这种东西,片内存储资源终究有限,实在谈不上海量存储。

万一哪天你想要海量存储数据了咋办?你是不是得用DRAM条子啊?什么?你还想用SRAM?今年已经2013年了童鞋~关于DRAM,或许是SDRAM,或许是DDR1(再次提醒你,2013年了已经),或许是DDR2或者DDR3。

这些条子都有一套控制协议,这套协议对不同的条子大同小异,但是里面又有各种细节的区别,这些你都搞懂了吗?没搞懂?其实,你不需要搞懂。

现在的EDA设计不需要你从基础知识开始研究。

这个时代,你要生存要发展,最佳的办法是站在巨人的肩膀上,而不是亲自长成个巨人。

DDR设计太常用了,只要你在搞FPGA,自然有人给你搞定一套IP,免费的给你用。

你不会还想自己从底层写起吧?多花些时间在没有免费IP用的协议合算法上吧。

现在进入正题:我刚刚讲的免费IP,在哪里?怎么用的?(小白问题,IP是什么,IP地址吗?)这里的IP就是Intelligence Property说白了就是xilinx里的core gen(对应于altera里面的mega wizard)这个文档就举一个例子来讲,选哪家呢?本人是xilinx和altera都来一个?条子选啥?SDR?DDR1? 各种条子全都写一套?(你以为写这个文档容易吗,是不是要连chipscope怎么用也一起出个文档啊?全部都写一套可以,先往我账户上打五千块钱,然后我再考虑考虑。

记住这个世界上没有白吃的午餐,你要看白痴都能看会的DDR教程,你就得听我在这里唠叨)本教程选择一个例子来讲,那就是xilinx平台下用DDR3(常见的笔记本内存条)接下来是你玩转这个教程所必须要准备的工具:xilinx ISE 14.1或者更高版本(不好意思,比14.1还低的版本我没试过。

vivado当然也可以,不过我是用的ISE)modelsim SE 6.6a或者更高版本(更低版本我负责的告诉你不可以,因为无法正常生成编译库,所以,6.5版本或者更低的你干脆就别装了)有鉴于这个文档的面相对象设定为连chiscope都不太会用的人,就是那种刚毕业不到一两年甚至还在校的,我必须郑重的告诉你一下这两个工具上哪里去下载:网上下载,百度股沟搜索会不会?什么?你告诉我搜不到?我给你跪了,菜鸟兄XILINX ISE 14.4这里下载http://simplecd.me/entry/L1a0enD2/破解文件:/f/62469961.htmlmodelsim 6.6这里下载(要注册和花积分的):/viewthread.php?tid=232457破解文件:/f/34760037.html(注意,时间长了以后这几个链接是可能失效的,比如你可能在2015年看到这个2013年11月写的文档,到时候可能只能自己找下载了)PPT翻了一页了,工具都装完了吗亲?已经装完了啊?很好哦,那我们就开始吧!你知道用ISE做DDR设计的第一步是啥吗?当然是打开工具了——我估计这你肯定知道打开工具之后做啥?当然是生成一个IP,对xilinx来说也就是core gen了我估计你即便是新手上路,这个也是知道的——因为我前面刚刚讲过了嘛那么core gen生成完了之后呢?是不是要仿真啊?仿真需要什么?当然是modelsim了——我还是刚刚讲过,哈哈那你知道用modelsim仿真DDR的core gen,是需要xilinx仿真库的吗?什么?你不知道啥叫仿真库?乖乖隆地洞,我还是给你讲讲啥叫仿真库吧先关于FPGA的仿真库本人不是学校里的学究,本人是工程师所以用工程师的语言告诉你啥叫仿真库FPGA本身是一种特定的芯片,这个芯片里有很多特定的基本电路单元。

DDR3,DIMM在FPGA上引脚分配规则,完全手打中文

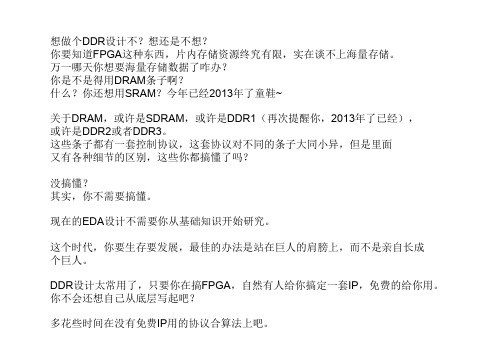

FPGA BANK选择页面中的图是所选部件物理表示的架构视图。

默认情况下, MIG 将使用推荐的选择,地址/控制BANK和数据BANK是根据V6对不同频率的规则限定的。

选择您想要使用的BANK for内存接口,你用不着选择的实际的引脚。

默认情况下MIG将使用所选bank中的任意引脚for内存接口。

设计规则:∙设计最大频率:o-1 FPGA 速度级器件: 400 MHzo-2 和-3 FPGA 速度级器件: 533 MHzo只有-2 FPGA 速度等级的 CXT 设备只要303 MHz支持o低功耗V6设备只需303303 MHz∙频率超过333 MHz,只有数据宽度低于72位被容许。

频率低于333 MHz 数据宽度低于144 位被允许∙内存类型、内存部件和数据宽度被限制基于所选的 FPGA 器件、 FPGA 器件速度等级和设计频率BANK的选择规则:∙地址/控制组只能选择在内部列BANK∙第一个选定的地址/控制组将有 CK [0] 和 CK #[0] 引脚∙包含CK [0] 和 CK #[0]的BANK,会有该MMCM应用与该H-Row∙对于设计频率400 MHz或更高,只有内部列BANK被允许用于数据组的选择。

对于设计频率为400 MHz以下,内部和外部列BANK被允许数据组的选择o内部或外部列BANK被唯一的允许for选择∙位于,包含CK [0]和CK #[0] 的BANK的上面一行、下面一行和同一行,的内外侧BANK,是可用的for数据组引脚选择∙此限制被一个称为vicinity box的边界箱描述∙系统时钟组只能被选择在包含GC引脚的BANK或者位于,和分配的MMCM 同一H-ROW的内部BANK。

∙控制和状态引脚即sys_rst,error等,在系统时钟BANK中分配.∙由于采用不同的电压标准,系统时钟组与其余的设计组针脚(地址/控制组和数据组)不能共存于同一BANK。

∙一个主BANK必须被选择for每个列,假如系统时钟BANK不能作为主BANK引脚分配规则:∙地址/控制组:o包含 A、BA、 CK、 CK #、 CKE、 CS #、 RAS #、 CAS #、 WE#、 ODT, RESET #o只能选择内部列BANKo内存时钟信号(CK [0] 和 CK#[0]) 分配给差分对引脚(P Npair)o VRN/VRP 引脚若被用于引脚分配,DCI级联应该被采用,用以支持地址/时钟的 DCI 标准PS: XILINX公司的Virtex系列FPGA芯片上,每个BANK都有一对VRP/VRN管脚。

Xilinx_ISE使用教程2

新建文件 的类型, 不同的类 型有着不 同的功能 和意义。

该文 件的 实体 名

Xilinx公司ISE10.1软件设计流程介绍

--添加实体端口

Next

端口名

端口的类型及位数

Xilinx公司ISE10.1软件设计流程介绍

--添加实体端口

给出了该文件 的概要

Finish

Xilinx公司ISE10.1软件设计流程介绍

Xilinx公司ISE10.1软件介绍

--处理(process)子窗口

在该窗口只有一个处理标签。该标签有下列功能: 添加已有文件; 创建新文件; 察看设计总结(访问符号产生工具,例化模板,察看 命令行历史和仿真库编辑); 用户约束文件(访问和编辑位置和时序约束); 综合(检查语法、综合、察看RTL和综合报告); 设计实现(访问实现工具,设计流程报告和其它一些 工具); 产生可编程文件(访问配置工具和产生比特流文件)。

Xilinx公司ISE10.1软件设计流程介绍

--打开ISE软件时的面板

当以前使用 过该软件时会默 认打开上一个工 程。

Xilinx公司ISE10.1软件设计流程介绍

--创建一个新工程

Xilinx公司ISE10.1软件设计流程介绍

--创建一个新工程

选择芯片 选择综合工具

选择仿真工具

选择代码语言

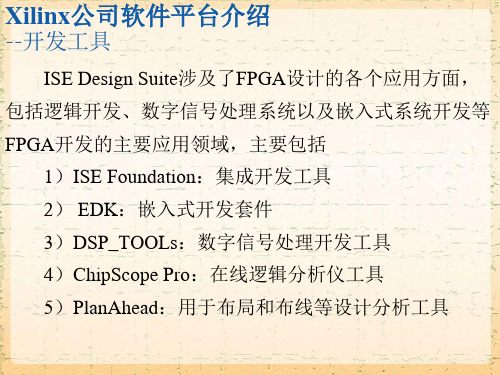

4)ChipScope Pro:在线逻辑分析仪工具

5)PlanAhead:用于布局和布线等设计分析工具

Xilinx公司软件平台介绍

--软件组成

集成开发环 境

在线逻辑分析 仪工具

片上系统开发

数字信号处 理开发工具

布局布线 工具

Xilinx公司软件平台介绍

xilinx 7系列fpga ddr3硬件设计规则

xilinx 7系列fpga ddr3硬件设计规则本文档旨在为使用Xilinx 7系列FPGA的设计师提供DDR3硬件设计规则的指导,确保设计的性能和可靠性满足要求。

2.DDR3简介DDR3(Double Data Rate 3)是一种高性能、高带宽的内存接口标准。

Xilinx 7系列FPGA支持DDR3 SDRAM,它具有更高的数据传输速度和较低的功耗。

3.电源和地线设计在DDR3硬件设计中,正确的电源和地线设计是保证稳定、可靠操作的关键。

以下是一些必须考虑的要点:- 为DDR3提供稳定的电源供应,包括供电线路的降噪和绕线规则。

- 将VCCINT和VCCAUX分别与主要飞线供电器件的专用电源连接。

- 使用低噪声电源滤波器和电源剥离电感,以降低电源噪声。

4.时钟设计DDR3使用时钟信号来同步数据传输。

以下是一些关键的时钟设计注意事项:- 使用低噪声时钟源,并且确保时钟信号干净和稳定。

- 时钟信号的布线要尽量短,以降低时钟抖动和延迟。

- 时钟信号分配必须满足时钟频率要求和布线规则。

5.布线和信号完整性良好的布线和信号完整性是DDR3硬件设计中的关键要点。

以下是一些布线和信号完整性设计注意事项:- DDR3接口线长度必须匹配,以确保信号同步和正常传输。

- 使用差分布线技术来减少噪声和串扰。

- 保持信号线和差分对之间的间距足够大,以降低串扰和干扰。

- 使用终端电阻来匹配DDR3总线阻抗,并提高信号完整性。

- 严格遵守DDR3布线规则,如保持信号线的最小长度、最大长度等。

6.时序约束为确保DDR3的正确操作,必须正确设置时序约束。

以下是几个重要的时序约束要点:- 根据DDR3存储器的数据手册和Xilinx 7系列FPGA的时序规格表,确定正确的时序约束。

- 确保时钟和时钟相关信号的约束满足要求,以保证数据传输的准确性。

- 将时序约束尽可能地贴近实际硬件设计,并进行时序分析和优化。

7.布局和引脚分配良好的布局和引脚分配是确保DDR3性能和可靠性的关键。

Xilinx中DCM的问题解决方案

Xilinx中DCM的问题解决方案标题:Xilinx中DCM的问题解决方案

引言概述:

Xilinx是一家领先的可编程逻辑器件制造商,其数字时钟管理器(DCM)是一种常用的时钟管理器。

然而,在使用Xilinx中的DCM时,用户可能会遇到一些问题。

本文将为您介绍Xilinx中DCM的问题解决方案。

一、时钟频率不准确的解决方案

1.1 使用精确的输入时钟源

1.2 调整DCM的时钟分频器

1.3 校准DCM的相位偏移

二、时钟抖动问题的解决方案

2.1 降低输入时钟的噪声

2.2 使用低抖动的时钟源

2.3 调整DCM的锁相环参数

三、时钟干扰问题的解决方案

3.1 使用适当的电源和地线布局

3.2 使用抗干扰滤波器

3.3 调整DCM的时钟延迟

四、时钟漂移问题的解决方案

4.1 使用温度稳定的时钟源

4.2 定期校准DCM的时钟频率

4.3 调整DCM的自动校准参数

五、时钟相位问题的解决方案

5.1 使用相位锁定环(PLL)来处理相位问题

5.2 调整DCM的相位校准参数

5.3 使用外部时钟触发器来同步时钟信号

总结:

Xilinx中的DCM是一种强大的时钟管理器,但在使用过程中可能会遇到一些问题。

通过使用精确的输入时钟源、调整DCM的参数以及采取适当的电路设计措施,可以解决时钟频率、抖动、干扰、漂移和相位等问题。

通过掌握这些问题的解决方案,用户可以更好地应对Xilinx中DCM的挑战,并确保系统的时钟管理工作正常运行。

xilinx平台DDR3设计教程之设计篇_中文版教程3

现在你应该已经看完了仿真和综合教程我们进入了设计篇,说白了就是讲一讲DDR IP的用户接口是怎么用的用户接口在哪里?请你打开下面这个目录里面的example_top.v这也就是你综合出来工程的顶层文件了我们来理一理这个文件的结构吧开头部分,全是介绍,你删了都关系然后是各种参数的设定这里有bank,row,column,rank,等等各种设置其实你不用动它们这些都是你之前选条子的时候已经选好了的不记得自己选什么条子了?乖乖,你不如再翻翻仿真教程先?各种仿真延迟参数也跟你选的条子有关你也别管了我都不管这些和DDR条子的各种接口你要知道,用户接口是个内部接口,你这里当然看不到了。

如果之前选了“use system clock”的话这里就看不到clk_ref相关的参考时钟管脚了。

这里顺便提一下column和row地址是在ddr3_addr里面复用的。

column一般是10bit宽度。

row一般14-16bit宽度。

ddr3_ba是选bank的,一般是3bit宽度,对应8个bank。

ddr3_cs_n是选rank的,有几个rank就有几个bit的宽度,因为要考虑啥都不选的情况,和之前几个参数不一样的。

各种参数配置相互之间的关系换算,选择继续和你没有关系作为设计者的你,可以继续无视这些部分各种wire定义你有兴趣研究不?我是没兴趣终于开始实例化DDR3了看见DDR3 右边的#号了没?这说明下面这些都不是管脚,而是配置用的参数。

你继续不用改这都六百多行了,你还是啥也不用改。

唉呀妈呀,DDR3实例化的实体总算找到了,就叫做u_DDR3找到没,我这里是747行接下来你要改动的,其实只有区区几行那就是769行Application interface开始的几个ports从770行的app_addr开始到775行的app_wdf_wren结束一共六行此外,因为你之前选了data mask,所以790行有个app_wdf_mask这一行的赋值你可以直接改成零。

Xilinx FPGA伴你玩转USB3.0与LVDS 第6章 基于FPGA的DDR3存储器控制实例

目录第6章基于FPGA的DDR3存储器控制实例 (2)6.1 DD R3 IP核配置与仿真 (2)6.1.1 DDR3 IP核概述 (2)6.1.2 DDR3 IP核配置 (3)6.1.3 DDR3 IP核仿真 (16)6.2 基于在线逻辑分析仪监控的DDR3数据读写 (23)6.2.1 功能概述 (23)6.2.2 DDR3控制器IP接口时序解析 (24)6.2.3 代码解析 (29)6.2.4 在线逻辑分析仪配置 (36)6.2.5 在线逻辑分析仪调试 (38)6.3 基于UART命令的DDR3数据读写 (41)6.3.1 功能概述 (41)6.3.2 代码解析 (42)6.3.3 板级调试 (46)本章导读高速时代,越来越高的带宽和数据吞吐量要求,使得用于协助FPGA做大数据缓存的存储器也必须与时俱进,SDRAM存储器从SDR、DDR、DDR2一路升级,如今已是DDR3甚至DDR4满天飞的时代。

本章通过Xilinx FPGA配置并例化使用DDR3存储器控制器IP核,引领读者掌握使用FPGA控制DDR3存储器进行基本的开发设计。

第6章基于FPGA的DDR3存储器控制实例6.1 DD R3 IP核配置与仿真6.1.1 DDR3 IP核概述本实例对Xilinx Vivado中提供的DDR3控制器IP核模块进行例化,实现基本的DDR3读写操作。

通过IP核自动生成的测试脚本实例实现对DDR3 IP核的仿真。

本实例对应工程文件夹at7_ex07。

DDR3控制器IP核内部模块及其与FPGA逻辑、DDR3芯片的接口框图如图6.1所示。

DDR3控制器包括用户接口(User Interface)模块、存储器控制器(Memory Controller)模块、初始化和校准(Initialization/Calibration)模块、物理层(Physical Layer)模块。

用户接口模块用于连接FPGA内部逻辑;存储器控制器模块实现DDR3的主要读写时序和数据缓存交互;初始化和校准模块实现DDR3芯片的上电初始化配置以及时序校准;物理层模块则实现和DDR3芯片的接口。

DDR3设计调试

DDR3设计调试DDR3设计配置:1.关于配置寄存器:部分配置寄存器基地址在0x2100_0000#define DDR3_BASE_ADDR (0x21000000)#define DDR_SDCFG (*(unsigned int*)(DDR3_BASE_ADDR + 0x00000008))#define DDR_SDRFC (*(unsigned int*)(DDR3_BASE_ADDR + 0x00000010))#define DDR_SDTIM1 (*(unsigned int*)(DDR3_BASE_ADDR + 0x00000018))#define DDR_SDTIM2 (*(unsigned int*)(DDR3_BASE_ADDR + 0x00000020))#define DDR_SDTIM3 (*(unsigned int*)(DDR3_BASE_ADDR + 0x00000028))#define DDR_PMCTL (*(unsigned int*)(DDR3_BASE_ADDR + 0x00000038))#define RDWR_LVL_RMP_WIN (*(unsigned int*)(DDR3_BASE_ADDR + 0x000000D4)) #define RDWR_LVL_RMP_CTRL (*(unsigned int*)(DDR3_BASE_ADDR + 0x000000D8)) #define RDWR_LVL_CTRL (*(unsigned int*)(DDR3_BASE_ADDR + 0x000000DC))#define DDR_ZQCFG (*(unsigned int*)(DDR3_BASE_ADDR + 0x000000C8))#define DDR_PHYCTRL (*(unsigned int*)(DDR3_BASE_ADDR + 0x000000E4))⼤部分寄存器位于chip-level registers 0x0262_0000 #define DDR3PLLCTL0 (*(unsigned int*)(0x02620330))#define DDR3PLLCTL1 (*(unsigned int*)(0x02620334))#define DATA0_WRLVL_INIT_RATIO (*(unsigned int*)(0x0262040C))#define DATA1_WRLVL_INIT_RATIO (*(unsigned int*)(0x02620410))#define DATA2_WRLVL_INIT_RATIO (*(unsigned int*)(0x02620414))#define DATA3_WRLVL_INIT_RATIO (*(unsigned int*)(0x02620418))#define DATA4_WRLVL_INIT_RATIO (*(unsigned int*)(0x0262041C))#define DATA5_WRLVL_INIT_RATIO (*(unsigned int*)(0x02620420))#define DATA6_WRLVL_INIT_RATIO (*(unsigned int*)(0x02620424))#define DATA7_WRLVL_INIT_RATIO (*(unsigned int*)(0x02620428))#define DATA8_WRLVL_INIT_RATIO (*(unsigned int*)(0x0262042C))#define DATA0_GTLVL_INIT_RATIO (*(unsigned int*)(0x0262043C))#define DATA1_GTLVL_INIT_RATIO (*(unsigned int*)(0x02620440))#define DATA2_GTLVL_INIT_RATIO (*(unsigned int*)(0x02620444))#define DATA3_GTLVL_INIT_RATIO (*(unsigned int*)(0x02620448))#define DATA4_GTLVL_INIT_RATIO (*(unsigned int*)(0x0262044C))#define DATA5_GTLVL_INIT_RATIO (*(unsigned int*)(0x02620450))#define DATA6_GTLVL_INIT_RATIO (*(unsigned int*)(0x02620454))#define DATA7_GTLVL_INIT_RATIO (*(unsigned int*)(0x02620458))#define DATA8_GTLVL_INIT_RATIO (*(unsigned int*)(0x0262045C))#define DDR3_CONFIG_REG_0 (*(unsigned int*)(0x02620404))#define DDR3_CONFIG_REG_12 (*(unsigned int*)(0x02620434))#define DDR3_CONFIG_REG_23 (*(unsigned int*)(0x02620460))#define DDR3_CONFIG_REG_24 (*(unsigned int*)(0x02620464))⼆、KICK Unlock和DDR3 PLL配置初始化DDR3控制器之前必须完成KICK Unlock和DDR3 PLL的配置。

【精品博文】FPGA器件预布线,以及ddr3调试问题汇总与总结

【精品博文】FPGA器件预布线,以及ddr3调试问题汇总与总结最近公司有一个新项目,方案定的是一款Cyclone V Soc FPGA,用到了两个ddr3,一个挂在Qsys系统的HPS里面,一个挂在Logic 的Hard Memory Controller那里,这两周一直在跟硬件配合,一起验证器件的管脚配置是否正确。

期间在调试这两个ddr3时遇到了好多问题,网上对这方面的资料也比较少,把这些问题的解决方法记录下来。

首先在综合ddr3 ip核时会遇到下面的errorID:15700 Termination calibration block atom "<name>" uses <name> port, which must be connected to <name> CAUSE: The specified Termination calibration block atom uses the specified port, but the port is not connected correctly. The port must be connected as specified.ACTION: Locate the specified port and connect it as specified.是因为OCT RZQIN这个引脚的问题,因为是用的FPGA逻辑里面的硬核资源做的设计,硬件那边也没有给这个引脚的原理图,找FAE和同事也没有得到很好的解答,在这里搜集资料花了很长时间。

Creating OCT SignalsIn ALTMEMPHY-based designs, the Quartus Prime Fitter creates the alt_oct block outside the IP core and connects it to the oct_ctl_rs_value and oct_ctl_rt_value signals.In UniPHY-based designs, the OCT block is part of the IP core, so the design no longer requires these two ports. Instead, the UniPHY-based design requires two additional ports, oct_rup and oct_rdn (for Strati III and Stratix IV devices), or oct_rzqin (for Stratix V devices). You must create these ports in theinstantiating entity as input pins and connect to the UniPHY instance. Then route these pins to the top leveldesign and connect to the OCT RUP and RDOWN resistors on the board. For information on OCT control block sharing, refer to “The OCT Sharing Interface” in this volume.DDR3 datasheet二、例化步骤本文皆用DDR3作为实例。

DDR3DIMM布线约束总结

DDR3DIMM布线约束总结1.总体约束DDR3 DIMM在布线过程中,根据其工作频率的不同,布线要求将有所降低。

各种电源的布线要求请参考DDR3 DIMM的控制器件(如DSP、ARM、CPU或FPGA)的具体要求。

不同信号线的特征阻抗也会随着不同的控制芯片、不同的工作频率有所不同。

比如,Altera的FPGA要求单端信号线阻抗50欧姆,差分信号线阻抗100欧姆;而Xilinx的FPGA要求单端信号线阻抗在低工作频率下为50欧姆,高工作频率下为40欧姆(1333Mb/s及以上);差分信号线阻抗在低工作频率下为100欧姆,高工作频率下为80欧姆(1333Mb/s及以上)。

以下主要总结走线长度约束。

1)同一组DQS/DQS#、DQ、DM之间的布线延时控制在±5ps以内,比如DQS0/DQS0#、DQ0~7、DM0之间控制在±5ps以内。

2)CK/CK#和所有的地址、命令、控制线之间的延时控制在±25ps 以内。

3)CK/CK#的布线延时必须大于任何DQS/DQS#的延时。

4)最大的DQS及其对应CK的总延时,减去最小的DQS及其对应CK的总延时必须小于1个CK时钟周期。

5)同一组DQS、DQ和DM在同一层走线。

6)CK和CKE远离地址线。

7)地址命令控制线远离DQS、DQ和DM线。

8)DQ/DQS/DM布线时需参考GND平面。

9)时钟、控制、地址和命令线在布线时需参考电源平面,如1.5V 或1.35V。

其他注意事项,如单端信号线、差分信号线的布线方法遵循高速信号线的布线要求即可。

2.补充说明针对第3、4条约束,需要做进一步说明。

当使用DIMM时,数据及选通信号(DQ/DQS/DM)、时钟线和地址控制命令线的布线长度需考虑DIMM本身的布线延时。

以RAW CARD A类DIMM为例,其时钟线和地址控制命令线到每个颗粒的布线延时是基本相等的,在DIMM上都进行了正确的补偿。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

DDR3 调试DDR3配置:时钟输入400M ,芯片V6 lx240t -2 ff1156 ,突发模式为BL=8,长度为64。

仿真:新建工程,添加用xilinx 生成DDR3核的sim_tb_top 等文件。

进行仿真。

traffic_gen 是xilinx 自带的一个测试DDR 的模块随机的读写DDR ,然后校验读取和写入的数值是不是一样。

如果有错,会拉高tg_compare_error 来报警。

而我们要做的就是自己看懂traffic_gen 向DDR 模块发送的时序,然后去重新编写一个模块来代替traffic_gen 。

traffic_gen 写数据时序图:traffic_gen 读数据时序图:设计读写模块:由于需要代替traffic_gen 模块,所以需要设计数据发送模块(cad_gen_1),命令时序模块(cad_gen_2)和数据校验模块(data_compare ),另外增加异步读写FIFO 来保证读写稳定不出错。

系统模块间信号连接图如下:Example_topDDR3_COREwr_fifoCad_gen_1Wr_endindout Cad_gen_2App_en App_wdf_wren App_wdf_end App_cmdApp_addrPhy_init_done App_rdy App_wdf_rdyRd_enrd_fifodin Wr_enRd_enData_co mparedataRd_en子模块功能cad_gen_1模块负责产要写入DDR3的数据。

先将数据存入写FIFO中。

cad_gen_2模块负责产生命令(app_com),地址(app_addr),控制器写数据有效使能(app_en),写数据使能(app_wdf_wren),写数据结束信号(app_wdf_end)。

data_compare模块负责将从的DDR3核中读出的数据与写入的数据相比较。

从而得出误码率。

子模块接口Cad_gen_1模块信号位宽方向描述Clk 1 Input 外部时钟rst 1 input 复位信号app_rdy 1 Input 由DDR3核输出的核ready信号app_wdf_rdy 1 Input 由DDR3核输出的接收数据ready信号phy_init_done 1 Input 核初始化成功时置1,只有初始化完成以后才能进行相应的读写操作。

fifo_wr_data 256 Output 写入DDR的数据,当FIFO的使能wr_fifo_wren为高时+1计数wr_fifo_wren 1 Output 数据存入fifo的使能,每次拉高两个时钟周期。

Cad_gen_2模块信号位宽方向描述clk 1 Input 与DDR核的时钟一直rst 1 Input 复位app_rdy 1 Input 由DDR3核输出的核ready信号phy_init_done 1 Input 核初始化成功时置1,只有初始化完成以后才能进行相应的读写操作。

app_wdf_rdy 1 Input 由DDR3核输出的接收数据ready信号app_cmd 3 Output 读写命令信号,1为读,0为写app_en 1 Output 操作地址app_addr的是能,只又它拉高的时候,命令和地址才有效。

(注意,当写入时,如果app_en为高,且app_rdy为低,则app_en保持高直到app_rdy为高时,app_en拉低)app_wdf_wren 1 Output 写数据使能,拉高时,写入数据有效。

在app_en有效的下一个时钟上升沿,数据使能拉高保持两个时钟周期后,拉低。

(准确的说,只能每个地址写入数据时,此信号要在app_en拉高后也拉高,持续两个时钟周期)app_addr 28 Output 读写的地址(注意:因为突发长度为8,所以地址应该以8递增。

)app_wdf_end1output写结束接口,在写使能有效的下一个时钟上升沿拉高,持续一个时钟周期。

Data_conpare 模块信号位宽方向 描述Clk 1 Input 时钟,与核一致Rst 1 Input 复位Data 256 Input DDR3核中读出的数据Rd_en 1 Input 读数据时,DDR3核反馈的读数据有效信号,拉高,则数据有效。

Error 1 Output 数据错误 Error_cnt32 Output错误计数读写时序图写入数据时序:Clk 8app_cmd 0app_addr app_en app_rdy app_wdf_rdy 12app_wdf_data app_wdf_wren app_wdf_end写数据时序图在保证app_wdf_rdy 和app_rdy 为高的情况下,写数据时,写命令app_cmd 为3’b000,地址每次计数+8。

当地址变化时,将app_en 置高一个时钟周期就置0,如果app_en 置高时,app_rdy 为低,则app_en 要保持拉高到app_rdy 置1后一个周期拉低,在此期间地址数据使能都不变。

在app_en 拉高的一个周期后,将app_wdf_wren 拉高2个时钟周期,并对应发送两个256位的数据,发送第二个数据时,拉高app_wdf_end 信号,表明,当前地址要发送的数据传输完成。

app_rdy 在app_rdy 为高的情况下,拉高一个周期表明当前地址数据有效。

否则数据地址均无效。

读出数据时序:Clk 8app_cmd 01app_addr app_en app_rdy 12app_rd_data app_rd_data_wren app_rd_data_end读数据时序图读数据和写数据类似,读数据命令app_cmd 为3’b001,同样在地址变化的同时拉高app_en 信号,同样要求app_rdy 为高,否则app_en 与地址保持到app_rdy 为高的下个时钟周期。

读使能app_rd_data_valid 与读数据app_rd_data 读结束app_rd_data_end 在地址给定后一段时间会从控制器中反馈出来。

对应的在软件中读写数据的时序图为:(其中data_valid_o 就是数据给DDR3的app_wdf_wren ,cmd_en_o 就是输出给DDR3的app_en ,data_wr_end_o 就是输出的app_wdf_end ,addr_o 是输出的写入或者读出的地址,具体由所对应的cmd 决定。

Data_o 为写入的数据,可写一个计数器,作为数据。

cmd_o 为读写命令。

) 软件写数据时序图:软件读数据时序图:DDR3总体工作状态机如下图:IDELWRITE_ADDRESSWRITE_DATAREAD_ADDRESSREAD_DELAYFINISH每次地址+8转入WRITE_DATA 状态,当地址计数到65536时,转入READ_ADDRESS 状态做一个计数器,让每个地址维持至少3个时钟周期,当计数器计到2时,跳转到WRITE_ADDRESS 状态每次当DDR3的fifo 可写,并且控制器有效时,读地址+8后挑转到READ_DELAY ,当地址计数器计到写地址挑战状态时就挑战到FINISH 状态做一个计数器,让每个地址维持至少3个时钟周期,当计数器计到1时,跳转到READ_ADDRESS 状态状态机停止运行控制器内部使用MMCM 产生的200M 时钟,用户接口使用系统顶层锁相环锁出的200M 时钟。

(会有相位差)FIFO 分为写数据FIFO 和读数据FIFO 。

写数据FIFO :● 写时钟:用户200M 时钟 ● 读时钟:控制器200M 时钟 ● 复位:控制器复位(高有效)● 写数据 (fifo_wr_data) :用户给的数据(计数器,在写使能为高,并且不满时计数)● 读数据 (app_wdf_data) :在控制器反馈的读使能时,读出数据。

● 写使能 (wrfifo_wren) :每次拉高2个时钟,保证每次写入2个数据。

● 读使能:将发送给DDR3核的写使能作为FIFO 的读使能。

将数据写入核中。

读数据FIFO :● 写时钟:控制器200M 时钟 ● 读时钟:用户200M 时钟● 复位:控制器复位(高有效)●写数据:从控制器中按所给地址读出的数据●写使能:给控制器后,控制器反馈的读数据有效信号app_rd_data_valid●读使能:因为读出的数据是在地址给定核一段时间后才会读出。

在检测到FIFO为非空的情况下,并且地址变化时,每次给2个时钟周期的使能,当命令app_cmd变为0时,则保持读使能为高,直到FIFO被读空。

FIFO的读写使能不能一直为高,否则会导致FIFO为满状态,这样会导致数据出错。

或者导致FIFO被读空。

在写数据时,fifo的使能与写入DDR3核的使能保持一致,每个地址拉高两个时钟周期,取出FIFO中的2个256位数据写入DDR3核。

读数据时,将给定有效地址后核反馈的读使能作为FIFO的写入使能,将读出数据写入FIFO。

这样读FIFO不会空,写FIFO也不会满,保证数据传输在异步FIFO中能正确传输。