SDMA15C-8.TB中文资料

聚灿8X15技术规格书new中英文版837

存储及使用条件(Ta=25℃)Store and use condition(Ta=25℃)

item

正向直流电流 forward direction DC electricity 反向电压 reverse voltage 可操作温度 exercisable temperature 储存温度 Store temperature ESD(人体模式)ESD Human Body Model

sign

IF VR TOPR TSTG ESDS

rated value

20 10 -30~85 -40~100 2000

unit

mA V ℃ ℃ V

*ESD 测试结果是建立在统计测量基础上的,销售商不能对每个 chip 提供质保。 The ESD result is

based on statistical measurement, so vendors can’t provide quality assurance for every chip. 光电性能(Ta=25℃)photoelectricity performance (Ta=25℃)

item

sign

test condition

IF=20 mA

grade

V1

min

3 3.2 3.4 --

model

3.1 3.3 3.5 ------------

max

3.2 3.4 3.6 1 452.5 455 457.5 460 18.5 20 21.5 23 24.5 26

unit

正向电压 Forward voltage 反向电流 Reverse current

description

Chip size Chip thickness N bonding pad diameter P bonding pad diameter P – N interval bonding pad material

三极管参数

SHENZHEN HIGHFOUND CO., LTD

摘要

恒丰德公司 WINSEMI 产品线 产品特性 抗冲击特性比较 导通压降特性比较 SCR特性比较 MCR温度特性曲线 BJT的开关时间比较 可靠性测试标准

2

WINSEMI产品线

3

WINSEMI产品

Power BJT 分离式 功率器件产品线

漏极电流ID

漏源极电压VDS

VV X10= VDS

注:其中有几颗常规料沿袭了IR公司的编码如:640(18N20); 730(6N40); 740(10N40); 830(5N50); 840(8N50); 3710(59N10)

10

POWER MOSFET-功率场效应管(1)

11

POWER MOSFET-功率场效应管(2)

TO202-3

TO126 TO252

TO220Insulated

Z0405MF

TO220

WTPA12A60TW STPB12A60TW

TO220Insulated TO220

BTA12-600TW BTB12-600TW MAC12-8FP BTA212-600E

注: ST尾缀 S<5mA; T<10mA; B<35mA; C<50mA PHI尾缀 D<5mA; E<10mA; F<25mA; 空<35mA; G<50mA

It gives : a narrow current gain to minimize asymmetry switching which induce device to destruct. 较小的电流增益使开关电源的不对称减到最小。 a wide forward biased SOA and reverse biased SOA. a enhanced switching speed and low dynamic Vce(sat) which makes system efficiency high. 更快的交换速度以及稳定的集电极-发射极电压,使系统效率更高,更稳定

ADC0808S125资料

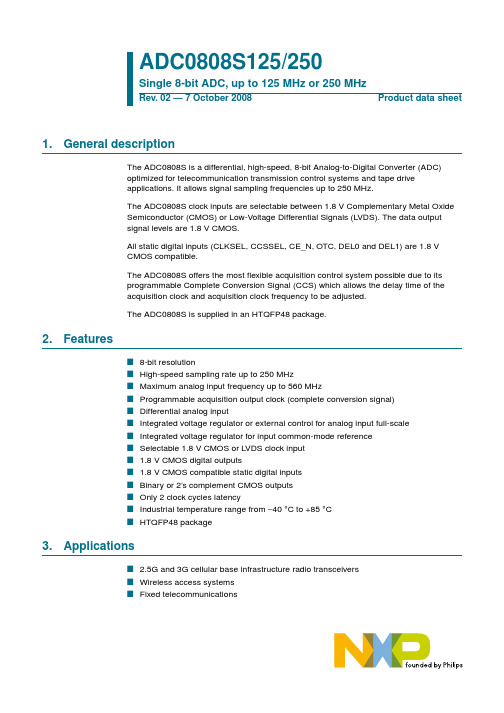

CLOCK DRIVER

ADC0808S

LATCH

17 26

CCS CCSSEL

IN INN

33 32

TRACK AND HOLD

8

RESISTOR LADDERS

ADC CORE

LATCH

8

D0 to D7 21 OTC

FSIN/ REFSEL

30 U/I LATCH

20

IR

INTERNAL REFERENCE

元器件交易网

ADC0808S125/250

Single 8-bit ADC, up to 125 MHz or 250 MHz

Rev. 02 — 7 October 2008 Product data sheet

1. General description

The ADC0808S is a differential, high-speed, 8-bit Analog-to-Digital Converter (ADC) optimized for telecommunication transmission control systems and tape drive applications. It allows signal sampling frequencies up to 250 MHz. The ADC0808S clock inputs are selectable between 1.8 V Complementary Metal Oxide Semiconductor (CMOS) or Low-Voltage Differential Signals (LVDS). The data output signal levels are 1.8 V CMOS. All static digital inputs (CLKSEL, CCSSEL, CE_N, OTC, DEL0 and DEL1) are 1.8 V CMOS compatible. The ADC0808S offers the most flexible acquisition control system possible due to its programmable Complete Conversion Signal (CCS) which allows the delay time of the acquisition clock and acquisition clock frequency to be adjusted. The ADC0808S is supplied in an HTQFP48 package.

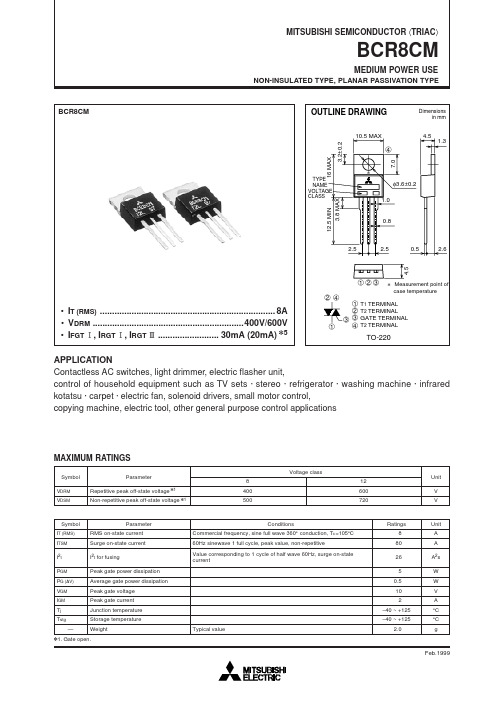

BCR8中文资料

GATE TRIGGER VOLTAGE (Tj = t°C) GATE TRIGGER VOLTAGE (Tj = 25°C)

MAXIMUM ON-STATE POWER DISSIPATION ON-STATE POWER DISSIPATION (W) 16 CASE TEMPERATURE (°C) 14 12 360° CONDUCTION 10 RESISTIVE, INDUCTIVE 8 LOADS 6 4 2 0 0 2 4 6 8 10 12 14 16 160 140 120 100 80 60

Symbol IT (RMS) ITSM I2t PGM PG (AV) VGM IGM Tj Tstg —

Parameter RMS on-state current Surge on-state current I2t for fusing Peak gate power dissipation Average gate power dissipation Peak gate voltage Peak gate current Junction temperature Storage temperature Weight Typical value

MAXIMUM RATINGS

Symbol VDRM VDSM Parameter Repetitive peak off-state voltage V1 Non-repetitive peak off-state voltage V1 Voltage class 8 400 500 12 600 720 Unit V V

GATE TRIGGER VOLTAGE VS. JUNCTION TEMPERATURE 100 (%) 103 7 5 4 3 2 102 7 5 4 3 2 101 –60 –40 –20 0 20 40 60 80 100 120 140 JUNCTION TEMPERATURE (°C) TYPICAL EXAMPLE TRANSIENT THERMAL IMPEDANCE (°C/W)

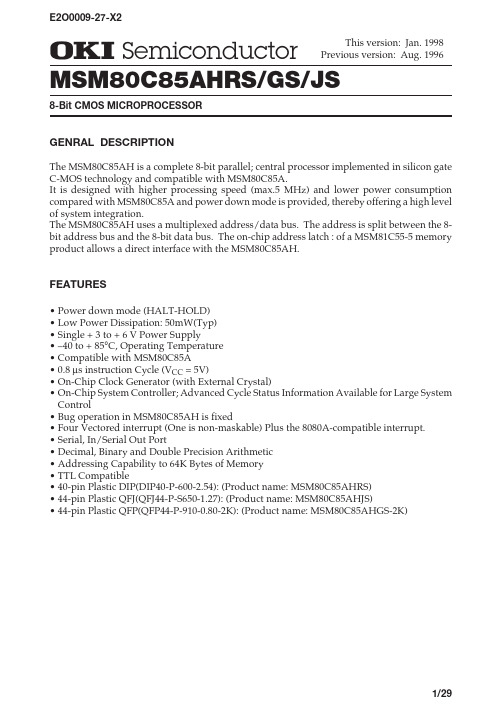

M80C85资料

GENRAL DESCRIPTIONThe MSM80C85AH is a complete 8-bit parallel; central processor implemented in silicon gate C-MOS technology and compatible with MSM80C85A.It is designed with higher processing speed (max.5 MHz) and lower power consumption compared with MSM80C85A and power down mode is provided, thereby offering a high level of system integration.The MSM80C85AH uses a multiplexed address/data bus. The address is split between the 8-bit address bus and the 8-bit data bus. The on-chip address latch : of a MSM81C55-5 memory product allows a direct interface with the MSM80C85AH.FEATURES•Power down mode (HALT-HOLD)•Low Power Dissipation: 50mW(Typ)•Single + 3 to + 6 V Power Supply•–40 to + 85°C, Operating Temperature •Compatible with MSM80C85A •0.8 m s instruction Cycle (V CC = 5V)•On-Chip Clock Generator (with External Crystal)•On-Chip System Controller; Advanced Cycle Status Information Available for Large System Control•Bug operation in MSM80C85AH is fixed•Four Vectored interrupt (One is non-maskable) Plus the 8080A-compatible interrupt.•Serial, In/Serial Out Port•Decimal, Binary and Double Precision Arithmetic •Addressing Capability to 64K Bytes of Memory •TTL Compatible•40-pin Plastic DIP(DIP40-P-600-2.54): (Product name: MSM80C85AHRS)•44-pin Plastic QFJ(QFJ44-P-S650-1.27): (Product name: MSM80C85AHJS)•44-pin Plastic QFP(QFP44-P-910-0.80-2K): (Product name: MSM80C85AHGS-2K)MSM80C85AHRS/GS/JS8-Bit CMOS MICROPROCESSORE2O0009-27-X2元器件交易网FUNCTIONAL BLOCK DIAGRAMINTR INTA 5.5 6.57.5TRAP SID SODRSTX1X2CLK OUT READY RD WR ALE S0S1IO / M HOLD HLDA RESET IN RESET OUT A15 - A8Address BusAD7- ADAddress/Data BusPIN CONFIGURATION (TOP VIEW)40 pin Plastic DIPA 8HOLD HLDA CLK(OUT)RESET IN READY IO/M S 1RD WR ALE S 0A 15A 14A 13A 12A 11A 10A 9V CC 39383736353433READY IO/M S 1RD WR NC ALE TRAP RST7.5RST6.5RST5.5INTR NC INTA 18192021222324A D 4N C A D 5A D 6A D 7G N D A 865432144S I DS O DR E S E T X 2X 1N C7891011121332313029S 0A 15A 14AD 0AD 1AD 2AD 314151617A 13V C C25262728A 9A 10A 11A 1243424140H O L D H L D AC L K (O R E S E T I NTRAP RST7.5RST6.5RST5.5INTR INTA AD 0A D 4A D 5A D 6A D 7G N D V C C A 8AD 1AD 2AD 3NC A 9A 10A 11N CMSM80C85AH FUNCTIONAL PIN DEFINITIONThe following describes the function of each pin:A 0 - A 7(Input/Output)3-state A 8 - A 15(Output, 3-state)Multiplexed Address/Data Bus: Lower 8-bits of the memory address (or I/O address) appear on the bus during the first clock cycle (T state) of a machine cycle. It then becomes the data bus during the second and third clock cycles.Address Bus: The most significant 8-bits of the memory address or the 8-bits of the I/O address, 3-stated during Hold and Halt modes and during RESET.Symbol FunctionALE (Output)Address Latch Enable: It occurs during the first clock state of a machine cycle and enables address to get latched into the on-chip latch peripherals. The falling edge of ALE is set to guarantee setup and hold times for the address information. The falling edge ALE can also be used to strobe the status information ALE is never 3-state.S 0 , S 1 , IO/M (Output)Machine cycle status:IO/M S 1 S 0 States S 1 can be used as an advanced R/W status. IO/M , S 0 and S 1 become valid at the beginning ofa machine cycle and remain stable throughout the cycle. The falling edge of ALE may be used to latch the state of these lines.RD(Output, 3-state)READ control: A low level on RD indicates the selected memory or I/O device is to be read thatthe Data Bus is available for the data transfer, 3-stated during Hold and Halt modes and during RESET.WR(Output, 3-state)WRITE control: A low level on WR indicates the data on the Data Bus is to be written into the selected memory or I/O location. Data is set up at the trailing edge of WR , 3-stated during Hold and Halt modes and during RESET.READY (Input)If READY is high during a read or write cycle, it indicates that the memory or peripheral is ready to send or receive data. If READY is low, the cpu will wait an integral number of clock cycles for READY to go high before completing the read or write cycle READY must conform to specified setup and hold times.HOLD (Input)HLDA (Output)HOLD ACKNOWLEDGE: Indicates that the cpu has received the HOLD request and that it will relinquish the bus in the next clock cycle. HLDA goes low after the Hold request is removed. The cpu takes the bus one half clock cycle after HLDA goes low.HOLD indicates that another master is requesting the use of the address and data buses.The cpu, upon receiving the hold request, will relinquish the use of the bus as soon as the completion of the current bus transfer. Internal processing can continue. The processor can regain the bus only after the HOLD is removed. When the HOLD is acknowledged, the Address, Data, RD , WR , and IO/M lines are 3-stated. And status of power down is controlled by HOLD.INTR (Output)INTERRUPT REQUEST: Is used as a general purpose interrupt. It is sampled on during the next to the last clock cycle of an instruction and during Hold and Halt states. If it is active, the Program Counter (PC) will be inhibited from incrementing and an INTA will be issued. During this cycle a RESTART or CALL instruction can be inserted to jump to the interrupt service routine. The INTR is enabled and disabled by software. It is disabled by Reset and immediately after an interrupt is accepted. Power down mode is reset by INTR.INTA (Output)INTERRUPT ACKNOWLEDGE: Is used instead of (and has the same timing as) RD during the instruction cycle after an INTR is accepted.RST 5.5RST 6.5RST 7.5(Input)RESTART INTERRUPTS: These three inputs have the same timing as INTR except they cause an internal RESTART to be automatically inserted.The priority of these interrupts is ordered as shown in Table 1. These interrupts have a higher priority than INTR. In addition, they may be individually masked out using the SIM instruction. Power down mode is reset by these interrupts.TRAP (Input)Trap interrupt is a nonmaskable RESTART interrupt. It is recognized at the same timing as INTR or RST 5.5 - 7.5. It is unaffected by any mask or Interrupt Disable. It has the highest priority of any interrupt. (See Table 1.) Power down mode is reset by input of TRAP.001100101110101Memory write Memory read I/O write I/O readOpcode fetchIO/M S 1 S 0 States 1...10¥¥10¥¥Interrupt Acknowledge Halt = 3-stateHold (high impedance)Reset ¥ = unspecifiedName Address Branched To (1)When Interrupt OccursType TriggerRST 7.53CH 34H Rising edge (latched).High level unitl sampled.RST 6.5RST 5.52CH (2)High level until sampled.High level until sampled.INTRTRAP Priority 2345124H Rising edge and high level unit sampled.Table 1 Interrupt Priority, Restart Address, and SensitivityNotes:(1)The processor pushes the PC on the stack before branching to the indicatedaddress.(2)The address branched to depends on the instruction provided to the cpuwhen the interrupt is acknowledged.RESET IN (Input)Sets the Program Counter to zero and resets the Interrupt Enable and HLDA flip-flops and release power down mode. The data and address buses and the control lines are 3-stated during RESET and because of the asynchronous nature of RESET IN, the processor's internal registers and flags may be altered by RESET with unpredictable results. RESET IN is a Schmitt-triggered input, allowing connection to an R-C network for power-on RESET delay. The cpu is held in the reset condition as long as RESET IN is applied.Symbol FunctionRESET OUT (Output)Indicated cpu is being reset. Can be used as a system reset. The signal is synchronized to the processor clock and lasts an integral number of clock periods.X 1, X 2(Input)X 1 and X 2 are connected to a crystal to drive the internal clock generator. X 1 can also be an external clock input from a logic gate. The input frequency is divided by 2 to give the processor's internal operating frequency.SID (Input)Serial input data line. The data on this line is loaded into accumulator bit 7 whenever a RIM instruction is executed.SOD (Output)Serial output data line. The output SOD is set or reset as specified by the SIM instruction.V CC + 5 Volt supply GNDGround Reference.CLK (Output)Clock Output for use as a system clock. The period of CLK is twice the X 1, X 2 input period.FUNCTIONAL DESCRIPTIONThe MSM80C85AH is a complete 8-bit parallel central processor. It is designed with silicon gate C-MOS technology and requires a single +5 volt supply. Its basic clock speed is 5 MHz, thus improving on the present MSM80C85A's performance with higher system speed and power down mode. Also it is designed to fit into a minimum system of two IC's: The CPU (MSM80C85AH), and a RAM/IO (MSM81C55-5)The MSM80C85AH has twelve addressable 8-bit register pairs. Six others can be used interchangeably as 8-bit registers or 16-bit register pairs. The MSM80C85AH register set is as follows:PC 16-bit address 8-bit ¥ 6 or 16-bits ¥ 3BC, DE, HL SP 16-bit address 5 flags (8-bit space)Flags or FProgram CounterACC or A 8-bits Accumulator Mnemonic ContentsRegisterGeneral-Purpose Registers; data pointer (HL)Stack Pointer Flag RegisterThe MSM80C85AH uses a multiplexed Data Bus. The address is spilt between the higher 8-bit Address Bus and the lower 8-bit Address/Data Bus. During the first T state (clock cycle) of a machine cycle the low order address is sent out on the Address/Data Bus. These lower 8-bits may be latched externally by the Address Latch Enable signal (ALE). During the rest of the machine cycle the data bus is used for mamory or I/O data.The MSM80C85AH provides RD , WR , S 0, S 1, and IO/M signals for bus control. An Interrupt Acknowledge signal (INTA ) is also provided. Hold and all Interrupts are synchronized with the processor's internal clock. The MSM80C85AH also provides Serial Input Data (SID) and Serial Output Data (SOD) lines for a simple serial interface.In addition to these features, the MSM80C85AH has three maskable, vector interrupt pins, one nonmaskable TRAP interrupt and power down mode with HALT and HOLD.INTERRUPT AND SERIAL I/OThe MSM80C85AH has 5 interrupt inputs: INTR, RST 5.5 RST 6.5, RST 7.5, and TRAP. INTR is identical in function to the 8080A INT. Each of the three RESTART inputs, 5.5, 6.5, and 7.5, has a programmable mask. TRAP is also a RESTART interrupt but it is nonmaskable.The three maskable interrupts cause the internal execution of RESTART ( saving the program counter in the stack branching to the RESTART address) it the interrupts are enable and if the interrupt mask is not set. The nonmaskable TRAP causes the internal execution of a RESTART vector independent of the state of the interrupt enable or masks. (See Table 1.)There are two different types of inputs in the restart interrupt. RST 5.5 and RST 6.5 are high level-sensitive like INTR (and INT on the 8080A) and are recognized with the same timing as INTR. RST 7.5 is rising edge-sensitive.For RST 7.5, only a pulse is required to set an internal flip-flop which generates the internal interrupt request. The RST 7.5 request flip-flop remains set until the request is serviced. Then it is reset automatically, This flip-flop may also be reset by using the SIM instruction or by issuing a RESET␣IN to the MSM80C85AH. The RST 7.5 internal flip-flop will be set by a pulse on the RST 7.5 pin even when the RST 7.5 interrupt is masked out.The interrupts are arranged in a flixed priority that determines which interrupt is to be recognized if more than one is pending, as follows: TRAP-highest priority, RST 7.5, RST 6.5, RST 5.5, INTR-lowest priority. This priority scheme does not take into account the priority of a routine that was started by a higher priority interrupt. RST 5.5 can interrupt an RST 7.5 routine if the interrupt are re-enabled before the end of the RST 7.5 routine.The TRAP interrupt is useful for catastrophic evens such as power failure or bus error. The TRAP input is recognized just as any other interrupt but has the highest priority. It is not affected by any flag or mask. The TRAP input is both edge and level sensitive. The TRAP input must go high and remain high until it is acknowledged. It will not be recognized again until it goes low, then high again. This avoids any false triggering due to noise or logic glitches. Figure 3 illustrates the TRAP interrupt request circuitry within the MSM80C85AH. Note that the servicing of any interrupt (TRAP, RST 7.5, RST 6.5, RST 5.5,INTR) disables all future interrupts (except TRAPs) until an El instruction is executed.The TRAP interrupt is special in that it disables interrupts, but preserves the previous interrupt enable status. Performing the first RIM instruction following a TRAP interrupt allows you to determine whether interrupts were enabled or disabled prior to the TRAP. All subsequent RIM instructions provide current interrupt enable status. Performing a RIM instruction following INTR or RST 5.5-7.5 will provide current interrupt Enable status, revealing that Interrupts are disabled.The serial I/O system is also controlled by the RIM and SIM instructions. SID is read by RIM, and SIM sets the SOD data.AcknowledgeFigure 3 Trap and RESET IN CircuitDRIVING THE X 1 AND X 2 INPUTSYou may drive the clock inputs of the MSM80C85AH with a crystal, or an external clock source.The driving frequency must be at least 1 MHz, and must be twice the desired internal clock frequency; hence, the MSM80C85AH is operated with a 6 MHz crystal (for 3 MHz clock). If a crystal is used, it must have the following characteristics:Parallel resonance at twice the clock frequency desired C L (load capacitance) £ 30 pF C S (shunt capacitance) £ 7 pFR S (equivalent shunt resistance) £ 75 ohms Drive level: 10 mWFrequency tolerance: ±0.05% (suggested)Note the use of the capacitors between X 1, X 2 and ground. These capacitors are required to assure oscillator startup at the correct frequency.Figure 4 shows the recommended clock driver circuits. Note in B that a pull-up resistor is required to assure that the high level voltage of the input is at least 4 V.For driving frequencies up to and including 6 MHz you may supply the driving signal to X, and leave X 2 open-circuited (Figure 4B). To prevent self-oscillation of the MSM80C85AH, be sure that X 2 is not coupled back to X 1 through the driving circuit.Note:Since the constant values may vary depending on oscillator, consult the manufacturer of the oscillator used when designing a circuit.Figure 4 Clock Driver Circuits* X 2 Left Floating33 pF Capacitor required for crystal frequency 10 to 6.25 MHz 50 pF Capacitor required for crystal frequency 6.25 to 4 MHz 100 pF Capacitor required for crystal frequency <4 MHzA. Quartz Crystal Clock DriverB. 1 - 10 MHz Input Frequency External Clock Drive CircuitBASIC SYSTEM TIMINGThe MSM80C85AH has a multiplexed Data Bus. ALE is used as a strobe to sample the lower 8-bits of address on the Data Bus. Figure 5 shows an instruction fetch, memory read and I/O write cycle (as would occur during processing of the OUT instruction). Note that during the I/ O write and read cycle that the I/O port address is copied on both the upper and lower half of the address.There are seven possible types of machine cycles. Which of these seven takes place is defined by the status of the three status lines (IO/M, S1, S0) and the three control signals (RD, WR,and INTA). (See Table 2.) The status line can be used as advanced controls (for device selection, for example), since they become active at the T1 state, at the outset of each machine cycle. Control lines RD and WR become active later, at the time when the transfer of data is to take place, so are used as command lines.A machine cycle normally consists of three T states, with the exception of OPCODE FETCH, which normally has either four or six T states (unless WAIT or HOLD states are forced by the receipt of READY or HOLD inputs). Any T state must be one of ten possible states, shown in Table 3.Table 2 MSM80C85AH Machine Cycle ChartTable 3 MSM80C85AH Machine State Chart0= Logic "0"1= Logic "1"TS = High Impedance ¥= UnspecifiedNotes:(1) ALE not generated during 2nd and 3rd machine cycles of DAD instruction.(2) IO/M = 1 during T 4 - T 6 of INA machine cycle.A AD IO/Figure 5 MSM80C85AH Basic System TimingPOWER DOWN ModeThe MSM80C85AH is compatible with the MSM80C85A in function and POWER DOWN mode. This reduces power consumption further.There are two methods available for starting this POWER DOWN mode. One is through software control by using the HALT command and the other is under hardware control by using the pin HOLD. This mode is released by the HOLD, RESET, and interrupt pins (TRAP, RST7.5, RST6.5 RST5.5, or INTR). (See Table 4.)Since the sequence of HALT, HOLD, RESET, and INTERRUPT is compatible with MSM80C85A, every the POWER DOWN mode can be used with no special attention.Start by means of Halt command Start by means of HOLD pin Released by using pins RESET and INTERRUPT (not by pin HOLD) Released by using RESET and HOLD pins (not by interrupt pins)Table 4 POWER DOWN Mode Releasing Method(1) Start by means of HALT command (See Figures 6 and 7.)The POWER DOWN mode can be started by executing the HALT command.At this time, the system is put into the HOLD status and therefore the POWER DOWN mode cannot be released even when the HOLD is released later.In this case, the POWER DOWN mode can be released by means of the RESET or interrupt.(2) Start by means of HOLD pin (See Figure 8.)During the execution of commands other than the HALT, the POWER DOWN mode is started when the system is put into HOLD status by means of the HOLD pin.Since no interrupt works during the execution of the HOLD, the POWER DOWN mode cannot be released by means of interrupt pins. In this case, the POWER DOWN mode can be released either by means of the RESET pin or by releasing the HOLD status by means of HOLD pin.CLK (OUT)ALEAD 0-7CPU MODE RESET INFigure 6 Started by HALT and Released by RESET INCLK (OUT)ALEHOLD CPU MODEHLDAFigure 8 Started and Released by HOLDCLK (OUT)ALECPU MODERST5.5Figure 7 Started by HALT and Released by RST5.5ABSOLUTE MAXIMUM RATINGS–55 - +150MSM80C85AHRS Power Supply Voltage V CC –0.5 - 7V Input Voltage V IN –0.5 - V CC +0.5V Output Voltage V OUT –0.5 - V CC +0.5V Storage Temperature T STG °CPower DissipationP D0.7WParameter Units Symbol With respect to GND—Ta = 25°CCondition LimitsMSM80C85AHGS MSM80C85AHJS1.01.0OPERATING RANGELimits Power Supply Voltage V CC 3 - 6V Operating TemperatureT OP–40 - +85°CParameterUnit Symbol RECOMMENDED OPERATING CONDITIONSDC CHARACTERISTICS"L"V ILR —–0.3+0.8Typ.Power Supply Voltage V CC 5V T OP +25"L" Input Voltage V IL —"H" Output Voltage V IH —Min.4.5–40–0.32.2Max.5.5+85+0.8V CC +0.3ParameterUnit Symbol °C V V Operating Temperature V V IHR—3.0V CC +0.3VRESET IN Input Voltage "H"RESET IN Input VoltageTyp.Max."L" Output Voltage V OL —0.4V "H" Output Voltage V OH ——V ——V Parameter Unit Symbol Min.—3.0V CC - 0.4I OL = 2.5 mA I OH = –2.5 mA I OH = –100 m A ConditionsV CC = 4.5 V - 5.5 V Ta = –40°C - +85°C Input Leak Current I LI —10m A Output Leak CurrentI LO—10m A –10–100 £ V IN £ V CC 0 £ V OUT £ V CC T cyc = 200 ns C L = 0 pF at reset Operating SupplyCurrentI CC1020mA 510mA——T cyc = 200 nsC L = 0 pF at power down modeAC CHARACTERISTICSParameter Symbol Condition Min.Max.UnitCLY Cycle Period t CYCt CYC=200 nsCL=150 pF 2002000nsCLY Low Time t140—ns CLY High Time t270—ns CLY Rise and Fall Time t r, t f—30nsX1 Rising to CLK Rising t XKR25120nsX1 Rising to CKK Falling t XKF30150nsA8~15 Valid to Leading Edge of Control (1)t AC115—ns AD0~7 Valid to Leading Edge of Control t ACL115—ns AD0~15 Valid Data in t AD—350ns Address Float After Leading Edge of RD INTA t AFR—0nsA8~15 Valid Before Trailing Edge of ALE (1)t AL50—ns AD0~7 Valid Before Trailing Edge of ALE t ALL50—ns READY Valid from Address Valid t ARY—100ns Address (A8~15) Valid After Control t CA60—ns Width of Control Law (RD, WR, INTA)t CC230—ns Trailing Edge of Control to Leading Edges of ALE t CL25—ns Data Valid to Trailing Edge of WR t DW230—ns HLDA to Bus Enable t HABE—150ns Bus Float After HLDA t HABF—150ns HLDA Valid to Trailing Edge of CLK t HACK40—ns HOLD Hold Time t HDH0—ns HOLD Step Up Time to Trailing Edge of CLK t HDS120—ns INTR Hold Time t INH0—ns INTR, RST and TRAP Setup Time to Falling Edge of CLK t INS150—ns Address Hold Time After ALE t LA50—ns Trailing Edge of ALE to Leading Edge of Control t LC60—ns ALE Low During CLK High t LCK50—ns ALE to Valid Data During Read t LDR—270ns ALE to Valid Data During Write t LDW—140ns ALE Width t LL80—ns ALE to READY Stable t LRY—30ns Trailing Edge of RD to Re-enabling of Address t RAE90—ns RD (or INTA) to Valid Data t RD—150ns Control Trailing Edge to Leading Edge of Next Control t RV220—ns Data Hold Time After RD INTA (7)t RDH0—ns READY Hold Time t RYH0—ns READY Setup Time to Leading Edge of CLK t RYS100—ns Data Valid After Trailing Edge of WR t WD60—ns LEADING Edge of WR to Data Vaild t WDL—20ns(Ta = –40°C ~ 85°C, V CC = 4.5 V ~ 5.5 V)Notes:(1)A 8 - A 15 address Specs apply to IO/M , S 0 and S 1.(2)Test condition: t CYC =200 ns C L =150 pF(3)For all output timing where C L =150 pF use the following correction factors:25 pF £ C L < 150 pF : –0.10ns/pF 150 pF < C L £ 200 pF : +0.30ns/pF(4)Output timings are measured with purely capacitive load.(5)All timings are measured to output voltage V L =0.8 V, V H =2.2 V, and 1.5 Vwith 10 ns rise and fall time on inputs.(6)To calculate timing specifications at other values of t CYC use Table 7.(7)Data hold time is guaranteed under all loading conditions.2.40.45Input Waveform for A.C. Tests:(1/2)T - 50t AL Min (Ta = -40°C - +85°C, V CC = 4.5 V - 5.5 V, C L = 150 pF)(1/2)T - 50t LA Min (1/2)T - 20t LL Min (1/2)T - 50t LCK Min (1/2)T - 40t LC Min (5/2+N)T - 150t AD Max (3/2+N)T - 150t RD Max (1/2)T - 10t RAE Min (1/2)T - 40t CA Min (3/2+N)T -70t DW Min (1/2)T - 40t WD Min (3/2+N)T - 70t CC Min (1/2)T - 75t CL Min (3/2)T - 200t ARY Max (1/2)T - 60t HACK Min (1/2)T + 50t HABF Max (1/2)T + 50(2/2)T - 85t HABE Max t AC Min (1/2)T - 60t 1Min (1/2)T - 30t 2Min (3/2)T - 80t RV Min t LDRMax——————————————————————MSM80C85AH Table 7 Bus Timing Specification as a T CYC DependentNote:N is equal to the total WAIT states.T = t CYC(2+N)T -130X1 INPUTCLKOUTPUTFigure 6 Clock Timing Waveform READ OPERATIONCLKA8-A15 AD0-AD7ALE RD / INTA T1T2T3T1WRITE OPERATIONCLK T1A8-A15AD0-AD7ALEWRT2T3T1CLKA 8~A 15AD 0~AD 7ALERD / INTAREADYT 1T 2T WAIT T 3T 1Note: READY must remain stable during setup and hold times.Figure 7 MSM80C85AH Bus Timing, With and Without WaitRead operation with Wait Cycle (Typical)–same READY timing applies to WRITE operationCLK HOLDHLDA BUSFigure 8 MSM80C85AH Hold TimingHOLD OPERATIONNOTE: (1) IO/M is also floating during this time.Figure 9 MSM80C85AH Interrupt and Hold TimingMOVE, LOAD, AND STORE MOVr1 r2MOV M r MOV r M MVI r MVI M LXI B LXI D LXI H LXI SP STAX B STAX D LDAX B LDAX D STA LDA SHLD LHLD XCHG MnemonicDescriptionInstruction Code (1)Clock (2)Cycles000000000000000001111000000000000001D 1D D 10011000011111D 1D D 10101010111000D 0D D 00000001101011S S 1110000000000000S S 1110000111111111S S 0001111000000001D 7D 6D 5D 4D 3D 2D 1D 0477710101010107777131316164Move register to register Move register to memory Move memory to register Move immediate register Move immediate memory Load immediate register Pair B & C Load immediate register Pair D & E Load immediate register Pair H & L Load immediate stack pointer Store A indirect Store A indirect Load A indirect Load A indirect Store A direct Load A direct Store H & L direct Load H & L direct Exchange D & E H & L registers STACK OPS PUSH B PUSH D PUSH H PUSH PSW POP B POP D POP H POP PSW XTHL SPHL 111111111111111111110011001111010101010100000000011111000000000000001011111111111212121210101010166Push register Pair B & C on stack Push register Pair D & E on stack Push register Pair H & L on stack Push A and Flags on stackPop register Pair B & C off stack Pop register Pair D & E off stack Pop register Pair H & L off stack Pop A and Flags off stack Exchange top of stack H & L H & L to stack pointer JUMP JMP JC JNC JZ JNZ JP JM JPE JPO PCHL 11111111111111111111000001111101100110000101001101000000000011111111101000000001107/107/107/107/107/107/107/107/106Jump unconditional Jump on carry Jump on no carry Jump on zero Jump on no zero Jump on positive Jump on minus Jump on parity even Jump on parity oddH & L to program counter CALL CALL CC CNC CZ CNZ CP CM CPE CPO111111111111111111000001111011001100110100110111111111000000000100000000189/189/189/189/189/189/189/189/18Call unconditional Call on carry Call on no carry Call on zero Call on no zero Call on positive Call on minus Call on parity even Call on parity oddTable 8 Instruction Set SummaryRETURN RET RC RNC RZ RNZ RP RM RPE RPO Mnemonic DescriptionInstruction Code (1)Clock (2)Cycles 111111111111111111000001111011001100110100110000000000000000000100000000D 7D 6D 5D 4D 3D 2D 1D 0106/126/126/126/126/126/126/126/12ReturnReturn on carry Return on no carry Return on zero Return on no zero Return on positive Return on minus Return on parity even Return on parity odd RESTART RST11A A A 11112Restart INPUT/OUTPUT IN OUT11110011100011111010Input OutputINCREMENT AND DECREMENT INR r DCR r INR M DCR M INX B INX D INX H INX SP DCX B DCX D DCX H DCX SP 000000000000000000000000D D 1100110011D D 1101010101D D 000000111111110000000000001111111101011111111144101066666666Increment register Decrement register Increment memory Decrement memory Increment B & C registers Increment D & E registers Increment H & L registers Increment stack pointer Decrement B & C Decrement D & E Decrement H & L Decrement stack pointer ADD ADD r ADC r ADD M ADC M ADI ACI DAD B DAD D DAD H DAD SP 11111100000000110000000000001100000001010101011111S S 11110000S S 11110000S S 0000111144777710101010Add register to AAdd register to A with carry Add memory to AAdd memory to A with carry Add immediate to AAdd immediate to A with carry Add B & C to H & L Add D & E to H & L Add H & L to H & LAdd stack pointer to H & LSUBTRACT SUB r SBB r SUB M SBB M SUI SBI111111000011000000111111010101S S 1111S S 1111S S 0000447777Subtract register from ASubtract register from A with borrow Subtract memory from ASubtract memory from A with borrow Subtract immediate from ASubtract immediate from A with borrowTable 8 Instruction Set Summary cont'd。

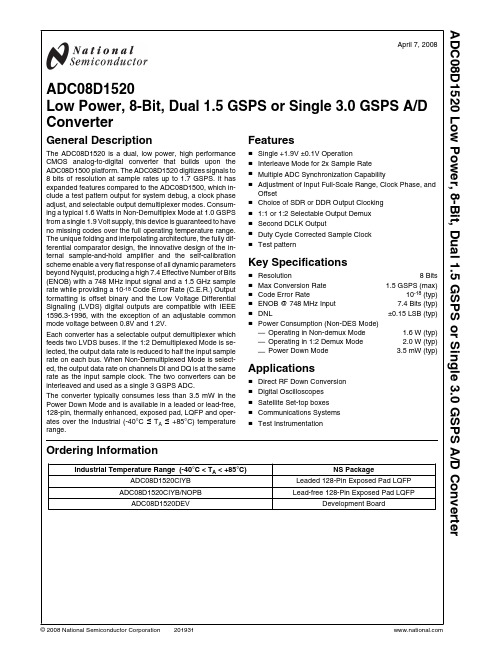

ADC08D1520资料

April 7, 2008 ADC08D1520Low Power, 8-Bit, Dual 1.5 GSPS or Single 3.0 GSPS A/D ConverterGeneral DescriptionThe ADC08D1520 is a dual, low power, high performance CMOS analog-to-digital converter that builds upon the ADC08D1500 platform. The ADC08D1520 digitizes signals to 8 bits of resolution at sample rates up to 1.7 GSPS. It has expanded features compared to the ADC08D1500, which in-clude a test pattern output for system debug, a clock phase adjust, and selectable output demultiplexer modes. Consum-ing a typical 1.6 Watts in Non-Demultiplex Mode at 1.0 GSPS from a single 1.9 Volt supply, this device is guaranteed to have no missing codes over the full operating temperature range. The unique folding and interpolating architecture, the fully dif-ferential comparator design, the innovative design of the in-ternal sample-and-hold amplifier and the self-calibration scheme enable a very flat response of all dynamic parameters beyond Nyquist, producing a high 7.4 Effective Number of Bits (ENOB) with a 748 MHz input signal and a 1.5 GHz sample rate while providing a 10-18 Code Error Rate (C.E.R.) Output formatting is offset binary and the Low Voltage Differential Signaling (LVDS) digital outputs are compatible with IE E E 1596.3-1996, with the exception of an adjustable common mode voltage between 0.8V and 1.2V.Each converter has a selectable output demultiplexer which feeds two LVDS buses. If the 1:2 Demultiplexed Mode is se-lected, the output data rate is reduced to half the input sample rate on each bus. When Non-Demultiplexed Mode is select-ed, the output data rate on channels DI and DQ is at the same rate as the input sample clock. The two converters can be interleaved and used as a single 3 GSPS ADC.The converter typically consumes less than 3.5 mW in the Power Down Mode and is available in a leaded or lead-free, 128-pin, thermally enhanced, exposed pad, LQFP and oper-ates over the Industrial (-40°C ≤ T A≤ +85°C) temperature range.Features■Single +1.9V ±0.1V Operation■Interleave Mode for 2x Sample Rate■Multiple ADC Synchronization Capability■Adjustment of Input Full-Scale Range, Clock Phase, and Offset■Choice of SDR or DDR Output Clocking■1:1 or 1:2 Selectable Output Demux■Second DCLK Output■Duty Cycle Corrected Sample Clock■Test patternKey Specifications■Resolution8 Bits ■Max Conversion Rate 1.5 GSPS (max)■Code Error Rate10-18 (typ)■ENOB @ 748 MHz Input7.4 Bits (typ)■DNL±0.15 LSB (typ)■Power Consumption (Non-DES Mode)—Operating in Non-demux Mode 1.6 W (typ)—Operating in 1:2 Demux Mode 2.0 W (typ)—Power Down Mode 3.5 mW (typ) Applications■Direct RF Down Conversion■Digital Oscilloscopes■Satellite Set-top boxes■Communications Systems■Test InstrumentationOrdering InformationIndustrial Temperature Range (-40°C < TA< +85°C)NS PackageADC08D1520CIYB Leaded 128-Pin Exposed Pad LQFPADC08D1520CIYB/NOPB Lead-free 128-Pin Exposed Pad LQFPADC08D1520DEV Development Board© 2008 National Semiconductor ADC08D1520 Low Power, 8-Bit, Dual 1.5 GSPS or Single 3.0 GSPS A/D ConverterBlock Diagram20193153 2A D C 08D 1520Pin Configuration20193101 Note: The exposed pad on the bottom of the package must be soldered to a ground plane to ensure rated performance. ADC08D1520Pin Descriptions and Equivalent CircuitsPin Functions Pin No.SymbolEquivalent CircuitDescription3OutV / SCLKOutput Voltage Amplitude and Serial Interface Clock. Tie this pin logic high for normal differential DCLK and dataamplitude. Ground this pin for a reduced differential output amplitude and reduced power consumption. See 1.1.6 The LVDS Outputs . When the Extended Control Mode isenabled, this pin functions as the SCLK input which clocks in the serial data. See 1.2 NON-EXTENDED ANDEXTENDED CONTROL MODE for details on the Extended Control Mode. See 1.3 THE SERIAL INTERFACE for description of the serial interface.29PDQPower Down Q-channel. A logic high on the PDQ pin puts only the Q-channel into the Power Down Mode.4OutEdge / DDR /SDATADCLK Edge Select, Double Data Rate Enable and Serial Data Input. This input sets the output edge of DCLK+ at which the output data transitions. See 1.1.5.2 OutEdge and Demultiplex Control Setting . When this pin is floating or connected to 1/2 the supply voltage, DDR clocking isenabled. When the Extended Control Mode is enabled, this pin functions as the SDATA input. See 1.2 NON-EXTENDED AND EXTENDED CONTROL MODE for details on the Extended Control Mode. See 1.3 THE SERIAL INTERFACE for description of the serial interface.15DCLK_RST /DCLK_RST+DCLK Reset. When single-ended DCLK_RST is selected by floating or setting pin 52 logic high, a positive pulse on this pin is used to reset and synchronize the DCLK outputs of multiple converters. See 1.5 MULTIPLE ADCSYNCHRONIZATION for detailed description. Whendifferential DCLK_RST is selected by setting pin 52 logic low,this pin receives the positive polarity of a differential pulse signal used to reset and synchronize the DCLK outputs of multiple converters.26PDPower Down Pins. A logic high on the PD pin puts the entire device into the Power Down Mode.30CALCalibration Cycle Initiate. A minimum t CAL_L input clockcycles logic low followed by a minimum of t CAL_H input clock cycles high on this pin initiates the self calibration sequence.See 2.4.2 Calibration for an overview of calibration and 2.4.2.2 On-Command Calibration for a description of on-command calibration. The calibration cycle may similarly be initiated via the CAL bit in the Calibration register (0h). 4A D C 08D 1520Pin Functions Pin No.SymbolEquivalent CircuitDescription14FSR/ALT_ECE/DCLK_RST-Full Scale Range Select, Alternate Extended Control Enable and DCLK_RST-. This pin has three functions. It canconditionally control the ADC full-scale voltage, enable the Extended Control Mode, or become the negative polarity signal of a differential pair in differential DCLK_RST mode.If pin 52 is floating or at logic high and pin 41 is floating, this pin can be used to set the full-scale-range or can be used as an alternate Extended Control Mode enable pin. When used as the FSR pin, a logic low on this pin sets the full-scale differential input range to a reduced V IN input level . A logic high on this pin sets the full-scale differential input range to a higher V IN input level. See Converter ElectricalCharacteristics. To enable the Extended Control Mode,whereby the serial interface and control registers are employed, allow this pin to float or connect it to a voltage equal to V A /2. See 1.2 NON-EXTENDED AND EXTENDED CONTROL MODE for information on the Extended Control Mode. Note that pin 41 overrides the Extended Control Mode enable of this pin. When pin 52 is held at logic low, this pin acts as the DCLK_RST- pin. When in differential DCLK_RST mode, there is no pin-controlled FSR and the full-scale-range is defaulted to the higher V IN input level.127CalDly / DES / SCSCalibration Delay, Dual Edge Sampling and Serial Interface Chip Select. In non-extended control mode, this pin functions as the Calibration Delay select. A logic high or low the number of input clock cycles after power up beforecalibration begins (See 1.1.1 Calibration ). When this pin is floating or connected to a voltage equal to V A /2, DES (Dual Edge Sampling) Mode is selected where the I-channel is sampled at twice the input clock rate and the Q-channel is ignored. See 1.1.5.1 Dual-Edge Sampling . In extended control mode, this pin acts as the enable pin for the serial interface input and the CalDly value becomes "0" (short delay with no provision for a long power-up calibration delay).1819CLK+CLK-Differential clock input pins for the ADC. The differential clock signal must be a.c. coupled to these pins. The input signal is sampled on the falling edge of CLK+. See 1.1.2 Acquiring the Input for a description of acquiring the input and 2.3 THE CLOCK INPUTS for an overview of the clock inputs.10112223V IN I-V IN I+V IN Q+V IN Q−Analog signal inputs to the ADC. The differential full-scale input range of this input is programmable using the FSR pin 14 in Non-Extended Control Mode and the Input Full-Scale Voltage Adjust register in the Extended Control Mode. Refer to the V IN specification in the Converter ElectricalCharacteristics for the full-scale input range in the Non-Extended Control Mode. Refer to 1.4 REGISTERDESCRIPTION for the full-scale input range in the Extended Control Mode.ADC08D1520Pin Functions Pin No.SymbolEquivalent CircuitDescription7V CMOCommon Mode Voltage. This pin is the common mode output in d.c. coupling mode and also serves as the a.c.coupling mode select pin. When d.c. coupling is used at the analog inputs, the voltage output at this pin is required to be the common mode input voltage at V IN + and V IN −. When a.c.coupling is used, this pin should be grounded. This pin is capable of sourcing or sinking 100 μA. See 2.2 THE ANALOG INPUT .31V BGBandgap output voltage. This pin is capable of sourcing or sinking 100 μA and can drive a load up to 80 pF.126CalRunCalibration Running indication. This pin is at a logic high when calibration is running.32R EXTExternal bias resistor connection. Nominal value is 3.3 k Ω(±0.1%) to ground. See 1.1.1 Calibration .3435Tdiode_P Tdiode_NTemperature Diode Positive (Anode) and Negative (Cathode). This pin is used for die temperature measurements. See 2.6.2 Thermal Management .41ECEExtended Control Enable. This pin always enables ordisables Extended Control Mode. When this pin is set logic high, the Extended Control Mode is inactive and all control of the device must be through control pins only . When it is set logic low, the Extended Control Mode is active. This pin overrides the Extended Control Enable signal set using pin 14.52DRST_SELDCLK_RST select. This pin selects whether the DCLK is reset using a single-ended or differential signal. When this pin is floating or logic high, the DCLK_RST operation is single-ended and pin 14 functions as FSR/ALT_ECE. When this pin is logic low, the DCLK_RST operation becomes differential with functionality on pin 15 (DCLK_RST+) and pin 14 (DCLK_RST-). When in differential DCLK_RST mode,there is no pin-controlled FSR and the full-scale-range is defaulted to the higher V IN input level. When pin 41 is set logic low, the Extended Control Mode is active and the Full-Scale Voltage Adjust registers can be programmed. 6A D C 08D 1520Pin FunctionsPin No.Symbol Equivalent Circuit Description83 / 7884 / 7785 / 7686 / 7589 / 7290 / 7191 / 7092 / 6993 / 6894 / 6795 / 6696 / 65 100 / 61 101 / 60 102 / 59 103 / 58DI7− / DQ7−DI7+ / DQ7+DI6− / DQ6−DI6+ / DQ6+DI5− / DQ5−DI5+ / DQ5+DI4− / DQ4−DI4+ / DQ4+DI3− / DQ3−DI3+ / DQ3+DI2− / DQ2−DI2+ / DQ2+DI1− / DQ1−DI1+ / DQ1+DI0− / DQ0−DI0+ / DQ0+I- and Q-channel LVDS Data Outputs that are not delayed inthe output demultiplexer. Compared with the DId and DQdoutputs, these outputs represent the later time samples.These outputs should always be terminated with a 100Ωdifferential resistor.In Non-demultiplexed Mode, only these outputs are active.104 / 57 105 / 56 106 / 55 107 / 54 111 / 50 112 / 49 113 / 48 114 / 47 115 / 46 116 / 45 117 / 44 118 / 43 122 / 39 123 / 38 124 / 37 125 / 36DId7− / DQd7−DId7+ / DQd7+DId6− / DQd6−DId6+ / DQd6+DId5− / DQd5−DId5+ / DQd5+DId4− / DQd4−DId4+ / DQd4+DId3− / DQd3−DId3+ / DQd3+DId2− / DQd2−DId2+ / DQd2+DId1− / DQd1−DId1+ / DQd1+DId0− / DQd0−DId0+ / DQd0+I- and Q-channel LVDS Data Outputs that are delayed byone CLK cycle in the output demultiplexer. Compared withthe DI and DQ outputs, these outputs represent the earliertime sample. These outputs should always be terminatedwith a 100Ω differential resistor.In Non-demultiplexed Mode, these outputs are disabled andare high impedance. When disabled, these outputs must beleft floating.79 80OR+/DCLK2+OR-/DCLK2-Out Of Range, second Data Clock output. When functioningas OR+/-, a differential high at these pins indicates that thedifferential input is out of range (outside the range ±VIN/2 asprogrammed by the FSR pin in Non-extended Control Modeor the Input Full-Scale Voltage Adjust register setting in theExtended Control Mode). This single out of range indicationis for both the I- and Q-channels, unless PDQ is asserted, inwhich case it only applies to the I-channel input. Whenfunctioning as DCLK2+/-, DCLK2 is the exact replica ofDCLK and outputs the same signal at the same rate. Thefunctionality of these pins is selectable in Extended ControlMode only; default is OR+/-.ADC08D1520Pin Functions Pin No.SymbolEquivalent CircuitDescription8182DCLK-DCLK+Data Clock. Differential Clock outputs used to latch the output data. Delayed and non-delayed data outputs are supplied synchronously to this signal. In 1:2 Demux Mode,this signal is at 1/2 the input clock rate in SDR mode and at 1/4 the input clock rate in the DDR mode. In the Non-demux Mode, DCLK can only be in DDR mode and is at 1/2 the input clock rate. By default, the DCLK outputs are not active during the termination resistor trim section of the calibration cycle.If a system requires DCLK to run continuously during a calibration cycle, the termination resistor trim portion of the cycle can be disabled by setting the Resistor Trim Disable (RTD) bit to logic high in the Extended ConfigurationRegister. This disables all subsequent termination resistor trims after the initial trim which occurs during power-on calibration. This output is not recommended as a system clock unless the resistor trim is disabled.2, 5, 8, 13,16, 17, 20,25, 28, 33,128V AAnalog power supply pins. Bypass these pins to ground.40, 51, 62,73, 88, 99,110, 121V DROutput Driver power supply pins. Bypass these pins to DR GND.1, 6, 9, 12,21, 24, 27GNDGround return for V A .42, 53, 64,74, 87, 97,108, 119DR GNDGround return for V DR .63, 98, 109,120NCNo Connection. Make no connection to these pins. 8A D C 08D 1520Absolute Maximum Ratings(Notes 1, 2)If Military/Aerospace specified devices are required,please contact the National Semiconductor Sales Office/Distributors for availability and specifications.Supply Voltage (V A , V DR ) 2.2VSupply Difference V DR - V A0V to 100 mVVoltage on Any Input Pin −0.15V to (V A +0.15V)Ground Difference |GND - DR GND|0V to 100 mVInput Current at Any Pin (Note 3)±25 mA Package Input Current (Note 3)±50 mAPower Dissipation at T A ≤ 85°C 2.35 WESD Susceptibility (Note 4) Human Body Model Machine ModelCharged Device Model 2500V 250V 1000VStorage Temperature−65°C to +150°COperating Ratings(Notes 1, 2)Ambient Temperature Range−40°C ≤ T A ≤ +85°CSupply Voltage (V A )+1.8V to +2.0V Driver Supply Voltage (V DR )+1.8V to V A Analog Input Common Mode Voltage V CMO ±50 mV V IN +, V IN - Voltage Range (Maintaining Common Mode)200mV to V AGround Difference (|GND - DR GND|)0V CLK Pins Voltage Range 0V to V ADifferential CLK Amplitude0.4V P-P to 2.0V P-PPackage Thermal ResistancePackage θJA θJC Top of Package θJC Thermal Pad 128-Lead,Exposed Pad LQFP26°C / W10°C / W2.8°C / WSoldering process must comply with National Semiconductor’s Reflow Temperature Profile specifications.Refer to /packaging. (Note 5)Converter Electrical CharacteristicsThe following specifications apply after calibration for V A = V DR = +1.9V; OutV = 1.9V; V IN FSR (a.c. coupled) = differential 870mV P-P ; C L = 10 pF; Differential, a.c. coupled Sine Wave Input Clock, f CLK = 1.5 GHz at 0.5 V P-P with 50% duty cycle; V BG = Floating;Non-extended Control Mode; SDR Mode; R EXT = 3300 Ω ±0.1%; Analog Signal Source Impedance = 100 Ω Differential; 1:2Demultiplex Mode; Duty Cycle Stabilizer on. Boldface limits apply for T A = T MIN to T MAX . All other limits T A = 25°C, unless otherwise noted. (Notes 6, 7, 16)SymbolParameterConditionsTypical (Note 8)Limits (Note 8)Units (Limits)STATIC CONVERTER CHARACTERISTICS INL Integral Non-Linearity (Best fit)DC Coupled, 1 MHz Sine Wave Over-ranged±0.3±0.9LSB (max)DNL Differential Non-Linearity DC Coupled, 1 MHz Sine Wave Over-ranged ±0.15±0.6LSB (max)Resolution with No Missing Codes 8Bits V OFF Offset Error−0.75 LSB V OFF _ADJ Input Offset Adjustment Range Extended Control Mode±45 mV PFSE Positive Full-Scale Error (Note 9) ±25mV (max)NFSE Negative Full-Scale Error (Note 9)±25mV (max)FS_ADJ Full-Scale Adjustment Range Extended Control Mode ±20±15%FS 1:2 DEMUX NON-DES MODE, DYNAMIC CONVERTER CHARACTERISTICS; F CLK = 1.5 GHZFPBW Full Power Bandwidth Non-DES Mode 2.0 GHz C.E.R.Code Error Rate10−18 Error/SampleGain Flatnessd.c. to 748 MHz ±0.5 dBFS d.c. to 1.5 GHz±1.0 dBFS ENOB Effective Number of Bitsf IN = 373 MHz, V IN = FSR − 0.5 dB 7.4 6.8Bits (min)f IN = 748 MHz, V IN = FSR − 0.5 dB7.4 Bits SINAD Signal-to-Noise Plus Distortion Ratio f IN = 373 MHz, V IN = FSR − 0.5 dB 46.542.5dB (min)f IN = 748 MHz, V IN = FSR − 0.5 dB 46.4 dB SNRSignal-to-Noise Ratiof IN = 373 MHz, V IN = FSR − 0.5 dB 46.844.0dB (min)f IN = 748 MHz, V IN = FSR − 0.5 dB47dBADC08D1520Symbol ParameterConditionsTypical (Note 8)Limits (Note 8)Units (Limits)THD Total Harmonic Distortion f IN = 373 MHz, V IN = FSR − 0.5 dB −58-47.5dB (max)f IN = 748 MHz, V IN = FSR − 0.5 dB −55dB 2nd Harm Second Harmonic Distortion f IN = 373 MHz, V IN = FSR − 0.5 dB −65dB f IN = 748 MHz, V IN = FSR − 0.5 dB −59dB 3rd Harm Third Harmonic Distortion f IN = 373 MHz, V IN = FSR − 0.5 dB −58dB f IN = 748 MHz, V IN = FSR − 0.5 dB −58dB SFDR Spurious-Free Dynamic Range f IN = 373 MHz, V IN = FSR − 0.5 dB 5847.5dB (min)f IN = 748 MHz, V IN = FSR − 0.5 dB 55 dB IMD Intermodulation Distortion f IN1 = 365 MHz, V IN = FSR − 7 dB −50 dB f IN2 = 375 MHz, V IN = FSR − 7 dBOut of Range Output Code(V IN +) − (V IN −) > + Full Scale 255 (V IN +) − (V IN −) < − Full Scale 0 NON-DEMUX NON-DES MODE, DYNAMIC CONVERTER CHARACTERISTICS; F CLK = 1 GHZ ENOB Effective Number of Bitsf IN = 248 MHz, V IN = FSR − 0.5 dB 7.3 Bits f IN = 498 MHz, V IN = FSR − 0.5 dB7.3Bits SINAD Signal to Noise Plus Distortion Ratio f IN = 248 MHz, V IN = FSR − 0.5 dB 45.7 dB f IN = 498 MHz, V IN = FSR − 0.5 dB 45.7dB SNR Signal to Noise Ratio f IN = 248 MHz, V IN = FSR − 0.5 dB 46 dB f IN = 498 MHz, V IN = FSR − 0.5 dB 46dB THD Total Harmonic Distortion f IN = 248 MHz, V IN = FSR − 0.5 dB -57dB f IN = 498 MHz, V IN = FSR − 0.5 dB -57dB 2nd Harm Second Harmonic Distortion f IN = 248 MHz, V IN = FSR − 0.5 dB -63dB f IN = 498 MHz, V IN = FSR − 0.5 dB -63dB 3rd Harm Third Harmonic Distortion f IN = 248 MHz, V IN = FSR − 0.5 dB -64dB f IN = 498 MHz, V IN = FSR − 0.5 dB -64dB SFDRSpurious Free Dynamic Rangef IN = 248 MHz, V IN = FSR − 0.5 dB 57 dB f IN = 498 MHz, V IN = FSR − 0.5 dB 57dB 1:4 DEMUX DES MODE, DYNAMIC CONVERTER CHARACTERISTICS; F CLK = 1.5 GHZ FPBW Full Power Bandwidth DES Mode1.3 GHz ENOB Effective Number of Bitsf IN = 748 MHz, V IN = FSR − 0.5 dB7.0 Bits SINAD Signal to Noise Plus DistortionRatiof IN = 748 MHz, V IN = FSR − 0.5 dB44 dB SNR Signal to Noise Ratio f IN = 748 MHz, V IN = FSR − 0.5 dB 46.3 dB THD Total Harmonic Distortion f IN = 748 MHz, V IN = FSR − 0.5 dB −47dB 2nd Harm Second Harmonic Distortion f IN = 748 MHz, V IN = FSR − 0.5 dB −55dB 3rd Harm Third Harmonic Distortionf IN = 748 MHz, V IN = FSR − 0.5 dB−64dB SFDRSpurious Free Dynamic Range f IN = 748 MHz, V IN = FSR − 0.5 dB47dB ANALOG INPUT AND REFERENCE CHARACTERISTICSV INFull Scale Analog Differential Input RangeFSR pin 14 Low 650590mV P-P (min)730mV P-P (max)FSR pin 14 High 870800mV P-P (min)940mV P-P (max)V CMICommon Mode Input VoltageV CMOV CMO − 0.05V (min)V CMO + 0.05V (max) 10A D C 08D 1520Symbol Parameter Conditions Typical(Note 8)Limits(Note 8)Units(Limits)C IN Analog Input Capacitance,Normal operation(Notes 10, 11)Differential0.02pFEach input pin to ground 1.6pF Analog Input Capacitance,DES Mode (Notes 10, 11)Differential0.08pFEach input pin to ground 2.2pFR IN Differential Input Resistance10094Ω (min)106Ω (max)ANALOG OUTPUT CHARACTERISTICSV CMO Common Mode Output Voltage I CMO = ±100 µA 1.260.95V (min)1.45V (max)TC VCMO Common Mode Output VoltageTemperature CoefficientTA= −40°C to +85°C118ppm/°CVCMO_LVL VCMOinput threshold to set D.C.Coupling modeVA= 1.8V0.60VVA= 2.0V0.66VC LOAD VCMOMaximum VCMOLoadCapacitance80pFV BG Bandgap Reference OutputVoltageIBG= ±100 µA 1.261.20V (min)1.33V (max)TC VBG Bandgap Reference VoltageTemperature CoefficientTA= −40°C to +85°C,IBG= ±100 µA28ppm/°CC LOAD VBGMaximum Bandgap Referenceload Capacitance80pFCHANNEL-TO-CHANNEL CHARACTERISTICSOffset Match1LSBPositive Full-Scale Match Zero offset selected in Control Register1LSBNegative Full-Scale Match Zero offset selected in Control Register1LSBPhase Matching (I, Q)f IN = 1.5 GHz< 1DegreeX-TALK Crosstalk from I-channel(Aggressor) to Q-channel(Victim)Aggressor = 867 MHz F.S.Victim = 100 MHz F.S.−65dBX-TALK Crosstalk from Q-channel(Aggressor) to I-channel(Victim)Aggressor = 867 MHz F.S.Victim = 100 MHz F.S.−65dBLVDS CLK INPUT CHARACTERISTICS (Typical specs also apply to DCLK_RST)V ID Differential Clock Input LevelSine Wave Clock0.60.4V P-P (min)2.0V P-P (max)Square Wave Clock0.60.4V P-P (min)2.0V P-P (max)VOSIInput Offset Voltage 1.2VC IN Input Capacitance(Notes 10, 11)Differential0.02pFEach input to ground 1.5pFDIGITAL CONTROL PIN CHARACTERISTICSV IH Logic High Input VoltageOutV, DCLK_RST, PD, PDQ, CAL, ECE,DRST_SEL0.69 x VAV (min)OutEdge, FSR, CalDly0.79 x V A V (min)V IL Logic Low Input VoltageOutV, DCLK_RST, PD, PDQ, CAL0.28 x V A V (max)OutEdge, FSR, CalDly, ECE, DRST_SEL0.21 x V A V (max)C IN Input Capacitance(Notes 11, 13)Each input to ground 1.2pFADC08D1520SymbolParameterConditionsTypical (Note 8)Limits (Note 8)Units (Limits)DIGITAL OUTPUT CHARACTERISTICSV ODLVDS Differential Output VoltageMeasured differentially, OutV = V A ,V BG = Floating (Note 15)740480mV P-P (min)950mV P-P (max)Measured differentially, OutV = GND, V BG = Floating (Note 15)560320mV P-P (min)720mV P-P (max)ΔV O DIFF Change in LVDS Output SwingBetween Logic Levels±1 mV V OS Output Offset Voltage See Figure 1V BG = Floating 800 mV V BG = V A (Note 15)1175 mV ΔV OS Output Offset Voltage ChangeBetween Logic Levels±1 mV I OS Output Short Circuit Current Output+ and Output−connected to 0.8V ±4 mA Z O Differential Output Impedance100 Ohms V OH CalRun H level output I OH = −400 µA (Note 12) 1.65 1.5V V OLCalRun L level outputI OH = 400 µA (Note 12)0.150.3V POWER SUPPLY CHARACTERISTICS (NON-DES MODE)I AAnalog Supply Current1:2 Demux Mode; f CLK = 1.5 GHz PD = PDQ = LowPD = Low, PDQ = High PD = PDQ = High 8185611.9 930640 mA (max)mA (max)mA Non-demux Mode; f CLK = 1.0 GHz PD = PDQ = LowPD = Low, PDQ = High PD = PDQ = High 7124641.5 803530 mA (max)mA (max)mA I DROutput Driver Supply Current1:2 Demux Mode; f CLK = 1.5 GHz PD = PDQ = LowPD = Low, PDQ = High PD = PDQ = High 2251230.074 305166 mA (max)mA (max)mA Non-demux Mode; f CLK = 1.0 GHz PD = PDQ = LowPD = Low, PDQ = High PD = PDQ = High 13683.50.047 212120 mA (max)mA (max)mA P DPower Consumption1:2 Demux Mode; f CLK = 1.5 GHz PD = PDQ = LowPD = Low, PDQ = High PD = PDQ = High 2.01.33.8 2.351.53 W (max)W (max)mW Non-demux Mode; f CLK = 1.0 GHz PD = PDQ = LowPD = Low, PDQ = High PD = PDQ = High 1.61.042.76 1.921.235W (max)W (max)mW PSRR1D.C. Power Supply Rejection RatioChange in Full Scale Error with change in V A from 1.8V to 2.0V-30dBA D C 08D 1520Symbol Parameter Conditions Typical(Note 8)Limits(Note 8)Units(Limits)A.C. ELECTRICAL CHARACTERISTICSfCLK (max)Maximum Input ClockFrequencyDemux Mode (DES or Non-DES Mode) 1.7 1.5GHz (max)Non-Demux Mode (DES or Non-DESMode)1.0GHz (max)fCLK (min)Minimum Input ClockFrequency1:2 Demux Non-DES Mode200MHz1:4 Demux DES Mode500MHz Input Clock Duty CyclefCLK(min)≤ fCLK≤ 1.5 GHz(Note 12)5020% (min)80% (max)tCLInput Clock Low Time(Note 11)333133ps (min)tCHInput Clock High Time(Note 11)333133ps (min)DCLK Duty Cycle(Note 11)5045% (min) 55% (max)tSRSetup Time DCLK_RST±(Note 12)90pstHRHold Time DCLK_RST±(Note 12)30pst PWR Pulse Width DCLK_RST±(Note 11)4Input ClockCycles (min)t LHT Differential Low-to-HighTransition Time10% to 90%, CL= 2.5 pF150pst HLT Differential High-to-LowTransition Time10% to 90%, CL= 2.5 pF150pst OSK DCLK-to-Data Output Skew50% of DCLK transition to 50% of Datatransition, SDR Modeand DDR Mode, 0° DCLK (Note 11)±50ps (max)tSUData-to-DCLK Set-Up Time DDR Mode, 90° DCLK (Note 11)400pstHDCLK-to-Data Hold Time DDR Mode, 90° DCLK (Note 11)560pstADSampling (Aperture) Delay Input CLK+ Fall to Acquisition of Data 1.6nstAJAperture Jitter0.4ps (rms)t OD Input Clock-to Data OutputDelay (in addition to PipelineDelay)50% of Input Clock transition to 50% of Datatransition4.0nsPipeline Delay (Latency) in 1:2Demux Mode(Notes 11, 14)DI Outputs13Input ClockCyclesDId Outputs14DQ OutputsNon-DES Mode13DES Mode13.5DQd OutputsNon-DES Mode14DES Mode14.5Pipeline Delay (Latency) inNon-Demux Mode(Notes 11, 14)DI Outputs13Input ClockCyclesDQ OutputsNon-DES Mode13DES Mode13.5Over Range Recovery TimeDifferential VINstep from ±1.2V to 0V to getaccurate conversion1Input ClockCyclet WU PD low to Rated AccuracyConversion (Wake-Up Time)Non-DES Mode (Note 11)500nsDES Mode (Note 11)1µsfSCLKSerial Clock Frequency(Note 11)15MHzt SSU Serial Data to Serial ClockRising Setup Time(Note 11) 2.5ns (min)t SH Serial Data to Serial ClockRising Hold Time(Note 11)1ns (min)t SCS CS to Serial Clock Rising SetupTime2.5nsADC08D1520Symbol ParameterConditionsTypical (Note 8)Limits (Note 8)Units (Limits)t HCS CS to Serial Clock Falling HoldTime1.5 ns Serial Clock Low Time 30ns (min) Serial Clock High Time 30ns (min)t CAL Calibration Cycle Time1.4 x 106Clock Cycles t CAL_L CAL Pin Low Time See Figure 10 (Note 11) 1280Clock Cycles(min)t CAL_HCAL Pin High TimeSee Figure 10 (Note 11)1280Clock Cycles(min)t CalDlyCalibration delay determined by CalDly (pin 127)CalDly = LowSee 1.1.1 Calibration , Figure 10,(Note 11)226Clock Cycles(max)CalDly = HighSee 1.1.1 Calibration , Figure 10,(Note 11)232Clock Cycles(max)Note 1:Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. There is no guarantee of operation at the Absolute Maximum Ratings. Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.Note 2:All voltages are measured with respect to GND = DR GND = 0V, unless otherwise specified.Note 3:When the input voltage at any pin exceeds the power supply limits (that is, less than GND or greater than V A ), the current at that pin should be limited to 25 mA. The 50 mA maximum package input current rating limits the number of pins that can safely exceed the power supplies with an input current of 25 mA to two. This limit is not placed upon the power, ground and digital output pins.Note 4:Human body model is 100 pF capacitor discharged through a 1.5 k Ω resistor. Machine model is 220 pF discharged through ZERO Ohms. Charged device model simulates a pin slowly acquiring charge (such as from a device sliding down the feeder in an automated assembler) then rapidly being discharged.Note 5:Reflow temperature profiles are different for lead-free and non-lead-free packages.Note 6:The analog inputs are protected as shown below. Input voltage magnitudes beyond the Absolute Maximum Ratings may damage this device.20193104Note 7:To guarantee accuracy, it is required that V A and V DR be well bypassed. Each supply pin must be decoupled with separate bypass capacitors. Additionally,achieving rated performance requires that the backside exposed pad be well grounded.Note 8:Typical figures are at T A = 25°C, and represent most likely parametric norms. Test limits are guaranteed to National's AOQL (Average Outgoing Quality Level).Note 9:Calculation of Full-Scale Error for this device assumes that the actual reference voltage is exactly its nominal value. Full-Scale Error for this device,therefore, is a combination of Full-Scale Error and Reference Voltage Error. See Figure 2. For relationship between Gain Error and Full-Scale Error, see Specification Definitions for Gain Error.Note 10:The analog and clock input capacitances are die capacitances only. Additional package capacitances of 0.65 pF differential and 0.95 pF each pin to ground are isolated from the die capacitances by lead and bond wire inductances.Note 11:This parameter is guaranteed by design and is not tested in production.Note 12:This parameter is guaranteed by design and/or characterization and is not tested in production.Note 13:The digital control pin capacitances are die capacitances only. Additional package capacitance of 1.6 pF each pin to ground are isolated from the die capacitances by lead and bond wire inductances.Note 14:The ADC08D1520 has two LVDS output buses, each of which clocks data out at one half the sample rate. The second bus (D0 through D7) has a pipeline latency that is one clock cycle less than the latency of the first bus (Dd0 through Dd7).Note 15:Tying V BG to the supply rail will increase the output offset voltage (V OS ) by 400mv (typical), as shown in the V OS specification above. Tying V BG to the supply rail will also affect the differential LVDS output voltage (V OD ), causing it to increase by 40mV (typical).Note 16:The maximum clock frequency for Non-Demux Mode is 1 GHz.A D C 08D 1520。

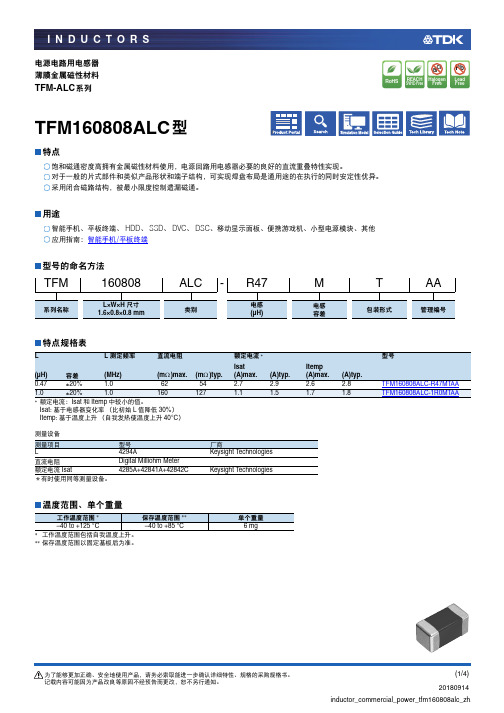

TFM160808ALC电源电路用电感器说明书

电源电路用电感器薄膜金属磁性材料TFM-ALC 系列TFM160808ALC 型特点用途HDD、SSD 、DVC 、DSC 、移动显示面板、便携游戏机、小型电源模块、其他应用指南:智能手机/平板终端型号的命名方法特点规格表* 额定电流:Isat 和Itemp 中较小的值。

Isat: 基于电感器变化率(比初始L 值降低30%)Itemp:基于温度上升(自我发热使温度上升40°C )测量设备*有时使用同等测量设备。

温度范围、单个重量*工作温度范围包括自我温度上升。

**保存温度范围以固定基板后为准。

TFM160808ALC-R47MTAA系列名称L×W×H 尺寸类别电感电感容差包装形式管理编号1.6×0.8×0.8 mm(µH)LL 测定频率直流电阻额定电流*型号Isat Itemp (µH)容差(MHz)(m Ω)max.(m Ω)typ.(A)max.(A)typ.(A)max.(A)typ.0.47±20% 1.0 6254 2.7 2.9 2.6 2.8TFM160808ALC-R47MT AA 1.0±20% 1.01601271.11.51.71.8TFM160808ALC-1R0MT AA测量项目型号厂商L4294AKeysight T echnologies 直流电阻Digital Milliohm Meter 额定电流 Isat4285A+42841A+42842CKeysight T echnologies工作温度范围*保存温度范围**单个重量–40 to +125 °C –40 to +85 °C6 mgL频率特性测量设备型号厂商4294A Keysight T echnologies*有时使用同等测量设备。

电感直流重叠特性测量设备型号厂商4285A+42841A+42842C Keysight T echnologies*有时使用同等测量设备。

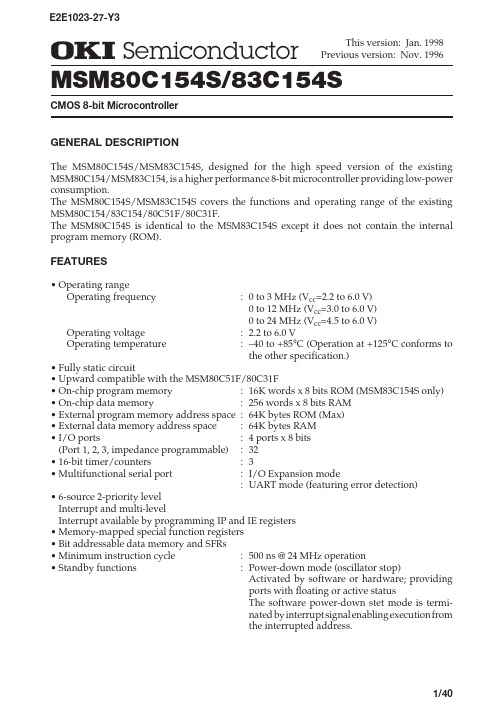

MSM80C154资料

GENERAL DESCRIPTION

The MSM80C154S/MSM83C154S, designed for the high speed version of the existing MSM80C154/MSM83C154, is a higher performance 8-bit microcontroller providing low-power consumption. The MSM80C154S/MSM83C154S covers the functions and operating range of the existing MSM80C154/83C154/80C51F/80C31F. The MSM80C154S is identical to the MSM83C154S except it does not contain the internal program memory (ROM).

NC 6 P3.1/TXD 7 P3.2/INT0 8 P3.3/INT1 9

P3.4/T0 10 P3.5/T1/HPDI 11

33 P0.4 32 P0.5 31 P0.6 30 P0.7 29 EA 28 NC 27 ALE 26 PSEN 25 P2.7 24 P2.6 23 P2.5

P3.6/WR 12 P3.7/RD 13

44-pin plastic QFP (QFP44-P-910-0.80-2K) :

44-pin QFJ (QFJ44-P-S650-1.27)

:

44-pin TQFP (TQFP44-P-1010-0.80-K) :

(Product name: MSM80C154SRS/ MSM83C154S-xxxRS)

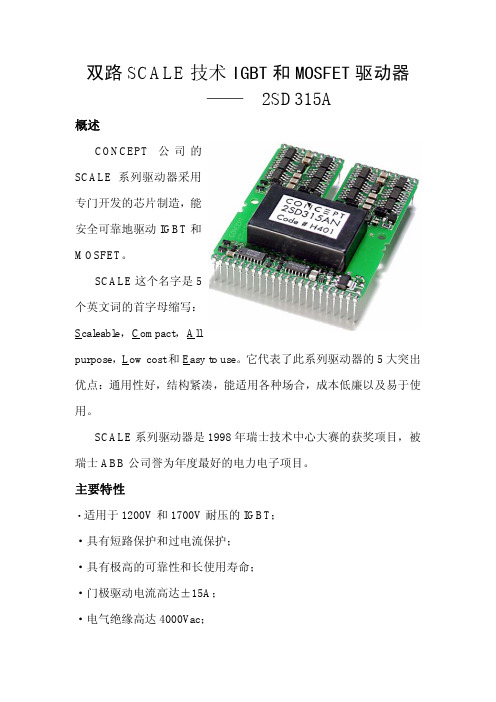

2SD315AI 中文版

最小值

最大值

单位

VDC 电源输入

0

16

Vdc

VDD 电源输入

0

16

Vdc

逻辑电平输入

到 GND 之间

0

VDD

Vdc

门极驱动峰值电流

Gx 到 Ex

-18

+18

A

DC/DC 变换器功率

所有桥臂总和

6

W

输入输出隔离电压

连续(注 8)

1200

Vdc

耐压测试

输入脚和输出脚间

4000

Vac 有效值

(50KHz/1min)

空载

30

mA

最大电源电流 IDC (注 2)

470

mA

DC/DC 变换器功率 (注 3)

6

W

效率

内置 DC/DC 变换器

85

%

VDD 电源输入

到 GND

15

Vdc

电源电流 IDD

空载

12

mA

电源电流 IDD

开关频率 25KHz

15

mA

电源监视 起动工作电压 电压滞环

测试条件 (注 4) (注 4)

最小值

驱动器设计的输出功率是 6W,每路输出 3W。一般足以驱动 1200A/1200V 的 IGBT(开关频率 6.25KHZ)。当驱动器输出 6W 时, 输入驱动器的功率将为 7W。驱动器本身损耗为 1W。因为驱动器可 能应用于不同的场合,所以驱动器的温升及输出最大功率没有给出推 荐值。在用于很高环境温度时,建议对整个系统的热设计进行校对。

双路 SCALE 技术 IGBT 和 MOSFET 驱动器 —— 2SD315A

概述

SMDA15CM中文资料

SMDA05CMthruSMDA24CMST ANDARD CAP ACIT ANCE TVS ARRA YOnly One Name Means ProTek’Tion™APPLICA TIONS✔ RS-232, RS-422 & RS-423 Data Lines✔ Microprocessor Based Equipment ✔ Control & Monitoring Equipment ✔ Modems✔ Portable Electronics ✔ Medical ElectronicsIEC COMP A TIBILITY (EN61000-4)✔ 61000-4-2 (ESD): Air - 15kV , Contact - 8kV ✔ 61000-4-4 (EFT): 40A - 5/50ns✔ 61000-4-5 (Surge): 12A, 8/20µs - Level 1(Line-Gnd) & Level 2(Line-Line)FEA TURES✔ 500 Watts Peak Pulse Power per Line (tp=8/20µs)✔ Bidirectional Configurations ✔ Monolithic Design✔ Available in Voltage Types Ranging From: 5V to 24V ✔ Protects 4 - 7 Lines✔ ESD Protection > 40 kilovolts✔ RoHS Compliant in Lead-Free VersionsMECHANICAL CHARACTERISTICS✔ Molded JEDEC SO-8 Package✔ Weight 70 milligrams (Approximate)✔ Available in Tin-Lead or Lead-Free Pure-Tin Plating(Annealed)✔ Solder Reflow Temperature:Tin-Lead - Sn/Pb, 85/15: 240-245°C Pure-Tin - Sn, 100: 260-270°C✔ Flammability rating UL 94V-0✔ 12mm T ape and Reel Per EIA Standard 481✔ Marking: Logo, Marking Code, Date Code & Pin One Defined By Dot on Top of Package05070PIN CONFIGURATIONSO-8SMDA05CMthruSMDA24CMDEVICE CHARACTERISTICSMAXIMUM RA TINGS @ 25°C Unless Otherwise SpecifiedOperating T emperature SYMBOL VALUE -55°C to 150°C°C°C -55°C to 150°C UNITS T J T STGPARAMETERStorage T emperaturePeak Pulse Power (t p = 8/20µs) - See Figure 1P PP 500Watts ELECTRICAL CHARACTERISTICS PER LINE @ 25°C Unless Otherwise SpecifiedPART NUMBERDEVICE MARKING CODEMINIMUM BREAKDOWN VOLTAGE@ 1mA V (BR)VOLTS MAXIMUM CLAMPING VOLTAGE (See Fig. 2)@ I P = 1AV C VOLTS MAXIMUM CLAMPING VOLTAGE (See Fig. 2)@8/20µs V C @ I PP MAXIMUM CAPACITANCE PER LINE@0V , 1 MHzC pFSMDA05CM SMDA08CM SMDA12CM SMDA15CM SMDA24CMREB REC RED REF REH6.08.513.416.726.79.813.419.024.043.019.0V @ 30A 23.7V @ 24A 29.2V @ 20A 31.1V @ 18A 45.0V @ 13A35030015010063MAXIMUM LEAKAGE CURRENT@V WMI D µA 10010111RATED STAND-OFF VOLTAGEV WM VOLTS5.08.012.015.024.0SMDA05CMthruSMDA24CMGRAPHST L - Lead T emperature - °C20406080100% O f R a t e d P o w e rFIGU RE 30 5 10 15 20 25 30t - Time - µs20406080100120I P P - P e a k P u l s e C u r r e n t -% o f I P PFIGU RE 20.1 1 10 100 1,000 10,000t d - Pulse Duration - µs101001,00010,000P P P - P e a k P u l s e P o w e r - W a t t sFIGU RE 1PEAK PULSE POWER VS PULSE TIMESMDA05CMthruSMDA24CMCOPYRIGHT © ProTek Devices 2005SPECIFICATIONS: ProTek reserves the right to change the electrical and or mechanical characteristics described herein without notice (except JEDEC).DESIGN CHANGES: ProTek reserves the right to discontinue product lines without notice, and that the final judgement concerning selection and specifications is the buyer’s and that in furnishing engineering and technical assistance, ProTek assumes no responsibility with respect to the selection or specifications of such products.P ACKAGE OUTLINE & DIMENSIONSProTek Devices2929 South Fair Lane, Tempe, AZ 85282Tel: 602-431-8101 Fax: 602-431-2288E-Mail: sales@ Web Site: 。

ICL8038CCPD中文资料

V

V+, V- Dual Supplies

±5 - ±15 ±5 - ±15 ±5 - ±15

V

Supply Current

ISUPPLY VSUPPLY = ±10V (Note 2)

12 20 - 12 20 - 12 20

mA

FREQUENCY CHARACTERISTICS (All Waveforms)

Pinout

ICL8038 (PDIP, CERDIP)

TOP VIEW

SINE WAVE ADJUST

1

SINE WAVE OUT

2

TRIANGLE OUT

3

DUTY CYCLE 4 FREQUENCY

ADJUST 5

V+ 6

FM BIAS 7

14 NC

13 NC

12 SINE WAVE ADJUST

NOTE: 1. θJA is measured with the component mounted on an evaluation PC board in free air.

Electrical Specifications

PARAMETER

VSUPPLY = ±10V or +20V, TA = 25oC, RL = 10kΩ, Test Circuit Unless Otherwise Specified

元器件交易网

c1No-8nO8ta8Rc-EItNCOoTOuBErMSRTOMSeLIEcLEhNoTnTDMrEiEcwaPDwlRRSwOuE.DDipPnUpaLteotCAarrTCstSiEClh.MceeonEemtNet /rTtsact

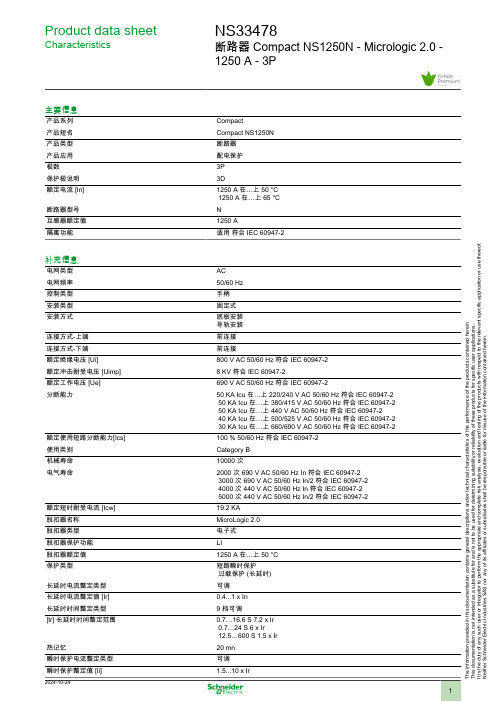

施耐德 NS33478 断路器 Compact NS1250N 数据表

Product data sheetCharacteristicsNS33478断路器 Compact NS1250N - Micrologic 2.0 -1250 A - 3P主要信息产品系列Compact产品短名Compact NS1250N 产品类型断路器产品应用配电保护极数3P 保护极说明3D额定电流 [In]1250 A 在…上 50 °C 1250 A 在…上 65 °C 断路器型号N 互感器额定值1250 A隔离功能适用 符合 IEC 60947-2补充信息电网类型AC 电网频率50/60 Hz 控制类型手柄安装类型固定式安装方式底板安装导轨安装连接方式-上端前连接连接方式-下端前连接额定绝缘电压 [Ui]800 V AC 50/60 Hz 符合 IEC 60947-2额定冲击耐受电压 [Uimp]8 KV 符合 IEC 60947-2额定工作电压 [Ue]690 V AC 50/60 Hz 符合 IEC 60947-2分断能力50 KA Icu 在…上 220/240 V AC 50/60 Hz 符合 IEC 60947-2 50 KA Icu 在…上 380/415 V AC 50/60 Hz 符合 IEC 60947-2 50 KA Icu 在…上 440 V AC 50/60 Hz 符合 IEC 60947-2 40 KA Icu 在…上 500/525 V AC 50/60 Hz 符合 IEC 60947-2 30 KA Icu 在…上 660/690 V AC 50/60 Hz 符合 IEC 60947-2额定使用短路分断能力[Ics]100 % 50/60 Hz 符合 IEC 60947-2使用类别Category B 机械寿命10000 次电气寿命2000 次 690 V AC 50/60 Hz In 符合 IEC 60947-2 3000 次 690 V AC 50/60 Hz In/2 符合 IEC 60947-2 4000 次 440 V AC 50/60 Hz In 符合 IEC 60947-2 5000 次 440 V AC 50/60 Hz In/2 符合 IEC 60947-2额定短时耐受电流 [Icw]19.2 KA 脱扣器名称MicroLogic 2.0脱扣器类型电子式脱扣器保护功能LI脱扣器额定值1250 A 在…上 50 °C 保护类型短路瞬时保护过载保护 (长延时)长延时电流整定类型可调长延时电流整定值 [Ir]0.4...1 x In 长延时时间整定类型9 档可调[tr] 长延时时间整定范围0.7…16.6 S 7.2 x Ir 0.7…24 S 6 x Ir 12.5…600 S 1.5 x Ir 热记忆20 mn 瞬时保护电流整定类型可调瞬时保护整定值 [Ii]1.5...10 x IrT h e i n f o r m a t i o n p r o v i d e d i n t h i s d o c u m e n t a t i o n c o n t a i n s g e n e r a l d e s c r i p t i o n s a n d /o r t e c h n i c a l c h a r a c t e r i s t i c s o f t h e p e r f o r m a n c e o f t h e p r o d u c t s c o n t a i n e d h e r e i n .T h i s d o c u m e n t a t i o n i s n o t i n t e n d e d a s a s u b s t i t u t e f o r a n d i s n o t t o b e u s e d f o r d e t e r m i n i n g s u i t a b i l i t y o r r e l i a b i l i t y o f t h e s e p r o d u c t s f o r s p e c i f i c u s e r a p p l i c a t i o n s .I t i s t h e d u t y o f a n y s u c h u s e r o r i n t e g r a t o r t o p e r f o r m t h e a p p r o p r i a t e a n d c o m p l e t e r i s k a n a l y s i s , e v a l u a t i o n a n d t e s t i n g o f t h e p r o d u c t s w i t h r e s p e c t t o t h e r e l e v a n t s p e c i f i c a p p l i c a t i o n o r u s e t h e r e o f .N e i t h e r S c h n e i d e r E l e c t r i c I n d u s t r i e s S A S n o r a n y o f i t s a f f i l i a t e s o r s u b s i d i a r i e s s h a l l b e r e s p o n s i b l e o r l i a b l e f o r m i s u s e o f t h e i n f o r m a t i o n c o n t a i n e d h e r e i n .区域选择性联锁 ZSI无高度327 Mm宽度210 Mm深度147 Mm污染等级 3 符合 IEC 60947净重14 Kg环境符合标准IEC 60947-2运行温度-25…70 °C贮存环境温度-50…85 °C包装单位Unit Type of Package 1PCENumber of Units in Package 11Package 1 Weight12 Kg可持续性产品类型Green Premium 产品REACh法规REACh 声明欧盟ROHS指令符合豁免条件Mercury free是中国 ROHS 管理办法中国 ROHS 声明RoHS exemption information是环境披露产品环境文件流通资料产品使用寿命终期信息WEEE该产品必须经特定废物回收处理后弃置于欧盟市场,绝不可丢弃于垃圾桶中。

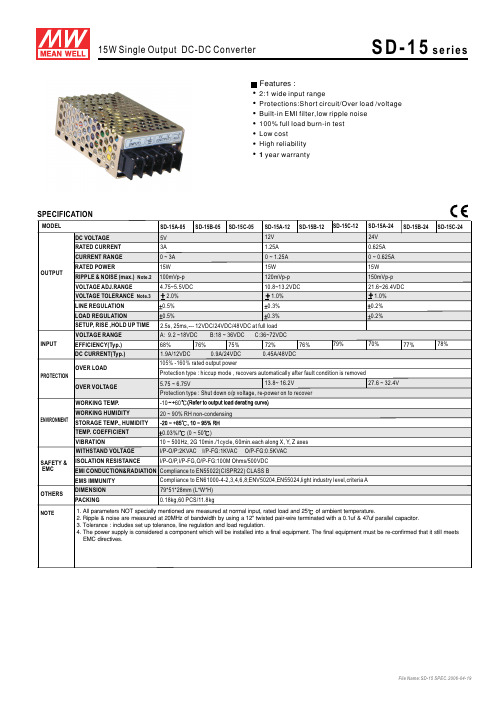

SD-15中文资料

1. All parameters NOT specially mentioned are measured at normal input, rated load and 25of ambient temperature.2. Ripple & noise are measured at 20MHz of bandwidth by using a 12" twisted pair-wire terminated with a 0.1uf & 47uf parallel capacitor.3. Tolerance : includes set up tolerance, line regulation and load regulation.4. The power supply is considered a component which will be installed into a final equipment. The final equipment must be re-confirmed that it still meets EMC directives.DC VOLTAGE SPECIFICATIONMODELOUTPUTRATED CURRENT CURRENT RANGERATED POWERRIPPLE & NOISE (max.)Note.2VOLTAGE TOLERANCE Note.3LINE REGULATION LOAD REGULATIONVOLTAGE RANGESETUP, RISE ,HOLD UP TIME EFFICIENCY(Typ.)DC CURRENT(Typ.)OVER LOADOVER VOLTAGE WORKING TEMP.WORKING HUMIDITY STORAGE TEMP., HUMIDITY TEMP. COEFFICIENT VIBRATIONWITHSTAND VOLTAGE ISOLATION RESISTANCEDIMENSIONINPUTPROTECTIONENVIRONMENTSAFETY &EMCOTHERSNOTE12V 1.25A 0 ~ 1.25A 15W 120mVp-p 1.0% 1.0%2.5s, 25ms,--- 12VDC/24VDC/48VDC at full loadA: 9.2 ~18VDC B C:36~72VDC:18 ~ 36VDC 68%1.9A/12VDC 0.9A/24VDC 0.45A/48VDC 105% -160%rated output powerProtection type : hiccup mode , recovers automatically after fault condition is removed5.75 ~6.75V20 ~ 90% RH non-condensing10 ~ 500Hz, 2G 10min./1cycle, 60min.each along X,Y, Z axes I/P-O/P:2KVAC I/P-FG:1KVAC O/P-FG:0.5KVAC I/P-O/P,I/P-FG,O/P-FG:100M Ohms/500VDC 79*51*28mm (L*W*H)2:1 wide input rangeProtections:Short circuit/Over load /voltage Built-in EMI filter,low ripple noise 100% full load burn-in test Low cost High reliability year warranty115W Single Output DC-DC ConverterSD-15series-1060SD-15C-125V 3A 0 ~ 3A 15W 100mVp-p 2.0%24V 0.625A 0 ~ 0.625A 15W 150mVp-p 72%70%13.8~ 16.2V 27.6 ~ 32.4VEMI CONDUCTION&RADIATION Compliance to EN55022(CISPR22) CLASS BSD-15A-24SD-15A-12SD-15B-12SD-15B-24SD-15C-24SD-15C-05SD-15B-05SD-15A-0576%75%76%79%77%78%VOLTAGE ADJ.RANGE4.75~5.5VDC 10.8~13.2VDC 21.6~26.4VDC 0.3%0.5%0.5%0.2%0.3%0.2%0.03%/(0 ~ 50)EMS IMMUNITY Compliance to EN61000-4-2,3,4,6,8;ENV50204,EN55024,light industry level,criteria A PACKING0.18kg,60 PCS/11.8kgFeatures :Protection type : Shut down o/p voltage, re-power on to recoverCase No.931 Unit:mmMechanical SpecificationOutput DeratingBlock DiagramSD-15series15W Single Output DC-DC ConverterStatic Characteristics1LED+V ADJ.235466.27.622-M3 L=666.510.555792.2514282-M3 L=425.451Terminal Pin. No AssignmentPin No.Pin No.12435Assignment Assignment DC OUTPUT +V DC OUTPUT -VFGDC INPUT V+DC INPUT V-L O A D (%)(HORIZONTAL)(VERTICAL)-10-10102030405045605520406080100AMBIENT TEMPERATURE ( )CIRCUITDETECTION EMI FILTERFILTER&RECTIFIERS+V -VI/Pfosc : 96KHzPWM RECTIFIERS&FILTERPOWER SWITCH-INGCONTROL OLPL O A D (%)9.218367220406080100INPUT VOLTAGE( VDC )Ta=25SD-15A SD-15B SD-15C。

ADC0808中文资料_数据手册_参数

Operating Conditions (1)(2)

Temperature Range Range of VCC

TMIN≤TA≤TMAX −40°C≤TA≤+85°C ቤተ መጻሕፍቲ ባይዱ.5 VDC to 6.0 VDC

(1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications do not apply when operating the device beyond its specified operating conditions.

KEY SPECIFICATIONS

• Resolution: 8 Bits • Total Unadjusted Error: ±½ LSB and ±1 LSB • Single Supply: 5 VDC • Low Power: 15 mW • Conversion Time: 100 μs

Figure 2. PLCC

See Package N0028E

Package

See Package FN0028A

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

SMDA15C-7TB中文资料

Symbol VRWM VBR IR VC IPP Cj

Conditions

Minimum

It = 1mA

VRWM = 12V, T=25°C

IPP = 1A, tp = 8/20µs

tp = 8/20µs

Between I/O Pins and Gnd

VR = 0V, f = 1MHz

13.3

Typical

Symbol VRWM VBR IR VC IPP Cj

Conditions

Minimum

It = 1mA

VRWM = 24V, T=25°C

IPP = 1A, tp = 8/20µs

tp = 8/20µs

Between I/O Pins and Gnd

VR = 0V, f = 1MHz

26.7

Typical

The SMDAxxC-7 is designed to protect up to 7 data or I/O lines. They are bidirectional devices and may be used on lines where the signal polarities are above and below ground.

Mechanical Characteristics

u JEDEC SO-8 package u Molding compound flammability rating: UL 94V-0 u Marking : Part number, date code, logo u Packaging : Tube or Tape and Reel per EIA 481

Maximum 15

at89c52单片机中英文资料对照外文翻译文献综述

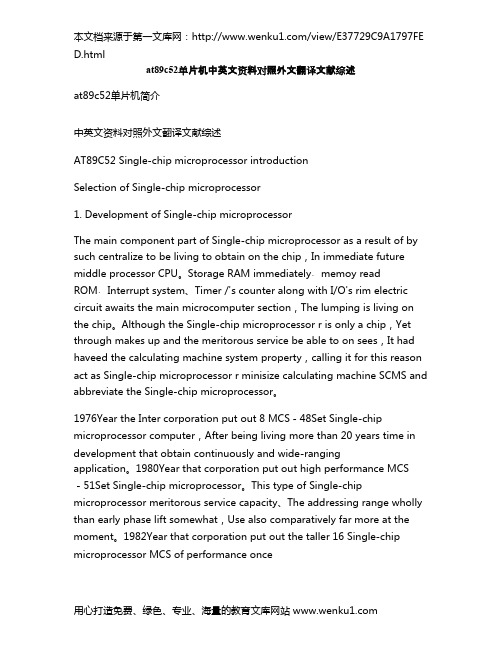

D.htmlat89c52单片机中英文资料对照外文翻译文献综述at89c52单片机简介中英文资料对照外文翻译文献综述AT89C52 Single-chip microprocessor introductionSelection of Single-chip microprocessor1. Development of Single-chip microprocessorThe main component part of Single-chip microprocessor as a result of by such centralize to be living to obtain on the chip,In immediate future middle processor CPU。

Storage RAM immediately﹑memoy readROM﹑Interrupt system、Timer /'s counter along with I/O's rim electric circuit awaits the main microcomputer section,The lumping is living on the chip。

Although the Single-chip microprocessor r is only a chip,Yet through makes up and the meritorous service be able to on sees,It had haveed the calculating machine system property,calling it for this reason act as Single-chip microprocessor r minisize calculating machine SCMS and abbreviate the Single-chip microprocessor。

adc0808中文资料[整理版]

![adc0808中文资料[整理版]](https://img.taocdn.com/s3/m/02ae1a6e84254b35effd345a.png)

adc0808中文资料[整理版]11.2.4 典型的集成ADC芯片为了满足多种需要,目前国内外各半导体器件生产厂家设计并生产出了多种多样的ADC芯片。

仅美国AD公司的ADC产品就有几十个系列、近百种型号之多。

从性能上讲,它们有的精度高、速度快,有的则价格低廉。

从功能上讲,有的不仅具有A/D转换的基本功能,还包括内部放大器和三态输出锁存器;有的甚至还包括多路开关、采样保持器等,已发展为一个单片的小型数据采集系统。

尽管ADC芯片的品种、型号很多,其内部功能强弱、转换速度快慢、转换精度高低有很大差别,但从用户最关心的外特性看,无论哪种芯片,都必不可少地要包括以下四种基本信号引脚端:模拟信号输入端(单极性或双极性);数字量输出端(并行或串行);转换启动信号输入端;转换结束信号输出端。

除此之外,各种不同型号的芯片可能还会有一些其他各不相同的控制信号端。

选用ADC芯片时,除了必须考虑各种技术要求外,通常还需了解芯片以下两方面的特性。

(1)数字输出的方式是否有可控三态输出。

有可控三态输出的ADC芯片允许输出线与微机系统的数据总线直接相连,并在转换结束RD后利用读数信号选通三态门,将转换结果送上总线。

没有可控三态输出(包括内部根本没有输出三态门和虽有三态门、但外部不可控两种情况)的ADC芯片则不允许数据输出线与系统的数据总线直接相连,而必须通过I/O接口与MPU交换信息。

(2)启动转换的控制方式是脉冲控制式还是电平控制式。

对脉冲启动转换的ADC 芯片,只要在其启动转换引脚上施加一个宽度符合芯片要求的脉冲信号,就能启动转换并自动完成。

一般能和MPU配套使用的芯片,MPU的I/O写脉冲都能满足ADC芯片对启动脉冲的要求。

对电平启动转换的ADC芯片,在转换过程中启动信号必须保持规定的电平不变,否则,如中途撤消规定的电平,就会停止转换而可能得到错误的结果。

为此,必须用D触发器或可编程并行I/O接口芯片的某一位来锁存这个电平,或用单稳等电路来对启动信号进行定时变换。

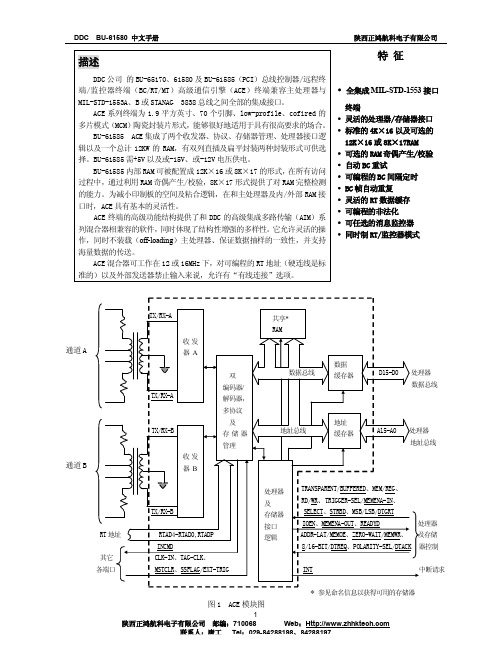

61580中文手册_DDC_BU-61585

单位

mA

mA mA mA mA

mA

mA mA mA mA

mA mA mA mA

W W W W

W W W W

W W W W

W W W W

4

陕西正鸿航科电子有限公司 邮编:710068

Web:

联系人:唐工 Tel:029-84288198、84288197

DDC BU-61580 中文手册

■ (BU-65170/61580/61585×3、BU-65170/61580/61585×6)(注 1-7)

门限电压(变压器耦合、短截线上测得)

0.200

共模电压(注 7)

发送器

差分输出电压

■ 跨接 35Ω直接耦合、在总线上测得

6

■ 跨接 70Ω变压器耦合、在总线上测得

■ (BU-65170/61580/61585×1、BU-65170/61580/61585×2、×3、×6)

处理器

ADDR-LAT/MEMOE、ZERO-WAIT/MEMWR、 及存储

8/16-BIT/DTREQ、POLARITY-SEL/DTACK 器控制

INT

中断请求

* 参见命名信息以获得可用的存储器

图 1 ACE 模块图

1

陕西正鸿航科电子有限公司 邮编:710068

Web:

数据总线

数据 缓存器

D15-D0

处理器 数据总线

地址总线

地址 缓存器

A15-A0

处理器 地址总线

处理器 及 存储器 接口 逻辑

TRANSPARENT/BUFFERED、MEM/REG、

RD/WR、TRIGGER-SEL/MEMENA-IN、

SELECT、STRBD、MSB/LSB/DTGRT

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Circuit Diagram

Schematic & PIN Configuration

1 & 14

7&8

2 3 12 13 5 6 9 10

Revision 04/12/05

1

1

14

2

13

3

12

4

11

5

10

6

9

7

8

SO-14 (Top View)

元器件交易网

8

15

2005 Semtech Corp.

4

元器件交易网

SMDA05C-8 through SMDA24C-8

PROTECTION PRODUCTS

Applications Information

Device Connection for Protection of Eight Data Lines

0 0

Pulse Waveform

e-t

Waveform Parameters:

tr = 8µs td = 20µs

td = IPP/2

5

10

15

20

25

30

Time (µs)

ESD Pulse Waveform (IEC 61000-4-2)

% of Rated Power or IPP

110 100

(A)

Peak Current at 30 ns

(A)

Peak Current at 60 ns

(A)

Test Voltage (Contact Discharge)

(kV)

Test Voltage

(Air Discharge)

(kV)

1

7.5

4

8

2

2

2

15

8

4

4

4

3 22.5

12

6

6

8

4

30

16

8

The SMDAxxC-8 TVS arrays employ a monolithic structure. Therefore, the working voltage (VRWM) and breakdown voltage (VBR) specifications apply to the differential voltage between any two data line pins. For example, the SMDA24C-8 is designed for a maximum voltage excursion of ±12V between any two data lines.

元器件交易网

SMDA05C-8 through SMDA24C-8

Bidirectional TVS Array for Protection of Eight Lines

PROTECTION PRODUCTS

Description

The SMDAxxC-8 series of transient voltage suppressors are designed to protect components which are connected to data and transmission lines from voltage surges caused by electrostatic discharge (ESD), electrical fast transients (EFT), and lightning.

Symbol Ppk TL TJ TSTG

Value 300 260 (10 sec.) -55 to +125 -55 to +150

Units Watts

°C °C °C

Electrical Characteristics

SMDA05C-8

Parameter Reverse Stand-Off Voltage Reverse Breakdown Voltage Reverse Leakage Current Clamping Voltage Peak Pulse Current Junction Capacitance

Non-Repetitive Peak Pulse Power vs. Pulse Time

10

Peak Pulse Power - Ppk (kW)

1

0.1

Percent of IPP

0.01 0.1

1

10

100

Pulse Duration - tp (µs)

1000

110 100

90 80 70 60 50 40 30 20 10

Features

Transient protection for data lines to

IEC 61000-4-2 (ESD) ±15kV (air), ±8kV (contact) IEC 61000-4-4 (EFT) 40A (5/50ns) IEC 61000-4-5 (Lightning) 12A (8/20µs) Small SO-14 surface mount package Protects eight I/O lines Working voltages: 5V, 12V, 15V and 24V Low leakage current Low operating and clamping voltages Solid-state silicon avalanche technology

Typical

Maximum 15

1 24 10 75

Units V V µA V A pF

SMDA24C-8 Parameter

Reverse Stand-Off Voltage Reverse Breakdown Voltage Reverse Leakage Current Clamping Voltage Peak Pulse Current Junction Capacitance

Symbol VRWM VBR IR V

C

IPP Cj

Conditions

Minimum

It = 1mA

VRWM = 15V, T=25°C