THC63LVD103_LVDS

THC63LVDM83R中文资料

/PDWN

32

Type LVDS OUT LVDS OUT LVDS OUT LVDS OUT LVDS OUT

IN IN IN IN

IN

RS

1

IN

R/F

17

IN

VCC

CLKIN

GND

LVDS VCC LVDS GND PLL VCC PLL GND

9, 26

31 5, 13, 21,

29, 53 44

LVDS swing 350mV : 200mV

Input Clock Triggering Edge Select. H: Rising edge, L: Falling edge

Power Supply Pins for TTL inputs and digital circuitry.

Clock in.

元器件交易网

THC63LVDM83R/THC63LVDM63R_Rev2.0

THC63LVDM83R/THC63LVDM63R

REDUCED SWING LVDS 24Bit/18Bit COLOR HOST-LCD PANEL INTERFACE

General Description

TA4 RS

1 2

TA5 TA6 GND TB0 TB1 VCC

TB2 TB3 GND TB4

3 4 5 6 7 8 9 10 11 12

TB5 13

R/F 14

TB6 TC0 GND TC1 TC2 TC3 VCC TC4

15 16 17 18 19 20 21 22

TC5 GND

23 24

48 47 46 45 44 43

/PDWN

27

创维液晶电视各种机芯维修实例

创维液晶电视各种机芯维修实例.doc机型/机芯故障现象解决方法15AAB/8TT1 刚开机能看到画面,一秒钟后有声无像,背光灯不亮判断为背光板引起的,拆开检测发现电容C18、C24(25V/22UF)爆裂,更换试机,故障排除。

15AAC/8TT1 无图像有伴音经检修发现PW1235在工作时发热严重,造成引脚虚焊,对IC 进行补焊,故障排除。

20L98TV8K60 放一段时间后失控,图花此机大概放5 分钟就出现按键失控,图花,怀疑MT8200 虚焊,补焊后故障依旧,在出现故障时测量各路供电,发现IC2/3.3V 只有3.1V 左右,换之老化,故障排除20L98TV/8K60 声音失真(声音制式错乱一样刚开机,图像声音正常,过一会儿声音成呼声(声音制式不对).因该机为新机型,手头无资料,试代换存储器24C32 后,长时间老化机器正常20L98TV/8K60 TV 图像拖尾,A V 正常AV 图像正常,说明故障出现在中放电路,试代换TDA9886TS,380W38-02,故障依旧.怀疑声表面K7262 坏,换之正常19L11IW/8K60 搜不到台首先查高频头的供电,发现没33V 调谐电压,因此机33V 采用的是自举升压电路,依次查D6,D1,ZD1。

D6烧坏,换之,再次烧坏,仔细检查C93/0.47UF 电容漏电,换D6,C93 故障排除22LEATV/8TT6 图不良模拟信号TV/A V 下时有时无图像,问题肯定在模拟信信号通道,TV/A V 信号解码是通过TVP5147 解码,查各供电,时钟正常,代换解码TVP5147 试机故障排除.22LEATV/8TT6 黑屏开盖检查,发现背光灯在开机瞬间亮一下即熄灭。

疑为背光板问题。

检查发现C34 虚焊,补焊后故障排除。

22LEATV/8TT6 该机开机黑屏伴音正常,背光不亮测背光板供电有,控制电压也有但FB1开路,怀疑背光板上负载短路,仔细查发现C305 有点变黄,拆下发现该电容已严重短路,于是找来一只50V10UF电容装上,再装上一只好的FB1 开机背光亮起来了,故障排除。

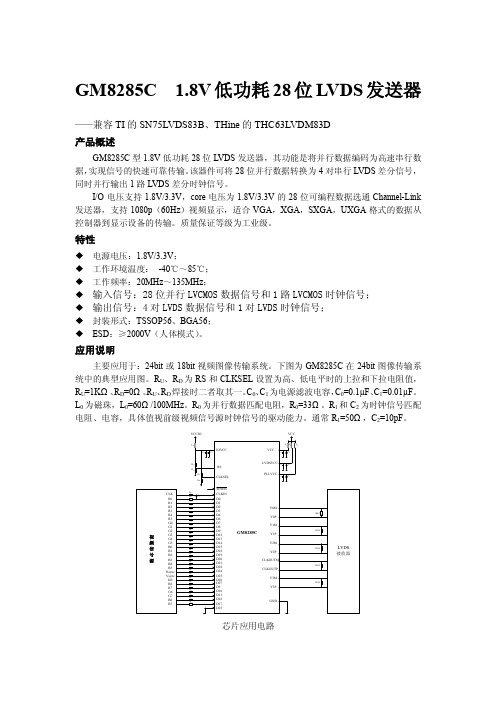

GM8285C产品资料

GM8285C 1.8V低功耗28位LVDS发送器——兼容TI的SN75LVDS83B、THine的THC63LVDM83D产品概述GM8285C型1.8V低功耗28位LVDS发送器,其功能是将并行数据编码为高速串行数据,实现信号的快速可靠传输。

该器件可将28位并行数据转换为4对串行LVDS差分信号,同时并行输出1路LVDS差分时钟信号。

I/O电压支持1.8V/3.3V,core电压为1.8V/3.3V的28位可编程数据选通Channel-Link 发送器,支持1080p(60Hz)视频显示,适合VGA,XGA,SXGA,UXGA格式的数据从控制器到显示设备的传输。

质量保证等级为工业级。

特性◆电源电压:1.8V/3.3V;◆工作环境温度:-40℃~85℃;◆工作频率:20MHz~135MHz;◆输入信号:28位并行LVCMOS数据信号和1路LVCMOS时钟信号;◆输出信号:4对LVDS数据信号和1对LVDS时钟信号;◆封装形式:TSSOP56、BGA56;◆ESD:≥2000V(人体模式)。

应用说明主要应用于:24bit或18bit视频图像传输系统。

下图为GM8285C在24bit图像传输系统中的典型应用图。

R U、R D为RS和CLKSEL设置为高、低电平时的上拉和下拉电阻值,R U=1KΩ、R D=0Ω。

R U、R D焊接时二者取其一。

C0、C1为电源滤波电容,C0=0.1µF、C1=0.01µF。

L0为磁珠,L0=60Ω/100MHz。

R0为并行数据匹配电阻,R0=33Ω。

R1和C2为时钟信号匹配电阻、电容,具体值视前级视频信号源时钟信号的驱动能力。

通常R1=50Ω,C2=10pF。

芯片应用电路。

THC63LVDM83R芯片手册

IN

RS

1

IN

R/F

17

IN

VCC

CLKIN

GND

LVDS VCC LVDS GND PLL VCC PLL GND

9, 26

31 5, 13, 21,

29, 53 44

36, 43, 49 34

33, 35

Power

IN

Ground

Power Ground Power Ground

DATA (LVDS) TA +/TB +/TC +/-

CMOS/TTL INPUTS

TA0-6 7

TB0-6 7

TC0-6 7

THC63LVDM63R

DATA (LVDS) TA +/TB +/TC +/-

TD +/-

(140-595Mbit/On Each

(140-595Mbit/On Each

Description

LVDS Data Out.

LVDS Clock Out.

Pixel Data Inputs.

H: Normal operation, L: Power down (all outputs are Hi-Z)

LVDS swing control. RS VCC : GND

LVDS swing 350mV : 200mV

TA4 RS

1 2

TA5 TA6 GND TB0 TB1 VCC

TB2 TB3 GND TB4

3 4 5 6 7 8 9 10 11 12

TB5 13

R/F 14

TB6 TC0 GND TC1 TC2 TC3 VCC TC4

INFINITY用户手册_中文

表示PALLET的动作状态 INDICATE LED 控制用 CONTROL BLOCK (利用I2C通信) ANALOG DIMMING, HVS, BIST SIGNAL的控制BLOCK (I2C 通信控制利用) 在POWER BLOCK供给的12V变换5V 5V电源变换3.3V 利用5V和3.3V变换1.2V, 1.8V, 2.5V 在POWER BLOCK上VDD/ VBL的电压, 电流检出转换DIGITAL值

EXTM_OUT_B2[0..9] EXTM_OUT_G2[0..9] EXTM_OUT_R2[0..9] VCC_3.3V R213 R214 R215 NC NC NC EXTM_OUT_DE EXTM_OUT_VS EXTM_OUT_HS

EXTM_OUT_G20 EXTM_OUT_R25 EXTM_OUT_R24 EXTM_OUT_R23 EXTM_OUT_R22 EXTM_OUT_R21 EXTM_OUT_R20

EXTM_OUT_B25 EXTM_OUT_B24 EXTM_OUT_B23 EXTM_OUT_B22

R350

0(1608)

VCC_3.3V

104(1608) BC36

104(1608) BC37

104(1608) BC38

104(1608) BC39

VCC_3.3V

R47

R48

R49

R50

R51

R52

43pattern不良moduel或signalcable等外部检查和adaptorcard交换之后问题继续时症状预想原因措施internalexternal没有全部点灯的时候fpga自体不良或pll不良预想power或别的功能上没问题display只有问题的时候u16pll的输入clock和出力clock确认没有输入clock的时候fpga不良概率高没有出力clock的时候pllic交换以上操作以后继续发生问题时修理委托fromfpgaclockinputtofpgacolckoutput症状预想原因措施external点灯不良u13ds90c3202的不良lvds输入接受由于ds90c3202的不良点灯不良的可能性高pattern点灯时ds90c3202的extmoutclk和extmout的出力情况确认没有出力的时候ds90c3202交换有出力没有点灯的时候fpga输入line上有问题可能性当pin上焊接从新做然后没什么改善的是时候修理委托tofpgacolckdeoutput症状预想原因措施internalexternalpatternnoisefpga出力port或者serialregister等有问题可能性fpga出力port和serialregister和破坏或者接触不良有可能性fpga出力port和焊接工作从新进行fpga和adaptor连接用100pconnector中间serialregisterex2的值测定10ohmregister的破坏的时候值有变形当register交换有关措施以后问题继续出来时fpga上有问题判断修理委托ex2pallet电路的抵抗表示时表示第三位子乘数但出力除了f级表示以外

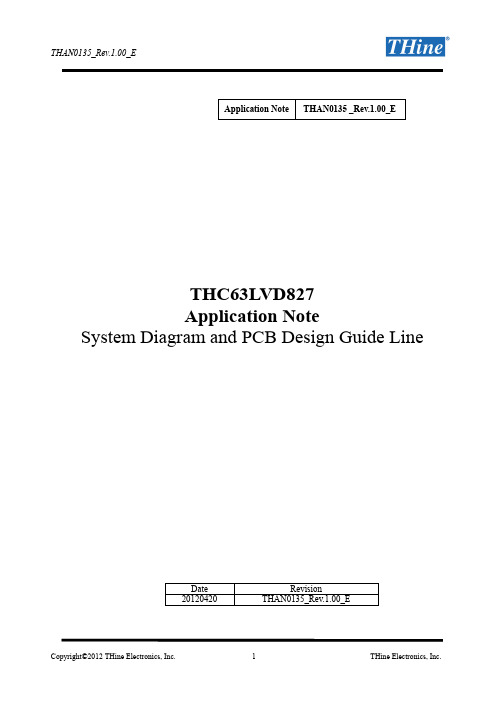

THC63LVD827参考设计TTL转LVDS

Application Note THAN0135_Rev.1.00_ETHC63LVD827Application NoteSystem Diagram and PCB Design Guide LineDate Revision20120420THAN0135_Rev.1.00_EContents1.Mode Settings P.32.Signal Flow for Each Setting P.3S/TTL DATA Timing Diagram P.44.LVDS DATA Timing Diagram P.65.LVDS DATA Mapping P.86.Example of System Diagram1)Single In–Single Out/8bit COMS/TTL Input/IO VCC=1.8V P.102)Single In–Dual Out/8bit COMS/TTL Input/IO VCC=1.8V P.113)Single In–Dual Out/6bit COMS/TTL Input/IO VCC=3.3V P.127.NOTE P.138.Trace Example for BGA P.149PCB Design Guide Line for LVDS P.15R[7:0]G[7:0]B[7:0]HSYNC VSYNCDE CLKINCLK FrequencyfDATA RatefDATA CLK Frequencyf RatefTA1+/-TB1+/-TC1+/-TD1+/-TCLK1+/-TA2+/-TB2+/-TC2+/-TD2+/-TCLK2+/-Hi-ZSingle In /Single OutR[7:0]G[7:0]B[7:0]HSYNC VSYNCDE CLKINCLK FrequencyfDATA RatefTA1+/-TB1+/-TC1+/-TD1+/-TCLK1+/-TA2+/-TB2+/-TC2+/-TD2+/-TCLK2+/-Single In /Dual Out Double Data Rate offDATA CLK Frequencyf/2Ratef/2DATA CLK Frequencyf/2Ratef/2TCLK1+/-R[7:0]G[7:0]B[7:0]HSYNC VSYNCDE CLKINCLK Frequencyf/2DATA RatefTA1+/-TB1+/-TC1+/-TD1+/-TCLK1+/-TA2+/-TB2+/-TC2+/-TD2+/-TCLK2+/-Single In /Dual Out Double Data Rate onDATA CLK Frequencyf/2Ratef/2DATA CLK Frequencyf/2Ratef/2TCLK1+/-1.Mode SettingsMODE DDRNO/EInput Mode Double Data Rate Output Enable Input /Output OptionH :Single L :Dual H :DDR Input off L :DDR Input on-H :Enable L :DisableOutput Disable (Hi-Z)H -L Single In /Single Out Output Enable H -H Output Disable (Hi-Z)L -L Output Enable/DDR off L H H Single In /Dual OutOutput Enable/DDR onLLH2.Signal Flow for Each SettingCLKINRGB HSYNC VSYNC DECLKINRGB HSYNC VSYNC DES/TTL Data Timing Diagram1)Single Edge Input Mode (MODE=H or MODE=L,DDR=H)2)Double Edge Input Mode (MODE=L,DDR=L)T H C 63L V D 827CH1CH2Single CMOS/TTL InputDual LVDS Output3)Data sorting example of TTL input versus LVDS output in Single-In Dual-Out mode with double edge Input mode for 1920x 1440panel.4.LVDS Data Timing Diagram1)Single In-Dual Out Mode(MODE=L)2)Single In-Single Out Mode(MODE=H)5.LVDS Data Mapping1)for8bit mode(6B/8B=L)2)for6bit mode(6B/8B=H)6.Example of System Diagram1)Single In–Single Out/8bit1.8V COMS/TTL InputNote:●O/E,RS,R/F,MAP:Please select IOVCC level or GND level,it depends on your operation.●Connect each Board GND●Please prepare the100ohm pair cable or PCB pattern trace that is controlled with100ohm forLVDS signal.2)Single In–Dual Out/8bit1.8V COMS/TTL InputDDR(Double Edge input)function disable.Note:●O/E,RS,R/F,MAP:Please select IOVCC level or GND level,it depends on your operation.●Connect each Board GND●Please prepare the100ohm pair cable or PCB pattern trace that is controlled with100ohm forLVDS signal.3)Single In–Dual Out/3.3V6bit COMS/TTL InputDDR(Double Edge input)function enableNote:●O/E,RS,R/F,MAP:Please select IOVCC level or GND level,it depends on your operation.●Connect each Board GND●Please prepare the100ohm pair cable or PCB pattern trace that is controlled with100ohm forLVDS signal.4.Note4.1)Cable Connection and DisconnectionDo not connect and disconnect the LVDS cable,when the power is supplied to the system.4.2)GND ConnectionConnect the each GND of the Board which THC63LVDM83E and Receiver on it.It is better for EMI reduction to place GND cable as close to LVDS cable as possible.4.3)Multi Drop ConnectionMulti drop connection is not recommended.4.3)Asynchronous useAsynchronous uses such as following systems are not recommended.If it’s not avoidable,please contact to mspsupport@thine.co.jp(for FAE mailing list)5.Trace Example for BGAR0R26.PCB Design Guide LineGeneral Guideline●Use4layers PCB(minimum).●Locate by-pass capacitors adjacent close to the device pins to a maximum extent.●Make the loop minimum which is consist of Power line and GND line.●Use large GND plane.●Separate VDD power supply for each block via ferrite bead.LVDS Trace●Interconnecting media between Transmitter and Receiver(i.e.PCB trace,connector and cable)should bewell balanced.(Keep all these differential impedance and the length of media as same as possible)●Minimize the distance between traces of a pair(S1)to maximize common mode rejection.See followingfigure.●Place adjacent LVDS trace pair at least twice(>2x S1)as far away as possible.●Avoid90degree bends and sharp angles.●Minimize the number of VIA on LVDS traces.●Match impedance of PCB trace,connector,cable and termination to minimize reflections(emissions)forcabled applications(typically100ohm differential mode characteristic impedance).●Place terminal resistor close to the Receiver pins to a maximum extent.●To place common mode choke coil is desired for EMI reduction.GNDNotices and Requests1.The product specifications described in this material are subject to change without prior notice.2.The circuit diagrams described in this material are examples of the application which may not always apply tothe customer's design.We are not responsible for possible errors and omissions in this material.Please note if errors or omissions should be found in this material,we may not be able to correct them immediately.3.This material contains our copyright,know-how or other proprietary.Copying or disclosing to third partiesthe contents of this material without our prior permission is prohibited.4.Note that if infringement of any third party's industrial ownership should occur by using this product,we willbe exempted from the responsibility unless it directly relates to the production process or functions of the product.5.This product is presumed to be used for general electric equipment,not for the applications which requirevery high reliability(including medical equipment directly concerning people's life,aerospace equipment,or nuclear control equipment).Also,when using this product for the equipment concerned with the control and safety of the transportation means,the traffic signal equipment,or various Types of safety equipment,please do it after applying appropriate measures to the product.6.Despite our utmost efforts to improve the quality and reliability of the product,faults will occur with a certainsmall probability,which is inevitable to a semi-conductor product.Therefore,you are encouraged to have sufficiently redundant or error preventive design applied to the use of the product so as not to have our product cause any social or public damage.7.Please note that this product is not designed to be radiation-proof.8.Customers are asked,if required,to judge by themselves if this product falls under the category of strategicgoods under the Foreign Exchange and Foreign Trade Control Law.THine Electronics,Inc.sales@thine.co.jp。

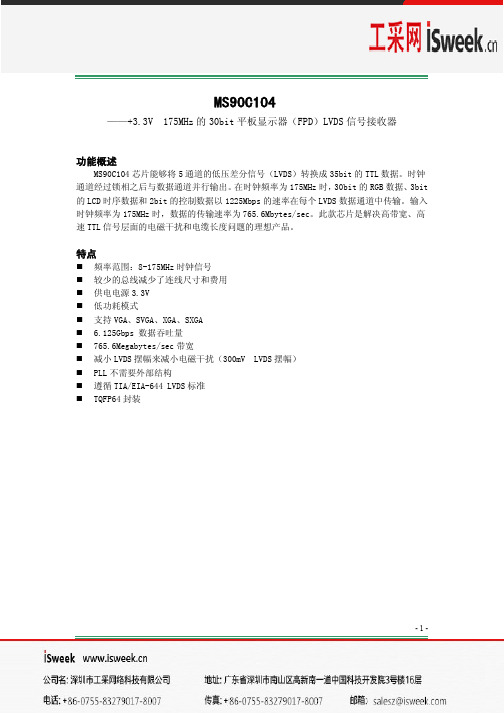

杭州瑞盟科技有限公司MS90C104 30bit平板显示器LVDS信号接收器说明书

2013.08.12

共9页 第6页

图 4.锁相环设置时间

MS90C104

图 5.接收器状态

Vdiff=(RxIN+)-(RxIN-),……(RxCLKIN+)-(RxCLKIN-)

图 6.并行 TTL 输出数据与 LVDS 输入数据匹配关系

Previous Cycle

Next Cycle

RCLK RL4

1.4W

电学特性

符号 VIH VIL VOH

VOL

IIN IOS

参数 输入高电平 输入低电平 输出高电平

输出低电平

输入电流 输出短路电流

条件

Min

2.0

GND

IOH = -4mA(data) 2.4 IOH = -8mA(clock) IOL = 4mA(data) IOL = 8mA(clock)

-3-

版本号:1.2

2013.08.12

共9页 第3页

MS90C104

推荐工作条件

电源电压(VCC) CMOS/TTL 输入电压 CMOS/TTL 输出电压 LVDS 接收输入电压 结点温度 温度范围 瞬间耐温(焊接,4 秒) 最大功耗(25℃) MS90C104

-0.3V - 4.0V -0.3V - (VCC+0.3V) -0.3V - (VCC+0.3V) -0.3V - (VCC+0.3V) +150℃ -40℃ - 100℃ +260℃

RX0/7/14/21/28

RX1/8/15/22/29

RX2/9/16/23/30 RX3/10/17/24/31 RX4/11/18/25/32 RX5/12/19/26/33 RX6/13/20/27/34

用于驱动共阴极和共阳极的数码显示管的译码器的分类

一、概述数码显示管是一种常见的显示设备,用于在电子设备和仪器中显示数字和字符。

为了控制数码显示管的工作,常常需要使用译码器来将输入信号转换为驱动数码显示管的信号。

其中,用于驱动共阴极和共阳极的数码显示管的译码器是常见的一种类型,本文将对其进行分类和介绍。

二、共阴极和共阳极数码显示管共阴极数码显示管和共阳极数码显示管是常见的两种数码显示管类型。

共阴极数码显示管的所有阴极都连接在一起,并通过负极性的驱动信号来显示数字和字符;而共阳极数码显示管的所有阳极都连接在一起,并通过正极性的驱动信号来显示数字和字符。

三、译码器的分类根据不同的工作原理和功能特点,译码器可以分为以下几种类型:1. BCD-7段译码器BCD-7段译码器是一种常见的译码器,它将二进制代码转换为驱动7段数码显示管的控制信号。

在共阴极和共阳极的数码显示管中,BCD-7段译码器可以根据输入的二进制代码来控制相应的数码显示管段的亮灭,从而实现数字和字符的显示。

2. 译码器/驱动器一体化芯片译码器/驱动器一体化芯片是一种集成了译码和驱动功能的芯片,它能够直接驱动数码显示管,提高了系统的集成度和稳定性。

在共阴极和共阳极的数码显示管中,译码器/驱动器一体化芯片能够减少外部电路的复杂度,简化系统设计与布局。

3. 数字集成电路数字集成电路中包含了多种用于驱动数码显示管的译码器,例如74系列芯片中的7447、7448等译码器。

这些数字集成电路与其他逻辑门、触发器等元件结合,可以实现更复杂的功能,适用于不同类型的共阴极和共阳极数码显示管驱动。

四、不同类型译码器的特点和应用不同类型的译码器在共阴极和共阳极数码显示管中有各自的特点和应用场景:1. BCD-7段译码器BCD-7段译码器具有简单、稳定的特点,适用于对数码显示管的基本显示功能。

它可以将二进制代码转换成相应数码显示管段的控制信号,实现数字和字符的显示,广泛应用于计数器、时钟、温度计等各种电子设备和仪器中。

THC63LVD827 Datasheet

IOVCC

G7

Power Power Supply Pin for IO inputs circuitry.

LVDSVCC

C5,D3

Power Power Supply Pins for LVDS Outputs.

PLLVCC

C7

Power Power Supply Pin for PLL circuitry.

The 2nd Link. LVDS OUT

The 2nd pixel output data when Dual out.

LVDS OUT LVDS Clock Out for 2nd Link.

IN

Pixel Data Inputs.

IN

Data Enable Input.

IN

Vsync Input.

1. Single in / Dual LVDS out

2. Single in / Single LVDS out

3. Double edge Single in / Dual LVDS out

• 2 LVDS data mapping to simplify PCB layout • Power down mode • Input clock triggering edge selectable by R/F pin • 6bit / 8bit modes selectable by 6B/8B pin

2/18

香港灏业科技 联系人:陈伟 手机:13510979382 QQ:744926516 地址:深圳市南山区高新南六道7B

THC63LVD827_Rev.1.00_E

Pin ription

Pin Name TA1+, TA1TB1+, TB1TC1+, TC1TD1+, TD1TCLK1+, TCLK1TA2+, TA2TB2+, TB2TC2+, TC2TD2+, TD2TCLK2+, TCLK2-

103方案的芯片功能

D103电子原理解说一.主板电路1.电源电路电源电路主要由电源芯片U23 HA13164A、U13 MPF1583组成。

U10 9435、Q24 8050为雷达、镜头供电。

D5 IN4148为CPU供电CPU-5V。

Q30 8050、Q8 2S1188为碟盒、IPOD供电CDC-ACC。

Q28 8050、Q7 2SB1188为外接功放供电AMP-C。

Q22 8050、Q23 8550为DVD9伏供电DVD-A9V。

Q9 8050、Q10 AO3401为收音天线放大器供电。

Q13 8050 Q5 AO3401为收音高频头供电EAC-ST7540AFIA 8V---9V。

Q21 8050、U4 LM317三端稳压器为风扇供电。

Q3 8550、D3 1N4148为蜂鸣器供电。

D11 BAV99倍压整流二极管为音频处理电路TDA7415供电+18V。

Q16 5551、Q6 2SB1188为高压板、倍压整流D11 BA V99、风扇供电U4 LM317供电12V-HG。

Q54 8050为倒车检测BACK。

Q55 5401为刹车检测BRAKE。

Q1 8050为静音控制MUTE。

Q19 8050为小灯控制ILL。

电源芯片HA13164A引脚功能说明:15-----GND 11-----SYS-P 2-----ANT-C8-------AMP-BATT 7 ------RADIO-P 4-----CPU-5V3-------ACC-IN 9 ------BATT-DET 5-----SYS-A5V6-----ACC-5V 10-----SYS-A9V 12-----SYS-8V 1-----TO---U10-RADAR-POWER 13-----ILM-ADJ14-----TO---Q7-AMP-C Q8-CDC-ACC电源芯片MP1583引脚功能说明:4-----GND 2-----BATT-O 7-----SYS-P 5-----FB6-----COMP 8-----SS 1-----BS3-----SW—OUT----GPS-5V、SYS-5V、经倍压输出18V。

THC63LVD823中文资料

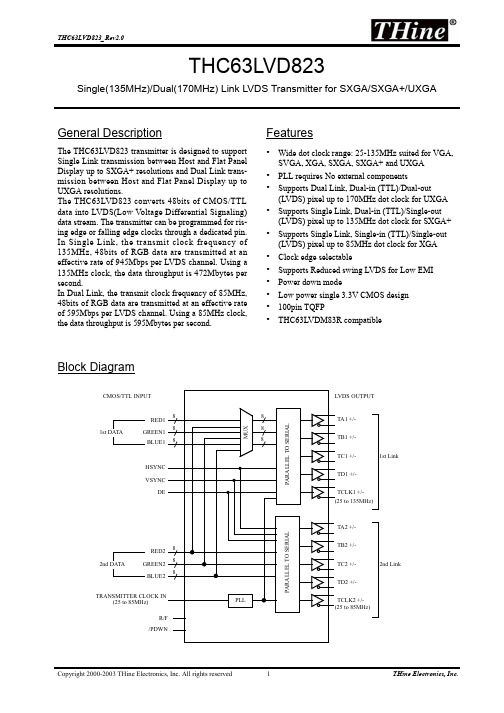

THC63LVD823Single(135MHz)/Dual(170MHz) Link LVDS Transmitter for SXGA/SXGA+/UXGAGeneral DescriptionThe THC63LVD823 transmitter is designed to support Single Link transmission between Host and Flat Panel Display up to SXGA+ resolutions and Dual Link trans-mission between Host and Flat Panel Display up to UXGA resolutions.The THC63LVD823 converts 48bits of CMOS/TTL data into LVDS(Low Voltage Differential Signaling)data stream. The transmitter can be programmed for ris-ing edge or falling edge clocks through a dedicated pin.In Single Link, the transmit clock frequency of 135MHz, 48bits of RGB data are transmitted at an effective rate of 945Mbps per LVDS channel. Using a 135MHz clock, the data throughput is 472Mbytes per second.In Dual Link, the transmit clock frequency of 85MHz,48bits of RGB data are transmitted at an effective rate of 595Mbps per LVDS channel. Using a 85MHz clock,the data throughput is 595Mbytes per second.Features•Wide dot clock range: 25-135MHz suited for VGA,SVGA, XGA, SXGA, SXGA+ and UXGA•PLL requires No external components•Supports Dual Link, Dual-in (TTL)/Dual-out(LVDS) pixel up to 170MHz dot clock for UXGA•Supports Single Link, Dual-in (TTL)/Single-out (LVDS) pixel up to 135MHz dot clock for SXGA+•Supports Single Link, Single-in (TTL)/Single-out (LVDS) pixel up to 85MHz dot clock for XGA •Clock edge selectable•Supports Reduced swing LVDS for Low EMI •Power down mode•Low power single 3.3V CMOS design •100pin TQFP•THC63LVDM83R compatibleBlock DiagramP A R A L L E L T O S E R I A LPLLTA1 +/-TB1 +/-TC1 +/-TD1 +/-TCLK1 +/-R/F /PDWN(25 to 135MHz)1st Link8RED1GREEN1BLUE1HSYNC VSYNCDERED2GREEN2BLUE2TRANSMITTER CLOCK IN(25 to 85MHz)1st DATA2nd DATACMOS/TTL INPUTP A R A L L E L T O S E R I A LTA2 +/-TB2 +/-TC2 +/-TD2 +/-TCLK2 +/-M U X88888888(25 to 85MHz)2nd LinkLVDS OUTPUTPin OutB15 B16 B17 R20 R21 R22 R23 R24 R25 R26 R27 VCC GND G20 G21 G22 G23 G24 G25 G26 G27 B20 B21 B22 B23767778798081828384858687888990919293949596979899100LVDS GNDTA1-TA1+TB1-TB1+LVDS VCCTC1-TC1+TCLK1-TCLK1+TD1-TD1+LVDS GNDTA2-TA2+TB2-TB2+LVDS VCCTC2-TC2+TCLK2-TCLK2+TD2-TD2+LVDS GND50494847464544434241403938373635343332313029282726 B24B25VCCGNDB26B27HSYNCVSYNCDECLKINR/FRSTEST1TEST2MODE1MODEOE6/8/PDWNTEST3TEST4TEST5PLLGNDPLLVCCPLLGND 123456789111121314151617181922122232425 B14B13B12GNDVCCB11B1G17G16G15G14G13G12G11G1R17R16R15R14GNDVCCR13R12R11R10 757473727176968676665646362616595857565554535251Pin DescriptionPin Name Pin #Type DescriptionTA1+, TA1-48, 49LVDS OUT The 1st Link. The 1st pixel output data when Dual Link.TB1+, TB1-46, 47LVDS OUT TC1+, TC1-43, 44LVDS OUT TD1+, TD1-39, 40LVDS OUT TCLK1+, TCLK1-41, 42LVDS OUT LVDS Clock Out for 1st Link.TA2+, TA2-36, 37LVDS OUT The 2nd Link. These pins are disabled when Single Link.TB2+, TB2-34, 35LVDS OUT TC2+, TC2-31, 32LVDS OUT TD2+, TD2-27, 28LVDS OUT TCLK2+, TCLK2-29, 30LVDS OUTLVDS Clock Out for 2nd Link.R17 ~ R1060, 59, 58, 57, 54, 53, 52, 51IN The 1st Pixel Data Inputs.G17 ~ G1068, 67, 66, 65, 64, 63, 62, 61IN B17 ~ B1078, 77, 76, 75, 74, 73, 70, 69IN R27 ~ R2086, 85, 84, 83, 82, 81, 80, 79IN The 2nd Pixel Data Inputs.G27 ~ G2096, 95, 94, 93, 92, 91, 90, 89IN B27 ~ B206, 5, 2, 1, 100, 99, 98, 97IN DE 9IN Data Enable Input.VSYNC 8IN Vsync Input.HSYNC 7IN Hsync Input.CLKIN 10IN Clock Input.TEST1, TEST513, 22OUT Test Pins.TEST3, TEST420, 21IN Test Pins, must be L for normal operation.TEST214IN Test Pins, must be H for normal operation./PDWN 19IN H: Normal operation,L: Power down (all outputs are Hi-Z)6/818IN 6bit/8bit color select.H: 6bit (TDx+/- are GND), L: 8bit.OE17INOutput enable.H: Output enable, L: Output disable (all outputs are Hi-Z)MODE1, MODE015, 16INRS 12INLVDS swing range select.H: Normal range, L: Reduced range.Pixel Data Mode.MODE1MODE0ModeL L Dual Link (Dual-in/Dual-out)L H Single Link (Dual-in/Single-out)HHSingle Link (Single-in/Single-out)Absolute Maximum Ratings 1Electrical Characteristics CMOS/TTL DC SpecificationsV CC = 3.0V ~ 3.6V , Ta = -10 ~ +70R/F 11IN Input Clock Triggering Edge Select.H: Rising edge, L: Falling edgeVCC 3, 55, 71, 87Power Power Supply Pins for TTL inputs, output and digital circuitry.GND 4, 56, 72, 88Ground Ground Pins for TTL inputs, outputs and digital circuitry.LVDS VCC 33, 45Power Power Supply Pins for LVDS Outputs.LVDS GND 26, 38, 50Ground Ground Pins for LVDS Outputs.PLL VCC 24Power Power Supply for PLL circuitry.PLL GND23, 25GroundGround Pin for PLL circuitry.Supply Voltage (V CC )-0.3V ~ +4.0V CMOS/TTL Input V oltage -0.3V ~ (V CC + 0.3V)CMOS/TTL Output Voltage -0.3V ~ (V CC + 0.3V)LVDS Driver Output Voltage -0.3V ~ (V CC + 0.3V)Output Current -30mA ~ 30mA Junction Temperature +125Storage Temperature Range -55 ~ +125Lead Temperature (Soldering, 4sec)+260Maximum Power Dissipation @+25 1.0W1.“Absolute Maximum Ratings” are those valued beyond which the safety of the device can not be guaranteed. They are not meant to imply that the device should be operated at these limits. The tables of “Electrical Characteristics” specify conditions for device operation.Symbol ParameterConditions Min.Typ.Max.Units V IH High Level Input Voltage 2.0V CC V V IL Low Level Input V oltage GND0.8V I INCInput CurrentµAPin Name Pin #Type Description°C°C °C °C °C°C °C0V V IN V CC≤≤10±LVDS Transmitter DC SpecificationsV CC = 3.0V ~ 3.6V , Ta = -10 ~ +70Supply CurrentV CC = 3.0V ~ 3.6V , Ta = -10 ~ +70(*) VESA is a trademark of the Video Electronics Standards Association.SymbolParameterConditionsMin.Typ.Max.Units VOD Differential Output Voltage RL=100ΩNormal swing 250350450mV Reduced swing100200300mV ∆VOD Change in VOD between complementary output states RL=100Ω35mV VOC Common Mode Voltage 1.1251.251.375V ∆VOC Change in VOC between complementary output states 35mV I OS Output Short Circuit Current VOUT=0V , RL=100Ω-24mA I OZOutput TRI-State current/PDWN=0V , VOUT=0V to VCCµASymbolParameterCondition(*)Typ.Max.UnitsI TCCGTransmitter SupplyCurrent(256 Gray Scale Pattern)VESA SXGA ( 60Hz )CLKIN=54MHzMODE<1:0>=LH RL=100Ω,CL=5pF VCC=3.3V 5058mAVESA UXGA ( 60Hz )CLKIN=81MHz MODE<1:0>=LL RL=100Ω,CL=5pF VCC=3.3V 7889mAI TCCWTransmitter SupplyCurrent(Double Checker Pattern)VESA SXGA ( 60Hz )CLKIN=54MHz MODE<1:0>=LH RL=100Ω,CL=5pF VCC=3.3V 5361mAVESA UXGA ( 60Hz )CLKIN=81MHzMODE<1:0>=LL RL=100Ω,CL=5pF VCC=3.38699mAI TCCSTransmitter Power Down Supply Current/PDWN = L 10µA°C °C°C °C10±256 Gray Scale PatternCLKINRx0/Gx0/Bx0Rx1/Gx1/Bx1Rx2/Gx2/Bx2Rx3/Gx3/Bx3Rx4/Gx4/Bx4Rx5/Gx5/Bx5Rx6/Gx6/Bx6Rx7/Gx7/Bx7x=1,2DEDouble Checker Pattern CLKINR1n/G1n/B1nR2n/G2n/B2nn=0~7DESwitching CharacteristicsV CC = 3.0V ~ 3.6V, Ta = -10 ~ +70 Symbol Parameter Min.Typ.Max.Units t TCIT CLK IN Transition time 5.0ns t TCIP CLK IN Period11.7640.0ns t TCH CLK IN High Time0.35t TCIP0.5t TCIP0.65t TCIP ns t TCL CLK IN Low Time0.35t TCIP0.5t TCIP0.65t TCIP ns t TS TTL Data Setup to CLK IN 2.5ns t TH TTL Data Hold from CKL IN0.0nst TCOP CLK OUT PeriodDual Link11.7640.0ns Single Link7.420.0nst LVT LVDS Transition Time0.5ns t TOP1Output Data Position0 (t TCOP = 7.4ns)-0.150.0+0.15nst TOP0Output Data Position1 (t TCOP = 7.4ns)ns t TOP6Output Data Position2 (t TCOP = 7.4ns)ns t TOP5Output Data Position3 (t TCOP = 7.4ns)ns t TOP4Output Data Position4 (t TCOP = 7.4ns)ns t TOP3Output Data Position5 (t TCOP = 7.4ns)ns t TOP2Output Data Position6 (t TCOP = 7.4ns)nst TPLL Phase Lock Loop Set10.0ms t OE OE High to Data Valid50nst CK12Skew Time between TCLK1+ and TCLK2+0.5ns°C°Ct TCOP7--------------0.15–t TCOP7--------------t TCOP7--------------0.15+2t TCOP7--------------0.15–2t TCOP7--------------2t TCOP7--------------0.15+3t TCOP7--------------0.15–3t TCOP7--------------3t TCOP7--------------0.15+4t TCOP7--------------0.15–4t TCOP7--------------4t TCOP7--------------0.15+5t TCOP7--------------0.15–5t TCOP7--------------5t TCOP7--------------0.15+6t TCOP7--------------0.15–6t TCOP7--------------6t TCOP7--------------0.15+AC Timing Diagrams TTL Input5pF20%80%20%80%t LVT t LVTCLK INLVDS Output90%10%90%10%t TCIT t TCITV diff100ΩV diff=(TA+)-(TA-) TA+TA-LVDS Output LoadAC Timing Diagrams TTL InputsR/F = LR/F = HCLK INRxn GxnBxnn = 0~7Phase Lock Loop Set TimeVCC3.0V2.0Vt TPLLCLKIN/PDWNTCLKx+/-V diff =0VHsync Vsync DEPower Up Sequence3.0VPDVCCGNDVCCGNDVCC PVCC LVCCGNDPD pin must be High after VCC voltage is 3.0V .1)Sequence1VCC/2PDVCCGNDt PDVCC/2VCCGNDVCC PVCC LVCCt PW1) t PW < 10msec 2) t PD > t PW2)Sequence2Power Up Sequence must be Sequence1 or Sequence2.V diff = 0V Tyx+/-AC Timing Diagrams LVDS OutputsTyx6Tyx5Tyx4Tyx3Tyx2Tyx1Tyx0Tyx6Tyx5Tyx4Tyx3Tyx2Tyx1V diff = 0Vt TOP2t TOP3t TOP4t TOP5t TOP6t TOP0t TOP1t TCOPTCLKx+x = 1,2y = A,B,C,DV diff = 0Vt CK12TCLK1+V diff = 0VTCLK2+Note:V diff = (Tyx+) - (Tyx-) , (TCLKx+) - (TCLKx-)Pixel Map Table for Single/Dual LinkTFT Panel DataLSB 24Bit18Bit823 TTL Input Pin 1st Pixel DataR10-MSB R11R12R13R14R15R16R17-R10R11R12R13R14R15LSBMSB G11G12G13G14G15G16G17-G10G11G12G13G14G15 G10-LSBMSB B11B12B13B14B15B16B17-B10B11B12B13B14B15B10-R10R11R12R13R14R15R16R17G11G12G13G14G15G16G17G10B11B12B13B14B15B16B17B10TFT Panel DataLSB24Bit18Bit823 TTL Input Pin2nd Pixel DataR20-MSBR21R22R23R24R25R26R27-R20R21R22R23R24R25LSBMSBG21G22G23G24G25G26G27-G20G21G22G23G24G25G20-LSBMSBB21B22B23B24B25B26B27-B20B21B22B23B24B25B20-R20R21R22R23R24R25R26R27G21G22G23G24G25G26G27G20B21B22B23B24B25B26B27B20TTL Data Inputs Timing Diagrams in Dual Link TA1+/-R16’R15’R14’R13’R12’G12R17R16R15R14R13R12G12’’TB1+/-G17’G16’G15’G14’G13’B13B12G17G16G15G14G13B13’’TC1+/-HSYNC’B17’B16’B15’B14’DEVSYNC HSYNCB17B16B15B14DE’’TD1+/-B10’G11’G10’R11’R10’L B11B10G11G10R11R10L’’TA2+/-R26’R25’R24’R23’R22’G22R27R26R25R24R23R22G22’’TB2+/-G27’G26’G25’G24’G23’B23B22G27G26G25G24G23B23’’TC2+/-B27’B26’B25’B24’B27B26B25B24TD2+/-B20’G21’G20’R21’R20’L B21B20G21G20R21R20L’’TCLK1+TCLK2+(Dual-in / Dual-out Mode)Previous Cycle Current CycleHSYNC’DEVSYNC HSYNCDE’’TTL Data Inputs Timing Diagrams in Single Link(Dual-in / Single-out Mode)Previous Cycle Current Cycle(2nd Pixel Data)(1st Pixel Data)TCLK1+TA1+/-R26’R25’R24’R23’R22’G12R17R16R15R14R13R12G22’’TB1+/-G27’G26’G25’G24’G23’B13B12G17G16G15G14G13B23’’TC1+/-HSYNC’B27’B26’B25’B24’DE VSYNC HSYNC B17B16B15B14DE’’TD1+/-B20’G21’G20’R21’R20’L B11B10G11G10R11R10L’’Package1.2M A XUNIT:mm1.00T Y PNotes to Users:1.The contents of this data sheet are subject to change without prior notice.2.Circuit diagrams shown in this data sheet are examples of application. Therefore, please pay sufficient attentionwhen designing circuits. Even if there are incorrect descriptions, we are not responsible for any problem due to them. Please note that incorrect descriptions sometimes cannot be corrected immediately if found.3.Our copyright and know-how are included in this data sheet. Duplication of the data sheet and disclosure to otherpersons are strictly prohibited without our permission.4.We are not responsible for any problems of industrial proprietorship occurring during THC63LVD823 use, exceptfor those directly related to THC63LVD823’s structure, manufacture or functions. THC63LVD823 is designed on the premise that it should be used for ordinary electronic devices. Therefore, it shall not be used for applications that require extremely high-reliability (space equipment, nuclear control equipment, medical equipment that affects peo-ple’s lives, etc.). In addition, when using THC63LVD823 for traffic signals, safety devices and control/safety units in transportation equipment, etc., appropriate measures should be taken.5.We are making the utmost effort to improve the quality and reliability of our products. However, there is a veryslight possibility of failure in semiconductor devices. To avoid damage to social or official organizations, much care should be taken to provide sufficient redundancy and fail-safe design.6.No radiation-hardened design is incorporated in THC63LVD823.7.Judgment on whether THC63LVD823 comes under strategic products prescribed by the Foreign Exchange and For-eign Trade Control Law is the user’s responsibility.8.This technical document was provisionally created during development of THC63LVD823, so there is a possibilityof differences between it and the product’s final specifications. When designing circuits using THC63LVD823, be sure to refer to the final technical documents.THine Electronics, Inc.Wakamatsu Bldg, 6F3-3-6, Nihombashi-Honcho,Chuo-ku, Tokyo, 103-0023 JapanTel: 81-3-3270-0666Fax: 81-3-3270-0688。

海信TPW5588等离子彩电维修手册

等离子电视维修手册――TPW4288/TPW5011H/TPW5588 一、产品介绍:(一)性能规格介绍:1、TPW4288:序号 性能 指标1 屏幕宽高比 16:92 物理分辨率 1366×7683 视角 大于160度4 峰值亮度 1000cd/m25 暗室对比度 5000:16 色坐标 X=0.285±0.03,Y=0.290±0.037 可显示高清信号格式 1080i/60Hz,720P/60Hz,1080i/50Hz,720P/50Hz,1080P/60Hz,1080P/50Hz8 射频接收 PAL BG/DK/I9 其它接口 VIDEO/S-VIDEO/VGA/HDMI10 特色功能 画中画(ALPHA BLENDING)、双视窗、图形OSD11 输入电压 交流100V到240V(50/60Hz)12 待机功率 <2W13 额定功率 500W2、TPW-5011H:序号性能 指标1 屏幕宽高比 16:92 物理分辨率 852×4803 视角 大于160度4 峰值亮度 1200cd/m25 暗室对比度 4000:16 色坐标 X=0.285±0.03,Y=0.290±0.037 可显示高清信号格式 1080i/60Hz,720P/60Hz,1080i/50Hz,720P/50Hz,1080P/60Hz,1080P/50Hz8 射频接收 PAL BG/DK/I9 其它接口 VIDEO/S-VIDEO/VGA/HDMI10 特色功能 画中画(ALPHA BLENDING)、双视窗、图形OSD11 输入电压 交流100V到240V(50/60Hz)12 待机功率 <2W13 额定功率 320W3、TPW5588:序号 性能 指标1 屏幕宽高比 16:92 物理分辨率 1366×7683 视角 大于160度4 峰值亮度 1000cd/m25 暗室对比度 2000:16 色坐标 X=0.285±0.03,Y=0.290±0.037可显示高清信号格式 1080i/60Hz,720P/60Hz,1080i/50Hz,720P/50Hz,1080P/60Hz,1080P/50Hz8 射频接收 PAL BG/DK/I9 其它接口 VIDEO/S-VIDEO/VGA/HDMI10 特色功能 画中画(ALPHA BLENDING)、双视窗、图形OSD11 输入电压 交流100V到240V(50/60Hz)12 待机功率 <2W13 额定功率 450W(二)外观及功能特点介绍:1、机型外观:TPW4288的外观(因图片质量,图片仅供参考)TPW5011H的外观(因图片质量,图片仅供参考)TPW5588的外观(因图片质量,图片仅供参考)2、功能特点:● 兼容10bit/8bit处理显示,实现真正的1080i到1080P的去隔行变换;● 运动自适应处理和新型小角度插补算法,减轻斜线锯齿;● 3:2和2:2电影模式,支持1080i,NTSC and PAL;● DCTI、DLTI等画质增强处理,黑白电平扩展;● 3D梳状滤波器,提高画质;● 256色图形化OSD;● 智能多窗口画面,射频画中画,PIP ALPHA BLENDING效果;● 支持HDMI输入;● 支持双路TV、双路VIDEO、双路S-VIDEO信号输入;● 支持双路高清色差信号输入;● 支持双USB数字媒体播放器功能;● SRS WOW音效。

THC63LVDM63R中文资料

Ground Pins for TTL inputs and digital circuitry.

Power Supply Pins for LVDS Outputs. Ground Pins for LVDS Outputs. Power Supply Pin for PLL circuitry. Ground Pins for PLL circuitry.

LVDS Channel)

LVDS Channel)

TRANSMITTER

TCLK +/-

CLOCK IN

PLL

TCLK +/-

CLOCK (LVDS)

(20 to 85MHz) R/F

CLOCK (LVDS)

20-85MHz

/PDWN

20-85MHz

RS

Copyright 2001-2003 THine Electronics, Inc. All rights reserved

TA4 RS

1TB1 VCC

TB2 TB3 GND TB4

3 4 5 6 7 8 9 10 11 12

TB5 13

R/F 14

TB6 TC0 GND TC1 TC2 TC3 VCC TC4

15 16 17 18 19 20 21 22

TC5 GND

23 24

48 47 46 45 44 43

VCC

CLKIN GND LVDS VCC LVDS GND PLL VCC PLL GND

Pin #

14

8, 21

26 5, 11, 17, 24, 46

37 36, 42

29 28, 30

Type

IN

创维液晶电视各机芯维修讲解手册

手头无资料,试代换存储器24C32 后,长

时间老化机器正常

20L98TV/8K60 TV 图像拖尾,AV 正常 AV 图像正常,说明故障出现在中放电

路,试代换TDA9886TS,380W38-02,故

障依旧.怀疑声表面K7262 坏,换之正常

19L11IW/8K60 搜不到台 首先查高频头的供电,发现没33V 调

其实的上门的过程中碰到此类问题不

妨先检查一下续流二极管,是否击穿。

32L16SW/8TTK 刚开机无图,菜单出不来. 更换24C432

32L16SW/8TTK 不定时出现有声无图像现象 根据故障现象,发现主板连接到屏的插

排(靠近屏的一端)有松动,用一薄纸

垫在插排的下方,使插排接触可靠后恢

电及其外围电路均正常,怀疑是高频头

本身性能不良引起 ,换之故障排除

(5200-380651-22)。

32L88IW/8TT3 七彩屏 因为TV 字符是在V12 里产生的,VGA

字符是在缩放TSU66AJW1 里产生的,

用8TT9 的遥控按VGA,此操作是在

无字符下进行的。VGA 字符正常,证

严重发热,断开U3 测负载无短路现象,

更换U3 后工作正常。

22LEATV/8TT6 TV 无图有点暗影 用AV 试机正常,检查TV 通道与切换

电路,都正常,进入总线后RESET 后

机器正常。

20LBATV/8TG3 无台,AV闪一下 当故障出现时输入VGA 信号显示正

常,怀疑VPC3230 不良换新后故障依

发现C305 有点变黄,拆下发现该电容

已严重短路,于是找来一只50V10UF

第三十四节 THC63LVD103135MHz30比特彩色LVDS传送器

THC63LVD103135MHz30比特彩色LVDS传送器

一、简介

THC63LVD103传送器设计于支持在主机与平板显示器间的像素数据传输,分辨率介于NTSC 至XSGA+之间。

THC63LVD103转换35比特的CMOS/TTL数据为LVDS数据流,通过指定的脚位它能为上升沿和下降沿时钟进行编程,在一个135MHz时钟频率里,30比特RGB数据和5比特时序和控制数据被转换成一个每通道945Mbps有效率的LVDS信号。

二、特点

1、宽点频范围:8~135MHz适于NTSC、VGA、SVGA、XGA、SXGA和SXGA+

2、PLL环路无需外部元件

3、支持展布频谱时钟发生器

4、单芯片抖动滤波

5、时钟沿可选择

6、支持低摆幅的LVDS以降低电磁干扰

7、电源跌落模式,单电源3.3V CMOS设计

8、64脚TQFP封装

9、向后兼容THC63LVDM63R/THC63LVDM83R

三、框图

四、脚功能。

thc63lvd103c原理

thc63lvd103c原理一、概述THC63LVD103C是一种高性能的电流检测芯片,广泛应用于电源、电子设备、马达控制等领域。

该芯片通过检测电流信号,可以实现对电路中电流的精确测量和控制,从而提高系统的稳定性和效率。

二、工作原理1. 电流检测:THC63LVD103C通过精密电阻采样电流信号,将其转换为电压信号,然后通过芯片内部的放大器和滤波器进行处理。

2. 信号处理:芯片内部集成有高性能的放大器和滤波器,可以对采样到的电流信号进行放大和滤波,消除干扰信号的影响,提高测量精度。

3. 输出信号:处理后的电流信号通过芯片的数字输出接口,以数字信号的形式输出,方便与微处理器或控制器进行通信和控制。

三、应用电路1. 电源电路:在电源电路中,THC63LVD103C可以用于检测输出电流,从而实现对输出电压的稳定控制。

2. 电子设备:在电子设备中,THC63LVD103C可以用于马达驱动、电源管理等电路中,实现对电路中电流的精确控制和保护。

3. 马达控制:在马达控制中,THC63LVD103C可以用于检测马达的电流信号,从而实现对马达转速和转向的控制。

四、注意事项1. 采样电阻的选择:根据实际应用场合的需求,选择合适的精密采样电阻,以确保采样信号的准确性和稳定性。

2. 电源干扰:在应用电路中,应采取适当的屏蔽和滤波措施,以防止电源干扰对芯片的影响。

3. 温度特性:THC63LVD103C具有较好的温度特性,但在高温环境下使用时,应采取适当的散热措施,以保证芯片的正常工作。

五、总结THC63LVD103C是一种高性能的电流检测芯片,通过精确检测电流信号,实现对电路中电流的精确控制和保护。

该芯片广泛应用于电源、电子设备、马达控制等领域,具有较高的实用价值。

在实际应用中,应选择合适的采样电阻,采取适当的屏蔽和滤波措施,以保证芯片的正常工作。

thc63lvdm83d应用案例

THC63LVDM83D 应用案例THC63LVDM83D 是一款用于高速数据传输的 LVDS 驱动器芯片,适用于工业控制、汽车电子、医疗设备等领域。

它具有低功耗、高可靠性、高速传输等优点,因此在各个领域都有广泛的应用。

以下是几个THC63LVDM83D 在不同领域的应用案例:1. 工业控制领域在工业控制领域,THC63LVDM83D 可以用于自动化设备、PLC 控制系统、工业通讯等各种场合。

由于工业环境对设备稳定性和抗干扰能力要求较高,THC63LVDM83D 的高可靠性和抗干扰能力使其成为了这些设备的理想选择。

该芯片的高速传输能力也能满足工业控制领域对数据传输速度的需求,确保设备能够及时准确地获取和处理数据,提高生产效率和质量。

2. 汽车电子领域在汽车电子领域,THC63LVDM83D 可以用于汽车信息娱乐系统、车载摄像头、车载监控系统等应用。

汽车作为移动的载体,对电子设备的可靠性和稳定性要求更高,而且在汽车行驶过程中会受到更多的振动和温度变化,因此要求芯片具有更高的抗干扰能力和工作稳定性。

THC63LVDM83D 符合汽车电子领域的这些要求,并且其高速传输能力也可以满足对数据传输速度的需求。

3. 医疗设备领域在医疗设备领域,THC63LVDM83D 可以用于医疗影像设备、医疗监护系统、医疗诊断设备等应用。

医疗设备对设备的稳定性和数据传输的准确性要求极高,因为一旦出现故障可能会对患者的生命造成影响。

THC63LVDM83D 的高可靠性和高速传输能力可以保证医疗设备的稳定工作和准确数据传输,为医疗工作提供可靠的技术支持。

THC63LVDM83D 是一款在工业控制、汽车电子、医疗设备等领域都有广泛应用的 LVDS 驱动器芯片。

它的低功耗、高可靠性和高速传输能力使其成为了各种应用场合的理想选择,为各个行业的发展提供了强大的技术支持。

相信随着技术的不断进步,THC63LVDM83D 在更多领域会有更广泛的应用。

LVDS驱动芯片

MS90C385SN75LVDS83十通道LVDS发送芯片DS90C365说明:4通道LVDS发送芯片主要用于驱动6bit液晶面板。

使用四通道LVDS发送芯片可以构成单路6bit LVDS接自电路和奇/偶双路6bit LVDS接口电路。

五通道LVDS发送芯片DS90C385十通道LVDS发送芯片DS90C3871.LVDS输出接口概述液晶显示器驱动板输出的数字信号中,除了包括RGB数据信号外,还包括行同步、场同步、像素时钟等信号,其中像素时钟信号的最高频率可超过28MHz。

采用TTL接口,数据传输速率不高,传输距离较短,且抗电磁干扰(EMI)能力也比较差,会对RGB数据造成一定的影响;另外,TTL多路数据信号采用排线的方式来传送,整个排线数量达几十路,不但连接不便,而且不适合超薄化的趋势。

采用LVDS输出接口传输数据,可以使这些问题迎刃而解,实现数据的高速率、低噪声、远距离、高准确度的传输。

那么,什么是LVDS输出接口呢?LVDS,即Low Voltage Differential Signaling,是一种低压差分信号技术接口。

它是美国NS公司(美国国家半导体公司)为克服以TTL电平方式传输宽带高码率数据时功耗大、EMI电磁干扰大等缺点而研制的一种数字视频信号传输方式。

LVDS输出接口利用非常低的电压摆幅(约350mV)在两条PCB走线或一对平衡电缆上通过差分进行数据的传输,即低压差分信号传输。

采用LVDS输出接口,可以使得信号在差分PCB线或平衡电缆上以几百Mbit/s的速率传输,由于采用低压和低电流驱动方式,因此,实现了低噪声和低功耗。

目前,LVDS输出接口在17in及以上液晶显示器中得到了广泛的应用。

2.LVDS接口电路的组成在液晶显示器中,LVDS接口电路包括两部分,即驱动板侧的LVDS输出接口电路(LVDS 发送器)和液晶面板侧的LVDS输入接口电路(LVDS接收器)。

LVDS发送器将驱动板主控芯片输出的17L电平并行RGB数据信号和控制信号转换成低电压串行LVDS信号,然后通过驱动板与液晶面板之间的柔性电缆(排线)将信号传送到液晶面板侧的LVDS接收器,LVDS接收器再将串行信号转换为TTL电平的并行信号,送往液晶屏时序控制与行列驱动电路。

thc63lvdm83d应用案例

thc63lvdm83d应用案例THC63LVDm83D应用案例1. 工业自动化:THC63LVDm83D可应用于工业自动化领域,例如控制机器人、传感器、电机等设备。

它提供可靠的数据传输和通信功能,确保设备之间的协调运行,提高生产效率。

2. 交通运输:THC63LVDm83D可用于车辆系统中,如车载摄像头、雷达、导航系统等。

它可以传输高质量的视频和数据信号,帮助驾驶员实时监测路况和行驶安全。

3. 医疗设备:THC63LVDm83D在医疗设备中的应用非常广泛,如超声诊断系统、激光治疗设备等。

它可提供高速、稳定的数据传输,确保医疗设备的准确性和可靠性。

4. 军事通信:THC63LVDm83D可应用于军事通信系统,如无人机、战术通信设备等。

它能够在恶劣环境下提供可靠的数据传输,确保军事行动的顺利进行。

5. 家庭娱乐:THC63LVDm83D可用于家庭娱乐系统,如高清电视、音频设备等。

它提供高质量的图像和音频传输,提升用户的观影和听音体验。

6. 智能家居:THC63LVDm83D可用于智能家居系统中的各种设备,如智能灯具、智能门锁等。

它可以稳定传输控制命令和状态信息,实现智能家居设备的互联互通。

7. 航空航天:THC63LVDm83D可应用于航空航天系统中的各种设备,如飞行控制系统、导航系统等。

它提供高速、可靠的数据传输,确保航空航天设备的安全性和可靠性。

8. 电信设备:THC63LVDm83D可用于电信设备中的数据传输和通信连接,如光纤通信设备、宽带路由器等。

它能够提供高速、稳定的数据传输,满足用户对于高速互联网的需求。

9. 电力系统:THC63LVDm83D可应用于电力系统中的各种设备,如电力监测装置、电网自动化设备等。

它能够传输大量的电力数据和控制信号,实现电力系统的智能化管理。

10. 教育领域:THC63LVDm83D可用于教育领域的各种设备,如智能白板、教育机器人等。

它提供高质量的图像和数据传输,帮助教育工作者实现更好的教学效果。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Copyright 2001-2006 THine Electronics, Inc. All rights reserved.

4

THine Electronics, Inc.

THC63LVD103 _Rev2.2

Electrical Characteristics CMOS/TTL DC Specifications

TD5 GND TD6 TE0 TE1 TE2 VCC TE3 TE4 GND TE5 CLK IN /PDWN PLL GND PLL VCC TE6

2

THine Electronics, Inc.

THC63LVD103 _Rev2.2

Pin Description

Pin Name TA+, TATB+, TBTC+, TCTD+, TDTE+,TETCLK+, TCLKTA0 ~ TA6 TB0 ~ TB6 TC0 ~ TC6 TD0 ~ TD6 TE0 ~ TE6 /PDWN Pin # 30, 31 28, 29 24, 25 20, 21 18, 19 22, 23 33,34,35,36,37,38,40 41,42,44,45,46,48,49 50,52,53,54,55,57,58 59,61,62,63,64,1,3 Type LVDS OUT LVDS OUT LVDS OUT LVDS OUT LVDS OUT LVDS OUT IN IN IN IN Pixel Data Inputs. LVDS Clock Out. LVDS Data Out. Description

VCC = 3.0V ~ 3.6V, Ta = 0 ° C ~ +70 ° C Symbol VIH VIL VDDQ1 VREF VSH2 VSL2 IINC Parameter High Level Input Voltage Low Level Input Voltage Small Swing Voltage Input Reference Voltage Small Swing High Level Input Voltage Small Swing Low Level Input Voltage Input Current Small Swing (RS=VDDQ/2) VREF = VDDQ/2 VREF = VDDQ/2

PLL

TCLK +/(8 to 135MHz)

Copyright 2001-2006 THine Electronics, Inc. All rights reserved.

1

THine Electronics, Inc.

THC63LVD103 _Rev2.2

Pin Out

TB6 TC0 VCC TC1 TC2 TC3 TC4 GND TC5 TC6 TD0 R/F TD1 TD2 TD3 TD4

49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17

RS VCC

RS

43

IN

0.6 ~ 1.4V GND

a. VREF is Input Reference Voltage.

R/F VCC CLKIN GND LVDS VCC LVDS GND PLL VCC PLL GND

60 51, 7 12 2, 10, 39, 47, 56 27 17, 26, 32 15 14

TB5 GND TB4 TB3 TB2 RS TB1 TB0 TA6 GND TA5 TA4 TA3 TA2 TA1 TA0

LVDS GND TATA+ TBTB+ LVDS VCC LVDS GND TCTC+ TCLKTCLK+ TDTD+ TETE+ LVDS GND

Copyright 2001-2006 THine Electronics, Inc. All rights reserved.

4,5,6,8,9,11,16

13

IN

IN H: Normal operation, L: Power down (all outputs are Hi-Z) LVDS swing mode, VREF select.

LVDS Swing 350mV 350mV 200mV Small Swing Input Support N/A RS=VREFa N/A

1. “Absolute Maximum Ratings” are those valued beyond which the safety of the device can not be guaranteed. They are not meant to imply that the device should be operated at these limits. The tables of “Electrical Characteristics” specify conditions for device operation.

Features

• Wide dot clock range: 8-135MHz suited for NTSC,

VGA, SVGA, XGA,SXGA and SXGA+

• • • • • • • • •

PLL requires no external components Supports spread spectrum clock generator On chip jitter filtering Clock edge selectable Supports reduced swing LVDS for low EMI Power down mode Low power single 3.3V CMOS design 64pin TQFP Backward compatible with THC63LVDM63R(18bits) / M83R(24bits)

IN Power IN Ground Power Ground Power Ground

Input Clock Triggering Edge Select. H: Rising edge, L: Falling edge Power Supply Pins for TTL inputs and digital circuitry. Clock in. Ground Pins for TTL inputs and digital circuitry. Power Supply Pins for LVDS Outputs. Ground Pins for LVDS Outputs. Power Supply Pin for PLL circuitry. Ground Pins for PLL circuitry.

0V ≤ V IN ≤ V CC

Conditions RS=VCC or GND RS=VCC or GND

Min. 2.0 GND 1.2

Typ.

Max. VCC 0.8 2.8

Units V V V

VDDQ/2 VDDQ/2 +100mV VDDQ/2 -100mV

± 10

V V μA

Notes: 1VDDQ voltage defines max voltage of small swing input. It is not an actual input voltage. 2 Small swing signal is applied to TA[6:0], TB[6:0], TC[6:0], TD[6:0], TE[6:0] and CLKIN.

THC63LVD103 _Rev2.2

THC63LVD103

135MHz 30Bits COLOR LVDS Transmitter

General Description

The THC63LVD103 transmitter is designed to support pixel data transmission between Host and Flat Panel Display from NTSC up to SXGA+ resolutions. The THC63LVD103 converts 35bits of CMOS/TTL data into LVDS(Low Voltage Differential Signaling) data stream. The transmitter can be programmed for rising edge or falling edge clocks through a dedicated pin. At a transmit clock frequency of 135MHz, 30bits of RGB data and 5bits of timing and control data (HSYNC, VSYNC, DE, CNTL1, CNTL2) are transmitted at an effective rate of 945Mbps per LVDS channel.

Block Diagram

CMOS/TTL INPUT

TA0-6 TB0-6 7 7 7

LVDS OUTPUT

TA +/TB +/TC +/TD +/TE +/-

TC0-6

TD0-6 TE0-6

7 7

PARALLEL TO SERIAL