epc管脚

EPCQCN引脚原理图

E P C Q C N引脚原理图Document serial number【UU89WT-UU98YT-UU8CB-UUUT-UUT108】SOPC开发模块原理图对应引脚分类 EP3C40Q240C8N 1.时钟2.LED和按键3. port——外接试验箱端口4. SAA7113HSAA7113是一种视频解码芯片,它可以输入4路模拟视频信号,通过内部寄存器的不同配置可以对4路输入进行转换,输入可以为4路CVBS或2路S视频(Y/C)信号,输出8位“VPO”总线,为标准的ITU 656、YUV 4:2:2格式。

7113兼容PAL、NTSC、SECAM多种制式,可以自动检测场频适用的50或60Hz,可以在PAL、NTSC之间自动切换。

7113内部具有一系列寄存器,可以配置为不同的参数,对色度、亮度等的控制都是通过对相应寄存器改写不同的值,寄存器的读写需要通过I2C总线进行。

7113的模拟与数字部分均采用+供电,数字I/O接口可兼容+5V,正常工作时功耗, 空闲时为。

7113需外接晶体,内部具有锁相环(LLC),可输出27MHz的系统时钟。

芯片具有上电自动复位功能,另有外部复位管脚(CE),低电平复位,复位以后输出总线变为三态,待复位信号变高后自动恢复,时钟丢失、电源电压降低都会引起芯片的自动复位。

7113为QFP44封装。

5.ADV7123——视频数模转换器ADV7123 (ADV?)是一款单芯片、三通道、高速数模转换器,内置三个高速、10位、带互补输出的视频数模转换器、一个标准TTL输入接口以及一个高阻抗、模拟输出电流源。

6. CH372——总线通用接口芯片7. Wm8731-编码解码器8. XPT2046——触摸屏控制器9. EPCS16-闪存10. FPGA所有bank引脚:。

简述epc编码规则

简述epc编码规则

EPC编码是一种用于标识物品和产品的全球唯一编码系统。

它由国际电子技术协会(GS1)制定,并被广泛应用于全球供应链管理和物流领域。

EPC编码规则基于电子产品代码(Electronic Product Code,简称EPC)标准,并使用数字表示不同的信息。

EPC编码一般由四个部分组成:企业前缀、物品参考号、序列号和校验位。

首先是企业前缀,它由GS1颁发给各个企业的唯一标识码组成,用于区分不同企业的编码。

企业前缀通常长度为7到10位数字,根据企业级别和需求的不同而有所变化。

接下来是物品参考号,它是企业根据自身需求对不同物品进行编码的部分。

物品参考号长度可以根据实际需要进行调整,一般为1到13位数字或字母的组合。

第三部分是序列号,它用于标识具体物品的唯一序号。

序列号的长度通常为1到20位数字,可以根据需要设定,在同一企业内必须保证唯一性。

最后是校验位,用于验证EPC编码的准确性。

校验位算法会根据前面三部分的数据计算得出,以确保编码的正确性和完整性。

通过这种编码规则,EPC可以实现对物品进行精确追踪和管理。

无论是在物流配送、库存管理还是零售环节,EPC编码都能够提高效率、减少错误,并为企业提供准确的数据支持。

总结而言,EPC编码规则是一种全球唯一的编码系统,由企业前缀、物品参考号、序列号和校验位组成。

它在供应链管理和物流领域发挥着重要作用,为企业提供了准确的物品追踪和管理手段。

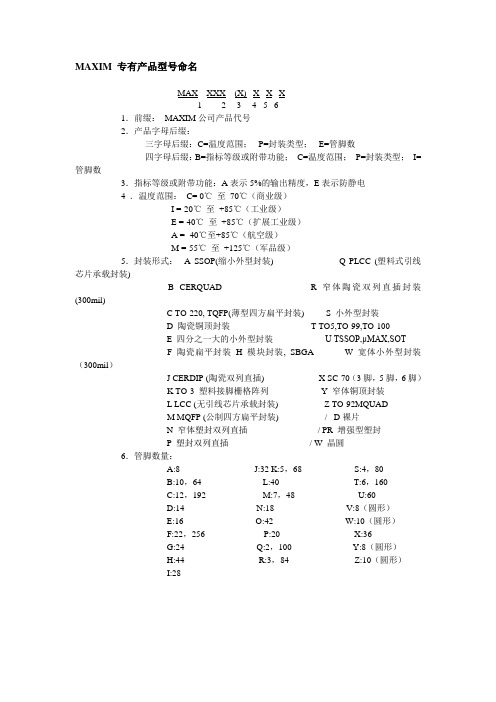

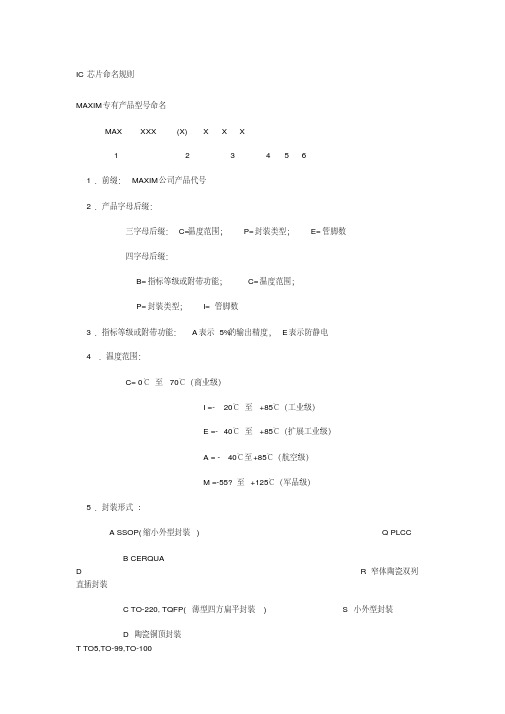

国外IC芯片命名规则

MAXIM专有产品型号命名MAX XXX (X) X X X1 2 3 4 5 61.前缀:MAXIM公司产品代号2.产品字母后缀:三字母后缀:C=温度范围;P=封装类型;E=管脚数四字母后缀:B=指标等级或附带功能;C=温度范围;P=封装类型;I=管脚数3.指标等级或附带功能:A表示5%的输出精度,E表示防静电4 .温度范围:C= 0℃至70℃(商业级)I =-20℃至+85℃(工业级)E =-40℃至+85℃(扩展工业级)A = -40℃至+85℃(航空级)M =-55℃至+125℃(军品级)5.封装形式: A SSOP(缩小外型封装) Q PLCC (塑料式引线芯片承载封装)B CERQUAD R 窄体陶瓷双列直插封装(300mil)C TO-220, TQFP(薄型四方扁平封装) S 小外型封装D 陶瓷铜顶封装T TO5,TO-99,TO-100E 四分之一大的小外型封装U TSSOP,μMAX,SOTF 陶瓷扁平封装H 模块封装, SBGA W 宽体小外型封装(300mil)J CERDIP (陶瓷双列直插) X SC-70(3脚,5脚,6脚)K TO-3 塑料接脚栅格阵列Y 窄体铜顶封装L LCC (无引线芯片承载封装) Z TO-92MQUADM MQFP (公制四方扁平封装) / D裸片N 窄体塑封双列直插/ PR 增强型塑封P 塑封双列直插/ W 晶圆6.管脚数量:A:8 J:32 K:5,68 S:4,80B:10,64 L:40 T:6,160C:12,192 M:7,48 U:60D:14 N:18 V:8(圆形)E:16 O:42 W:10(圆形)F:22,256 P:20 X:36G:24 Q:2,100 Y:8(圆形)H:44 R:3,84 Z:10(圆形)I:28AD常用产品型号命名单块和混合集成电路XX XX XX X X X1 2 3 4 51.前缀:AD模拟器件, HA 混合集成A/D, HD 混合集成D/A2.器件型号3.一般说明:A 第二代产品,DI 介质隔离,Z 工作于±12V4.温度范围/性能(按参数性能提高排列):I、J、K、L、M 0℃至70℃A、B、C-25℃或-40℃至85℃S、T、U -55℃至125℃5.封装形式:D 陶瓷或金属密封双列直插R 微型“SQ”封装E 陶瓷无引线芯片载体RS 缩小的微型封装F 陶瓷扁平封装S 塑料四面引线扁平封装G 陶瓷针阵列ST 薄型四面引线扁平封装H 密封金属管帽 T TO-92型封装J J形引线陶瓷封装U 薄型微型封装M 陶瓷金属盖板双列直插 W 非密封的陶瓷/玻璃双列直插N 料有引线芯片载体Y 单列直插Q 陶瓷熔封双列直插Z 陶瓷有引线芯片载体P 塑料或环氧树脂密封双列直插高精度单块器件XXX XXXX BI E X /8831 2 3 4 5 61.器件分类: ADC A/D转换器OP 运算放大器AMP 设备放大器PKD 峰值监测器BUF缓冲器 PM PMI二次电源产品CMP比较器REF 电压比较器DAC D/A转换器 RPT PCM线重复器JAN Mil-M-38510 SMP 取样/保持放大器LIU 串行数据列接口单元 SW 模拟开关MAT 配对晶体管SSM 声频产品MUX 多路调制器TMP 温度传感器2.器件型号3.老化选择4.电性等级5.封装形式:H 6腿TO-78 S 微型封装J8腿TO-99 T 28腿陶瓷双列直插K10腿TO-100 TC 20引出端无引线芯片载体P 环氧树脂B双列直插 V 20腿陶瓷双列直插PC 塑料有引线芯片载体 X 18腿陶瓷双列直插Q 16腿陶瓷双列直插 Y 14腿陶瓷双列直插R 20腿陶瓷双列直插 Z 8腿陶瓷双列直插RC 20引出端无引线芯片载体6.军品工艺ALTERA产品型号命名XXX XXX X X XX X1 2 3 4 5 61.前缀: EP 典型器件EPC 组成的EPROM器件EPF FLEX 10K或FLFX 6000系列、FLFX 8000系列EPM MAX5000系列、MAX7000系列、MAX9000系列EPX 快闪逻辑器件2.器件型号3.封装形式:D陶瓷双列直插 Q 塑料四面引线扁平封装P 塑料双列直插R 功率四面引线扁平封装S 塑料微型封装T 薄型J形引线芯片载体J 陶瓷J形引线芯片载体 W 陶瓷四面引线扁平封装L 塑料J形引线芯片载体 B 球阵列4.温度范围: C ℃至70℃,I -40℃至85℃,M -55℃至125℃5.腿数6.速度ATMEL产品型号命名AT XX X XX XX X X X1 2 3 4 5 61.前缀:ATMEL公司产品代号2.器件型号3.速度4.封装形式:A TQFP封装P 塑料双列直插B 陶瓷钎焊双列直插Q 塑料四面引线扁平封装C 陶瓷熔封R 微型封装集成电路D 陶瓷双列直插S 微型封装集成电路F 扁平封装T 薄型微型封装集成电路G 陶瓷双列直插,一次可编程U 针阵列J 塑料J形引线芯片载体 V 自动焊接封装K 陶瓷J形引线芯片载体W 芯片L 无引线芯片载体 Y 陶瓷熔封M 陶瓷模块Z 陶瓷多芯片模块N 无引线芯片载体,一次可编程5.温度范围: C 0℃至70℃, I -40℃至85℃, M -55℃至125℃6.工艺:空白标准/883 Mil-Std-883, 完全符合B级B Mil-Std-883,不符合B级BB产品型号命名XXX XXX (X) X X X1 2 3 4 5 6DAC 87 X XXX X /883B4 7 81.前缀:ADC A/D转换器MPY 乘法器ADS 有采样/保持的A/D转换器OPA 运算放大器DAC D/A转换器 PCM 音频和数字信号处理的A/D和D/A转换器DIV 除法器 PGA 可编程控增益放大器INA 仪用放大器 SHC 采样/保持电路ISO 隔离放大器 SDM 系统数据模块MFC 多功能转换器 VFC V/F、F/V变换器MPC 多路转换器 XTR 信号调理器2.器件型号3.一般说明:A 改进参数性能L 锁定Z + 12V电源工作HT 宽温度范围4.温度范围:H、J、K、L 0℃至70℃A、B、C -25℃至85 ℃R、S、T、V、W -55℃至125℃5.封装形式:L 陶瓷芯片载体H 密封陶瓷双列直插M 密封金属管帽G 普通陶瓷双列直插N 塑料芯片载体U 微型封装P 塑封双列直插6.筛选等级: Q 高可靠性 QM 高可靠性,军用7.输入编码: CBI 互补二进制输入COB 互补余码补偿二进制输入CSB 互补直接二进制输入CTC 互补的两余码8.输出: V 电压输出 I 电流输出CYPRESS产品型号命名XXX 7 C XXX XX X X X1 2 3 4 5 61.前缀:CY Cypress公司产品, CYM 模块, VIC VME 总线2.器件型号:7C128 CMOS SRAM 7C245 PROM 7C404 FIFO7C9101 微处理器3.速度:A 塑料薄型四面引线扁平封装 V J形引线的微型封装B 塑料针阵列U 带窗口的陶瓷四面引线扁平封装D 陶瓷双列直插W 带窗口的陶瓷双列直插F 扁平封装X 芯片G 针阵列Y 陶瓷无引线芯片载体H 带窗口的密封无引线芯片载体 HD 密封双列直插J 塑料有引线芯片载体K 陶瓷熔封 HV 密封垂直双列直插L 无引线芯片载体PF 塑料扁平单列直插P 塑料PS 塑料单列直插Q 带窗口的无引线芯片载体 PZ 塑料引线交叉排列式双列直插R 带窗口的针阵列E 自动压焊卷S 微型封装IC T 带窗口的陶瓷熔封 N 塑料四面引线扁平封装5.温度范围: C 民用(0℃至70℃)I 工业用(-40℃至85℃)M 军用(-55℃至125℃)6.工艺: B 高可靠性HITACHI常用产品型号命名XX XXXXX X X1 2 3 41.前缀:HA 模拟电路 HB 存储器模块HD 数字电路 HL 光电器件(激光二极管/LED)HM 存储器(RAM)HR光电器件(光纤)HN 存储器(NVM)PF RF功率放大器HG 专用集成电路2.器件型号3.改进类型4.封装形式:P 塑料双列 PG 针阵列C 陶瓷双列直插 S 缩小的塑料双列直插CP 塑料有引线芯片载体 CG 玻璃密封的陶瓷无引线芯片载体FP 塑料扁平封装 G 陶瓷熔封双列直插SO 微型封装INTERSIL产品型号命名XXX XXXX X X X X1 2 3 4 5 61.前缀: D 混合驱动器 G 混合多路FETICL 线性电路 ICM 钟表电路IH 混合/模拟门 IM 存储器AD 模拟器件DG 模拟开关DGM 单片模拟开关ICH 混合电路MM 高压开关NE/SE SIC产品2.器件型号3.电性能选择4.温度范围: A -55℃至125℃,B -20℃至85℃, C 0℃至70℃I -40℃至125℃,M -55℃至125℃5.封装形式:A TO-237型L 无引线陶瓷芯片载体B 微型塑料扁平封装P 塑料双列直插C TO-220型S TO-52型D 陶瓷双列直插T TO-5、TO-78、TO-99、TO-100型E TO-8微型封装U TO-72、TO-18、TO-71型F 陶瓷扁平封装V TO-39型H TO- 66型Z TO-92型I 16脚密封双列直插 /W 大圆片J 陶瓷双列直插/D 芯片K T O-3型Q 2引线金属管帽6.管脚数:A 8,B 10,C 12,D 14,E 16,F 22,G 24,H 42, I 28, J 32,K 35, L 40, M 48, N 18,P 20, Q 2, R 3,S 4, T 6, U 7,V 8(引线间距0.2"",绝缘外壳) W 10(引线间距0.23"",绝缘外壳)Y 8(引线间距0.2"",4脚接外壳) Z 10(引线间距0.23"",5脚接外壳)NEC常用产品型号命名μP X XXXX X1 2 3 41.前缀2.产品类型:A 混合元件 B 双极数字电路,C 双极模拟电路D 单极型数字电路3.器件型号:4.封装形式:A 金属壳类似TO-5型封装 J 塑封类似TO-92型B 陶瓷扁平封装 M 芯片载体C 塑封双列 V 立式的双列直插封装D 陶瓷双列 L 塑料芯片载体G 塑封扁平 K 陶瓷芯片载体H 塑封单列直插 E 陶瓷背的双列直插MICROCHIP产品型号命名PIC XX XXX XXX (X) -XX X /XX1 2 3 4 561. 前缀: PIC MICROCHIP公司产品代号2. 器件型号(类型):C CMOS电路 CR CMOS ROMLC 小功率CMOS电路LCS 小功率保护AA 1.8V LCR 小功率CMOS ROMLV 低电压 F 快闪可编程存储器HC 高速CMOS FR FLEX ROM3.改进类型或选择4.速度标示:-55 55ns, -70 70ns, -90 90ns, -10 100ns, -12 120ns-15 150ns, -17 170ns, -20 200ns, -25 250ns, -30 300ns晶体标示: LP 小功率晶体,RC 电阻电容,XT 标准晶体/振荡器HS 高速晶体频率标示: -20 2MHZ, -04 4MHZ, -10 10MHZ,-16 16MHZ-20 20MHZ,-25 25MHZ,-33 33MHZ5.温度范围:空白 0℃至70℃,I -45℃至85℃, E -40℃至125℃6.封装形式:L PLCC封装JW 陶瓷熔封双列直插,有窗口P 塑料双列直插PQ 塑料四面引线扁平封装W 大圆片 SL 14腿微型封装-150milJN 陶瓷熔封双列直插,无窗口SM 8腿微型封装-207milSN 8腿微型封装-150 mil VS 超微型封装8mm×13.4mmSO 微型封装-300 mil ST 薄型缩小的微型封装-4.4mmSP 横向缩小型塑料双列直插CL 68腿陶瓷四面引线,带窗口SS 缩小型微型封装PT 薄型四面引线扁平封装TS 薄型微型封装8mm×20mm TQ 薄型四面引线扁平封装ST产品型号命名普通线性、逻辑器件MXXX XXXXX XX X X1 2 3 4 51.产品系列:74AC/ACT 先进CMOS HCF4XXXM7 4HC 高速CMOS2.序列号3.速度4.封装: BIR,BEY 陶瓷双列直插M,MIR 塑料微型封装5.温度普通存贮器件XX X XXXX X XX X XX1 2 3 4 5 6 71.系列:ET21 静态RAM ETL21 静态RAMETC27 EPROM MK41 快静态RAMMK45 双极端口FIFO MK48 静态RAMTS27 EPROM S28 EEPROMTS29 EEPROM2.技术:空白…NMOS C…CMOS L…小功率3.序列号4.封装: C 陶瓷双列 J 陶瓷双列N 塑料双列 Q UV 窗口陶瓷熔封双列直插5.速度6.温度:空白 0℃~70℃ E -25℃~70℃V -40℃~85℃ M -55℃~125℃7.质量等级:空白标准B/B MIL-STD-883B B级存储器编号(U.V EPROM和一次可编程OTP)M XX X XXX X X XXX X X1 2 3 4 5 6 7 81.系列:27…EPROM 87…EPROM锁存2.类型:空白…NMOS,C…CMOS,V…小功率3.容量:64…64K位(X8)256…256K位(X8)512…512K位(X8)1001…1M位(X8)101…1M位(X8)低电压1024…1M位(X8)2001…2M位(X8)201…2M位(X8)低电压4001…4M位(X8)401…4M位(X8)低电压4002…4M位(X16)801…4M位(X8)161…16M位(X8/16)可选择160…16M位(X8/16)4.改进等级5.电压范围:空白5V +10%Vcc,X 5V +10%Vcc6.速度: 55 55n,60 60ns,70 70ns,80 80ns90 90ns, 100/10 100 n120/12 120 ns,150/15 150 ns200/20 200 ns,250/25 250 ns7.封装:F 陶瓷双列直插(窗口) L 无引线芯片载体(窗口)B 塑料双列直插C 塑料有引线芯片载体(标准)M 塑料微型封装N 薄型微型封装K 塑料有引线芯片载体(低电压)8.温度: 1 0℃~70℃, 6 -40℃~85℃, 3 -40℃~125℃快闪EPROM的编号M XX X A B C X X XXX X X1 2 3 4 5 6 7 8 9 101.电源2.类型: F 5V +10%, V 3.3V +0.3V3.容量: 1 1M, 2 2M, 3 3M,8 8M,16 16M4.擦除: 0 大容量 1 顶部启动逻辑块 2 底部启动逻辑块 4 扇区5.结构:0 ×8/×16可选择, 1 仅×8, 2 仅×166.改型:空白 A7.Vcc:空白 5V+10%Vcc X +5%Vcc8.速度:60 60ns,70 70ns, 80 80ns,90 90ns100 100ns,120 120ns,150 150ns,200 200ns9.封装:M 塑料微型封装N 薄型微型封装,双列直插C/K 塑料有引线芯片载体B/P 塑料双列直插10.温度:1 0℃~70℃, 6 -40℃~85℃, 3 -40℃~125℃仅为3V和仅为5V的快闪EPROM编号M XX X XXX X XXX X X1 2 3 4 5 6 71.器件系列: 29 快闪2.类型: F 5V单电源V 3.3单电源3.容量:100T (128K×8.64K×16)顶部块,100B(128K×8.64K×16)底部块200T (256K×8.64K×16)顶部块,200B (256K×8.64K×16)底部块400T (512K×8.64K×16)顶部块,400B (512K×8.64K×16)底部块040 (12K×8)扇区,080 (1M×8)扇区016 (2M×8)扇区4.Vcc:空白 5V+10%Vcc, X +5%Vcc5.速度:60 60ns,70 70ns, 80 80ns90 90ns, 120 120ns6.封装: M 塑料微型封装N 薄型微型封装K 塑料有引线芯片载体P 塑料双列直插7.温度: 1 0℃~70℃, 6 -40℃~85℃, 3 -40℃~125℃串行EEPROM的编号ST XX XX XX X X X1 2 3 4 5 61.器件系列: 24 12C , 25 12C(低电压),93 微导线95 SPI总线 28 EEPROM2.类型/工艺:C CMOS(EEPROM) E 扩展I C 总线W 写保护士 CS 写保护(微导线)P SPI总线LV 低电压(EEPROM)3.容量:01 1K,02 2K,04 4K,08 8K16 16K, 32 32K,64 64K4.改型:空白 A、 B、 C、 D5.封装: B 8腿塑料双列直插M 8腿塑料微型封装ML 14腿塑料微型封装6.温度: 1 0℃~70℃ 6 -40℃~85℃ 3 -40℃~125℃微控制器编号ST XX X XX X X1 2 3 4 5 61.前缀2.系列: 62 普通ST6系列63 专用视频ST6系列72 ST7系列90 普通ST9系列92 专用ST9系列10 ST10位系列20 ST20 32位系列3.版本:空白ROM T OTP(PROM)R ROMless P 盖板上有引线孔E EPROMF 快闪4.序列号5.封装:B 塑料双列直插D 陶瓷双列真插F 熔封双列直插M 塑料微型封装S 陶瓷微型封装CJ 塑料有引线芯片载体K 无引线芯片载体L 陶瓷有引线芯片载体QX 塑料四面引线扁平封装G 陶瓷四面扁平封装成针阵列R 陶瓷什阵列T 薄型四面引线扁平封装6.温度范围:1.5 0℃~70℃(民用)2 -40℃~125℃(汽车工业)61 -40℃~85℃(工业)E -55℃~125℃XICOR产品型号命名X XXXXX X X X (-XX)1 2 3 4 5 6EEPOT X XXXXX X X1 2 7 3 4串行快闪X XX X XXX X X -X1 2 3 4 81.前缀2.器件型号3.封装形式:D 陶瓷双列直插P 塑料双列直插E 无引线芯片载体R 陶瓷微型封装F 扁平封装S 微型封装J 塑料有引线芯片载体T 薄型微型封装K 针振列V 薄型缩小型微型封装L薄型四面引线扁平封装X 模块M 公制微型封装Y 新型卡式4.温度范围:空白标准,B B级(MIL-STD-883),E -20℃至85℃I -40℃至85℃,M -55℃至125℃5.工艺等级:空白标准,B B级(MIL-STD-883)6.存取时间(仅限EEPROM和NOVRAM):20 200NS, 25 250NS, 空白 300ns, 35 350ns, 45 450ns55 55ns, 70 70ns, 90 90ns, 15 150nsVcc限制(仅限串行EEPROM):空白 4.5V至 5.5V,-3 3V至5.5V-2.7 2.7V至 5.5V,-1.8 1.8V至5.5V7.端到末端电阻:Z 1KΩ,Y 2KΩ,W 10KΩ,U50KΩ,T 100KΩ8. Vcc限制:空白 1.8V至3.6V,-5 4.5V至5.5VZILOG产品型号命名Z XXXXX XX X X X XXXX1 2 3 4 5 6 71.前缀2.器件型号3.速度:空白 2.5MHz, A 4.0MHz,B 6.0MHzH 8.0MHz,L 低功耗的,直接用数字标示4.封装形式:A 极小型四面引线扁平封装C 陶瓷钎焊D 陶瓷双列直插E 陶瓷,带窗口F 塑料四面引线扁平封装G 陶瓷针阵列H 缩小型微型封装I PCB芯片载体K 陶瓷双列直插,带窗口L 陶瓷无引线芯片载体P 塑料双列直插Q 陶瓷四列S 微型封装V 塑料有引线芯片载体5.温度范围: E -40℃至100℃, M -55℃至125℃, S 0℃至70 ℃6.环境试验过程:A 应力密封,B 军品级,C 塑料标准,D 应力塑料,E 密封标准。

FPGA(ep2c8q208c8n)引脚中文详解

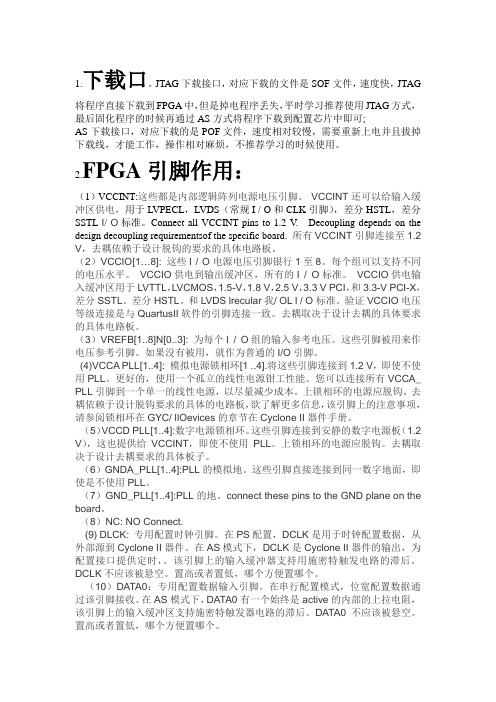

1.下载口。

JTAG下载接口,对应下载的文件是SOF文件,速度快,JTAG 将程序直接下载到FPGA中,但是掉电程序丢失,平时学习推荐使用JTAG方式,最后固化程序的时候再通过AS方式将程序下载到配置芯片中即可;AS下载接口,对应下载的是POF文件,速度相对较慢,需要重新上电并且拔掉下载线,才能工作,操作相对麻烦,不推荐学习的时候使用。

2.FPGA引脚作用:(1)VCCINT:这些都是内部逻辑阵列电源电压引脚。

VCCINT还可以给输入缓冲区供电,用于LVPECL,LVDS(常规I / O和CLK引脚),差分HSTL,差分SSTL I/ O标准。

Connect all VCCINT pins to 1.2 V. Decoupling depends on the design decoupling requirementsof the specific board.所有VCCINT引脚连接至1.2 V,去耦依赖于设计脱钩的要求的具体电路板。

(2)VCCIO[1…8]: 这些I / O电源电压引脚银行1至8。

每个组可以支持不同的电压水平。

VCCIO供电到输出缓冲区,所有的I / O标准。

VCCIO供电输入缓冲区用于LVTTL,LVCMOS,1.5-V,1.8 V,2.5 V,3.3 V PCI,和3.3-V PCI-X,差分SSTL。

差分HSTL。

和LVDS lrecular我/ OL I / O标准。

验证VCCIO电压等级连接是与QuartusII软件的引脚连接一致。

去耦取决于设计去耦的具体要求的具体电路板。

(3)VREFB[1..8]N[0..3]: 为每个I / O组的输入参考电压。

这些引脚被用来作电压参考引脚。

如果没有被用,就作为普通的I/O引脚。

(4)VCCA PLL[1..4]: 模拟电源锁相环[1 ..4].将这些引脚连接到1.2 V,即使不使用PLL。

更好的,使用一个孤立的线性电源钳工性能。

(完整版)ALTERA产品型号命名

ALTERA产品型号命名

XXX XX XX X XX X X

1 2 3 4 5 6 7

工艺+ 型号+ LE数量+ 封装+ 管脚数目+ 温度范围+ 器件速度。

1.前缀:

EP 典型器件

EPC 组成的EPROM 器件

EPF FLEX 10K 或FLFX 6000 系列、FLFX 8000 系列

EPM MAX5000 系列、MAX7000 系列、MAX9000 系列

EPX 快闪逻辑器件

2.器件型号

3.LE数量: XX(k)

4.封装形式:

D 陶瓷双列直插

Q 塑料四面引线扁平封装

P 塑料双列直插

R 功率四面引线扁平封装

S 塑料微型封装

T 薄型J 形引线芯片载体

J 陶瓷J 形引线芯片载体

W 陶瓷四面引线扁平封装

L 塑料J 形引线芯片载体

B 球阵列

5.管脚

6.温度范围:

C ℃至70℃,

I -40℃至85℃,

M -55℃至125℃

7.速度:

数字越小速度越快。

举例:

EP2C20F484C6

EP 工艺

2C cyclone2 (S代表stratix。

A代表arria) 20 2wLE数量

F484 FBGA484pin 封装

C6 八速。

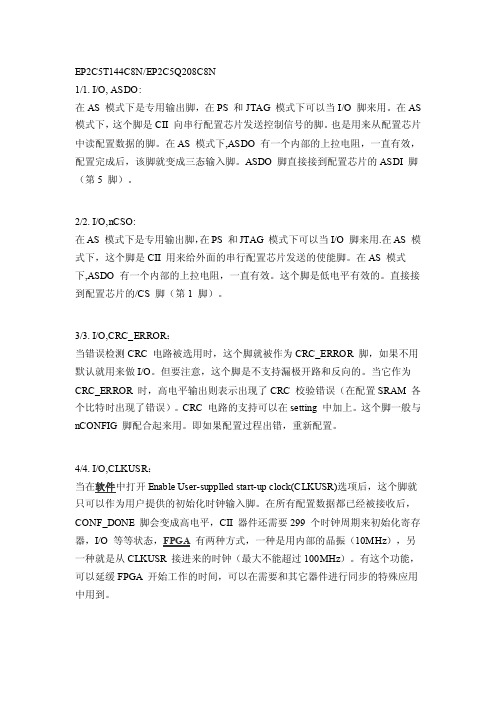

EP2C5T144C8NEP2C5Q208C8N-Read

EP2C5T144C8N/EP2C5Q208C8N1/1. I/O, ASDO:在AS 模式下是专用输出脚,在PS 和JTAG 模式下可以当I/O 脚来用。

在AS 模式下,这个脚是CII 向串行配置芯片发送控制信号的脚。

也是用来从配置芯片中读配置数据的脚。

在AS 模式下,ASDO 有一个内部的上拉电阻,一直有效,配置完成后,该脚就变成三态输入脚。

ASDO 脚直接接到配置芯片的ASDI 脚(第5 脚)。

2/2. I/O,nCSO:在AS 模式下是专用输出脚,在PS 和JTAG 模式下可以当I/O 脚来用.在AS 模式下,这个脚是CII 用来给外面的串行配置芯片发送的使能脚。

在AS 模式下,ASDO 有一个内部的上拉电阻,一直有效。

这个脚是低电平有效的。

直接接到配置芯片的/CS 脚(第1 脚)。

3/3. I/O,CRC_ERROR:当错误检测CRC 电路被选用时,这个脚就被作为CRC_ERROR 脚,如果不用默认就用来做I/O。

但要注意,这个脚是不支持漏极开路和反向的。

当它作为CRC_ERROR 时,高电平输出则表示出现了CRC 校验错误(在配置SRAM 各个比特时出现了错误)。

CRC 电路的支持可以在setting 中加上。

这个脚一般与nCONFIG 脚配合起来用。

即如果配置过程出错,重新配置。

4/4. I/O,CLKUSR:当在软件中打开Enable User-supplled start-up clock(CLKUSR)选项后,这个脚就只可以作为用户提供的初始化时钟输入脚。

在所有配置数据都已经被接收后,CONF_DONE 脚会变成高电平,CII 器件还需要299 个时钟周期来初始化寄存器,I/O 等等状态,FPGA有两种方式,一种是用内部的晶振(10MHz),另一种就是从CLKUSR 接进来的时钟(最大不能超过100MHz)。

有这个功能,可以延缓FPGA 开始工作的时间,可以在需要和其它器件进行同步的特殊应用中用到。

IC芯片命名规则大全

IC芯片命名规则MAXIM 专有产品型号命名MAX XXX (X) X X X1 2 3 4 5 61.前缀: MAXIM公司产品代号2.产品字母后缀:三字母后缀:C=温度范围; P=封装类型; E=管脚数四字母后缀:B=指标等级或附带功能; C=温度范围;P=封装类型; I=管脚数3.指标等级或附带功能:A表示5%的输出精度,E表示防静电4 .温度范围:C= 0℃至70℃(商业级)I =-20℃至+85℃(工业级)E =-40℃至+85℃(扩展工业级)A = -40℃至+85℃(航空级)M =-55?至+125℃(军品级)5.封装形式:A SSOP(缩小外型封装) Q PLCCB CERQUAD R 窄体陶瓷双列直插封装C TO-220, TQFP(薄型四方扁平封装) S 小外型封装D 陶瓷铜顶封装T TO5,TO-99,TO-100E 四分之一大的小外型封装 U TSSOP,μMAX,SOTF 陶瓷扁平封装 H 模块封装, SBGA W 宽体小外型封装(300mil)J CERDIP (陶瓷双列直插) X SC-70(3脚,5脚,6脚)K TO-3 塑料接脚栅格阵列 Y 窄体铜顶封装L LCC (无引线芯片承载封装) Z TO-92MQUADM MQFP (公制四方扁平封装) / D裸片N 窄体塑封双列直插 / PR增强型塑封P 塑料 / W 晶圆6.管脚数量:A:8 J:32 K:5,68 S:4,80B:10,64 L:40 T:6,160C:12,192 M:7,48 U:60D:14 N:18 V:8(圆形)E:16 O:42 W:10(圆形)F:22,256 P:20 X:36G:24 Q:2,100 Y:8(圆形)H:44 R:3,84 Z:10(圆形)I:28AD 常用产品型号命名单块和混合集成电路XX XX XX X X X1 2 3 4 51.前缀:AD模拟器件 HA 混合集成A/D HD 混合集成D/A 2.器件型号3.一般说明: A 第二代产品,DI 介质隔离,Z 工作于±12V4.温度范围/性能(按参数性能提高排列):I、J、K、L、M 0℃至70℃A、B、C-25℃或-40℃至85℃S、T、U -55℃至125℃5.封装形式:D 陶瓷或金属密封双列直插R 微型“SQ”封装E 陶瓷无引线芯片载体RS 缩小的微型封装F 陶瓷扁平封装S 塑料四面引线扁平封装G 陶瓷针阵列 ST 薄型四面引线扁平封装H 密封金属管帽 T TO-92型封装J J形引线陶瓷封装U 薄型微型封装M 陶瓷金属盖板双列直插 W 非密封的陶瓷/玻璃双列直插N 料有引线芯片载体Y 单列直插Q 陶瓷熔封双列直插Z 陶瓷有引线芯片载体P 塑料或环氧树脂密封双列直插高精度单块器件XXX XXXX BI E X /8831 2 3 4 5 61.器件分类: ADC A/D转换器 OP 运算放大器AMP 设备放大器PKD 峰值监测器BUF 缓冲器 PM PMI二次电源产品CMP 比较器 REF 电压比较器DAC D/A转换器 RPT PCM线重复器JAN Mil-M-38510 SMP 取样/保持放大器LIU 串行数据列接口单元SW 模拟开关MAT 配对晶体管SSM 声频产品MUX 多路调制器TMP 温度传感器2.器件型号3.老化选择4.电性等级5.封装形式:H 6腿TO-78 S 微型封装J 8腿TO-99 T 28腿陶瓷双列直插K 10腿TO-100 TC 20引出端无引线芯片载体P 环氧树脂B双列直插V 20腿陶瓷双列直插PC 塑料有引线芯片载体X 18腿陶瓷双列直插Q 16腿陶瓷双列直插 Y 14腿陶瓷双列直插R 20腿陶瓷双列直插 Z 8腿陶瓷双列直插RC 20引出端无引线芯片载体6.军品工艺ALTERA 产品型号命名XXX XXX X X XX X1 2 3 4 5 61.前缀: EP 典型器件EPC 组成的EPROM器件EPF FLEX 10K或FLFX 6000系列、FLFX 8000系列EPM MAX5000系列、MAX7000系列、MAX9000系列EPX 快闪逻辑器件2.器件型号3.封装形式:D 陶瓷双列直插 Q 塑料四面引线扁平封装P 塑料双列直插R 功率四面引线扁平封装S 塑料微型封装 T 薄型J形引线芯片载体J 陶瓷J形引线芯片载体 W 陶瓷四面引线扁平封装L 塑料J形引线芯片载体 B 球阵列 4.温度范围: C ℃至70℃,I -40℃至85℃,M -55℃至125℃5.腿数6.速度ATMEL 产品型号命名AT XX X XX XX X X X1 2 3 4 5 61.前缀:ATMEL公司产品代号2.器件型号3.速度4.封装形式:A TQFP封装 P 塑料双列直插B 陶瓷钎焊双列直插Q 塑料四面引线扁平封装C 陶瓷熔封R 微型封装集成电路D 陶瓷双列直插S 微型封装集成电路F 扁平封装T 薄型微型封装集成电路G 陶瓷双列直插,一次可编程U 针阵列J 塑料J形引线芯片载体 V 自动焊接封装K 陶瓷J形引线芯片载体W 芯片L 无引线芯片载体 Y 陶瓷熔封M 陶瓷模块 Z 陶瓷多芯片模块N 无引线芯片载体,一次可编程5.温度范围: C 0℃至70℃, I -40℃至85℃, M -55℃至125℃6.工艺:空白标准/883 Mil-Std-883, 完全符合B级B Mil-Std-883,不符合B级BB 产品型号命名XXX XXX (X) X X X1 2 3 4 5 6DAC 87 X XXX X /883B4 7 81.前缀:ADC A/D转换器MPY 乘法器ADS 有采样/保持的A/D转换器OPA 运算放大器DAC D/A转换器 PCM 音频和数字信号处理的A/D和D/A转换器DIV 除法器 PGA 可编程控增益放大器INA 仪用放大器 SHC 采样/保持电路ISO 隔离放大器 SDM 系统数据模块MFC 多功能转换器 VFC V/F、F/V变换器MPC 多路转换器 XTR 信号调理器2.器件型号3.一般说明:A 改进参数性能 L 锁定Z + 12V电源工作 HT 宽温度范围4.温度范围:H、J、K、L 0℃至70℃A、B、C -25℃至85 ℃ R、S、T、V、W -55℃至125℃5.封装形式:L 陶瓷芯片载体 H 密封陶瓷双列直插M 密封金属管帽 G 普通陶瓷双列直插N 塑料芯片载体 U 微型封装P 塑封双列直插6.筛选等级: Q 高可靠性 QM 高可靠性,军用7.输入编码:CBI 互补二进制输入COB 互补余码补偿二进制输入CSB 互补直接二进制输入CTC 互补的两余码8.输出: V 电压输出 I 电流输出CYPRESS 产品型号命名XXX 7 C XXX XX X X X1 2 3 4 5 61.前缀: CY Cypress公司产品, CYM 模块, VIC VME总线2.器件型号:7C128 CMOS SRAM 7C245 PROM7C404 FIFO 7C9101 微处理器3.速度:A 塑料薄型四面引线扁平封装 V J形引线的微型封装B 塑料针阵列U 带窗口的陶瓷四面引线扁平封装D 陶瓷双列直插 W 带窗口的陶瓷双列直插F 扁平封装X 芯片G 针阵列 Y 陶瓷无引线芯片载体H 带窗口的密封无引线芯片载体 HD 密封双列直插J 塑料有引线芯片载体K 陶瓷熔封 HV 密封垂直双列直插L 无引线芯片载体 PF 塑料扁平单列直插P 塑料 PS 塑料单列直插Q 带窗口的无引线芯片载体 PZ 塑料引线交叉排列式双列直插R 带窗口的针阵列 E自动压焊卷S 微型封装IC T 带窗口的陶瓷熔封 N 塑料四面引线扁平封装5.温度范围:C 民用(0℃至70℃)I 工业用(-40℃至85℃)M 军谩(-55℃至125℃)6.工艺: B 高可靠性HITACHI 常用产品型号命名XX XXXXX X X1 2 3 41.前缀:HA 模拟电路 HB 存储器模块HD 数字电路 HL 光电器件(激光二极管/LED)HM 存储器(RAM) HR光电器件(光纤)HN 存储器(NVM)PF RF功率放大器HG 专用集成电路2.器件型号3.改进类型4.封装形式:P 塑料双列 PG 针阵列C 陶瓷双列直插 S 缩小的塑料双列直插CP 塑料有引线芯片载体 CG 玻璃密封的陶瓷无引线芯片载体FP 塑料扁平封装 G 陶瓷熔封双列直插SO 微型封装INTERSIL 产品型号命名XXX XXXX X X X X1 2 3 4 5 61.前缀: D 混合驱动器 G 混合多路FETICL 线性电路 ICM 钟表电路IH 混合/模拟门 IM 存储器AD 模拟器件 DG 模拟开关DGM 单片模拟开关 ICH 混合电路MM 高压开关 NE/SE SIC产品2.器件型号3.电性能选择4.温度范围:A -55℃至125℃,B -20℃至85℃,C 0℃至70℃ I -40℃至125℃,M -55℃至125℃5.封装形式:A TO-237型 L 无引线陶瓷芯片载体B 微型塑料扁平封装P 塑料双列直插C TO-220型 S TO-52型D 陶瓷双列直插T TO-5、TO-78、TO-99、TO-100型E TO-8微型封装 U TO-72、TO-18、TO-71型F 陶瓷扁平封装V TO-39型H TO- 66型 Z TO-92型I 16脚密封双列直插 /W 大圆片J 陶瓷双列直插/D 芯片K T O-3型 Q 2引线金属管帽6.管脚数:A 8,B 10,C 12,D 14,E 16,F 22,G 24,H 42, I 28, J 32, K 35, L 40, M 48, N 18,P 20, Q 2, R 3, S 4, T 6, U 7,V 8(引线间距0.2"",绝缘外壳)W 10(引线间距0.23"",绝缘外壳)Y 8(引线间距0.2"",4脚接外壳)Z 10(引线间距0.23"",5脚接外壳)NEC 常用产品型号命名μP X XXXX X1 2 3 41.前缀2.产品类型: A 混合元件 B 双极数字电路,C 双极模拟电路D 单极型数字电路3.器件型号:4.封装形式:A 金属壳类似TO-5型封装 J 塑封类似TO-92型B 陶瓷扁平封装 M 芯片载体C 塑封双列 V 立式的双列直插封装D 陶瓷双列 L 塑料芯片载体G 塑封扁平 K 陶瓷芯片载体H 塑封单列直插 E 陶瓷背的双列直插MICROCHIP 产品型号命名PIC XX XXX XXX (X) -XX X /XX1 2 3 4 561. 前缀: PIC MICROCHIP公司产品代号2. 器件型号(类型):C CMOS电路 CR CMOS ROMLC 小功率CMOS电路LCS 小功率保护AA 1.8V LCR 小功率CMOS ROMLV 低电压 F 快闪可编程存储器HC 高速CMOS FR FLEX ROM3.改进类型或选择4.速度标示:-55 55ns, -70 70ns, -90 90ns, -10 100ns, -12 120ns-15 150ns -17 170ns, -20 200ns, -25 250ns, -30 300ns晶体标示:LP 小功率晶体,RC 电阻电容,XT 标季/振荡器HS 高速晶体频率标示:-20 2MHZ, -04 4MHZ, -10 10MHZ, -16 16MHZ-20 20MHZ,-25 25MHZ,-33 33MHZ5.温度范围:空白0℃至70℃,I -45℃至85℃, E -40℃至125℃6.封装形式:L PLCC封装JW 陶瓷熔封双列直插,有窗口P 塑料双列直插PQ 塑料四面引线扁平封装W 大圆片SL 14腿微型封装-150milJN 陶瓷熔封双列直插,无窗口 SM 8腿微型封装-207milSN 8腿微型封装-150 mil VS 超微型封装8mm×13.4mmSO 微型封装-300 mil ST 薄型缩小的微型封装-4.4mmSP 横向缩小型塑料双列直插 CL 68腿陶瓷四面引线,带窗口SS 缩小型微型封装 PT 薄型四面引线扁平封装TS 薄型微型封装8mm×20mm TQ 薄型四面引线扁平封装ST 产品型号命名普通线性、逻辑器件MXXX XXXXX XX X X1 2 3 4 51.产品系列:74AC/ACT 先进CMOSHCF4XXX M74HC 高速CMOS2.序列号3.速度4.封装: BIR,BEY 陶瓷双列直插M,MIR 塑料微型封装5.温度普通存贮器件XX X XXXX X XX X XX1 2 3 4 5 6 71.系列:ET21 静态RAM ETL21 静态RAMETC27 EPROM MK41 快静态RAMMK45 双极端口FIFO MK48 静态RAMTS27 EPROM S28 EEPROMTS29 EEPROM2.技术:空白…NMOS C…CM OS L…小功率3.序列号4.封装:C 陶瓷双列 J 陶瓷双列N 塑料双列 Q UV窗口陶瓷熔封双列直插5.速度6.温度:空白0℃~70℃ E -25℃~70℃ V -40℃~85℃ M -55℃~125℃7.质量等级:空白标准B/B MIL-STD-883B B级存储器编号(U.V EPROM和一次可编程OTP)M XX X XXX X X XXX X X1 2 3 4 5 6 7 81.系列:27…EPROM 87…EPROM锁存2.类型:空白…NMOS,C…CMOS,V…小功率 3.容量:64…64K位(X8)256…256K位(X8)512…512K位(X8)1001…1M位(X8)101…1M位(X8)低电压1024…1M位(X8)2001…2M位(X8)201…2M位(X8)低电压4001…4M位(X8)401…4M位(X8)低电压4002…4M位(X16)801…4M位(X8)161…16M位(X8/16)可选择160…16M位(X8/16)4.改进等级5.电压范围:空白 5V +10%Vcc, X 5V +10%Vcc6.速度:55 55n,60 60ns,70 70ns,80 80ns90 90ns,100/10 100 n120/12 120 ns,150/15 150 ns200/20 200 ns,250/25 250 ns7.封装:F 陶瓷双列直插(窗口)L 无引线芯片载体(窗口)B 塑料双列直插C 塑料有引线芯片载体(标准)M 塑料微型封装N 薄型微型封装K 塑料有引线芯片载体(低电压)8.温度: 1 0℃~70℃, 6 -40℃~85℃, 3 -40℃~125℃快闪EPROM的编号M XX X A B C X X XXX X X1 2 3 4 5 6 7 8 9 1 01.电源2.类型: F 5V +10%, V 3.3V +0.3V3.容量: 1 1M, 2 2M, 3 3M,8 8M,16 16M4.擦除:0 大容量 1 顶部启动逻辑块2 启动逻辑块 4 扇区5.结构:0 ×8/×16可选择, 1 仅×8, 2 仅×166.改型:空白 A7.Vcc:空白 5V+10%Vcc X +5%Vcc8.速度:60 60ns,70 70ns, 80 80ns,90 90ns100 100ns,120 120ns,150 150ns,200 200ns 9.封装:M 塑料微型封装N 薄型微型封装,双列直插C/K 塑料有引线芯片载体 B/P 塑料双列直插10.温度:1 0℃~70℃, 6 -40℃~85℃, 3 -40℃~125℃仅为3V和仅为5V的快闪EPROM编号M XX X XXX X XXX X X1 2 3 4 5 6 7 1.器件系列: 29 快闪2.类型: F 5V单电源V 3.3单电源3.容量:100T (128K×8.64K×16)顶部块,100B (128K×8.64K×16)底部块200T (256K×8.64K×16)顶部块,200B (256K×8.64K×16)底部块 400T (512K×8.64K×16)顶部块,400B (512K×8.64K×16)底部块 040 (12K×8)扇区,080 (1M×8)扇区016 (2M×8)扇区4.Vcc:空白 5V+10%Vcc, X +5%Vcc5.速度:60 60ns,70 70ns, 80 80ns90 90ns, 120 120ns6.封装:M 塑料微型封装N 薄型微型封装K 塑料有引线芯片载体P 塑料双列直插 7.温度: 1 0℃~70℃, 6 -40℃~85℃, 3 -40℃~125℃串行EEPROM的编号ST XX XX XX X X X1 2 3 4 5 61.器件系列:24 12C ,25 12C(低电压),93 微导线95 SPI总线 28 EEPROM2.类型/工艺:C CMOS(EEPROM) E 扩展I C总线W 写保护士 CS 写保护(微导线)P SPI总线V 低电压(EEPROM)3.容量:01 1K 02 2K,04 4K,08 8K16 16K,32 32K, 64 64K4.改型:空白 A、 B、 C、 D5.封装:B 8腿塑料双列直插M 8腿塑料微型封装ML 14腿塑料微型封装6.温度:1 0℃~70℃ 6 -40℃~85℃ 3 -40℃~125℃微控制器编号ST XX X XX X X1 2 3 4 5 61.前缀2.系列: 62 普通ST6系列63 专用视频ST6系列72 ST7系列90 普通ST9系列92 专用ST9系列10 ST10位系列20 ST20 32位系列3.版本:空白 ROM T OTP(PROM)R ROMless P 盖板上有引线孔E EPROMF 快闪4.序列号5.封装:B 塑料双列直插 D 陶瓷双列真插F 熔封双列直插M 塑料微型封装S 陶瓷微型封装CJ 塑料有引线芯片载体K 无引线芯片载体L 陶瓷有引线芯片载体QX 塑料四面引线扁平封装 G 陶瓷四面扁平封装成针阵列R 陶瓷什阵列T 薄型四面引线扁平封装 6.温度范围:1.5 0℃~70℃(民用) 2 -40℃~125℃(汽车工业)61 -40℃~85℃(工业) E -55℃~125℃XICOR 产品型号命名X XXXXX X X X (-XX)1 2 3 4 5 6EEPOT X XXXX X X X1 2 7 3 4串行快闪 X XX X XXX X X -X1 2 3 4 81.前缀2.器件型号3.封装形式:D 陶瓷双列直插P 塑料双列直插E 无引线芯片载体R 陶瓷微型封装F 扁平封装S 微型封装J 塑料有引线芯片载体T 薄型微型封装K 针振列 V 薄型缩小型微型封装L薄型四面引线扁平封装X 模块M 公∑微型封装 Y 新型卡式4.温度范围:空白标准, B B级(MIL-STD-883),E -20℃至85℃I -40℃至85℃,M -55℃至125℃ 5.工艺等级:空白标准, B B级(MIL-STD-883)6.存取时间(仅限EEPROM和NOVRAM):20 200NS, 25 250NS, 空白 300ns, 35 350ns, 45 450ns55 55ns, 70 70ns, 90 90ns, 15 150nsVcc限制(仅限串行EEPROM):空白 4.5V至5.5V,-3 3V至5.5V-2.7 2.7V至5.5V,-1.8 1.8V至5.5V 7.端到末端电阻:Z 1KΩ, Y 2KΩ, W 10KΩ,U 50KΩ, T 100KΩ 8. Vcc限制:空白 1.8V至3.6V,-5 4.5V至5.5VZILOG 产品型号命名Z XXXXX XX X X X XXXX1 2 3 4 5 6 71.前缀2.器件型号3.速度:空白 2.5MHz, A 4.0MHz, B 6.0MHzH 8.0MHz,L 低功耗的,直接用数字标示4.封装形式:A 极小型四面引线扁平封装 C 陶瓷钎焊D 陶瓷双列直插E 陶瓷,带窗口F 塑料四面引线扁平封装G 陶瓷针阵列H 缩小型微型封装I PCB芯片载体K 陶瓷双列直插,带窗口L 陶瓷无引线芯片载体P 塑料双列直插Q 陶瓷四列S 微型封装V 塑料有引线芯片载体 5.温度范围:E -40℃至100℃, M -55℃至125℃,S 0℃至70 ℃6.环境试验过程:A 应力密封,B 军品级,C 塑料标准,D 应力塑料,E 密封标准。

Quectel_EC20_R2.0_硬件设计手册_V1.2

e 3.5.2. 飞行模式 ......................................................................................................................... 29 fid 3.6. 电源设计 ................................................................................................................................ 29

10. 图 31 增加备注 3。

11. 增加射频信号线 Layout 参考指导(5.1.4 章节)。

12. 更新模块耗流数据(表 33)。

13. 增加 GNSS 耗流数据(表 34)。

14. 更新 7.3 章节中模块俯视图。

上海移远通信技术股份ຫໍສະໝຸດ 限公司2 / 83EC20 R2.0 硬件设计手册

目录

3.6.1. 管脚介绍 ......................................................................................................................... 29 3.6.2. 减少电压跌落.................................................................................................................. 30

LED显示屏各芯片管脚定义

一、1.2L E D板的芯片功能74HC245的作用:信号功率放大。

第1脚DIR,为输入输出转换端口,当DIR=“1”高电平(接VCC)时信号由“A”端输入“B”端输出,DIR=“0”低电平(接GND)时信号由“B”端输入“A”端输出。

第19脚G,使能端,若该脚为“1”A/B端的信号将不导通,只有为“0”时A/B 端才被启用,该脚也就是起到开关的作用.第2~9脚“A”信号输入\输出端,A1=B1、、、、、、A8=B8,A1与B1是一组,如果DIR=“1”G=“0”则A1输入B1输出,其它类同。

如果DIR=“0”G=“0”则B1输入A1输出,其它类同。

第11~18脚“B”信号输入\输出端,功能与“A”端一样。

第10脚GND,电源地。

第20脚VCC,电源正极。

74HC595的作用:LED驱动芯片,8位移位锁存器。

第8脚GND,电源地。

第16脚VCC,电源正极第14脚DATA,串行数据输入口,显示数据由此进入,必须有时钟信号的配合才能移入。

QA~QH的输出由输入的数据控制。

第12脚STB,锁存端,当输入的数据在传入寄存器后,只有供给一个锁存信号才能将移入的数据送QA~QH口输出。

第11脚CLK,时钟端,每一个时钟信号将移入一位数据到寄存器。

第10脚SCLR,复位端,只要有复位信号,寄存器内移入的数据将清空,显示屏不用该脚,一般接VCC。

第9脚DOUT,串行数据输出端,将数据传到下一个。

第15、1~7脚,并行输出端也就是驱动输出端,驱动LED。

HC16126\TB62726的作用:LED驱动芯片,16位移位锁存器。

备注:HC16126驱动芯片定义和5020,5024,2016等芯片一样第1脚GND,电源地。

第24脚VCC,电源正极第2脚DATA,串行数据输入第3脚CLK,时钟输入第4脚STB,锁存输入第23脚输出电流调整端,接电阻调整第22脚DOUT,串行数据输出第21脚EN,使能输入其它功能与74HC595相似,只是TB62726是16位移位锁存器,并带输出电流调整功能,但在并行输出口上不会出现高电平,只有高阻状态和低电平状态。

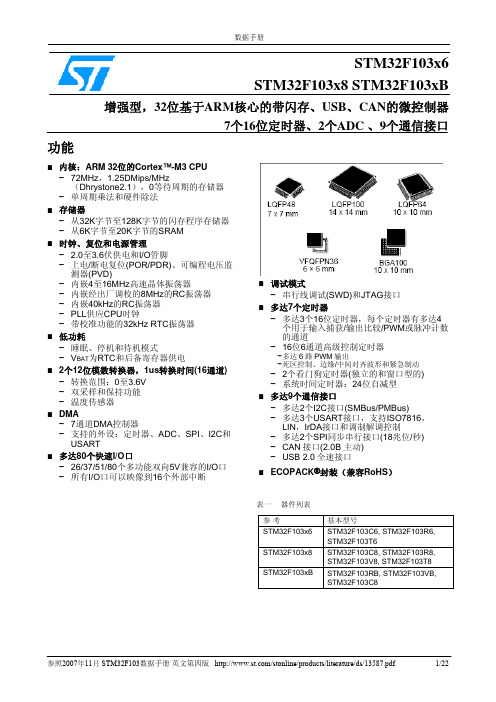

STM32F103VET6

完整的STM32F103xx增强型系列产品包括从36脚至100脚的五种不同封装形式;根据不同的封装形 式,器件中的外设配置不尽相同。下面给出了该系列产品中所有外设的基本介绍。数据手册来自STM32F103x6

功能

STM32F103x8 STM32F103xB

增强型,32位基于ARM核心的带闪存、USB、CAN的微控制器 7个16位定时器、2个ADC 、9个通信接口

■ 内核:ARM 32位的Cortex™-M3 CPU

− 72MHz,1.25DMips/MHz (Dhrystone2.1),0等待周期的存储器

40c至105c结温达125cstm32f103增强型管脚定义图二stm32f103xx增强型vfqfpn36管脚2007年11月第四版第11页stm32f103增强型图三stm32f103xx增强型lqfp100管脚2007年11月第四版第12页stm32f103增强型stm32f103xx增强型lqfp48管脚2007年11月第四版第13页stm32f103增强型stm32f103xx增强型bga100管脚2007年11月第四版第14页stm32f103增强型默认功能重定义功能a3ftpe2traceckb3ftpe3traced0c3ftpe4traced1d3ftpe5traced2e3ftpe6traced3b2vbata2pc13tamperrtc4pc135tamperrtca1pc14osc32in4pc145osc32inb1pc15osc32out4pc155osc32outc2vss5d2vdd5c1oscind1oscoute1nrstf1pc0adc12in10f2pc1adc12in11e21017pc2adc12in12f31118pc3adc12in13g11219vssah1vrefj1vrefk11322vddag2101423pa0wkupusart2cts7adc12in0tim2ch1etr7h2111524pa1usart2rts7adc12in1tim2ch27j2121625pa2usart2tx7adc12in2tim2ch37k213172610pa3pa3usart2rx7adc12in3tim2ch47e41827vss4可选功能脚位管脚名称主功能复位后1928vdd42007年11月第四版第15页stm32f103增强型默认功能重定义功能g314202911pa4pa4spi1nss7usart2ck7adc12in4h315213012pa5pa5spi1sck7adc12in5j316223113pa6pa6spi1miso7adc12in6tim3ch17tim1bkink317233214pa7pa7spi1mosi7adc12in7tim3ch27tim1ching42433pc4adc12in14h42534pc5adc12in15j418263515pb0pb0adc12in8tim3ch37tim1ch2nk419273616pb1pb1a

FLEX10K的PS配置方式及EPC2的应用

Alr t a的可重 复编程 逻辑器件 E C e P 2满足 了在系统编程 的要求 ,具有 Fah配置存储 器 ,可 用来配 置 5 0 3 3 l s .V、 .V、 25 . V器 件 。通 过 内置 的 IE Sd 14 . T E E t 19 1 AG接 口, P 2 J EC 可 以在 5 0 和 3 3 电压 下进行在 系统编程 ( P 。A t a .V .V I ) l r S e

门阵列 , 它是在 P L G L、 P D 等可编程器 件 的基础 上进 A 、A CL

~

步发展的产物 。F G P A采用 C MOSS AM 制 造工艺 , R 使用

MS L E1 0 l

MS L Eo 0 O

配 置方 式 E C1配 置 或 被 动 串行 配置 P 被 动 并 行 同步 配 置

二 者 选 取 不 同值 时 的配 置 方式 。

为测试 数据输入 ,数据通 过 T 引脚输入 J A DI T G接 口; D TO 为测试数据输 出, 数据通过 T O引脚从 JAG接 口输 出。 D T

( ) P 2引 脚 2EC EC P 2的 n S和 O C E引脚 控制 D T A A输 出引脚 的三 态

缓冲器 、 能地址计数 器和 E C 使 P 2的振荡器 。n S引脚控 制 C 配置器件 的输 出 。当 O E引脚 接低 电平 时, 不论 n S为 何状 C

态 , 址计数器复位 , AT 引脚输 出为高阻状态 。当 O 地 D A E引 脚 接 高 电平 时 , 果 n 如 CS保 持高 电平 , 计数器 停止 计数 , 则

S A 来存储编程数据 ,具有系统可编程特 性 。当掉 电后 , R M FG P A恢 复成 白片 , 内部逻 辑关 系消 失, 因此 ,P A 能够 反 FG 复使用 。当需要修 改 F G P A功能 时, 需换一片 E R M 即 只 PO

LED显示屏IC管脚功能及参数自制

LED显示屏IC管脚功能及参数自制

1、CPU管脚:CPU管脚是LED显示屏IC最重要的管脚,主要用于处

理信息输入或输出,如操作信息、数据信息等,CPU管脚的传输频率一般

在几十MHz到几GHz之间,传输信号的电压通常在2.5V-3.3V之间,CPU

管脚有8路、16路、20路等不同类型。

2、存储管脚:存储管脚是LED显示屏IC的一个重要部分,主要用于

存储显示数据,包括存储显示文字、图像、视频等数据,存储管脚的传输

速度一般在几GHz到几GHz之间,传输信号的电压通常在2.5V-3.3V之间,存储管脚有8路、16路、20路等不同类型。

3、控制管脚:控制管脚是LED显示屏IC的一个重要部分,主要用于

控制LED显示屏的功能,包括控制显示内容、亮度、对比度等,控制管脚

的电压在2.5V-3.3V之间,有8路、16路、20路等不同类型。

4、计时、PWM管脚:计时、PWM管脚是LED显示屏IC的一个重要部分,主要用于控制显示器的刷新频率,主要使用PWM(脉冲宽度调制)技

术来控制刷新频率,计时、PWM管脚的传输频率一般在几KHz到几MHz之间。

物联网概论智慧树知到答案章节测试2023年长春师范大学

第一章测试1.#define SEG_D 4语句表示()。

A:将4口定义为c 段B:将4口定义为b 段C:将4口定义为a 段D:将4口定义为d段答案:D2.#define COM2 11语句表示()。

A:定义11口为片选3B:定义10口为片选1C:定义11口为片选0D:定义11口为片选2答案:D3.enum {Color_R,Color_G,Color_B,Color_RG,Color_RB,Color_GB,Color_RGB};枚举表示数值1-7()。

A:错B:对答案:A4.analogWrite(LED_R,255)表示读取LED_R口数据()。

A:错B:对答案:A5.shiftOut(dataPin, clockPin, bitOrder, byte_value);bitOrder 可以是 LSBFIRST或 MSBFIRST: LSBFIRST 最左边的 bit 最先送出()。

A:对B:错答案:B6.利用万用表检测二极管正负极时,将万用表拨到二极管测量档,表笔与二极管的阳、阴极相连,如果读数在0.2~0.7之间,说明红色表笔连接的管脚为()极,黑色表笔为()极。

A:阳,阴B:阴,阴C:阴,阳D:阳,阳答案:A7.提出感知中国战略构想的是谁()。

A:温家宝B:马云C:马化腾D:李鹏答案:A8.射频识别技术的简称()。

A:RRRDB:RFIDC:RFIID:RLID答案:B9.感知层:是物联网的( ),是联系物理世界和信息世界的纽带。

A:应用技术B:使用技术C:入门技术D:核心技术答案:D10.( )网络则主要利用各种类型的传感器对物质性质、环境状态、行为模式等信息,开展大规模、长期、实时的获取。

A:有线传感器B:无线传感器C:有线感知D:无线感知答案:B11.物联网信息中心:()作为处理大数据的重要平台为海量数据的存储和分析提供了有力的支持与保障。

A:物联网B:人工智能C:云计算D:大数据答案:C12.应用层从早期的以( )为主要特征:文件传输、电子邮件等。

正泰中自电动机算法功能块管脚

正泰中自电动机算法功能块管脚正泰中自电动机是一种高效、可靠的电机,它采用了先进的控制

系统和优化的算法来实现卓越的性能。

对于这种电动机而言,算法功

能块管脚是非常重要的组成部分,能够实现电机控制、保护、监控等

多种功能,同时支持多种信号输入和输出接口。

算法功能块包括速度控制、电流控制、位置控制、过流保护、欠

压保护等,这些功能可以通过不同的管脚接口进行设置和调整,以满

足不同的应用需求。

比如,速度控制功能可以通过调整PWM输出端口

实现,实现电机的平稳启动和精确运行;电流控制功能则可以通过感

应电流传感器来检测电机运行时的电流变化,实现电机控制的精确度。

除此之外,算法功能块还可以实现位置控制、转矩控制、速度反

馈等功能,具有很强的实用性和灵活性。

在应用过程中,我们可以通

过对算法功能块管脚的设置和调整,来实现电机的最佳性能和保护。

总之,正泰中自电动机算法功能块管脚是电机控制和保护的重要

组成部分,具有多种功能,可以通过不同的管脚接口进行设置和调整,以满足不同的应用需求。

对于电机应用者而言,了解和掌握这些功能

块的使用方法和接口,对于实现电机最佳性能和保护都是非常有帮助的,同时也可以提高电机应用的效率和可靠性。

芯片epad管脚

芯片epad管脚

在现代电子产品中,芯片epad管脚连接器的种类和形式非常多样化,以满足不同芯片和

外部设备的连接需求。

它们可以按照连接方式分为插入式连接器和焊接式连接器;按照连

接位置分为表面安装连接器和插入连接器;按照连接数量分为单端子连接器和排针连接器。

每种连接器都有其特定的优点和适用范围,可以根据实际需求进行选择和应用。

芯片epad管脚连接器的设计原则主要包括以下几点:第一是连接性能要稳定可靠,能够

确保信号的传输质量和稳定性;第二是安装方便快捷,能够提高生产效率和产品质量;第

三是体积小巧,占用空间少,适合在狭小的空间中进行布局和安装;第四是结构简单合理,易于维护和维修。

通过合理的设计和选材,芯片epad管脚连接器可以实现优质的连接效果,确保设备的可靠性和稳定性。

在实际应用中,芯片epad管脚连接器的安装和连接是至关重要的。

首先,要保证连接器

的引脚与芯片的引脚对应正确,避免短路和接触不良;其次,在焊接过程中要控制好温度

和时间,避免焊接温度过高或时间过长导致元器件损坏;最后,在连接完成后要进行信号

检测和质量验证,确保连接器的正常工作和稳定性。

总的来说,芯片epad管脚连接器在现代电子产品中起着至关重要的作用,它们连接芯片

和外部设备,实现信号的传输和交换,是电子设备正常运行的基础。

在未来,随着电子产

品的不断发展和升级,芯片epad管脚连接器的设计和制造将会越来越重要,我们需要不

断创新和提高,以适应新的应用需求和发展趋势。

光模块管脚定义

光模块管脚定义

《光模块管脚定义那些事儿》

嘿呀,今天咱就来聊聊光模块管脚定义这玩意儿。

你们知道吗,我之前有一次特别的经历,就和这光模块管脚定义有关呢!

那是一次公司里的项目,我负责搞光模块相关的部分。

当时我就对着那些管脚,脑袋都大了呀!就好像面对着一群小怪兽,每个管脚都有它独特的脾气和作用。

我拿着说明书,一个一个地研究,哎呀,真的是费了老劲了。

比如说那个电源管脚吧,我可得小心翼翼地对待它,不然整个光模块都没法好好工作啦。

还有那些信号管脚,就像是传递信息的小使者,一个都不能弄错,不然信号就乱套啦。

我就这么一点点地去理解,去记住它们的定义。

在那几天里,我感觉自己就像是个管脚侦探,在努力破解这些管脚背后的秘密。

我不断地尝试、摸索,有时候弄错了还得重来。

但慢慢地,我还真就搞清楚了这些管脚的定义。

到后来,再看到光模块管脚,我就觉得它们像是我的老朋友一样啦。

我知道它们各自的职责,也知道怎么和它们好好相处。

总之呢,光模块管脚定义虽然有点复杂,但只要我们用心去了解,就一定能搞明白它们哒!就像我那次的经历一样,只要坚持,就没有搞不定的管脚定义呀!哈哈!。

acdc芯片引脚指标

acdc芯片引脚指标1. 输入电压引脚(VIN):输入电压引脚是ACDC芯片的电源输入端,用于接收外部电源提供的电压信号。

它通常具有广泛的工作电压范围,可以适应不同的输入电压条件。

2. 输出电压引脚(VOUT):输出电压引脚是ACDC芯片的电源输出端,用于提供稳定的输出电压给其他电路或设备。

它通常具有较低的输出电压波动和较高的输出电压精度,以确保系统的稳定性和可靠性。

3. GND引脚:GND引脚是ACDC芯片的接地引脚,用于与系统的地连接,以确保电路的正常运行。

它通常与输入和输出电压引脚相连,共同形成完整的电路路径。

4. 使能引脚(EN):使能引脚是ACDC芯片的控制引脚,用于控制芯片的开关状态。

当使能引脚接收到高电平信号时,芯片开始工作;当使能引脚接收到低电平信号时,芯片停止工作。

通过控制使能引脚,可以灵活地控制芯片的运行状态,以满足不同的需求。

5. 超温保护引脚(OTP):超温保护引脚是ACDC芯片的温度监测引脚,用于检测芯片的工作温度。

当芯片温度超过一定阈值时,超温保护引脚会输出一个高电平信号,以提醒系统进行温度保护措施。

这有助于避免芯片因过热而损坏,提高系统的可靠性和安全性。

6. 错误输出引脚(ERR):错误输出引脚是ACDC芯片的故障检测引脚,用于检测芯片的工作状态。

当芯片出现故障或异常情况时,错误输出引脚会输出一个高电平信号,以提醒系统进行相应的处理。

这有助于及时发现和解决问题,保障系统的正常运行。

7. 芯片复位引脚(RESET):芯片复位引脚是ACDC芯片的复位控制引脚,用于恢复芯片的初始状态。

当复位引脚接收到高电平信号时,芯片会被复位,并重新开始工作。

这有助于解决芯片在工作过程中出现的异常情况,保证系统的稳定性和可靠性。

8. 参考电压引脚(VREF):参考电压引脚是ACDC芯片的参考电压输出引脚,用于提供一个稳定的参考电压给其他电路或设备。

它通常具有较高的输出精度和较低的输出电压波动,以确保系统的准确性和稳定性。

平台硬件模块管脚分配表

LED16

B9

SWC0

4*4键盘行线

B10

SWC1

D10

SWC2

F9

SWC3

A13

SWR0

4*4键盘行线

A14

SWR1

A15

SWR2

A16

SWR3

C4

模式3:2x16 LCD(液晶),并行AD模块,并行DA模块

(将控制拨码开关模块CTRL_SW中SEL1拨置于下,SEL2拨置于上,逻辑电平为01,

V15

LED4

OV_D8

由开关VLPO选择

W13

LED5

OV_D9

由开关VLPO选择

W15

LED6

VSYNC

由开关VLPO选择

Y17

LED7

PCLK

由开关VLPO选择

R16

LED8

OV_RES

由开关VLPO选择

T17

F1

AB15

F2

AA16

F3

AB19

F4

W19

F5

U19

F6

AA22

F7

SMBUS_SDA

ADC_D2

C13

ADC_D3

F11

ADC_D4

C15

ADC_D5

E14

ADC_D6

B7

ADC_D7

B8

ADC_Noe

B9

DAC_D0

D/A模块

B10

DAC_D1

D10

DAC_D2

F9

DAC_D3

A13

DAC_D4

A14

DAC_D5

A15

DAC_D6

A16

DAC_D7

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Pin NamePin Type (1st, 2nd, & 3rd Function)Pin DescriptionVCCIO[1..4]Power These are I/O supply voltage pins for banks 1 through 4. Each bank can support a different voltage level. VCCIO supplies power to the output buffers for all I/O standards. VCCIO also supplies power to the input buffers used for the LVTTL, LVCMOS, 1.5-V, 1.8-V, 2.5-V, and 3.3-V PCI I/O standards.VCCINT Power These are internal logic array voltage supply pins. VCCINT also supplies power to the input buffers used for the LVDS, SSTL2, and SSTL3 I/O standards.GNDGroundDevice ground pins. All GND pins should be connected to the board GND plane.VREF[0..2]B[1..4]I/O, Input Input reference voltage for banks 1-4. If a bank uses a voltage-referenced I/O standard, then these pins are used as the voltage-reference pins for the bank. If voltage reference I/O standards are not used in the bank, the VREF pins are available as user I/O pins.VCCA_PLL[1..2]Power Analog power for PLLs[1..2]. The designer must connect this pin to 1.5 V, even if the PLL is not used.GNDA_PLL[1..2]Ground Analog ground for PLLs[1..2]. The designer can connect this pin to the GND plane on the board.GNDG_PLL[1..2]Ground Guard ring ground for PLLs[1..2]. The designer can connect this pin to the GND plane on the board.NCNo Connect No connect pins should not be connected on the board. They should be left floating.CONF_DONE Bidirectional (open-drain)This is a dedicated configuration status pin; it is not available as a user I/O pin.nSTATUS Bidirectional (open-drain)This is a dedicated configuration status pin; it is not available as a user I/O pin.nCONFIGInputDedicated configuration control input. A low transition resets the target device; a low-to-high transition begins configuration. All I/O pins tri-state when nCONFIG is driven low.DCLK Input (PS mode), Output (AS mode)In passive serial configuration mode, DCLK is a clock input used to clock configuration data from an external source into the Cyclone device. In active serial configuration mode, DCLK is a clock outputfrom the Cyclone device (the Cyclone device acts as master in this mode). This is a dedicated pinused for configuration.DATA0InputDedicated configuration data input pin.nCE Input Active-low chip enable. Dedicated chip enable input used to detect which device is active in a chain of devices. When nCE is low, the device is enabled. When nCE is high, the device is disabled.nCEOOutputOutput that drives low when device configuration is complete. During multi-device configuration, this pin feeds a subsequent device’s nCE pin.ASDO I/O, OutputActive serial data output from the Cyclone device. This output pin is utilized during active serial configuration mode. The Cyclone device controls configuration and drives address and control information out on ASDO. In passive serial configuration, this pin is available as a user I/O pin.nCSO I/O, OutputChip select output that enables/disables a serial configuration device. This output is utilized during active serial configuration mode. The Cyclone device controls configuration and enables the serial configuration device by driving nCSO low. In passive serial configuration, this pin is available as a user I/O pin.CRC_ERRORI/O, OutputActive high signal that indicates that the error detection circuit has detected errors in the configuration SRAM bits. This pin is optional and is used when the CRC error detection circuit is enabled.INIT_DONE I/O, Output (open-drain)This is a dual-purpose pin and can be used as an I/O pin when not enabled as INIT_DONE. When enabled, the pin indicates when the device has entered user mode. This pin can be used as a user I/Opin after configuration.CLKUSRI/O, InputOptional user-supplied clock input. Synchronizes the initialization of one or more devices. This pin can be used as a user I/O pin after configuration.DEV_CLRn I/O, InputDual-purpose pin that can override all clears on all device registers. When this pin is driven low, all registers are cleared; when this pin is driven high, all registers behave as defined in the design.DEV_OE I/O, Input Dual-purpose pin that can override all tri-states on the device. When this pin is driven low, all I/O pins are tri-stated; when this pin is driven high, all I/O pins behave as defined in the design.MSEL[1..0]Input Dedicated mode select control pins that set the configuration mode for the device.TMS Input This is a dedicated JTAG input pin.TDI Input This is a dedicated JTAG input pin.TCK Input This is a dedicated JTAG input pin.TDO OutputThis is a dedicated JTAG output pin.CLK0Input, LVDS Input Dedicated global clock input. The dual-function of CLK0 is LVDSCLK1p, which is used for differential input to PLL1.CLK1Input, LVDS Input Dedicated global clock input. The dual-function of CLK1 is LVDSCLK1n, which is used for differential input to PLL1.CLK2Input, LVDS Input Dedicated global clock input. The dual-function of CLK2 is LVDSCLK2p, which is used for differential input to PLL2.CLK3Input, LVDS InputDedicated global clock input. The dual-function of CLK3 is LVDSCLK2n, which is used for differential input to PLL2.Configuration and JTAG Pins Pin Information for the Cyclone™ EP1C12 DeviceVersion 1.4Supply and Reference PinsClock and PLL PinsPT-EP1C12-1.4Copyright © 2006 Altera Corp.Pin DefinitionsPage 12 of 15Pin NamePin Type (1st, 2nd, & 3rd Function)Pin DescriptionPin Information for the Cyclone™ EP1C12 DeviceVersion 1.4DPCLK[7..0]I/O Dual-purpose clock pins that can connect to the global clock network. These pins can be used forhigh fan-out control signals, such as clocks, clears, IRDY, TRDY, or DQS signals. These pins are also available as user I/O pins.PLL1_OUTp I/O, Output External clock output from PLL 1. This pin can be used with differential or single ended I/O standards. If clock output from PLL1 is not used, this pin is available as a user I/O pin.PLL1_OUTn I/O, Output Negative terminal for external clock output from PLL1. If the clock output is single ended, this pin is available as a user I/O pin.PLL2_OUTp I/O, Output External clock output from PLL 2. This pin can be used with differential or single ended I/O standards. If clock output from PLL2 is not used, this pin is available as a user I/O pin.PLL2_OUTnI/O, OutputNegative terminal for external clock output from PLL2. If the clock output is single ended, this pin is available as a user I/O pin.LVDS[0..102]p I/O, LVDS RX or TXDual-purpose LVDS I/O channels 0 to 102. These channels can be used for receiving or transmitting LVDS compatible signals. Pins with a "p" suffix carry the positive signal for the differential channel. If not used for LVDS interfacing, these pins are available as user I/O pins.LVDS[0..102]n I/O, LVDS RX or TX Dual-purpose LVDS I/O channels 0 to 102. These channels can be used for receiving or transmitting LVDS compatible signals. Pins with an "n" suffix carry the negative signal for the differential channel. If not used for LVDS interfacing, these pins are available as user I/O pins.LVDSCLK1p Input, LVDS Input Dual-purpose LVDS clock input to PLL1. If differential input to PLL1 is not required, this pin is available as the CLK0 input pin.LVDSCLK1n Input, LVDS Input Dual-purpose LVDS clock input to PLL1. If differential input to PLL1 is not required, this pin is available as the CLK1 input pin.LVDSCLK2p Input, LVDS Input Dual-purpose LVDS clock input to PLL2. If differential input to PLL2 is not required, this pin is available as the CLK2 input pin.LVDSCLK2nInput, LVDS InputDual-purpose LVDS clock input to PLL2. If differential input to PLL2 is not required, this pin is available as the CLK3 input pin.DQS[0..1][L,R,T,B]I/O Optional data strobe signal for use in external memory interfacing. These pins also function as DPCLK pins; therefore, the DQS signals can connect to the global clock network. A programmable delay chain is used to shift the DQS signals by 90 or 72 degrees.DQ[0..7][L,R,T,B]I/O Optional data signal for use in external memory interfacing.DM[0..1][L,R,T,B]I/OOptional data mask output signal for use in external memory interfacing.Dual-Purpose LVDS & External Memory Interface PinsPT-EP1C12-1.4Copyright © 2006 Altera Corp.Pin DefinitionsPage 13 of 15Pin Information for the Cyclone™ EP1C12 Device, ver 1.4VREF2B2VREF1B2VREF0B2B2V R E F 0B 1B 1B 3V R E F 0B 3V R E F 1B 1V R E F 1B 3PLL1PLL2V R E B 2B 1V R E B 2B 3B4VREF2B4VREF1B4VREF0B4Notes:1.This is a top view of the silicon die.2.This is a pictoral representation only to get an idea of placement on the device. Refer to the pin-list andthe Quartus II for exact locations.PT-EP1C12-1.4Copyright © 2006 Altera Corp.Bank & PLL DiagramPage 14 of 15Pin Information for the Cyclone™ EP1C12 DeviceVersion 1.4Version NumberDate Changes Made1.43/6/2006Added CRC_ERROR pin in Pin List and Pin DefinitionsPT-EP1C12-1.4Copyright © 2006 Altera Corp.Revision HistoryPage 15 of 15。