UA733中文资料

NX7337BF-AA中文资料

TC

−20 to +60ห้องสมุดไป่ตู้

°C

Storage Temperature

Tstg

−40 to +85

°C

Lead Soldering Temperature

Tsld

260 (10 sec)

°C

Relative Humidity (noncondensing) RH

85

%

*1 Pulse Condition: Pulse Width (PW) = 10 µs, Duty = 1%

Optical Fiber

SMF Length = 1 m

φ 0.9 φ7

2 4 27.4

2– φ 2.2

φ6 12.7 17.0

PIN CONNECTIONS

P.C.D. = φ 2 4 3 1 2

1 3.7

7.2

20

φ 0.45

1

2

LD

CASE

The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version.

Restricted Substance per RoHS

Lead (Pb) Mercury Cadmium Hexavalent Chromium PBB PBDE

Concentration Limit per RoHS (values are not yet fixed) < 1000 PPM < 1000 PPM < 100 PPM < 1000 PPM < 1000 PPM < 1000 PPM

TPS7333Q, TPS7348Q, TPS7350Q中文资料

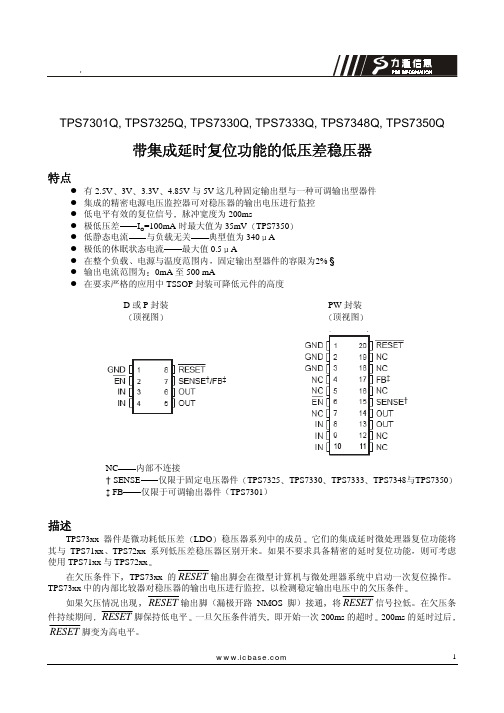

TPS7301Q, TPS7325Q, TPS7330Q, TPS7333Q, TPS7348Q, TPS7350Q 带集成延时复位功能的低压差稳压器特点z有2.5V3V 3.3V 4.85V与5V这几种固定输出型与一种可调输出型器件z集成的精密电源电压监控器可对稳压器的输出电压进行监控z低电平有效的复位信号脉冲宽度为200msz极低压差I=100mA时最大值为35mV TPS7350z低静态电流与负载无关典型值为340Az极低的休眠状态电流最大值0.5Az在整个负载电源与温度范围内固定输出型器件的容限为2% §z输出电流范围为0mA至500 mAz在要求严格的应用中TSSOP封装可降低元件的高度D或P封装PW封装顶视图顶视图NC内部不连接† SENSE仅限于固定电压器件TPS7325TPS7330TPS7333TPS7348与TPS7350‡ FB仅限于可调输出器件TPS7301描述TPS73xx器件是微功耗低压差LDO稳压器系列中的成员它们的集成延时微处理器复位功能将其与TPS71xx TPS72xx系列低压差稳压器区别开来如果不要求具备精密的延时复位功能则可考虑使用TPS71xx与TPS72xx在欠压条件下TPS73xx的RESET输出脚会在微型计算机与微处理器系统中启动一次复位操作TPS73xx中的内部比较器对稳压器的输出电压进行监控以检测稳定输出电压中的欠压条件如果欠压情况出现RESET输出脚漏极开路NMOS脚接通将RESET信号拉低在欠压条件持续期间RESET脚保持低电平一旦欠压条件消失即开始一次200ms的超时200ms的延时过后RESET脚变为高电平可选器件D与PW封装的器件有盘装与卷装形式在器件型号后加后缀R如TPS7350QDR TPS7301Q可以通过外部电阻分压器进行编程见应用资料芯片形式在25时测试§ TPS7325在全温度范围的基础上有3%的容限¶ TPS71xx与TPS72xx分别是500mA与250 mA输出的稳压器可进行与TPS37xx相似的操作但是没有延时复位的功能TPS72xx系列器件还可以通过其8引脚扁平缩小型封装TSSOP来区分这种封装适合于需要最小封装尺寸的应用用PMOS器件代替典型的PNP旁路晶体管可以使常规LDO的下降电压与静态电流逐级下降因为PMOS器件可用作一个低阻值电阻而下降电压也非常低TPS7350在输出电流为100mA时其最大下降电压为35mV它与输出电流成正比见图1此外因为PMOS通路元件是由电压驱动所以静态电流为低并保持恒定不受输出负载在整个输出电流范围0mA至500mA内典型值为340A影响这两项关键指标大大延长了电池供电系统的使用寿命休眠模式也是该LDO系列的一大特色在EN enable脚上加一个逻辑高电平的信号可关断稳=25时的最大值压器将静态电流减至0.5A TTPS73xx系列既包含2.5V3V 3.3V 4.85V5V的固定输出电压型器件也有一种可调电压型器件输出电压可在1.2V到9.75V范围内编程在电源负载与温度范围内规定输出电压的最大容限为2%对于2.5V器件与可调器件则为3%TPS37xx系列有PDIP8脚SO8脚与TSSOP20脚这几种封装形式TSSOP的最大高度为1.2mm图1 下降电压与输出电流的关系† TPS7325, TPS7330, TPS7333, TPS7348, TPS7350固定电压型器件‡ 电容的选择非常重要详情见应用资料一节图2 典型应用配置TPS73xxY的芯片信息这些芯片若正确装配则会呈现出与TPS73xxQ类似的特性可对掺杂铝质焊片进行热压缩或超声波焊接芯片可以用导电环氧树脂或金-硅压片安装焊片配置芯片厚度典型值15焊片最小4X4=150T容限10%所有的尺寸均以密耳为单位† SENSE仅限于固定电压器件TPS7325TPS7330TPS7333TPS7348与TPS7350‡ FB仅限于可调输出器件TPS7301注A对于多数应用OUT与SENSE脚应连接在尽可能靠近器件的位置其它信息请参考本数据手册的应用资料一节中有关SENSE脚连接法的论述功能方框图§ 对于多数应用SENSE脚应在外部连接到OUT脚尽可能地靠近器件其它信息请参考应用资料一节中有关SENSE脚连接法的论述¶ 开关位置如图所示EN脚为低电平有效时序图† Vres是有效RESET要求的最小输入电压符号Vres还未列入EIA或JEDE半导体符号体系标准在工作温度范围内自然通风的极限参数除非另有说明‡输入电压范围§VI RESET SENSE EN0.3V至11V输出电流IO2A 持续总功耗见额定功耗表1和表2工作实际结温范围TJ55到150贮存温度范围Tstg65到150引线温度距外壳1.6mm1/16英寸10秒260‡ 强度超出所列的极限参数可能导致器件的永久性损坏这些仅仅是极限参数并不意味着在极限条件下或在任何其它超出推荐工作条件所示参数的情况下器件能有效工作延长在极限参数条件下的工作时间会影响器件的可靠性§ 所有的电压值均相对于网络端点地network terminal ground额定功耗表1自然通风温度见图3额定功耗表2外壳温度见图4† 对于使用TSSOP封装时需考虑的功耗问题请参考热信息一节最大持续功耗与自然通风温度的关系最大持续功耗与外壳温度的关系图3 图4推荐工作条件† 推荐工作条件中定义的最小输入电压指规定的最大输出电压加上最大规定负载范围内的下降电压V DO 因为下降电压是输出电流的函数所以可用范围可扩展到更轻的负载可用以下公式计算指定应用中最大负载电流情况下的最小输入电压V I min=V O max+V DO max load因为TPS7301是可编程的在应用以上公式之前应该用r DS(on)来计算VDO 用r DS(on)计算VDO的公式见TPS7301电气特性表下的注释2最小值2.97V适用于TPS7301的推荐输入电压范围极限值的下限电气特性I=10mA, EN=0V, C O=4.7F(CSR‡=1), SENSE/FB短接到OUT时除非另有说明O‡ CSR补偿串联电阻指串联电阻的总阻值包括电容器的等效串联电阻ESR任何外部串联电阻端的PWB连线电阻与接到CO§ 采用脉冲测试技术来使实际结温尽可能地接近周围环境温度必须单独考虑热效应TPS7301Q 的电气特性IO =10mA, V I =3.5V , EN =0V , C O =4.7F(CSR†=1), FB 短接到OUT 时除非另有说明† CSR 补偿串联电阻指串联电阻的总阻值包括电容的等效串联电阻ESR任何外部串联电阻与接到C O 端的PWB 连线电阻‡ 采用脉冲测试技术来使实际结温尽可能地接近周围环境温度必须单独考虑热效应§ 用闭环配置可将输出电压编程为2.5V 见应用资料注1 当VI <2.9V 同时I O >150mA 时通路元件r DS(on)上升到某值见图33此时所得的下降电压使稳压器不能保持规定的容限范围2 要计算下降电压可用公式V DO =I O r DS(on)r DS(on)是输出电流与输入电压的函数此参数表列出了V I =2.4 V , 2.9 V , 3.9 V 与5.9 V 时的r DS(on)它们分别与2.5 V, 3 V, 4 V , 6 V 编程输出电压的下降情况对应其它可编程值请参考图33TPS7325Q的电气特性I=10mA, V I=3.5V, EN=0V, C O=10F(CSR†=1), SENSE短接到OUT时除非另有说明† CSR补偿串联电阻指串联电阻的总阻值包括电容的等效串联电阻ESR任何外部串联电阻与端的PWB连线电阻接到CO‡ 采用脉冲测试技术来使实际结温尽可能地接近周围环境温度必须单独考虑热效应§ 下降测试与通路元件的串联电阻测试不是生产测试测试方法要求SENSE端从输出电压端断开TPS7330Q的电气特性I=10mA, V I=4V, EN=0V, C O=4.7F(CSR†=1), SENSE短接到OUT时O除非另有说明† CSR补偿串联电阻指串联电阻的总阻值包括电容的等效串联电阻ESR任何外部串联电阻与接到C端的PWB连线电阻O‡ 采用脉冲测试技术来使实际结温尽可能地接近周围环境温度必须单独考虑热效应TPS7333Q的电气特性I=10mA, V I=4.3V, EN=0V, C O=4.7F(CSR†=1), SENSE短接到OUT时除非另有说明† CSR补偿串联电阻指串联电阻的总阻值包括电容的等效串联电阻ESR任何外部串联电阻与端的PWB连线电阻接到CO‡ 采用脉冲测试技术来使实际结温尽可能地接近周围环境温度必须单独考虑热效应TPS7348Q的电气特性I=10mA, V I=5.85V, EN=0V, C O=4.7F(CSR†=1), SENSE短接到OUTO时除非另有说明† CSR补偿串联电阻指串联电阻的总阻值包括电容的等效串联电阻ESR任何外部串联电阻与端的PWB连线电阻接到CO‡ 采用脉冲测试技术来使实际结温尽可能地接近周围环境温度必须单独考虑热效应TPS7350Q的电气特性I=10mA, V I=6V, EN=0V, C O=4.7F(CSR†=1), SENSE短接到OUT时O除非另有说明† CSR补偿串联电阻指串联电阻的总阻值包括电容的等效串联电阻ESR任何外部串联电阻与端的PWB连线电阻接到CO‡ 采用脉冲测试技术来使实际结温尽可能地接近周围环境温度必须单独考虑热效应开关特性电气特性I=10mA, EN=0V, C O=4.7F(CSR†=1), T J=25, SENSE/FB短接到OUT时除非另有说明† CSR补偿串联电阻指串联电阻的总阻值包括电容的等效串联电阻ESR任何外部串联电阻与接到C端的PWB连线电阻O‡ 采用脉冲测试技术来使实际结温尽可能地接近周围环境温度必须单独考虑热效应TPS7301Y的电气特性I=10mA, V I=3.5V, EN=0V, C O=4.7F(CSR†=1), T J=25, FB短接到OOUT时除非另有说明† CSR补偿串联电阻指串联电阻的总阻值包括电容的等效串联电阻ESR任何外部串联电阻与端的PWB连线电阻接到CO‡ 采用脉冲测试技术来使实际结温尽可能地接近周围环境温度必须单独考虑热效应§ 用闭环配置可将输出电压编程为2.5V见应用资料注<2.9V同时I O>150mA时通路元件r DS(on)上升到某值见图33此时所得的下降电压将使1当V稳压器不能保持规定的容限范围2要计算下降电压可用公式V=I O r DS(on)r DS(on)是输出电流与输入电压的函数此参数表列出了V I=2.4 V, 2.9 V, 3.9 V与5.9 V时的r DS(on)它们分别与2.5 V, 3 V, 4 V, 6 V编程输出电压的下降情况对应其它可编程值请参考图33TPS7325Y的电气特性I=10mA, V I=3.5V, EN=0V, C O=10F(CSR†=1), T J=25, SENSE短接O到OUT时除非另有说明† CSR补偿串联电阻指串联电阻的总阻值包括电容的等效串联电阻ESR任何外部串联电阻与端的PWB连线电阻接到CO‡ 采用脉冲测试技术来使实际结温尽可能地接近周围环境温度必须单独考虑热效应§ 下降测试与通路元件的串联电阻测试不是生产测试测试方法要求SENSE端从输出电压端断开TPS7330Y的电气特性I=10mA, V I=4V, EN=0V, C O=4.7F(CSR†=1), T J=25, SENSE短接O到OUT时除非另有说明† CSR补偿串联电阻指串联电阻的总阻值包括电容的等效串联电阻ESR任何外部串联电阻与端的PWB连线电阻接到CO‡ 采用脉冲测试技术来使实际结温尽可能地接近周围环境温度必须单独考虑热效应TPS7333Y的电气特性I=10mA, V I=4.3V, EN=0V, C O=4.7F(CSR†=1), T J=25, SENSE短接O到OUT时除非另有说明† CSR补偿串联电阻指串联电阻的总阻值包括电容的等效串联电阻ESR任何外部串联电阻与端的PWB连线电阻接到CO‡ 采用脉冲测试技术来使实际结温尽可能地接近周围环境温度必须单独考虑热效应TPS7348Y的电气特性I=10mA, V I=5.85V, EN=0V, C O=4.7F(CSR†=1), T J=25, SENSE短O接到OUT时除非另有说明† CSR补偿串联电阻指串联电阻的总阻值包括电容的等效串联电阻ESR任何外部串联电阻与端的PWB连线电阻接到CO‡ 采用脉冲测试技术来使实际结温尽可能地接近周围环境温度必须单独考虑热效应TPS7350Y的电气特性I=10mA, V I=6V, EN=0V, C O=4.7F(CSR†=1), T J=25, SENSE短接O到OUT时除非另有说明† CSR补偿串联电阻指串联电阻的总阻值包括电容的等效串联电阻ESR任何外部串联电阻与端的PWB连线电阻接到CO‡ 采用脉冲测试技术来使实际结温尽可能地接近周围环境温度必须单独考虑热效应参数测试资料图5 测试电路与电压波形† 陶瓷电容图6 典型稳定区域的测试电路参照图29至图32典型特性曲线典型特性图列表静态电流与输出电流的关系静态电流与输入电压的关系图7 图8TPS7348的静态电流与自然通风温度的关系TPS7325的静态电流与输入电压的关系图9 图10TPS7325的静态电流与自然通风温度的关系下降电压与输出电流的关系图11 图12下降电压的变化量与自然通风温度的关系TPS7301的下降电压与输出电流的关系图13 图14输出电压的变化量与自然通风温度的关系输出电压与输入电压的关系图15 图16TPS7325的输出电压与输入电压的关系电源调节图17 图18TPS7301的输出电压与输出电流的关系TPS7325的输出电压与输出电流的关系图19 图20TPS7330的输出电压与输出电流的关系TPS7333的输出电压与输出电流的关系图21 图22TPS7348的输出电压与输出电流的关系TPS7350的输出电压与输出电流的关系图23 图24对使能信号EN的输出电压响应图25TPS7301V O被编程为2.5V或TPS7333的负载瞬态响应图26TPS7325的负载瞬态响应图27TPS7348或TPS7350的负载瞬态响应图28TPS7301V O被编程为2.5V的电源瞬态响应图29TPS7333的电源瞬态响应图30TPS7348或TPS7350的电源瞬态响应图31纹波抑制与频率的关系 输出噪声频谱密度与频率的关系图32 图33典型稳定区域补偿串联电阻CSR †与输出电流的关系典型稳定区域补偿串联电阻CSR †与外加陶瓷电容的关系图34 图35典型稳定区域补偿串联电阻CSR †与输出电流的关系典型稳定区域补偿串联电阻CSR †与外加陶瓷电容的关系图36 图37通路元件电阻与输入电压的关系 有效RESET 最小输入电压与自然通风温度的关系图38 图39负向复位门限与自然通风温度的关系RESET输出电流与输入电压的关系图40 图41复位延迟时间与自然通风温度的关系复位延时的分布图42 图43热信息为适应系统微型化的潮流集成电路多采用低剖面小口距的表面安装封装形式在使用这种封装形式的高性能器件时多数要特别注意其功耗许多由系统决定的问题例如热耦合通风所采用的散热片对流面以及其它发热元件的使用都会影响指定元件的功耗极限以下会讨论可以改善热性能的三种基本方法z 改善PWB 设计的功耗容量z 改进元件与PWB 的热耦合z 将气流引入系统图44是20脚TSSOP 封装的热性能增强型PWB 布局实例这种布局方法包括加铜块到PWB 来将热量导离器件用于该元件/电路板系统的R JA 热电阻结点到周围环境如图45所示这一系列曲线图显示了扩大铜散热片表面面积的所产生的影响该PWB 是标准的FR4电路板长X 宽X 高=3.2英寸X 3.2英寸X 0.062英寸电路板的连线与散热片为1盎司每平方英尺的铜料图46显示了用于同一系统的热电阻同时在TSSOP 封装的主体部分与器件下方的PWB 铜面之间加置了导热化合物此例中化合物的导热性为0.815W/m根据这些图形来确定系统的R JA 最大功耗极限可由以下公式算出P D(max) = [T J(max) – T A ]/ R JA (system)其中T J(max)指允许的最高结温150的极限参数与125的最高推荐工作温度用于特定的操作此极限应该用于TPS73xx 稳压器的内部功耗限制计算TPS73xx 内部总功耗的公式为P D(total)=V I V O I O +V I I Q因为TPS73xx 系列产品的静态电流很低第二部分可以被忽略可将以上从公式进一步简化为P D(total)=V I V O I O对于一个20脚的TSSOP/FR4电路板系统若在电路板与器件主体之间带有导热化合物且TA =55气流=100英尺/分钟铜散热片的面积=1cm 2则可以算出其最大功耗极限 如图46所示系统R JA为94/W 因此最大功耗极限是PD(max) = [T J(max) – T A ]/ R JA (system)=12555/94/W=745mW 如果系统采用的是TPS7348稳压器此时VI =6V I O =150mA 内部功耗则为PD(total)=V I V OI O =64.850.150=173 mW比较P D(max)与P D(total)则可发现此例中的功耗未超出最大极限在超出最大极限时有两种校正措施可使用可通过增加气流或散热片的面积来增加功耗极限值或者可以通过减少输入电压或负载电流来降低稳压器的内部功耗无论用哪种方法都要以新的系统参数来重新进行以上计算过程图44 20脚TSSOP的热性能增强型PWB布局不按比例热电阻结点到周围环境与气流的关系热电阻结点到周围环境与气流的关系图45 图46应用资料TPS73xx系列低压差稳压器弥补了前一代稳压器的许多不足之处增加了许多新的特色设计如节电关断模式与电源电压监控器TPS73xx系列含有五种固定输出电压的稳压器TPS7325 (2.5 V), TPS7330 (3 V), TPS7333(3.3 V), TPS7348 (4.85 V)和TPS7350 (5 V)该系列还可有一种可调稳压器TPS7301可调电压范围 1.2V至9.75V器件的工作TPS73xx系列产品不像其它的LDO它们以极低的静态电流为特点其静态电流即使在变化不定的负载下也可以保持恒定传统LDO稳压器使用的是PNP通路元件其基极电流与流过稳压器的负载电流成/仔细审阅数据手册可发现对这些器件的典型规定值是在无负载的条件下的参数实际正比IB=I工作电流则要高得多如典型静态电流与负载电流的关系曲线图图7所示TPS73xx用PMOS晶体管来传送电流因为PMOS元件的栅极是由电压驱动的所以工作电流低并且在全负载范围内是不可变的TPS73xx的规格参数反映了有负载时的实际性能的增加以维持负载电PNP通路元件的其它缺陷是在器件下降时PNP元件易于饱和的下降迫使I流在上电期间这就被当作是较大的启动电流限定电源电流的系统可能不能启动在电池供电的系统中当电压降低到要求的最小调节电压以下时则意味着电池被快速放电而TPS73xx即使是在稳压器下降时其静态电流也保持为低因而可以避免这两种问题TPS73xx系列还包括一个4.85V的稳压器TPS7348它是专为5V的移动电话系统设计输出电压为4.85V并且可以在2%的范围内进行调节可以在容限为5%的5V系统的下限工作因此在器件下降之前可以从电池组获得最长的稳定工作寿命包括每次充电之间的重要通话时间TPS73xx系列产品还以关断模式为特点可以将输出端置于高阻抗状态实质上等于反馈分压电阻并将静态电流降低到0.5A在不使用关断功能时应将EN脚接地器件对使能端的跃变反应很快重建稳定输出电压的典型时间是120s最小负载要求TPS73xx系列产品即使是在负载为0时也可保持稳定工作时没有最小负载要求SENSE端的连接为了使稳压器正常工作固定输出器件的SENSE端必须连接到稳压器的输出端通常这种连接应尽可能短但是可以在靠近关键回路处远程检测进行连接以增强该处的性能在内部SENSE端通过电阻分压器网络连接到一个高阻抗宽带放大器噪声拾取则馈送到稳压器的输出端按这种方法连接SENSE端是很有必要的这样可以最小化或避免噪声拾取不推荐在SENSE与OUT端之间加一个RC 网络来滤除噪声因为这种方法可能会导致稳压器振荡外部电容要求不需要输入电容但是当TPS73xx位于离电源几英寸远的地方时使用陶瓷旁路电容0.047pF到0.1 F可以改善负载瞬态响应与噪声抑制功能如果预计在快速上升时间内会出现大负载几百毫安瞬变现象则可能需要一个大电容量的电解电容与多数低压差稳压器一样TPS73xx系列产品也需要一个输出电容来保持稳定一个连接在稳压器输出端与地线之间的低ESR等效串联电阻10F的固态钽电容就足以保证全负载范围内器件的稳定性见图42使用高频率的陶瓷或薄膜电容例如用于数字或模拟IC的电源旁路电容会导致稳压器不稳定除非钽电容的ESR在温度范围内低于1.2明确标出ESR规格的电容如AVX TPSD106M035R0300与Sprague 593D106X0035D2W就很适合因为25时最大ESR为300m通常当温度从25下降到40时固态钽电容的ESR则要乘以2或小于2的因数在对元件的高度与/或安装面积有要求的应用中可以使用对ESR进行了筛选的10F或者更小的器件图29到图32显示了使用不同输出电容与不同陶瓷负载电容时的稳定工作区域在带有小旁路电容<0.2F或者不带高频旁路电容的应用中假如ESR保持在0.7至2.5之间输出电容就可减少至4.7F因为对电容的最小ESR的规定很少必须加一个与电容串联的0.5到1的电阻并将ESR的最大值限制在1.5以内如CSR曲线图图29到图32所示在使用10F或更大的输出电容时可以不用考虑最小ESR以下是适合TPS73xx系列产品的部分表面安装的电容列表这些信息与CSR典线图均是为了帮助用户选择适合的电容器若要使器件的高度更低同时需要高输出电流与/或陶瓷高负载电容可以并联几种较高ESR的电容来达到以上要求所有的负载与温度条件下最大1F的陶瓷负载电容器件号制造商数值最大ESR†大小高长宽†T421C226M010AS Kemet22F, 10 V0.5 2.86 3.2593D156X0025D2W Sprague15F, 25 V0.3 2.87.3 4.3593D106X0035D2W Sprague10F, 35 V0.3 2.87.3 4.3TPSD106M035R0300A VX10F, 35 V0.3 2.87.3 4.3负载<200mA陶瓷负载电容<0.2F全温度范围器件号制造商数值最大ESR†大小高长宽†592D156X0020R2T Sprague15F, 20 V 1.1 1.27.26595D156X0025C2T Sprague15F, 25 V1 2.57.1 3.2595D106X0025C2T Sprague10F, 25 V 1.2 2.57.1 3.2293D226X0016D2W Sprague22F, 16 V 1.1 2.87.3 4.3负载<100mA陶瓷负载电容<0.2F全温度范围器件号制造商数值最大ESR†大小高长宽†195D106X06R3V2T Sprague10F, 6.3 V 1.5 1.3 3.5 2.7195D106X0016X2T Sprague10F, 16 V 1.5 1.37 2.7595D156X0016B2T Sprague15F, 16 V 1.8 1.6 3.8 2.6695D226X0015F2T Sprague22 F, 15 V 1.4 1.8 6.5 3.4695D156X0020F2T Sprague15F, 20 V 1.5 1.8 6.5 3.4695D106X0035G2T Sprague10F, 35 V 1.3 2.57.6 2.5† 尺寸大小以毫米为单位ESR是100kHz T A=25时的最大电阻器件按高度排序† TPS7333, TPS7348, TPS7350固定电压产品图47 典型应用电路对TPS7301可调低压差稳压器进行编程通过图43所示的外部电阻分压器可以对可调稳压器编程计算输出电压的公式为= Vref 1+R1/R2V其中Vref指基准电压典型值为1.182V电阻R1与R2是为7A左右的分压器电流而选择推荐的R2阻值为169k而R1则根据所需的输出电压来调节也可使用更小的电阻但是具备内在优势而且会消耗更多电能应避免使用较大阻值的R1与R2因为FB脚上的漏泄电流会引起误差为计算R1可推导出一个更有用的公式可用于选择恰当的电阻R1=V O / Vref 1R2输出电压编程指南图48 对TPS7301可调低压差稳压器进行编程欠压监控功能在欠压情况下TPS73xx的RESET输出脚可在微型计算机与微处理器系统中启动一次复位操作TPS73xx的内部比较器监控稳压器的输出电压来检测欠压情况一旦这种情况出现RESET输出晶体管接通将RESET信号拉低上电时输出电压跟踪输入电压在V达到有效RESET信号要求的最小值25时为1.5V在推荐的工作温度范围内为 1.9V时RESET输出端变为有效低电平在输出电压大约达到正向输入门时一次200ms典型值的延时开始在此期间RESET输出端保持低电平一旦延时限电压V终止RESET输出端变为无效因为RESET输出端是漏极开路NMOS需要加上拉电阻以确保可以显示逻辑高电平信号在掉电期间该电源电压监控功能也有效在输入电压衰减并且达到下降电压时输出电压与逐见电气特步衰减的输入电压成线性比例当输出电压下降到低于规定的负向输入门限电压V性表时RESET输出端变为有效低电平必须注意如果输入电压衰减到有效RESET要求的最小电压以下则RESET的状态不确定因为该电路监控着稳压器的输出电压RESET输出端也可以通过禁止稳压器或者通过任何导致输出电压下降到低于V的故障条件来触发这类故障情形包括例如输出端的短路或输入电压低一旦输IT出电压被重新设置无论是通过重新使能稳压器还是通过排除故障条件内部定时器就会被启动这样就会使RESET信号在200ms典型值的超时周期内处于有效状态如果在选择输入与输出电容时不适当地加以注意瞬变负载或电源线脉冲也有可能导致复位如果使用的是高ESR输出电容大约大于7则5s以下的负载瞬变现象也会导致一次复位若使用的是ESR大于3.5的输出电容则1s的瞬变就会导致复位注意瞬变现象中输出电压的峰值会下降到刚好低于复位门限并且如果瞬变持续的时间短这一峰值电压还会保持不变在触发复位电路以前1s的瞬变必须下降到低于门限至少500mV在正好低于门限电压400mV时2s的瞬变会触发RESET较低的ESR输出电容在瞬变中有助于减少输出电压的下降程度而且在希望瞬变快速进行时也应该采用较低ESR的输出电容注V= V IT + 滞后量IT+输出噪声TPS73xx的输出噪声极低其噪声频谱密度<2V/Hz在噪声敏感的系统如音频放大器由稳压器供电时这一点是非常重要的稳压器保护TPS73xx的PMOS通路晶体管有一个内置的反向二极管在输入电压下降到输出电压以下时例如在掉电期间可以安全地传导反向电流电流被从输出端导向输入端并且在内部不受限制如果预计有较大的反向电压那么采取外部限制措施可能比较适合TPS73xx还具有内部电流限制与热保护的特点在正常工作期间TPS73xx将输出电流限制在1A左右在电流受到限制时输出电压按线性规律反比例变化直到过流情况结束为止在电流限制功能被设计成防止整个器件出现故障时必须注意不要超过封装的额定功耗如果器件的温度超过165热保护电路则会将器件关断一旦器件冷却下来稳压器就可恢复工作。

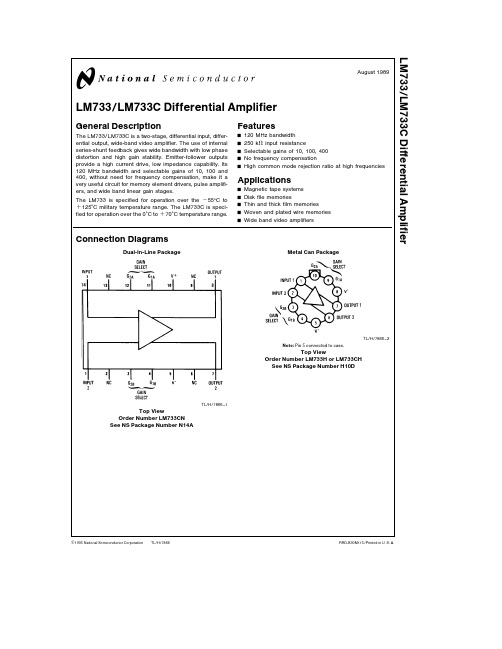

LM733中文资料

TL H 7866LM733 LM733C Differential AmplifierAugust 1989LM733 LM733C Differential AmplifierGeneral DescriptionThe LM733 LM733C is a two-stage differential input differ-ential output wide-band video amplifier The use of internal series-shunt feedback gives wide bandwidth with low phase distortion and high gain stability Emitter-follower outputs provide a high current drive low impedance capability Its 120MHz bandwidth and selectable gains of 10 100and 400 without need for frequency compensation make it a very useful circuit for memory element drivers pulse amplifi-ers and wide band linear gain stagesThe LM733is specified for operation over the b 55 C to a 125 C military temperature range The LM733C is speci-fied for operation over the 0 C to a 70 C temperature rangeFeaturesY 120MHz bandwidth Y 250k X input resistanceY Selectable gains of 10 100 400Y No frequency compensationYHigh common mode rejection ratio at high frequenciesApplicationsY Magnetic tape systems Y Disk file memoriesY Thin and thick film memoriesY Woven and plated wire memories YWide band video amplifiersConnection DiagramsDual-In-Line PackageTL H 7866–1Top ViewOrder Number LM733CN See NS Package Number N14AMetal Can PackageTL H 7866–2Note Pin 5connected to caseTop ViewOrder Number LM733H or LM733CH See NS Package Number H10DC 1995National Semiconductor Corporation RRD-B30M115 Printed in U S AAbsolute Maximum RatingsIf Military Aerospace specified devices are required please contact the National Semiconductor Sales Office Distributors for availability and specifications Diffential Input Voltage g5V Common Mode Input Voltage g6V V CC g8V Output Current10mA Power Dissipation(Note1)500mW Junction Temperature a150 C Storage Temperature Range b65 C to a150 C Operating Temperature RangeLM733b55 C to a125 C LM733C0 C to a70 C Lead Temperature(Soldering 10sec )260 CElectrical Characteristics(T A e25 C unless otherwise specified see test circuits V S e g6 0V)Characteristics Test Test Conditions LM733LM733CUnitsCircuit Min Typ Max Min Typ MaxDifferential Voltage GainGain1(Note2)300400500250400600Gain2(Note3)19010011080100120Gain3(Note4)R L e2k X V OUT e3Vp-p9 010118 01012BandwidthGain14040MHz Gain229090MHz Gain3120120MHzRise TimeGain1V OUT e1Vp-p10 510 5ns Gain224 5104 512ns Gain32 52 5nsPropagation Delay V OUT e1Vp-pGain17 57 5ns Gain226 0106 010ns Gain33 63 6nsInput ResistanceGain14 04 0k X Gain220301030k X Gain3250250k XInput Capacitance Gain22 02 0pFInput Offset Current0 43 00 45 0m AInput Bias Current9 0209 030m AInput Noise Voltage BW e1kHz to10MHz1212m VrmsInput Voltage Range1g1 0g1 0VCommon Mode Rejection RatioGain21V CM e g1V f s100kHz60866086dB Gain2V CM e g1V f e5MHz6060dBSupply Voltage Rejection RatioGain21D V S e g0 5V50705070dBOutput Offset VoltageGain11R L e%0 61 50 61 5V Gain2and30 351 00 351 5VOutput Common Mode Voltage1R L e%2 42 93 42 42 93 4VOutput Voltage Swing1R L e2k3 04 03 04 0Output Sink Current2 53 62 53 6mAOutput Resistance2020XPower Supply Current1R L e%18241824mA2Electrical Characteristics (Continued)(The following specifications apply for b 55 C k T A k 125 C for the LM733and 0 C k T A k 70 C for the LM733C V S e g 6 0V)CharacteristicsTest Test ConditionsLM733LM733CUnitsCircuitMin TypMax Min TypMax Differential Voltage Gain Gain 1200600250600Gain 21R L e 2k X V OUT e 3Vp-p8012080120Gain 38 012 08 012 0Input Resistance Gain 288k X Input Offset Current 56m A Input Bias Current 4040m A Input Voltage Range1g 1g 1V Common Mode Rejection Ratio Gain 21V CM e g 1V f s 100kHz 5050dB Supply Voltage Rejection Ratio Gain 21D V S e g 0 5V 5050dBOutput Offset Voltage Gain 11R L e %1 51 5V Gain 2and 31 21 5V Output Voltage Swing 1R L e 2k2 52 8V pp Output Sink Current 2 22 5mAPower Supply Current1R L e %2727mANote 1 The maximum junction temperature of the LM733is 150 C while that of the LM733C is 100 C For operation at elevated temperatures devices in the TO-100package must be derated based on a thermal resistance of 150 C W junction to ambient or 45 C W junction to case Thermal resistance of the dual-in-line package is 90 C WNote 2 Pins G1A and G1B connected together Note 3 Pins G2A and G2B connected together Note 4 Gain select pins openNote 5 Refer to RETS733X drawing for specifications of LM733H versionTypical Performance CharacteristicsPulse ResponseTemperaturePulse Response vs Supply VoltagePulse Response vs vs Frequency Phase Shift vs Frequency Phase Shift Recovery TimeDifferential Overdrive TL H 7866–63Typical Performance Characteristics (Continued)Voltage Gain vs FrequencyTemperatureGain vs Frequency Supply VoltageGain vs Frequency vs Voltage Gain vs R ADJVoltage Gain vs TemperatureSupply VoltageVoltage Gain vs FrequencyOutput Voltage Swing vs Voltageand Current Swing vs Supply Supply Current Output Voltage Load ResistanceOutput Voltage Swing vs Ratio vs Frequency Common Mode Rejection Source Resistance Input Noise Voltage vs Resistance vs TemperatureSupply Current and Input TL H 7866–74Test CircuitsTest Circuit1TL H 7866–3Test Circuit2TL H 7866–4Voltage Gain Adjust CircuitTL H 7866–5V S e6V T A e25 C(Pin numbers apply to TO-5package)Schematic DiagramTL H 7866–85L M 733 L M 733C D i f f e r e n t i a l A m p l i f i e rPhysical Dimensions inches (millimeters)Metal Can Package (H)Order Number LM733H or LM733CHNS Package Number H10DMolded Dual-In-Line Package (N)Order Number LM733CN NS Package Number N14ALIFE SUPPORT POLICYNATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION As used herein 1 Life support devices or systems are devices or 2 A critical component is any component of a life systems which (a)are intended for surgical implant support device or system whose failure to perform can into the body or (b)support or sustain life and whose be reasonably expected to cause the failure of the life failure to perform when properly used in accordance support device or system or to affect its safety or with instructions for use provided in the labeling can effectivenessbe reasonably expected to result in a significant injury to the userNational Semiconductor National Semiconductor National Semiconductor National Semiconductor CorporationEuropeHong Kong LtdJapan Ltd1111West Bardin RoadFax (a 49)0-180-530858613th Floor Straight Block Tel 81-043-299-2309。

733机型熟悉的讲义

飞机制造商为了加速飞机的生产,按设计和 工艺要求将飞机分成许多段件,生产后再 组装成整架飞机。

B737-300机身分成四段:41、43、46、 48

2020/12/21

Training Division of Maintenance and Engineering Dept.

12

B737飞机基本ion of Maintenance and Engineering Dept.

35

36章 气源系统

APU和地面气源也可以给系统提供气源。 APU给气源系统的左半部分提供气源,地 面气源给右半部分提供气源。

交输引气管附近上装了两个压力传感器, 分别指示左右部分的引气压力。

亿飞行小时,2.32亿个航班,759亿海里。 目前全球共有104个国家的347家航空公司拥有

737系列飞机。

2020/12/21

Training Division of Maintenance and Engineering Dept.

8

B737飞机基本介绍

➢ 基本尺寸

3.76m

28.88m

11.13m

2020/12/21

Training Division of Maintenance and Engineering Dept.

13

B737飞机基本介绍

➢ 飞机区域编号

2020/12/21

Training Division of Maintenance and Engineering Dept.

14

2020/12/21

Training Division of Maintenance and Engineering Dept.

10

AN7337NS资料

AN7337NS

7-element graphic equalizer IC for Hi-Fi audio equipment

s Overview

The AN7337NS is a graphic equalizer IC for high performance Hi-Fi audio equipment developed for deck. It incorporates an output buffer circuit and 7 resonance buffer circuits, and can set resonance frequency by external capacitor.

GND

17

or m

SOP020-P-0300B

at io n.

1

AN7337NS

s Pin Descriptions

Pin No. 1 2 3 4 5 6 7 8 9 In 1 NF 1 In 2 NF 2 In 3 NF 3 In 4 In 5 NF 4 Description Pin No. 11 12 13 14 15 16 17 18 19 20

(1) If any of the products or technical information described in this book is to be exported or provided to non-residents, the laws and regulations of the exporting country, especially, those with regard to security export control, must be observed. (2) The technical information described in this book is intended only to show the main characteristics and application circuit examples of the products, and no license is granted under any intellectual property right or other right owned by our company or any other company. Therefore, no responsibility is assumed by our company as to the infringement upon any such right owned by any other company which may arise as a result of the use of technical information described in this book. (3) The products described in this book are intended to be used for standard applications or general electronic equipment (such as office equipment, communications equipment, measuring instruments and household appliances). Consult our sales staff in advance for information on the following applications: – Special applications (such as for airplanes, aerospace, automobiles, traffic control equipment, combustion equipment, life support systems and safety devices) in which exceptional quality and reliability are required, or if the failure or malfunction of the products may directly jeopardize life or harm the human body. – Any applications other than the standard applications intended. (4) The products and product specifications described in this book are subject to change without notice for modification and/or improvement. At the final stage of your design, purchasing, or use of the products, therefore, ask for the most up-to-date Product Standards in advance to make sure that the latest specifications satisfy your requirements. (5) When designing your equipment, comply with the range of absolute maximum rating and the guaranteed operating conditions (operating power supply voltage and operating environment etc.). Especially, please be careful not to exceed the range of absolute maximum rating on the transient state, such as power-on, power-off and mode-switching. Otherwise, we will not be liable for any defect which may arise later in your equipment. Even when the products are used within the guaranteed values, take into the consideration of incidence of break down and failure mode, possible to occur to semiconductor products. Measures on the systems such as redundant design, arresting the spread of fire or preventing glitch are recommended in order to prevent physical injury, fire, social damages, for example, by using the products. (6) Comply with the instructions for use in order to prevent breakdown and characteristics change due to external factors (ESD, EOS, thermal stress and mechanical stress) at the time of handling, mounting or at customer's process. When using products for which damp-proof packing is required, satisfy the conditions, such as shelf life and the elapsed time since first opening the packages. (7) This book may be not reprinted or reproduced whether wholly or partially, without the prior written permission of Matsushita Electric Industrial Co., Ltd.

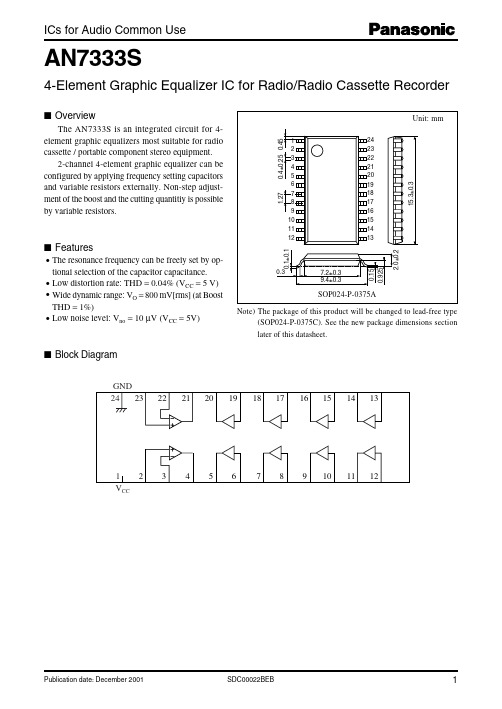

AN7333S中文资料

I Block Diagram

GND 24 23

22

21

20

19

18

17

16

15

14

1 VCC

2

3

45678 Nhomakorabea9

10

11

0.15 0.925

13

12

2.0±0.2

I Features

15.3±0.3

1.27

Publication date: December 2001

SDC00022BEB

1

元器件交易网

AN7333S

1 VCC

2

3

4

5

6 0.056 µF 0.68 µF

7

8 0.018 µF 0.22 µF

50 kΩ VR

9

10

11

12 0.0018 µF 0.022 µF

50 kΩ VR

0.0056 µF 0.068 µF

50 kΩ VR

50 kΩ VR

50 kΩ VR

10 µF 4.7 kΩ 10 µF 0.0047 µF 10 kΩ

Rating 14.4 30 432 −20 to +75 −55 to +125

ADG733资料

REV.0Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.aADG733/ADG734One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.Tel: 781/329-4700World Wide Web Site: Fax: 781/326-8703© Analog Devices, Inc., 2001CMOS, 2.5 ⍀ Low Voltage,Triple/Quad SPDT SwitchesFEATURES1.8 V to 5.5 V Single Supply ؎3 V Dual Supply2.5 ⍀ On Resistance0.5 ⍀ On Resistance Flatness 100 pA Leakage Currents 19 ns Switching Times Triple SPDT: ADG733Quad SPDT: ADG734Small TSSOP and QSOP Packages Low Power ConsumptionTTL/CMOS-Compatible Inputs APPLICATIONSData Acquisition Systems Communication Systems Relay ReplacementAudio and Video Switching Battery-Powered SystemsGENERAL DESCRIPTION The ADG733 and ADG734 are low voltage, CMOS devices comprising three independently selectable SPDT (single pole,double throw) switches and four independently selectable SPDT switches respectively.Low power consumption and operating supply range of 1.8 V to 5.5 V and dual ±3 V make the ADG733 and ADG734 ideal for battery powered, portable instruments. All channels exhibit break-before-make switching action preventing momentary shorting when switching channels. An EN input on the ADG733is used to enable or disable the device. When disabled, all chan-nels are switched OFF.These 2–1 multiplexers/SPDT switches are designed on an enhanced submicron process that provides low power dissipation yet gives high switching speed, very low on resistance, high signal bandwidths and low leakage currents. On resistance is in the region of a few ohms, is closely matched between switches and very flat over the full signal range. These parts can operate equally well in either direction and have an input signal range which extends to the supplies.The ADG733 is available in small TSSOP and QSOP packages,while the ADG734 is available in a small TSSOP package.PRODUCT HIGHLIGHTS1.Single/Dual Supply Operation. The ADG733 and ADG734 are fully specified and guaranteed with 3 V and 5 V single supply rails and ±3 V dual supply rails.2.Low On Resistance (2.5Ω typical).3.Low Power Consumption (<0.01 µW).4.Guaranteed Break-Before-Make Switching Action.FUNCTIONAL BLOCK DIAGRAMSS3BD3S3A SWITCHES SHOWN FOR A “1” INPUT LOGICENADG733/ADG734–SPECIFICATIONS1(V DD = 5 V ؎ 10%, V SS = 0 V, GND = 0 V, unless otherwise noted.)B Version–40؇CParameter25؇C to +85؇C Unit Test Conditions/CommentsANALOG SWITCHAnalog Signal Range0 V to V DD VOn Resistance (R ON) 2.5Ω typ V S = 0 V to V DD, I DS = 10 mA;4.55.0Ω max Test Circuit 1On-Resistance Match between0.1Ω typ V S = 0 V to V DD, I DS = 10 mAChannels (∆R ON)0.4Ω maxOn-Resistance Flatness (R FLAT(ON))0.5Ω typ V S = 0 V to V DD, I DS = 10 mA1.2Ω maxLEAKAGE CURRENTS V DD = 5.5 VSource OFF Leakage I S (OFF)±0.01nA typ V D = 4.5 V/1 V, V S = 1 V/4.5 V;±0.1±0.3nA max Test Circuit 2Channel ON Leakage I D, I S (ON)±0.01nA typ V D = V S = 1 V, or 4.5 V;±0.1±0.5nA max Test Circuit 3DIGITAL INPUTSInput High Voltage, V INH 2.4V minInput Low Voltage, V INL0.8V maxInput CurrentI INL or I INH0.005µA typ V IN = V INL or V INH±0.1µA maxC IN, Digital Input Capacitance4pF typDYNAMIC CHARACTERISTICS2t ON19ns typ R L = 300 Ω, C L = 35 pF;34ns max V S = 3 V, Test Circuit 4t OFF7ns typ R L = 300 Ω, C L = 35 pF;12ns max V S = 3 V, Test Circuit 4ADG733t ON(EN)20ns typ R L = 300 Ω, C L = 35 pF;40ns max V S = 3 V, Test Circuit 5t OFF(EN)7ns typ R L = 300 Ω, C L = 35 pF;12ns max V S = 3 V, Test Circuit 5Break-Before-Make Time Delay, t D13ns typ R L = 300 Ω, C L = 35 pF;1ns min V S = 3 V, Test Circuit 6Charge Injection±3pC typ V S = 2 V, R S = 0 Ω, C L = 1 nF;Test Circuit 7Off Isolation–62dB typ R L = 50 Ω, C L = 5 pF, f = 10 MHz;–82dB typ R L = 50 Ω, C L = 5 pF, f = 1 MHz;Test Circuit 8Channel-to-Channel Crosstalk–62dB typ R L = 50 Ω, C L = 5 pF, f = 10 MHz;–82dB typ R L = 50 Ω, C L = 5 pF, f = 1 MHz;Test Circuit 9–3 dB Bandwidth200MHz typ R L = 50 Ω, C L = 5 pF, Test Circuit 8C S (OFF)11pF typC D, C S (ON)34pF typPOWER REQUIREMENTS V DD = 5.5 VI DD0.001µA typ Digital Inputs = 0 V or 5.5 V1.0µA maxNOTES1Temperature range is as follows: B Version: –40°C to +85°C.2Guaranteed by design, not subject to production test.Specifications subject to change without notice.–2–REV. 0REV. 0–3–ADG733/ADG734B Version–40؇CParameter25؇C to +85؇CUnit Test Conditions/CommentsANALOG SWITCH Analog Signal Range 0 V to V DDV On Resistance (R ON )6Ω typ V S = 0 V to V DD , I DS = 10 mA;1112Ω max Test Circuit 1On-Resistance Match between 0.1Ω typ V S = 0 V to V DD , I DS = 10 mA Channels (∆R ON )0.4Ω max On-Resistance Flatness (R FLAT(ON))3Ω typ V S = 0 V to V DD , I DS = 10 mA LEAKAGE CURRENTSV DD = 3.3 VSource OFF Leakage I S (OFF)±0.01nA typ V S = 3 V/1 V, V D = 1 V/3 V;±0.1±0.3nA max Test Circuit 2Channel ON Leakage I D , I S (ON)±0.01nA typ V S = V D = 1 V or 3 V;±0.1±0.5nA max Test Circuit 3DIGITAL INPUTSInput High Voltage, V INH 2.0V min Input Low Voltage, V INL 0.4V max Input Current I INL or I INH 0.005µA typ V IN = V INL or V INH±0.1µA max C IN , Digital Input Capacitance 4pF typ DYNAMIC CHARACTERISTICS 2t ON 28ns typ R L = 300 Ω, C L = 35 pF;55ns max V S = 2 V, Test Circuit 4t OFF9ns typ R L = 300 Ω, C L = 35 pF;16ns max V S = 2 V, Test Circuit 4ADG733t ON (EN )29ns typ R L = 300 Ω, C L = 35 pF;60ns max V S = 2 V, Test Circuit 5t OFF (EN )9ns typ R L = 300 Ω, C L = 35 pF;16ns max V S = 2 V, Test Circuit 5Break-Before-Make Time Delay, t D 22ns typ R L = 300 Ω, C L = 35 pF;1ns min V S = 2 V, Test Circuit 6Charge Injection ±3pC typ V S = 1 V, R S = 0 Ω, C L = 1 nF;Test Circuit 7Off Isolation–62dB typ R L = 50 Ω, C L = 5 pF, f = 10 MHz;–82dB typ R L = 50 Ω, C L = 5 pF, f = 1 MHz;Test Circuit 8Channel-to-Channel Crosstalk –62dB typ R L = 50 Ω, C L = 5 pF, f = 10 MHz;–82dB typ R L = 50 Ω, C L = 5 pF, f = 1 MHz;Test Circuit 9–3 dB Bandwidth 200MHz typ R L = 50 Ω, C L = 5 pF, Test Circuit 8C S (OFF)11pF typ CD , C S (ON)34pF typ POWER REQUIREMENTS V DD = 3.3 VI DD0.001µA typ Digital Inputs = 0 V or 3.3 V1.0µA maxNOTES 1Temperature ranges are as follows: B Version: –40°C to +85°C.2Guaranteed by design, not subject to production test.Specifications subject to change without notice.(V DD = 3 V ؎ 10%, V SS = 0 V, GND = 0 V, unless otherwise noted.)SPECIFICATIONS1ADG733/ADG734–SPECIFICATIONS1DUAL SUPPLY(V DD = +3 V ؎ 10%, V SS = –3 V ؎ 10%, GND = 0 V, unless otherwise noted.)B Version–40؇CParameter25؇C to +85؇C Unit Test Conditions/CommentsANALOG SWITCHAnalog Signal Range V SS to V DD VOn Resistance (R ON) 2.5Ω typ V S = V SS to V DD, I DS = 10 mA;4.55.0Ω max Test Circuit 1On-Resistance Match between0.1Ω typ V S = V SS to V DD, I DS = 10 mAChannels (∆R ON)0.4Ω maxOn-Resistance Flatness (R FLAT(ON))0.5Ω typ V S = V SS to V DD, I DS = 10 mA1.2Ω maxLEAKAGE CURRENTS V DD = +3.3 V, V SS = –3.3 VSource OFF Leakage I S (OFF)±0.01nA typ V S = +2.25 V/–1.25 V, V D = –1.25 V/+2.25 V;±0.1±0.3nA max Test Circuit 2Channel ON Leakage I D, I S (ON)±0.01nA typ V S = V D = +2.25 V/–1.25 V, Test Circuit 3±0.1±0.5nA maxDIGITAL INPUTSInput High Voltage, V INH 2.0V minInput Low Voltage, V INL0.4V maxInput CurrentI INL or I INH0.005µA typ V IN = V INL or V INH±0.1µA maxC IN, Digital Input Capacitance4pF typDYNAMIC CHARACTERISTICS2t ON21ns typ R L = 300 Ω, C L = 35 pF;35ns max V S = 1.5 V, Test Circuit 4t OFF10ns typ R L = 300 Ω, C L = 35 pF;16ns max V S = 1.5 V, Test Circuit 4ADG733t ON(EN)21ns typ R L = 300 Ω, C L = 35 pF;40ns max V S = 1.5 V, Test Circuit 5t OFF(EN)10ns typ R L = 300 Ω, C L = 35 pF;16ns max V S = 1.5 V, Test Circuit 5Break-Before-Make Time Delay, t D13ns typ R L = 300 Ω, C L = 35 pF;1ns min V S = 1.5 V, Test Circuit 6Charge Injection±5pC typ V S = 0 V, R S = 0 Ω, C L = 1 nF;Test Circuit 7Off Isolation–62dB typ R L = 50 Ω, C L = 5 pF, f = 10 MHz;–82dB typ R L = 50 Ω, C L = 5 pF, f = 1 MHz;Test Circuit 8Channel-to-Channel Crosstalk–62dB typ R L = 50 Ω, C L = 5 pF, f = 10 MHz;–82dB typ R L = 50 Ω, C L = 5 pF, f = 1 MHz;Test Circuit 9–3 dB Bandwidth200MHz typ R L = 50 Ω, C L = 5 pF, Test Circuit 8C S (OFF)11pF typC D, C S (ON)34pF typPOWER REQUIREMENTS V DD = 3.3 VI DD0.001µA typ Digital Inputs = 0 V or 3.3 V1.0µA maxI SS0.001µA typ V SS = –3.3 V1.0µA max Digital Inputs = 0 V or 3.3 VNOTES1Temperature range is as follows: B Version: –40°C to +85°C.2Guaranteed by design, not subject to production test.Specifications subject to change without notice.–4–REV. 0REV. 0ADG733/ADG734–5–ABSOLUTE MAXIMUM RATINGS 1(T A = 25°C unless otherwise noted)V DD to V SS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7 V V DD to GND . . . . . . . . . . . . . . . . . . . . . . . . . .–0.3 V to +7 V V SS to GND . . . . . . . . . . . . . . . . . . . . . . . . . .+0.3 V to –3.5 V Analog Inputs 2 . . . . . . . . . . . . . .V SS – 0.3 V to V DD + 0.3 V or30 mA, Whichever Occurs FirstDigital Inputs 2. . . . . . . . . . . . . . . . .–0.3 V to V DD + 0.3 V or30 mA, Whichever Occurs FirstPeak Current, S or D . . . . . . . . . . . . . . . . . . . . . . . . . .100 mA(Pulsed at 1 ms, 10% Duty Cycle max)Continuous Current, S or D . . . . . . . . . . . . . . . . . . . .30 mA Operating Temperature RangeIndustrial (A, B Versions) . . . . . . . . . . . . .–40°C to +85°C Storage Temperature Range . . . . . . . . . . . .–65°C to +150°CCAUTIONESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection.Although the ADG733/ADG734 features proprietary ESD protection circuitry, permanent dam-age may occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.Junction Temperature . . . . . . . . . . . . . . . . . . . . . . . . . .150°C 16-Lead TSSOP, θJA Thermal Impedance . . . . . . .150.4°C/W 20-Lead TSSOP, θJA Thermal Impedance . . . . . . . .143°C/W 16-Lead QSOP, θJA Thermal Impedance . . . . . . .149.97°C/W Lead Temperature, Soldering (10 sec) . . . . . . . . . . . . .300°C IR Reflow, Peak Temperature . . . . . . . . . . . . . . . . . . . .220°CNOTES 1Stresses above those listed under Absolute Maximum Ratings may cause perma-nent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Only one absolute maximum rating may be applied at any one time.2Overvoltages at IN, S or D will be clamped by internal diodes. Current should be limited to the maximum ratings given.ORDERING GUIDEModel Temperature Range Package DescriptionPackage Option ADG733BRU –40°C to +85°C Thin Shrink Small Outline Package (TSSOP)RU-16ADG733BRQ –40°C to +85°C Quarter Size Outline Package (QSOP)RQ-16ADG734BRU–40°C to +85°CThin Shrink Small Outline Package (TSSOP)RU-20PIN CONFIGURATIONSTSSOP/QSOPTSSOPS2B DD S2A S3B D3S3A EN V SS GNDNC = NO CONNECTDDVREV. 0ADG733/ADG734–6–Table I.ADG733 Truth TableA2A1A0EN ON SwitchX X X 1None0000D1-S1A, D2-S2A, D3-S3A 0010D1-S1B, D2-S2A, D3-S3A 0100D1-S1A, D2-S2B, D3-S3A 0110D1-S1B, D2-S2B, D3-S3A 1000D1-S1A, D2-S2A, D3-S3B 1010D1-S1B, D2-S2A, D3-S3B 1100D1-S1A, D2-S2B, D3-S3B 111D1-S1B, D2-S2B, D3-S3BX = Don’t Care.Table II. ADG734 Truth TableLogic Switch A Switch B 0OFF ON 1ONOFFV DD Most Positive Power Supply Potential.V SSMost Negative Power Supply in a Dual Supply Application. In single supply applications, this should be tied to ground close to the device.I DD Positive Supply Current.I SS Negative Supply Current.GND Ground (0 V) Reference.S Source Terminal. May be an input or output.D Drain Terminal. May be an input or output.IN Logic Control Input.V D (V S )Analog Voltage on Terminals D, S R ON Ohmic Resistance between D and S.∆R ON On Resistance Match between Any Two Channels, i.e., R ON max – R ON minR FLAT(ON)Flatness is defined as the difference between the maximum and minimum value of on-resistance as measured over the specified analog signal range.I S (OFF)Source Leakage Current with the Switch “OFF.”I D , I S (ON)Channel Leakage Current with the Switch “ON.”V INL Maximum Input Voltage for Logic “0.”V INH Minimum Input Voltage for Logic “1.”I INL (I INH )Input Current of the Digital Input.C S (OFF)“OFF” Switch Source Capacitance.Measured with reference to ground.C D , C S (ON)“ON” Switch Capacitance. Measured with reference to ground.C IN Digital Input Capacitance.t ONDelay time measured between the 50% and 90% points of the digital inputs and the switch “ON” condition.t OFFDelay time measured between the 50% and 90% points of the digital input and the switch “OFF” condition.t ON (EN )Delay time between the 50% and 90% points of the EN digital input and the switch “ON”condition.t OFF (EN )Delay time between the 50% and 90% points of the EN digital input and the switch “OFF”condition.t OPEN“OFF” time measured between the 80%points of both switches when switching from one address state to another.Charge A measure of the glitch impulse transferred Injection from the digital input to the analog output during switching.Off Isolation A measure of unwanted signal coupling through an “OFF” switch.CrosstalkA measure of unwanted signal that is coupled through from one channel toanother as a result of parasitic capacitance.Bandwidth The frequency at which the output is attenuated by 3 dBs.On ResponseThe Frequency Response of the “ON” Switch.Insertion Loss The loss due to the ON resistance of the switch.TERMINOLOGYREV. 0–7–Typical Performance Characteristics–ADG733/ADG734V D , V S , DRAIN OR SOURCE VOLTAGE – V1O N R E S I S T A N C E – ⍀TPC 1. On Resistance as a Function of V D(V S ) for Single SupplyV D OR V S – DRAIN OR SOURCE VOLTAGE – V76543210O N R E S I S T A N C E – ⍀8TPC 4. On Resistance as a Function of V D (V S ) for Different Temperatures,Single Supply V S (V D ) – V0.10C U R R E N T – n A0.080.060.040.020–0.02–0.04–0.06–0.08–0.10TPC 7. Leakage Currents as a Function of V D (V S )V D , OR V S /DRAIN OR SOURCE VOLTAGE – V 876543210O N R E S I S T A N C E – ⍀TPC 2. On Resistance as a Function of V D (V S ) for Dual SupplyV D , OR V S DRAIN OR SOURCE VOLTAGE – V 1O N R E S I S T A N C E – ⍀TPC 5. On Resistance as a Function of V D (V S ) for Different Temperatures,Dual SupplyV S (V D ) – V0.15C U R R E N T – n A0.100.050–0.05–0.10–0.15TPC 8. Leakage Currents as a Function of V D (V S )V D , OR V S DRAIN OR SOURCE VOLTAGE – V876543210O N R E S I S T A N C E – ⍀TPC 3. On Resistance as a Function of V D (V S ) for Different Temperatures,Single SupplyV S (V D ) – V0.1C U R R E N T – n A0.05–0.05–0.1–0.15TPC 6. Leakage Currents as a Function of V D (V S)TEMPERATURE – ؇C0.25C U R R E N T – n A0.200.150.100.050–0.05–0.10TPC 9. Leakage Currents as a Function of TemperatureREV. 0ADG733/ADG734–8–TEMPERATURE – ؇C 0.25C U R R E N T – n A0.200.150.100.050–0.05–0.10TPC 10.Leakage Currents as a Function of TemperatureFREQUENCY – kHzC U R R E N T – A100101TPC 13.Input Current, I DD vs.Switching FrequencyVOLTAGE –V2010–10Q I N J – p CTPC 16.Charge Injection vs. Source VoltageTEMPERATURE – ؇C40T I M E – n s35302520151005TPC 11.t ON /t OFF Times vs.TemperatureFREQUENCY – kHz030kA T T E N U A T I O N – d B–20–40–60–80–100–120100k1M 10M100M TPC 14.Off Isolation vs. Frequency FREQUENCY – H Z–4–2–6O N R E S P O N S E – dBTPC 12.On Response vs. FrequencyFREQUENCY – kHz030kA T T E N U A T I O N – d B–20–40–60–80–100–120100k1M 10M 100MTPC 15.Crosstalk vs. FrequencyREV. 0ADG733/ADG734–9–V Test Circuit 1.On ResistanceTest CircuitsDV STest Circuit 2.I S (OFF)DTest Circuit 3.I D (ON)VTest Circuit 4.Switching Times, t ON , t OFFOVTest Circuit 5.Enable Delay, t ON (EN ), t OFF (EN )OUTV *A0, A1, A2 FOR ADG733, IN1-4 FOR ADG734ADDRESS3VV OUT0V V Test Circuit 6.Break-Before-Make Delay, t OPENREV. 0ADG733/ADG734–10–* IN1–4 FOR ADG734OUTV V Test Circuit 7.Charge InjectionSWITCH OPEN FOR OFF ISOLATION MEASUREMENTS SWITCH CLOSED FOR BANDWIDTH MEASUREMENTS OFF ISOLATION = 20LOG 10(V OUT /V S )INSERTION LOSS = 20LOG 10(V OUT WITH SWITCH V OUT WITHOUT SWITCH)V V OUTTest Circuit 8.OFF Isolation and BandwidthV SV NC = NO CONNECTTest Circuit 9.Channel-to-Channel CrosstalkREV. 0ADG733/ADG734–11–16-Lead TSSOP (RU-16)OUTLINE DIMENSIONSDimensions shown in inches and (mm).20-Lead TSSOP (RU-20)16-Lead QSOP(RQ-16)BSC 0.007 (0.18)C 01602–2.5–1/01 (r e v . 0)P R I N T E D I N U .S .A .元器件交易网。

ua723中文资料

元器件交易网IMPORTANT NOTICETexas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinueany product or service without notice, and advise customers to obtain the latest version of relevant informationto verify, before placing orders, that information being relied on is current and complete. All products are soldsubject to the terms and conditions of sale supplied at the time of order acknowledgement, including thosepertaining to warranty, patent infringement, and limitation of liability.TI warrants performance of its semiconductor products to the specifications applicable at the time of sale inaccordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extentTI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarilyperformed, except those mandated by government requirements.CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OFDEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICALAPPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, ORWARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHERCRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TOBE FULLY AT THE CUSTOMER’S RISK.In order to minimize risks associated with the customer’s applications, adequate design and operatingsafeguards must be provided by the customer to minimize inherent or procedural hazards.TI assumes no liability for applications assistance or customer product design. TI does not warrant or representthat any license, either express or implied, is granted under any patent right, copyright, mask work right, or otherintellectual property right of TI covering or relating to any combination, machine, or process in which suchsemiconductor products or services might be or are used. TI’s publication of information regarding any thirdparty’s products or services does not constitute TI’s approval, warranty or endorsement thereof.Copyright © 1999, Texas Instruments Incorporated。

7330中文说明书

ION7300&7330面板操作指南I O N7300和I O N7330是加拿大P M L公司研制生产的新一代三相多功能智能型电能表。

I O N7300除了提供高精度电能计量外,还测量电压、电流、功率、功率因数、频率、需量、谐波、不平衡度等,I O N7300具有一个标准R S-485通信口(标准M O D B U S),并可扩展4路遥控输出,可选择P r o f i b u s、E t h e r n e t 网口等配置。

I O N7330除了具有I O N7300所有高精度测量外,还具有2个标准R S-485通信口(标准M O D B U S),增加了4个开关量输入、对任何电量的越限记录、2组大容量负荷曲线记录等功能,可直接配置作为网关使用的E t h e r n e t网口和内置M o d e m。

本文将介绍该电能表的面板操作方法,以及基本参数的整定等,为用户使用提供方便。

目录一、显示面板设置基本操作 (3)1.1 显示面板操作按键及基本操作 (3)1.2 选项设置菜单 (3)1.3 数值整定 (3)1.4 密码的输入 (4)二、显示面板显示方式整定 (4)2.1 自动循环显示设定 (4)2.2 屏幕显示对比度设定 (5)2.3 显示器背光持续时间设定 (5)2.4 实时数据显示更新速率设定 (5)2.5 显示模式设定 (5)三、“Password”密码的设定 (6)四、7300ION&7330ION参数的整定 (7)4.1 基本参数的整定 (7)4.2 高级参数整定 (8)五、用户设定数据显示模式 (10)5.1 每屏显示数据数量的设定 (10)5.2 每屏显示数据类型的设定 (11)六、电能量及最值清零设定 (12)七、自诊断选项(7330ION) (13)1 显示面板设置基本操作1.1 显示面板操作按键及基本操作菜单翻转选择键功能设定键及确认键•按设定键进入“Select Setup”整定菜单。

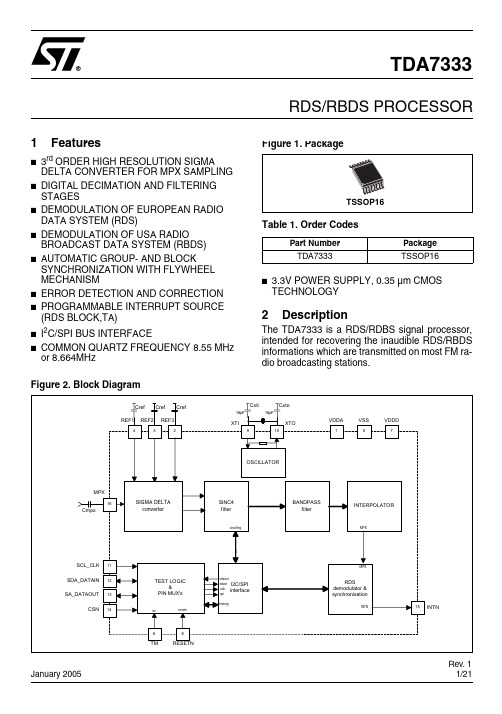

TDA7333资料

Digital Inputs( pin 6,8,11,12,13,14)

Digital Outputs (pin 12,13,15) are open drains

Analog Inputs (pin 16) VMPX SRDS RMPX fosc tsu gm Cxti,Cxto Fs OVR THD+N Input Range of MPX Signal RDS Detection Sensitivity Input Impedance of MPX pin Quartz Frequency Start up Time Transconductance Load Capacitance Sample Rate Oversampling Ratio Relative Total Harmonic Dist. plus Noise Decimated Sample Rate Attenuation at 57 kHz Attenuation Difference Bandpass Filter fs fp Sample Rate Passband Frequencies fosc =8.55 MHz 55.6 267.2 58.4 kHz kHz BW= 54.5 .. 59.5 kHz fosc =8.55 MHz f =57 kHz BW= 54.5 .. 59.5 kHz, unweigted, Vrds = 3mVrms fosc = 8.55 MHz 0.0006 16 4.275 38 27 dB 1 55k 8.55 or 8.664 10 0.75 Vrms mVrms Ohm MHz ms A/V pF MHz

6.2

General Interface Electrical Characteristics

733机型熟悉讲义

19

B737飞机基本介绍

飞机勤务站位

2013-7-15

Training Division of Maintenance and Engineering Dept.

20

B737飞机基本介绍

飞机顶点

2013-7-15

Training Division of Maintenance and Engineering Dept.

35

36章 气源系统

APU和地面气源也可以给系统提供气源。 APU给气源系统的左半部分提供气源,地 面气源给右半部分提供气源。 交输引气管附近上装了两个压力传感器, 分别指示左右部分的引气压力。

2013-7-15

Training Division of Maintenance and Engineering Dept.

飞行阶段控制程序控制方法座舱高度放气活门位置在地面发动机没运转不增压程序飞行电门在地位起落架空地继电器在地位起飞场高度放气活门全开在地面发动机运预增压程序飞行电门在飞行位起落架空地继电器在地位调节座舱高度在起飞场高度200ft起飞场高200ft放气活门由全开关小到一定位置在空中爬爬升程序飞行电门在飞行位起落架空地继电器在air位按比例上升参照对照表放气活门随飞行高度增加逐渐关巡航巡航程序巡航程序执行等压余压控制大于外界压78psi放气活门关到最小开度下降下降程序飞行电门在飞行位起落架空地继电器在air位按比例下降参照对照表放气活门放气活门逐渐开大着陆预增压程序飞行电门在飞行位起落架空地继电器在地位调节座舱高度在起飞场高度200ft着陆场高200ft放气活门开到保证舱内的预增压压力停机点不增压飞行电门在地位起落架空地继电器在地位着陆场高度放气活门全开位备用增压方式程序表201227trainingdivisionengineeringdept

HT82V733中文资料

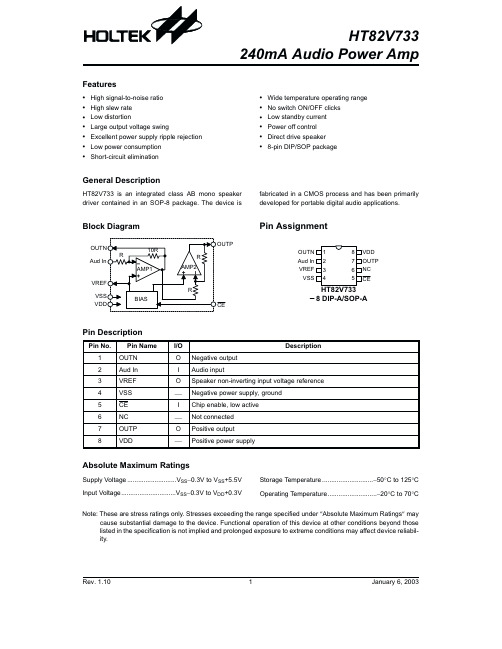

HT82V733240mA Audio Power AmpBlock DiagramPin AssignmentPin DescriptionPin No.Pin Name I/O Description1OUTN O Negative output 2Aud In I Audio input3VREF O Speaker non-inverting input voltage reference 4VSS ¾Negative power supply,ground 5CE I Chip enable,low active 6NC ¾Not connected 7OUTP O Positive output 8VDD¾Positive power supplyAbsolute Maximum RatingsSupply Voltage...........................V SS -0.3V to V SS +5.5V Storage Temperature............................-50°C to 125°C Input Voltage..............................V SS -0.3V to V DD +0.3VOperating Temperature...........................-20°C to 70°CNote:These are stress ratings only.Stresses exceeding the range specified under ²Absolute Maximum Ratings ²maycause substantial damage to the device.Functional operationof this device at other conditions beyond those listed in the specification is not implied and prolonged exposure to extreme conditions may affect device reliabil-ity.Rev.1.101January 6,2003Features·High signal-to-noise ratio ·High slew rate ·Low distortion·Large output voltage swing·Excellent power supply ripple rejection ·Low power consumption ·Short-circuit elimination·Wide temperature operating range ·No switch ON/OFF clicks ·Low standby current ·Power off control ·Direct drive speaker ·8-pin DIP/SOP packageGeneral DescriptionHT82V733is an integrated class AB mono speaker driver contained in an SOP-8package.The device isfabricated in a CMOS process and has been primarily developed for portable digital audio applications.Electrical Characteristics VSS=0V,Ta=25°CSymbol ParameterTest ConditionsMin.Typ.Max.Unit V DD ConditionsSuppliesV DD Supply Voltage¾¾ 2.4 5.0 5.5V V SS Negative Supply Voltage5V¾¾0¾V I STB Standby Current¾¾¾¾1m AI DD Operating Current¾V i=0,No load2410mA V P-P=500mV,f i=1kHzNo load4.812.323.5P tot Total Power Dissipation¾V P-P=500mV,f i=1kHzNo load1560140mW DC CharacteristicsV I(OS)Input Offset Voltage 5V¾¾12¾mV 3V¾ 2.5¾I O Maximum Output Current(THD+N)/S<1%5V Current¾240¾mA 3V Current¾160¾V O Output Voltage Swing(THD+N)/S<1%5VR L=16W 1.2¾4V R L=8W 1.8¾ 3.4R L=4W 2.1¾33VR L=16W0.6¾ 2.3V R L=8W0.9¾ 1.9R L=4W 1.1¾ 1.7PSRR Power Supply Rejection Ratio 5V fi=100Hz;V ripple(p-p)=100mV¾71¾dB 3V¾62¾AC Characteristics(THD+N)/S Total Harmonic DistortionPlus Noise-to-signal Ratio5VV O(p-p)=3.5VR L=8W¾-48¾dB¾3¾%3VV O(p-p)=1.5VR L=8W¾-30¾dB¾3¾%S/N Signal-to-noise Ratio 5V¾¾60¾dB 3V¾58¾Rev.1.102January6,2003Functional DescriptionOUTP Rising Time(t R)When CE active low,the HT82V733need rising time to output fully on OUTP pin.However,the rising time depends on C1.(*see the application circuits)Capacitort R0.1m F1m F 4.7m F10m F Voltage2.2V15ms30ms90ms185ms3V15ms30ms90ms185ms4V15ms30ms90ms185msFor battery based applications,power consumption is a key issue,therefore the amplifier should be turned off when in the standby state.In order to eliminate any speaker sound bursts while turning the amplifier on,the application circuit, which will incorporate a capacitance value of C1,should be adjusted in accordance with the speaker s audio frequency response.A greater value of C1will improve the noise burst while turning on the amplifier.The recommended opera-tion sequence is:Turn On:audio1signal standby(1/2VDD)®enable amplifier®wait t R for amplifier ready®audio1outputTurn Off:audio1signal finished®disable amplifier®wait t R for amplifier off®audio1signal offIf the application is not powered by batteries and there is no problem with amplifier On/Off issue,a capacitor value of 0.1uF for C1is recommended.Application CircuitsRev.1.103January6,2003Package Information8-pin DIP(300mil)Outline DimensionsSymbolDimensions in milMin.Nom.Max.A355¾375B240¾260C125¾135D125¾145E16¾20F50¾70G¾100¾H295¾315I335¾375a0°¾15°Rev.1.104January6,20038-pin SOP(150mil)Outline DimensionsSymbolDimensions in milMin.Nom.Max.A228¾244B149¾157C14¾20C¢189¾197D53¾69E¾50¾F4¾10G22¾28H4¾12a0°¾10°Rev.1.105January6,2003Product Tape and Reel SpecificationsReel DimensionsSOP8NSymbol Description Dimensions in mmA Reel Outer Diameter330±1.0B Reel Inner Diameter62±1.5C Spindle Hole Diameter 13.0+0.5-0.2D Key Slit Width 2.0±0.15T1Space Between Flange 12.8+0.3-0.2T2Reel Thickness18.2±0.2Rev.1.106January6,2003Carrier Tape DimensionsSOP8NSymbol Description Dimensions in mmW Carrier Tape Width 12.0+0.3-0.1P Cavity Pitch8.0±0.1E Perforation Position 1.75±0.1F Cavity to Perforation(Width Direction) 5.5±0.1D Perforation Diameter 1.55±0.1D1Cavity Hole Diameter 1.5+0.25P0Perforation Pitch 4.0±0.1P1Cavity to Perforation(Length Direction) 2.0±0.1A0Cavity Length 6.4±0.1B0Cavity Width 5.20±0.1K0Cavity Depth 2.1±0.1t Carrier Tape Thickness0.3±0.05C Cover Tape Width9.3Rev.1.107January6,2003Holtek Semiconductor Inc.(Headquarters)No.3,Creation Rd.II,Science Park,Hsinchu,TaiwanTel:886-3-563-1999Fax:886-3-563-1189Holtek Semiconductor Inc.(Taipei Sales Office)4F-2,No.3-2,YuanQu St.,Nankang Software Park,Taipei115,TaiwanTel:886-2-2655-7070Fax:886-2-2655-7373Fax:886-2-2655-7383(International sales hotline)Holtek Semiconductor Inc.(Shanghai Sales Office)7th Floor,Building2,No.889,Yi Shan Rd.,Shanghai,China200233Tel:021-6485-5560Fax:021-6485-0313Holtek Semiconductor Inc.(Shenzhen Sales Office)43F,SEG Plaza,Shen Nan Zhong Road,Shenzhen,China518031Tel: 0755-8346-5589Fax: 0755-8346-5590ISDN: 0755-8346-5591Holtek Semiconductor Inc. (Beijing Sales Office)Suite 1721, Jinyu Tower, A129 West Xuan Wu Men Street, Xicheng District, Beijing, China 100031Tel: 010-6641-0030, 6641-7751, 6641-7752Fax: 010-6641-0125Holmate Semiconductor,Inc.(North America Sales Office)46712Fremont Blvd.,Fremont,CA94538Tel:510-252-9880Fax:510-252-9885Copyright Ó 2003 by HOLTEK SEMICONDUCTOR INC.The information appearing in this Data Sheet is believed to be accurate at the time of publication.However,Holtek as-sumes no responsibility arising from the use of the specifications described.The applications mentioned herein are used solely for the purpose of illustration and Holtek makes no warranty or representation that such applications will be suitable without further modification,nor recommends the use of its products for application that may present a risk to human life due to malfunction or otherwise. Holtek¢s products are not authorized for use as critical components in life support devices or systems. Holtek reserves the right to alter its products without prior notification. For the most up-to-date information, please visit our web site at .Rev.1.108January6,2003。

AD73311ARZ;AD73311ARSZ;AD73311LARUZ-RL;AD73311LARSZ-REEL;AD73311LARUZ-RL7;中文规格书,Datasheet资料

REV.BInformation furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.aAD73311One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.Tel: 781/329-4700World Wide Web Site: Fax: 781/326-8703© Analog Devices, Inc., 2000Low Cost, Low Power CMOS General Purpose Analog Front EndFUNCTIONAL BLOCK DIAGRAMAGND2VINPVINNVOUTN REFCAP REFOUTSDISDIFSSCLKSDO SDOFS SE MCLK RESETFEATURES16-Bit A/D Converter 16-Bit D/A ConverterProgrammable Input/Output Sample Rates 75 dB ADC SNR 70 dB DAC SNR64 kS/s Maximum Sample Rate –90 dB CrosstalkLow Group Delay (25s Typ per ADC Channel,50 s Typ per DAC Channel)Programmable Input/Output GainFlexible Serial Port which Allows up to 8 Devices to Be Connected in CascadeSingle (+2.7V to +5.5V) Supply Operation 50mW Max Power Consumption at 2.7V On-Chip Reference20-Lead SOIC/SSOP PackageAPPLICATIONSGeneral Purpose Analog I/O Speech ProcessingCordless and Personal Communications TelephonyActive Control of Sound & Vibration Data CommunicationsGENERAL DESCRIPTIONThe AD73311 is a complete front-end processor for general purpose applications including speech and telephony. It features a 16-bit A/D conversion channel and a 16-bit D/A conversion channel. Each channel provides 70dB signal-to-noise ratio over a voiceband signal bandwidth. The final channel bandwidth can be reduced, and signal-to-noise ratio improved, by external digital filtering in a DSP engine.The AD73311 is suitable for a variety of applications in the speech and telephony area including low bit rate, high quality compression, speech enhancement, recognition and synthesis.The low group delay characteristic of the part makes it suitable for single or multichannel active control applications.The gains of the A/D and D/A conversion channels are pro-grammable over 38 dB and 21 dB ranges respectively. An on-chip reference voltage is included to allow single supply operation. A serial port (SPORT) allows easy interfacing of single or cascaded devices to industry standard DSP engines.The AD73311 is available in both 20-lead SOIC and SSOP packages./–2–REV. BAD73311–SPECIFICATIONS1 AD73311A ParameterMin TypMaxUnitTest Conditions/Comments REFERENCE 5VEN = 0REFCAPAbsolute Voltage, V REFCAP 1.081.2 1.32VREFCAP TC 50ppm/°C 0.1µF Capacitor Required from REFOUTREFCAP to AGND2Typical Output Impedance 68ΩAbsolute Voltage, V REFOUT 1.08 1.21.32V UnloadedMinimum Load Resistance 1k ΩMaximum Load Capacitance 100pF ADC SPECIFICATIONSMaximum Input Range at VIN 2, 3 1.578V p-p 5VEN = 0, Measured Differentially –2.85dBm Nominal Reference Level at VIN 1.0954V p-p 5VEN = 0, Measured Differentially (0 dBm0)–6.02dBm Absolute Gain PGA = 0 dB –0.750.1+1.0dB 1.0 kHz, 0 dBm0PGA = 38 dB –1.5–0.5+0.5dB 1.0 kHz, 0 dBm0Gain Tracking Error±0.1dB 1.0 kHz, +3 dBm0 to –50 dBm0Signal to (Noise + Distortion)Refer to Figure 5PGA = 0 dB 7076dB 300 Hz to 3.4 kHz Frequency Range 5556dB 0 Hz to 32 kHz Frequency Range PGA = 38 dB6165dB 300 Hz to 3.4 kHz Frequency Range 5354dB0 Hz to 32 kHz Frequency RangeTotal Harmonic Distortion PGA = 0 dB –83–70dB PGA = 38 dB–83–70dB Intermodulation Distortion –78dB PGA = 0 dB Idle Channel Noise –76dBm0PGA = 0 dBCrosstalk–100dB ADC Input Signal Level:1.0 kHz, 0dBm0DAC Input at Idle DC Offset–20+15+50mV PGA = 0 dBPower Supply Rejection –55dB Input Signal Level at AVDD and DVDD Pins 1.0 kHz, 100 mV p-p Sine Wave Group Delay 4, 525µs 64 kHz Output Sample Rate Input Resistance at VIN 2, 425k Ω6DMCLK = 16.384 MHzDAC SPECIFICATIONSMaximum Voltage Output Swing 2Single Ended1.578V p-p 5VEN = 0, PGA = 6 dB –2.85dBm Differential3.156V p-p 5VEN = 0, PGA = 6 dB 3.17dBm Nominal Voltage Output Swing (0 dBm0)Single-Ended 1.0954V p-p 5VEN = 0, PGA = 6 dB –6.02dBm Differential2.1909V p-p 5VEN = 0, PGA = 6 dB0dBm Output Bias Voltage 1.08 1.2 1.32V 5VEN = 0, REFOUT Unloaded Absolute Gain–0.75+0.2+1.0dB 1.0 kHz, 0 dBm0Gain Tracking Error±0.1dB 1.0 kHz, +3 dBm0 to –50 dBm0Signal to (Noise + Distortion)AVDD = +3 V ± 5%; Refer to Figure 5PGA = 0 dB 62.570dB 300 Hz to 3.4 kHz Frequency Range 62.5dB 0 Hz to 32 kHz Frequency Range PGA = 6 dB62.571dB 300 Hz to 3.4 kHz Frequency Range 62.5dB 0 Hz to 32 kHz Frequency Range Total Harmonic Distortion AVDD = +3 V ± 5%PGA = 0 dB –70–62.5dB PGA = 6 dB–70–62.5dB Intermodulation Distortion –68dB PGA = 0 dB Idle Channel Noise –82dBm0PGA = 0 dBCrosstalk–100dBADC Input Signal Level:AGND; DAC Output Signal Level:1.0 kHz, 0 dBm0(AVDD = +3V ؎ 10%; DVDD = +3V ؎ 10%; DGND = AGND = 0V, f MCLK = 16.384 MHz,F S = 64 kHz; T A = T MIN to T MAX , unless otherwise noted)/AD73311AParameter Min Typ Max Unit Test Conditions/CommentsDAC SPECIFICATIONS (Continued)Power Supply Rejection–55dB Input Signal Level at AVDD and DVDDPins: 1.0 kHz, 100 mV p-p Sine Wave Group Delay4, 525µs64 kHz Input Sample Rate, InterpolatorBypassed (CRE:5 = 1)Output DC Offset2, 7–30+20+70mV PGA = 6 dBMinimum Load Resistance, R L2, 8Single-Ended150ΩDifferential150ΩMaximum Load Capacitance, C L2, 8Single-Ended500pFDifferential100pFFREQUENCY RESPONSE(ADC AND DAC)9 Typical Output0 Hz0dB2000 Hz–0.1dB4000 Hz–0.25dB8000 Hz–0.6dB12000 Hz–1.4dB16000 Hz–2.8dB20000 Hz–4.5dB Channel Frequency Response Is24000 Hz–7.0dB Programmable by Means of External 28000 Hz–9.5dB Digital Filtering> 32000 Hz< –12.5dBLOGIC INPUTSV INH, Input High Voltage V DD– 0.8V DD VV INL, Input Low Voltage00.8VI IH, Input Current10µAC IN, Input Capacitance10pFLOGIC OUTPUTV OH, Output High Voltage V DD– 0.4V DD V|IOUT| ≤ 100 µAV OL, Output Low Voltage00.4V|IOUT| ≤ 100 µAThree-State Leakage Current–10+10µAPOWER SUPPLIESAVDD1, AVDD2 2.7 3.3VDVDD 2.7 3.3VI DD10See Table INOTES1Operating temperature range is as follows:–40°C to +85°C. Therefore, TMIN = –40°C and T MAX = +85°C.2Test conditions:Input PGA set for 0dB gain, Output PGA set for 6 dB gain, no load on analog outputs (unless otherwise noted).3At input to sigma-delta modulator of ADC.4Guaranteed by design.5Overall group delay will be affected by the sample rate and the external digital filtering.6The ADC’s input impedance is inversely proportional to DMCLK and is approximated by: (4 × 1011)/DMCLK.7Between VOUTP and VOUTN.8At VOUT output.9Frequency responses of ADC and DAC measured with input at audio reference level (the input level that produces an output level of –10 dBm0), with 38dB preamplifier bypassed and input gain of 0 dB.10Test Conditions:no load on digital inputs, analog inputs ac coupled to ground, no load on analog outputs.Specifications subject to change without notice.Table I.Current Summary (AVDD = DVDD = +3.3V)Analog Internal Digital External Interface Total Current MCLKConditions Current Current Current(Max)SE ON CommentsADC On Only730.511.51YES REFOUT DisabledADC and DAC On1050.517.51YES REFOUT DisabledREFCAP On Only0.7500 1.20NO REFOUT DisabledREFCAP andREFOUT On Only3.000 4.50NOAll Sections Off00.850 1.20YES MCLK Active Levels Equal to0 V and DVDDAll Sections Off0.000.00700.040NO Digital Inputs Static and Equalto 0 V or DVDD The above values are in mA and are typical values unless otherwise noted.AD73311–3–REV. B/AD73311–SPECIFICATIONS1(AVDD = +5V ؎ 10%; DVDD = +5V ؎ 10%; DGND = AGND = 0 V, f MCLK = 16.384 MHz,F S = 64 kHz; T A = T MIN to T MAX, unless otherwise noted)AD73311AParameter Min Typ Max Unit Test Conditions/Comments REFERENCEREFCAPAbsolute Voltage, V REFCAP 1.2V5VEN = 02.4V5VEN = 1REFCAP TC50ppm/°C0.1 µF Capacitor Required fromREFOUT REFCAP to AGND2Typical Output Impedance68ΩAbsolute Voltage, V REFOUT 1.2V5VEN = 0, Unloaded2.4V5VEN = 1, UnloadedMinimum Load Resistance2kΩ5VEN = 1Maximum Load Capacitance100pFADC SPECIFICATIONSMaximum Input Range at VIN2, 3 3.156V p-p5VEN = 1, Measured Differentially3.17dBmNominal Reference Level at VIN 2.1908V p-p5VEN = 1, Measured Differentially(0 dBm0)0dBmAbsolute GainPGA = 0 dB0.1dB 1.0 kHz, 0 dBm0PGA = 38 dB–0.5dB 1.0 kHz, 0 dBm0Gain Tracking Error±0.1dB 1.0 kHz, +3 dBm0 to –50 dBm0Signal to (Noise + Distortion)Refer to Figure 5PGA = 0 dB76dB300 Hz to 3.4 kHz Frequency Range59dB0 Hz to 32 kHz Frequency Range PGA = 38 dB71dB300 Hz to 3.4 kHz Frequency Range57dB0 Hz to 32 kHz Frequency Range Total Harmonic DistortionPGA = 0 dB–76dBPGA = 38 dB–69dBIntermodulation Distortion–69dB PGA = 0 dBIdle Channel Noise–67dBm0PGA = 0 dBCrosstalk–80dB ADC Input Signal Level: 1.0 kHz, 0dBm0DAC Input at Idle DC Offset+20mV PGA = 0 dBPower Supply Rejection–55dB Input Signal Level at AVDD and DVDDPins 1.0 kHz, 100 mV p-p Sine Wave Group Delay4, 525µs64 kHz Output Sample RateInput Resistance at VIN2, 425kΩ6DMCLK = 16.384 MHzDAC SPECIFICATIONSMaximum Voltage Output Swing2Single Ended 3.156V p-p5VEN = 1, PGA = 6 dB3.17dBmDifferential 6.312V p-p5VEN = 1, PGA = 6 dB9.19dBmNominal Voltage Output Swing (0 dBm0)Single-Ended 2.1908V p-p5VEN = 1, PGA = 6 dB0dBmDifferential 4.3918V p-p5VEN = 1, PGA = 6 dB6.02dBmOutput Bias Voltage V REFOUT V typ5VEN = 1, REFOUT UnloadedAbsolute Gain±0.4dB 1.0 kHz, 0 dBm0Gain Tracking Error±0.1dB 1.0 kHz, +3 dBm0 to –50 dBm0Signal to (Noise + Distortion)Refer to Figure 5PGA = 0 dB66dB300 Hz to 3.4 kHz Frequency Range64dB0 Hz to 32 kHz Frequency Range PGA = 6 dB66dB300 Hz to 3.4 kHz Frequency Range64dB0 Hz to 32 kHz Frequency Range Total Harmonic DistortionPGA = 0 dB–62.5dBPGA = 6 dB–62.5dBIntermodulation Distortion–60dB PGA = 0Idle Channel Noise–75dBm0PGA = 0Crosstalk–80dB ADC Input Signal Level: AGND; DACOutput Signal Level: 1.0 kHz, 0 dBm0–4–REV. B /–5–REV. BAD73311AD73311A ParameterMinTyp Max Unit Test Conditions/CommentsDAC SPECIFICATIONS (Continued)Power Supply Rejection –55dB Input Signal Level at AVDD and DVDD Pins: 1.0 kHz, 100 mV p-p Sine Wave Group Delay 4, 525µs 64 kHz Input Sample Rate, Interpolator Bypassed (CRE:5 = 1)Output DC Offset 2, 7+30mV PGA = 6 dBMinimum Load Resistance, R L 2, 8Single-Ended 150ΩDifferential150ΩMaximum Load Capacitance, C L 2, 8Single-Ended 500pF Differential100pFFREQUENCY RESPONSE(ADC AND DAC)9 Typical Output 0 Hz 0dB 2000 Hz –0.1dB 4000 Hz –0.25dB 8000 Hz –0.6dB 12000 Hz –1.4dB 16000 Hz –2.8dB 20000 Hz –4.5dB Channel Frequency Response Is 24000 Hz –7.0dB Programmable by Means of External 28000 Hz –9.5dB Digital Filtering> 32000 Hz < –12.5dB LOGIC INPUTSV INH , Input High Voltage V DD – 0.8V DD V V INL , Input Low Voltage 00.8V I IH , Input Current–0.5µA C IN , Input Capacitance 10pF LOGIC OUTPUTV OH , Output High Voltage V DD – 0.4V DD V |I OUT | < 100 µA V OL , Output Low Voltage 00.4V |I OUT | < 100 µAThree-State Leakage Current –0.3µA POWER SUPPLIES AVDD1, AVDD2 4.5 5.5V DVDD 4.55.5VI DD 10See Table IIN OTES1Operating temperature range is as follows: –40°C to +85°C. Therefore, T MIN = –40°C and T MAX = +85°C.2Test conditions: Input PGA set for 0dB gain, Output PGA set for 6 dB gain, no load on analog outputs (unless otherwise stated).3At input to sigma-delta modulator of ADC.4Guaranteed by design.5Overall group delay will be affected by the sample rate and the external digital filtering.6The ADC ’s input impedance is inversely proportional to DMCLK and is approximated by: (4 × 1011)/DMCLK.7Between VOUTP and VOUTN.8At VOUT output.9Frequency responses of ADC and DAC measured with input at audio reference level (the input level that produces an output level of –10 dBm0), with 38 dB preamplifier bypassed and input gain of 0 dB.10Test conditions: no load on digital inputs, analog inputs ac coupled to ground, no load on analog outputs.Specifications subject to change without notice./AD73311–6–REV. BTable III.Signal Ranges3 V Power Supply 5 V Power Supply5VEN = 05VEN = 05VEN = 1V REFCAP 1.2 V ± 10% 1.2V 2.4V V REFOUT 1.2 V ± 10% 1.2V 2.4V ADCMaximum Input Range at V IN1.578 V p-p 1.578 V p-p 3.156 V p-p Nominal Reference Level 1.0954 V p-p1.0954 V p-p2.1908 V p-pDACMaximum Voltage Output Swing Single-Ended 1.578 V p-p 1.578 V p-p 3.156 V p-p Differential3.156 V p-p 3.156 V p-p 6.312 V p-p Nominal Voltage Output Swing Single-Ended 1.0954 V p-p 1.0954 V p-p 2.1908 V p-p Differential2.1909 V p-p 2.1909 V p-p 4.3818 V p-p Output Bias VoltageV REFOUTV REFOUTV REFOUTTIMING CHARACTERISTICSLimit atParameter T A = –40؇C to +85؇C Unit Description Clock Signals See Figure 1t 161ns min MCLK Periodt 224.4ns min MCLK Width High t 324.4ns min MCLK Width LowSerial Port See Figures 3 and 4t 4t 1ns min SCLK Periodt 50.4 × t 1ns min SCLK Width High t 60.4 × t 1ns min SCLK Width Lowt 720ns min SDI/SDIFS Setup Before SCLK Low t 80ns min SDI/SDIFS Hold After SCLK Low t 910ns max SDOFS Delay from SCLK High t 1010ns min SDOFS Hold After SCLK High t 1110ns min SDO Hold After SCLK High t 1210ns max SDO Delay from SCLK High t 1330ns maxSCLK Delay from MCLK(AVDD = +3 V ؎ 10%; DVDD = +3 V ؎ 10%; AGND = DGND = 0 V; T A = T MlN to T MAX , unless otherwise noted)Table II.Current Summary (AVDD = DVDD = +5.5V)AnalogInternal Digital External Interface MCLK Conditions Current Current Current Total Current SE ON CommentsADC On Only 8.56216.51YES REFOUT Disabled ADC and DAC On 14.56222.51YES REFOUT Disabled REFCAP On Only 0.800 1.00NO REFOUT DisabledREFCAP andREFOUT On Only 3.500 3.50NO All Sections Off 0 1.50 1.70YES MCLK Active Levels Equal to 0 V and DVDDAll Sections Off00.010.02NODigital Inputs Static and Equal to 0 V or DVDDThe above values are in mA and are typical values unless otherwise noted./AD73311–7–REV. BFigure 1.MCLK TimingTIMING CHARACTERISTICSLimit atParameter T A = –40؇C to +85؇C Unit Description Clock Signals See Figure 1t 161ns min MCLK Periodt 224.4ns min MCLK Width High t 324.4ns min MCLK Width LowSerial Port See Figures 3 and 4t 4t 1ns min SCLK Periodt 50.4 × t 1ns min SCLK Width High t 60.4 × t 1ns min SCLK Width Lowt 720ns typ SDI/SDIFS Setup Before SCLK Low t 80ns typ SDI/SDIFS Hold After SCLK Low t 910ns typ SDOFS Delay from SCLK High t 1010ns typ SDOFS Hold After SCLK High t 1110ns typ SDO Hold After SCLK High t 1210ns typ SDO Delay from SCLK High t 1330ns typSCLK Delay from MCLK(AVDD = +5 V ؎ 10%; DVDD = +5 V ؎ 10%; AGND = DGND = 0 V; T A = T MlN to TMAX , unless otherwise noted)TO OUTPUTPINFigure 2.Load Circuit for Timing SpecificationsMCLKSCLK *SCLK IS INDIVIDUALLY PROGRAMMABLEIN FREQUENCY (MCLK/4 SHOWN HERE).*Figure 3.SCLK Timing/AD73311–8–REV. BV IN – dBm0–853.17–75–65–55–45–35–25–1508070–10S /(N +D ) – d B3020100504060–5Figure 5a.S/(N+D) vs. V IN (ADC @ 3V) over Voiceband Bandwidth (300 Hz – 3.4kHz)V IN – dBm0–853.17–75–65–55–45–35–25–158070–10S /(N +D ) – d B3020100504060–5Figure 5b.S/(N+D) vs. V IN (DAC @ 3V) over Voiceband Bandwidth (300 Hz – 3.4 kHz)V IN – dBm0–853.17–75–65–55–45–35–25–158070–10S /(N +D ) – d B3020100504060–5Figure 5c.S/(N+D) vs. V IN (ADC @ 5 V) over Voiceband Bandwidth (300 Hz – 3.4 kHz)V IN – dBm0–853.17–75–65–55–45–35–25–1508070–10S /(N +D ) – d B3020100504060–5Figure 5d. S/(N+D) vs. V IN (DAC @ 5 V) over VoicebandBandwidth (300 Hz – 3.4 kHz)SE (I)SCLK (O)SDIFS (I)SDI (I)SDOFS (O)SDO (O)Figure 4. Serial Port (SPORT)/AD73311–9–REV. BABSOLUTE MAXIMUM RATINGS*(T A = +25°C unless otherwise noted)AVDD, DVDD to GND . . . . . . . . . . . . . . . . . –0.3 V to +7 V AGND to DGND . . . . . . . . . . . . . . . . . . . . . –0.3 V to +0.3 V Digital I/O Voltage to DGND . . . . ..–0.3 V to DVDD + 0.3 V Analog I/O Voltage to AGND . . . . . –0.3 V to AVDD + 0.3 V Operating Temperature RangeIndustrial (A Version) . . . . . . . . . . . . . . . . –40°C to +85°C Storage Temperature Range . . . . . . . . . . . . –65°C to +150°C Maximum Junction Temperature . . . . . . . . . . . . . . . . +150°C SOIC, θJA Thermal Impedance . . . . . . . . . . . . . . . . . . 75°C/W Lead Temperature, SolderingVapor Phase (60 sec) . . . . . . . . . . . . . . . . . . . . . . . . +215°C Infrared (15 sec) . . . . . . . . . . . . . . . . . . . . . . . . . . . . +220°C SSOP, θJA Thermal Impedance . . . . . . . . . . . . . . . . . .90°C/W Lead Temperature, SolderingVapor Phase (60 sec) . . . . . . . . . . . . . . . . . . . . . . . . +215°C Infrared (15 sec) . . . . . . . . . . . . . . . . . . . . . . . . . . . . +220°C*Stresses above those listed under Absolute Maximum Ratings may cause perma-nent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.ORDERING GUIDETemperature Package ModelRangeOption 1AD73311AR –40°C to +85°C R-20AD73311ARS–40°C to +85°C RS-20EVAL-AD73311EB Evaluation Board 2+EZ-KIT Lite Upgrade 3EVAL-AD73311EZEvaluation Board 2+EZ-KIT Lite 4NOTES 1R = 0.3' Small Outline IC (SOIC), RS = Shrink Small Outline Package (SSOP).2The AD73311 evaluation board features a selectable number of codecs in cascade (from 1 to 4). It can be interfaced to an ADSP-2181 EZ-KIT Lite or to a Texas Instruments EVM kit.3The upgrade consists of a replacement PROM and connector. This option is intended for existing owners of EZ-KIT Lite.4The EZ-KIT Lite has been modified to allow it to interface with the AD73311evaluation board. This option is intended for users who do not already have an EZ-KIT Lite.CAUTIONESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000V readily accumulate on the human body and test equipment and can discharge without detection.Although the AD73311 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.PIN CONFIGURATIONVOUTP SDOFSSDIFS SDI SE VOUTN AVDD1AGND1SCLK MCLK SDOVINP VINN REFOUT REFCAP AVDD2AGND2DGNDDVDD RESET /AD73311PIN FUNCTION DESCRIPTIONSPinNumber Mnemonic Function1VOUTP Analog Output from the Positive Terminal of the Output Channel.2VOUTN Analog Output from the Negative Terminal of the Output Channel.3AVDD1Analog Power Supply Connection for the Output Driver.4AGND1Analog Ground Connection for the Output Driver.5VINP Analog Input to the Positive Terminal of the Input Channel.6VINN Analog Input to the Negative Terminal of the Input Channel.7REFOUT Buffered Reference Output, which has a nominal value of 1.2V or 2.4V, the value being dependenton the status of Bit 5VEN (CRC:7).8REFCAP A Bypass Capacitor to AGND2 of 0.1µF is required for the on-chip reference. The capacitor shouldbe fixed to this pin.9AVDD2Analog Power Supply Connection.10AGND2Analog Ground/Substrate Connection.11DGND Digital Ground/Substrate Connection.12DVDD Digital Power Supply Connection.13RESET Active Low Reset Signal. This input resets the entire chip, resetting the control registers and clearingthe digital circuitry.14SCLK Output Serial Clock whose rate determines the serial transfer rate to/from the codec. It is used to clock data or control information to and from the serial port (SPORT). The frequency of SCLK is equal tothe frequency of the master clock (MCLK) divided by an integer number—this integer number beingthe product of the external master clock rate divider and the serial clock rate divider.15MCLK Master Clock Input. MCLK is driven from an external clock signal.16SDO Serial Data Output of the Codec. Both data and control information may be output on this pin and is clocked on the positive edge of SCLK. SDO is in three-state when no information is being transmittedand when SE is low.17SDOFS Framing Signal Output for SDO Serial Transfers. The frame sync is one-bit wide and it is active oneSCLK period before the first bit (MSB) of each output word. SDOFS is referenced to the positiveedge of SCLK. SDOFS is in three-state when SE is low.18SDIFS Framing Signal Input for SDI Serial Transfers. The frame sync is one-bit wide and it is valid oneSCLK period before the first bit (MSB) of each input word. SDIFS is sampled on the negative edge ofSCLK and is ignored when SE is low.19SDI Serial Data Input of the Codec. Both data and control information may be input on this pin and areclocked on the negative edge of SCLK. SDI is ignored when SE is low.20SE SPORT Enable. Asynchronous input enable pin for the SPORT. When SE is set low by the DSP, the output pins of the SPORT are three-stated and the input pins are ignored. SCLK is also disabledinternally in order to decrease power dissipation. When SE is brought high, the control and data regis-ters of the SPORT are at their original values (before SE was brought low), however the timingcounters and other internal registers are at their reset values.–10–REV. B /分销商库存信息:ANALOG-DEVICESAD73311ARZ AD73311ARSZ AD73311LARUZ-RL AD73311LARSZ-REEL AD73311LARUZ-RL7AD73311LARSZ-REEL7 AD73311LARUZ AD73311ARSZ-REEL AD73311ARZ-REEL AD73311LARSZ。

APT-646 733内部电压变压器-仪器变压器说明书