(完整版)stm32f407引脚分配表

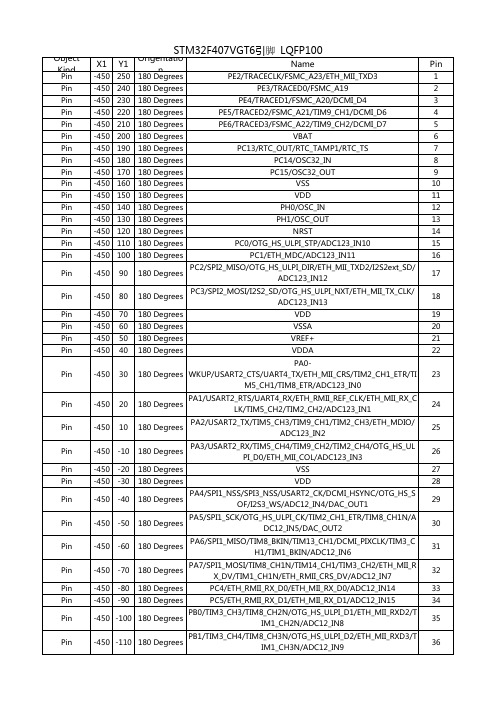

STM32F407VGT6引脚功能定义

Object Kind X1

Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin

Y1 Origentation

180 Degrees 180 Degrees 180 Degrees 180 Degrees 180 Degrees 180 Degrees 180 Degrees 180 Degrees 180 Degrees 180 Degrees 180 Degrees 180 Degrees 180 Degrees 180 Degrees 180 Degrees 180 Degrees

450 450 450 450 450 450 450 450 450 450 450 450 450 450 450 450 450 450 450 450 450 450 450 450 450 450

Pin

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23

-450 250 -450 240 -450 230 -450 220 -450 210 -450 200 -450 190 -450 180 -450 170 -450 160 -450 150 -450 140 -450 130 -450 120 -450 110 -450 100 -450 -450 -450 -450 -450 -450 -450 90 80 70 60 50 40 30

PB1/TIM3_CH4/TIM8_CH3N/OTG_HS_ULPI_D2/ETH_MII_RXD3/T IM1_CH3N/ADC12_IN9 PB2/BOOT1 PE7/FSMC_D4/TIM1_ETR PE8/FSMC_D5/TIM1_CH1N PE9/FSMC_D6/TIM1_CH1 PE10/FSMC_D7/TIM1_CH2N PE11/FSMC_D8/TIM1_CH2 PE12/FSMC_D9/TIM1_CH3N PE13/FSMC_D10/TIM1_CH3 PE14/FSMC_D11/TIM1_CH4 PE15/FSMC_D12/TIM1_BKIN PB10/SPI2_SCK/I2S2_CK/I2C2_SCL/USART3_TX/OTG_HS_ULPI_D 3/ETH_MII_RX_ER/TIM2_CH3 PB11/I2C2_SDA/USART3_RX/OTG_HS_ULPI_D4/ETH_RMII_TX_E N/ETH_MII_TX_EN/TIM2_CH4 VCAP_1 VDD PB12/SPI2_NSS/I2S2_WS/I2C2_SMBA/USART3_CK/TIM1_BKIN/C AN2_RX/OTG_HS_ULPI_D5/ETH_RMII_TXD0/ETH_MII_TXD0/OT G_HS_ID PB13/SPI2_SCK/I2S2_CK/USART3_CTS/TIM1_CH1N/CAN2_TX/O TG_HS_ULPI_D6/ETH_RMII_TXD1/ETH_MII_TXD1 PB14/SPI2_MISO/TIM1_CH2N/TIM12_CH1/OTG_HS_DM/USART 3_RTS/TIM8_CH2N/I2S2ext_SD PB15/SPI2_MOSI/I2S2_SD/TIM1_CH3N/TIM8_CH3N/TIM12_CH2 /OTG_HS_DP PD8/FSMC_D13/USART3_TX PD9/FSMC_D14/USART3_RX PD10/FSMC_D15/USART3_CK PD11/FSMC_CLE/FSMC_A16/USART3_CTS PD12/FSMS_ALE/FSMC_A17/TIM4_CH1/USART3_RTS PD13/FSMC_A18/TIM4_CH2 PD14/FSMC_D0/TIM4_CH3 PD15/FSMC_D1/TIM4_CH4 PC6/I2S2_MCK/TIM8_CH1/SDIO_D6/USART6_TX/DCMI_D0/TIM 3_CH1 PC7/I2S3_MCK/TIM8_CH2/SDIO_D7/USART6_RX/DCMI_D1/TIM 3_CH2 PC8/TIM8_CH3/SDIO_D0/TIM3_CH3/USART6_CK/DCMI_D2 PC9/I2S_CKIN/MCO2/TIM8_CH4/SDIO_D1/I2C3_SDA/DCMI_D3/ TIM3_CH4 PA8/MCO1/USART1_CK/TIM1_CH1/I2C3_SCL/OTG_FS_SOF PA9/USART1_TX/TIM1_CH2/I2C3_SMBA/DCMI_D0/OTG_FS_VB US PA10/USART1_RX/TIM1_CH3/OTG_FS_ID/DCMI_D1 PA11/USART1_CTS/CAN1_RX/TIM1_CH4/OTG_FS_DM PA12/USART1_RTS/CAN1_TX/TIM1_ETR/OTG_FS_DP PA13/JTMS_SWDIO VCAP_2 VSS

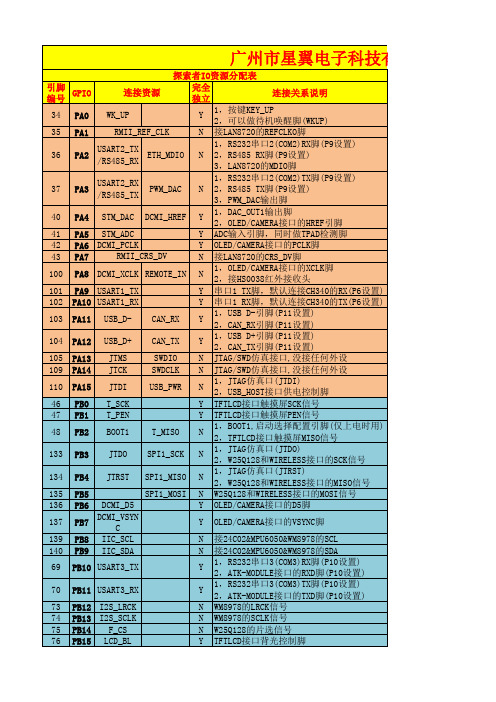

stm32f407IO引脚分配表讲课讲稿

140 PB9 IIC_SDA

N 接24C02&MPU6050&WM8978的SDA

69 PB10 USART3_TX

Y

1,RS232串口3(COM3)RX脚(P10设置) 2,ATK-MODULE接口的RXD脚(P10设置)

70 PB11 USART3_RX

Y

1,RS232串口3(COM3)TX脚(P10设置) 2,ATK-MODULE接口的TXD脚(P10设置)

68 PE15 FSMC_D12

10 PF0 FSMC_A0

N

1,ATK-MODULE接口的LED引脚 2,MPU6050模块的中断脚

N 接LAN8720的MDC脚

N WM8978的SDOUT信号

N WM8978的SDIN信号

N 接LAN8720的RXD0脚

N 接LAN8720的RXD1脚

N

1,WM8978的SDIN信号 2,OLED/CAMERA接口的D0脚

109 PA14 JTCK

SWDCLK N JTAG/SWD仿真接口,没接任何外设

110 PA15 JTDI

USB_PWR

N

1,JTAG仿真口(JTDI) 2,USB_HOST接口供电控制脚

46 PB0 T_SCK

Y TFTLCD接口触摸屏SCK信号

47 PB1 T_PEN

Y TFTLCD接口触摸屏PEN信号

2 PE3 KEY1

3 PE4 KEY0

4 PE5 DCMI_D6

5 PE6 DCMI_D7

58 PE7 FSMC_D4

59 PE8 FSMC_D5

60 PE9 FSMC_D6

63 PE10 FSMC_D7

64 PE11 FSMC_D8

STM32F407ZGT6引脚功能定义

Pin

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34

-450 360 -450 350 -450 340 -450 330 -450 320 -450 310 -450 300 -450 290 -450 280 -450 270 -450 260 -450 250 -450 240 -450 230 -450 220 -450 210 -450 200 -450 190 -450 180 -450 170 -450 160 -450 150 -450 140 -450 130 -450 120 -450 110 -450 100 -450 -450 -450 -450 -450 -450 -450 90 80 70 60 50 40 30

Pin Pin Pin Pin Pin-320 450 -310 450 -300

0 Degrees 0 Degrees 0 Degrees 0 Degrees 0 Degrees 0 Degrees

74 75 76 77 78 79

Name

PE2/TRACECLK/FSMC_A23/ETH_MII_TXD3 PE3/TRACED0/FSMC_A19 PE4/TRACED1/FSMC_A20/DCMI_D4 PE5/TRACED2/FSMC_A21/TIM9_CH1/DCMI_D6 PE6/TRACED3/FSMC_A22/TIM9_CH2/DCMI_D7 VBAT PC13/RTC_OUT/RTC_TAMP1/RTC_TS PC14/OSC32_IN PC15/OSC32_OUT PF0/FSMC_A0/I2C2_SDA PF1/FSMC_A1/I2C2_SCL PF2/FSMC_A2/I2C2_SMBA PF3/FSMC_A3/ADC3_IN9 PF4/FSMC_A4/ADC3_IN14 PF5/FSMC_A5/ADC3_IN15 VSS VDD PF6/TIM10_CH1/FSMC_NIORD/ADC3_IN4 PF7/TIM11_CH1/FSMC_NREG/ADC3_IN5 PF8/TIM13_CH1/FSMC_NIOWR/ADC3_IN6 PF9/TIM14_CH1/FSMC_CD/ADC3_IN7 PF10/FSMC_INTR/ADC3_IN8 PH0/OSC_IN PH1/OSC_OUT NRST PC0/OTG_HS_ULPI_STP/ADC123_IN10 PC1/ETH_MDC/ADC123_IN11 PC2/SPI2_MISO/OTG_HS_ULPI_DIR/ETH_MII_TXD2/I2S2ext_SD/ ADC123_IN12 PC3/SPI2_MOSI/I2S2_SD/OTG_HS_ULPI_NXT/ETH_MII_TX_CLK/ ADC123_IN13 VDD VSSA VREF+ VDDA

STM32F407ZGT6引脚功能定义

Pin Pin Pin Pin Pin Pin

-450 -450 -450 -450 -450 -450

20 10 -10 -20 -30 -40

35 36 37 38 39 40

Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin

STM32F407ZGT6引脚 LQFP144

Object Kind X1

Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin Pin

Pin

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 30 31 32 33 34

-450 360 -450 350 -450 340 -450 330 -450 320 -450 310 -450 300 -450 290 -450 280 -450 270 -450 260 -450 250 -450 240 -450 230 -450 220 -450 210 -450 200 -450 190 -450 180 -450 170 -450 160 -450 150 -450 140 -450 130 -450 120 -450 110 -450 100 -450 -450 -450 -450 -450 -450 -450 90 80 70 60 50 40 30

STM32F407ZGT6引脚功能定义

41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73

PB0/TIM3_CH3/TIM8_CH2N/OTG_HS_ULPI_D1/ETH_MII_RXD2/T -450 -100 180 Degrees IM1_CH2N/ADC12_IN8 -450 -110 180 Degrees -450 -120 180 Degrees -450 -130 180 Degrees -450 -140 180 Degrees -450 -150 180 Degrees -450 -160 180 Degrees -450 -170 180 Degrees -450 -180 180 Degrees -450 -190 180 Degrees -450 -200 180 Degreesgrees -450 -230 180 Degrees -450 -240 180 Degrees -450 -250 180 Degrees -450 -260 180 Degrees -450 -270 180 Degrees -450 -280 180 Degrees -450 -290 180 Degrees -450 -300 180 Degrees -450 -310 180 Degrees -450 -320 180 Degrees -450 -330 180 Degrees -450 -340 180 Degrees -450 -350 180 Degrees -450 -360 180 Degrees 450 -360 0 Degrees PB1/TIM3_CH4/TIM8_CH3N/OTG_HS_ULPI_D2/ETH_MII_RXD3/T IM1_CH3N/ADC12_IN9 PB2/BOOT1 PF11/DCMI_D12 PF12/FSMC_A6 VSS VDD PF13/FSMC_A7 PF14/FSMC_A8 PF15/FSMC_A9 PG0/FSMC_A10 PG1/FSMC_A11 PE7/FSMC_D4/TIM1_ETR PE8/FSMC_D5/TIM1_CH1N PE9/FSMC_D6/TIM1_CH1 VSS VDD PE10/FSMC_D7/TIM1_CH2N PE11/FSMC_D8/TIM1_CH2 PE12/FSMC_D9/TIM1_CH3N PE13/FSMC_D10/TIM1_CH3 PE14/FSMC_D11/TIM1_CH4 PE15/FSMC_D12/TIM1_BKIN PB10/SPI2_SCK/I2S2_CK/I2C2_SCL/USART3_TX/OTG_HS_ULPI_D 3/ETH_MII_RX_ER/TIM2_CH3 PB11/I2C2_SDA/USART3_RX/OTG_HS_ULPI_D4/ETH_RMII_TX_E N/ETH_MII_TX_EN/TIM2_CH4 VCAP_1 VDD PB12/SPI2_NSS/I2S2_WS/I2C2_SMBA/USART3_CK/TIM1_BKIN/C AN2_RX/OTG_HS_ULPI_D5/ETH_RMII_TXD0/ETH_MII_TXD0/OT G_HS_ID PB13/SPI2_SCK/I2S2_CK/USART3_CTS/TIM1_CH1N/CAN2_TX/O TG_HS_ULPI_D6/ETH_RMII_TXD1/ETH_MII_TXD1 PB14/SPI2_MISO/TIM1_CH2N/TIM12_CH1/OTG_HS_DM/USART 3_RTS/TIM8_CH2N/I2S2ext_SD PB15/SPI2_MOSI/I2S2_SD/TIM1_CH3N/TIM8_CH3N/TIM12_CH2 /OTG_HS_DP PD8/FSMC_D13/USART3_TX PD9/FSMC_D14/USART3_RX PD10/FSMC_D15/USART3_CK

stm32f407vet6数据手册_引脚图_参数

This is information on a product in full production. June 2013DocID022152 Rev 41/185STM32F405xxSTM32F407xxDatasheet - production dataFeatures•Core: ARM 32-bit Cortex™-M4 CPU with FPU, Adaptive real-time accelerator (ART Accelerator™) allowing 0-wait state execution from Flash memory, frequency up to 168MHz, memory protection unit, 210DMIPS/1.25DMIPS/MHz (Dhrystone 2.1), and DSP instructions•Memories –Up to 1 Mbyte of Flash memory–Up to 192+4Kbytes of SRAM including 64-Kbyte of CCM (core coupled memory) data RAM–Flexible static memory controller supporting Compact Flash, SRAM, PSRAM, NOR and NAND memories•LCD parallel interface, 8080/6800 modes•Clock, reset and supply management – 1.8 V to 3.6 V application supply and I/Os–POR, PDR, PVD and BOR–4-to-26MHz crystal oscillator–Internal 16 MHz factory-trimmed RC (1% accuracy)–32 kHz oscillator for RTC with calibration–Internal 32 kHz RC with calibration•Low power –Sleep, Stop and Standby modes–V BAT supply for RTC, 20×32 bit backup registers + optional 4 KB backup SRAM•3×12-bit, 2.4MSPS A/D converters: up to 24 channels and 7.2MSPS in triple interleaved mode•2×12-bit D/A converters•General-purpose DMA: 16-stream DMA controller with FIFOs and burst support•Up to 17 timers: up to twelve 16-bit and two 32-bit timers up to 168MHz, each with up to 4 IC/OC/PWM or pulse counter and quadrature (incremental) encoder input •Debug mode –Serial wire debug (SWD) & JTAG interfaces –Cortex-M4 Embedded Trace Macrocell™•Up to 140 I/O ports with interrupt capability –Up to 136 fast I/Os up to 84MHz –Up to 138 5 V-tolerant I/Os •Up to 15 communication interfaces –Up to 3 × I 2C interfaces (SMBus/PMBus)–Up to 4 USARTs/2 UARTs (10.5Mbit/s, ISO 7816 interface, LIN, IrDA, modem control)–Up to 3 SPIs (42Mbits/s), 2 with muxed full-duplex I 2S to achieve audio class accuracy via internal audio PLL or external clock – 2 × CAN interfaces (2.0B Active)–SDIO interface •Advanced connectivity –USB 2.0 full-speed device/host/OTG controller with on-chip PHY –USB 2.0 high-speed/full-speed device/host/OTG controller with dedicated DMA, on-chip full-speed PHY and ULPI –10/100 Ethernet MAC with dedicated DMA: supports IEEE 1588v2 hardware, MII/RMII •8- to 14-bit parallel camera interface up to 54Mbytes/s •True random number generator •CRC calculation unit •96-bit unique ID •RTC: subsecond accuracy, hardware calendarTable 1. Device summary Reference Part number STM32F405xx STM32F405RG, STM32F405VG, STM32F405ZG, STM32F405OG, STM32F405OE STM32F407xxSTM32F407VG, STM32F407IG, STM32F407ZG,STM32F407VE, STM32F407ZE, STM32F407IERevision history STM32F405xx, STM32F407xx 176/185DocID022152 Rev 48 Revision historyTable 98. Document revision historyDateRevision Changes 15-Sep-20111Initial release.24-Jan-20122Added WLCSP90 package on cover page.Renamed USART4 and USART5 into UART4 and UART5,respectively.Updated number of USB OTG HS and FS in Table 2: STM32F405xxand STM32F407xx: features and peripheral counts .Updated Figure 3: Compatible board design betweenSTM32F10xx/STM32F2xx/STM32F4xx for LQFP144 package andFigure 4: Compatible board design between STM32F2xx andSTM32F4xx for LQFP176 and BGA176 packages , and removed note1 and 2.Updated Section 2.2.9: Flexible static memory controller (FSMC).Modified I/Os used to reprogram the Flash memory for CAN2 andUSB OTG FS in Section 2.2.13: Boot modes .Updated note in Section 2.2.14: Power supply schemes .PDR_ON no more available on LQFP100 package. UpdatedSection 2.2.16: Voltage regulator . Updated condition to obtain aminimum supply voltage of 1.7V in the whole document.Renamed USART4/5 to UART4/5 and added LIN and IrDA feature forUART4 and UART5 in Table 5: USART feature comparison .Removed support of I2C for OTG PHY in Section 2.2.30: Universalserial bus on-the-go full-speed (OTG_FS).Added Table 6: Legend/abbreviations used in the pinout table .Table 7: STM32F40x pin and ball definitions : replaced V SS _3, V SS _4,and V SS _8 by V SS ; reformatted Table 7: STM32F40x pin and balldefinitions to better highlight I/O structure, and alternate functionsversus additional functions; signal corresponding to LQFP100 pin 99changed from PDR_ON to V SS ; EVENTOUT added in the list ofalternate functions for all I/Os; ADC3_IN8 added as alternate functionfor PF10; FSMC_CLE and FSMC_ALE added as alternate functionsfor PD11 and PD12, respectively; PH10 alternate functionTIM15_CH1_ETR renamed TIM5_CH1; updated PA4 and PA5 I/Ostructure to TTa.Removed OTG_HS_SCL, OTG_HS_SDA, OTG_FS_INTN in Table 7:STM32F40x pin and ball definitions and Table 9: Alternate functionmapping .Changed TCM data RAM to CCM data RAM in Figure 18: STM32F40xmemory map .Added I VDD and I VSS maximum values in Table 12: Currentcharacteristics .Added Note 1 related to f HCLK , updated Note 2 in Table 14: Generaloperating conditions , and added maximum power dissipation values.Updated Table 15: Limitations depending on the operating powersupply range .STM32F405xx, STM32F407xx Revision history24-Jan-20122(continued)Added V12 in Table19: Embedded reset and power control blockcharacteristics.Updated Table21: Typical and maximum current consumption in Runmode, code with data processing running from Flash memory (ARTaccelerator disabled) and Table20: Typical and maximum currentconsumption in Run mode, code with data processing running fromFlash memory (ART accelerator enabled) or RAM. Added Figure,Figure25, Figure26, and Figure27.Updated Table22: Typical and maximum current consumption in Sleepmode and removed Note 1.Updated Table23: Typical and maximum current consumptions in Stopmode and Table24: Typical and maximum current consumptions inStandby mode, Table25: Typical and maximum current consumptionsin VBAT mode, and Table26: Switching output I/O currentconsumption.Section: On-chip peripheral current consumption: modified conditions,and updated Table27: Peripheral current consumption and Note2.Changed f HSE_ext to 50MHz and t r(HSE)/t f(HSE) maximum value inTable29: High-speed external user clock characteristics.Added C in(LSE) in Table30: Low-speed external user clockcharacteristics.Updated maximum PLL input clock frequency, removed related note,and deleted jitter for MCO for RMII Ethernet typical value in Table35:Main PLL characteristics. Updated maximum PLLI2S input clockfrequency and removed related note in Table36: PLLI2S (audio PLL)characteristics.Updated Section: Flash memory to specify that the devices areshipped to customers with the Flash memory erased. UpdatedTable38: Flash memory characteristics, and added t ME in Table39:Flash memory programming.Updated Table42: EMS characteristics, and Table43: EMIcharacteristics.Updated Table56: I2S dynamic characteristicsUpdated Figure46: ULPI timing diagram and Table62: ULPI timing.Added t COUNTER and t MAX_COUNT in Table51: Characteristics of TIMxconnected to the APB1 domain and Table52: Characteristics of TIMxconnected to the APB2 domain. Updated Table65: Dynamiccharacteristics: Ethernet MAC signals for RMII.Removed USB-IF certification in Section: USB OTG FScharacteristics.Table 98. Document revision history (continued)Date Revision ChangesDocID022152 Rev 4177/185Revision history STM32F405xx, STM32F407xx 178/185DocID022152 Rev 424-Jan-20122(continued)Updated Table 61: USB HS clock timing parameters Updated Table 67: ADC characteristics .Updated Table 68: ADC accuracy at fADC = 30MHz .Updated Note 1 in Table 74: DAC characteristics .Section 5.3.25: FSMC characteristics : updated Table 75 to Table 86, changed C L value to 30pF, and modified FSMC configuration for asynchronous timings and waveforms. Updated Figure 60: Synchronous multiplexed PSRAM write timings .Updated Table 96: Package thermal characteristics .Appendix A.1: USB OTG full speed (FS) interface solutions : modified Figure 86: USB controller configured as peripheral-only and used inFull speed mode added Note 2, updated Figure 87: USB controllerconfigured as host-only and used in full speed mode and addedNote 2, changed Figure 88: USB controller configured in dual modeand used in full speed mode and added Note 3.Appendix A.2: USB OTG high speed (HS) interface solutions : removedfigures USB OTG HS device-only connection in FS mode and USBOTG HS host-only connection in FS mode, and updated Figure 89:USB controller configured as peripheral, host, or dual-mode and usedin high speed mode and added Note 2.Added Appendix A.3: Ethernet interface solutions .Table 98. Document revision history (continued)Date Revision ChangesSTM32F405xx, STM32F407xx Revision history31-May-20123Updated Figure5: STM32F40x block diagram and Figure7: Power supply supervisor interconnection with internal reset OFFAdded SDIO, added notes related to FSMC and SPI/I2S in Table2: STM32F405xx and STM32F407xx: features and peripheral counts. Starting from Silicon revision Z, USB OTG full-speed interface is now available for all STM32F405xx devices.Added full information on WLCSP90 package together with corresponding part numbers.Changed number of AHB buses to 3.Modified available Flash memory sizes in Section2.2.4: Embedded Flash memory.Modified number of maskable interrupt channels in Section2.2.10: Nested vectored interrupt controller (NVIC).Updated case of Regulator ON/internal reset ON, RegulatorON/internal reset OFF, and Regulator OFF/internal reset ON in Section2.2.16: Voltage regulator.Updated standby mode description in Section2.2.19: Low-power modes.Added Note1 below Figure16: STM32F40x UFBGA176 ballout. Added Note1 below Figure17: STM32F40x WLCSP90 ballout. Updated Table7: STM32F40x pin and ball definitions.Added Table8: FSMC pin definition.Removed OTG_HS_INTN alternate function in Table7: STM32F40x pin and ball definitions and Table9: Alternate function mapping. Removed I2S2_WS on PB6/AF5 in Table9: Alternate function mapping.Replaced JTRST by NJTRST, removed ETH_RMII _TX_CLK, and modified I2S3ext_SD on PC11 in Table9: Alternate function mapping. Added Table10: STM32F40x register boundary addresses.Updated Figure18: STM32F40x memory map.Updated V DDA and V REF+ decoupling capacitor in Figure21: Power supply scheme.Added power dissipation maximum value for WLCSP90 in Table14: General operating conditions.Updated V POR/PDR in Table19: Embedded reset and power control block characteristics.Updated notes in Table21: Typical and maximum current consumption in Run mode, code with data processing running from Flash memory (ART accelerator disabled), Table20: Typical and maximum current consumption in Run mode, code with data processing running from Flash memory (ART accelerator enabled) or RAM, and Table22: Typical and maximum current consumption in Sleep mode.Updated maximum current consumption at T A = 25°n Table23: Typical and maximum current consumptions in Stop mode.Table 98. Document revision history (continued)Date Revision ChangesDocID022152 Rev 4179/185Revision history STM32F405xx, STM32F407xx 180/185DocID022152 Rev 431-May-2012 3 (continued)Removed f HSE_ext typical value in Table 29: High-speed external user clock characteristics . Updated Table 31: HSE 4-26 MHz oscillator characteristics and Table 32: LSE oscillator characteristics (fLSE = 32.768 kHz).Added f PLL48_OUT maximum value in Table 35: Main PLL characteristics .Modified equation 1 and 2 in Section 5.3.11: PLL spread spectrum clock generation (SSCG) characteristics .Updated Table 38: Flash memory characteristics , Table 39: Flash memory programming , and Table 40: Flash memory programming with VPP .Updated Section : Output driving current .Table 53: I2C characteristics : Note 4 updated and applied to t h(SDA) in Fast mode, and removed note 4 related to t h(SDA) minimum value.Updated Table 67: ADC characteristics . Updated note concerning ADCaccuracy vs. negative injection current below Table 68: ADC accuracyat fADC = 30MHz .Added WLCSP90 thermal resistance in Table 96: Package thermalcharacteristics .Updated Table 90: WLCSP90 - 0.400 mm pitch wafer level chip sizepackage mechanical data .Updated Figure 83: UFBGA176+25 - ultra thin fine pitch ball grid array10 × 10 × 0.6 mm, package outline and Table 94: UFBGA176+25 -ultra thin fine pitch ball grid array 10 × 10 × 0.6 mm mechanical data .Added Figure 85: LQFP176 recommended footprint .Removed 256 and 768 Kbyte Flash memory density from Table 97:Ordering information scheme .Table 98. Document revision history (continued)Date Revision ChangesSTM32F405xx, STM32F407xx Revision history04-Jun-20134Modified Note1 below Table2: STM32F405xx and STM32F407xx: features and peripheral counts.Updated Figure4 title.Updated Note3 below Figure21: Power supply scheme.Changed simplex mode into half-duplex mode in Section2.2.25: Inter-integrated sound (I2S).Replaced DAC1_OUT and DAC2_OUT by DAC_OUT1 andDAC_OUT2, respectively.Updated pin 36 signal in Figure15: STM32F40x LQFP176 pinout. Changed pin number from F8 to D4 for PA13 pin in Table7:STM32F40x pin and ball definitions.Replaced TIM2_CH1/TIM2_ETR by TIM2_CH1_ETR for PA0 and PA5 pins in Table9: Alternate function mapping.Changed system memory into System memory + OTP in Figure18: STM32F40x memory map.Added Note1 below Table16: VCAP_1/VCAP_2 operating conditions. Updated I DDA description in Table74: DAC characteristics.Removed PA9/PB13 connection to VBUS in Figure86: USB controller configured as peripheral-only and used in Full speed mode and Figure87: USB controller configured as host-only and used in full speed mode.Updated SPI throughput on front page and Section2.2.24: Serial peripheral interface (SPI)Updated operating voltages in Table2: STM32F405xx andSTM32F407xx: features and peripheral countsUpdated note in Section2.2.14: Power supply schemesUpdated Section2.2.15: Power supply supervisorUpdated “Regulator ON” paragraph in Section2.2.16: Voltage regulatorRemoved note in Section2.2.19: Low-power modesCorrected wrong reference manual in Section2.2.28: Ethernet MAC interface with dedicated DMA and IEEE1588 supportUpdated Table15: Limitations depending on the operating power supply rangeUpdated Table24: Typical and maximum current consumptions in Standby modeUpdated Table25: Typical and maximum current consumptions in VBAT modeUpdated Table36: PLLI2S (audio PLL) characteristicsUpdated Table43: EMI characteristicsUpdated Table48: Output voltage characteristicsUpdated Table50: NRST pin characteristicsUpdated Table55: SPI dynamic characteristicsUpdated Table56: I2S dynamic characteristicsDeleted Table 59Updated Table62: ULPI timingUpdated Figure47: Ethernet SMI timing diagramTable 98. Document revision history (continued)Date Revision ChangesDocID022152 Rev 4181/185Revision history STM32F405xx, STM32F407xx 182/185DocID022152 Rev 404-Jun-20134(continued)Updated Figure 83: UFBGA176+25 - ultra thin fine pitch ball grid array 10 × 10 × 0.6 mm, package outline Updated Table 94: UFBGA176+25 - ultra thin fine pitch ball grid array 10 × 10 × 0.6 mm mechanical data Updated Figure 5: STM32F40x block diagram Updated Section 2: Description Updated footnote (3) in Table 2: STM32F405xx and STM32F407xx: features and peripheral counts Updated Figure 3: Compatible board design between STM32F10xx/STM32F2xx/STM32F4xx for LQFP144 package Updated Figure 4: Compatible board design between STM32F2xx and STM32F4xx for LQFP176 and BGA176 packages Updated Section 2.2.14: Power supply schemes Updated Section 2.2.15: Power supply supervisor Updated Section 2.2.16: Voltage regulator , including figures.Updated Table 14: General operating conditions , including footnote (2).Updated Table 15: Limitations depending on the operating power supply range , including footnote (3).Updated footnote (1) in Table 67: ADC characteristics .Updated footnote (3) in Table 68: ADC accuracy at fADC = 30MHz .Updated footnote (1) in Table 74: DAC characteristics .Updated Figure 9: Regulator OFF .Updated Figure 7: Power supply supervisor interconnection with internal reset OFF .Added Section 2.2.17: Regulator ON/OFF and internal reset ON/OFFavailability .Updated footnote (2) of Figure 21: Power supply scheme .Replaced respectively “I2S3S_WS" by "I2S3_WS”, “I2S3S_CK” by“I2S3_CK” and “FSMC_BLN1” by “FSMC_NBL1” in Table 9: Alternatefunction mapping .Added “EVENTOUT” as alternate function “AF15” for pin PC13, PC14,PC15, PH0, PH1, PI8 in Table 9: Alternate function mappingReplaced “DCMI_12” by “DCMI_D12” in Table 7: STM32F40x pin andball definitions .Removed the following sentence from Section : I2C interfacecharacteristics : ”Unless otherwise specified, the parametersgiven in Table 53 are derived from tests performed under theambient temperature, f PCLK1 frequency and V DD supply voltageconditions summarized in Table 14.”.In Table 7: STM32F40x pin and ball definitions on page 45:–For pin PC13, replaced “RTC_AF1” by “RTC_OUT, RTC_TAMP1,RTC_TS”–for pin PI8, replaced “RTC_AF2” by “RTC_TAMP1, RTC_TAMP2,RTC_TS”.–for pin PB15, added RTC_REFIN in Alternate functions column.In Table 9: Alternate function mapping on page 60, for portPB15, replaced “RTC_50Hz” by “RTC_REFIN”.Table 98. Document revision history (continued)Date Revision ChangesSTM32F405xx, STM32F407xx Revision history04-Jun-20134(continued)Updated Figure6: Multi-AHB matrix.Updated Figure7: Power supply supervisor interconnection withinternal reset OFFChanged 1.2V to V12 in Section: Regulator OFFUpdated LQFP176 pin 48.Updated Section1: Introduction.Updated Section2: Description.Updated operating voltage in Table2: STM32F405xx andSTM32F407xx: features and peripheral counts.Updated Note1.Updated Section2.2.15: Power supply supervisor.Updated Section2.2.16: Voltage regulator.Updated Figure9: Regulator OFF.Updated Table3: Regulator ON/OFF and internal reset ON/OFFavailability.Updated Section2.2.19: Low-power modes.Updated Section2.2.20: VBAT operation.Updated Section2.2.22: Inter-integrated circuit interface (I²C) .Updated pin 48 in Figure15: STM32F40x LQFP176 pinout.Updated Table6: Legend/abbreviations used in the pinout table.Updated Table7: STM32F40x pin and ball definitions.Updated Table14: General operating conditions.Updated Table15: Limitations depending on the operating powersupply range.Updated Section5.3.7: Wakeup time from low-power mode.Updated Table33: HSI oscillator characteristics.Updated Section5.3.15: I/O current injection characteristics.Updated Table47: I/O static characteristics.Updated Table50: NRST pin characteristics.Updated Table53: I2C characteristics.Updated Figure39: I2C bus AC waveforms and measurement circuit.Updated Section5.3.19: Communications interfaces.Updated Table67: ADC characteristics.Added Table70: Temperature sensor calibration values.Added Table73: Internal reference voltage calibration values.Updated Section5.3.25: FSMC characteristics.Updated Section5.3.27: SD/SDIO MMC card host interface (SDIO)characteristics.Updated Table23: Typical and maximum current consumptions in Stopmode.Updated Section: SPI interface characteristics included Table55.Updated Section: I2S interface characteristics included Table56.Updated Table64: Dynamic characteristics: Ehternet MAC signals forSMI.Updated Table66: Dynamic characteristics: Ethernet MAC signals forMII.Table 98. Document revision history (continued)Date Revision ChangesDocID022152 Rev 4183/185Revision history STM32F405xx, STM32F407xx 184/185DocID022152 Rev 404-Jun-20134(continued)Updated Table 64: Dynamic characteristics: Ehternet MAC signals for SMI .Updated Table 66: Dynamic characteristics: Ethernet MAC signals for MII .Updated Table 79: Synchronous multiplexed NOR/PSRAM read timings .Updated Table 80: Synchronous multiplexed PSRAM write timings .Updated Table 81: Synchronous non-multiplexed NOR/PSRAM read timings .Updated Table 82: Synchronous non-multiplexed PSRAM writetimings .Updated Section 5.3.26: Camera interface (DCMI) timing specificationsincluding Table 87: DCMI characteristics and addition of Figure 73:DCMI timing diagram .Updated Section 5.3.27: SD/SDIO MMC card host interface (SDIO)characteristics including Table 88.Updated Chapter Figure 9.Table 98. Document revision history (continued)Date Revision ChangesSTM32F405xx, STM32F407xxPlease Read Carefully:Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries (“ST”) reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.All ST products are sold pursuant to ST’s terms and conditions of sale.Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.UNLESS OTHERWISE SET FORTH IN ST’S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.ST PRODUCTS ARE NOT AUTHORIZED FOR USE IN WEAPONS. NOR ARE ST PRODUCTS DESIGNED OR AUTHORIZED FOR USE IN: (A) SAFETY CRITICAL APPLICATIONS SUCH AS LIFE SUPPORTING, ACTIVE IMPLANTED DEVICES OR SYSTEMS WITH PRODUCT FUNCTIONAL SAFETY REQUIREMENTS; (B) AERONAUTIC APPLICATIONS; (C) AUTOMOTIVE APPLICATIONS OR ENVIRONMENTS, AND/OR (D) AEROSPACE APPLICATIONS OR ENVIRONMENTS. WHERE ST PRODUCTS ARE NOT DESIGNED FOR SUCH USE, THE PURCHASER SHALL USE PRODUCTS AT PURCHASER’S SOLE RISK, EVEN IF ST HAS BEEN INFORMED IN WRITING OF SUCH USAGE, UNLESS A PRODUCT IS EXPRESSLY DESIGNATED BY ST AS BEING INTENDED FOR “AUTOMOTIVE, AUTOMOTIVE SAFETY OR MEDICAL” INDUSTRY DOMAINS ACCORDING TO ST PRODUCT DESIGN SPECIFICATIONS. PRODUCTS FORMALLY ESCC, QML OR JAN QUALIFIED ARE DEEMED SUITABLE FOR USE IN AEROSPACE BY THE CORRESPONDING GOVERNMENTAL AGENCY.Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.DocID022152 Rev 4185/185万联芯城专注电子元器件配单服务,只售原装现货库存,万联芯城所售芯片IC,电阻电容,二三极管等物料,原装质量有保障,价格有明显优势,已为全国多家企业提供配套服务,客户只需提交BOM表,即可获得优势报价,整单采购有优惠,万联芯城拥有完善的产品供应链体系及现代化仓储系统,可满足多种BOM报价需求,PDF完整版点击进入万联芯城。

STM32F407VGT6芯片管脚功能定义

OTG_HS_ULPI_D7 /

ETH_PPS_OUT/TIM3_CH

2 / SPI1_MOSI/

SPI3_MOSI / DCMI_D10 /

I2S3_SD/ EVENTOUT

92 PB6 I2C1_SCL/ TIM4_CH1 /

CAN2_TX /

ETH_MII_TXD0/

OTG_HS_ID/ EVENTOUT 52 PB13 SPI2_SCK / I2S2_CK /

USART3_CTS/

TIM1_CH1N /CAN2_TX /

OTG_HS_ULPI_D6 /

ETH_RMII_TXD1 /

ETH_MII_TXD1/

EVENTOUT

53 PB14 SPI2_MISO/ TIM1_CH2N /

OTG_HS_ULPI_CK /

TIM2_CH1_ETR/

TIM8_CHIN/ EVENTOUT 31 PA6 SPI1_MISO /

TIM8_BKIN/TIM13_CH1 /

DCMI_PIXCLK / TIM3_CH1

/ TIM1_BKIN/ EVENTOUT 32 PA7 SPI1_MOSI/ TIM8_CH1N /

EVENTOUT

56 PD9 FSMC_D14 / USART3_RX/

EVENTOUT

57 PD10 FSMC_D15 / USART3_CK/

EVENTOUT

58 PD11 FSMC_CLE /

FSMC_A16/USART3_CTS/

EVENTOUT

59 PD12 FSMC_ALE/

FSMC_A17/TIM4_CH1 /

USART3_RTS/

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

OLED/CAMERA接口的D1脚

98

PC8

SDIO_D0

DCMI_D2

N

1,SD卡接口的D0

2,OLED/CAMERA接口的D2脚

99

PC9

SDIO_D1

DCMI_D3

N

1,SD卡接口的D1

2,OLED/CAMERA接口的D3脚

111

PC10

SDIO_D2

N

SD卡接口的D2

112

PC11

SDIO_D3

PF6

GBC_KEY

Y

接ATK-MODULE接口的KEY脚

19

PF7

LIGHT_SENSOR

N

接光敏传感器(LS1)

20

PF8

BEEP

N

接蜂鸣器(BEEP)

21

PF9

LED0

N

接DS0 LED灯(红色)

22

PF10

LED1

N

接DS1 LED灯(绿色)

49

PF11

T_MOSI

Y

TFTLCD接口触摸屏MOSI信号

如不用LAN8720,并去掉P9跳线帽,可以做普通IO用

该IO通过P9选择连接RS232还是RS485,并同时连接了PWM_DAC, 这里的RS232 TX脚是指SP3232芯片的TX脚,接STM32的RX脚

去掉P9跳线帽,可以做普通IO用

该IO可做DAC输出,同时也连接在OLED/CAMERA接口,如不插外设在OLED/CAMERA接口,

137

PB7

DCMI_VSYNC

Y

OLED/CAMERA接口的VSYNC脚

139

PB8

IIC_SCL

N

接24C02&MPU6050&WM8978的SCL

140

PB9

IIC_SDA

N

接24C02&MPU6050&WM8978的SDA

69

PB10

USART3_TX

Y

1,RS232串口3(COM3)RX脚(P10设置)

2,RS485 RX脚(P9设置)

3,LAN8720的MDIO脚

37

PA3

USART2_RX

/RS485_TX

PWM_DAC

N

1,RS232串口2(COM2)TX脚(P9设置)

2,RS485 TX脚(P9设置)

3,PWM_DAC输出脚

40

PA4

STM_DAC

DCMI_HREF

Y

1,DAC_OUT1输出脚

控制,不建议做普通IO使用

该IO通过P6选择是否连接CH340的RXD,如果不连接,则该IO完全独立

该IO通过P6选择是否连接CH340的TXD,如果不连接,则该IO完全独立

该IO通过P11选择连接USB D-还是CAN_RX,如果去掉P11的跳线帽,则该IO完全独立

该IO通过P11选择连接USB D+还是CAN_TX,如果去掉P11的跳线帽,则该IO完全独立

2,W25Q128和WIRELESS接口的SCK信号

134

PB4

JTRST

SPI1_MISO

N

1,JTAG仿真口(JTRST)

2,W25Q128和WIRELESS接口的MISO信号

135

PB5

SPI1_MOSI

N

W25Q128和WIRELESS接口的MOSI信号

136

PB6

DCMI_D5

Y

OLED/CAMERA接口的D5脚

128

PG13

RMII_TXD0

N

接LAN8720的TXD0脚

129

PG14

RMII_TXD1

N

接LAN8720的TXD1脚

132

PG15

DCMI_RESET

Y

OLED/CAMERA接口的RESET脚

引脚编号:对应STM32F407ZGT6的引脚编号GPIO:STM32F407ZGT6的IO口

完全独立:指该IO通过一定的方法,可以达到完全悬空的效果(即不接任何其他外连接关系说明:说明每个IO口与外设的连接关系

119

PD5

FSMC_NWE

N

FSMC总线NWE(WR)(LCD/SRAM共用)

122

PD6

DCMI_SCL

Y

OLED/CAMERA接口的SCL脚

123

PD7

DCMI_SDA

Y

OLED/CAMERA接口的SDA脚

77

PD8

FSMC_D13

N

FSMC总线数据线D13(LCD/SRAM共用)

78

PD9

FSMC_D14

104

PA12

USB_D+

CAN_TX

Y

1,USBD+引脚(P11设置)

2,CAN_TX引脚(P11设置)

105

PA13

JTMS

SWDIO

N

JTAG/SWD仿真接口,没接任何外设

109

PA14

JTCK

SWDCLK

N

JTAG/SWD仿真接口,没接任何外设

110

PA15

JTDI

USB_PWR

N

1,JTAG仿真口(JTDI)

Y

接按键KEY2

2

PE3

KEY1

Y

接按键KEY1

3

PE4

KEY0

Y

接按键KEY0

4

PE5

DCMI_D6

Y

OLED/CAMERA接口的D6脚

5

PE6

DCMI_D7

Y

OLED/CAMERA接口的D7脚

58

PE7

FSMC_D4

N

FSMC总线数据线D4(LCD/SRAM共用)

59

PE8

FSMC_D5

N

FSMC总线数据线D5(LCD/SRAM共用)

2,接HS0038红外接收头

101

PA9

USART1_TX

Y

串口1 TX脚,默认连接CH340的RX(P6设置)

102

PA10

USART1_RX

Y

串口1 RX脚,默认连接CH340的TX(P6设置)

103

PA11

USB_D-

CAN_RX

Y

1,USBD-引脚(P11设置)

2,CAN_RX引脚(P11设置)

75

PB14

F_CS

N

W25Q128的片选信号

76

PB15

LCD_BL

Y

TFTLCD接口背光控制脚

26

PC0

GBC_LED

3D_INT

N

1,ATK-MODULE接口的LED引脚

2,MPU6050模块的中断脚

27

PC1

ETH_MDC

N

接LAN8720的MDC脚

28

PC2

I2S_SDOUT

N

WM8978的SDOUT信号

则可以完全独立

拔了P12的跳线帽,则该IO完全独立

仅连接OLED/CAMERA接口的PCLK,当不使用OLED/CAMERA接口时,该IO完全独立

该IO直接接LAN8720的CRS_DV引脚,当LAN8720处于复位状态时,可以做普通IO用

同时连接了XCLK脚HS0038红外头,HS0038红外接收头,有4.7K上拉电阻,且受HS0038

JTAG/SWD仿真接口,没连外设。建议仿真器选择SWD调试,这样仅SWDIO和SWDCLK两个

2,OLED/CAMERA接口的HREF引脚

41

PA5

STM_ADC

Y

ADC输入引脚,同时做TPAD检测脚

42

PA6

DCMI_PCLK

Y

OLED/CAMERA接口的PCLK脚

43

PA7

RMII_CRS_DV

N

接LAN8720的CRS_DV脚

100

PA8

DCMI_XCLK

REMOTE_IN

N

1,OLED/CAMERA接口的XCLK脚

29

PC3

I2S_SDIN

N

WM8978的SDIN信号

44

PC4

RMII_RXD0

N

接LAN8720的RXD0脚

45

PC5

RMII_RXD1

N

接LAN8720的RXD1脚

96

PC6

I2S_MCLK

DCMI_D0

N

1,WM8978的SDIN信号

2,OLED/CAMERA接口的D0脚

97

PC7

DCMI_D1

使用提示:介绍每个IO的特点和使用方法,方便大家掌握开发板每一个IO口的使用

只要KEY_UP不按下,该IO完全独立

该IO直接接LAN8720的REFCLKO引脚,接收50M时钟(一直有),不建议做普通IO用

该IO通过P9选择连接RS232还是RS485,并同时连接了LAN8720的MDIO脚这里的RS232 0

N

FSMC总线数据线D10(LCD/SRAM共用)

67

PE14

FSMC_D11

N

FSMC总线数据线D11(LCD/SRAM共用)

68

PE15

FSMC_D12

N

FSMC总线数据线D12(LCD/SRAM共用)

10

PF0

FSMC_A0

N

FSMC总线地址线A0(SRAM专用)

11

PF1

FSMC_A1

N

FSMC总线数据线D14(LCD/SRAM共用)