quartus分享--SignalTap的使用方法

quartusII13.0逻辑分析仪使用

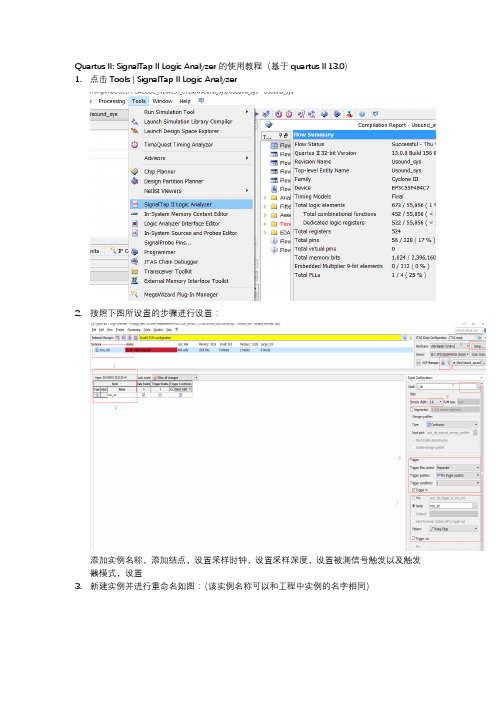

Quartus II: SignalTap II Logic Analyzer的使用教程(基于quartus II 13.0)

1.点击Tools | SignalTap II Logic Analyzer

2.按照下图所设置的步骤进行设置:

添加实例名称,添加结点,设置采样时钟,设置采样深度,设置被测信号触发以及触发器模式,设置

3.新建实例并进行重命名如图:(该实例名称可以和工程中实例的名字相同)

4.为仿真实例添加结点,按软件提示新建结点

4.1打开结点查找器,将新建的实例的与工程中的信号结点绑定起来。

如图:点击1处设置过滤类型为前综合类型,点击2处的List,选择相应的结点。

4.2点击下图1导入结点,设置完成后,点击2处确定。

5.信号配置:

a)设置采样时钟:

点击1处,打开结点查找器,点击2搜索相应结点,并导入工程系统时钟,设置完

成后点击OK

b)设置采样深度,以及信号触发模式以及触发器模式按照下图进行设置即可

6.所有设置完成后点击保存,

7.按照如图下步骤进行硬件配置以及下载,然后进行JTAG调试

点击2处设置JTAG连接器硬件,

点击3处进行FPGA芯片扫描

点击4处进行下载

点击1处进行调试,观察仿真结果

8.运行结果如图所示:

9.注意:断电之后拔掉JTAG。

静电可以击穿芯片。

Signal TAP使用案例

初步学习使用Signal Tap 进行调试。

使用signal tap需要先建立一个 signaltap II logic analyzer file .将这个文件添加到qeartus project当中。

在此之前要先编译好之前的project,添加好signaltap文件并设置好之后,重新编译,然后下载到FPGA中运行,此时,在signaltap的操作界面点击运行,就可以看到相关的采样数据。

理解:signal文件是添加到project并编译的,所以一样是下载到了FPGA里面,是实际的电路。

在最后调试完之后,把这部分文件删除再重新编译,不然很浪费FPGa空间。

设置界面是这样的:segmented 用来设置分段存储模式!不选的话是设置成连续模式。

这点与下面将要转载的文章不一致,其他都是参考这篇文章来的。

下面将这篇文章插入进来,仔细研读这篇文章就好了!SignalTap II将逻辑分析模块嵌入到FPGA中,如图1所示。

逻辑分析模块对待测节点的数据进行捕获,数据通过JTAG接口从FPGA传送到Quartus II软件中显示。

使用SignalTap II 无需额外的逻辑分析设备,只需将一根JTAG接口的下载电缆连接到要调试的FPGA器件。

SignalTap II对FPGA的引脚和内部的连线信号进行捕获后,将数据存储在一定的RAM块中。

因此,需要用于捕获的采样时钟信号和保存被测信号的一定点数的RAM块。

使用SignalTap II的一般流程是:设计人员在完成设计并编译工程后,建立SignalTap II (.stp)文件并加入工程、配置STP文件、编译并下载设计到FPGA、在Quartus II软件中显示被测信号的波形、在测试完毕后将该逻辑分析仪从项目中删除。

以下描述设置SignalTap II 文件的基本流程:1.设置采样时钟。

采样时钟决定了显示信号波形的分辨率,它的频率要大于被测信号的最高频率,否则无法正确反映被测信号波形的变化。

SignalTapII及SignalProbe使用指南

SignalTapII 及SignalProbe 使用指南1.SignalTapII 支持器件及下载电缆SignalTapII 内嵌式规律需要占用ALMs/LEs 布线资源和RAM 采样存储资源,支持下面的器件系列:StratxiII、Stratix、StratixIIGX、StratixGX、CycloneII、Cyclone、APEXII、APEX20K/E/C、Excalibur 和Mercury。

SignalII 规律支持目前Altera 全部下载电缆,包括USB Blaster、ByteBlasterII、ByteBlasterMV 和MasterBlaster。

2.SignalTapII 工作流程及资源消耗○1配置ELA〔Embedded Logic Analyzer〕。

○2通过QuartusII软件完成布局布线,ELA下载至FPGA中。

○3ELA采样到内部触发信号。

○4ELA通过JTAG电路与QuartusII软件发生通信,以图形化的界面显示出来。

ELA 占用片内LE 资源由信号通道数及触发级数打算,占用片内RAM 资源由信号通道数及采样深度来打算。

Altera 建议选择选择通道数量和采样深度时要考虑二者之间的平衡,以免占用太多RAM 资源,影响原本的规律设计。

比方不推举同时使用1024 个最大通道数和128K 最大采样深度〔相当于消耗了32,768 个M4K 的资源〕。

下表给出了在Statix/Cyclone 器件中使用ELA 的资源占用状况。

8316 371 42632 566 773 981256 2900 4528 61568< 1 1416 6432 2416 64 256256 16 32 128 5123.SignalTapII 设计流程在设计中嵌入SignalTapII有两种方法:一是创立一个SignalTapII文件〔.stp〕,然后定义STP 文件的具体内容;二是用MegaWizard Plug-In Manager 建立并配置STP 文件,然后用MegaWizard 实例化一个HDL 输出模块。

SignalTapII简单使用小记

SignalTapII简单使用小记Signal Tap II有助于观察逻辑内部信号行为,可使不借助外部设备进行设计调试。

(当然使用的前提条件是有硬件平台)Signal Tap II ELA 组成框图采样获得的数据会存储在器件的存储器块中,通过JTAG下载线可以把数据传回Quartus 中进行波形显示。

可以设置数据采集缓冲器(Buffers)的大小、数据采集方式和存储方式、以及此Buffer的存储器类型。

可以在一片FPGA上生成多个ELA,这一功能非常适合在设计中为每个时钟域配备一个分析仪。

ELA可以计算每个实例用到的逻辑资源和存储器资源,并显示在实例管理器中。

要使用Signal Tap II ELA,必须对其进行配置:1 设置采样时钟。

ELA只能在采样时钟的上升沿采样数据,可以使用设计中的任何信号作为采样时钟(推荐使用全局的与被测信号同步的非门控信号)。

采样时钟决定了信号波形的分辨率,它的频率要大于被测信号的最高频率。

2 设置被测信号。

可以分配两种信号(通过Node List信号设置触发条件):Pre-Synthesis:设计拟定之后,综合优化之前的信号,反映RTL 级信号。

(RTL Viewer)Post-fitting :物理综合优化和布局布线后的信号(Technical Map Viewer)为了可以使用增量编译,建议不要混合使用两种信号;若使用了预综合信号则要采取信号保留(Signal Preservation)措施。

不可测试引脚:Post-fit输出引脚、进位链信号、JTAG控制信号、ALTGXB宏功能信号、LVDS信号(串行/解串器块的数据输出)、DQ/DQS信号。

3 设置采样深度。

代表每个信号的采样数量,即采样Buffer大小。

还可以选择采样Buffer的RAM类型,如M4K、M512、M_RAM等。

被测信号波形的时间长度为t,则t = N × T. N为Buffer存储的采样点数(采样深度),T为采样时钟周期。

QuartusII中 SignalTapⅡ逻辑分析仪的使用

第10章SignalTapⅡ嵌入式逻辑分析仪的使用10.1 在设计中嵌入SignalTapⅡ逻辑分析仪10.2 在SOPC Builder中使用SignalTapⅡ逻辑分析仪10.3 在DSP Builder中使用SignalTapⅡ逻辑分析仪思考题10.1 在设计中嵌入SignalTapⅡ逻辑分析仪在设计中嵌入SignalTapⅡ逻辑分析仪有两种方法:第一种方法是建立一个SignalTapⅡ文件(.stp),然后定义STP文件的详细内容;第二种方法是用MegaWizard Plug-In Manager建立并配置STP文件,然后用MegaWizard实例化一个HDL输出模块。

图10.1给出用这两种方法建立和使用SignalTapⅡ逻辑分析仪的过程。

SignalTapMegaWizardQuartusSTPQuartus,/ 图10.1 SignalTapⅡ操作流程10.1.1 使用STP文件建立嵌入式逻辑分析仪1.创建STP文件STP文件包括SignalTapⅡ逻辑分析仪设置部分和捕获数据的查看、分析部分。

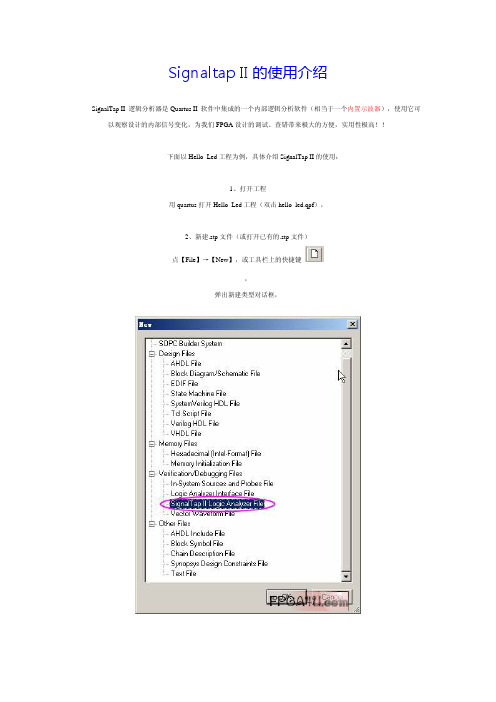

创建一个STP文件的步骤如下:(1) 在QuartusⅡ软件中,选择File→New命令。

(2) 在弹出的New对话框中,选择Other Files标签页,从中选择SignalTapⅡ File,如图10.2所示。

图10.2 新建一个STP文件(3) 点击OK按钮确定,一个新的SignalTapⅡ窗口如图10.3所示。

DataS etup图10.3 SignalTapⅡ窗口上面的操作也可以通过Tools→SignalTapⅡLogic Analyzer命令完成,这种方法也可以用来打开一个已经存在的STP文件。

2.设置采集时钟在使用SignalTapⅡ逻辑分析仪进行数据采集之前,首先应该设置采集时钟。

采集时钟在上升沿处采集数据。

设计者可以使用设计中的任意信号作为采集时钟,但Altera建议最好使用全局时钟,而不要使用门控时钟。

altera signaltap核例化与使用

altera signaltap核例化与使用SignalTap是Altera公司提供的一个强大的逻辑分析工具。

它可以用于调试和分析FPGA设计中的信号。

SignalTap提供了FPGA内部信号的实时观察和记录功能,可以用于查看特定信号的波形和统计信息,从而有效地进行调试和分析。

为了方便使用SignalTap,首先需要对其进行核例化。

核例化是在设计中插入一个SignalTap模块,以便于对指定信号进行分析。

下面将详细介绍SignalTap的核例化和使用。

1.核例化SignalTap:a.打开Quartus Prime软件,在项目导航器中选择要核例化SignalTap的设计文件。

b.右键点击设计文件,选择“Start Analysis & Synthesis",进入设计的综合和分析设置。

c.在综合设置对话框中,选择“Add/Remove Assignments",在控制面板中选择“SignalTap II Logic Analyzer",点击“OK"。

d.在SignalTap Logic Analyzer对话框中,选择“Create a new SignalTap II instance"。

e.在SignalTap II Analyzer Instance对话框中,选择要观察的信号和模块,并设置时钟和采样点等参数。

点击“OK"保存设置。

f.回到设计窗口,编译设计文件,核例化SignalTap。

2. SignalTap使用:a.完成核例化后,可以打开SignalTap II Logic Analyzer的视图。

点击菜单栏上的“Tools"并选择“S ignalTap II Logic Analyzer",或者使用快捷键Ctrl+Alt+L。

b.在SignalTap II Logic Analyzer的视图中,可以选择要观察的信号,并设置触发条件和触发位置等参数。

altera signaltap ip核例化与使用

Altera(现在由英特尔公司拥有)的SignalTap是一种用于逻辑分析和调试的IP核,用于FPGA设计。

它允许你在FPGA中捕获和分析信号以进行调试。

下面是关于如何实例化和使用Altera SignalTap IP核的一般步骤:1. **打开Quartus Prime**:首先,打开Altera的Quartus Prime集成开发环境(IDE)。

2. **创建一个工程**:创建一个新的FPGA工程或打开现有的工程。

3. **添加SignalTap IP核**:在Quartus Prime中,你可以通过以下步骤添加SignalTap IP 核:- 在"Project"菜单下,选择"Add/Remove MegaWizard Plug-In Manager"。

- 在"MegaWizard Plug-In Manager"对话框中,选择"SignalTap II"。

- 配置SignalTap II,选择你要捕获和分析的信号。

你可以选择要监视的信号,设置触发条件,以及其他配置选项。

4. **生成和编译设计**:确保你的设计和SignalTap IP核都已经添加到工程中,并生成和编译你的FPGA设计。

5. **配置SignalTap II**:在Quartus Prime中,选择"Tools" > "SignalTap II Logic Analyzer"以打开SignalTap II配置界面。

在此界面中,你可以完成以下操作:- 添加捕获点:选择要捕获的信号,并将它们添加到捕获点列表中。

- 配置触发条件:设置触发条件,以确定何时开始捕获信号。

- 配置存储深度:设置存储深度,以确定SignalTap II可以捕获多少时钟周期的数据。

- 配置触发操作:设置触发后要执行的操作,如停止或暂停捕获。

quartus分享--SignalTap的使用方法

SignalTap的使用方法SignalTap是由Altera公司开发的一个在线、片内信号分析的工具,为设计开发者验证所用。

我们什么时候会用到signalTap呢?当代码经过仿真没有问题,但加载到FPGA电路板后,发现功能不正确时,我们就可以用signalTap工具进行分析,它的作用就类似于一个数字逻辑分析仪。

利用signaltap基本上可以代替数字逻辑分析仪了,它是quartus里最常用的工具,同学们必须熟练使用这个工具。

1.SignalTapII原理在使用signalTap前,我们先理解一下SignalTap的原理,这样就助于理解每个参数。

如下图所示,我们想观察一组信号,我们称之为“被测信号”(可以是多个),同时我们指定一个采样时钟。

现在我们想看这个被测信号,在其下降沿前后几个时钟内,被测信号的值是多少。

那么“下降沿”就是触发条件。

当满足触发条件时,signaltap会将触发条件前后,时钟上升沿时的所有信号值保存到一个RAM当中。

我们可以指定触发条件前后采多少个样点。

如果RAM比较大,那么可以保存的数据就比较多。

如果RAM比较小,那么保存的数据自然少。

(因此RAM大小决定了观察数据的多少)。

SignalTap将数据保存到RAM后,将读出RAM中的数据,然后逐个在显示器中显示出来(因此SignalTap看到的都是理想的,没有毛刺的信号)。

2.打开SignalTapII打开Quartus后,在菜单栏中,选择“Tools”->”SignalTal II Logic Analyzer”,就可以打开SignalTap工具。

如下图:3.界面介绍上面是SignalTap的界面,我们按照使用顺序简述地介绍每个部分功能。

红色标号1:下载线选择,点击setup选择硬件的USB接口红色标号2:硬件检测,扫描有没有FPGA硬件。

红色标号3:选择工程配置文件。

可以将综合后的sof文件加载进来红色标号4:正式加载sof工程文件红色标号5:设置采样时钟红色标号6:设置RAM的大小红色标号7:选择要观察的信号,并且设置触发条件红色标号8:开始运行,等待触发条件满足后显示波形红色标号9:这里可以观察FPGA资源使用情况。

SignalTap Ⅱ的使用方法

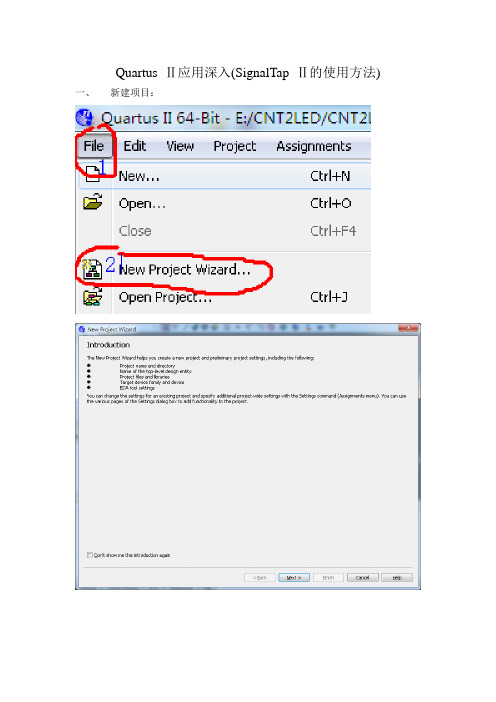

Quartus Ⅱ应用深入(SignalTap Ⅱ的使用方法) 一、新建项目:二、新建Verilog文件:三、输入代码:module CNT2LED(CLK,RST,EN,LOAD,DATA,COUT,LED,DOUT,SCL); input CLK,RST,EN,LOAD;input[3:0] DATA;output COUT,SCL;output[3:0] DOUT;output[6:0] LED;wire[6:0] led;CNT10 inst(.CLK(CLK),.RST(RST),.EN(EN),.LOAD(LOAD),.DATA(DATA),.COUT(COUT),.DOUT(DOUT));DECL7S inst1(.A(DOUT),.LED7S(led));assign LED=~led;assign SCL=0;endmodule保存CNT2LEDmodule CNT10 (CLK,RST,EN,LOAD,COUT,DOUT,DATA);input CLK;input EN;input RST ;input LOAD;input [3:0] DATA;output [3:0] DOUT;output COUT ;reg [3:0] Q1;reg COUT;assign DOUT = Q1;always @(posedge CLK or negedge RST)beginif(!RST) Q1<= 4'b0000;else if(!EN)beginif(!LOAD) Q1<= DATA;else if(Q1<9) Q1<= Q1+1;else Q1<= 4'b0000;endendalways @(Q1)if (Q1==4'h9) COUT = 1'b1;else COUT = 1'b0;endmodulemodule DECL7S(A,LED7S);input[3:0] A;output[6:0] LED7S;reg [6:0] LED7S;always@(A)case(A)4'b0000: LED7S<=7'b0111111;4'b0001: LED7S<=7'b0000110;4'b0010: LED7S<=7'b1011011;4'b0011: LED7S<=7'b1001111;4'b0100: LED7S<=7'b1100110;4'b0101: LED7S<=7'b1101101;4'b0110: LED7S<=7'b1111101;4'b0111: LED7S<=7'b0000111;4'b1000: LED7S<=7'b1111111;4'b1001: LED7S<=7'b1101111;4'b1010: LED7S<=7'b1110111;4'b1011: LED7S<=7'b1111100;4'b1100: LED7S<=7'b0111001;4'b1101: LED7S<=7'b1011110;4'b1110: LED7S<=7'b1111001;4'b1111: LED7S<=7'b1110001;default: LED7S<=7'b0111111;endcaseendmodule四、输完代码后编译:查错改错,通过后可进行一次全编译,之后进行管脚分配五、管脚分配:查电路原理图分配脚:放大全编译,出现错误Error: Can't place multiple pins assigned to pin location Pin_101(IOPAD_X34_Y18_N21)Info: Pin LED[5] is assigned to pin location Pin_101(IOPAD_X34_Y18_N21)Info: Pin ~ALTERA_nCEO~ is assigned to pin location Pin_101(IOPAD_X34_Y18_N21)原因:101引脚是一个多功能管脚(multiple pin),可以当普通IO连LED[5]来用也可以做nCEO,nCEO是默认功能,这里要用它做普通IO连LED[5],需要设置一下。

altera signaltap核例化与使用

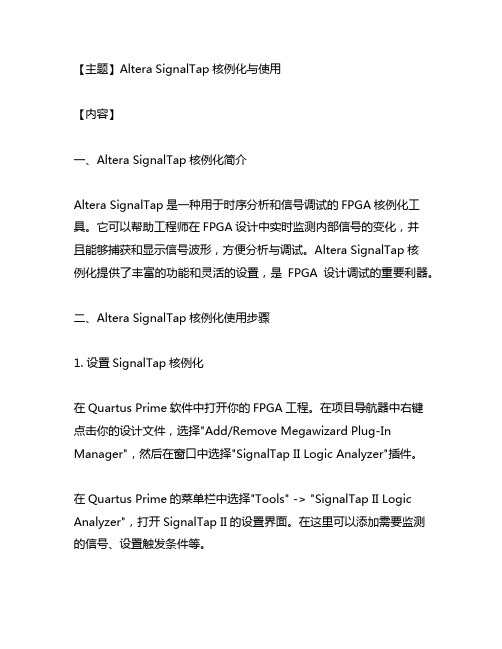

【主题】Altera SignalTap核例化与使用【内容】一、Altera SignalTap核例化简介Altera SignalTap是一种用于时序分析和信号调试的FPGA核例化工具。

它可以帮助工程师在FPGA设计中实时监测内部信号的变化,并且能够捕获和显示信号波形,方便分析与调试。

Altera SignalTap核例化提供了丰富的功能和灵活的设置,是FPGA设计调试的重要利器。

二、Altera SignalTap核例化使用步骤1. 设置SignalTap核例化在Quartus Prime软件中打开你的FPGA工程。

在项目导航器中右键点击你的设计文件,选择"Add/Remove Megawizard Plug-In Manager",然后在窗口中选择"SignalTap II Logic Analyzer"插件。

在Quartus Prime的菜单栏中选择"Tools" -> "SignalTap II Logic Analyzer",打开SignalTap II的设置界面。

在这里可以添加需要监测的信号、设置触发条件等。

2. 编译工程完成SignalTap核例化的设置后,需要重新编译你的FPGA工程,以便将SignalTap插入到FPGA中。

在Quartus Prime软件中选择"Processing" -> "Start Compilation",等待编译完成。

3. 下载到FPGA编译完成后,需要将设计下载到FPGA中。

在Quartus Prime软件中选择"Tools" -> "Programmer",选择你的FPGA芯片类型和连接方式,然后点击"Start"按钮下载到FPGA。

4. 运行SignalTap核例化下载完成后,在Quartus Prime软件中选择"Tools" -> "SignalTap II Logic Analyzer",打开SignalTap II的运行界面。

SignalTap II的简易使用方法

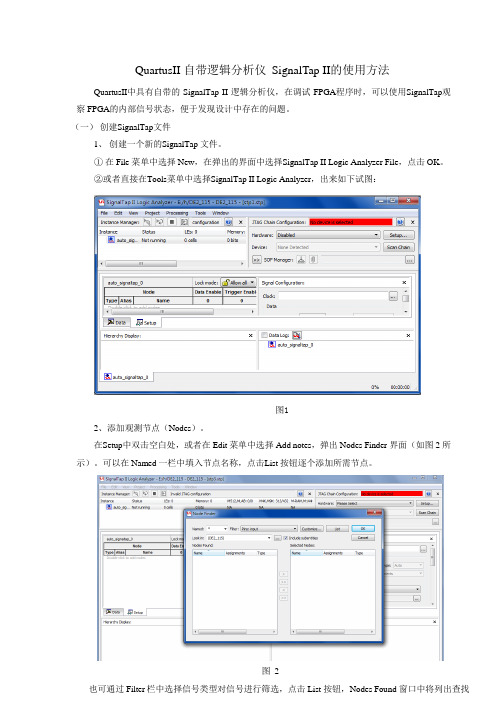

QuartusII 自带逻辑分析仪SignalTap II的使用方法QuartusII中具有自带的 SignalTap II 逻辑分析仪,在调试 FPGA程序时,可以使用SignalTap观察 FPGA的内部信号状态,便于发现设计中存在的问题。

(一)创建SignalTap文件1、创建一个新的SignalTap 文件。

①在 File 菜单中选择 New,在弹出的界面中选择SignalTap II Logic Analyzer File,点击 OK。

②或者直接在Tools菜单中选择SignalTap II Logic Analyzer,出来如下试图:图12、添加观测节点(Nodes)。

在Setup中双击空白处,或者在 Edit 菜单中选择 Add notes,弹出 Nodes Finder 界面(如图 2 所示)。

可以在 Named 一栏中填入节点名称,点击List 按钮逐个添加所需节点。

图2也可通过 Filter栏中选择信号类型对信号进行筛选,点击 List 按钮,Nodes Found 窗口中将列出查找到的信号(如图3所示),双击以选取所需的信号,完成后点击 OK。

图3观测节点添加完毕,如图4。

图44、为新建的 Instance 添加采样时钟。

在 Setup 界面中的 Signal 窗口中(如图 5 所示),点击Clock 旁边的Browse(…),同样弹出如图2 所示的Node Finder,选择恰当的信号后,点击OK。

图55、为新建的 Instance 设置采样深度、Ram 类型以及触发级数。

在 Setup 界面中的 Signal 窗口中,Data 一栏中的Sample 下来菜单中选择采样深度,在Ram 下来菜单中选择Ram 类型,并在Trigger 一栏中的下来框中选择触发级数,最多可以支持10 级触发。

选择的采样深度越大,触发级数越高,所占用的 LE 和 Memory 的资源就越多(在 Instance 一栏中可以看到目前每个 Instance所用的资源)。

signal_tap进行逻辑分析使用方法,实例演示

具体配置方法: 1.设置采样时钟//决定了显示信号波形的分辨率 2.设置被测信号//添加要观察的信号 3.配置采样深度 4.配置storage qualifier 5.设置trigger//包括循环采样存储、连续存储两种模式

SignalTapII简易使用方法

实例分析

对象:FFT设计 软件:Quartus ii 10.1 硬件平台:DE2-70

点击 选择.sof文件后点击open。再点 将嵌入了 逻辑分析仪的配置文件下载到目标器件中。

SignalTapII简易使用方法

下面就可以进行逻辑分析了。

1.之前我们一直在setup界面配置,分析数据需要转到 Data界面。(点击左下角的Data)

2.左上角的auto analysis ,可以发现status变成 waiting for trigger.

SignalTapII简易使用方法 2.设置被测信号

双击setup空白区进入note finder界面

在 Filter 列 表 中 选 择SignalTap Ⅱ : pre-synthesis

SignalTapII简易使用方法

3.配置采样深度

决定了被测信号波形显示的时间长度

注意:如果参数设置太大,硬件资源可能不够

以上资料来源: /Services/peixun/Altera/200912/2185.html

SignalTapII——基本使用和高级技巧

SignalTapII——基本使⽤和⾼级技巧 本⽂以4个led灯闪烁,来介绍 SignalTap II 的使⽤。

⼀、Verilog案例 led灯以1秒的时间循环左移,代码如下:1module led2//========================< 参数 >==========================================3 #(4parameter TIME = 26'd5000_0000 //1s5 )6//========================< 端⼝ >==========================================7 (8input wire clk , //时钟,50Mhz9input wire rst_n , //复位,低电平有效10output reg [ 3:0] led //4位led灯11 );12//========================< 信号 >==========================================13reg [25:0] cnt ;14wire add_cnt /*synthesis keep*/ ;15wire end_cnt /*synthesis keep*/ ;1617//==========================================================================18//== 0.2秒计数19//==========================================================================20always @(posedge clk or negedge rst_n) begin21if(!rst_n)22 cnt <= 'd0;23else if(add_cnt)begin24if(end_cnt)25 cnt <= 'd0;26else27 cnt <= cnt + 1'b1;28end29end3031assign add_cnt = 1'b1;32assign end_cnt = add_cnt && cnt== TIME-1'b1;3334//==========================================================================35//== led灯循环左移36//==========================================================================37always @(posedge clk or negedge rst_n) begin38if(!rst_n) begin39 led <= 4'b1110;40end41else if(end_cnt) begin42 led[3:0] <= {led[2:0],led[3]}; //右移:{led[0],led[3:1]};43end44end454647endmodule⼆、SignalTap II 的使⽤1、选择 File > New 打开 SignalTap II 窗⼝,选择 SignalTapII Logic Analyzer File 并单击OK。

SignalTap Logic Analyzer使用说明

下方的窗口中,然后按 OK 按钮关闭对话框。此时,Signal Configuration 窗口中的 Clock 项中显示的就是系统的主时钟(图 4)。 5) 在 Signal Configuration 窗口中,Sample depth 是采样深度。也就是 Signal Tap Logic Analyzer 在执行一次采集过程中的采样次数。这个一般可以设置成 1K,就是每次 对每个信号采集 1000 个点。因为 Signal Tap Logic Analyzer 是一种嵌入式的逻辑 分析仪,所以它会占用一定量的 FPGA 的资源。采样深度的大小与 FPGA 资源的使 用量是成正比的,所以这个值并不是越大越好。

Signal Tap Logic Analyzer 使用说明

Signal Tap Logic Analyzer 是 Altera 提供的一个实时的嵌入式逻辑分析工具,通过它可 以观察到 FPGA 中信号时域的逻辑变化情况,其功能与逻辑分析仪相似。Signal Tap Logic Analyzer 并非逻辑仿真,而是在 FPGA 的实际运行过程中,把其中指定信号的逻辑值按时间 顺序进行采集,因而使用 Signal Tap Logic Analyzer 必须有 FPGA 实物,而且需要有真实的 输入信号。图 1 为 Signal Tap Logic Analyzer 的用户界面。常用的三个窗口是实体管理窗口, JTAG 配置窗口和信号显示窗口。

5. 采集信号 点击快捷按钮栏中的“单次采集”(见图 9),Signal Tap Logic Analyzer 会进行一次

Signaltap II的使用介绍

Signaltap II的使用介绍SignalTap II 逻辑分析器是Quartus II 软件中集成的一个内部逻辑分析软件(相当于一个内置示波器),使用它可以观察设计的内部信号变化,为我们FPGA设计的调试、查错带来极大的方便,实用性极高!!下面以Hello_Led工程为例,具体介绍SignalTap II的使用:1、打开工程用quartus打开Hello_Led工程(双击hello_led.qpf),2、新建.stp文件(或打开已有的.stp文件)点【File】→【New】,或工具栏上的快捷键,弹出新建类型对话框,选择“SingalTap Logic Analyzer File”,点【OK】,3、设置采样时钟点击Clock处的浏览按钮,添加采样时钟,(所有的信号都是通过这个时钟采样得来,所以这个作为采样时钟的信号频率要比待测信号频率高才行,不然采不到或失真!)4、设置采样深度在“Sample depth”处选择采样深度,即信号能看多长,该值受FPGA芯片内置存储器大小的限制,设的过长,编译会通不过。

5、设置触发条件触发条件即只有当触发信号(source处选择的信号)发生变化时(pattern处选择的变化:高电平、低电平、上升沿、下降沿、上/下变化沿),singaltap会捕获/暂停一次,在“Trigger in”前打上勾,点击浏览按钮,在节点选择对话框中选择合适的信号作为触发信号,选择触发条件,即触发信号发生何种变化时,待测信号数据会更新一次,上图表示有沿产生就捕获一次数据,6、选择待测信号在图中空白处双击,弹出节点选择窗口,我们来选择待测信号,如果要添加中间信号,在“filter”处需选择“Design Entry(all names)”,按住ctrl可选多个信号,7、保存.stp文件保存后,会弹出对话框,询问是否激活.stp文件,选择是8、重新编译工程新建一个.stp文件或在.stp增删待测信号,需要重新编译工程9、加载程序点击“Hardware”处的【setup】,选择“USB-Blaster”,双击选中即可点击sof浏览按钮,选择“hello_led.sof”如果加载按钮呈灰化,点下【scan chain】刷新一下应该就好了点击加载按钮,加载成功后,led灯会闪烁。

QuartusII中 SignalTapⅡ逻辑分析仪的使用

第10章SignalTapⅡ嵌入式逻辑分析仪的使用10.1 在设计中嵌入SignalTapⅡ逻辑分析仪10.2 在SOPC Builder中使用SignalTapⅡ逻辑分析仪10.3 在DSP Builder中使用SignalTapⅡ逻辑分析仪思考题10.1 在设计中嵌入SignalTapⅡ逻辑分析仪在设计中嵌入SignalTapⅡ逻辑分析仪有两种方法:第一种方法是建立一个SignalTapⅡ文件(.stp),然后定义STP文件的详细内容;第二种方法是用MegaWizard Plug-In Manager建立并配置STP文件,然后用MegaWizard实例化一个HDL输出模块。

图10.1给出用这两种方法建立和使用SignalTapⅡ逻辑分析仪的过程。

SignalTapMegaWizardQuartusSTPQuartus,/ 图10.1 SignalTapⅡ操作流程10.1.1 使用STP文件建立嵌入式逻辑分析仪1.创建STP文件STP文件包括SignalTapⅡ逻辑分析仪设置部分和捕获数据的查看、分析部分。

创建一个STP文件的步骤如下:(1) 在QuartusⅡ软件中,选择File→New命令。

(2) 在弹出的New对话框中,选择Other Files标签页,从中选择SignalTapⅡ File,如图10.2所示。

图10.2 新建一个STP文件(3) 点击OK按钮确定,一个新的SignalTapⅡ窗口如图10.3所示。

DataS etup图10.3 SignalTapⅡ窗口上面的操作也可以通过Tools→SignalTapⅡLogic Analyzer命令完成,这种方法也可以用来打开一个已经存在的STP文件。

2.设置采集时钟在使用SignalTapⅡ逻辑分析仪进行数据采集之前,首先应该设置采集时钟。

采集时钟在上升沿处采集数据。

设计者可以使用设计中的任意信号作为采集时钟,但Altera建议最好使用全局时钟,而不要使用门控时钟。

lab13用Quartus II建立工程,调用 SignalTap II,形成波形

Lab 131.实验目的用Quartus II建立工程,调用 SignalTap II,形成波形!2.实验内容学习SignalTap II 的使用,了解工程内部信息,生成一个信号逻辑,并传输到屏幕显示。

3.代码分析dds原理代码与实验12一样:module DDS#( parameter PHASE_W = 24,parameter DATA_W = 16,parameter TABLE_AW = 12,parameter MEM_FILE = "SineTable.dat")( input [PHASE_W - 1 : 0] FreqWord,input [PHASE_W - 1 : 0] PhaseShift,input Clock,input ClkEn,output signed [DATA_W - 1 : 0] Out);reg signed [DATA_W - 1 : 0] sinTable[2 ** TABLE_AW - 1 : 0]; // SinetableROMreg [PHASE_W - 1 : 0] phase; // Phase Accumulaterwire [PHASE_W - 1 : 0] addr = phase + PhaseShift; // Phase Shiftassign Out = sinTable[addr[PHASE_W - 1 : PHASE_W - TABLE_AW]]; // Look up the tableinitial beginphase = 0;$readmemh(MEM_FILE, sinTable); // Initialize the ROMendalways@(posedge Clock) beginif(ClkEn)phase <= phase + FreqWord;endendmoduledds_test代码序列:module dds_test (input CLOCK_50,output [15:0] GPIO0_D);dds the_dds_inst (.FreqWord(24'h10000),.PhaseShift(24'h0),.Clock(CLOCK_50),.ClkEn(1'b1),.Out(GPIO0_D));Endmodule4.实验步骤打开quartus II,打开上一次实验所用到的工程。

signaltap 条件

SignalTap是Intel FPGA(现场可编程门阵列)设备上的一种实时逻辑分析工具。

它允许用户捕获和观察FPGA内部的信号状态,以便进行调试和分析。

在使用SignalTap时,用户可以设置触发条件来控制何时开始捕获数据。

这些触发条件可以是基于特定信号的值或事件。

SignalTap的条件设置通常涉及以下几个步骤:

选择信号:首先,用户需要从FPGA设计中选择想要观察的信号。

这些信号可以是任何内部信号,例如寄存器、输入/输出端口等。

设置触发条件:接下来,用户需要定义一个或多个触发条件。

触发条件可以是基于信号值的简单比较(例如,等于、不等于、大于、小于等),也可以是更复杂的逻辑表达式。

当满足触发条件时,SignalTap将开始捕获数据。

配置捕获参数:用户还可以配置其他捕获参数,例如捕获深度(即要捕获的数据量)和捕获模式(例如,单次捕获或连续捕获)。

启动捕获:配置完成后,用户可以启动SignalTap来开始捕获数据。

当满足触发条件时,SignalTap将记录相关信号的状态。

分析和调试:最后,用户可以使用SignalTap的界面来分析捕获的数据,以便进行调试和设计验证。

总的来说,SignalTap的条件设置是一个灵活而强大的功能,可以帮助FPGA设计人员更有效地进行调试和分析。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

SignalTap的使用方法

SignalTap是由Altera公司开发的一个在线、片内信号分析的工具,为设计开发者验证所用。

我们什么时候会用到signalTap呢?当代码经过仿真没有问题,但加载到FPGA电路板后,发现功能不正确时,我们就可以用signalTap工具进行分析,它的作用就类似于一个数字逻辑分析仪。

利用signaltap基本上可以代替数字逻辑分析仪了,它是quartus里最常用的工具,同学们必须熟练使用这个工具。

1.SignalTapII原理

在使用signalTap前,我们先理解一下SignalTap的原理,这样就助于理解每个参数。

如下图所示,我们想观察一组信号,我们称之为“被测信号”(可以是多个),同时我们指定一个采样时钟。

现在我们想看这个被测信号,在其下降沿前后几个时钟内,被测信号的值是多少。

那么“下降沿”就是触发条件。

当满足触发条件时,signaltap会将触发条件前后,时钟上升沿时的所有信号值保存到一个RAM当中。

我们可以指定触发条件前后采多少个样点。

如果RAM比较大,那么可以保存的数据就比较多。

如果RAM比较小,那么保存的数据自然少。

(因此RAM大小决定了观察数据的多少)。

SignalTap将数据保存到RAM后,将读出RAM中的数据,然后逐个在显示器中显示出来(因此SignalTap看到的都是理想的,没有毛刺的信号)。

2.打开SignalTapII

打开Quartus后,在菜单栏中,选择“Tools”->”SignalTal II Logic Analyzer”,就可以打开

SignalTap工具。

如下图:

3.界面介绍

上面是SignalTap的界面,我们按照使用顺序简述地介绍每个部分功能。

红色标号1:下载线选择,点击setup选择硬件的USB接口

红色标号2:硬件检测,扫描有没有FPGA硬件。

红色标号3:选择工程配置文件。

可以将综合后的sof文件加载进来

红色标号4:正式加载sof工程文件

红色标号5:设置采样时钟

红色标号6:设置RAM的大小

红色标号7:选择要观察的信号,并且设置触发条件

红色标号8:开始运行,等待触发条件满足后显示波形

红色标号9:这里可以观察FPGA资源使用情况。

如果资源多于FPGA本身的资源,综合时会报错。

4.SignalTapII使用步骤

a选择下载线、fpga芯片型号、工程配置文件

b设置采样时钟、采样深度

这里我们选择内部pll的输出信号c1作为采样时钟,注意采样时钟不一定是工程里的时钟,内部任何信号都可以是采样时钟。

这里我们将采样深度设置为128个。

也就是我们总共能看到128采样点的数据。

c选择采样信号

在setup窗口中,双击空白地方,弹出如下界面

红色框是选择哪个阶段的信号,例如是综合前、综合后等,因为综合时会优化,有些信号可能就找不到了。

我们一般选择pre-synthesis或Design Entry(all name)。

在Nodes Found选择我们要观察的信号,添加到右边框即可。

我们这里选择key_col和rst_n信号来观察。

d设置触发条件

选择好信号后,设置触发条件。

同学们可以观察到trigger Conditions一列,key_col的值为xh,rst_n的值为don’t care。

这意味着只要一观察,立刻捕获信号。

在trigger Conditions一列中,右击rst_n那个位置,将有6个选择。

don’t care:表示不关心,也就是说这个信号的值不影响触发条件。

Low :表示为0时触发,也就是说触发条件包括该信号的值为0.

Falling Edge:下降沿触发。

即该信号的下降沿是触发条件

Rising Edge:上升沿触发。

High:给为1时触发

Either Edge:双沿触发,即有变化时触发。

以上是对一个信号的触发。

如果触发条件包含多个信号,如下图所示:

此时的触发条件是:当rst_n为上升沿并且key_col为F。

注意,这里是“与”的关系,很多同学会误认为是“或”的关系。

e点击“Run Analysis”按钮,开始抓波形

f观看结果

如果触发条件成立,则可在Data窗口观察到采样波形,此处是某一工程的采样结果,可以看到,其与modelsim波形是很相似的。

点击波形,则可以放大波形观看;右击波形,则是缩小波形。

SignalTap工具的使用方法就介绍到这里,接下来明德扬的点拨FPGA课程提供了几个SignalTap的练习,同学们通过练习熟悉掌握SignalTap。