AM335x GPMC模块地址区域划分详解

03 AM335x处理器

• EMIF0 SDRAM

– 0x8000_0000 0xBFFF_FFFF, 1GB 8-/16-bit External Memory, (ex/e/w)

北京交通大学

国家电工电子教学基地

Main processor

ARM Cortex-A8 MPU子系统

• MPU 子系统处理 ARM A8核心 , L3 互联和中断控制 器 (INTC)之间的 数据交换. • MPU把A8处理器 和其他附加逻辑 集成在一起,实 现协议转换、仿 真、中断处理和 调试增强功能。

L3 Slow clock domain

目标模块 : 只能响应 r/w请求

To L4 interconnect

北京交通大学国家电工电子教学基地 Main processor

L4 互联结构*

北京交通大学

国家电工电子教学基地

Main processor

片上模块 (驱动开发相关)

• cache : 高速缓存 • mDDR: 移动双倍速率同步动态随机存储器 • PRU-ICSS: 可编程实时单元和工业用通信子系统

• AXI2OCP桥

– 支持OCP 2.2.

– 在两个端口实现单次请求多个数据协议。 – 多个目标,包括三个 OCP ports (128-bit, 64-bit and 32-bit).

• 中断控制器

– 最多支持128个中断请求

• 仿真/调试

– 与CoreSight结构兼容

• 时钟产生

– 通过PRCM(电源、复位、时钟微控制器)

北京交通大学

国家电工电子教学基地

Main processor

存储器子系统: GPMC

• GPMC 为器件提供访问NAND Flash, NOR Flash和其他异步/同步接 口外设 的手段.

AM335x 处理器 SDK RTOS 板库端口和启动说明书

Board Porting\Bring up using Processor SDK RTOS for AM335xProcessor SDK RTOS component known as board library consolidates all the board-specific information so that all the modifications made when moving to a new custom platform using the SOC can be made in the source of this library.There are three different components in PRSDK that help in porting and bring up of a custom board:∙Board library updatesa.PLL Clocking and PRCMb.Pin mux Updatec.DDR Configurationd.Peripheral instances updates∙Diagnostics tests∙Boot loader updatesBoard Library Updates in Processor SDK RTOS:PLL ClockingThere are two places where the device PLL configurations are performed when using Processor SDK RTOS and CCS.Debug environment:Debug environment refers to development setup where code is debugged using JTAG emulator on the SOC. The PRSDK software relies on the GEL file that is part of the target configuration to setup the clocks and the DDR for the device. The CCS GEL file for AM335x platforms is located in the CCS package at the location ccsv7\ccs_base\emulation\boards\<boardName>For example for beagle bone black, the files can be found atccsv7\ccs_base\emulation\boards\beaglebone\gelThe GEL is the first piece of software that should be brought up on a custom board.Production environment:Production environment refers to the setup when the base application is booted from a boot media like a flash memory or host interface. In this environment, the bootloader sets performs all the SOC and board initialization and copies the application from flash memory to the device memory.The clock setup in the bootloader code can be located atpdk_am335x_x_x_x\packages\ti\starterware\bootloader\src\am335xUsers can choose to use the platform clocking similar to one of TI reference platforms or can modify them as per their application requirements. By default the PLL settings are setup for OPP_NOM settings (MPU= 600 MHz.)TI provides Clock Tree tool to allow users to simulate the clocking on the SOC. For quick reference of the multiplier and divider settings to change the PLL setting is provided in the spreadsheetAM335x_DPLL_CALCv3.xlsx.After modifying the clocking in the bootloader, users need to rebuild the bootloader using instructions provided in Processor_SDK_RTOS_BOOT_AM335x/AM437xPRCM Modules Enable:PRCM Module Enable is required to turn on the power domain and the clocking to each of the modules on the SOC. The PRCM Enable calls to enable each module are made from the functionBoard_moduleClockInit which is found in the location.pdk_am335x_1_0_9\packages\ti\board\src\bbbAM335x\bbbAM335x.cCheck every instance and peripheral required in the application platform and enable the module in the board library.For example to use three UARTs 0, 1 and 4, ensure that you have the following code as part of the board library setup:/* UART */status = PRCMModuleEnable(CHIPDB_MOD_ID_UART, 0U, 0U);status = PRCMModuleEnable(CHIPDB_MOD_ID_UART, 1U, 0U);status = PRCMModuleEnable(CHIPDB_MOD_ID_UART, 4U, 0U);Note: PRCMEnable function is defined in pdk_am335x_1_0_9\packages\ti\starterware\soc\am335x Pinmux updates in the Board library:Generating a New PinMux Configuration Using the PinMux Utility: This procedure uses the cloud-based pinmux utilityNavigate to ${PDK_INSTALL_DIR}\packages\ti\starterware\tools\pinmux_config\am335x and Load beaglebone_black_configAdd and remove peripheral instances and select the appropriate use cases required for development based on the application platform requirements and resolve all conflicts.Refer Pin_Mux_Utility_for_ARM_MPU_ProcessorsPost Processing steps:1.Change the Category filter to starterware and download the pinmux files am335x_pimnmux.hand am335x_pinmux_data.c2.At the bottom of am335x_pinmux.h change extern pinmuxBoardCfg_t gAM335xPinmuxData[];to extern pinmuxBoardCfg_t gBbbPinmuxData[];3.Change am335x_pinmux_data.c to am335x_beagleboneblack_pinmux_data.c.4.Change gAM335xPinmuxData to gBbbPinmuxData at the end of the file in file5.am335x_beagleboneblack_pinmux_data.c.Replace the existing files with the new files and rebuild the board library using the instructions in the section Rebuilding board Library in Processor SDK RTOS:Updating DDR settings:Similar to clock and PLL settings, DDR initialization is configured in the Debug environment through GEL files and in production environment using bootloader source files.TI provides AM335x_EMIF_Configuration_tips which contains a spreadsheet to enter the timing from the DDR datasheet to compute the EMIF timing number required to initialize DDR.We strongly recommend changing the value and testing using GEL files before using them in the bootloader software. For Sanity test, you can perform read/write tests using CCS Memory Browser or run the diagnostic memory read/write test that we provide in diagnostics package here:PDK_INSTALL_PATH\packages\ti\board\diag\memOnce the DDR timings have been confirmed, you can use the settings in the file:PDK_INSTALL_PATH \packages\ti\starterware\bootloader\src\am335x\sbl_am335x_platform_ddr.c Peripheral initialization:The board library is responsible for most of the SOC initialization but it also setup some board level components such as ethernet PHY and debug UART and I2C for reading board ID from EEPROM. All of the other peripheral instances and initialization needs to be done from the application level.For example for beagleboneblack, the peripheral initialization are performed from the source filepdk_am335x_1_0_9\packages\ti\board\src\bbbAM335x\bbbAM335x_lld_init.cThe debug UART instance, I2C Addresses are set using the file board_cfg.h found under:pdk_am335x_1_0_9\packages\ti\board\src\bbbAM335x\includeDefault UART instance is set to 0 in the board library. The Board initialization will configure the UART instance 0 to send binary log data to serial console using the Board_UARTInit function. If you wish to use more UART instances then we recommend linking in the UART driver in the application and using UART_open() and UART_stdioInit API calls from the application.Each peripheral driver in the Processor SDK RTOS has a SOC configuration that provides the interrupt numbers, base address, EDMA channels which can be updated using the file <peripheral>_soc.c file. This is used as default setup for initializing the driver instance. It can be overridden from the application using peripheral_getSOCInitCfg() and peripheral_setSOCInitCfg()For Example: All instances of UART for AM335x have been mapped in the filepdk_am335x_1_0_9\packages\ti\drv\uart\soc\am335x\UART_soc.cSystem integrators need to ensure that no interrupt numbers and EDMA resource conflicts exist in the SOC configuration for all drivers used in the system.To exercise three UARTs in the system, users can use the following code://Setup Debug UARTboardCfg = BOARD_INIT_PINMUX_CONFIG |BOARD_INIT_MODULE_CLOCK |BOARD_INIT_UART_STDIO;Board_init(boardCfg);// Open Additional UART Instances:/* UART SoC init configuration */UART_initConfig(false);/* Initialize the default configuration params. */UART_Params_init(&uartParams);// Open UART Instance 1uartTestInstance =1;uart1 = UART_open(uartTestInstance, &uartParams);//Open UART Instance 4uartTestInstance = 4;uart4 = UART_open(uartTestInstance, &uartParams);BoardID Detect:TI supports multiple evaluation and reference platforms for AM335x hence the hardware platforms are populated with an EEPROM which contains information that identifies the hardware and its revision. The board library and software components read the boardID and initialize the platform based on the boardID. The BoardID_detect function can be found in the source in the file bbbAM335x_info.c in the board library and board_am335x.c in the bootloader source at:<PDK_INSTALL_PATH>\packages\ti\starterware\board\am335xRebuilding board Library in Processor SDK RTOS:While Creating a new folder for the custom board is an option users can explore, TI recommends that users make there changes in existing board package using either bbbAM335x, evmAM335x oriceAM335x folder to avoid spending additional effort to modify the build files for including the customBord.Once all the update to the board library are completed, the board library can be updated using the following instructions.Instructions to rebuild board library:Setup Processor SDK build environment before following steps provided below.cd pdk_am335x_1_0_9\packagesgmake board_libFor a specific board users are required to provide the LIMIT_BOARDS argument.LIMIT_BOARDS : evmAM335x icev2AM335x iceAMIC110 bbbAM335x skAM335xFor Example for beagleboneblack, users can use the following build option:gmake board_lib LIMIT_BOARDS=bbbAM335xDiagnostics:After the board library is built, we highly recommend that you create a diagnostics package similar to one provided in board library to test different interfaces functionally during board bring up.The diagnostics package can be located at pdk_am335x_1_0_9\packages\ti\board\diag. These are simple bare-metal tests that use peripheral drivers to help functionally validate the pins and interfaces.Documentation for all available diagnostic tests is provided here:/index.php/Processor_SDK_RTOS_DIAGBootloader in Processor SDK RTOS:As part of the production flow, users are required to develop/port flashing and booting utilities so the application can be launched on the custom board with JTAG. TI provides a bootloader mechanism where the ROM bootloader loads a secondary bootloader on the onchip memory that initializes the SOC and DDR and then copies the application into DDR memory.The boot process and flashing tools have been described in detail in the following article that is part of processor SDK RTOS Software developer`s guide:/index.php/Processor_SDK_RTOS_BOOT_AM335x/AM437x#Building_the_B ootloader。

盈鹏飞嵌入式_AM335XGPMC使用总结

盈鹏飞嵌入式_AM335XGPMC使用总结AM335X GPMC使用比较灵活,可以配置为● 8-bit 同步或者异步并行总线 (非burst)● 16-bit 同步或者异步并行中线● 16-bit 非复用的NOR Flash● 16-bit 数据和地址总线复用的NOR Flash● 8-bit 和 16-bit NAND Flash● 16-bit pSRAM.下面以EVB335X扩展EXAR ST16C554为例,讲解如何配置GPMC。

1. 配置GPMC引脚static struct pinmux_config gpmc_pin_mux[] = {/********* 8-bit data bus **************/{"gpmc_ad0.gpmc_ad0", OMAP_MUX_MODE0 | AM33XX_PIN_INPUT_PULLUP},{"gpmc_ad1.gpmc_ad1", OMAP_MUX_MODE0 | AM33XX_PIN_INPUT_PULLUP},{"gpmc_ad2.gpmc_ad2", OMAP_MUX_MODE0 | AM33XX_PIN_INPUT_PULLUP},{"gpmc_ad3.gpmc_ad3", OMAP_MUX_MODE0 | AM33XX_PIN_INPUT_PULLUP},{"gpmc_ad4.gpmc_ad4", OMAP_MUX_MODE0 | AM33XX_PIN_INPUT_PULLUP},{"gpmc_ad5.gpmc_ad5", OMAP_MUX_MODE0 | AM33XX_PIN_INPUT_PULLUP},{"gpmc_ad6.gpmc_ad6", OMAP_MUX_MODE0 | AM33XX_PIN_INPUT_PULLUP},{"gpmc_ad7.gpmc_ad7", OMAP_MUX_MODE0 |AM33XX_PIN_INPUT_PULLUP},/**************** 8-bit address bus ****************/{"gpmc_a0.gpmc_a0", OMAP_MUX_MODE0 | AM33XX_PIN_OUTPUT},{"gpmc_a1.gpmc_a1", OMAP_MUX_MODE0 | AM33XX_PIN_OUTPUT},{"gpmc_a2.gpmc_a2", OMAP_MUX_MODE0 | AM33XX_PIN_OUTPUT},{"gpmc_a3.gpmc_a3", OMAP_MUX_MODE0 | AM33XX_PIN_OUTPUT},{"gpmc_a4.gpmc_a4", OMAP_MUX_MODE0 | AM33XX_PIN_OUTPUT},{"gpmc_a5.gpmc_a5", OMAP_MUX_MODE0 | AM33XX_PIN_OUTPUT},{"gpmc_a6.gpmc_a6", OMAP_MUX_MODE0 | AM33XX_PIN_OUTPUT},{"gpmc_a7.gpmc_a7", OMAP_MUX_MODE0 | AM33XX_PIN_OUTPUT},{"gpmc_csn2.gpmc_csn2", OMAP_MUX_MODE0 | AM33XX_PULL_DISA},{"gpmc_oen_ren.gpmc_oen_ren", OMAP_MUX_MODE0 | AM33XX_PULL_DISA},{"gpmc_wen.gpmc_wen", OMAP_MUX_MODE0 | AM33XX_PULL_DISA},{NULL, 0},};setup_pin_mux(gpmc_pin_mux);2. 申请GPMC内存unsigned long serial_gpmc_mem_base_phys;int cs = 2; /* EVB335X评估板中ST16C554接在CS2上 */gpmc_cs_request(cs, SZ_16M, &serial_gpmc_mem_base_phys)此时serial_gpmc_mem_base_phys存放的是该CS上多对应的物理起始地址。

AM335XGPIO详解

AM335XGPIO详解1、配置GPIO1的时钟CM_PER RegistersCM_PER_GPIO1_CLKCTRL该寄存器管理GPIO1时钟。

OPTFCLKEN_GPIO_1_GDBCLK 可选功能时钟控制0X0 = FCLK_DIS :可选功能的时钟被禁止0x1 = FCLK_EN :可选功能时钟使能IDLEST 模块为空闲状态0X0 =函数功能:模块功能齐全,包括OCP0x1 =反:模块进行转换:唤醒或休眠,或睡眠流产0X2 =空闲:模块处于空闲模式(仅OCP部分)。

它是功能,如果使用独立的时钟功能0x3的=禁止:禁止模块,不能访问CM_PER_L4LS_CLKSTCTRL该寄存器使能域功率状态转换。

它控制着SW监督时钟域状态ON- PER和ON- INPER状态之间的转换。

它也认为每个时钟输入1个状态位域。

CLKACTIVITY_GPIO_1_GDBCLK 该字段表示在该GPIO1_GDBCLK时钟的状态域。

0X0 = INACT :对应的时钟门控0x1 =ACT:通讯时钟有效2、配置GPIO端口功能CONTROL_MODULE Registersconf_gpmc_a0-a11 设置内部上拉和管脚传输速率:快或慢3、重启GPIO模块GPIO_SYSCONFIG 寄存器1 SOFTRESET R/W Software reset.This bit is automatically reset by the hardware. During reads, it always returns 0.0x0 = Normal mode0x1 = The module is rese软件复位。

该位由硬件自动复位。

在读取时,它总是返回0 。

0X0 =普通模式为0x1 =该模块复位4、设置GPIO方向GPIO_OE[0-31] 寄存器输出数据使能0X0 =相应的GPIO端口被配置为输出。

0x1 =相应的GPIO端口配置为输入。

TIAM335x系列处理器6LoWPAN网络参考设计TIDA010032

TI公司的AM335x系列微处理器是基于ARM Cortex-A8处理器,工作频率高达1GHz,具有增强图像,图形处理,外设和工业接口选择如EtherCAT和PROFIBUS,支持高级操作系统(HLOS).器件还具有NEON™ SIMD协处理器,32KB L1指令和32KB数据缓存,256KB L2高速缓存,176KB引导ROM和64KB专用RAM,主要用在数据集中器和无线通信.本文介绍了AM335x处理器主要特性,功能框图以及支持以太网,6LoWPAN RF网络和更多的通用数据集中器参考设计TIDA-010032主要指标,网络指标,框图,系统架构图,电路图,材料清单和PCB设计图.The AM335x microprocessors, based on the ARM Cortex-A8 processor, are enhanced with image,graphics processing, peripherals and industrialinterface options such as EtherCAT and PROFIBUS. Thedevices supporthigh-level operating systems (HLOS). Processor SDK Linux® and TI-RTOS are availablefree of charge from TI.The AM335x microprocessor contains the subsystems shown in theFunctional Block Diagram and a briefdescription of each follows: The contains the subsystems shown in the Functional Block Diagramand a brief description of eachfollows:The microprocessor unit (MPU) subsystem is based on the ARM Cortex-A8 processor and the PowerVRSGX™ Graphics Accelerator subsystemprovides 3D graphics acceleration to support display and gamingeffects.The PRU-ICSS is separate from the ARM core, allowing independentoperation and clocking for greaterefficiency and flexibility.The PRU-ICSS enables additional peripheral interfaces and real-time protocolssuch as EtherCAT, PROFINET, EtherNet/IP, PROFIBUS, Ethernet Powerlink, Sercos, and others.Additionally, the programmable nature of the PRU-ICSS, along with its access to pins, events and allsystem-on-chip (SoC) resources, providesflexibility in implementing fast, real-time responses, specializeddatahandling operations, custom peripheral interfaces, and in offloading tasks from the other processorcores of SoC.AM335x处理器主要特性:• Up to 1-GHz Sitara™ ARM® Cortex®-A8 32 BitRISC Processor– NEON™ SIMD Coprocessor– 32KB of L1 Instruction and 32KB of Data CacheWith Single-ErrorDetection (Parity)– 256KB of L2 Cache With Error Correcting Code(ECC)– 176KB of On-Chip Boot ROM– 64KB of Dedicated RAM– Emulation and Debug - JTAG– Interrupt Controller (up to 128 InterruptRequests)• On-Chip Memory (Shared L3 RAM)– 64KB of General-Purpose On-Chip MemoryController (OCMC) RAMTI AM335x系列处理器6LoWPAN网络参考设计TIDA-010032– Accessible to All Masters– Supports Retention for Fast Wakeup• External Memory Interfaces (EMIF)– mDDR(LPDDR), DDR2, DDR3, DDR3LController:– mDDR: 200-MHz Clock (400-MHz Data Rate)– DDR2: 266-MHz Clock (532-MHz Data Rate)– DDR3: 400-MHz Clock (800-MHz Data Rate)– DDR3L: 400-MHz Clock (800-MHz DataRate)– 16-Bit Data Bus– 1GB of Total Addressable Space– Supports One x16 or Two x8 Memory DeviceConfigurations– General-Purpose Memory Controller (GPMC)– Flexible 8-Bit and 16-Bit AsynchronousMemory Interface With up toSeven Chip Selects (NAND, NOR, Muxed-NOR, SRAM)– Uses BCH Code to Support 4-, 8-, or 16-BitECC– Uses Hamming Code to Support 1-Bit ECC– Error Locator Module (ELM)– Used in Conjunction With the GPMC toLocate Addresses of Data Errors fromSyndrome Polynomials Generated Using aBCH Algorithm– Supports 4-, 8-, and 16-Bit per 512-ByteBlock Error Location Based on BCHAlgorithms • Programmable Real-Time Unit Subsystem andIndustrial Communication Subsystem (PRU-ICSS)– Supports Protocols such as EtherCAT®,PROFIBUS, PROFINET,EtherNet/IP™, and More– Two Programmable Real-Time Units (PRUs)– 32-Bit Load/Store RISC Processor Capableof Running at 200 MHz– 8KB of Instruction RAM With Single-ErrorDetection (Parity)– 8KB of Data RAM With Single-Error Detection(Parity)– Single-Cycle 32-Bit Multiplier With 64-BitAccumulator– Enhanced GPIO Module Provides Shift-In/Out Support and Parallel Latch on External Signal– 12KB of Shared RAM With Single-ErrorDetection (Parity)– Three 120-Byte Register Banks Accessible byEach PRU– Interrupt Controller (INTC) for Handling SystemInput Events– Local Interconnect Bus for Connecting Internaland External Masters to the Resources Insidethe PRU-ICSS– Peripherals Inside the PRU-ICSS:– One UART Port With Flow Control Pins,Supports up to 12 Mbps– One Enhanced Capture (eCAP) Module– Two MII Ethernet Ports that Support IndustrialEthernet, such as EtherCAT – One MDIO Port• Power, Reset, and Clock Management (PRCM)Module– Controls the Entry and Exit of Stand-By andDeep-Sleep Modes– Responsible for Sleep Sequencing, PowerDomain Switch-Off Sequencing, Wake-Up Sequencing, and Power Domain Switch-OnSequencing– Clocks– Integrated 15- to 35-MHz High-frequencyOscillator Used to Generate a Reference Clock for Various System and PeripheralClocks– Supports Individual Clock Enable and DisableControl for Subsystems and Peripherals toFacilitate Reduced Power Consumption– Five ADPLLs to Generate System Clocks(MPU Subsystem, DDR Interface, USB and Peripherals [MMC and SD, UART, SPI, I2C],L3, L4, Ethernet, GFX [SGX530], LCD Pixel Clock)– Power– Two Nonswitchable Power Domains (Real-Time Clock [RTC], Wake-UpLogic[WAKEUP])– Three Switchable Power Domains (MPUSubsystem [MPU], SGX530 [GFX], Peripherals and Infrastructure [PER])– Implements SmartReflex™ Class 2B for CoreVoltage Scaling Based On Die Temperature,Process Variation, and Performance(Adaptive Voltage Scaling [AVS])– Dynamic Voltage Frequency Scaling (DVFS)• Real-Time Clock (RTC)– Real-Time Date (Day-Month-Year-Day of Week)and Time (Hours-Minutes-Seconds) Information– Internal 32.768-kHz Oscillator, RTC Logic and1.1-V Internal LDO– Independent Power-on-Reset(RTC_PWRONRSTn) Input– Dedicated Input Pin (EXT_WAKEUP) forExternal Wake Events– Programmable Alarm Can be Used to GenerateInternal Interrupts to the PRCM (for Wakeup) orCortex-A8 (for Event Notification)– Programmable Alarm Can be Used WithExternal Output(PMIC_POWER_EN) to Enablethe Power Management IC to Restore Non-RTCPower Domains• Peripherals– Up to Two USB 2.0 High-Speed DRD (Dual-Role Device) Ports WithIntegrated PHY– Up to Two Industrial Gigabit Ethernet MACs (10,100, 1000 Mbps)– Integrated Switch– Each MAC Supports MII, RMII, RGMII, andMDIO Interfaces– Ethernet MACs and Switch Can OperateIndependent of Other Functions – IEEE 1588v2 Precision Time Protocol (PTP)– Up to Two Controller-Area Network (CAN) Ports– Supports CAN Version 2 Parts A and B– Up to Two Multichannel Audio Serial Ports(McASPs)– Transmit and Receive Clocks up to 50 MHz– Up to Four Serial Data Pins per McASP PortWith Independent TX and RX Clocks– Supports Time Division Multiplexing (TDM),Inter-IC Sound (I2S), andSimilar Formats– Supports Digital Audio Interface Transmission(SPDIF, IEC60958-1, and AES-3 Formats)– FIFO Buffers for Transmit and Receive (256Bytes)– Up to Six UARTs– All UARTs Support IrDA and CIR Modes– All UARTs Support RTS and CTS FlowControl– UART1 Supports Full Modem Control– Up to Two Master and Slave McSPI SerialInterfaces– Up to Two Chip Selects– Up to 48 MHz– Up to Three MMC, SD, SDIO Ports– 1-, 4- and 8-Bit MMC, SD, SDIO Modes– MMCSD0 has Dedicated Power Rail for 1.8 Vor 3.3-V Operation– Up to 48-MHz Data Transfer Rate– Supports Card Detect and Write Protect– Complies With MMC4.3, SD, SDIO 2.0Specifications– Up to Three I2C Master and Slave Interfaces– Standard Mode (up to 100 kHz)– Fast Mode (up to 400 kHz)– Up to Four Banks of General-Purpose I/O(GPIO) Pins– 32 GPIO Pins per Bank (Multiplexed WithOther Functional Pins)– GPIO Pins Can be Used as Interrupt Inputs(up to Two Interrupt Inputs per Bank)– Up to Three External DMA Event Inputs that canAlso be Used as Interrupt Inputs– Eight 32-Bit General-Purpose Timers– DMTIMER1 is a 1-ms Timer Used forOperating System (OS) Ticks– DMTIMER4–DMTIMER7 are Pinned Out– One Watchdog Timer– SGX530 3D Graphics Engine– Tile-Based Architecture Delivering up to 20Million Polygons per Second – Universal Scalable Shader Engine (USSE) isa Multithreaded EngineIncorporating Pixel and Vertex Shader Functionality– Advanced Shader Feature Set in Excess ofMicrosoft VS3.0, PS3.0, andOGL2.0– Industry Standard API Support of Direct3DMobile, OGL-ES 1.1 and 2.0,and OpenMax– Fine-Grained Task Switching, LoadBalancing, and Power Management– Advanced Geometry DMA-Driven Operationfor Minimum CPU Interaction – Programmable High-Quality Image Anti-Aliasing– Fully Virtualized Memory Addressing for OSOperation in a UnifiedMemory Architecture– LCD Controller– Up to 24-Bit Data Output; 8 Bits per Pixel(RGB)– Resolution up to 2048 × 2048 (WithMaximum 126-MHz Pixel Clock)– Integrated LCD Interface Display Driver(LIDD) Controller– Integrated Raster Controller– Integrated DMA Engine to Pull Data from theExternal Frame BufferWithout Burdening theProcessor via Interrupts or a Firmware Timer– 512-Word Deep Internal FIFO– Supported Display Types:– Character Displays - Uses LIDD Controllerto Program these Displays– Passive Matrix LCD Displays - Uses LCDRaster Display Controller toProvideTiming and Data for Constant GraphicsRefresh to a Passive Display – Active Matrix LCD Displays – UsesExternal Frame Buffer Space andtheInternal DMA Engine to Drive StreamingData to the Panel– 12-Bit Successive Approximation Register(SAR) ADC– 200K Samples per Second– Input can be Selected from any of the EightAnalog Inputs MultiplexedThrough an 8:1 Analog Switch– Can be Configured to Operate as a 4-Wire, 5-Wire, or 8-Wire ResistiveTouch Screen Controller (TSC) Interface– Up to Three 32-Bit eCAP Modules – Configurable as Three Capture Inputs orThree Auxiliary PWM Outputs– Up to Three Enhanced High-Resolution PWMModules (eHRPWMs)– Dedicated 16-Bit Time-Base Counter WithTime and Frequency Controls – Configurable as Six Single-Ended, Six Dual-Edge Symmetric, or ThreeDual-Edge Asymmetric Outputs– Up to Three 32-Bit Enhanced QuadratureEncoder Pulse (eQEP) Modules • Device Identification– Contains Electrical Fuse Farm (FuseFarm) ofWhich Some Bits are Factory Programmable– Production ID– Device Part Number (Unique JTAG ID)– Device Revision (Readable by Host ARM)• Debug Interface Support– JTAG and cJTAG for ARM (Cortex-A8 andPRCM), PRU-ICSS Debug– Supports Device Boundary Scan– Supports IEEE 1500• DMA– On-Chip Enhanced DMA Controller (EDMA) hasThree Third-Party Transfer Controllers (TPTCs)and One Third-Party Channel Controller(TPCC), Which Supports up to 64 Programmable Logical Channels and EightQDMAChannels. EDMA is Used for:– Transfers to and from On-Chip Memories– Transfers to and from External Storage(EMIF, GPMC, Slave Peripherals)• Inter-Processor Communication (IPC)– Integrates Hardware-Based Mailbox for IPC andSpinlock for Process Synchronization BetweenCortex-A8, PRCM, and PRU-ICSS – Mailbox Registers that Generate Interrupts – Four Initiators (Cortex-A8, PRCM, PRU0,PRU1)– Spinlock has 128 Software-Assigned LockRegisters • Security– Crypto Hardware Accelerators (AES, SHA,RNG)– Secure Boot • Boot Modes– Boot Mode is Selected Through BootConfiguration Pins Latched on the Rising Edge of the PWRONRSTn Reset Input Pin • Packages:– 298-Pin S-PBGA-N298 Via Channel Package(ZCE Suffix), 0.65-mm Ball Pitch– 324-Pin S-PBGA-N324 Package(ZCZ Suffix), 0.80-mm Ball PitchAM335x处理器应用:• Gaming Peripherals• Home and Industrial Automation • Consumer Medical Appliances • Printers • Smart Toll Systems• Connected Vending Machines • Weighing Scales • Educational Consoles • Advanced Toys图1:AM335x处理器功能框图支持以太网,6LoWPAN RF 网络和更多的通用数据集中器参考设计TIDA-010032IPv6-based grid communications are becoming the standard choice in industrial markets and applications like smart meters and grid automation. The universal data concentrator design provides a complete IPv6-based network solution integrated with Ethernet backbone communication, 6LoWPAN RF mesh networking, RS-485 and more. The 6LoWPAN mesh networking addresses key concerns such as standard-basedinteroperability, reliability, security and long-distance connectivity. This design allows controlling and monitoring end devices remotely with a webserver accessible via Ethernet backbone communication. It also provides 3.3V and 5V voltage rails and various peripheral interfaces to extend to additional connectivity such as broadband power-line communication (PLC), cellular and Wi-Fi®.参考设计TIDA-010032主要特性:Implements universal data concentrator supporting Ethernet, 6LoWPAN mesh and RS-485 connectivity devicesAllows Internet of Things (IoT) services with web server and Ethernet backbone connectivityImplements 6LoWPAN RF mesh network protocols of 6LoWPAN, RPL, IPv6/ICMPv6 and UDPIntegrates with TI 15.4-Stack that supports frequency hopping (FH) and data encryption Fully compatible with the TIDA-010003 and TIDA-010024 end-node reference designs to provide a complete network solution Capable of extending to other connectivity devices such as broadband PLC, cellular and Wi-Fi参考设计TIDA-010032应用:Data concentrators Wireless communications图2:参考设计TIDA-010032外形图。

关于AM335系列的板卡和相关模块产品常见问题

关于AM335系列的板卡和相关模块产品常见问题最近有客户在使用OK335x系列开发板中遇到了一些问题,所以在这里简单地总结了几点常见问题和解决方案,在这里分享一下。

如果您手中正好有飞凌的AM335x系列板卡,请仔细阅读,可能目前困扰您的问题答案就在这里!一.关于OK335x系列开发板,启动时,调试串口循环打印CCCCC问题分析以下为打印信息:建议从两方面进行问题排查:(1)OK335x系列开发板启动方式有2种:SD卡、nand. 请检查是否设置的SD卡启动,但是没有插SD卡或者SD卡中无程序。

底板上的拨码开关要拨到相应位置,参考以下说明:1. SD 卡启动设置:直接拨到 On2. NandFlash 启动设置:直接拨到 Off注:On 代表拨到上方,Off 代表拨到下方(2)飞凌OK335x系列开发板DI8-13的引脚,是boot启动项相关引脚。

如果您这几个引脚上接的外设模块电平跟uboot(下拉)启动电平相反,也可能会影响启动。

可以排查下是否是这几个引脚导致。

(3)如果排查以上两点还未解决问题,请联系飞凌技术支持************!二.关于OK335x系列开发板启动时,串口打印信息出现:please contact forlinx问题分析。

以下为打印信息:建议从两方面进行问题排查:(1)FET335x系列核心板上有个加密芯片:DS2406,通过IIC 接的CPU,这个芯片用户不能使用,因为出厂时里面已经写入了飞凌的加密信息,只有飞凌系统可以使用。

uboot在启动过程中会取读取保存在DS2460里的密码。

验证不通过的时候,会在串口打印信息里提示“Contact Forlinx….”,这种情况一般是加密芯片里的密码丢了,也可能是出厂没有烧写加密芯片。

(2)除了加密芯片用了一路IIC接口,核心板还支持2路,有些用户需要接自己的IIC外设模块。

如果您把设备挂载到加密芯片的这路IIC上,地址出现冲突,这样也可能会有影响,出现“please contact forlinx”信息。

AM335x核心板

SOM335x 是 EMA 推出的一款基于 TI Cortex-A8 AM335x 系列处理器的低功耗工业级 ARM 核心板, 板载高达 512MB DDR3,4GB eMMC /1GB NAND 大容量存储。SOM335x 体积极小,通过两个 2x50pin B2B 插针连接器,将多路 UART/IIC/SPI/MMC、8 路 ADC、2 路 CAN、2 路千兆 MAC、24bit LCD 等外设 全部引出,系统集成度高,有效降低客户开发成本。提供完善的参考设计,大大降低客户的开发周期。

2

HMI335x 是广州英码科技发布的一款基于 SOM335x 设计的工业级主板,通过两路 2x50pin B2B 插针 连接器与 SOM335x 连接。基于 HMI335x,客户只需要关注于上层应用软件。

n n n 可根据客户需要,提供配套的产品外壳 9~24V宽压DC电源输入 串口资源 2x RS232(一个DB9接口、一个TJC3接口)

1

1xRS485(DB9接口) 1x 3.3V TTL UART(TJC3接口) n n n n n n n n n n n 1x DCAN 2.0B(DB9接口) 1x 千兆网口 1x WIFI Module(可选) 8x 12-bit ADC/TSC 1x 24bit LCD接口 2x USB 2.0 Host 2x SPI总线接口 1x 蜂鸣器 1x6-bit 启动拨码开关 1x14针JTAG标准接口 音频接口 1x双声道扬声器输出接口 1x双声道麦克风输入接口 n 按钮 1x复位按键 1x自定义按键 n n MMC/SD/SDIO/SDHC卡槽,最高支持32GByte 扩展功能接口 1x GPMC总线接口 2x USB 2.0 Host接口 2x USB 2.0 OTG接口 1x Reset信号线 1x MDIO总线 Linux 操作系统 Bootloader:u-boot 2011.9, 支持从 SD Card/eMMC/NAND 启动,支持串口和网络下载 内核版本:Linux3.2,文件系统:UBIFS 相关驱动:eMMC,CAN, Serial port, RTC, Ethernet, LCD, McSPI, EEPROM, Touch screen, MMC/SD , USB OTG, USB , Audio input/output 等 Android 操作系统 Android 版本:Android4.0 内核版本:Linux3.2 I-Android 工业控制套件: 支持 CAN 总线、RS232、RS485、I2C、GPIO 设备等设备接入

珠海鼎芯 AM335x EVM硬件用户手册

A8_RGMII1_MDIO_CLK

7

A8_RGMII1_MDIO_DATA

8

A8_RGMII1_RXCLK

9~12

A8_RGMII1_RXD[0..3]

13~16

A8_RGMII1_TXD[0..3]

17

A8_RGMII1_TXCLK

18

A8_RGMII1_TXEN

19

A8_RGMII1_RXDV

系列

Up to 720MHz ARM Cortex™-A8 32bit RISC内核

NEON™SIMD协处理器

Power VR SGX™5303D图形加速处理引擎

RAM

256MByte DDR3

PMIC

TPS 65910

电源

5V DC

晶振

24MHz主时钟

32.768KHz RTC时钟

LED

2个运行指示灯

3.2.1处理器

AM335x作为开发板的核心处理器,提供高达720MHz的主频速度。AM335x支持mDDR/DDR2/DDR3,并配有NEON™SIMD协处理器、SGX5303D图形引擎。同时AM335x提供了丰富的接口资源。极高的性价比,使得它能适用性极广。开发板围绕AM335x设计的资源,为开发者提供了基于AM335x系列的硬件和软件开发的所有可能性。

TPS65910

AM335x

Voltage

VAUX2

VDDSHV6

3.3V

VMMC

VDDSHV2,3,4,5,VDDA3P3V_USB0/1

3.3V

VDD2 SMPS

VDD_CORE

1.1V

VDD1 SMPS

VDD_MPU

1.2V

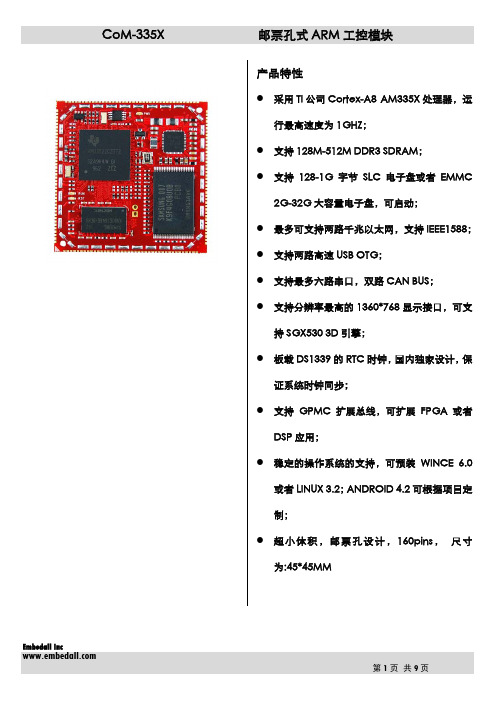

AM335X工业核心模块CoM-335X,邮票孔设计,带扩展总线

产品特性●采用TI公司Cortex-A8 AM335X处理器,运行最高速度为1GHZ;●支持128M-512M DDR3 SDRAM;●支持128-1G字节 SLC电子盘或者EMMC2G-32G大容量电子盘,可启动;●最多可支持两路千兆以太网,支持IEEE1588;●支持两路高速USB OTG;●支持最多六路串口,双路CAN BUS;●支持分辨率最高的1360*768显示接口,可支持SGX530 3D引擎;●板载DS1339的RTC时钟,国内独家设计,保证系统时钟同步;●支持GPMC扩展总线,可扩展FPGA或者DSP应用;●稳定的操作系统的支持,可预装WINCE 6.0或者LINUX 3.2;ANDROID 4.2可根据项目定制;●超小体积,邮票孔设计,160pins, 尺寸为:45*45MM简要介绍工业宽温设计,工作更稳定:CoM-335X Computer-on-Module (CoM),该产品集成了 ARM Cortex-A8 1GHz(MAX) TI AM335X 处理器,稳定运行WindowsCE 6.0 和Linux 3.2。

CoM-335X提供了3.3V I/O接口,可提供宽温的工业组件,运行于条件恶劣的工业现场!提供开发套件,可快速应用开发套件中包括主板、各种LCD配件,提供开发工具以及API函数、参考代码、详细的使用手册,让客户快速上手。

部件组成FUNCTION CoM-335X主控制器 TI Am335X,Cortex-A8,1GHZ(Max)内存256MB DDR3(最大可到512MB)闪存SLC NAND 128MB (最大到1GMB) 或者EMMC(最大到32GMB)图形显示 内置24位 LCD控制器主要参数时钟 DS1339U-33看门狗 有电源管理 TPS65217C (可支持电池供电的移动应用)复位 支持软件和硬件复位 (直接写寄存器)串口 串口6个,LVTTL电平以太网 2,10/100/1000MbpsUSB 2.0 Client1个,高速USB 2.0 Host 1个,高速SD/MMC卡 四线触摸屏 支持4线、5线、8线I/O系统总线 支持16位数据总线、12位地址总线,可支持接口FPGA或DSP(与24位LCD接口复用)IIC接口 2SPI接口 2GPIO 多个3.3V LVTTL电平MCASP音频 1CAN总线 2(与IIC复用一路)Graphic Chip支持2D/3D,仅对于AM3354多媒体分辨率最大1360×768LCD接口 16-bit TTL接口电源 5.0 V (+-5%)电源PowerTBDConsumption尺寸45MM*45MM*3.2MM尺寸 & 环境工作温度-20 ~ 70° C (可定制-40 ~85°C)工作湿度 5 ~ 95 % ,冷凝结RoHS YES其他认证CE软件支持Linux 3.2 (WCE6.0或者ANDROID项目定制支持)引脚定义支持软件订购信息Part No. CPU RAM FlashMemory UART LAN USBHostUSBOTGLCD videodecoderTouch SD IIC SPI EBI BUS PowerInputOperatingtemp.Com-335X-A1 AM3352 128M 256M 6 1 1 1 24-bit yes1 2 1 yes 5.0v 0-70 Com-335X-A2 AM3352 128M 256M 6 1 1 1 24-bit yes1 2 1 yes 5.0v -20-70 Com-335X-B1 AM3354 128M 256M 6 1 1 1 24-bit 3D yes 1 2 1 yes 5.0v -20-70 Com-335X-B2 AM3354 256M 256M 6 1 1 1 24-bit 3D yes 1 2 1 yes 5.0v -20-70Com-335X-C1 AM3352 512M EMMC2G 6 1 1 1 24-bit yes1 2 1 NO 5.0v -20-70Com-335X-C2 AM3352 512M EMMC4G 6 1 1 1 24-bit yes1 2 1 NO 5.0v -20-70Com-335X-D1 AM3354 512M EMMC2G6 1 1 1 24-bit 3D yes 1 2 1 NO 5.0v -20-70Com-335X-D2 AM3354 512M EMMC4G6 1 1 1 24-bit 3D yes 1 2 1 NO 5.0v -20-70尺寸(mm)评估套件推荐应用1.应用案例1-POS机2.应用案例2-监护仪3.应用案例3-人机界面。

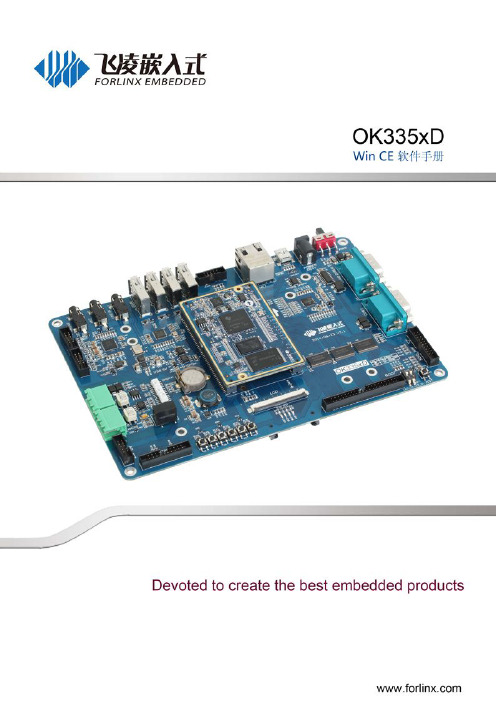

飞凌嵌入式-AM335x Wince软件手册

第 CE软件手册

注意事项与维护

产品使用环境

供电电压: DC5V ± 10% 运行温度: 商用级 0 – 80 ℃ 工业级 -40 – 85 ℃ 10 – 90%(不结露) 湿度:

注意事项

·请勿带电插拔核心板及外围模块!

·请遵循所有标注在产品上的警示和指引信息。 ·请保持本产品干燥。如果不慎被任何液体泼溅或浸润,请立刻断电并充分晾干。 ·使用中注意本产品的通风散热,避免温度过高造成元器件损坏。 ·请勿在多尘、脏乱的环境中使用或存放本产品。 ·请勿将本产品应用在冷热交替环境中,避免结露损坏元器件。 ·请勿粗暴对待本产品,跌落、敲打或剧烈晃动都可能损坏线路及元器件。 ·请勿使用有机溶剂或腐蚀性液体清洗本产品。 ·请勿自行修理、拆卸本公司产品,如产品出现故障请及时联系本公司进行维修。 ·擅自修改或使用未经授权的配件可能损坏本产品,由此造成的损坏将不予以保修。 如果产品出现故障,请联系飞凌技术服务部。

2技术讨论范围(非必解决问题)

2.1 源码的修改以及理解; 2.2 操作系统如何移植; 2.3 用户在自行修改以及开发中遇到的软硬件问题;

3技术支持方式

3.1 电话(即时):0312-3119192 3.2 邮箱(非即时): 3. Linux 技术支持:linux@ 4. WinCE 技术支持:wince@ 5. Android 技术支持:android@ 3.3 论坛(非即时):

4

OK335xD Win CE软件手册

目 录

注意事项与维护................................................................................................................

TI-AM335XGPMC7个config寄存器重点

TI-AM335XGPMC7个config寄存器重点每个Config寄存器有32位Config1:1-0 GPMCFCLKDIVIDER Divides the GPMC.FCLK clock//⽤于设置时钟使⽤默认00 GPMC_CLK frequency = GPMC_FCLK frequency1h GPMC_CLK frequency = GPMC_FCLK frequency/22h GPMC_CLK frequency = GPMC_FCLK frequency/33h GPMC_CLK frequency = GPMC_FCLK frequency/44 TIMEPARAGRANULARITY Signals timing latencies scalar factor (Rd/WRCycleTime, AccessTime,PageBurstAccessTime, CSOnTime, CSRd/WrOffTime, ADVOnTime,//设置时间速度有关,没懂,默认0ADVRd/WrOffTime, OEOnTime, OEOffTime, WEOnTime, WEOffTime,Cycle2CycleDelay, BusTurnAround, TimeOutStartValue)0 ×1 latencies1 ×2 latencies9-8 MUXADDDATA Enables the Address and data multiplexed protocol (Reset value isCS0MUXDEVICE input pin sampled at IC reset for CS[0] and 0 for CS[1-5])//使⽤默认00 Non-multiplexed attached device1h AAD-multiplexed protocol device2h Address and data multiplexed attached device3h Reserved11-10 DEVICETYPE Selects the attached device type//默认0,我的是SRAM0 NOR Flash like, asynchronous and synchronous devices1h Reserved2h NAND Flash like devices, stream mode3h Reserved13-12 DEVICESIZE Selects the device size attached (Reset value is BOOTDEVICESIZE input //终于⾃⼰设置了,要操作的ram是16位的,当然以后操作别的ram就改为其它的pin sampled at IC reset for CS[0] and 01 for CS[1-5])0 8 bit1h 16 bit2h Reserved3h Reserved28 WRITEMULTIPLE Selects the write single or multiple access//28 30设置读写为单个或复⽤?有点不肯定,但这⾥都设置为00 Single access1 Multiple access (burst if synchronous, considered as single if asynchronous)30 READMULTIPLE Selects the read single or multiple access0 single access1 multiple access (burst if synchonous, page if asynchronous)config2-6://按照芯⽚⼿册757页时序图配置config7:5-0 BASEADDRESS 0-3Fh Chip-select base address.//设置为0x10;A24设置为有效CSi base address where i = 0 to 3 (16 Mbytes minimum granularity). Bits [5-0] correspondsto A29, A28, A27, A26, A25, and A24.11-8 MASKADDRESS Chip-select mask address. Values not listed must be avoided as they create holes in the chip-select address space.//默认设置为00 Chip-select size of 256 Mbytes8h Chip-select size of 128 MbytesCh Chip-select size of 64 MbytesEh Chip-select size of 32 MbytesFh Chip-select size of 16 Mbytes。

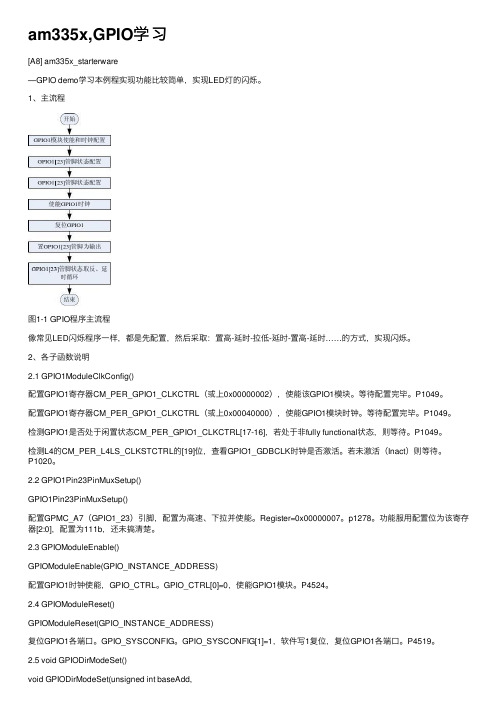

am335x,GPIO学习

am335x,GPIO学习[A8] am335x_starterware—GPIO demo学习本例程实现功能⽐较简单,实现LED灯的闪烁。

1、主流程图1-1 GPIO程序主流程像常见LED闪烁程序⼀样,都是先配置,然后采取:置⾼-延时-拉低-延时-置⾼-延时……的⽅式,实现闪烁。

2、各⼦函数说明2.1 GPIO1ModuleClkConfig()配置GPIO1寄存器CM_PER_GPIO1_CLKCTRL(或上0x00000002),使能该GPIO1模块。

等待配置完毕。

P1049。

配置GPIO1寄存器CM_PER_GPIO1_CLKCTRL(或上0x00040000),使能GPIO1模块时钟。

等待配置完毕。

P1049。

检测GPIO1是否处于闲置状态CM_PER_GPIO1_CLKCTRL[17-16],若处于⾮fully functional状态,则等待。

P1049。

检测L4的CM_PER_L4LS_CLKSTCTRL的[19]位,查看GPIO1_GDBCLK时钟是否激活。

若未激活(Inact)则等待。

P1020。

2.2 GPIO1Pin23PinMuxSetup()GPIO1Pin23PinMuxSetup()配置GPMC_A7(GPIO1_23)引脚,配置为⾼速、下拉并使能。

Register=0x00000007。

p1278。

功能服⽤配置位为该寄存器[2:0],配置为111b,还未搞清楚。

2.3 GPIOModuleEnable()GPIOModuleEnable(GPIO_INSTANCE_ADDRESS)配置GPIO1时钟使能,GPIO_CTRL。

GPIO_CTRL[0]=0,使能GPIO1模块。

P4524。

2.4 GPIOModuleReset()GPIOModuleReset(GPIO_INSTANCE_ADDRESS)复位GPIO1各端⼝。

GPIO_SYSCONFIG。

GPIO_SYSCONFIG[1]=1,软件写1复位,复位GPIO1各端⼝。

飞凌AM335x开发板Linux用户手册

OK335X-Linux用户手册第一章OK335X简介OK335X开发板基于TI AM335X处理器,运行主频最高720M,支持Linux,WinCE,Android三大操作系统,可用于工业产品设计。

OK335X有核心板和底板组成,核心板主要芯片有:CPU,NandFlash,Memory,PowerManage。

使用我们的核心板,只需要根据您的业务需求开发自己的底板,这样可加速您的产品上市时间,让您从平台搭建的复杂环境中脱离。

下面我们具体描述OK335X核心板和底板资源。

OK335X产品图片如下所示:核心板硬件资源:1CPU主频:720M(支持AM3352,AM3354,AM3356,AM3357,AM3358,AM3359)2NandFlash:256M(Micro SLC)3Memory:265M(Micro DDR2)4PowerManage IC:TPS65217B(TI AM335X专用电源IC)底板资源:14路串口(2个232电平,2个TTL电平,232电平已经使用DB9座子引出,其中COM0作为调试串口使用,注意:OK335X-V1底板中UART4暂时不能使用,下一硬件版本将修正这个问题)。

21路100M网口3音频接口(1路Phone输出,1路Line-in输入)41个SD卡接口56个用户按键63路I2C接口71个LCD接口(支持RGB888模式,支持电阻触摸和电容触摸。

默认标配7寸电阻屏)81路PWM接口,用于蜂鸣器测试。

91路Can接口101路SDIO接口11多路用户IO接口12四路USB2.0接口,一路USB2.0OTG(目前板子为一路USB Host接口,后续会增加到四路USB HUB)131路SPI接口148路AD(其中4路用于电阻触摸,1路用于滑动变阻器AD测试,其余3路通过插针引出,另外滑动变阻器端有跳线设置,通过跳线可以设置这路AD用于插针引出,还是用于可调电阻测试)15引出总线接口(缺省未焊接底座)161个RESET按钮,用于系统复位。

am335x双网络工控板原理图

4

3

2

1

COVER PAGE

D D

C

C

B

B

A

深圳市盈鹏飞科技有限公司 设计 Bills 日期 2015.03.25 日期 Date 校对 Leo 审核 Ping 日期 Date 批准 Ping 日期 Date

Friday, September 04, 2015

5 4 3 2

名称 编号 说明 版本 页码 工业单板电脑 EVB-335X-II COVER PAGE V1.00 第 1 页 共 23 页

B

GPIO0_26 GPIO0_27 GPIO0_28 GPIO0_29 GPIO0_30 GPIO0_31

B

A

深圳市盈鹏飞科技有限公司 设计 Bills 日期 2015.03.11 日期 Date 校对 Leo 审核 Ping 日期 Date 批准 Ping 日期 Date

Friday, September 04, 2015

B

PCB层数:四层 PCB尺寸:120*120MM

名称 编号 说明 版本 页码 工业单板电脑 EVB-335X-II PCB LAYERS V1.00 第 2 页 共 23 页

1 A

A

5

4

3

2

5

4

3

2

1

PCB LAYOUT

D D

固定核心板螺钉

H1 TH_D1.4MM

H2 TH_D1.4MM

LAYOUT NOTE(PING): H1,H2为非金属化孔,无焊盘 与CoM-335x的定位孔对应;

LAYOUT NOTE(PING): 双拼板,注意MARK点设置;

C

C

结构固定镙孔

AM335X核心板 AM335X核心板详细资料

335X核心板◆采用TI AM335X系列处理器,最高720MHz高速ARM Cortex-A8核心;◆准确定位工业控制领域,低功耗、低成本、高集成度核心模块+定制底板应用;◆提供管脚复用图表,客户可以精准匹配核心板管脚复用,实现更多应用;◆提供底板全部资源(含PCB文件)让您快速完成底板硬件设计,缩短研发周期;◆板载2路千兆网卡、多路RS232/485、2路CAN总线、GPMC总线等工业接口;◆核心板可全部升级工业级器件,邮票孔封装,稳定适用于各种现场环境;◆预装Linux3.2操作系统,提供丰富例程及源代码;产品参数核心板采用高密度6层板(沉金)设计,,集成了CPU、DDR2 RAM、NandFlash、千兆网卡、采用5V直流供电,超低功耗,邮票封引出各种常用接口资源,核心板与AM335x-ARM Cortex-A8系列处理器全部兼容,用户可根据需要选择不同型号的处理器芯片以适当降低成本,此种选择只适合于批量用户。

注意:标配A M3354处理器,以满足广大用户降低成本的要求,其余型号均为PIN脚兼容,仅供批量用户选择!AM335X系列处理器(批量用户可选):标号ARM CPUARMMHz(MAX.)ARMMIPS(MAX.)GraphicsAccelerationOther Hardware AccelerationAM3359 1 ARM Cortex-A8 275600720120014401 3D2 PRU-ICSSCrypto AcceleratorAM3358 1 ARM Cortex-A8 2756005007201000120014401 3D2 PRU-ICSSCrypto AcceleratorAM3357 1 ARM Cortex-A8 275600720550120014402 PRU-ICSSCrypto AcceleratorAM3356 1 ARM Cortex-A8 2756005007205501000120014402 PRU-ICSSCrypto AcceleratorAM3354 1 ARM Cortex-A8 2756005007201000120014401 3D Crypto AcceleratorAM3352 1 ARM Cortex-A8 275600500720100012001440Crypto Accelerator核心板资源说明:CPU处理器• TI AM335X,ARM Cortex-A8内核• 标配主频600MHZ,批量可选800MHZ、1GHZDDR RAM内存• 512MB DDR2 RAM,133MHz,16bit数据总线,FLASH存储板载512M*8bits NandFlash接口资源• 邮票封,稳定板载其他资源•AR8035网络芯片,完美支持10M/100M/1000M网口自适应,采用RGMII模式• 电源管理,单5V输入,输出核心板需要的所有电压PCB规格尺寸• 采用6层PCB板高精度工艺,具有最佳的电气性能和抗干扰性能• 58x 52x 1.6mm温湿度工作参数• 工作温度:-20°C~ 70°C 批量用户可定制-40°C~ 85°C工业级温宽• 工作湿度:5%到95%,非凝结超低功耗• 5V直流电压供电,单板超低功耗,小于2W操作系统支持• Linux3.2.0 + QT ouch(QT界面组态软件)核心板软件及技术支持:• 客户使用开发过程中遇到的和产品相关的问题• 根据客户需求进行系统的裁剪• QTOUCH软件基础应用,包含常用的ModbusRTU等通讯• 使用QTOUCH软件和其它设备通讯驱动开发(另收费)• 根据客户的需求,辅助开发相关驱动(另收费)• 根据客户的具体需求,进行底板的定制开发(另收费)。

工业、军用级别arm基于TI AM335x平台介绍

(自适应电压缩放(AVS))• 动态电压频率调整 实时时钟 (RTC)

- 实时的日期(日/月/年/天的周)和时间(小时/分钟/秒)的信息 - 内部 32.768 khz 振荡器,RTC 逻辑和 1.1 - v 内部 LDO - 独立的 Power-on-Reset (RTC_PWRONRSTn) 输入 - 为外部唤醒事件预留的专用输入针脚 - 可编程报警可以用来生成内部中断给 PRCM (唤醒) 或者 Cortex-A8 (事件通知) - 可编程报警可以使用外部输(PMIC_POWER_EN) 使电源管理 IC 恢复成非实时时

微处理器子系统:

275-MHz, 500-MHz, 600-MHz, 或者 720-MHz ARM® Cortex™-A8 32-Bit RISC 微处理器 - NEON™ SIMD 协处理器 - 具有单一错误检测(奇偶校验)的 32KB 的 L1 指令缓存 - 具有单一错误检测(奇偶校验)的 32KB 的 L1 数据缓存 - 具有 ECC 的 256KB L2 缓存 - 176KB 板载 Boot ROM

RTC:实时时钟 RTC 串口:

- 两个区域网络端口控制器 - 6 个 UARTs,2 个 McASPs,2 个 McSPI,3 个 I2C 接口 - 12bit 逐次逼近寄存器型模数转换器 - 3 个 32bit 增强捕获模块 - 3 个增强的高分辨率 PWM 模块 - 加密硬件加速器(AES,SHA,PKA,RNG) 以太网:两个支持工业以太网的 MII 以太网接口

- 控制进入和退出的备用和深度睡眠模式 - 负责睡眠测序,电力领域关闸测序,唤醒测序和电力领域接通测序 - 时钟 集成 15 35 MHz 高频振荡器用于生成一个基准时钟为各种系统和外围时钟 支持单个时钟启用/禁用控制子系统和外设,有利于降低功耗 五个 ADPLLs 生成系统时钟(微控制器子系统,DDR 接口,USB 和外围设备(MMC / SD,UART,SPI、I2C,等等。),L3、L4,以太网,GFX[SGX530],液晶像素时钟) 供电 - 两个非可切换的电力域(实时时钟(RTC),唤醒逻辑[唤醒]) - 三个可切换的电力域(微控制器子系统(微处理器),SGX530[GFX]、外围设备和

AM335x通用EVM硬件用户指南_中文

AM335x通用EVM硬件用户指南本文档介绍了AM335x评估模块(EVM)(TMDXEVM3358)这是基于德州仪器AM335x处理器的硬件体系结构。

该EVM通常也被称为AM335x通用(GP)EVM。

AM335x通用EVM是一个独立的测试,开发和评估模块系统,它使开发人员能够编写周围的AM335x处理器子系统的软件和硬件开发。

已经可用的EVM板的基础上,为开发人员提供了所需的基本资源最通用的类型的项目,包括作为主处理器的AM335x AM335x子系统的主要内容。

此外,额外的,“典型的”外围设备内置的的EVM如存储器,传感器,LCD,以太网PHY等,使未来的系统可以模拟快速显着的额外的硬件资源。

以下各节提供有关EVM的更多细节。

AM335x通用EVM的系统视图是由底板,子板,液晶显示板叠放在一起,通过标准的通孔连接器连接。

请参阅下面的图片的EVM。

图1:AM335x通用EVM 图2:的AM335x底板底查看AM335x完整的通用EVM被划分在三个不同的电路板的模块化。

GP EVM包括基板(处理器和主电源),子板(外围设备)和液晶显示板(LCD和触摸屏)。

图3:AM335x的EVM系统板图处理器TMXAM3359ZCZ处理器是此EVM的中央处理器。

在黑板上的所有资源环绕TMXAM3359处理器提供的硬件和软件开发能力。

请参阅的TMXAM3359数据表和TRM的处理器的详细信息。

有系统的配置信号,SYSBOOT,也可以设置在EVM上AM335x处理器定义一些启动参数。

有关详细信息,请参阅“配置/设置”一节。

EVM有几个时钟,支持AM3359处理器。

为处理器的主时钟是来自从24MHz晶体。

片上振荡器的AM3359产生基准时钟,后续的模块需要在AM3359处理器的时钟。

一个32kHz的时钟RTC的AM3359是来自一个32kHz的晶体在黑板上。

SYS_RESETn是运行多个外设和的AM335x其中执行这些外围设备的复位信号。

AM335x GPMC模块地址区域划分详解

AM335x GPMC模块地址区域划分详解我们知道AM335x的GPMC模块作为一组并行的外部总线接口,使用的频率还是挺高的,在这上面可以挂NAND FLASH,NOR FLASH,FPGA,DM9000等等设备。

使用的方式,从硬件方面来说,GPMC总线上挂的设备共享了数据线、地址线和一些控制线,然后由片选信号控制、使能对应的设备。

这里需要提到一点,不同片选的地址空间配置、时序配置,都是分开的,参考TRM中关于GPMC_CONFIG1_i~GPMC_CONFIG7_i的配置说明,i的取值决定了写入的地址区间不同,对应的就是不同的片选。

软件配置上面,时序配置就不赘述了,主要有个问题容易引起大家疑惑,那个地址空间的配置是怎样的?下面就这个问题,简要解析一下:首先,GPMC是可以对每个片选上的设备进行地址区间的分配,配置起来也非常灵活。

举个例子:对于片选0,我们把地址空间配置为0x0000_0000~0x0400_0000;对于片选1,地址空间配置成0x0600_0000~0x0A00_0000;这样完成配置了后,如果往0x0000_0004这个地址里写数据,由于它属于片选0的地址区间,所以这个时候CPU就会去使能片选0(拉低GPMC_CS0n),从而对片选0上的设备进行操作;如果写的是0x0600_0010地址空间,属于片选1的,就会去使能片选1(拉低GPMC_CS1n),操作片选1上的设备。

通过这种方式,就实现对不同的设备操作。

PS: 如果是对未分配的地址空间操作,则没有片选信号会拉低,操作无效;对于已经分配了的片选地址空间,一定要注意,不要交叠,以免发生冲突。

打开AM335x的TRM,第二章2.1 ARM Cortex-A8 Memory Map中可以看到,对GPMC的外部内存地址分配的空间为512MB,从0x0000_0000~0x1FFF_FFFF。

这个意思就是说,GPMC给所有片选分配的地址空间都必须要在这个区域之内。

03 AM335x处理器

北京交通大学

国家电工电子教学基地

Introduction to AM335x

AM335X 系列处理器

• 不同配置,引脚兼容

北京交通大学

国家电工电子教学基地

AM335x Processor

基于AM335x处理器的硬件系统

• AM335x介绍 • 主处理器

• 片上模块

• 硬件构成要点

• 开发资源

北京交通大学

国家电工电子教学基地

Main processor

存储器映射 (L3)

• GPMC (外接存储器)

– 0x0000_0000- 0x1FFF_FFFF, 512MB 8-/16-bit External Memory (ex/r/w)

• Boot ROM

– 0x4002_0000 0x4002_BFFF 48KB, (32b, ex/r)

北京交通大学 国家电工电子教学基地

Main processor

存储器子系统: EMIF

• 16-bit data width

• support DDR2/DDR3/mDDR • On-chip 128-bit interface

Cmd/addr 128-bit OCP DDR2/3/ mDDR Memory Controller DDR data

• 可应用于家庭自动化,工业自动化,工业平板,便携导 航设备和网络互联。

北京交通大学 国家电工电子教学基地

Introduction to AM335x

AM335X 功能模块

• 3个子系统

– A8 MPU 子系统 – POWERVR SGX 图形加速子系统 – PRU-ICSS 实时单元和工业 通信子系统

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

AM335x GPMC模块地址区域划分详解

我们知道AM335x的GPMC模块作为一组并行的外部总线接口,使用的频率还是挺高的,在这上面可以挂NAND FLASH,NOR FLASH,FPGA,DM9000等等设备。

使用的方式,从硬件方面来说,GPMC总线上挂的设备共享了数据线、地址线和一些控制线,然后由片选信号控制、使能对应的设备。

这里需要提到一点,不同片选的地址空间配置、时序配置,都是分开的,参考TRM中关于

GPMC_CONFIG1_i~GPMC_CONFIG7_i的配置说明,i的取值决定了写入的地址区间不同,对应的就是不同的片选。

软件配置上面,时序配置就不赘述了,主要有个问题容易引起大家疑惑,那个地址空间的配置是怎样的?下面就这个问题,简要解析一下:

首先,GPMC是可以对每个片选上的设备进行地址区间的分配,配置起来也非常灵活。

举个例子:对于片选0,我们把地址空间配置为0x0000_0000~0x0400_0000;对于片选1,地址空间配置成0x0600_0000~0x0A00_0000;这样完成配置了后,如果往

0x0000_0004这个地址里写数据,由于它属于片选0的地址区间,所以这个时候CPU就会去使能片选0(拉低GPMC_CS0n),从而对片选0上的设备进行操作;如果写的是0x0600_0010地址空间,属于片选1的,就会去使能片选1(拉低GPMC_CS1n),操作片选1上的设备。

通过这种方式,就实现对不同的设备操作。

PS: 如果是对未分配的地址空间操作,则没有片选信号会拉低,操作无效;对于已经分配了的片选地址空间,一定要注意,不要交叠,以免发生冲突。

打开AM335x的TRM,第二章2.1 ARM Cortex-A8 Memory Map中可以看到,对GPMC的外部内存地址分配的空间为512MB,从0x0000_0000~0x1FFF_FFFF。

这个意思就是说,GPMC给所有片选分配的地址空间都必须要在这个区域之内。

每个片选的地址分布,是在GPMC_CONFIG7_i中定义的,可以参考TRM中详细的示例讲解,在这里时间有限,我就挑重点的说了。

1. 首先要确定你是GPMC的device是NAND类型的,还是NOR类型的,在GPMC_CONFIG1中有定义,对于位宽的定义、同步、异步操作模式的定义也是在GPMIC_CONFIG1中定义的,不赘述。

2. 时序,这一点根据你实际的NAND/NOR或者相关手册定义就好,配置到相应片选信号的GPMC_CONFIG中。

3.地址,重点!GPMC_CONFIG7中:

bit[6]明显是确定当前所在的片选信号是否可用,即为,当前的片选上是否挂有device需要使用。

有就置为1即可。

bit[11-8]这个mask address,其实是规划了当前片选地址空间的大小,注意最小为16MB。

16MB的地址空间的跨度即为0~0x00FF_FFFF(低24位),所以在规划基地址的时候,只需要定义最高位即可,因为低位的地址,低24位都是可以由写入的地址区间

来决定,只有基地址需要我们定义和片选相关联。

bit[5-0]是base address,即为基地址的规划。

上面提到过地址空间的最小规划为16MB地址空间跨度最小为为0~0x00FF_FFFF,对应的,这个基地址定义了高位上面的地址值(高8位),同时把这个地址与当前的片选相关联。

举个例子,当前寄存器为GPMC_CONFIG7_0,当我的基地址规划为0x08,大小划归成16MB时,也就是说,我规划的片选0的地址空间为0x0800_0000 ~ 0x08FF_FFF;类似的,当我在寄存器中GPMC_CONFIG7_2的基地址定为0x0A,大小规划为128MB时,地址空间即为:起始地址:0x0A00_0000,结束地址为0x0A00_0000+0x08FF_FFFF=0x12FF_FFFF。

最后强调两点:1.地址空间的分步,不要重叠;2.地址空间的区域要在

0x0000_0000~0x1FFF_FFFF范围之内。