AK5384VF中文资料

AK5358AET中文资料

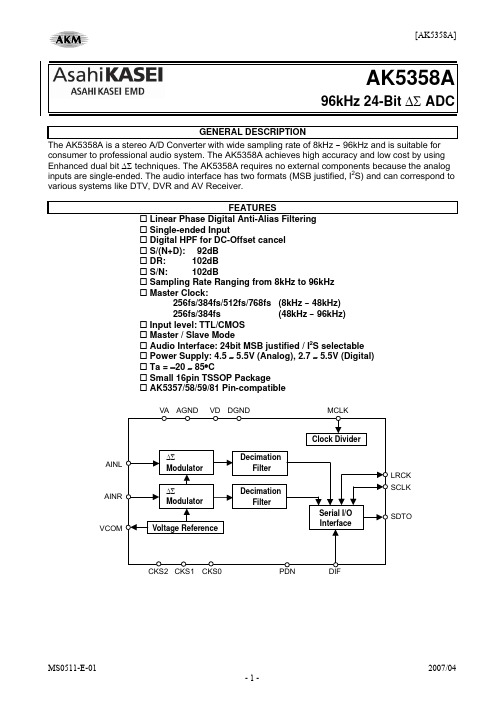

FEATURES

Linear Phase Digital Anti-Alias Filtering

Single-ended Input

Digital HPF for DC-Offset cancel

S/(N+D): 92dB

DR:

102dB

S/N:

102dB

Sampling Rate Ranging from 8kHz to 96kHz

- Digital Power Supply Pin, 2.7 ∼ 5.5V

- Digital Ground Pin

Audio Serial Data Output Pin O

“L” Output at Power-down mode.

Output Channel Clock Pin I/O

“L” Output in Master Mode at Power-down mode.

Classification Analog

AINL AINR

Pin Name

Setting This pin should be open. This pin should be open.

MS0511-E-01 -3-

2007/04

元器件交易网

[AK5358A]

ABSOLUTE MAXIMUM RATINGS

-

Analog Input Voltage (AINL, AINR, CKS1 pins)

VINA

−0.3

Digital Input Voltage

(Note 3)

VIND

−0.3

Ambient Temperature (powered applied)

AK5385BVFP-E2;AK5385BVSP-E2;中文规格书,Datasheet资料

MS0406-E-00 -2-

/

2005/08

ASAHI KASEI

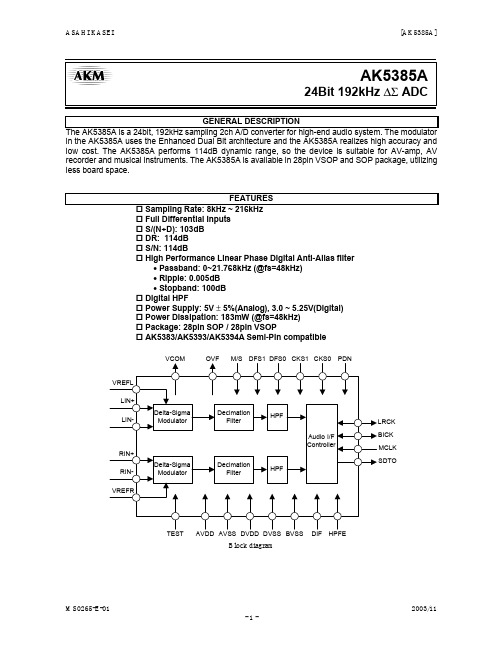

Compatibility with AK5383/AK5394A

Pin 1 Pin 2 Pin 3 Pin 6 Pin 9 Pin 11 Pin 12 Pin 16 Pin 18 Pin 20 Pin 26 Pin 27 Pin 28 fs MCLK at 48kHz MCLK at 96kHz MCLK at 192kHz DR, S/N Input Voltage Offset Calibration

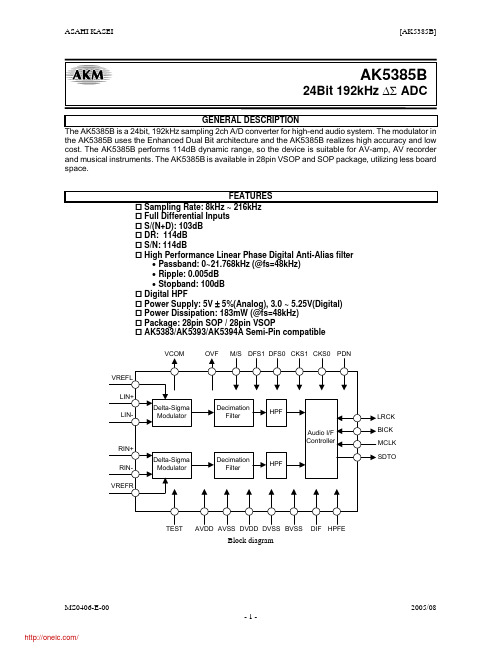

• Passband: 0~21.768kHz (@fs=48kHz)

• Ripple: 0.005dB

• Stopband: 100dB Digital HPF Power Supply: 5V ± 5%(Analog), 3.0 ~ 5.25V(Digital) Power Dissipation: 183mW (@fs=48kHz) Package: 28pin SOP / 28pin VSOP AK5383/AK5393/AK5394A Semi-Pin compatible

Pin Layout

VREFL AVSS VCOM LIN+ LINCKS0 DVDD DVSS OVF PDN DIF M/S LRCK BICK

[AK5385B]

–10 ~ +70°C

28pin SOP (1.27mm pitch)

–40 ~ +85°C

28pin VSOP (0.65mm pitch)

FEATURES

Sampling Rate: 8kHz ~ 216kHz Full Differential Inputs S/(N+D): 103dB DR: 114dB S/N: 114dB High Performance Linear Phase Digital Anti-Alias filter

CZ5384B资料

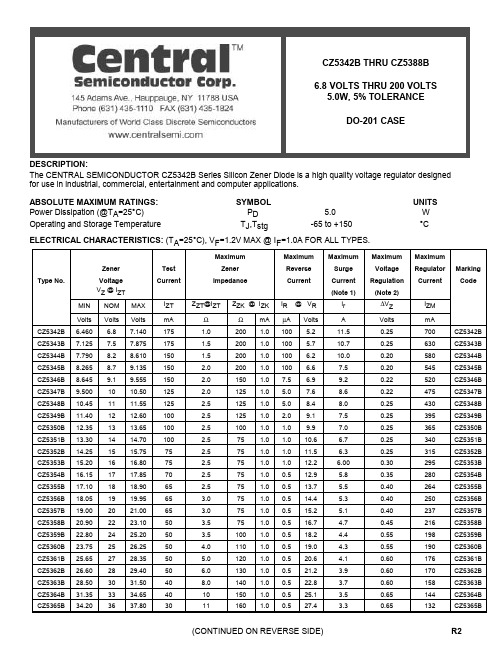

ELECTRICAL CHARACTERISTICS: (TA=25°C), VF=1.2V MAX @ IF=1.0A FOR ALL TYPES.

Maximum Zener Type No. Voltage VZ @ IZT MIN Volts CZ5342B CZ5343B CZ5344B CZ5345B CZ5346B CZ5347B CZ5348B CZ5349B CZ5350B CZ5351B CZ5352B CZ5353B CZ5354B CZ5355B CZ5356B CZ5357B CZ5358B CZ5359B CZ5360B CZ5361B CZ5362B CZ5363B CZ5364B CZ5365B 6.460 7.125 7.790 8.265 8.645 9.500 10.45 11.40 12.35 13.30 14.25 15.20 16.15 17.10 18.05 19.00 20.90 22.80 23.75 25.65 26.60 28.50 31.35 34.20 NOM Volts 6.8 7.5 8.2 8.7 9.1 10 11 12 13 14 15 16 17 18 19 20 22 24 25 27 28 30 33 36 MAX Volts 7.140 7.875 8.610 9.135 9.555 10.50 11.55 12.60 13.65 14.70 15.75 16.80 17.85 18.90 19.95 21.00 23.10 25.20 26.25 28.35 29.40 31.50 34.65 37.80 Test Current IZT mA 175 175 150 150 150 125 125 100 100 100 75 75 70 65 65 65 50 50 50 50 50 40 40 30 Zener Impedance ZZT@IZT Ω 1.0 1.5 1.5 2.0 2.0 2.0 2.5 2.5 2.5 2.5 2.5 2.5 2.5 2.5 3.0 3.0 3.5 3.5 4.0 5.0 6.0 8.0 10 11 ZZK @ IZK Ω 200 200 200 200 150 125 125 125 100 75 75 75 75 75 75 75 75 100 110 120 130 140 150 160 mA 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 Maximum Reverse Current IR µA 100 100 100 100 7.5 5.0 5.0 2.0 1.0 1.0 1.0 1.0 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 @ VR Volts 5.2 5.7 6.2 6.6 6.9 7.6 8.4 9.1 9.9 10.6 11.5 12.2 12.9 13.7 14.4 15.2 16.7 18.2 19.0 20.6 21.2 22.8 25.1 27.4 Maximum Surge Current (Note 1) ir A 11.5 10.7 10.0 7.5 9.2 8.6 8.0 7.5 7.0 6.7 6.3 6.00 5.8 5.5 5.3 5.1 4.7 4.4 4.3 4.1 3.9 3.7 3.5 3.3 Maximum Voltage Regulation (Note 2) ∆VZ Volts 0.25 0.25 0.20 0.20 0.22 0.22 0.25 0.25 0.25 0.25 0.25 0.30 0.35 0.40 0.40 0.40 0.45 0.55 0.55 0.60 0.60 0.60 0.65 0.65 IZM mA 700 630 580 545 520 475 430 395 365 340 315 295 280 264 250 237 216 198 190 176 170 158 144 132 CZ5342B CZ5343B CZ5344B CZ5345B CZ5346B CZ5347B CZ5348B CZ5349B CZ5350B CZ5351B CZ5352B CZ5353B CZ5354B CZ5355B CZ5356B CZ5357B CZ5358B CZ5359B CZ5360B CZ5361B CZ5362B CZ5363B CZ5364B CZ5365B Maximum Regulator Current Marking Code

AK4324-VF中文资料

19 AOUTL+ O Lch Positive analog output pin

20 AVSS

- Analog Ground pin

21 VREF

I Voltage Reference Input Pin

22 AVDD

- Analog Power Supply Pin

23 DZFR

O Rch Zero Input Detect Pin

Parameter

min

typ

max

Units

Resolution

24

Bits

Dynamic Characteristics (Note 4 )

THD+N

0dB Output -20dB Output -60dB Output

-94

-88

dB

-81

-

dB

-41

-

dB

Dynamic Range (-60dB Output, A weight) (Note5 ) 100

(Ta=25°C; AVDD,DVDD=5.0V; VREF=AVDD; fs=44.1kHz; BICK=64fs; Signal Frequency=1kHz; 24bit Input Data; Measurement Bandwidth=10Hz∼20kHz; RL≥5kΩ; unless otherwise specified)

Output Voltage

(Note 8 ) ±2.66

±2.8

±2.94

Vpp

Load Resistance

5

kΩ

Output Current

300

uA

Power Supplies

AK4384_06资料

GENERAL DESCRIPTIONThe AK4384 offers the perfect mix for cost and performance based audio systems. Using AKM's multi bit architecture for its modulator the AK4384 delivers a wide dynamic range while preserving linearity for improved THD+N performance. The AK4384 integrates a combination of SCF and CTF filters increasing performance for systems with excessive clock jitter. The 24 Bit word length and 192kHz sampling rate make this part ideal for a wide range of applications including DVD-Audio. The AK4384 is offered in a space saving 16pin TSSOP package.FEATURESSampling Rate Ranging from 8kHz to 192kHz 128 times Oversampling (Normal Speed Mode) 64 times Oversampling (Double Speed Mode) 32 times Oversampling (Quad Speed Mode) 24-Bit 8 times FIR Digital FilterSCF with High Tolerance to Clock Jitter 2nd order Analog LPFSingle Ended Output BufferDigital de-emphasis for 32k, 44.1k and 48kHz sampling Soft muteDigital Attenuator (Linear 256 steps)I/F format: 24-Bit MSB justified, 24/20/16-Bit LSB justified or I 2SMaster clock: 256fs, 384fs, 512fs, 768fs or 1152fs (Normal Speed Mode)128fs, 192fs, 256fs or 384fs (Double Speed Mode) 128fs, 192fs (Quad Speed Mode)THD+N: -94dBDynamic Range: 106dB Power supply: 4.5 to 5.5VVery Small Package: 16pin TSSOP (6.4mm x 5.0mm)LRCK BICK SDTIMCLK AOUTLAOUTRVDDVSS VCOM SMUTE/CSN ACKS/CCLK DIF0/CDTIDZFRDZFLOrdering GuideAK4384ET -20 ∼ +85°C 16pin TSSOP (0.65mm pitch) AK4384VT -40 ∼ +85°C 16pin TSSOP (0.65mm pitch) AKD4384 Evaluation Board for AK4384Pin LayoutMCLKLRCKBICKSMUTE/CSN ACKS/CCLK DIF0/CDTI DZFL DZFRVSS VDD VCOM AOUTL AOUTR P/SPDNSDTIPIN/FUNCTIONNo. PinName I/O Function1 MCLK I Master Clock Input PinAn external TTL clock should be input on this pin.2 BICK I Audio Serial Data Clock Pin3 SDTI I Audio Serial Data Input Pin4 LRCK I L/RClockPin5 PDN I Power-DownModePinWhen at “L”, the AK4384 is in the power-down mode and is held in reset. TheThe AK4384 must be reset once upon power-up.SMUTE I Soft Mute Pin in parallel mode“H”: Enable, “L”: Disable6CSN I Chip Select Pin in serial modeACKS I Auto Setting Mode Pin in parallel mode“L”: Manual Setting Mode, “H”: Auto Setting Mode 7CCLK I Control Data Clock Pin in serial modeDIF0 I Audio Data Interface Format Pin in parallel mode8CDTI I Control Data Input Pin in serial mode9 P/S I Parallel/Serial Select Pin (Internal pull-up pin)“L”: Serial control mode, “H”: Parallel control mode10 AOUTR O Rch Analog Output Pin11 AOUTL O Lch Analog Output Pin12 VCOM O Common Voltage Pin, VDD/2Normally connected to VSS with a 0.1µF ceramic capacitor in parallel with a10µF electrolytic cap.13 VSS - GroundPin14 VDD - Power Supply Pin15 DZFR O Rch Data Zero Input Detect Pin16 DZFL O Lch Data Zero Input Detect PinNote: All input pins except pull-up pin should not be left floating.ABSOLUTE MAXIMUM RATINGS(VSS=0V; Note 1)maxUnitsminParameter SymbolPower Supply VDD -0.3 6.0 VInput Current (any pins except for supplies) IIN - ±10 mAInput Voltage VIND -0.3 VDD+0.3 VAmbient Operating TemperatureAK4384ET Ta -20 85 °C(Powered applied) AK4384VT Ta -40 85 °CStorage Temperature Tstg -65 150 °CNote: 1. All voltages with respect to ground.WARNING: Operation at or beyond these limits may results in permanent damage to the device.Normal operation is not guaranteed at these extremes.RECOMMENDED OPERATING CONDITIONS(VSS=0V; Note 1)UnitsmaxParameter SymboltypminPower Supply VDD 4.5 5.0 5.5 V*AKM assumes no responsibility for the usage beyond the conditions in this datasheet.ANALOG CHARACTERISTICS(Ta=25°C; VDD=5.0V; fs=44.1kHz; BICK=64fs; Signal Frequency=1kHz; 24bit Input Data;Measurement frequency=20Hz ∼ 20kHz; R L ≥5kΩ; unless otherwise specified)Parameter mintypmaxUnits Resolution24Bits Dynamic Characteristics (Note 3)fs=44.1kHz BW=20kHz 0dBFS-60dBFS-94-42-84-dBdBfs=96kHz BW=40kHz 0dBFS-60dBFS-92-39--dBdBTHD+Nfs=192kHz BW=40kHz 0dBFS-60dBFS-92-39--dBdBDynamic Range (-60dBFS with A-weighted) (Note 4) 100 106 dB S/N (A-weighted) (Note 5) 100 106 dB Interchannel Isolation (1kHz) 90 100 dB Interchannel Gain Mismatch 0.2 0.5 dB DC AccuracyGain Drift 100 - ppm/°C Output Voltage (Note 6) 3.15 3.40 3.65 Vpp Load Resistance (Note 7) 5 kΩPower SuppliesPower Supply Current (VDD)Normal Operation (PDN = “H”, fs≤96kHz)Normal Operation (PDN = “H”, fs=192kHz)Power-Down Mode (PDN = “L”) (Note 8) 1720102732100mAmAµANotes: 3. Measured by Audio Precision (System Two). Refer to the evaluation board manual.4. 100dB at 16bit data.5. S/N does not depend on input bit length.6. Full-scale voltage (0dB). Output voltage scales with the voltage of VREF,AOUT (typ.@0dB) = 3.4Vpp × VDD/5.7. For AC-load.8. All digital inputs including clock pins (MCLK, BICK and LRCK) are held VDD or VSS.SHARP ROLL-OFF FILTER CHARACTERISTICS(Ta = 25°C; VDD = 4.5 ∼ 5.5V; fs = 44.1kHz; DEM = OFF; SLOW = “0”)Parameter SymbolmintypmaxUnits Digital filterPassband ±0.05dB (Note 9) -6.0dB PB 0- 22.0520.0-kHzkHzStopband (Note 9) SB 24.1 kHz Passband Ripple PR ± 0.02 dB Stopband Attenuation SA 54 dB Group Delay (Note 10) GD - 19.3 - 1/fs Digital Filter + LPFFrequency Response 20.0kHz40.0kHz80.0kHz fs=44.1kHzfs=96kHzfs=192kHzFRFRFR---± 0.03± 0.03± 0.03---dBdBdBNotes: 9. The passband and stopband frequencies scale with fs(system sampling rate).For example, PB=0.4535×fs (@±0.05dB), SB=0.546×fs.10. The calculating delay time which occurred by digital filtering. This time is from setting the 16/24bit dataof both channels to input register to the output of analog signal.SLOW ROLL-OFF FILTER CHARACTERISTICS(Ta = 25°C; VDD = 4.5 ~ 5.5V; fs = 44.1kHz; DEM = OFF; SLOW = “1”)Parameter Symbol min typ max Units Digital FilterPassband ±0.04dB (Note 11) -3.0dB PB 0- 18.28.1-kHzkHzStopband (Note 11) SB 39.2 kHz Passband Ripple PR ± 0.005 dB Stopband Attenuation SA 72 dB Group Delay (Note 10) GD - 19.3 - 1/fs Digital Filter + LPFFrequency Response 20.0kHz40.0kHz80.0kHz fs=44.kHzfs=96kHzfs=192kHzFRFRFR---+0.02/-5+0.02/-4+0.02/-5---dBdBdBNote: 11. The passband and stopband frequencies scale with fs.For example, PB = 0.185×fs (@±0.04dB), SB = 0.888×fs.DC CHARACTERISTICS(Ta=25°C; VDD=4.5 ∼ 5.5V)Parameter SymbolmintypmaxUnitsHigh-Level Input Voltage Low-Level Input Voltage VIHVIL2.2----0.8VVHigh-Level Output Voltage (Iout=-80µA) Low-Level Output Voltage (Iout=80µA) VOHVOLVDD-0.4-- -0.4VVInput Leakage Current (Note 12) Iin - - ± 10 µA Note: 12. P/S pin has internal pull-up device, normally 100kΩ.SWITCHING CHARACTERISTICS(Ta=25°C; VDD=4.5 ∼ 5.5V)Parameter SymbolmintypmaxUnitsMaster Clock FrequencyDuty Cycle fCLKdCLK2.0484011.2896 36.86460MHz%LRCK FrequencyNormal Speed Mode Double Speed Mode Quad Speed Mode Duty CyclefsnfsdfsqDuty86012045489619255kHzkHzkHz%Audio Interface Timing BICK PeriodNormal Speed ModeDouble/Quad Speed ModeBICK Pulse Width LowPulse Width HighBICK rising to LRCK Edge (Note 13) LRCK Edge to BICK rising (Note 13) SDTI Hold TimeSDTI Setup TimetBCKtBCKtBCKLtBCKHtBLRtLRBtSDHtSDS1/128fs1/64fs303020202020nsnsnsnsnsnsnsnsControl Interface TimingCCLK PeriodCCLK Pulse Width Low Pulse Width High CDTI Setup TimeCDTI Hold TimeCSN “H” TimeCSN “↓” to CCLK “↑” CCLK “↑” to CSN “↑” tCCKtCCKLtCCKHtCDStCDHtCSWtCSStCSH200808040401505050nsnsnsnsnsnsnsnsReset TimingPDN Pulse Width (Note 14)tPD 150 ns Notes: 13. BICK rising edge must not occur at the same time as LRCK edge.14. The AK4384 can be reset by bringing PDN= “L”.Timing DiagramVIHMCLKVILVIH LRCKVILVIH BICKVILClock TimingLRCKVIH BICKVILVIH SDTIVIL VIH VILSerial Interface TimingCSNVIH CCLKVILVIH CDTI VILVIHVILWRITE Command Input TimingCSNVIH CCLKVILVIH CDTI VILVIHVILD3D2D1D0WRITE Data Input TimingVILPDNPower-down TimingOPERATION OVERVIEWSystem ClockThe external clocks, which are required to operate the AK4384, are MCLK, LRCK and BICK. The master clock (MCLK)should be synchronized with LRCK but the phase is not critical. The MCLK is used to operate the digital interpolationfilter and the delta-sigma modulator. There are two methods to set MCLK frequency. In Manual Setting Mode (ACKS =“0”: Register 00H), the sampling speed is set by DFS0/1(Table 1). The frequency of MCLK at each sampling speed is setautomatically. (Table 2~4).After exiting reset (PDN = “↑”), the AK4384 is in Auto Setting Mode. In Auto Setting Mode(ACKS = “1”: Default), as MCLK frequency is detected automatically (Table 5), and the internal master clock becomesthe appropriate frequency (Table 6), it is not necessary to set DFS0/1.In parallel mode, the sampling speed can be set by ACKS pin. The internal DFS0 andDFS1 bits are fixed to “0”.Therefore, when ACKS pin is “L”, the AK4384 operates in Normal Speed Mode. The AK4384 operates in Auto SettingMode at ACKS = “H”. In parallel mode, the AK4384 does not support 128fs and 192fs of Double Speed Mode.All external clocks (MCLK,BICK and LRCK) should always be present whenever the AK4384 is in the normal operationmode (PDN= ”H”). If these clocks are not provided, the AK4384 may draw excess current and may fall into unpredictableoperation. This is because the device utilizes dynamic refreshed logic internally. The AK4384 should be reset by PDN=“L” after threse clocks are provided. If the external clocks are not present, the AK4384 should be in the power-downmode (PDN= “L”). After exiting reset at power-up etc., the AK4384 is in the power-down mode until MCLK and LRCKare input.(fs)RateDFS1 DFS0 Sampling0 0 Normal Speed Mode 8kHz~48kHz Default0 1 Double Speed Mode 60kHz~96kHzSpeedMode 120kHz~192kHzQuad1 0Table 1. Sampling Speed (Manual Setting Mode)LRCK MCLK BICK fs 256fs 384fs 512fs 768fs 1152fs 64fs32.0kHz 8.1920MHz 12.2880MHz16.3840MHz24.5760MHz36.8640MHz 2.0480MHz44.1kHz 11.2896MHz 16.9344MHz22.5792MHz33.8688MHz N/A 2.8224MHz48.0kHz 12.2880MHz 18.4320MHz24.5760MHz36.8640MHz N/A 3.0720MHzTable 2. System Clock Example (Normal Speed Mode @Manual Setting Mode)LRCK MCLK BICKfs 128fs 192fs 256fs 384fs 64fs88.2kHz 11.2896MHz 16.9344MHz22.5792MHz33.8688MHz 5.6448MHz96.0kHz 12.2880MHz 18.4320MHz24.5760MHz36.8640MHz 6.1440MHzTable 3. System Clock Example (Double Speed Mode @Manual Setting Mode)LRCK MCLK BICK fs 128fs 192fs 64fs 176.4kHz 22.5792MHz 33.8688MHz 11.2896MHz 192.0kHz 24.5760MHz 36.8640MHz 12.2880MHzTable 4. System Clock Example (Quad Speed Mode @Manual Setting Mode)MCLK Sampling Speed 512fs 768fs Normal 256fs 384fs Double 128fs 192fs QuadTable 5. Sampling Speed (Auto Setting Mode: Default)LRCK MCLK (MHz) fs 128fs 192fs 256fs 384fs 512fs 768fs 1152fsSamplingSpeed 32.0kHz - - - - 16.3840 24.5760 36.8640 44.1kHz - - - - 22.5792 33.8688 - 48.0kHz - - - - 24.5760 36.8640 - Normal 88.2kHz - - 22.579233.8688 - - -96.0kHz - - 24.576036.8640 - - - Double176.4kHz 22.5792 33.8688 - - - - -192.0kHz 24.5760 36.8640 - - - - -QuadTable 6. System Clock Example (Auto Setting Mode)Audio Serial Interface FormatData is shifted in via the SDTI pin using BICK and LRCK inputs. The DIF0-2 as shown in Table 7 can select five serial data modes. In all modes the serial data is MSB-first, 2’s compliment format and is latched on the rising edge of BICK. Mode 2 can be used for 16/20 MSB justified formats by zeroing the unused LSBs.Mode DIF2 DIF1 DIF0SDTI Format BICK Figure 0 0 0 0 16bit LSB Justified ≥32fs Figure 1 1 0 0 1 20bit LSB Justified ≥40fs Figure 2 2 0 1 0 24bit MSB Justified ≥48fsFigure 3 Default 3 0 1 1 24bit I 2S Compatible ≥48fs Figure 4 4 1 0 0 24bit LSB Justified ≥48fs Figure 2Table 7. Audio Data Formats (Serial mode)Mode DIF0 SDTI Format BICK Figure 2 0 24bit MSB Justified ≥48fs Figure 3 3 1 24bit I 2S Compatible ≥48fsFigure 4Table 8. Audio Data Formats (Parallel mode)SDTI BICKLRCKSDTIBICK (32fs)(64fs)Mode 0Mode 0Figure 1. Mode 0 TimingSDTILRCK BICK (64fs)Mode 1SDTI Mode 4Figure 2. Mode 1,4 TimingLRCKBICK (64fs)SDTIFigure 3. Mode 2 TimingBICK(64fs)SDTIFigure 4. Mode 3 TimingDe-emphasis FilterA digital de-emphasis filter is available for 32, 44.1 or 48kHz sampling rates (tc = 50/15µs) and is enabled or disabled with DEM0 and DEM1. In case of double speed and quad speed mode, the digital de-emphasis filter is always off.DEM1DEM0Mode44.1kHz0 0Default0 1 OFF1 0 48kHz1 1 32kHzTable 9. De-emphasis Filter Control (Normal Speed Mode)Output VolumeThe AK4384 includes channel independent digital output volumes (ATT) with 256 levels at linear step including MUTE. These volumes are in front of the DAC and can attenuate the input data from 0dB to –48dB and mute. When changing levels, transitions are executed via soft changes; thus no switching noise occurs during these transitions. The transition time of 1 level and all 256 levels is shown in Table 10.Transition TimeSampling Speed1 Level 255 to 0Normal Speed Mode 4LRCK 1020LRCKDouble Speed Mode 8LRCK 2040LRCKQuad Speed Mode 16LRCK 4080LRCKTable 10. ATT Transition TimeThe AK4384 has channel-independent zeros detect function. When the input data at each channel is continuously zeros for 8192 LRCK cycles, DZF pin of each channel goes to “H”. DZF pin of each channel immediately goes to “L” if input data of each channel is not zero after going DZF “H”. If RSTN bit is “0”, DZF pins of both channels go to “H”. DZF pin of both channels go to “L” at 2~3/fs after RSTN bit returns to “1”. If DZFM bit is set to “1”, DZF pins of both channels go to “H” only when the input data at both channels are continuously zeros for 8192 LRCK cycles. Zero detect function can be disabled by DZFE bit. In this case, DZF pins of both channels are always “L”. DZFB bit can invert the polarity of DZF pin.Soft Mute OperationSoft mute operation is performed at digital domain. When the SMUTE bit goes to “1”, the output signal is attenuated by -∞ during ATT_DATA×ATT transition time (Table 10) from the current ATT level. When the SMUTE bit is returned to “0”, the mute is cancelled and the output attenuation gradually changes to the ATT level during ATT_DATA×ATT transition time. If the soft mute is cancelled before attenuating to -∞ after starting the operation, the attenuation is discontinued and returned to ATT level by the same cycle. The soft mute is effective for changing the signal source without stopping the signal transmission.SMUTE bit AttenuationDZF pin-AOUTNotes:(1) ATT_DATA×ATT transition time (Table 10). For example, in Normal Speed Mode, this time is 1020LRCK cycles(1020/fs) at ATT_DATA=255.(2) The analog output corresponding to the digital input has a group delay, GD.(3) If the soft mute is cancelled before attenuating to -∞ after starting the operation, the attenuation is discontinued andreturned to ATT level by the same cycle.(4) When the input data at each channel is continuously zeros for 8192 LRCK cycles, DZF pin of each channel goes to“H”. DZF pin immediately goes to “L” if input data are not zero after going DZF “H”.Figure 5. Soft Mute and Zero DetectionThe AK4384 should be reset once by bringing PDN= “L” upon power-up. The AK4384 is powered up and the internal timing starts clocking by LRCK “↑” after exiting reset and power down state by MCLK. The AK4384 is in the power-down mode until MCLK and LRCK are input.Power-downThe AK4384 is placed in the power-down mode by bringing PDN pin “L” and the anlog outputs are floating (Hi-Z). Figure 6 shows an example of the system timing at the power-down and power-up.Internal State PDN D/A Out (Analog)D/A In (Digital)Clock InDZFL/DZFR External MUTE(5)Mute ONNotes:(1) The analog output corresponding to digital input has the group delay (GD). (2) Analog outputs are floating (Hi -Z) at the power-down mode.(3) Click noise occurs at the edge of PDN signal. This noise is output even if “0” data is input.(4) The external clocks (MCLK, BICK and LRCK) can be stopped in the power-down mode (PDN = “L”). (5) Please mute the analog output externally if the click noise (3) influences system application.The timing example is shown in this figure.(6) DZF pins are “L” in the power-down mode (PDN = “L”).Figure 6. Power-down/up Sequence ExampleWhen RSTN=0, DAC is powered down but the internal register values are not initialized. The analog outputs go to VCOM voltage and DZFL/DZFR pins go to “H”. Figure 7 shows the example of reset by RSTN bit.Internal State RSTN bitD/A Out (Analog)D/A In (Digital)Clock InMCLK,LRCK,BICKDZFInternal RSTN bitNotes:(1) The analog output corresponding to digital input has the group delay (GD). (2) Analog outputs go to VCOM voltage (VDD/2).(3) Click noise occurs at the edges(“↑ ↓”) of the internal timing of RSTN bit. This noise is output even if “0” data isinput.(4) The external clocks (MCLK, BICK and LRCK) can be stopped in the reset mode (RSTN = “L”).(5) DZF pins go to “H” when the RSTN bit becomes “0”, and go to “L” at 2/fs after RSTN bit becomes “1”.(6) There is a delay, 3~4/fs from RSTN bit “0” to the internal RSTN bit “0”, and 2~3/fs from RSTN bit “1” to theinternal RSTN “1”.Figure 7. Reset Sequence ExampleMode Control InterfaceSome function of the AK4384 can be controlled by pins (parallel control mode) shown in Table 11. The serial control interface is enabled by the P/S pin = “L”. Internal registers may be written by 3-wire µP interface pins, CSN, CCLK and CDTI. The data on this interface consists of Chip Address (2bits, C1/0; fixed to “01”), Read/Write (1bit; fixed to “1”, Write only), Register Address (MSB first, 5bits) and Control Data (MSB first, 8bits). AK4384 latches the data on the rising edge of CCLK, so data should clocked in on the falling edge. The writing of data becomes valid by CSN “↑”. The clock speed of CCLK is 5MHz (max).Function Parallel mode Serial mode Double sampling mode at 128/192fs X ODe-emphasis X O SMUTE O O Zero Detection X O 16/20/24bit LSB justified format X OTable 11. . Function list (O: available, X: not available)PDN = “L” resets the registers to their default values. When the state of P/S pin is changed, the AK4384 should be reset by PDN= “L”. The internal timing circuit is reset by RSTN bit, but the registers are not initialized.CDTICCLKCSN123456789101112131415C1-C0: Chip Address (Fixed to “01”)R/W: READ/WRITE (Fixed to “1”, Write only) A4-A0: Register Address D7-D0: Control DataFigure 8. Control I/F Timing*The AK4384 does not support the read command and chip address. C1/0 and R/W are fixed to “011”*When the AK4384 is in the power down mode (PDN = “L”) or the MCLK is not provided, writing into the control register is inhibited.Register MapAddr Register Name D7 D6 D5 D4 D3 D2 D1 D0 00H Control 1 ACKS 0 0DIF2 DIF1 DIF0 PW RSTN 01H Control 2 DZFE DZFM SLOW DFS1 DFS0 DEM1 DEM0 SMUTE 02H Control 3 0 0 0 INVL INVR DZFB 0 003H Lch ATT ATT7 ATT6 ATT5 ATT4 ATT3 ATT2 ATT1 ATT0 04H Rch ATTATT7 ATT6 ATT5ATT4 ATT3 ATT2 ATT1 ATT0Notes:For addresses from 05H to 1FH, data must not be written.When PDN pin goes “L”, the registers are initialized to their default values.When RSTN bit goes “0”, the only internal timing is reset and the registers are not initialized to their default values. All data can be written to the register even if PW or RSTN bit is “0”.Register DefinitionsName D7 D6 D5 D4 D3 D2 D1 D0Addr Register00H Control 1 ACKS 0 0 DIF2 DIF1 DIF0 PW RSTN111default 1RSTN: Internal timing reset control0: Reset. All registers are not initialized.1: Normal OperationWhen MCLK frequency or DFS changes, the click noise can be reduced by RSTN bit.PW: Power down control0: Power down. All registers are not initialized.1: Normal OperationDIF2-0: Audio data interface formats (see Table 7)Initial: “010”, Mode 2ACKS: Master Clock Frequency Auto Setting Mode Enable0: Disable, Manual Setting Mode1: Enable, Auto Setting ModeMaster clock frequency is detected automatically at ACKS bit “1”. In this case, the setting of DFS1-0are ignored. When this bit is “0”, DFS1-0 set the sampling speed mode.Name D7 D6 D5 D4 D3 D2 D1 D0Addr Register01H Control 2 DZFE DZFM SLOW DFS1 DFS0 DEM1 DEM0 SMUTE1default 0SMUTE: Soft Mute Enable0: Normal operation1: DAC outputs soft-mutedDEM1-0: De-emphasis Response (see Table 9)Initial: “01”, OFFDFS1-0: Sampling speed control00: Normal speed01: Double speed10: Quad speedWhen changing between Normal/Double Speed Mode and Quad Speed Mode, some click noiseoccurs.SLOW: Slow Roll-off Filter Enable0: Sharp Roll-off Filter1: Slow Roll-off FilterDZFE: Data Zero Detect Enable0: Disable1: EnableZero detect function can be disabled by DZFE bit “0”. In this case, the DZF pins of both channels arealways “L”.DZFM: Data Zero Detect Mode0: Channel Separated Mode1: Channel ANDed ModeIf the DZFM bit is set to “1”, the DZF pins of both channels go to “H” only when the input data at bothchannels are continuously zeros for 8192 LRCK cycles.Name D7 D6 D5 D4 D3 D2 D1 D0Addr Register02H Control 3 0 0 0 INVL INVR DZFB 0 0default 0DZFB: Inverting Enable of DZF0: DZF goes “H” at Zero Detection1: DZF goes “L” at Zero DetectionINVR: Inverting Lch Output Polarity0: Normal Output1: Inverted OutputINVL: Inverting Rch Output Polarity0: Normal Output1: Inverted OutputName D7 D6 D5 D4 D3 D2 D1 D0Addr Register03H Lch ATT ATT7 ATT6 ATT5 ATT4 ATT3 ATT2 ATT1 ATT004H Rch ATT ATT7 ATT6 ATT5 ATT4 ATT3 ATT2 ATT1 ATT011111default 111ATT = 20 log(ATT_DATA / 255) [dB]1000H: MuteSYSTEM DESIGNFigure 9 and 10 show the system connection diagram. An evaluation board (AKD4384) is available in order to allow an easy study on the layout of a surrounding circuit.Figure 9. Typical Connection Diagram (Parallel Mode)Figure 10. Typical Connection Diagram (Serial Mode)Notes:- LRCK = fs, BICK = 64fs.- When AOUT drives some capacitive load, some resistor should be added in series between AOUT andcapacitive load.- All input pins except pull-up pin should not be left floating.1. Grounding and Power Supply DecouplingVDD and VSS are supplied from analog supply and should be separated from system digital supply. Decoupling capacitor, especially 0.1µF ceramic capacitor for high frequency should be placed as near to VDD as possible. The differential Voltage between VDD and VSS pins set the analog output range.2. Analog OutputsThe analog outputs are single-ended and centered around the VCOM voltage. The output signal range is typically3.40Vpp (typ@VDD=5V). The phase of the analog outputs can be inverted channel independently by INVL/INVR bits. The internal switched-capacitor filter and continuous-time filter attenuate the noise generated by the delta-sigmamodulator beyond the audio passband. The output voltage is a positive full scale for 7FFFFFH (@24bit) and a negative full scale for 800000H (@24bit). The ideal output is VCOM voltage for 000000H (@24bit).DC offsets on analog outputs are eliminated by AC coupling since analog outputs have DC offsets of VCOM + a few mV. Figure 11 shows an example of the external LPF with 2Vrms output.AOUTfc=111.8kHz, Q=0.714, g=-0.04dB at 40kHzAnalog OutFigure 11. External 2nd order LPF Circuit Example (using op-amp with dual power supplies)PACKAGE 16pin TSSOP (Unit: mm)Package & Lead frame materialPackage molding compound: EpoxyLead frame material: CuLead frame surface treatment: Solder(Pb free) plateAKM4384VTXXYYY1) Pin #1 indication2) Date Code : XXYYY (5 digits)XX: Lot#YYY: Date Code3) Marketing Code : 4384VT4) Asahi Kasei LogoAKM4384ETXXYYY5) Pin #1 indication6) Date Code : XXYYY (5 digits)XX: Lot#YYY: Date Code7) Marketing Code : 4384ET8) Asahi Kasei LogoRevision HistoryDate (YY/MM/DD) Revision Reason Page Contents 02/09/11 00 First Edition 2 Ordering GuideAK4384ET was added.06/01/11 01 Spec Addition 23 MARKINGAK4384ET was added.IMPORTANT NOTICE• These products and their specifications are subject to change without notice. Before considering any use or application, consult the Asahi Kasei Microsystems Co., Ltd. (AKM) sales office or authorized distributor concerning their current status.• AKM assumes no liability for infringement of any patent, intellectual property, or other right in the application or use of any information contained herein.• Any export of these products, or devices or systems containing them, may require an export license or other official approval under the law and regulations of the country of export pertaining to customs and tariffs, currency exchange, or strategic materials.• AKM products are neither intended nor authorized for use as critical components in any safety, life support, or other hazard related device or system, and AKM assumes no responsibility relating to any such use, except with the express written consent of the Representative Director of AKM. As used here:(a) A hazard related device or system is one designed or intended for life support or maintenance ofsafety or for applications in medicine, aerospace, nuclear energy, or other fields, in which its failure to function or perform may reasonably be expected to result in loss of life or in significant injury or damage to person or property.(b) A critical component is one whose failure to function or perform may reasonably be expected toresult, whether directly or indirectly, in the loss of the safety or effectiveness of the device or system containing it, and which must therefore meet very high standards of performance and reliability.• It is the responsibility of the buyer or distributor of an AKM product who distributes, disposes of, or otherwise places the product with a third party to notify that party in advance of the above content and conditions, and the buyer or distributor agrees to assume any and all responsibility and liability for and hold AKM harmless from any and all claims arising from the use of said product in the absence of such notification.。

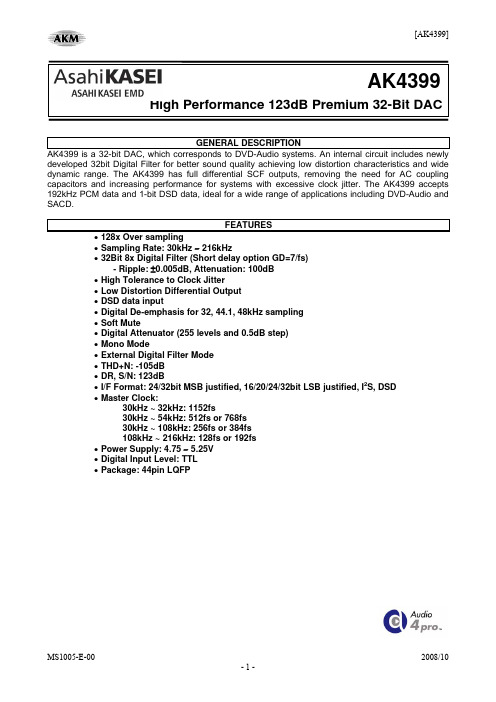

AK4399中文资料

No internal bonding.

-

Connect to GND.

Right channel Common Voltage Pin,

-

Normally connected to VSS with a 10uF electrolytic cap.

O Rch Positive Analog Output Pin

I Control Data Input Pin in Serial Control Mode

I Digital Input Format 0 Pin in PCM Mode

I Chip Address 1 Pin in Serial Control Mode

I Digital Input Format 1 Pin in PCM Mode

No internal bonding.

-

Connect to GND.

I Rch Audio Serial Data Input Pin

(Internal pull-down pin)

I Lch Audio Serial Data Input Pin

(Internal pull-down pin)

36 NC

37 NC

38 NC

39 NC 40 VSS3 41 AVDD 42 MCLK 43 VSS4 44 NC

Parallel or Serial Select Pin

(Internal pull-up pin)

I

“L”: Serial Control Mode, “H”: Parallel Control Mode

13 NC

I/O

Function

- Digital Power Supply Pin, 4.75 ∼ 5.25V

CS5381-KZZ;CS5381-KSZ;CS5381-KZZR;CS5381-KSZR;中文规格书,Datasheet资料

192 kHz ! 260 mW Power Consumption ! High-Pass Filter or DC Offset Calibration ! Supports Logic Levels between 5 and 2.5 V ! Differential Analog Architecture ! Low-Latency Digital Filtering ! Overflow Detection ! Pin-Compatible with the CS5361

Analog Supply 5V

Digital Supply 3.3 V to 5 V

Interface Supply 2.5 V to 5 V

Differential Inputs

Differential Inputs

Internal Voltage Reference

Switch-Cap ADC

Switch-Biblioteka ap ADCDigital Filters

Digital Filters

Level Translator

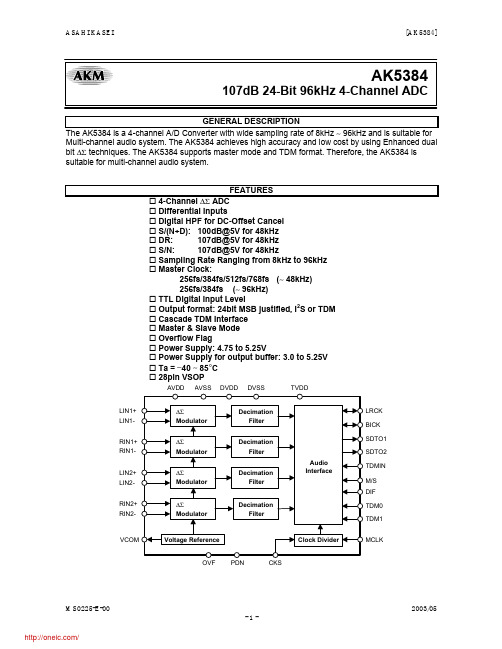

AK5384VF中文资料

AK5384VF中⽂资料GENERAL DESCRIPTIONThe AK5384 is a 4-channel A/D Converter with wide sampling rate of 8kHz ~ 96kHz and is suitable for Multi-channel audio system. The AK5384 achieves high accuracy and low cost by using Enhanced dual bit ?Σ techniques. The AK5384 supports master mode and TDM format. Therefore, the AK5384 is suitable for multi-channel audio system.FEATURESo 4-Channel ?Σ ADC o Differential Inputso Digital HPF for DC-Offset Cancel o S/(N+D): 100dB@5V for 48kHz o DR: 107dB@5V for 48kHz o S/N: 107dB@5V for48kHzo Sampling Rate Ranging from 8kHz to 96kHz o Master Clock:256fs/384fs/512fs/768fs (~ 48kHz) 256fs/384fs (~ 96kHz)o TTL Digital Input Levelo Output format: 24bit MSB justified, I 2S or TDM o Cascade TDM Interface o Master & Slave Mode o Overflow Flago Power Supply: 4.75 to 5.25Vo Power Supply for output buffer: 3.0 to 5.25V o Ta = ?40 ~ 85°C o 28pin VSOPLIN1-LRCK BICK SDTO1VCOM AVSSAVDDDVSSDVDDPDNLIN1+RIN1-RIN1+LIN2-LIN2+RIN2-RIN2+SDTO2DIF TDM0M/S MCLKCKSOVFn Ordering GuideAK5384VF ?40 ~ +85°C 28pin VSOP (0.65mm pitch) AKD5384 Evaluation Board for AK5384n Pin LayoutRIN2+RIN2-AVSS AVDD LIN2+LIN2-TEST VCOM TDM1TDM0TDMIN MCLK OVFDIF Top View876543212122232425262728RIN1+RIN1-PDN CKS M/S LIN1-LIN1+91011121314181920TVDD 151617LRCKBICK SDTO2DVDD DVSS SDTO1PIN/FUNCTIONNo. Pin Name I/O Function1 LIN2+ I ADC2 Lch Positive Analog Input Pin2 LIN2?I ADC2 Lch Negative Analog Input Pin3 RIN2+ I ADC2 Rch Positive Analog Input Pin4 RIN2?I ADC2 Rch Negative Analog Input Pin5 TEST I Test Pin (Connected to AVSS)6 VCOM O Common Voltage Output Pin, AVDD/2Normally connected to AVSS with a 0.1µF ceramic capacitor in parallel with an electrolytic capacitor less than 2.2µF.7 AVSS - Analog Ground Pin8 AVDD - Analog Power Supply Pin, 4.75 ~ 5.25V9 DIF I Audio Interface Format Pin“L” : 24bit MSB justified, “H” : 24bit I2S Compatible10 TDM1 I TDM I/F BICK Frequency Select Pin “L” : 256fs, “H” : 128fs11 TDM0 I TDM I/F Format Enable Pin“L” : Normal Mode, “H” : TDM Mode12 TDMIN I TDM Data Input Pin13 MCLK I Master Clock Input Pin14 OVF O Analog Input Overflow Detect PinThis pin goes to “H” if one of four analog inputs overflows.15 LRCK I/O Output Channel Clock Pin“L” Output in Master Mode at Power-down mode.17 SDTO2 O ADC2 Audio Serial Data Output Pin “L” Output at Power-down mode.18 SDTO1 O ADC1 Audio Serial Data Output Pin “L” Output at Power-down mode.19 TVDD - Output Buffer Power Supply Pin, 3.0 ~ 5.25V20 DVDD - Digital Power Supply Pin, 4.75 ~ 5.25V21 DVSS - Digital Ground Pin22 PDN I Power-Down Mode PinWhen “L”, the circuit is in power-down mode.The AK5384 should always be reset upon power-up.23 CKS I Master Clock Select Pin“L” : 256fs, “H” : 512fsThis pin is enabled in Master Mode.24 M/S I Master / Slave Mode Pin“L” : Slave Mode, “H” : Master Mode25 RIN1?I ADC1 Rch Negative Analog Input Pin26 RIN1+ I ADC1 Rch Positive Analog Input Pin27 LIN1?I ADC1 Lch Negative Analog Input Pin28 LIN1+ I ADC1 Lch Positive Analog Input Pin Note: All digital input pins should not be left floating. ABSOLUTE MAXIMUM RATINGS(AVSS, DVSS=0V; Note 1)Parameter Symbol min max UnitsPower Supplies: AnalogDigitalOutput buffer|AVSS – DVSS| (Note 2) AVDDDVDDTVDDGND0.30.30.3-6.06.0VInput Current, Any Pin Except Supplies IIN - ±10 mA Analog Input Voltage VINA ?0.3 AVDD+0.3 V Digital Input Voltage (Except BICK, LRCK pins) (BICK, LRCK pins) VIND1VIND20.30.3DVDD+0.3TVDD+0.3VVAmbient Temperature (Powered applied) Ta ?40 85 °C Storage Temperature Tstg ?65 150 °CNote 1. All voltages with respect to ground.Note 2. AVSS and DVSS must be connected to the same analog ground plane.WARNING: Operation at or beyond these limits may result in permanent damage to the device.Normal operation is not guaranteed at these extremes.RECOMMENDED OPERATING CONDITIONS(AVSS, DVSS=0V; Note 1)Parameter Symbol min typ max UnitsPower Supplies (Note 3) AnalogDigitalOutput buffer AVDDDVDDTVDD4.754.753.05.05.05.05.25Note 1. All voltages with respect to ground.Note 3. The power up sequence between AVDD, DVDD and TVDD is not critical. WARNING: AKM assumes no responsibility for the usage beyond the conditions in this datasheet.ANALOG CHARACTERISTICS(Ta=25°C; AVDD=DVDD=TVDD=5.0V; AVSS=DVSS=0V; fs=48kHz, 96kHz; I/F format=Mode 0;Signal Frequency=1kHz; Measurement frequency=20Hz ~ 20kHz at fs=48kHz, 40Hz ~ 40kHz at fs=96kHz; unless otherwise specified)Parameter min typ max Units ADC Analog Input Characteristics:Resolution 24 BitsS/(N+D) (?1dBFS) fs=48kHzfs=96kHz 888210094dBdBDR (?60dBFS) fs=48kHz, A-weightedfs=96kHz 10094107102dBdBS/N fs=48kHz, A-weightedfs=96kHz 10094107102dBdBInterchannel Isolation 90 110 dB DC Accuracy:11 2616k?k?Power Supply Rejection (Note 5) 50 - dB Power SuppliesPower Supply Current (AVDD+DVDD+TVDD)Normal Operation (PDN pin = “H”, fs=48kHz) (Note 6) Normal Operation (PDN pin = “H”, fs=96kHz) (Note 6) Power-down mode (PDN pin = “L”) (Note 7) 4355106583100mAmAµANote 4. This value is the full scale (0dB) of the input voltage. This voltage is input to LIN(RIN)+ and LIN(RIN)? pin, and is proportional to AVDD. (Vin = 0.58 × AVDD)Note 5. PSR is applied to AVDD, DVDD and TVDD with 1kHz, 50mVpp.Note 6. AVDD=28mA; DVDD=15mA@48kHz&5V, DVDD=26mA@96kHz&5V(typ).Note 7. All digital input pins are fixed to DVDD or DVSS.FILTER CHARACTERISTICS (fs=48kHz)(Ta=25°C; AVDD, DVDD=4.75 ~ 5.25V; TVDD=3.0 ~ 5.25V; fs=48kHz)Parameter Symbol min typ max Units ADC Digital Filter (Decimation LPF):Passband (Note 8) ?0.005dB0.02dB0.06dB6.0dB PB 0---21.76822.024.0-kHzkHzkHzkHzStopband (Note 8) SB 26.5 kHz Passband Ripple PR ±0.005 dB Stopband Attenuation SA 80 dB Group Delay (Note 9) GD 27.6 1/fs Group Delay Distortion ?GD 0 µs ADC Digital Filter (HPF):Frequency Response (Note 8) ?3dB0.5dB0.1dB FR 1.02.96.5HzHzHzFILTER CHARACTERISTICS (fs=96kHz)(Ta=25°C; AVDD, DVDD=4.75 ~ 5.25V; TVDD=3.0 ~ 5.25V; fs=96kHz)Parameter Symbol min typ max Units ADC Digital Filter (Decimation LPF):Passband (Note 8) ?0.005dB0.02dB0.06dB6.0dB PB 0---43.53644.048.043.0---kHzStopband (Note 8) SB 53.0 kHz Passband Ripple PR ±0.005 dB Stopband Attenuation SA 80 dB Group Delay (Note 9) GD 27.6 1/fs Group Delay Distortion ?GD 0 µs ADC Digital Filter (HPF):Frequency Response (Note 8) ?3dB0.5dB0.1dB FR 2.05.813.0HzHzHzNote 8. The passband and stopband frequencies scale with fs.Note 9. The calculated delay time induced by digital filtering. This time is from the input of an analog signalto the setting of 24bit data both channels to the ADC output register for ADC.DC CHARACTERISTICS(Ta=25°C; AVDD, DVDD=4.75 ~ 5.25V; TVDD=3.0 ~ 5.25V)Parameter Symbol min typ max UnitsHigh-Level Input Voltage (TVDD=3.0 ~ 3.6V) Low-Level Input Voltage (TVDD=3.0 ~ 3.6V) High-Level Input Voltage (TVDD=3.6 ~ 5.25V) Low-Level Input Voltage (TVDD=3.6 ~ 5.25V) VIHVILVIHVIL2.2-2.7------0.8-0.5VHigh-Level Output Voltage (Iout=?100µA) Low-Level Output Voltage (Iout=100µA) VOH VOLTVDD-0.5----0.5VVInput Leakage Current Iin - - ±10 µASWITCHING CHARACTERISTICS(Ta=25°C; AVDD, DVDD=4.75 ~ 5.25V; TVDD=3.0 ~ 5.25V; C L=20pF) Parameter Symbol min typ max Units Master Clock TimingMaster Clock 256fs:Pulse Width Low Pulse Width High 384fs:Pulse Width Low Pulse Width High 512fs:Pulse Width Low Pulse Width High 768fs:Pulse Width Low Pulse Width HighfCLKtCLKLtCLKHfCLKtCLKLtCLKHfCLKtCLKLtCLKHfCLKtCLKLtCLKH3.07211114.09616166.144111112.28818.43224.57636.86424.57636.86424.57636.864MHznsnsMHznsnsMHznsnsMHznsnsLRCK Timing (Slave Mode) Normal mode (TDM1=“L”, TDM0=“L”) LRCK Frequency Duty Cycle9655kHz%TDM256 MODE (TDM1=“L”, TDM0=“H”) LRCK Frequency “H” time“L” timefstLRHtLRL81/256fs1/256fs48 kHznsnsTDM128 MODE (TDM1=“H”, TDM0=“H”) LRCK Frequency “H” time“L” timefstLRHtLRL81/128fs1/128fs96 kHznsnsLRCK Timing (Master Mode)Normal mode (TDM1=“L”, TDM0=“L”) LRCK Frequency Duty Cycle96 kHz%TDM256 MODE (TDM1=“L”, TDM0=“H”)LRCK Frequency“H” time (Note 10)fstLRH81/8fs48 kHznsTDM128 MODE (TDM1=“H”, TDM0=“H”)LRCK Frequency“H” time (Note 10)fstLRH81/4fs96 kHznsNote 10. “L” time at I2S format.Parameter Symbol min typ max Units Audio Interface Timing (Slave mode)Normal mode (TDM1=“L”, TDM0=“L”)BICK PeriodBICK Pulse Width LowPulse Width HighLRCK Edge to BICK “↑” (Note 11) BICK “↑” to LRCK Edge (Note 11) LRCK to SDTO1/2 (MSB) (Except I2S mode) BICK “↓”to SDTO1/2tBCKtBCKLtBCKHtLRB6530303535nsnsnsnsnsnsnsTDM256 mode (TDM1=“L”, TDM0=“H”)BICK PeriodBICK Pulse Width LowPulse Width HighLRCK Edge to BICK “↑” (Note 11) BICK “↑” to LRCK Edge (Note 11) BICK “↓” to SDTO1/2 tBCKtBCKLtBCKHtLRBtBLRtBSD813232202020nsTDM128 mode (TDM1=“H”, TDM0=“H”)BICK PeriodBICK Pulse Width LowPulse Width HighLRCK Edge to BICK “↑” (Note 11) BICK “↑” to LRCK Edge (Note 11) BICK “↓” to SDTO1 (Note 12) tBCKtBCKLtBCKHtLRBtBLRtBSD813232202020nsnsnsnsnsnsAudio Interface Timing (Master mode) Normal mode (TDM1=“L”, TDM0=“L”)BICK Frequency BICK DutyBICK “↓” to LRCK BICK “↓” to SDTO1/2fBCKdBCKtMBLRtBSD40Hz%nsnsTDM256 mode (TDM1=“L”, TDM0=“H”) BICK FrequencyBICK Duty (Note 13) BICK “↓” to LRCK BICK “↓” to SDTO1/2fBCKdBCKtMBLRtBSD1220256fs501220Hz%nsnsTDM128 mode (TDM1=“H”, TDM0=“H”) BICK FrequencyBICK DutyBICK “↓” to LRCKBICK “↓” to SDTO1 (Note 12)fBCKdBCK501220Hz%nsnsPower-Down & Reset TimingPDN Pulse Width (Note 14) PDN “↑” to SDTO1/2 valid (Note 15)tPDtPDV150516ns1/fsNote 11. BICK rising edge must not occur at the same time as LRCK edge.Note 12. SDTO2 output is fixed to “L”.Note 13. This value is MCLK=512fs. Duty cycle is not guaranteed when MCLK=256fs/384fs. Note 14. The AK5384 can be reset by bringing the PDN pin = “L”.Note 15. This cycle is the number of LRCK rising edges from the PDN pin = “H”.n Timing DiagramVIHMCLKVILLRCKVIH BICKVILClock Timing (TDM0 pin = “L”)VIH MCLKVILLRCKVIH VILVIH BICKVILClock Timing (TDM0 pin = “H”)LRCK VIH VILBICK VIH VILSDTO50%TVDD Audio Interface Timing (Slave mode, TDM0 pin = “L”)BICK VIH VILSDTO50%TVDDAudio Interface Timing (Slave mode, TDM0 pin = “H”) Note: SDTO shows SDTO1 and SDTO2.LRCK BICK50%TVDDSDTO50%TVDD50%TVDDAudio Interface Timing (Master mode)PDNVIH VILSDTO50%TVDDPower Down & Reset TimingNote: SDTO shows SDTO1 and SDTO2.OPERATION OVERVIEWn System ClockThe external clocks which are required to operate the AK5384 are MCLK(256fs/384fs/512fs/768fs), BICK(48fs~), LRCK(1fs) in slave mode (M/S pin = “L”). MCLK should be synchronized with LRCK but the phase is not critical. When 384fs, 512fs or 768fs clock is input to MCLK pin, the internal master clock becomes 256fs(=384fs x 2/3=512fs x1/2=768fs x 1/3) automatically. Table 1 illustrates standard audio word rates and corresponding frequencies used in theAK5384.In master mode (M/S pin = “H”), MCLK select 256fs or 512fs by CKS pin. But 384fs and 768fs are not supported. 512fs does not support 96kHz sampling.All external clocks (MCLK, BICK, LRCK) should always be present whenever the AK5384 is in normal operation mode (PDN pin = “H”). If these clocks are not provided, the AK5384 may draw excess current and may fall into unpredictable operation. This is because the device utilizes dynamic refreshed logic internally. If the external clocks are not present, the AK5384 should be in the power-down mode (PDN pin = “L”). After exiting reset at power-up etc., the AK5384 is in the power-down mode until MCLK and LRCK are input. In master mode, the master clock (MCLK) must be provided unless PDN pin = “L”. MCLK BICK fs256fs 384fs 512fs 768fs 64fs 128fs32.0kHz 8.1920MHz 12.2880MHz 16.3840MHz 24.576MHz 2.0480MHz 4.0960MHz44.1kHz 11.2896MHz 16.9344MHz 22.5792MHz 33.8688MHz 2.8224MHz 5.6448MHz48.0kHz 12.2880MHz 18.4320MHz 24.5760MHz 36.8640MHz 3.0720MHz 6.1440MHz96.0kHz 24.5760MHz 36.8640MHz N/A N/A 6.1440MHz N/ATable 1. System clock example (Slave mode)MCLKCKS8kHz ≤ fs ≤ 48kHz 48kHz < fs ≤ 96kHzL 256fs 256fsH 512fs N/ATable 2. Master clock frequency select (Master mode)n Audio Interface Format12 types of audio data interface can be selected by the TDM1-0, M/S and DIF pins as shown in Table 3. The audio data format can be selected by the DIF pin. In all formats the serial data is MSB-first, 2's compliment format. The SDTO1/2 is clocked out on the falling edge of BICK.In normal mode, Mode 0-1 are the slave mode, and BICK is available up to 128fs at fs=48kHz. BICK outputs 64fs clock in Mode 2-3.In TDM128 mode, the serial data of all ADC (four channels) is output from the SDTO1 pin. The SDTO2 output is fixed to “L”. BICK should be fixed to 128fs. In the slave mode, “H” time and “L” time of LRCK should be 1/128fs at least. In the master mode, “H” time (“L” time at I2S mode) of LRCK is 1/4fs typically. TDM128 mode supports up to 96kHz sampling.LRCK BICK Mode TDM1TDM0M/S DIFSDTOI/OI/O 0 L 24bit, MSB justified H/L I 48-128fs I 1 LH 24bit, I 2S Compatible L/H I 48-128fs I 2 L 24bit, MSB justifiedH/L O 64fs O 3 Normal L LHH 24bit, I 2S Compatible L/H O64fsO 4 L 24bit, MSB justified↑I 256fs I 5 LH 24bit, I 2S Compatible ↓I 256fs I 6 L 24bit, MSB justified↑O 256fs O 7 TDM256 L HHH 24bit, I 2S Compatible ↓O 256fs O 8 L 24bit, MSB justified↑I 128fsI 9 LH 24bit, I 2S Compatible ↓I 128fs I 10 L 24bit, MSB justified↑O 128fs O 11 TDM128 H H HH 24bit, I 2S Compatible↓O 128fs O 12 N/AN/A N/A N/AN/A N/AN/AN/ATable 3. Audio Interface FormatsLRCKBICK(64fs)SDTO1/2(o)Figure 1. Mode 0, 2 Timing (Normal mode, MSB justified) LRCKBICK(64fs)SDTO1/2(o)Figure 2. Mode 1, 3 Timing (Normal mode, I S Compatible)LRCK (Mode 4)BICK (256fs)SDTO1LRCK (Mode 6)LRCK (Mode5) BICK (256fs) SDTO1LRCK (Mode 7)LRCK (Mode 8)BICK (128fs)SDTO1LRCK (Mode 10)LRCK (Mode 9)BICK (128fs)SDTO1LRCK (Mode 11)Figure 6. Mode 9, 11 Timing (TDM128 mode, I2S Compatible)n Master Mode and Slave ModeThe M/S pin selects either master or slave mode. M/S pin = “H” selects master mode and “L” selects slave mode. TheAK5384 outputs BICK and LRCK in master mode. In slave mode, MCLK, BICK and LRCK are input externally.M/S pin Mode BICK, LRCKL Slave Mode BICK = Input LRCK = InputH Master Mode BICK = Output LRCK = OutputTable 4. Master mode/Slave moden Digital High Pass FilterThe ADC has a digital high pass filter for DC offset cancellation. The cut-off frequency of the HPF is 1.0Hz(@fs=48kHz) and scales with sampling rate (fs).n Overflow DetectionThe AK5384 has overflow detect function for analog input. OVF pin goes to “H” if one of 4-channels overflows (more than ?0.3dBFS). OVF output for overflowed analog input has the same group delay as ADC(GD=27.6/fs=575µs@fs=48kHz). OVF is “L” for 516/fs (=10.75ms@fs=48kHz) after PDN pin = “↑”, and then overflow detection is enabled.n Power downThe AK5384 is placed in the power-down mode by bringing PDN pin “L” and the digital filter is also reset at the same time. This reset should always be done after power-up. In the power-down mode, the VCOM are AVSS level. An analog initialization cycle starts after exiting the power-down mode. Therefore, the output data SDTO1/2 becomes available after 516 cycles of LRCK clock. During initialization, the ADC digital data outputs of both channels are forced to a 2’s complement “0”. The ADC outputs settle in the data corresponding to the input signals after the end of initialization (Settling approximatelytakes the group delay time).PDNInternalStateA/D In(Analog)A/D Out(Digital)Clock InMCLK,LRCK,BICKNotes:(1) Digital output corresponding to analog input has the group delay (GD).(2) ADC output is “0” data at the power-down state.(3) When the external clocks (MCLK, BICK, LRCK) are stopped, the AK5384 should be in the power-down state.Figure 7. Power-down/up sequence examplen System ResetThe AK5384 should be reset once by bringing PDN pin “L” after power-up. The internal timing starts clocking by the rising edge (falling edge at I2S mode) of LRCK upon exiting from reset.n Cascade TDM ModeThe AK5384 supports cascading of up to two devices in a daisy chain configuration at TDM256 mode. In this mode, SDTO2 pin of device #1 is connected to TDMIN pin of device #2. SDTO1 pin of device #2 can output 8ch TDM data multiplexed with 4ch TDM data of device #1 and 4ch TDM data of device #2. Figure 8 shows a connection example of a daisy chain.BICK(256fs)#1 SDTO1(o)#1 SDTO2(o)#2 TDMIN(i)#2 SDTO1(o)Figure 9. Cascade TDM TimingSYSTEM DESIGNFigure 10 shows the system connection diagram. An evaluation board is available which demonstrates application circuits,the optimum layout, power supply arrangements and measurement results.4.75 ~5.25VNote:- AVSS and DVSS of the AK5384 should be distributed separately from the ground of external digital devices (MPU, DSP etc.).- All digital input pins should not be left floating.Figure 10. Typical Connection Diagram (Normal mode)1. Grounding and Power Supply DecouplingThe AK5384 requires careful attention to power supply and grounding arrangements. AVDD and DVDD are usually supplied from the analog supply in the system. Alternatively if AVDD and DVDD are supplied separately, the power up sequence is not critical. AVSS and DVSS of the AK5384 must be connected to analog ground plane. System analog ground and digital ground should be connected together near to where the supplies are brought onto the printed circuit board. Decoupling capacitors should be as near to the AK5384 as possible, with the small value ceramic capacitor being the closest.2. Voltage Reference InputsThe differential voltage between AVDD and AVSS sets the analog input range. VCOM is a signal ground of this chip. An electrolytic capacitor 2.2µF parallel with a 0.1µF ceramic capacitor attached to VCOM pin eliminates the effects of high frequency noise. No load current may be drawn from the VCOM pin. All signals, especially clocks, should be kept away from the VCOM pin in order to avoid unwanted coupling into the AK5384.3. Analog InputsThe AK5384 accepts +5V supply voltage. Any voltage which exceeds the upper limit of AVDD+0.3V and lower limit of AVSS?0.3V and any current beyond 10mA for the analog input pins (LIN+/?, RIN+/?) should be avoided. Excessive currents to the input pins may damage the device. Hence input pins must be protected from signals at or beyond these limits. Use caution specially in case of using ±15V in other analog circuits.The analog inputs are differential and internally biased to the common voltage (AVDD/2) with 26k?(typ). The input signal range between LIN(RIN)+ and LIN(RIN)? scales with the supply voltage and nominally ±0.58 x AVDD. The AK5384 can accept input voltages from AVSS to AVDD. The ADC output data format 2’s compliment. The internal HPF removes the DC offset.The AK5384 samples the analog inputs at 64fs. The digital filter rejects noise above the stop band except for multiples of64fs.4. External Analog Inputs CircuitFigure 11 shows an input buffer circuit example 1. The input level of this circuit is 5.7Vpp (AK5384: typ. ±2.9Vpp).Figure 11. Input buffer circuit example 1 (DC coupled single-end input)Figure 12 shows an input buffer circuit example 2. The input level of this circuit is 5.7Vpp (AK5384: typ. ±2.9Vpp).5.7VppFigure 12. Input buffer circuit example 2 (AC coupled single-end input)Figure 13 shows an input buffer circuit example 3. The input level of this circuit is 2.9Vpp (AK5384: typ. 2.9Vpp).2.9Vpp2.9VppFigure 13. Input buffer circuit example 3 (Differential input)。

AKD5383 评估板用户手册说明书

[JP2,JP3,JP4,JP5]: Open The resistor value of R10, R11, R18 and R19 should be properly selected in order to much the output impedance of the signal source.

1-1. Using D/A converter board for the analog performance analysis.

The AK5383 can be evaluated by distortion analyzer using various AKM's D/A converter evaluation boards through PORT2.

(5) AK5383 can be reset by SW4 during operation. Lower position resets the device, and the upper position is for normal operation.

Note: In any case of changing clocks during operation, the device should be reset by bringing PD "L". If not followed, the AK5383 may be destroyed since its internal logic uses dynamic circuit.

* AKM assumes no responsibility for the trouble when using the above circuit examples.

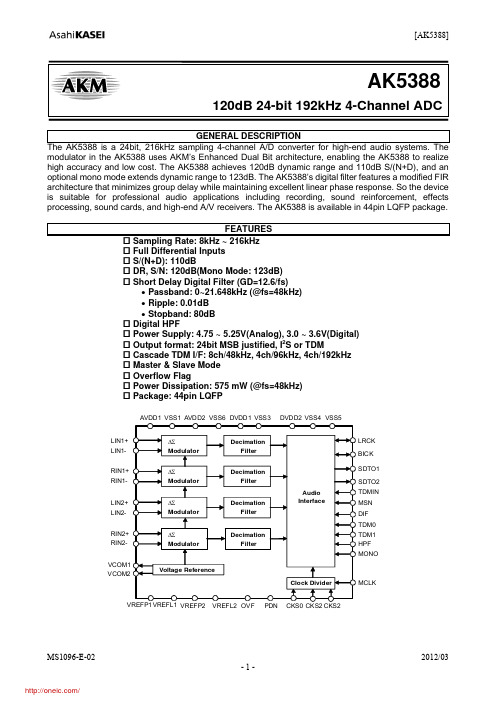

AK5388EQP;中文规格书,Datasheet资料

Ground pin I Clock Mode Select #0 Pin I Clock Mode Select #1 Pin

I Clock Mode Select #2 Pin

Power-Down Mode Pin

I

When “L”, the circuit is in power-down mode.

10 PDN

11 MSN 12 MCLK 13 BICK

14 LRCK 15 DVDD1 16 VSS3 17 SDTO1

18 SDTO2

19 OVF

20 TDMIN 21 TDM0

22 TDM1

23 DIF

24 MONO

25 HPFE 26 DVDD2 27 VSS4 28 VSS5

PIN / FUNCTION

/

2012/03

[AK5388]

■ Handling of Unused Pin

The unused I/O pins should be processed appropriately as below.

AK5383VS中文资料

Normally connected to GNDR with a 10µF electrolytic capacitor and a 0.1µF ceramic capacitor

Note: All digitalng.

M0049-E-03 -4-

I Test Pin ( pull-down pin) Should be connected to GND.

- Substrate Ground Pin, 0V - Analog Ground Pin, 0V - Analog Supply Pin, 5V I Rch Analog negative input Pin I Rch Analog positive input Pin O Rch Common Voltage Pin, 2.75V - Rch Reference Ground Pin, 0V O Rch Reference Voltage Pin, 3.75V

- Lch Reference Ground Pin, 0V

O Lch Common Voltage Pin, 2.75V I Lch Analog positive input Pin

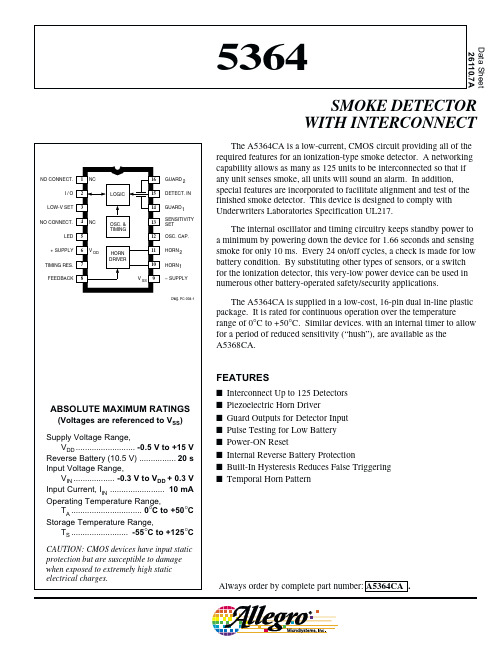

5364中文资料

SMOKE DETECTOR WITH INTERCONNECTThe A5364CA is a low-current, CMOS circuit providing all of the required features for an ionization-type smoke detector. A networking capability allows as many as 125 units to be interconnected so that if any unit senses smoke, all units will sound an alarm. In addition,special features are incorporated to facilitate alignment and test of the finished smoke detector. This device is designed to comply with Underwriters Laboratories Specification UL217.The internal oscillator and timing circuitry keeps standby power to a minimum by powering down the device for 1.66 seconds and sensing smoke for only 10 ms. Every 24 on/off cycles, a check is made for low battery condition. By substituting other types of sensors, or a switch for the ionization detector, this very-low power device can be used in numerous other battery-operated safety/security applications.The A5364CA is supplied in a low-cost, 16-pin dual in-line plastic package. It is rated for continuous operation over the temperaturerange of 0°C to +50°C. Similar devices. with an internal timer to allow for a period of reduced sensitivity (“hush”), are available as the A5368CA.Always order by complete part number: A5364CA .Data Sheet 26110.7AFEATURESI Interconnect Up to 125 Detectors I Piezoelectric Horn DriverI Guard Outputs for Detector Input I Pulse Testing for Low Battery I Power-ON ResetI Internal Reverse Battery ProtectionI Built-In Hysteresis Reduces False Triggering ITemporal Horn Pattern53645364SMOKE DETECTOR WITHINTERCONNECT115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-5000Copyright © 1998, 1999 Allegro MicroSystems, Inc.9 VGUARD GUARD +V581110712691415165364SMOKE DETECTOR WITH INTERCONNECTTestLimitsCharacteristic Pin Test Conditions Min.Typ.Max.Units Supply Voltage Range 6Operating6.09.012V Detector Input Current 150 to 40% RH, V IN = 0 to 9.0 V ——±1.0pA Input Offset Voltage14-15Active Guard ——±100mV 16-15Active Guard ——±100mV 15-13Detect Comparator ——±50mV Hysteresis13No Alarm to Alarm 90130170mV Common Mode Range14-15Guard Amplifier 2.0—V DD - 0.5V 13-15Smoke Comparator 0.5—V DD - 2.0V Active Guard Impedance14to V SS —10—k Ω16to V SS —500—k Ω Oscillator Period12No Alarm 1.34 1.67 2.00s Alarm324048ms Oscillator Pulse Width 48.01012ms Low Voltage Threshold 6T A = 0 to 50°C7.2—7.8V Sensitivity Adj. Voltage 13V 13/V DD , pin 13 open circuit 48.55051.5% Horn Output Voltage10-11I OUT = 16 mA, V DD = 9.0 V —0.10.5V I OUT = 16 mA, V DD = 7.2 V ——0.9V I OUT = -16 mA, V DD = 9.0 V 8.58.8—V I OUT = -16 mA, V DD = 7.2 V6.3——V Horn Output ON Time10-11Alarm (see figure, time “A”)450500550ms Low Battery8.01012ms Horn Output OFF Time10-11Alarm (see figure, time “B”)450500550ms Alarm (see figure, time “C”)135015001650ms Low Battery324048s LED Output ON Current 5V DD = 7.2 V, V OUT = 1.0 V 10——mA LED Output ON Time 5No Local Alarm; Not Latched 8.01012ms LED Output OFF Time5No Alarm, In Standby324048sELECTRICAL CHARACTERISTICS at T A = +25°C, V DD = 9.0 V, V SS = 0 V, C 12 = 0.1 µF,R 7 = 8.2 M Ω (unless otherwise noted).Continued next page . . .NOTE 1:Negative current is defined as coming out of (sourcing) the specified device pin.NOTE 2:Alarm (Smoke) Condition is defined as V 15 < V 13; No Alarm (No Smoke) Condition as V 15 > V 13.5364SMOKE DETECTOR WITH INTERCONNECT115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-5000I/O Current2No Alarm, V I/O = V DD - 2.0 V 25—60µA Alarm, V I/O = V DD - 2.0 V-7.5——mA I/O Alarm Voltage 2External “Alarm” In 3.0——V I/O Delay 2“Alarm” Out— 3.0—s Supply Current6V DD = 9.0 V, No Alarm, No Loads — 5.09.0µA V DD = 12 V, No Alarm, No Loads——12µATestLimitsCharacteristic Pin Test Conditions Min.Typ.Max.Units ELECTRICAL CHARACTERISTICS (continued)CIRCUIT DESCRIPTIONThe A5364CA is a low-current CMOS circuit providing all of the required features for an ionization-type smoke detector.Oscillator. An internal oscillator operates with a period of 1.67 seconds during no-smoke conditions. Every 1.67 seconds,internal power is applied to the entire circuit and a check is made for smoke. Every 24clock cycles (40 seconds), the LED is pulsed and a check is made for low battery by comparing V DD to an internal reference.Because very-low currents are used in the device, the oscillator capacitor at pin 12should be a low-leakage type (PTFE, polysty-rene, or polypropylene).Detector Circuitry. When smoke isdetected, the resistor divider network that sets the sensitivity (smoke trip point) is altered to increase the sensitivity set voltage (pin 13) by typically 130 mV with no external connec-tions to pins 3 or 13. This provides hysteresis and reduces false triggering. An active guard is provided on both pins adjacent to the detector input (pin 15). The voltage at pins 14 and 16 will be within 100 mV of the input.This will keep surface leakage currents to a minimum and provide a method of measuring the input voltage without loading the ionization chamber. The active guard amplifier is not power strobed and thus provides constant protection from surface leakage currents. The detector input has internal diode protection against static damage.Alarm Circuitry. If smoke is detected, the oscillator period changes to 40 ms and the horn is enabled. The horn output is typically 0.5 s ON, 0.5 s OFF, 0.5 s ON, 0.5 s OFF, 0.5 s ON, 1.5 s OFF (temporal horn pattern). During the OFF time, smoke is checked and will inhibit further alarm output if smoke is not sensed. During smoke conditions the low battery alarm is inhibited and the LED is driven at a 1 Hz rate.Sensitivity Adjust. The detector sensitivity to smoke is set inter-nally by a voltage divider connected between V DD and V SS . Thesensitivity can be externally adjusted to the individual characteristics of the ionization chamber by connecting a resistor between pin 13 and V DD , or between pin 13 and V SS .Low Battery. The low battery threshold is set internally by a voltage divider connected between V DD and V SS . The threshold can be in-creased by connecting a resistor between pin 3 and V DD . The threshold can be decreased by connecting a resistor between pin 3 and V SS . The battery voltage level is checked every 40 seconds during the 10 mA,10 ms LED pulse. If an LED is not used, it should be replaced with an equivalent resistor (typically 500 Ω to 1000 Ω) such that the battery loading remains at 10 mA.NOTE 1:Negative current is defined as coming out of (sourcing) the specified device pin.NOTE 2:Alarm (Smoke) Condition is defined as V 15 < V 13; No Alarm (No Smoke) Condition as V 15 > V 13.5364SMOKE DETECTOR WITH INTERCONNECTV12OSC. CAPINTERNAL CLOCKLED SMOKE COMPARATORSMOKE CHAMBERHORNDwg. WC-003-3I/OI/O. A connection is provided at pin 2 to allow multiple smoke detectors to becommoned. If any single unit detects smoke (I/O is driven high), all connected units will sound their associated horns after a nominal 3second delay. The LED is suppressed when an alarm is signaled from an interconnected unit.Testing. On power up, all internal counters are reset. Internal test circuitry allows for low battery check by holding pins 8 and 12low during power up, then reducing V DD and monitoring HORN 1 (pin 10). All functional tests can be accelerated by driving pin 12with a 2 kHz square wave. The 10 ms strobe period must be maintained for proper opera-tion of the comparator circuitry.313TIMING DIAGRAM IN TYPICAL APPLICATION5364SMOKE DETECTOR WITHINTERCONNECT115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-5000I/O OPERATIONINTERNAL CLOCKHORNV2 IN I/OV2 OUT I/OINTERNAL CLOCKDwg. WC-004-2HORN5364SMOKE DETECTOR WITH INTERCONNECTDimensions in Inches(controlling dimensions)Dimensions in Millimeters(for reference only)NOTES:1.Lead thickness is measured at seating plane or below.2.Lead spacing tolerance is non-cumulative.3.Exact body and lead configuration at vendor’s option within limits shown.Dwg. MA-001-16A in1618Dwg. MA-001-16A mm16185364SMOKE DETECTOR WITHINTERCONNECT115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-5000The products described here are manufactured under one or more U.S. patents or U.S. patents pending.Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, ormanufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.Allegro products are not authorized for use as critical components in life-support devices or systems without express written approval.The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsi-bility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.SAFETY & SECURITY ICsPart Number FunctionA3054KU/SU Multiplexed two-wire Hall-effect sensorA5348CA Ionization-type smoke detector with interconnect, timer, and reverse-battery protection A5349CA Ionization-type smoke detector with interconnect and timer for ac line operation A5350CA Ionization-type smoke detector with interconnect and reverse-battery protection A5354CA Ionization-type smoke detector with interconnect and reverse-battery protection A5358CA Photoelectric-type smoke detector with interconnect and timerA5364CA Ionization-type smoke detector with interconnect, reverse-battery protection,and temporal horn patternA5368CAIonization-type smoke detector with interconnect, timer, reverse-battery protection,and temporal horn pattern。

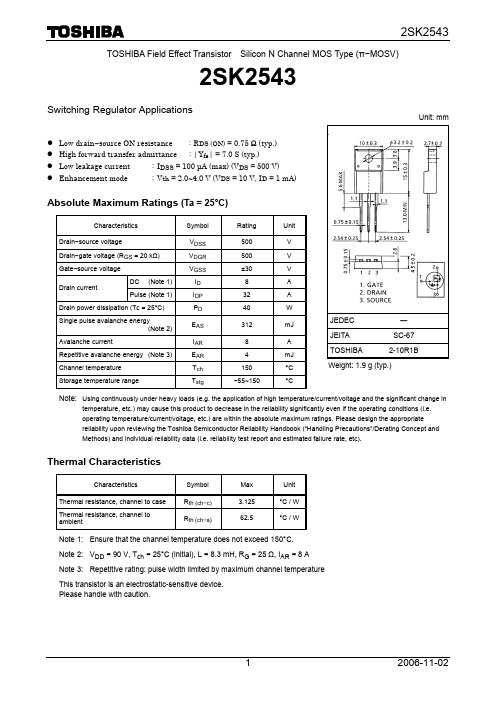

原版sk2543三极管产品说明书

TOSHIBA Field Effect Transistor Silicon N Channel MOS Type (π−MOSV)2SK2543Switching Regulator Applicationsz Low drain −source ON resistance : R DS (ON) = 0.75 Ω (typ.) z High forward transfer admittance : |Y fs | = 7.0 S (typ.)z Low leakage current : I DSS = 100 μA (max) (V DS = 500 V) z Enhancement mode : V th = 2.0~4.0 V (V DS = 10 V, I D = 1 mA)Absolute Maximum Ratings (Ta = 25°C)Characteristics Symbol Rating UnitDrain −source voltageV DSS 500 VDrain −gate voltage (R GS = 20 k Ω) V DGR 500 VGate −source voltage V GSS ±30 V DC (Note 1) I D 8 A Drain currentPulse (Note 1)I DP 32A Drain power dissipation (Tc = 25°C)P D 40 WSingle pulse avalanche energy (Note 2) E AS 312mJ Avalanche currentI AR 8 ARepetitive avalanche energy (Note 3) E AR 4 mJChannel temperature T ch 150 °CStorage temperature rangeT stg−55~150 °CNote: Using continuously under heavy loads (e.g. the application of high temperature/current/voltage and the significant change intemperature, etc.) may cause this product to decrease in the reliability significantly even if the operating conditions (i.e. operating temperature/current/voltage, etc.) are within the absolute maximum ratings. Please design the appropriate reliability upon reviewing the Toshiba Semiconductor Reliability Handbook (“Handling Precautions”/Derating Concept and Methods) and individual reliability data (i.e. reliability test report and estimated failure rate, etc).Thermal CharacteristicsCharacteristics Symbol Max UnitThermal resistance, channel to case R th (ch −c)3.125°C / W Thermal resistance, channel to ambientR th (ch −a) 62.5°C / WNote 1: Ensure that the channel temperature does not exceed 150°C. Note 2: V DD = 90 V, T ch = 25°C (initial), L = 8.3 mH, R G = 25 Ω, I AR = 8 A Note 3: Repetitive rating: pulse width limited by maximum channel temperature This transistor is an electrostatic-sensitive device. Please handle with caution.Unit: mmJEDEC ―JEITA SC-67 TOSHIBA 2-10R1BWeight: 1.9 g (typ.)Electrical Characteristics (Ta = 25°C)Characteristics SymbolTest ConditionMin Typ. Max Unit Gate leakage currentI GSS V GS = ±25 V, V DS = 0 V — — ±10μA Gate −source breakdown voltage V (BR) GSS I G = ±10 μA, V GS = 0 V ±30 — — V Drain cut −off currentI DSS V DS = 500 V, V DS = 0 V — — 100μA Drain −source breakdown voltage V (BR) DSSI D = 10 mA, V GS = 0 V 500 — — V Gate threshold voltage V th V DS = 10 V, I D = 1 mA 2.0 — 4.0 V Drain −source ON resistance R DS (ON)V GS = 10 V, I D = 4 A— 0.75 0.85Ω Forward transfer admittance |Y fs | V DS = 10 V, I D = 4 A3.57.0—SInput capacitanceC iss — 1300 —Reverse transfer capacitance C rss — 130 — Output capacitanceC ossV DS = 10 V, V GS = 0 V, f = 1 MHz — 400 —pF Rise timet r — 26 —Turn −on timet on — 45 —Fall timet f — 40 —Switching timeTurn −off timet off— 140 —nsTotal gate charge (Gate −sourceplus gate −drain) Q g —30 — Gate −source charge Q gs — 17 — Gate −drain (“miller”) chargeQ gdV DD ≈ 400 V, V GS = 10 V, I D = 8 A — 13 —nCSource −Drain Ratings and Characteristics (Ta = 25°C)Characteristics SymbolTest ConditionMin Typ. Max UnitContinuous drain reverse current(Note 1) I DR —— — 8 A Pulse drain reverse current(Note 1) I DRP — — — 32 A Forward voltage (diode) V DSFI DR = 8 A, V GS = 0 V — — −1.7VReverse recovery time t rr — 1200 — ns Reverse recovery chargeQ rrI DR= 8 A, V GS= 0 V dI DR / dt = 100 A / μs— 10 — μCMarkinglead (Pb)-free package or lead (Pb)-free finish.K2543⎟⎠⎞⎜⎝⎛−⋅⋅⋅=DD V VDSS B VDSS B I L 21AS E 2R G = 25 ΩV DD = 90 V , L = 8.3 mHRESTRICTIONS ON PRODUCT USE20070701-EN •The information contained herein is subject to change without notice.•TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the “Handling Guide for Semiconductor Devices,” or “TOSHIBA Semiconductor Reliability Handbook” etc.• The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.).These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury (“Unintended Usage”). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in his document shall be made at the customer’s own risk.•The products described in this document shall not be used or embedded to any downstream products of which manufacture, use and/or sale are prohibited under any applicable laws and regulations.• The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patents or other rights of TOSHIBA or the third parties.• Please contact your sales representative for product-by-product details in this document regarding RoHS compatibility. Please use these products in this document in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances. Toshiba assumes no liability for damage or losses occurring as a result of noncompliance with applicable laws and regulations.。

ph538中文说明书

ph538中文说明书产品简介:PH538是一款功能强大的电子设备,用于在家庭和办公环境中提供高质量的音频和视频体验。

它具有多种接口和功能,可满足用户对多媒体娱乐和工作需求的各种要求。

产品特点:1.高清显示:PH538支持高清视频输出,可提供清晰、细腻的图像和影像效果,让用户享受更加逼真的视觉体验。

2.多媒体连接:PH538配备多种接口,包括HDMI、USB和VGA等,可连接各种外部设备,如电视、投影仪、电脑等,实现多种多媒体设备的互联互通。

3.多功能遥控:PH538配备一款智能遥控器,用户可以通过遥控器方便地切换不同的输入源和功能,轻松控制设备的各项操作。

4.音频输出:PH538支持多种音频格式,可提供清晰、逼真的音频效果,让用户享受更加震撼的音乐和影音体验。

5.节能环保:PH538采用先进的节能技术,具有低功耗和环保的特点,可有效降低用电成本,减少对环境的影响。

产品使用注意事项:1.在使用PH538之前,请仔细阅读本说明书,并按照说明书中的操作步骤正确使用设备。

2.使用过程中,请确保设备与电源的连接牢固可靠,以免发生松动或短路等安全问题。

3.使用PH538时,请保持设备周围通风良好,避免长时间封闭使用,以防设备过热或损坏。

4.请勿将PH538放置在潮湿或温度极高的环境中,以免影响设备的正常运行。

5.请勿将PH538的外壳打开或拆解,以免触电或损坏设备,如需维修请联系专业人员。

6.当设备长时间不使用时,请及时关闭电源,以节省能源和延长设备寿命。

7.请妥善保管PH538及其配件,避免受到撞击、摔落或水浸等物理损坏。

产品售后服务:1.本产品提供一年的质保服务,从购买日期起计算,质保期内可享受免费维修和更换服务。

2.如需售后服务,请携带有效购买凭证和相关配件到指定的售后服务中心进行维修或更换。

3.在售后服务过程中,请遵守维修人员的操作规定,以免导致不必要的损失或安全问题。

感谢您选择PH538电子设备,希望我们的产品能为您带来愉快的使用体验和便利。

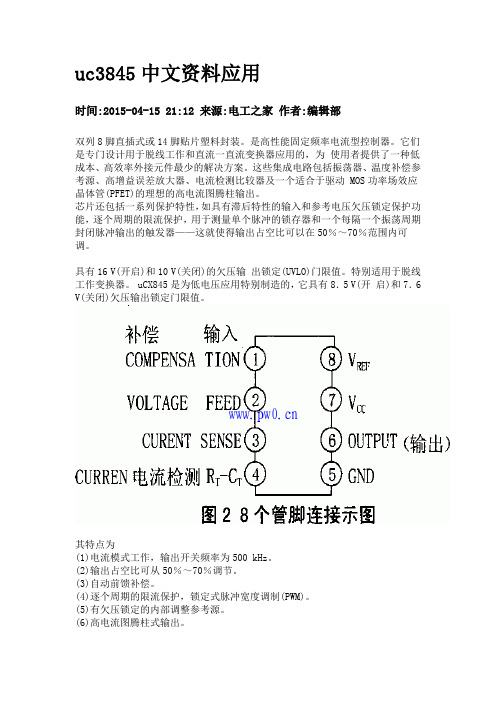

uc3845中文资料应用

uc3845中文资料应用

时间:2015-04-15 21:12 来源:电工之家作者:编辑部

双列8脚直插式或14脚贴片塑料封装。

是高性能固定频率电流型控制器。

它们是专门设计用于脱线工作和直流一直流变换器应用的,为使用者提供了一种低成本、高效率外接元件最少的解决方案。

这些集成电路包括振荡器、温度补偿参考源、高增益误差放大器、电流检测比较器及一个适合于驱动 MOS功率场效应晶体管(PFET)的理想的高电流图腾柱输出。

芯片还包括一系列保护特性,如具有滞后特性的输入和参考电压欠压锁定保护功能,逐个周期的限流保护,用于测量单个脉冲的锁存器和一个每隔一个振荡周期封闭脉冲输出的触发器——这就使得输出占空比可以在50%~70%范围内可调。

具有16 V(开启)和10 V(关闭)的欠压输出锁定(UVLO)门限值。

特别适用于脱线工作变换器。

uCX845是为低电压应用特别制造的,它具有8.5 V(开启)和7.6 V(关闭)欠压输出锁定门限值。

其特点为

(1)电流模式工作,输出开关频率为500 kHz。

(2)输出占空比可从50%~70%调节。

(3)自动前馈补偿。

(4)逐个周期的限流保护,锁定式脉冲宽度调制(PWM)。

(5)有欠压锁定的内部调整参考源。

(6)高电流图腾柱式输出。

(7)带滞后的输入欠压锁定。

封装引脚图:

【互换兼容】

CS3845 CW3845 KA3885脚同(FA13845N)FA13845P L3845 LM3845 ST3845UC UC3845W UC3845N脚同UC3845A。

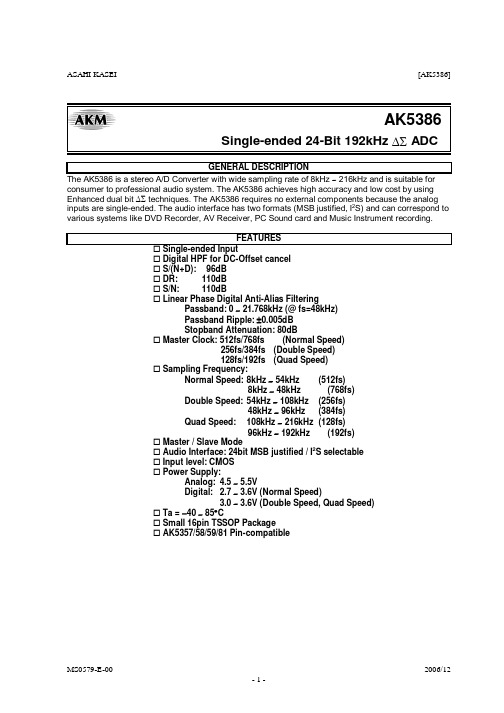

AK5386中文资料

Power Down & Reset Mode Pin

13 PDN

I

“H”: Power up, “L”: Power down & Reset

The AK5386 must be reset once upon power-up.

4.5 to 5.5V 2.7 to 5.5V 3.0 to 5.5V@ fs=96kHz Available ET: −20∼+85°C VT: −40∼+85°C XT: −40∼+85°C

AK5359 8kHz to 216kHz

94dB 102dB

256/512/384/768fs

Not Available

FEATURES

Single-ended Input

Digital HPF for DC-Offset cancel

S/(N+D): 96dB

DR:

110dB

S/N:

110dB

Linear Phase Digital Anti-Alias Filtering

Passband: 0 ∼ 21.768kHz (@ fs=48kHz)

WARNING: Operation at or beyond these limits may result in permanent damage to the device. Normal operation is not guaranteed at these extremes.

Units V V mA V V °C °C

5 AGND

- Analog Ground Pin

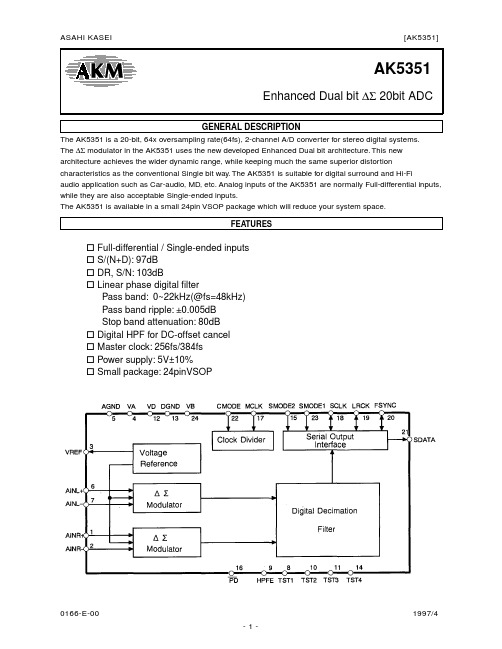

AK5351资料