Wiring_Diagrams_for_Ford_Tractors

写出光线跟踪递归函数的伪代码。

写出光线跟踪递归函数的伪代码。

光线跟踪是一种计算机图形学中常用的方法,用于模拟物体表面反射光线的行为,从而生成逼真的图像。

下面是光线跟踪递归函数的伪代码:```pythonRay Trace(Point3D origin, Vector3D direction, int depth):if depth == MAX_DEPTH: # 达到递归深度,结束递归return BACKGROUND_COLOR# 找到离射线最近的交点hit_distance, hit_point, hit_norm, hit_obj = findIntersection(origin, direction)if not hit_obj: # 未与任何物体相交,返回背景颜色return BACKGROUND_COLOR# 计算环境光照color = hit_obj.material.ambient_color * AMBIENT_LIGHT_COLOR# 计算入射光照for light in scene.lights:light_direction = normalize(light.position - hit_point)# 检查是否有阴影if not isShadowed(hit_point, light.position, hit_obj):color += computeDiffuseColor(hit_obj.material.diffuse_color, light.color, light_direction, hit_norm)color += computeSpecularColor(hit_obj.material.specular_color, light.color, light_direction, hit_norm, direction)前两个参数是光线的起点和方向向量,第三个参数是当前递归深度。

计算机专业英语教程第5版中译英参考

Unit 1A computer system consists of hardware system and software system. The hardware of the computer is usually divided into three major parts or three primary subsystems: the CPU, the memory subsystem, and the I/O subsystem.The CPU performs many operations and controls computer. The memory subsystem is used to store program being executed by the CPU, along with the program’s data. The I/O subsystem allows the CPU to interact with input and output devices such as the keyboard and monitor of a personal computer. The components of the computer are connected to the buses.The part of the computer that performs the bulk of data processing operations is called the central processing unit and is referred to as the CPU. In microcomputer, it is often called the microprocessor. The CPU is made up of three major parts: control unit, ALU, and register set.Memory is also known as internal memory or main memory. It refers to the circuits in the computer that hold whatever programs and data are available for immediate use by the CPU.I/O subsystem includes I/O devices and interface. There are a wide variety of I/O devices, such as mouse, printer, sensor, disk, and so on. Input-output interface provides a method for transferring information between internal storage and external I/O devices. Peripherals connected to a computer need special communication links for interfacing them with the CPU. The purpose of the communication link is to resolve the differences that exist between the central computer and each peripheral.Unit 3(a) A program is a list of instructions or statements for directing the computer to perform a required data processing task. Programming is a multistep process for creating that list of instructions.(b) It is important to understand the difference between a class and an object of that class. A class is simply a specification for creating objects. Thus, a single class may create multiple objects.(c) Java is an object-oriented, network-friendly high-lever programming language that allows programmers to build applications that can run on almost any operating system.(e) Programming involves a great deal of creativity. The design is guide to the function or purpose of each component, but the programmer has great flexibility in implementing the design as code. No matter what language is used, each program component involves at least three major aspects: control structures, algorithms, and data structures.Unit 4The software system can be divided into two broad categories: application software and system software. Application software consists of the program for performing tasks particular to the machine’s utilization. In contrast to application software, system software comprises a large number of programs. These programs start up the computer and function as the principle coordinator of all hardware components and application software. Without system software loaded into RAM of your computer, your hardware and application software are useless.System software can be grouped into three basic parts: operating system, utility software, and language translators. The majority of an installation’s utility software consists of programs for performing activities that are fundamental to computer installations yet not included in the operating system. In a sense, utility software consists of software units that extend the capabilities of the operating system.A computer’s OS is the main collection of programs that manage its activities. The primary chores of an OS are management and control. The OS ensures that all actions requested by a user are valid and processed in an orderly fashion. It also manages the computer system’s resources to perform these operations with efficiency and consistency.Application software is the software designed to help you solve problems specific to business or perform specific business tasks. Application software then is the layer of software closest to you. Basically, there are four categories of application software: productivity software, business and specialty software, entertainment software and education/reference software.Unit 5A computer network is often classified as being either a local area network (LAN), a metropolitan area network (WAN), or a wide area network (WAN). The connection of two or more networks is called an internetwork. The worldwide Internet is a well-known example of an internetwork.LANs are privately owned networks within a single building or campus of up to a few kilometers in size. They are widely used to connect personal computers and workstations in company offices and factories to share resources and exchange information.In general, a given LAN will use only one type of transmission medium. Various topologies are possible for LANs. The most common LAN topologies are bus, ring and star.A MAN is basically a bigger version of a LAN and normally uses similar technology. MAN is designed to extend over an entire city. It may be a single network such as a cable television network, or it may be a means of connecting a number of LANs into a large network so that resources may be shared LAN-to-LAN as well as device-to-device. For example, a company can use a MAN to connect the LANs in all of its offices throughout a city.A WAN spans a large geographical area that may comprise a country, a continent, or even the world. It provides long-distance transmission of data, voice, image, and video information over large geographical area.In contrast to LANs, WANs may utilize public leased, or private communication devices, usually in combinations, and can therefore span an unlimited number of miles.Unit 6Transmission media are used to transfer messages over a network. For instance, the transmission media used in a network may be a privately owned set of cables, the public phone lines, or a satellite system. Transmission media can either be wired or wireless.The three types of wired media most commonly used to carry messages are twisted-pair wire, coaxial cable, and fiber-optic cable. One of the most successful developments in transmission media in recent years has been fiber optics. Fiber-optic cable is commonly used for the high-speed backbone lines of a network, or for Internet infrastructure.Wireless transmission media have become especially popular in recent years. They support communications in situations in which physical wiring is impractical or inconvenient, as well as facilitate mobility. Wireless media are commonly used to connect devices to a network, to share information between computers, to connect wireless mice to a computer, and for handheld PCs, wireless phones, and other mobile devices. Radio signals transferred through the air are the heart of most types of wireless media. In addition to conventional broadcast radio application, the microwave, cellular, and satellite transmission media also use radio signals to transmit data.Radio transmissions require the use of a transmitter to send the radio signals through the air. A receiver (usually containing some type of antenna) accepts the date at the other end. When a device functions as both a receiver and transmitter, it is commonly called a transceiver or transmitter-receiver.Unit 7(a) Since many database systems users are not computer trained, developers hide the complexity from users through several levels of abstraction, to simplify user’s int eractions with the system: physical level, logical level, and view level.(b) A database schema is specified by a set of definitions expressed by a special language called a data-definition language (DDL). The result of compilation of DDL statements is a set of tables that is stored in a special file called data dictionary, or data directory.(c) The structured query language (SQL) is the most widely used and standard query language for relational database management systems. It is a kind of non-procedural language.(d) An entity is a “thing” or “object” in the real world that is distinguishable from other objects. For example, each person is an entity, and bank accounts can be considered to be entities. Entities are described in a database by a set of attributes.(e) Data warehouse is one of the newest and hottest buzzwords and concepts in the IT field and the business environment.A data warehouse is a logical collection of information——gathered from many different operational databases——that supports business analysis activities and decision-making tasks.Unit 9(a) AI is currently being applied in business in the form of knowledge systems, which use human knowledge to solve problems. The most popular type of knowledge-based system is the expert system. An expert system is a computer program that attempts to represent the knowledge of human experts in the form of heuristics. The term heuristic is derived from the same Greek root as the word eureka, which means “to discover”.(b) The user interface enables the manager to enter instructions and information into the expert system and to receive information from it. The instructions specify the parameters that guide the expert system through its reasoning processing. The information is in the form of values assigned to certain variables.(c) The knowledge base contains both facts that describe the problem area and knowledge representation techniques that describe how the facts fit together in a logical manner. The term problem domain is used to describe the problem area.(d) An expert system, also called a knowledge-based system, is an artificial intelligence system that applies reasoning capabilities to reach a conclusion. Expert systems are excellent for diagnostic and prescriptive problems.(e) The DSS is not intended to replace the manager. The computer can be applied to the structured portion of the problem, but the manager is responsible for the unstructured portion——applying judgment or intuition and conducting analyses.1。

ULPI_v1_1

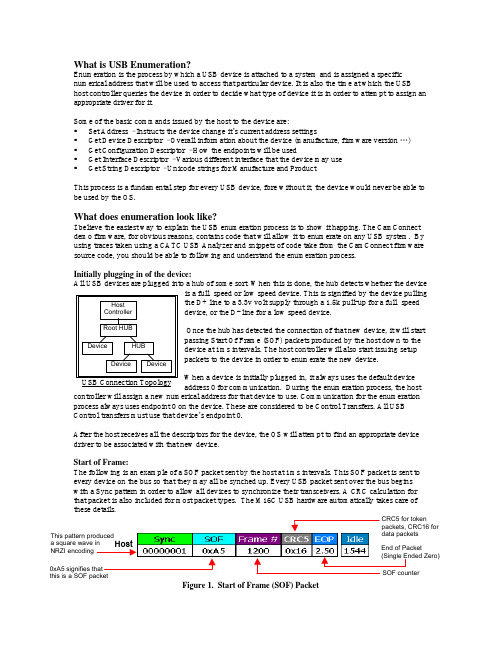

UTMI+ Low Pin Interface (ULPI)SpecificationRevision 1.1October 20, 2004Revision HistoryDate CommentRevision Issue0.9 November 12, 2003 Pre-release.1.0rc1 January 3, 2004 Introduce PHY interface “modes”.Update interface timings. Clarify 4-bit data clocking.Clarify sending of RX CMD’s and interrupts.Introduce AutoResume feature.Route int pin to data(3) during 6-pin Serial Mode.Explain VBUS thresholds.Add T&MT diagram and updated text.Add new section to explain how PHY is aborted by Link.Various clarifications.1.0rc2 January 13, 2004 Add block diagram.Tighten interface timing.Modify suspend protocol to more closely resemble UTMI.Add SPKR_L and SPKR_MIC to signal list and T&MTconnector.Various clarifications.1.0rc3 January 19, 2004 Specify that PHY must send RX CMD after Reset.Link + PHY clock startup time of no more than 5.6ms for aperipheral is now mandatory.PHY output delay reduced from 10ns to 9ns.Added link decision time numbers for low speed.Various Clarifications.1.0 February 2, 2004 1.0rc3 adopted as 1.0 release.1.1rc1 September 1, 2004 Various clarifications and fixes to hold time numbers, sendingRXCMDs, FsLsSerialMode, Vbus control and monitoring,Test_J and Tesk_K signalling, Low Power Mode,Hostdisconnect, ID detection, HS SOF packets, interrupts,Carkit Mode, interface protection, No SYNC/EOP mode,linestate filtering, and AutoResume.1.1rc2 October 4, 2004 Re-arranged text in section 3.8.7.3. Updated contributors list.1.1 October 20, 2004 1.1rc2 adopted as 1.1 release.The present Specification has been circulated for the sole benefit of legally-recognized Promoters, Adopters and Contributors of the Specification. All rights are expressly reserved, including but not limited to intellectual property rights under patents, trademarks, copyrights and trade secrets. The respective Promoter's, Adopter's or Contributor's agreement entered into by Promoters, Adopters and Contributors sets forth their conditions of use of the Specification.iiPromotersARC International Inc.Conexant Systems, Inc.Mentor Graphics CorporationPhilipsSMSCTransDimension, Inc.ContributorsVertenten PhilipsBartOkur PhilipsBatuhanBillAnderson MotorolaMcInerney TransDimensionBillBooker CypressBrianARCBelangerChrisKolb ARCChrisChrisSchell PhilipsChung Wing Yan PhilipsSrokaPhilipsDaveWang PhilipsDavidWooten TransDimensionDavidSMSCEricKawamotoPhilipsMackayFarranFrazier ConexantFrankFredRoberts SynopsysFarooqConexantHassanLee TransDimensionHyunParr MentorIanStandiford TransDimensionJayPhilipsTjiaJeromeMentorSaundersMarkMohamed Benromdhane ConexantSMSCMorganMonksISINabilTaklaTengstrand ARCPeterRamanand Mandayam ConexantDouglas MentorRobSaleemMohamed Synopsys(Author)ShaunReemeyer PhilipsCypressSimonNguyenSubramanyam Sankaran PhilipsTexasInstrumentsViningSueRemple QualcommTerryChen ConexantTimothyConexantChangVincentQuestions should be emailed to lpcwg@.iiiTable of Contents1.Introduction (1)1.1General (1)1.2Naming Convention (1)1.3Acronyms and Terms (1)1.4References (1)2.Generic Low Pin Interface (2)2.1General (2)2.2Signals (2)2.3Protocol (3)2.3.1Bus Ownership (3)2.3.2Transferring Data (3)2.3.3Aborting Data (4)3.UTMI+ Low Pin Interface (5)3.1General (5)3.2Signals (6)3.3Block Diagram (7)3.4Modes (9)3.5Power On and Reset (10)3.6Interrupt Event Notification (10)3.7Timing (11)3.7.1Clock (11)3.7.2Control and Data (13)3.8Synchronous Mode (15)3.8.1ULPI Command Bytes (15)3.8.2USB Packets (18)3.8.3Register Operations (30)3.8.4Aborting ULPI Transfers (37)3.8.5USB Operations (39)3.8.6Vbus Power Control (internal and external) (52)3.8.7OTG Operations (52)3.9Low Power Mode (55)3.9.1Data Line Definition For Low Power Mode (55)3.9.2Entering Low Power Mode (55)3.9.3Exiting Low Power Mode (56)3.9.4False Resume Rejection (57)3.10Full Speed / Low Speed Serial Mode (Optional) (58)3.10.1Data Line Definition For FsLsSerialMode (58)3.10.2Entering FsLsSerialMode (59)3.10.3Exiting FsLsSerialMode (60)3.11Carkit Mode (Optional) (61)3.12Safeguarding PHY Input Signals (62)4.Registers (65)4.1Register Map (65)4.2Immediate Register Set (67)4.2.1Vendor ID and Product ID (67)4.2.2Function Control (68)4.2.3Interface Control (69)4.2.4OTG Control (71)4.2.5USB Interrupt Enable Rising (72)4.2.6USB Interrupt Enable Falling (73)4.2.7USB Interrupt Status (74)4.2.8USB Interrupt Latch (75)4.2.9Debug (76)4.2.10Scratch Register (76)4.2.11Carkit Control (77)4.2.12Carkit Interrupt Delay (77)iv4.2.13Carkit Interrupt Enable (78)4.2.14Carkit Interrupt Status (78)4.2.15Carkit Interrupt Latch (79)4.2.16Carkit Pulse Control (79)4.2.17Transmit Positive Width (80)4.2.18Transmit Negative Width (80)4.2.19Receive Polarity Recovery (80)4.2.20Reserved (81)4.2.21Access Extended Register Set (81)4.2.22Vendor-specific (81)4.3Extended Register Set (81)4.4Register Settings for all Upstream and Downstream signalling modes (81)5.T&MT Connector (83)5.1General (83)5.2Daughter-card (UUT) Specification (83)vFiguresFigure 1 – LPI generic data bus ownership (3)Figure 2 – LPI generic data transmit followed by data receive (3)Figure 3 – Link asserts stp to halt receive data (4)Figure 4 – Creating a ULPI system using wrappers (5)Figure 5 – Block diagram of ULPI PHY (7)Figure 6 – Jitter measurement planes (12)Figure 7 – ULPI timing diagram (13)Figure 8 – Clocking of 4-bit data interface compared to 8-bit interface (14)Figure 9 – Sending of RX CMD (17)Figure 10 – USB data transmit (NOPID) (18)Figure 11 – USB data transmit (PID) (19)Figure 12 – PHY drives an RX CMD to indicate EOP (FS/LS LineState timing not to scale) (20)Figure 13 – Forcing a full/low speed USB transmit error (timing not to scale) (21)Figure 14 – USB receive while dir was previously low (22)Figure 15 – USB receive while dir was previously high (23)Figure 16 – USB receive error detected mid-packet (24)Figure 17 – USB receive error during the last byte (25)Figure 18 – USB HS, FS, and LS bit lengths with respect to clock (26)Figure 19 – HS transmit-to-transmit packet timing (29)Figure 20 – HS receive-to-transmit packet timing (29)Figure 21 – Register write (30)Figure 22 – Register read (31)Figure 23 – Register read or write aborted by USB receive during TX CMD byte (31)Figure 24 – Register read turnaround cycle or Register write data cycle aborted by USB receive (32)Figure 25 – USB receive in same cycle as register read data. USB receive is delayed (33)Figure 26 – Register read followed immediately by a USB receive (33)Figure 27 – Register write followed immediately by a USB receive during stp assertion (34)Figure 28 – Register read followed by a USB receive (34)Figure 29 – Extended register write (35)Figure 30 – Extended register read (35)Figure 31 – Extended register read aborted by USB receive during extended address cycle (36)Figure 32 – PHY aborted by Link asserting stp. Link performs register write or USB transmit (37)Figure 33 – PHY aborted by Link asserting stp. Link performs register read (38)Figure 34 – Link aborts PHY. Link fails to drive a TX CMD. PHY re-asserts dir (38)Figure 35 – Hi-Speed Detection Handshake (Chirp) sequence (timing not to scale) (40)Figure 36 – Preamble sequence (D+/D- timing not to scale) (41)Figure 37 – LS Suspend and Resume (timing not to scale) (43)Figure 38 – FS Suspend and Resume (timing not to scale) (44)Figure 39 – HS Suspend and Resume (timing not to scale) (46)Figure 40 – Low Speed Remote Wake-Up from Low Power Mode (timing not to scale) (47)Figure 41 – Full Speed Remote Wake-Up from Low Power Mode (timing not to scale) (48)Figure 42 – Hi-Speed Remote Wake-Up from Low Power Mode (timing not to scale) (49)Figure 43 – Automatic resume signalling (timing not to scale) (50)Figure 44 – USB packet transmit when OpMode is set to 11b (51)Figure 45 – RX CMD V A_VBUS_VLD ≤Vbus indication source (54)Figure 46 – Entering low power mode (55)Figure 47 – Exiting low power mode when PHY provides output clock (56)Figure 48 – Exiting low power mode when Link provides input clock (56)Figure 49 – PHY stays in Low Power Mode when stp de-asserts before clock starts (57)Figure 50 – PHY re-enters Low Power Mode when stp de-asserts before dir de-asserts (57)Figure 51 – Interface behaviour when entering Serial Mode and clock is powered down (59)Figure 52 – Interface behaviour when entering Serial Mode and clock remains powered (59)Figure 53 – Interface behaviour when exiting Serial Mode and clock is not running (60)Figure 54 – Interface behaviour when exiting Serial Mode and clock is running (60)Figure 55 – PHY interface protected when the clock is running (62)Figure 56 – Power up sequence when PHY powers up before the link. Interface is protected (63)Figure 57 – PHY automatically exits Low Power Mode with interface protected (63)Figure 58 – Link resumes driving ULPI bus and asserts stp because clock is not running (64)viFigure 59 – Power up sequence when link powers up before PHY (ULPI 1.0 compliant links) (64)Figure 60 – Recommended daughter-card configuration (not to scale) (83)viiTablesTable 1 – LPI generic interface signals (2)Table 2 – PHY interface signals (6)Table 3 – Mode summary (9)Table 4 – Clock timing parameters (11)Table 5 – ULPI interface timing (13)Table 6 – Transmit Command (TX CMD) byte format (15)Table 7 – Receive Command (RX CMD) byte format (16)Table 8 – USB specification inter-packet timings (26)Table 9 – PHY pipeline delays (27)Table 10 – Link decision times (28)Table 11 – OTG Control Register power control bits (52)Table 12 – Vbus comparator thresholds (52)Table 13 – RX CMD VbusValid over-current conditions (53)Table 14 – Vbus indicators in the RX CMD required for typical applications (54)Table 15 – Interface signal mapping during Low Power Mode (55)Table 16 – Serial Mode signal mapping for 6-pin FsLsSerialMode (58)Table 17 – Serial Mode signal mapping for 3-pin FsLsSerialMode (58)Table 18 – Carkit signal mapping (61)Table 19 – Register map (66)Table 20 – Register access legend (67)Table 21 – Vendor ID and Product ID register description (67)Table 22 – Function Control register (68)Table 23 – Interface Control register (70)Table 24 – OTG Control register (71)Table 25 – USB Interrupt Enable Rising register (72)Table 26 – USB Interrupt Enable Falling register (73)Table 27 – USB Interrupt Status register (74)Table 28 – USB Interrupt Latch register (75)Table 29 – Rules for setting Interrupt Latch register bits (75)Table 30 – Debug register (76)Table 31 – Scratch register (76)Table 32 – Carkit Control Register (77)Table 33 – Carkit Interrupt Delay register (77)Table 34 – Carkit Interrupt Enable register (78)Table 35 – Carkit Interrupt Status Register (78)Table 36 – Carkit Interrupt Latch register (79)Table 37 – Carkit Pulse Control (79)Table 38 – Transmit Positive Width (80)Table 39 – Transmit Negative Width (80)Table 40 – Receive Polarity Recovery (81)Table 41 – Upstream and downstream signalling modes (82)Table 42 – T&MT connector pin view (84)Table 43 – T&MT connector pin allocation (84)Table 44 – T&MT pin description (85)viii1. Introduction1.1 GeneralThis specification defines a generic PHY interface in Chapter 2.In Chapter 3, the generic interface is applied to the UTMI+ protocol, reducing the pin count for discrete USB transceiver implementations supporting On-The-Go, host, and peripheral application spaces.Convention1.2 NamingEmphasis is placed on normal descriptive text using underlined Arial font, e.g. must.Signal names are represented using the lowercase bold Arial font, e.g. clk.Registers are represented using initial caps, bold Arial font, e.g. OTG Control.Register bits are represented using initial caps, bold italic Arial font, e.g. USB Interrupt Enable Falling. 1.3 Acronyms and TermsA-device Device with a Standard-A or Mini-A plug inserted into its receptacleB-device Device with a Standard-B or Mini-B plug inserted into its receptacleDeviceDRD Dual-RoleFPGA Field Programmable Gate ArraySpeedFS FullHNP Host Negotiation ProtocolHS Hi-SpeedLink ASIC, SIE, or FPGA that connects to an ULPI transceiverLPI Low Pin InterfaceSpeedLS LowOTG On-The-GoPHY Physical Layer (Transceiver)PLL Phase Locked LoopSE0 Single Ended ZeroSIE Serial Interface EngineSRP Session Request ProtocolT&MT Transceiver and Macrocell TesterULPI UTMI+ Low Pin InterfaceUSB Universal Serial BusUSB-IF USB Implementers ForumUTMI USB 2.0 Transceiver Macrocell InteraceUUT Unit Under Test1.4 References[Ref 1] Universal Serial Bus Specification, Revision 2.0[Ref 2] On-The-Go Supplement to the USB 2.0 Specification, Revision 1.0a[Ref 3] USB 2.0 Transceiver Macrocell Interface (UTMI) Specification, v1.05[Ref 4] UTMI+ Specification, Revision 1.0[Ref 5] CEA-2011, OTG Transceiver Specification[Ref 6] CEA-936A, Mini-USB Analog Carkit Interface Specification[Ref 7] USB 2.0 Transceiver and Macrocell Tester (T&MT) Interface Specification, Version 1.212. Generic Low Pin Interface2.1 GeneralThis section describes a generic low pin interface (LPI) between a Link and a PHY. Interface signals are defined and the basic communication protocol is described. The generic interface can be used as a common starting point for defining multiple application-specific interfaces.Chapter 3 defines the UTMI+ Low Pin Interface (ULPI), which is based on the generic interface described here. For ULPI implementations, the definitions in chapter 3 over-ride anything defined in chapter 2.2.2 SignalsThe LPI transceiver interface signals are described in Table 1. The interface described here is generic, and can be used to transport many different data types. Depending on the application, the data stream can be used to transmit and receive packets, access a register set, generate interrupts, and even redefine the interface itself. All interface signals are synchronous when clock is toggling, and asynchronous when clock is not toggling. Data stream definition is application-specific and should be explicitly defined for each application space for inter-operability.Control signals dir, stp, and nxt are specified with the assumption that the PHY is the master of the data bus. If required, an implementation can define the Link as the master. If the Link is the master of the interface, the control signal direction and protocol must be reversed.Signal Direction DescriptionPHY Interfaceclock I/O Interface clock. Both directions are allowed. All interface signals are synchronous to clock.data I/O Bi-directional data bus, driven low by the Link during idle. Bus ownership is determined by dir. The Link and PHY initiate data transfers by driving a non-zero pattern onto the data bus. LPI defines interface timing for single-edge data transfers with respect to rising edge of clock. An implementation may optionally define double-edge data transfers with respect to both rising and falling edges of clock.dir OUT Direction. Controls the direction of the data bus. When the PHY has data to transfer to the Link, it drives dir high to take ownership of the bus. When the PHY has no data to transfer it drives dir low and monitors the bus for Link activity. The PHY pulls dir high whenever the interface cannot accept data from the Link. For example, when the internal PHY PLL is not stable.stp IN Stop. The Link asserts this signal for 1 clock cycle to stop the data stream currently on the bus. If the Link is sending data to the PHY, stp indicates the last byte of data was on the bus in the previous cycle. If the PHY is sending data to the Link, stp forces the PHY to end its transfer, de-assert dir and relinquish control of the the data bus to the Link.nxt OUT Next. The PHY asserts this signal to throttle the data. When the Link is sending data to the PHY, nxt indicates when the current byte has been accepted by the PHY. The Link places the next byte on the data bus in the following clock cycle. When the PHY is sending data to the Link, nxt indicates when a new byte is available for the Link to consume.Table 1 – LPI generic interface signals22.3 ProtocolOwnership2.3.1 BusThe PHY is the master of the LPI bi-directional data bus. Ownership of the data bus is determined by the dir signal from the PHY, as shown in Figure 1. When dir is low, the Link can drive data on the bus. When dir is high, the PHY can drive data on the bus. A change in dir causes a turnaround cycle on the bus during which, neither Link nor PHY can drive the bus. Data during the turnaround cycle is undefined and must be ignored by both Link and PHY.The dir signal can be used to directly control the data output buffers of both PHY and Link.Figure 1 – LPI generic data bus ownershipData2.3.2 TransferringAs shown in the first half of Figure 2, the Link continuously drives the data bus to 00h during idle. The Link transmits data to the PHY by driving a non-zero value on the data bus. To signal the end of data transmission, the Link asserts stp in the cycle following the last data byte.In the second half of Figure 2, the Link receives data when the PHY asserts dir. The PHY asserts dir only when it has data to send to the Link, and keeps dir low at all other times. The PHY drives data to the Link after the turnaround cycle.The nxt signal can be used by the PHY to throttle the data during transmit and receive. During transmit, nxt may be asserted in the same cycle that the Link asserts stp.Figure 2 – LPI generic data transmit followed by data receive2.3.3 AbortingDataThe PHY can assert dir to interrupt any data being transmitted by the Link. If the Link needs to interrupt data being received from the PHY, it asserts stp for one clock cycle, as shown in Figure 3. This causes the PHY to unconditionally1 de-assert dir and accept a complete data transmit from the Link. The PHY may re-assert dir again only when the data transmit from the Link has completed.Figure 3 – Link asserts stp to halt receive data1 The PHY will not de-assert dir if the ULPI interface is not usable. For example, if the internal PLL is not stable.3. UTMI+ Low Pin Interface3.1 GeneralThis section describes how any UTMI+ core can be wrapped to convert it to the smaller LPI interface. The generic interface described in chapter 2 is used as a starting point. This section always over-rides anything stated in chapter 2. While this specification details support of UTMI+ Level 3, PHY implementers may choose to support any of the Levels defined in UTMI+.ULPI defines a PHY to Link interface of 8 or 12 signals that allows a lower pin count option for connecting to an external transceiver that may be based on the UTMI+ specification. The pin count reduction is achieved by having relatively static UTMI+ signals be accessed through registers and by providing a bi-directional data bus that carries USB data and provides a means of accessing register data on the ULPI transceiver.This specification relies on concepts and terminology that are defined in the UTMI+ specification [Ref 4]. Specifically, if a ULPI PHY design is based on an internal UTMI+ core, then that core must implement the following UTMI+ features.Linestate must accurately reflect D+/D- to within 2-3 clocks. It is up to individual Link designers to use Linestate to time bus events.Filtering to prevent spurious SE0/SE1 states appearing on Linestate due to skew between D+ and D-. Filtering of 14 clock cycles is required in Low Speed, and 2 clock cycles in Full Speed and Hi-Speed modes.The PHY must internally block the USB receive path during transmit. The receive path can be unblocked when the internal Squelch (HS) or SE0-to-J (FS/LS) is seen.TxReady must be used for all types of data transmitted, including Chirp.Due to noise on the USB, it is possible that RxActive asserts and then de-asserts without any valid data being received, and RxValid will not assert. The Link should operate normally with these data-less RxActive assertions.As shown in Figure 4, a PHY or Link based on this specification can be implemented as an almost transparent wrapper around existing UTMI+ IP cores, preserving the original UTMI+ packet timing, while reducing pin count and leaving all functionality intact. This should not be taken to imply that other implementations are not possible.Figure 4 – Creating a ULPI system using wrappers3.2 SignalsTable 2 describes the ULPI interface on the PHY. The PHY is always the master of the ULPI bus. USB and Miscellaneous signals may vary with each implementation and are given only as a guide to PHY designers.Signal Direction DescriptionPHY Interfaceclock I/O Interface clock. The PHY must be capable of providing a 60MHz output clock. Support for an input 60MHz clock is optional. If the PHY supports both clock directions, it must not use the ULPI control and data signals for setting the clock direction.Data bus. Driven to 00h by the Link when the ULPI bus is idle. Two bus widths are allowed:• 8-bit data timed on rising edge of clock.data I/O• (Optional) 4-bit data timed on rising and falling edges of clock.dir OUT Controls the direction of the data bus2. The PHY pulls dir high whenever the interface cannot accept data from the Link. For example, when the internal PLL is not stable. This applies whether Link or PHY is the clock source.stp IN The Link must assert stp to signal the end of a USB transmit packet or a register write operation, and optionally to stop any receive. The stp signal must be asserted in the cycle after the last data byte is presented on the bus.nxt OUT The PHY asserts nxt to throttle all data types, except register read data and the RX CMD. Identical to RxValid during USB receive, and TxReady during USB transmit. The PHY also asserts nxt and dir simultaneously to indicate USB receive activity (RxActive), if dir was previously low. The PHY is not allowed to assert nxt during the first cycle of the TX CMD driven by the Link.USB InterfaceD+ I/O D+ pin of the USB cable. Required.D- I/O D- pin of the USB cable. Required.ID IN ID pin of the USB cable. Required for OTG-capable PHY’s.VBUS I/O V BUS pin of the USB cable. Required for OTG-capable PHY’s. Required for driving V BUS and the V BUS comparators.MiscellaneousXI IN Crystal input pin. Vendors should specify supported crystal frequencies. XO OUT Crystal output pin.C+ I/O Positive terminal of charge pump capacitor.C- I/O Negative terminal of charge pump capacitor.SPKR_L IN Optional Carkit left/mono speaker input signal.SPKR_MIC I/O Optional Carkit right speaker input or microphone output signal.RBIAS I/O Bias current resistor.Table 2 – PHY interface signals2 UTMI+ wrapper developers should note that data bus control has been reversed from UTMI to ensure that USB data reception is not interrupted by the Link.3.3 BlockDiagramAn example block diagram of a ULPI PHY is shown in Figure 5. This example is based on an internal UTMI+ Level 3 core [Ref 4], which can interface to peripheral, host, and On-The-Go Link cores. A description of each major block is given below.ULPI InterfaceUSBCableChargePumpCapacitor Figure 5 – Block diagram of ULPI PHYUTMI+ Level 3 PHY coreThe ULPI PHY may contain a core that is compliant to any UTMI+ level [Ref 4]. Signals for 16-bit data buses are not supported in ULPI. While Figure 5 shows the typical blocks for a Level 3 UTMI+ core, the PHY vendor must specify the intended UTMI+ level, and provide the functionality necessary for compliance to that level.ULPI PHY WrapperThe ULPI PHY wrapper of Figure 5 reduces the UTMI+ interface to the Low Pin Interface described in this document. All signals shown on the UTMI+ Level 3 PHY core are reduced to the ULPI interface signals clock, data, dir, stp, and nxt. The Register Map stores the relatively static signals of the UTMI+ interface. Crystal Oscillator and PLLWhen a crystal is attached to the PHY, the internal clock(s) and the external 60MHz interface clock are generated from the internal PLL. When no crystal is attached, the PHY may optionally generate the internal clock(s) from an input 60MHz clock provided by the Link.General BiasingInternal analog circuits require an accurate bias current. This is typically generated using an external, accurate reference resistor.DrvVbusExternal and ExternalVbusIndicatorThe PHY may optionally control an external VBUS power source via the optional pin DrvVbusExternal. For example, the external supply could be a charge pump or 5V power supply controlled using a power switch. The external supply is controlled by the DrvVbus and the optional DrvVbusExternal bits in the OTG Control register. The polarity of the DrvVbusExternal output pin is implementation dependent.If control of an external VBUS source is provided the PHY may optionally provide for a VBUS power source feed back signal on the optional pin ExternalVbusIndicator. If this pin is provided, the use of the pin is defined by the optional control bits in the OTG Control and Interface Control registers. See Section 3.8.6.3 for further detail.Power-On-ResetA power-on-reset circuit must be provided in the PHY. When power is first applied to the PHY, the power-on-reset will reset all circuitry and leave the ULPI interface in a usable state.Carkit OptionThe PHY may optionally support Carkit Mode [Ref 6]. While in Carkit Mode, the PHY routes speaker and microphone signals between the Link and the USB cable. In carkit mono mode, SPKR_L inputs a mono speaker signal and SPKR_MIC outputs the microphone signal, MIC. In carkit stereo mode, SPKR_L inputs the left speaker signal, and SPKR_MIC inputs the right speaker signal, SPKR_R.3.4 ModesThe ULPI interface can operate in one of five independent modes listed in Table 3. The interface is in Synchronous Mode by default. Other modes are enabled by bits in the Function Control and Interface Control registers. In Synchronous Mode, the data bus carries commands and data. In other modes, the data pins are redefined with different functionality. Synchronous Mode and Low Power Mode are mandatory.Mode Name Mode DescriptionSynchronous Mode This is the normal mode of operation. The clock is running and is stablewith the characteristics defined in section 3.6. The ULPI interface carriescommands and data that are synchronous to clock.Low Power Mode The PHY is powered down with the clock stopped. The PHY keeps dirasserted, and the data bus is redefined to carry LineState and interrupts.See section 3.9 for more information.6-pin FS/LS Serial Mode (optional) The data bus is redefined to 6-pin serial mode, including 6 pins to transmit and receive serial USB data, and 1 pin to signal interrupt events. The clock can be enabled or disabled. This mode is valid only for implementations with an 8-bit data bus. See section 3.10 for more information.3-pin FS/LS Serial Mode (optional) The data bus is redefined to 3-pin serial mode, including 3 pins to transmit and receive serial USB data, and 1 pin to signal interrupt events. The clock can be enabled or disabled. See section 3.10 for more information.Carkit Mode (optional) The data bus is redefined to Carkit mode [Ref 6], including 2 pins for serial UART data, and 1 pin to signal interrupt events. The clock may optionally be stopped. See section 3.11 for more information.Table 3 – Mode summary。

elvis 运算符 -回复

elvis 运算符-回复Elvis operator, also known as the ternary operator, is a conditional operator used in programming languages to simplify conditional expressions. Its syntax is often represented as `[condition] ? [value_if_true] : [value_if_false]`. In this article, we will discuss the Elvis operator, how it works, its advantages and disadvantages, and some examples to illustrate its usage.The Elvis operator is particularly useful when evaluating and assigning values based on a condition. It provides a concise and readable way to handle conditional assignments in a single line of code. It is often used as an alternative to traditional if-else statements for simpler conditional checks.To understand how the Elvis operator works, let's break down its components. The condition placed within the square brackets `[]` is the expression that evaluates to either true or false. If the condition is true, the value before the `:` is returned; otherwise, the value after the `:` is returned. This allows us to assign different values based on the outcome of the condition.One of the main advantages of using the Elvis operator is its brevity.By condensing the condition and assignment into a single line of code, it improves code readability and reduces the need for extensive if-else statements. This makes the code more concise and easier to understand. In addition, the Elvis operator promotes a more functional programming style by enabling the use of functional constructs such as mapping or filtering without the need for explicit if checks.Another advantage of the Elvis operator is that it can handle null values efficiently. When used in conjunction with null check expressions, it allows for a more graceful handling of null values without the need for additional code blocks. It simplifies the process of assigning default values or fallback options when dealing with nullable variables.However, it is important to consider the Elvis operator's limitations and potential disadvantages. One limitation is that it can only handle binary conditions. It is not suitable for complex conditions that require multiple branches or nested if statements. In such cases, using traditional if-else statements may be more appropriate.Moreover, excessive use of the Elvis operator can lead to code that is difficult to read and maintain. While it is a concise way to handle simple conditional assignments, overreliance on the operator can make the code less explicit and more prone to errors. Therefore, it is recommended to use the Elvis operator judiciously and prioritize code readability and maintainability.Let's now look at some practical examples to better understand the Elvis operator's usage. Consider the following code snippet in Python:pythonx = 10y = 20 if x > 5 else 30print(y)In this example, if the condition `x > 5` evaluates to true, the value `20` is assigned to `y`. Otherwise, the value `30` is assigned to `y`. The resulting output will be `20`, as `x` is indeed greater than `5`.Now let's consider a scenario where we want to assign a defaultvalue to a variable only if it is currently `null`. We can accomplish this using the Elvis operator in the following manner:javaString name = existingName != null ? existingName : "Default";In this example, if `existingName` is not `null`, it will be assigned to `name`. Otherwise, the value `"Default"` is assigned to `name`. This allows for a concise and efficient handling of null values without the need for additional checks or code blocks.In conclusion, the Elvis operator is a powerful and concise tool for handling conditional assignments. It provides a simplified syntax to evaluate conditions and assign values based on the outcome. While it has its limitations and should be used judiciously, the operator offers significant benefits in terms of code readability and null value handling. By understanding its usage and considering its advantages and disadvantages, developers can leverage the Elvis operator to write more concise and efficient code.。

Multicamera People Tracking with a Probabilistic Occupancy Map

Multicamera People Tracking witha Probabilistic Occupancy MapFranc¸ois Fleuret,Je´roˆme Berclaz,Richard Lengagne,and Pascal Fua,Senior Member,IEEE Abstract—Given two to four synchronized video streams taken at eye level and from different angles,we show that we can effectively combine a generative model with dynamic programming to accurately follow up to six individuals across thousands of frames in spite of significant occlusions and lighting changes.In addition,we also derive metrically accurate trajectories for each of them.Our contribution is twofold.First,we demonstrate that our generative model can effectively handle occlusions in each time frame independently,even when the only data available comes from the output of a simple background subtraction algorithm and when the number of individuals is unknown a priori.Second,we show that multiperson tracking can be reliably achieved by processing individual trajectories separately over long sequences,provided that a reasonable heuristic is used to rank these individuals and that we avoid confusing them with one another.Index Terms—Multipeople tracking,multicamera,visual surveillance,probabilistic occupancy map,dynamic programming,Hidden Markov Model.Ç1I NTRODUCTIONI N this paper,we address the problem of keeping track of people who occlude each other using a small number of synchronized videos such as those depicted in Fig.1,which were taken at head level and from very different angles. This is important because this kind of setup is very common for applications such as video surveillance in public places.To this end,we have developed a mathematical framework that allows us to combine a robust approach to estimating the probabilities of occupancy of the ground plane at individual time steps with dynamic programming to track people over time.This results in a fully automated system that can track up to six people in a room for several minutes by using only four cameras,without producing any false positives or false negatives in spite of severe occlusions and lighting variations. As shown in Fig.2,our system also provides location estimates that are accurate to within a few tens of centimeters, and there is no measurable performance decrease if as many as20percent of the images are lost and only a small one if 30percent are.This involves two algorithmic steps:1.We estimate the probabilities of occupancy of theground plane,given the binary images obtained fromthe input images via background subtraction[7].Atthis stage,the algorithm only takes into accountimages acquired at the same time.Its basic ingredientis a generative model that represents humans assimple rectangles that it uses to create synthetic idealimages that we would observe if people were at givenlocations.Under this model of the images,given thetrue occupancy,we approximate the probabilities ofoccupancy at every location as the marginals of aproduct law minimizing the Kullback-Leibler diver-gence from the“true”conditional posterior distribu-tion.This allows us to evaluate the probabilities ofoccupancy at every location as the fixed point of alarge system of equations.2.We then combine these probabilities with a color and amotion model and use the Viterbi algorithm toaccurately follow individuals across thousands offrames[3].To avoid the combinatorial explosion thatwould result from explicitly dealing with the jointposterior distribution of the locations of individuals ineach frame over a fine discretization,we use a greedyapproach:we process trajectories individually oversequences that are long enough so that using areasonable heuristic to choose the order in which theyare processed is sufficient to avoid confusing peoplewith each other.In contrast to most state-of-the-art algorithms that recursively update estimates from frame to frame and may therefore fail catastrophically if difficult conditions persist over several consecutive frames,our algorithm can handle such situations since it computes the global optima of scores summed over many frames.This is what gives it the robustness that Fig.2demonstrates.In short,we combine a mathematically well-founded generative model that works in each frame individually with a simple approach to global optimization.This yields excellent performance by using basic color and motion models that could be further improved.Our contribution is therefore twofold.First,we demonstrate that a generative model can effectively handle occlusions at each time frame independently,even when the input data is of very poor quality,and is therefore easy to obtain.Second,we show that multiperson tracking can be reliably achieved by processing individual trajectories separately over long sequences.. F.Fleuret,J.Berclaz,and P.Fua are with the Ecole Polytechnique Fe´de´ralede Lausanne,Station14,CH-1015Lausanne,Switzerland.E-mail:{francois.fleuret,jerome.berclaz,pascal.fua}@epfl.ch..R.Lengagne is with GE Security-VisioWave,Route de la Pierre22,1024Ecublens,Switzerland.E-mail:richard.lengagne@.Manuscript received14July2006;revised19Jan.2007;accepted28Mar.2007;published online15May2007.Recommended for acceptance by S.Sclaroff.For information on obtaining reprints of this article,please send e-mail to:tpami@,and reference IEEECS Log Number TPAMI-0521-0706.Digital Object Identifier no.10.1109/TPAMI.2007.1174.0162-8828/08/$25.00ß2008IEEE Published by the IEEE Computer SocietyIn the remainder of the paper,we first briefly review related works.We then formulate our problem as estimat-ing the most probable state of a hidden Markov process and propose a model of the visible signal based on an estimate of an occupancy map in every time frame.Finally,we present our results on several long sequences.2R ELATED W ORKState-of-the-art methods can be divided into monocular and multiview approaches that we briefly review in this section.2.1Monocular ApproachesMonocular approaches rely on the input of a single camera to perform tracking.These methods provide a simple and easy-to-deploy setup but must compensate for the lack of 3D information in a single camera view.2.1.1Blob-Based MethodsMany algorithms rely on binary blobs extracted from single video[10],[5],[11].They combine shape analysis and tracking to locate people and maintain appearance models in order to track them,even in the presence of occlusions.The Bayesian Multiple-BLob tracker(BraMBLe)system[12],for example,is a multiblob tracker that generates a blob-likelihood based on a known background model and appearance models of the tracked people.It then uses a particle filter to implement the tracking for an unknown number of people.Approaches that track in a single view prior to computing correspondences across views extend this approach to multi camera setups.However,we view them as falling into the same category because they do not simultaneously exploit the information from multiple views.In[15],the limits of the field of view of each camera are computed in every other camera from motion information.When a person becomes visible in one camera,the system automatically searches for him in other views where he should be visible.In[4],a background/foreground segmentation is performed on calibrated images,followed by human shape extraction from foreground objects and feature point selection extraction. Feature points are tracked in a single view,and the system switches to another view when the current camera no longer has a good view of the person.2.1.2Color-Based MethodsTracking performance can be significantly increased by taking color into account.As shown in[6],the mean-shift pursuit technique based on a dissimilarity measure of color distributions can accurately track deformable objects in real time and in a monocular context.In[16],the images are segmented pixelwise into different classes,thus modeling people by continuously updated Gaussian mixtures.A standard tracking process is then performed using a Bayesian framework,which helps keep track of people,even when there are occlusions.In such a case,models of persons in front keep being updated, whereas the system stops updating occluded ones,which may cause trouble if their appearances have changed noticeably when they re-emerge.More recently,multiple humans have been simulta-neously detected and tracked in crowded scenes[20]by using Monte-Carlo-based methods to estimate their number and positions.In[23],multiple people are also detected and tracked in front of complex backgrounds by using mixture particle filters guided by people models learned by boosting.In[9],multicue3D object tracking is addressed by combining particle-filter-based Bayesian tracking and detection using learned spatiotemporal shapes.This ap-proach leads to impressive results but requires shape, texture,and image depth information as input.Finally, Smith et al.[25]propose a particle-filtering scheme that relies on Markov chain Monte Carlo(MCMC)optimization to handle entrances and departures.It also introduces a finer modeling of interactions between individuals as a product of pairwise potentials.2.2Multiview ApproachesDespite the effectiveness of such methods,the use of multiple cameras soon becomes necessary when one wishes to accurately detect and track multiple people and compute their precise3D locations in a complex environment. Occlusion handling is facilitated by using two sets of stereo color cameras[14].However,in most approaches that only take a set of2D views as input,occlusion is mainly handled by imposing temporal consistency in terms of a motion model,be it Kalman filtering or more general Markov models.As a result,these approaches may not always be able to recover if the process starts diverging.2.2.1Blob-Based MethodsIn[19],Kalman filtering is applied on3D points obtained by fusing in a least squares sense the image-to-world projections of points belonging to binary blobs.Similarly,in[1],a Kalman filter is used to simultaneously track in2D and3D,and objectFig.1.Images from two indoor and two outdoor multicamera video sequences that we use for our experiments.At each time step,we draw a box around people that we detect and assign to them an ID number that follows them throughout thesequence.Fig.2.Cumulative distributions of the position estimate error on a3,800-frame sequence(see Section6.4.1for details).locations are estimated through trajectory prediction during occlusion.In[8],a best hypothesis and a multiple-hypotheses approaches are compared to find people tracks from 3D locations obtained from foreground binary blobs ex-tracted from multiple calibrated views.In[21],a recursive Bayesian estimation approach is used to deal with occlusions while tracking multiple people in multiview.The algorithm tracks objects located in the intersections of2D visual angles,which are extracted from silhouettes obtained from different fixed views.When occlusion ambiguities occur,multiple occlusion hypotheses are generated,given predicted object states and previous hypotheses,and tested using a branch-and-merge strategy. The proposed framework is implemented using a customized particle filter to represent the distribution of object states.Recently,Morariu and Camps[17]proposed a method based on dimensionality reduction to learn a correspondence between the appearance of pedestrians across several views. This approach is able to cope with the severe occlusion in one view by exploiting the appearance of the same pedestrian on another view and the consistence across views.2.2.2Color-Based MethodsMittal and Davis[18]propose a system that segments,detects, and tracks multiple people in a scene by using a wide-baseline setup of up to16synchronized cameras.Intensity informa-tion is directly used to perform single-view pixel classifica-tion and match similarly labeled regions across views to derive3D people locations.Occlusion analysis is performed in two ways:First,during pixel classification,the computa-tion of prior probabilities takes occlusion into account. Second,evidence is gathered across cameras to compute a presence likelihood map on the ground plane that accounts for the visibility of each ground plane point in each view. Ground plane locations are then tracked over time by using a Kalman filter.In[13],individuals are tracked both in image planes and top view.The2D and3D positions of each individual are computed so as to maximize a joint probability defined as the product of a color-based appearance model and2D and 3D motion models derived from a Kalman filter.2.2.3Occupancy Map MethodsRecent techniques explicitly use a discretized occupancy map into which the objects detected in the camera images are back-projected.In[2],the authors rely on a standard detection of stereo disparities,which increase counters associated to square areas on the ground.A mixture of Gaussians is fitted to the resulting score map to estimate the likely location of individuals.This estimate is combined with a Kallman filter to model the motion.In[26],the occupancy map is computed with a standard visual hull procedure.One originality of the approach is to keep for each resulting connex component an upper and lower bound on the number of objects that it can contain. Based on motion consistency,the bounds on the various components are estimated at a certain time frame based on the bounds of the components at the previous time frame that spatially intersect with it.Although our own method shares many features with these techniques,it differs in two important respects that we will highlight:First,we combine the usual color and motion models with a sophisticated approach based on a generative model to estimating the probabilities of occu-pancy,which explicitly handles complex occlusion interac-tions between detected individuals,as will be discussed in Section5.Second,we rely on dynamic programming to ensure greater stability in challenging situations by simul-taneously handling multiple frames.3P ROBLEM F ORMULATIONOur goal is to track an a priori unknown number of people from a few synchronized video streams taken at head level. In this section,we formulate this problem as one of finding the most probable state of a hidden Markov process,given the set of images acquired at each time step,which we will refer to as a temporal frame.We then briefly outline the computation of the relevant probabilities by using the notations summarized in Tables1and2,which we also use in the following two sections to discuss in more details the actual computation of those probabilities.3.1Computing the Optimal TrajectoriesWe process the video sequences by batches of T¼100frames, each of which includes C images,and we compute the most likely trajectory for each individual.To achieve consistency over successive batches,we only keep the result on the first 10frames and slide our temporal window.This is illustrated in Fig.3.We discretize the visible part of the ground plane into a finite number G of regularly spaced2D locations and we introduce a virtual hidden location H that will be used to model entrances and departures from and into the visible area.For a given batch,let L t¼ðL1t;...;L NÃtÞbe the hidden stochastic processes standing for the locations of individuals, whether visible or not.The number NÃstands for the maximum allowable number of individuals in our world.It is large enough so that conditioning on the number of visible ones does not change the probability of a new individual entering the scene.The L n t variables therefore take values in f1;...;G;Hg.Given I t¼ðI1t;...;I C tÞ,the images acquired at time t for 1t T,our task is to find the values of L1;...;L T that maximizePðL1;...;L T j I1;...;I TÞ:ð1ÞAs will be discussed in Section 4.1,we compute this maximum a posteriori in a greedy way,processing one individual at a time,including the hidden ones who can move into the visible scene or not.For each one,the algorithm performs the computation,under the constraint that no individual can be at a visible location occupied by an individual already processed.In theory,this approach could lead to undesirable local minima,for example,by connecting the trajectories of two separate people.However,this does not happen often because our batches are sufficiently long.To further reduce the chances of this,we process individual trajectories in an order that depends on a reliability score so that the most reliable ones are computed first,thereby reducing the potential for confusion when processing the remaining ones. This order also ensures that if an individual remains in the hidden location,then all the other people present in the hidden location will also stay there and,therefore,do not need to be processed.FLEURET ET AL.:MULTICAMERA PEOPLE TRACKING WITH A PROBABILISTIC OCCUPANCY MAP269Our experimental results show that our method does not suffer from the usual weaknesses of greedy algorithms such as a tendency to get caught in bad local minima.We thereforebelieve that it compares very favorably to stochastic optimization techniques in general and more specifically particle filtering,which usually requires careful tuning of metaparameters.3.2Stochastic ModelingWe will show in Section 4.2that since we process individual trajectories,the whole approach only requires us to define avalid motion model P ðL n t þ1j L nt ¼k Þand a sound appearance model P ðI t j L n t ¼k Þ.The motion model P ðL n t þ1j L nt ¼k Þ,which will be intro-duced in Section 4.3,is a distribution into a disc of limited radiusandcenter k ,whichcorresponds toalooseboundonthe maximum speed of a walking human.Entrance into the scene and departure from it are naturally modeled,thanks to the270IEEE TRANSACTIONS ON PATTERN ANALYSIS AND MACHINE INTELLIGENCE,VOL.30,NO.2,FEBRUARY 2008TABLE 2Notations (RandomQuantities)Fig.3.Video sequences are processed by batch of 100frames.Only the first 10percent of the optimization result is kept and the rest is discarded.The temporal window is then slid forward and the optimiza-tion is repeated on the new window.TABLE 1Notations (DeterministicQuantities)hiddenlocation H,forwhichweextendthemotionmodel.The probabilities to enter and to leave are similar to the transition probabilities between different ground plane locations.In Section4.4,we will show that the appearance model PðI t j L n t¼kÞcan be decomposed into two terms.The first, described in Section4.5,is a very generic color-histogram-based model for each individual.The second,described in Section5,approximates the marginal conditional probabil-ities of occupancy of the ground plane,given the results of a background subtractionalgorithm,in allviewsacquired atthe same time.This approximation is obtained by minimizing the Kullback-Leibler divergence between a product law and the true posterior.We show that this is equivalent to computing the marginal probabilities of occupancy so that under the product law,the images obtained by putting rectangles of human sizes at occupied locations are likely to be similar to the images actually produced by the background subtraction.This represents a departure from more classical ap-proaches to estimating probabilities of occupancy that rely on computing a visual hull[26].Such approaches tend to be pessimistic and do not exploit trade-offs between the presence of people at different locations.For instance,if due to noise in one camera,a person is not seen in a particular view,then he would be discarded,even if he were seen in all others.By contrast,in our probabilistic framework,sufficient evidence might be present to detect him.Similarly,the presence of someone at a specific location creates an occlusion that hides the presence behind,which is not accounted for by the hull techniques but is by our approach.Since these marginal probabilities are computed indepen-dently at each time step,they say nothing about identity or correspondence with past frames.The appearance similarity is entirely conveyed by the color histograms,which has experimentally proved sufficient for our purposes.4C OMPUTATION OF THE T RAJECTORIESIn Section4.1,we break the global optimization of several people’s trajectories into the estimation of optimal individual trajectories.In Section 4.2,we show how this can be performed using the classical Viterbi’s algorithm based on dynamic programming.This requires a motion model given in Section 4.3and an appearance model described in Section4.4,which combines a color model given in Section4.5 and a sophisticated estimation of the ground plane occu-pancy detailed in Section5.We partition the visible area into a regular grid of G locations,as shown in Figs.5c and6,and from the camera calibration,we define for each camera c a family of rectangular shapes A c1;...;A c G,which correspond to crude human silhouettes of height175cm and width50cm located at every position on the grid.4.1Multiple TrajectoriesRecall that we denote by L n¼ðL n1;...;L n TÞthe trajectory of individual n.Given a batch of T temporal frames I¼ðI1;...;I TÞ,we want to maximize the posterior conditional probability:PðL1¼l1;...;L Nül NÃj IÞ¼PðL1¼l1j IÞY NÃn¼2P L n¼l n j I;L1¼l1;...;L nÀ1¼l nÀ1ÀÁ:ð2ÞSimultaneous optimization of all the L i s would beintractable.Instead,we optimize one trajectory after theother,which amounts to looking for^l1¼arg maxlPðL1¼l j IÞ;ð3Þ^l2¼arg maxlPðL2¼l j I;L1¼^l1Þ;ð4Þ...^l Nüarg maxlPðL Nül j I;L1¼^l1;L2¼^l2;...Þ:ð5ÞNote that under our model,conditioning one trajectory,given other ones,simply means that it will go through noalready occupied location.In other words,PðL n¼l j I;L1¼^l1;...;L nÀ1¼^l nÀ1Þ¼PðL n¼l j I;8k<n;8t;L n t¼^l k tÞ;ð6Þwhich is PðL n¼l j IÞwith a reduced set of the admissiblegrid locations.Such a procedure is recursively correct:If all trajectoriesestimated up to step n are correct,then the conditioning onlyimproves the estimate of the optimal remaining trajectories.This would suffice if the image data were informative enoughso that locations could be unambiguously associated toindividuals.In practice,this is obviously rarely the case.Therefore,this greedy approach to optimization has un-desired side effects.For example,due to partly missinglocalization information for a given trajectory,the algorithmmight mistakenly start following another person’s trajectory.This is especially likely to happen if the tracked individualsare located close to each other.To avoid this kind of failure,we process the images bybatches of T¼100and first extend the trajectories that havebeen found with high confidence,as defined below,in theprevious batches.We then process the lower confidenceones.As a result,a trajectory that was problematic in thepast and is likely to be problematic in the current batch willbe optimized last and,thus,prevented from“stealing”somebody else’s location.Furthermore,this approachincreases the spatial constraints on such a trajectory whenwe finally get around to estimating it.We use as a confidence score the concordance of theestimated trajectories in the previous batches and thelocalization cue provided by the estimation of the probabil-istic occupancy map(POM)described in Section5.Moreprecisely,the score is the number of time frames where theestimated trajectory passes through a local maximum of theestimated probability of occupancy.When the POM does notdetect a person on a few frames,the score will naturallydecrease,indicating a deterioration of the localizationinformation.Since there is a high degree of overlappingbetween successive batches,the challenging segment of atrajectory,which is due to the failure of the backgroundsubtraction or change in illumination,for instance,is met inseveral batches before it actually happens during the10keptframes.Thus,the heuristic would have ranked the corre-sponding individual in the last ones to be processed whensuch problem occurs.FLEURET ET AL.:MULTICAMERA PEOPLE TRACKING WITH A PROBABILISTIC OCCUPANCY MAP2714.2Single TrajectoryLet us now consider only the trajectory L n ¼ðL n 1;...;L nT Þof individual n over T temporal frames.We are looking for thevalues ðl n 1;...;l nT Þin the subset of free locations of f 1;...;G;Hg .The initial location l n 1is either a known visible location if the individual is visible in the first frame of the batch or H if he is not.We therefore seek to maximizeP ðL n 1¼l n 1;...;L n T ¼l nt j I 1;...;I T Þ¼P ðI 1;L n 1¼l n 1;...;I T ;L n T ¼l nT ÞP ðI 1;...;I T Þ:ð7ÞSince the denominator is constant with respect to l n ,we simply maximize the numerator,that is,the probability of both the trajectories and the images.Let us introduce the maximum of the probability of both the observations and the trajectory ending up at location k at time t :Èt ðk Þ¼max l n 1;...;l nt À1P ðI 1;L n 1¼l n 1;...;I t ;L nt ¼k Þ:ð8ÞWe model jointly the processes L n t and I t with a hidden Markov model,that isP ðL n t þ1j L n t ;L n t À1;...Þ¼P ðL n t þ1j L nt Þð9ÞandP ðI t ;I t À1;...j L n t ;L nt À1;...Þ¼YtP ðI t j L n t Þ:ð10ÞUnder such a model,we have the classical recursive expressionÈt ðk Þ¼P ðI t j L n t ¼k Þ|fflfflfflfflfflfflfflfflffl{zfflfflfflfflfflfflfflfflffl}Appearance modelmax P ðL n t ¼k j L nt À1¼ Þ|fflfflfflfflfflfflfflfflfflfflfflfflfflfflfflfflffl{zfflfflfflfflfflfflfflfflfflfflfflfflfflfflfflfflffl}Motion modelÈt À1ð Þð11Þto perform a global search with dynamic programming,which yields the classic Viterbi algorithm.This is straight-forward,since the L n t s are in a finite set of cardinality G þ1.4.3Motion ModelWe chose a very simple and unconstrained motion model:P ðL n t ¼k j L nt À1¼ Þ¼1=Z Áe À k k À k if k k À k c 0otherwise ;&ð12Þwhere the constant tunes the average human walkingspeed,and c limits the maximum allowable speed.This probability is isotropic,decreases with the distance from location k ,and is zero for k k À k greater than a constantmaximum distance.We use a very loose maximum distance cof one square of the grid per frame,which corresponds to a speed of almost 12mph.We also define explicitly the probabilities of transitions to the parts of the scene that are connected to the hidden location H .This is a single door in the indoor sequences and all the contours of the visible area in the outdoor sequences in Fig.1.Thus,entrance and departure of individuals are taken care of naturally by the estimation of the maximum a posteriori trajectories.If there are enough evidence from the images that somebody enters or leaves the room,then this procedure will estimate that the optimal trajectory does so,and a person will be added to or removed from the visible area.4.4Appearance ModelFrom the input images I t ,we use background subtraction to produce binary masks B t such as those in Fig.4.We denote as T t the colors of the pixels inside the blobs and treat the rest of the images as background,which is ignored.Let X tk be a Boolean random variable standing for the presence of an individual at location k of the grid at time t .In Appendix B,we show thatP ðI t j L n t ¼k Þzfflfflfflfflfflfflfflfflffl}|fflfflfflfflfflfflfflfflffl{Appearance model/P ðL n t ¼k j X kt ¼1;T t Þ|fflfflfflfflfflfflfflfflfflfflfflfflfflfflfflfflfflffl{zfflfflfflfflfflfflfflfflfflfflfflfflfflfflfflfflfflffl}Color modelP ðX kt ¼1j B t Þ|fflfflfflfflfflfflfflfflfflfflffl{zfflfflfflfflfflfflfflfflfflfflffl}Ground plane occupancy:ð13ÞThe ground plane occupancy term will be discussed in Section 5,and the color model term is computed as follows.4.5Color ModelWe assume that if someone is present at a certain location k ,then his presence influences the color of the pixels located at the intersection of the moving blobs and the rectangle A c k corresponding to the location k .We model that dependency as if the pixels were independent and identically distributed and followed a density in the red,green,and blue (RGB)space associated to the individual.This is far simpler than the color models used in either [18]or [13],which split the body area in several subparts with dedicated color distributions,but has proved sufficient in practice.If an individual n was present in the frames preceding the current batch,then we have an estimation for any camera c of his color distribution c n ,since we have previously collected the pixels in all frames at the locations272IEEE TRANSACTIONS ON PATTERN ANALYSIS AND MACHINE INTELLIGENCE,VOL.30,NO.2,FEBRUARY2008Fig.4.The color model relies on a stochastic modeling of the color of the pixels T c t ðk Þsampled in the intersection of the binary image B c t produced bythe background subtraction and the rectangle A ck corresponding to the location k .。

Formal Description of OCL Specification Patterns for Behavioral Specification of Software C