PMOS开关管的选择与电路图

pmos和noms管的电路符号

pmos和noms管的电路符号在电子电路中,PMOS(P型金属氧化物半导体场效应晶体管)和NMOS(N型金属氧化物半导体场效应晶体管)是常见的器件类型,它们在数字和模拟电路中都扮演着重要的角色。

了解它们的电路符号对于理解和设计电子电路至关重要。

1. PMOS管的电路符号PMOS管由P型衬底和N型栅极构成,其电路符号通常表示为一个P 型晶体管符号,同时在符号上方标示一个小的圆圈,表示P型晶体管的栅极连接至电源端(即VDD)。

PMOS管的电路符号如下所示:[示意图]2. NMOS管的电路符号相对于PMOS管,NMOS管的结构是N型衬底和P型栅极构成,其电路符号通常表示为一个N型晶体管符号,同时在符号上方标示一个小的圆圈,表示N型晶体管的栅极连接至地端(即VSS)。

NMOS管的电路符号如下所示:[示意图]在电路设计中,PMOS和NMOS管经常一起使用,构成CMOS(互补金属氧化物半导体)电路。

在CMOS电路中,PMOS和NMOS管可以根据逻辑需求进行串联或并联,实现不同的功能。

总结回顾通过本文的介绍,我们了解了PMOS和NMOS管的电路符号以及它们的工作原理。

PMOS管的符号由P型晶体管符号和一个在上方的小圆圈组成,表示栅极连接至电源端;NMOS管的符号由N型晶体管符号和一个在上方的小圆圈组成,表示栅极连接至地端。

在CMOS电路中,PMOS和NMOS管经常一起使用,以实现不同的逻辑功能。

个人观点和理解对于电子电路工程师来说,深入理解PMOS和NMOS管的电路符号及其工作原理至关重要。

掌握这些知识可以帮助工程师更好地设计和分析数字电路,确保电路的可靠性和稳定性。

在实际工作中,我发现对PMOS和NMOS管的电路符号有一个清晰的认识,可以更快速、准确地理解和解决电路设计中的问题。

我建议花一些时间来学习和熟悉这些符号,这将对在电子电路领域取得成功有很大帮助。

在今后的工作中,我将继续深入学习电子电路知识,不断提升自己的技能和能力,为电路设计和分析提供更专业、高质量的支持。

pmos逻辑

PMOS逻辑1. 什么是PMOS逻辑?PMOS逻辑是一种基于PMOS(P型金属氧化物半导体)晶体管的逻辑电路设计方法。

在PMOS逻辑中,PMOS晶体管被用作开关来实现逻辑功能。

PMOS逻辑是早期的MOS逻辑家族之一,与NMOS逻辑相对应。

与NMOS逻辑使用NMOS晶体管作为开关不同,PMOS逻辑使用PMOS晶体管作为开关。

2. PMOS逻辑的特点PMOS逻辑具有以下特点: - PMOS逻辑使用PMOS晶体管作为开关,当输入为低电平时,PMOS晶体管导通,输出为高电平;当输入为高电平时,PMOS晶体管截断,输出为低电平。

- PMOS逻辑的输入电平与输出电平相反,即输入为低电平时,输出为高电平;输入为高电平时,输出为低电平。

- PMOS逻辑的输入电阻较高,输出电阻较低。

- PMOS逻辑的功耗较高,速度较慢,不适用于高速应用。

3. PMOS逻辑的基本电路PMOS逻辑电路可以由PMOS晶体管和电阻构成。

常见的PMOS逻辑电路包括PMOS反相器(PMOS Inverter)、PMOS与门(PMOS AND Gate)和PMOS或门(PMOS OR Gate)。

3.1 PMOS反相器PMOS反相器由一个PMOS晶体管和一个电阻组成。

当输入为低电平时,PMOS晶体管导通,输出为高电平;当输入为高电平时,PMOS晶体管截断,输出为低电平。

具体电路图如下所示:VDD││─┼─│─┼─│┼─── Output│┴PMOS│Input3.2 PMOS与门PMOS与门由多个PMOS晶体管组成。

当所有输入为低电平时,所有PMOS晶体管导通,输出为高电平;当任一输入为高电平时,对应PMOS晶体管截断,输出为低电平。

具体电路图如下所示:VDD││─┼─ ─┬─│ │─┼─ ││ │┼─── Output│ │┴ │PMOS ││ │Input1 Input23.3 PMOS或门PMOS或门由多个PMOS晶体管组成。

当任一输入为低电平时,对应PMOS晶体管导通,输出为高电平;当所有输入为高电平时,所有PMOS晶体管截断,输出为低电平。

PMOS管用作电源开关注意事项

PMOS管⽤作电源开关注意事项

PMOS管⽤作电源开关注意事项:PMOS管作电源开关时因开关速度过快导致电源被拉下。

最近在设计电路时踩了⼀个坑,给⼤家分享下。

在电路中⽤到了三极管和MOS管做电源开关,原有问题电路如下图:POWER_RESET为⾼,Q4和Q2均导通,电源接通;

POWER_RESET为低时,Q4和Q2均不导通,电源不通。

做好PCB板,焊上相应器件,上电发现电路⼯作不正常,表现为,在POWER_RESET突然变⾼时,即电源3V3突然接通时,前级电源DCDC_3V3被拉下。

⽤⽰波器测量如下:

那么是为什么呢?原因是因为开关的开启速度过快,瞬间导通,⽽后级3V3电源有很多电路均在使⽤,会接了很多滤波电容,总电容量很⼤。

在电源突然接通的时候,需要对这些电容进⾏充电,电容量⼤,导致刚开始需要的电流很⼤,⽽前级来不及提供,导致电源被拉下。

知道了问题的原因,那么如何修正呢?那就需要让开关不能打开过快,需要慢慢打开。

改进电路如下。

⾸先C169可以让Q4导通时间变缓,这是⼀⽅⾯。

然后C168和R171可以让Q3导通变缓。

Q4导通前Q3的Vgs=0。

当Q4由不导通变为导通时,因为Q3的GS上⾯有电容,电容两端电压不能突变,Q3的G极不会马上被拉低,⽽是需要通过R171对电容C168和C167进⾏充电,充电的过程就是G极电压变低的过程,即Vgs是慢慢变化的,所以Q3也是慢慢导通的,开启的速度取决于C167和C168及R171的值。

pmos管原理

pmos管原理

PMOS (Positive-channel Metal-oxide-semiconductor)是一种常用

的MOSFET (Metal-Oxide-Semiconductor Field-Effect Transistor) 类型。

它是一种开关(或放大)电路元件。

PMOS的原理如下:

1. 结构:PMOS管有一个P型半导体基底,两个N型别廉电

极(Source和Drain)和一个强加正电压的闸极(Gate)。

2. 工作方式:当Gate极上加一个负电压时,PMOS中形成的

电场会修护阻止电子从Drain流入Source,从而PMOS处于关闭状态。

3. 当Gate电极上的电压为零,或者Grounded时,将源极接地,就会形成一个强的P型层到N型层的电荷的吸引,PMOS处

于导通状态,电流可以从Drain到Source流动。

4. 控制:通过改变Gate电极上的电压,可以控制PMOS的导

通或截止状态。

负电压会导致截止,而零电压或接地则会导致导通。

总结:

PMOS是一种根据电压控制导通和截止状态的半导体器件。

它是根据PN结的结构和电流方向来工作的,在晶体管的电流放大、放大倍数以及数字电路中具有重要的应用。

MOS管驱动电路综述连载

相对通用的电路电路图如下:图1 用于NMOS的驱动电路图2 用于PMOS的驱动电路这里只针对NMOS驱动电路做一个简单分析:Vl和Vh分别是低端和高端的电源,两个电压可以是相同的,但是Vl不应该超过Vh。

Q1和Q2组成了一个反置的图腾柱,用来实现隔离,同时确保两只驱动管Q3和Q4不会同时导通。

R2和R3提供了PWM电压基准,通过改变这个基准,可以让电路工作在PWM信号波形比较陡直的位置。

Q3和Q4用来提供驱动电流,由于导通的时候,Q3和Q4相对Vh和GND最低都只有一个Vce的压降,这个压降通常只有0.3V左右,大大低于0.7V的Vce。

R5和R6是反馈电阻,用于对gate电压进行采样,采样后的电压通过Q5对Q1和Q2的基极产生一个强烈的负反馈,从而把gate电压限制在一个有限的数值。

这个数值可以通过R5和R6来调节。

最后,R1提供了对Q3和Q4的基极电流限制,R4提供了对MOS管的gate电流限制,也就是Q3和Q4的Ice的限制。

必要的时候可以在R4上面并联加速电容。

这个电路提供了如下的特性:1,用低端电压和PWM驱动高端MOS管。

2,用小幅度的PWM信号驱动高gate电压需求的MOS管。

3,gate电压的峰值限制4,输入和输出的电流限制5,通过使用合适的电阻,可以达到很低的功耗。

6,PWM信号反相。

NMOS并不需要这个特性,可以通过前置一个反相器来解决。

在设计便携式设备和无线产品时,提高产品性能、延长电池工作时间是设计人员需要面对的两个问题。

DC-DC转换器具有效率高、输出电流大、静态电流小等优点,非常适用于为便携式设备供电。

目前DC-DC转换器设计技术发展主要趋势有:(1)高频化技术:随着开关频率的提高,开关变换器的体积也随之减小,功率密度也得到大幅提升,动态响应得到改善。

小功率DC-DC转换器的开关频率将上升到兆赫级。

(2)低输出电压技术:随着半导体制造技术的不断发展,微处理器和便携式电子设备的工作电压越来越低,这就要求未来的DC-DC变换器能够提供低输出电压以适应微处理器和便携式电子设备的要求。

PMOS功率管开关电路设计

PMOS开关管电路设计指南一、NMOS管等效电路A)B)图2 NMOS管等效模型1、驱动G极时,因为输入电容Ciss(Cgd+Cgs)的存在,要求电压变化快,i=Cdu/dt,当G极电流大时,du/dt也大,增大开关速度。

2、根据B图,功率MOS管内部存在等效三极管,当S接地,刚上电时,三极管会导通,且电流有可能过大,所以,最好D极有缓启动电路保护。

3、根据A图,反向寄生二极管有可能被正向或反向击穿。

反向击穿有可能因为D极部分,当电源开启时会有冲击电流,因为线上电感原因,U = Ldi/dt,导致U过大。

正向击穿,可能因为S极在关电时,因为线上电感原因,造成U 过大;或者线上串入能量较大干扰电压,导致寄生二极管正向通道电流过大,烧毁寄生二极管,从而造成MOS管失效。

二、控制盒PMOS开关电路分析1、小电流切换电路A)B)图3 5V激光器驱动电路和24V LED灯驱动电路1、电路A:1)三极管集电极电阻过大,导致开关速度不高;考虑是激光器驱动电路,正好使用这个缓启动功能。

2)MOS管损坏过,现象是能够正常开启MOS管,但不能完全关断MOS管,怀疑是MOS管寄生二极管损坏导致。

解决办法,a)更换Vds较大的MOS管(IRLML5203,Vds最大30V,而6401的Vds最大12V)b)电源处增加缓启动c)D端增加5V TVSd)在输出端口增加电阻等措施e)去掉输出π型滤波电路上的并接反向二极管,如有可能,在输出放置防反接二极管。

2、电路B1)24V驱动电路,导通时Vgs过大,影响PMOS管寿命解决办法:修改R13为10K,R11为20K,Vgs最大为-8V2)电源上电有可能Vgs过大,在G、S极增加一个8V稳压二极管保护3)IRF9393的最大Vds约55V,更改为IRF6217,最大Vds变为150V4)在D极增加24V TVS5)在输出端口增加电阻等措施6)去掉输出π型滤波电路上的并接反向二极管,如有可能,在输出放置防反接二极管。

NMOS管和PMOS管开关控制电路原理及应用

NMOS管和PMOS管开关控制电路原理及应⽤了解MOS管的开通/关断原理你就会发现,使⽤PMOS做上管、NMOS做下管⽐较⽅便。

使⽤PMOS做下管、NMOS做上管的电路设计复杂,⼀般情况下意义不⼤,所以很少采⽤。

下⾯先了解MOS管的开通/关断原理,请看下图:

NMOS管的主回路电流⽅向为D→S,导通条件为VGS有⼀定的压差,⼀般为510V(G电位⽐S电位

-10V(S电位⽐G电位

⾼);⽽PMOS管的主回路电流⽅向为S→D,导通条件为VGS有⼀定的压差,⼀般为-5

⾼),下⾯以导通压差6V为例。

NMOS管

使⽤NMOS当下管,S极直接接地(为固定值),只需将G极电压固定值6V即可导通;若使⽤NMOS当上管,D极接正电源,⽽S极的电压不固定,⽆法确定控制NMOS导通的G极电压,因

为S极对地的电压有两种状态,MOS管截⽌时为低电平,导通时接近⾼电平VCC。

当然NMOS

也是可以当上管的,只是控制电路复杂,这种情况必须使⽤隔离电源控制,使⽤⼀个PMOS管

就能解决的事情⼀般不会这么⼲,明显增加电路难度。

PMOS管

使⽤PMOS当上管,S极直接接电源VCC,S极电压固定,只需G极电压⽐S极低6V即可导通

,使⽤⽅便;同理若使⽤PMOS当下管,D极接地,S极的电压不固定(0V或VCC),⽆法确定

控制极G极的电压,使⽤较⿇烦,需采⽤隔离电压设计。

综上所述,是Nmos的话,就S极接地。

Pmos就S极接电源。

都是给S极⼀个固定的电位。

NMOS PMOS管驱动电路图

NMOS PMOS管驱动电路图Vl和Vh分别是低端和高端的电源,两个电压可以是相同的,但是Vl不应该超过Vh。

Q1和Q2组成了一个反置的图腾柱,用来实现隔离,同时确保两只驱动管Q3和Q4不会同时导通。

R2和R3提供了PWM电压基准,通过改变这个基准,可以让电路工作在PWM信号波形比较陡直的位置。

Q3和Q4用来提供驱动电流,由于导通的时候,Q3和Q4相对Vh 和GND最低都只有一个Vce的压降,这个压降通常只有0.3V左右,大大低于0.7V的Vce。

R5和R6是反馈电阻,用于对gate电压进行采样,采样后的电压通过Q5对Q1和Q2的基极产生一个强烈的负反馈,从而把gate 电压限制在一个有限的数值。

这个数值可以通过R5和R6来调节。

最后,R1提供了对Q3和Q4的基极电流限制,R4提供了对MOS管的gate电流限制,也就是Q3和Q4的Ice的限制。

必要的时候可以在R4上面并联加速电容。

图1 用于NMOS的驱动电路这个电路提供了如下的特性:1,用低端电压和PWM驱动高端MOS管。

2,用小幅度的PWM信号驱动高gate电压需求的MOS管。

3,gate电压的峰值限制4,输入和输出的电流限制5,通过使用合适的电阻,可以达到很低的功耗。

6,PWM信号反相。

NMOS并不需要这个特性,可以通过前置一个反相器来解决。

在设计便携式设备和无线产品时,提高产品性能、延长电池工作时间是设计人员需要面对的两个问题。

DC-DC转换器具有效率高、输出电流大、静态电流小等优点,非常适用于为便携式设备供电。

目前DC-DC转换器设计技术发展主要趋势有:(1)高频化技术:随着开关频率的提高,开关变换器的体积也随之减小,功率密度也得到大幅提升,动态响应得到改善。

小功率DC-DC转换器的开关频率将上升到兆赫级。

(2)低输出电压技术:随着半导体制造技术的不断发展,微处理器和便携式电子设备的工作电压越来越低,这就要求未来的DC-DC变换器能够提供低输出电压以适应微处理器和便携式电子设备的要求。

PMOS开关管的选择与电路图

PMOS 开关管的选择与电路图

首先要进行MOSFET 的选择,MOSFET 有两大类型:N 沟道和P 沟道。

在功率系统中,MOSFET 可被看成电气开关。

当在N 沟道MOSFET 的栅极和源极间加上正电压时,其开关导通。

导通时,电流可经开关从漏极流向源极。

漏极和源极之间存在一个内阻,称为导通电阻RDS(ON)。

必须清楚MOSFET 的栅极是个高阻抗端,因此,总是要在栅极加上一个电压。

这就是后面介绍电路图中栅极所接电阻至地。

如果栅极为悬空,器件将不能按设计意图工作,并可能在不恰当的时刻导通或关闭,导致系统产生潜在的功率损耗。

当源极和栅极间的电压为零时,开关关闭,而电流停止通过器件。

虽然这时器件已经关闭,但仍然有微小电流存在,这称之为漏电流,即IDSS。

p沟道增强型mos管开关电路

p沟道增强型mos管开关电路

p沟道增强型MOS管(PMOS)是一种常用的场效应管,可以用

于开关电路。

在开关电路中,PMOS通常被用作负载开关或电压级移器。

当PMOS处于导通状态时,负载电路将被连接到电源,从而允许

电流流过。

当PMOS处于截止状态时,负载电路与电源断开,电流被

阻断。

在一个典型的PMOS开关电路中,PMOS的栅极与输入信号相连,当输入信号为高电平时(逻辑1),PMOS导通,负载电路连接到电源。

当输入信号为低电平时(逻辑0),PMOS截止,负载电路与电

源断开。

这样就实现了一个简单的开关功能。

除了基本的开关功能外,PMOS还可以用于级移器电路。

通过将PMOS与NMOS(n沟道增强型MOS管)结合使用,可以实现逻辑电平

的转换,从而将高电平转换为低电平,或者将低电平转换为高电平。

总的来说,p沟道增强型MOS管在开关电路中扮演着重要的角色,通过控制其导通和截止状态,可以实现信号的开关和级移功能。

在实际应用中,工程师们会根据具体的电路设计需求,结合PMOS的

特性和工作原理,来设计和实现各种不同功能的开关电路。

NMOS和PMOS详解以及电路设计

NMOS和PMOS详解以及电路设计一、简介MOS管,是MOSFET的缩写。

MOSFET金属-氧化物半导体场效应晶体管,简称金氧半场效晶体管(Metal-Oxide-Semiconductor Field-Effect Transistor, MOSFET)。

其中,G是栅极,S是源极,D是漏极。

二、常见的nmos和pmos的原理与区别NMOSNMOS英文全称为N-Metal-Oxide-Semiconductor。

意思为N 型金属-氧化物-半导体,而拥有这种结构的晶体管我们称之为NMOS 晶体管。

MOS晶体管有P型MOS管和N型MOS管之分。

由MOS 管构成的集成电路称为MOS集成电路,由NMOS组成的电路就是NMOS集成电路,由PMOS管组成的电路就是PMOS集成电路,由NMOS和PMOS两种管子组成的互补MOS电路,即CMOS电路。

PMOSPMOS是指n型衬底、p沟道,靠空穴的流动运送电流的MOS 管。

NMOS和PMOS工作原理P沟道MOS晶体管的空穴迁移率低,因而在MOS晶体管的几何尺寸和工作电压绝对值相等的情况下,PMOS晶体管的跨导小于N沟道MOS晶体管。

此外,P沟道MOS晶体管阈值电压的绝对值一般偏高,要求有较高的工作电压。

它的供电电源的电压大小和极性,与双极型晶体管——晶体管逻辑电路不兼容。

PMOS因逻辑摆幅大,充电放电过程长,加之器件跨导小,所以工作速度更低,在NMOS电路(见N沟道金属—氧化物—半导体集成电路)出现之后,多数已为NMOS电路所取代。

只是,因PMOS电路工艺简单,价格便宜,有些中规模和小规模数字控制电路仍采用PMOS电路技术。

三、MOS管应用分析1.导通特性NMOS的特性,Vgs大于一定的值就会导通,适合用于源极接地时的情况(低端驱动),只要栅极电压达到4V或10V就可以了。

PMOS的特性,Vgs小于一定的值就会导通,适合用于源极接VCC时的情况(高端驱动)。

但是,虽然PMOS可以很方便地用作高端驱动,但由于导通电阻大,价格贵,替换种类少等原因,在高端驱动中,通常还是使用NMOS。

nmos和pmos互补型开关电路

NMOS(N沟道金属氧化物半导体晶体管)和PMOS(P沟道金属氧化物半导体晶体管)是两种不同类型的金属氧化物半导体场效应晶体管。

互补型开关电路是将这两种类型的MOS管结合使用,以实现互补效应,提高电路的性能。

在互补型开关电路中,NMOS和PMOS的特性互补,可以实现高速度开关,减小导通电阻,提高电路的效率和可靠性。

当电路需要高电平驱动时,可以使用这两个管子组成肖特基二极管,这种组合是基于两个导通性能相反的原理,即互补功能。

这些优势使得互补型开关电路在许多电子应用中都有应用,如数字和模拟电路、功率转换、无线通信、功率MOSFET栅极驱动等。

需要注意的是,在实际应用中,需要合理选择MOS管的型号和参数,以及进行合理的电路设计,才能充分发挥互补型开关电路的性能。

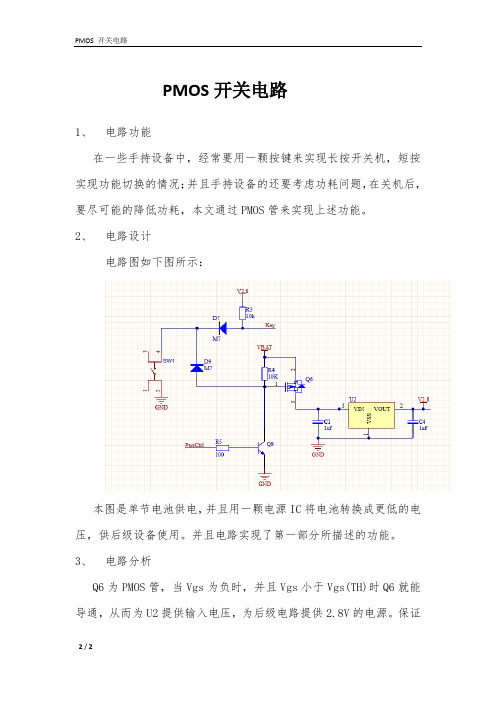

PMOS开关电路

PMOS开关电路1、电路功能在一些手持设备中,经常要用一颗按键来实现长按开关机,短按实现功能切换的情况;并且手持设备的还要考虑功耗问题,在关机后,要尽可能的降低功耗,本文通过PMOS管来实现上述功能。

2、电路设计电路图如下图所示:本图是单节电池供电,并且用一颗电源IC将电池转换成更低的电压,供后级设备使用。

并且电路实现了第一部分所描述的功能。

3、电路分析Q6为PMOS管,当Vgs为负时,并且Vgs小于Vgs(TH)时Q6就能导通,从而为U2提供输入电压,为后级电路提供2.8V的电源。

保证Vgs为负有两个条件,两个条件满足一个,就可以使后级电路工作,其中一个条件是SW1被按下,它使G极通过二极管D9接地,从而实现PMOS的导通,当PMOS导通后,后续电路就可以进行工作,标号Key接到MCU的一个IO口上,当按键按下时,Key为低,MCU在运行时侦测Key的信号,如果低电平持续1-2秒,MCU就进行开机动作,将PwrCtrl引脚设置为高电平,使三极管Q9导通,也就是使PMOS的G极接地,此时松开按键,由于PwrCtrl的电平由MCU给出,所以PMOS 的G极仍然接地,从而实现了开机过程。

关机过程,当SW1不被按下时,Key被上拉为高,当SW1被按下时Key就被置为低,MCU就可以通过侦测到Key脚电平的变化,当SW1被按下1-2S时,MCU就可以PwrCtrl设置为低电平,断开Q9,当SW1松开时,PMOS的G极电位为VBat,Vgs就是0,所以PMOS不导通,后级电路就不能工作。

功能按键侦测,通过按下按键的时间长短来区分功能按键还是开关机按键,开机器按键可以规定按键被一致按下1-2S,功能按键要这短很多。

4、功耗手持设备对功耗要求很严格,功耗除了在是使用过程中,要考虑功耗外,还要考虑静态功耗,就是当设备不再使用时的功耗,本电路关机之后,静态功耗极小,只是Q9和Q6的静态功耗,这个静态电路是na级的。

MOS开关电路的分析

MOS开关电路的分析

MOS开关电路

PMOS用于高边开关,电源输入->PMOS->负载->电源地

NMOS用于低边开关,电源输入->负载->NMOS ->电源地

MOS开关电路

NMOS保证截止发生在栅极G电位小于等于源极S

PMOS保证截止发生在栅极G电位大于等于源极S。

寄生二极管是因为基底与源极间连接形成的PN结。

MOS开关电路

PMOS用于高边开关,电源输入->PMOS->负载->电源地

NMOS用于低边开关,电源输入->负载->NMOS ->电源地

Proteus仿真PMOS开关电路,如图所示

在R4的输入端加一定宽度脉冲,控制Q2的导通和截止。

Q2导通时,Q1的栅极电压14V,小于源极28V,Q1导通,LED 亮。

Q2截止时,Q1的栅极电压28V,等于源极28V,Q1截止,LED 灭。

Q1的漏极D和源极S反接,LED一直亮。

由附生二极管导通导致了开关管的功能不能达到。

nmos管pmos组成的电路

nmos管pmos组成的电路

由NMOS管和PMOS管组成的电路有多种形式,它们可以用来实现各种逻辑功能。

在CMOS电路中,PMOS和NMOS晶体管通常会以串联或并联的方式配置来实现各种不同的逻辑功能。

在串联配置中,PMOS和NMOS晶体管被连接在一起,以形成逻辑门电路。

根据其连接方式不同,CMOS逻辑电路主要包括非逻辑门、与逻辑门、或逻辑门、异或逻辑门等。

这些逻辑门可以通过正确的布置和连接,组合成可靠的电路,用于实现计算机中的各种功能和任务。

在单片机电路中,经常使用一个增强型NMOS管和一个增强型PMOS管组成的MOS管组合控制电路。

这个电路的IO_CON接到单片机(单片机供电3.3V)的IO口上。

单片机电平控制有两种情况:

当IO_CON为高电平时,增强型NMOS管AO3400的Ugs>0,所以此时NMOS管导通,那么此时增强型PMOS管AO3401的G脚为低电平,此时AO3401的Ugs<0,此时PMOS管导通,这样一来VCC_IN的电就直接到了VCC_OUT。

当IO_CON为低电平时,增强型NMOS管AO3400的Ugs<0,所以此时NMOS管截止,那么此时增强型PMOS管AO3401的G脚的电压就是VCC_IN的电压,此时AO3401的Ugs=0,此时PMOS管截止(不导通),这样一来VCC_IN和VCC_OUT就被隔离开了。

PMOS——用于电源开关浅析

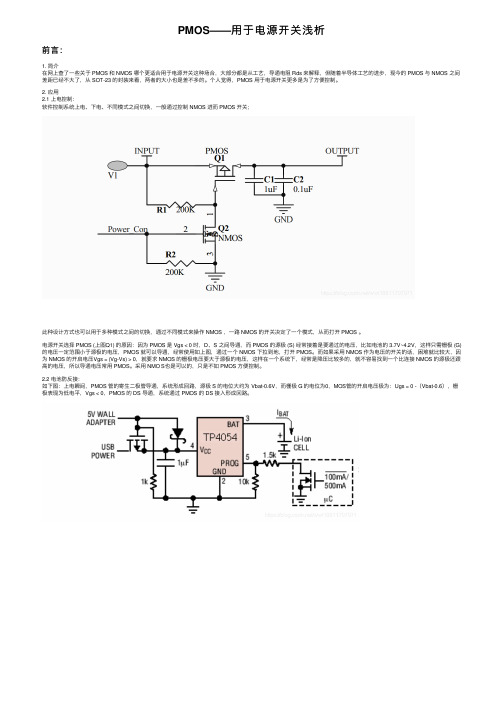

PMOS——⽤于电源开关浅析前⾔:1. 简介在⽹上查了⼀些关于 PMOS 和 NMOS 哪个更适合⽤于电源开关这种场合,⼤部分都是从⼯艺,导通电阻 Rds 来解释,但随着半导体⼯艺的进步,现今的 PMOS 与 NMOS 之间差距已经不⼤了,从 SOT-23 的封装来看,两者的⼤⼩也是差不多的。

个⼈觉得,PMOS ⽤于电源开关更多是为了⽅便控制。

2. 应⽤2.1 上电控制:软件控制系统上电、下电、不同模式之间切换,⼀般通过控制 NMOS 进⽽ PMOS 开关;此种设计⽅式也可以⽤于多种模式之间的切换,通过不同模式来操作 NMOS ,⼀路 NMOS 的开关决定了⼀个模式,从⽽打开 PMOS 。

电源开关选择 PMOS (上图Q1) 的原因:因为 PMOS 是 Vgs < 0 时,D、S 之间导通,⽽ PMOS 的源极 (S) 经常接着是要通过的电压,⽐如电池的 3.7V~4.2V,这样只需栅极 (G)的电压⼀定范围⼩于源极的电压,PMOS 就可以导通,经常使⽤如上图,通过⼀个 NMOS 下拉到地,打开 PMOS。

⽽如果采⽤ NMOS 作为电压的开关的话,困难就⽐较⼤,因为 NMOS 的开启电压Vgs = (Vg-Vs) > 0,就要求 NMOS 的栅极电压要⼤于源极的电压,这样在⼀个系统下,经常是降压⽐较多的,就不容易找到⼀个⽐连接 NMOS 的源极还跟⾼的电压,所以导通电压常⽤ PMOS。

采⽤ NMO S也是可以的,只是不如 PMOS ⽅便控制。

2.2 电池防反接:如下图:上电瞬间,PMOS 管的寄⽣⼆极管导通,系统形成回路,源极 S 的电位⼤约为 Vbat-0.6V,⽽栅极 G 的电位为0,MOS管的开启电压极为:Ugs = 0 -(Vbat-0.6),栅极表现为低电平,Vgs < 0,PMOS 的 DS 导通,系统通过 PMOS 的 DS 接⼊形成回路。

如上图,USB 上电与 Battery 供电的切换。

nmospmos管驱动电路图[最新]

![nmospmos管驱动电路图[最新]](https://img.taocdn.com/s3/m/de4f8f0c6ad97f192279168884868762caaebb0f.png)

NMOS PMOS管驱动电路图Vl和Vh分别是低端和高端的电源,两个电压可以是相同的,但是Vl不应该超过Vh。

Q1和Q2组成了一个反置的图腾柱,用来实现隔离,同时确保两只驱动管Q3和Q4不会同时导通。

R2和R3提供了PWM电压基准,通过改变这个基准,可以让电路工作在PWM信号波形比较陡直的位置。

Q3和Q4用来提供驱动电流,由于导通的时候,Q3和Q4相对Vh和GND最低都只有一个Vce的压降,这个压降通常只有0.3V左右,大大低于0.7V的Vce。

R5和R6是反馈电阻,用于对gate电压进行采样,采样后的电压通过Q5对Q1和Q2的基极产生一个强烈的负反馈,从而把gate电压限制在一个有限的数值。

这个数值可以通过R5和R6来调节。

最后,R1提供了对Q3和Q4的基极电流限制,R4提供了对MOS管的gate电流限制,也就是Q3和Q4的Ice的限制。

必要的时候可以在R4上面并联加速电容。

图1 用于NMOS的驱动电路这个电路提供了如下的特性:1,用低端电压和PWM驱动高端MOS管。

2,用小幅度的PWM信号驱动高gate电压需求的MOS管。

3,gate电压的峰值限制4,输入和输出的电流限制5,通过使用合适的电阻,可以达到很低的功耗。

6,PWM信号反相。

NMOS并不需要这个特性,可以通过前置一个反相器来解决。

在设计便携式设备和无线产品时,提高产品性能、延长电池工作时间是设计人员需要面对的两个问题。

DC-DC转换器具有效率高、输出电流大、静态电流小等优点,非常适用于为便携式设备供电。

目前DC-DC转换器设计技术发展主要趋势有:(1)高频化技术:随着开关频率的提高,开关变换器的体积也随之减小,功率密度也得到大幅提升,动态响应得到改善。

小功率DC-DC转换器的开关频率将上升到兆赫级。

(2)低输出电压技术:随着半导体制造技术的不断发展,微处理器和便携式电子设备的工作电压越来越低,这就要求未来的DC-DC变换器能够提供低输出电压以适应微处理器和便携式电子设备的要求。

pmos限流电路

pmos限流电路

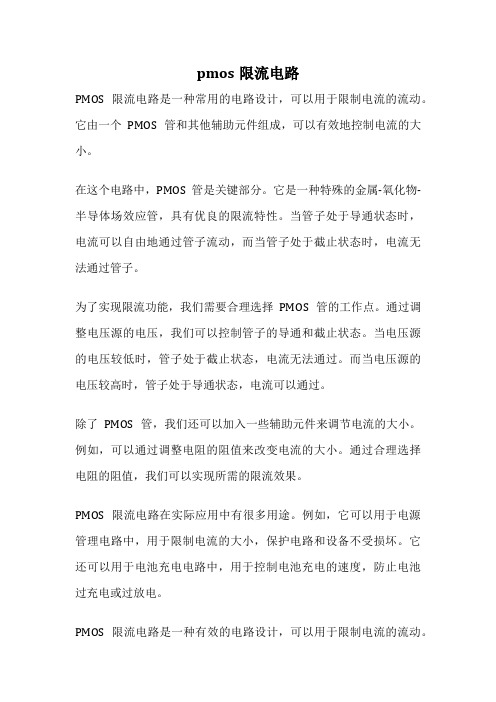

PMOS限流电路是一种常用的电路设计,可以用于限制电流的流动。

它由一个PMOS管和其他辅助元件组成,可以有效地控制电流的大小。

在这个电路中,PMOS管是关键部分。

它是一种特殊的金属-氧化物-半导体场效应管,具有优良的限流特性。

当管子处于导通状态时,电流可以自由地通过管子流动,而当管子处于截止状态时,电流无法通过管子。

为了实现限流功能,我们需要合理选择PMOS管的工作点。

通过调整电压源的电压,我们可以控制管子的导通和截止状态。

当电压源的电压较低时,管子处于截止状态,电流无法通过。

而当电压源的电压较高时,管子处于导通状态,电流可以通过。

除了PMOS管,我们还可以加入一些辅助元件来调节电流的大小。

例如,可以通过调整电阻的阻值来改变电流的大小。

通过合理选择电阻的阻值,我们可以实现所需的限流效果。

PMOS限流电路在实际应用中有很多用途。

例如,它可以用于电源管理电路中,用于限制电流的大小,保护电路和设备不受损坏。

它还可以用于电池充电电路中,用于控制电池充电的速度,防止电池过充电或过放电。

PMOS限流电路是一种有效的电路设计,可以用于限制电流的流动。

它具有简单可靠的特点,广泛应用于各种电子设备和电路中。

通过合理选择元件和调整工作点,我们可以实现所需的限流效果,保护电路和设备的安全运行。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

PMOS开关管的选择与电路图

首先要进行MOSFET的选择,MOSFET有两大类型:N沟道和P沟道。

在功率系统中,MOSFET可被看成电气开关。

当在N沟道MOSFET的栅极和源极间加上正电压时,其开关导通。

导通时,电流可经开关从漏极流向源极。

漏极和源极之间存在一个内阻,称为导通电阻RDS(ON)。

必须清楚MOSFET的栅极是个高阻抗端,因此,总是要在栅极加上一个电压。

这就是后面介绍电路图中栅极所接电阻至地。

如果栅极为悬空,器件将不能按设计意图工作,并可能在不恰当的时刻导通或关闭,导致系统产生潜在的功率损耗。

当源极和栅极间的电压为零时,开关关闭,而电流停止通过器件。

虽然这时器件已经关闭,但仍然有微小电流存在,这称之为漏电流,即IDSS。

第一步:选用N沟道还是P沟道

为设计选择正确器件的第一步是决定采用N沟道还是P沟道MOSFET。

在典型的功率应用中,当一个MOSFET接地,而负载连接到干线电压上时,该MOSFET就构成了低压侧开关。

在低压侧开关中,应采用N沟道MOSFET,这是出于对关闭或导通器件所需电压的考虑。

当MOSFET连接到总线及负载接地时,就要用高压侧开关。

通常会在这个拓扑中采用P沟道MOSFET,这也是出于对电压驱动的考虑。

第二步:确定额定电流

第二步是选择MOSFET的额定电流。

视电路结构而定,该额定电流应是负载在所有情况下能够承受的最大电流。

与电压的情况相似,设计人员必须确保所选的MOSFET能承受这个额定电流,即使在系统产生尖峰电流时。

两个考虑的电流情况是连续模式和脉冲尖峰。

该参数以FDN304P管DATASHEET为参考,参数如图所示:

在连续导通模式下,MOSFET处于稳态,此时电流连续通过器件。

脉冲尖峰是指有大量电涌(或尖峰电流)流过器件。

一旦确定了这些条件下的最大电流,只需直接选择能承受这个最大电流的器件便可。

选好额定电流后,还必须计算导通损耗。

在实际情况下,MOSFET并不是理想的器件,因为在导电过程中会有电能损耗,这称之为导通损耗。

MOSFET在“导通”时就像一个可变电阻,由器件的RDS(ON)所确定,并随温度而显著变化。

器件的功率耗损可由Iload2×RDS(ON)计算,由于导通电阻随温度变化,因此功率耗损也会随之按比例变化。

对MOSFET施加的电压VGS越高,RDS(ON)就会越小;反之RDS(ON)就会越高。

对系统设计人员来说,这就是取决于系统电压而需要折中权衡的地方。

对便携式设计来说,采用较低的电压比较容易(较为普遍),而对于工业设计,可采用较高的电压。

注意RDS(ON)电阻会随着电流轻微上升。

关于RDS(ON)电阻的各种电气参数变化可在制造商提供的技术资料表中查到。

第三步:确定热要求

选择MOSFET的下一步是计算系统的散热要求。

设计人员必须考虑两种不同的情况,即最坏情况和真实情况。

建议采用针对最坏情况的计算结果,因为这个结果提供更大的安全余量,能确保系统不会失效。

在MOSFET的资料表上还有一些需要注意的测量数据;比如封装器件的半导体结与环境之间的热阻,以及最大的结温。

器件的结温等于最大环境温度加上热阻与功率耗散的乘积(结温=最大环境温度+[热阻×功率耗散])。

根据这个方程可解出系统的最大功率耗散,即按定义相等于I2×RDS(ON)。

由于设计人员已确定将要通过器件的最大电流,因此可以计算出不同温度下的RDS(ON)。

值得注意的是,在处理简单热模型时,设计人员还必须考虑半导体结/器件外壳及外壳/环境的热容量;即要求印刷电路板和封装不会立即升温。

通常,一个PMOS管,会有寄生的二极管存在,该二极管的作用是防止源漏端反接,对于PMOS而言,比起NMOS的优势在于它的开启电压可以为0,而DS电压之间电压相差不大,而NMOS的导通条件要求VGS要大于阈值,这将导致控制电压必然大于所需的电压,会出现不必要的麻烦。

选用PMOS作为控制开关,有下面两种应用:

第一种应用,由PMOS来进行电压的选择,当V8V存在时,此时电压全部由V8V 提供,将PMOS关闭,VBAT不提供电压给VSIN,而当V8V为低时,VSIN由8V供电。

注意R120的接地,该电阻能将栅极电压稳定地拉低,确保PMOS的正常开启,这也是前文所描述的栅极高阻抗所带来的状态隐患。

D9和D10的作用在于防止电压的倒灌。

D9可以省略。

这里要注意到实际上该电路的DS接反,这样由附生二极管导通导致了开关管的功能不能达到,实际应用要注意。

来看这个电路,控制信号PGC控制V4.2是否给P_GPRS供电。

此电路中,源漏两端没有接反,R110与R113存在的意义在于R110控制栅极电流不至于过大,R113控制栅极的常态,将R113上拉为高,截至PMOS,同时也可以看作是对控制信号的上拉,当MCU内部管脚并没有上拉时,即输出为开漏时,并不能驱动PMOS关闭,此时,就需要外部电压给予的上拉,所以电阻R113起到了两个作用。

R110可以更小,到100欧姆也可。