VLMW32T2V1-5K8L-08中文资料

MEMORY存储芯片MT29F32G08CBADAWP中文规格书

Electrical Specifications – AC Characteristics and Operating Conditions AC Characteristics: Command, Data, and Address Input (3.3V)Notes: 1.Operating mode timings meet ONFI timing mode 5 parameters.2.Timing for t ADL begins in the address cycle, on the final rising edge of WE#, and endswith the first rising edge of WE# for data input.AC Characteristics: Command, Data, and Address Input (1.8V) Note 1Notes: 1.Operating mode timings meet ONFI timing mode 4 parameters.2.Timing for t ADL begins in the address cycle on the final rising edge of WE#, and endswith the first rising edge of WE# for data input.4Gb, 8Gb, 16Gb: x8, x16 NAND Flash Memory Electrical Specifications – AC Characteristics and Operating ConditionsElectrical Specifications – DC Characteristics and Operating Conditions DC Characteristics and Operating Conditions (3.3V)Notes: 1.Measurement is taken with 1ms averaging intervals and begins after V CC reachesV CC(MIN).2.I OL (R/B#) may need to be relaxed if R/B pull-down strength is not set to full.3.V OH and V OL may need to be relaxed if I/O drive strength is not set to full.DC Characteristics and Operating Conditions (1.8V)Notes: 1.Typical and maximum values are for single-plane operation only. If device supports dual-plane operation, values are 20mA (TYP) and 40mA (MAX).2.Values are for single-die operations. Values could be higher for interleaved-die opera-tions.3.Measurement is taken with 1ms averaging intervals and begins after V CC reachesV CC(MIN).4.Test conditions for V OH and V OL.5.DC characteristics may need to be relaxed if R/B# pull-down strength is not set to full.。

V54C365804VDL资料

MOSEL VITELIC V54C365804VD(L)HIGH PERFORMANCE143/133/125MHz3.3VOLT8M X8SYNCHRONOUS DRAM4BANKS X2Mbit X8PRELIMINARY7758PC8 System Frequency(f CK)143MHz133MHz125MHz125MHz Clock Cycle Time(t CK3)7ns7.5ns8ns8ns Clock Access Time(t AC3)CAS Latency=3 5.4ns 5.4ns6ns7ns Clock Access Time(t AC2)CAS Latency=2 5.5ns6ns6ns7nsFeaturess4banks x2Mbit x8organizations High speed data transfer rates up to143MHzs Full Synchronous Dynamic RAM,with all signals referenced to clock rising edges Single Pulsed RAS Interfaces Data Mask for Read/Write Controls Four Banks controlled by BA0&BA1s Programmable CAS Latency:2,3s Programmable Wrap Sequence:Sequential or Interleaves Programmable Burst Length:1,2,4,8and full page for Sequential Type1,2,4,8for Interleave Types Multiple Burst Read with Single Write Operation s Automatic and Controlled Precharge Command s Random Column Address every CLK(1-N Rule) s Suspend Mode and Power Down Modes Auto Refresh and Self Refreshs Refresh Interval:4096cycles/64mss Available in54Pin400mil TSOP-IIs LVTTL Interfaces Single+3.3V±0.3V Power Supply DescriptionThe V54C365804VD(L)is a four bank Synchro-nous DRAM organized as4banks x2Mbit x8.The V54C365804VD(L)achieves high speed data trans-fer rates up to143MHz by employing a chip archi-tecture that prefetches multiple bits and then synchronizes the output data to a system clockAll of the control,address,data input and output circuits are synchronized with the positive edge of an externally supplied clock.Operating the four memory banks in an inter-leaved fashion allows random access operation to occur at higher rate than is possible with standard DRAMs.A sequential and gapless data rate of up to 143MHz is possible depending on burst length, latency and speed grade of the device.Device Usage ChartOperating Temperature Range Package Outline Access Time(ns)PowerTemperatureMark T7758PC8Std.L0°C to70°C•••••••Blank54Pin Plastic TSOP-II PIN CONFIGURATIONTop ViewPin NamesCLK Clock Input CKEClock Enable CS Chip SelectRAS Row Address Strobe CAS Column Address Strobe WE Write Enable A 0–A 11Address Inputs BA0,BA1Bank Select I/O 1–I/O 8Data Input/Output DQM Data Mask V CC Power (+3.3V)V SS GroundV CCQ Power for I/O ’s (+3.3V)V SSQ Ground for I/O ’s NCNot connectedDescription Pkg.Pin CountTSOP-IIT54Capacitance*T A =0to 70°C,V CC =3.3V ±0.3V,f =1Mhz*Note:Capacitance is sampled and not 100%tested.Symbol ParameterMax.UnitC I1Input Capacitance (A0to A11)5pF C I2Input CapacitanceRAS,CAS,WE,CS,CLK,CKE,DQM 5pF C IO Output Capacitance (I/O) 6.5pF C CLKInput Capacitance (CLK)4pFBlock DiagramC L C K C R A C A WD QSignal Pin DescriptionPin Type Signal Polarity FunctionCLK Input Pulse PositiveEdge The system clock input.All of the SDRAM inputs are sampled on the rising edge of the clock.CKE Input Level Active High Activates the CLK signal when high and deactivates the CLK signal when low,therebyinitiates either the Power Down mode,Suspend mode,or the Self Refresh mode.CS Input Pulse Active Low CS enables the command decoder when low and disables the command decoder whenhigh.When the command decoder is disabled,new commands are ignored but previousoperations continue.RAS,CASWE Input Pulse Active Low When sampled at the positive rising edge of the clock,CAS,RAS,and WE define thecommand to be executed by the SDRAM.A0-A11Input Level—During a Bank Activate command cycle,A0-A11defines the row address(RA0-RA11)when sampled at the rising clock edge.During a Read or Write command cycle,A0-An defines the column address(CA0-CAn)when sampled at the rising clock edge.CAn depends from the SDRAM organization:8M x8SDRAM CA0–CA8(Page Length=512bits)In addition to the column address,A10(=AP)is used to invoke autoprecharge operationat the end of the burst read or write cycle.If A10is high,autoprecharge is selected andBA0,BA1defines the bank to be precharged.If A10is low,autoprecharge is disabled.During a Precharge command cycle,A10(=AP)is used in conjunction with BA0and BA1to control which bank(s)to precharge.If A10is high,all four banks will BA0and BA1areused to define which bank to precharge.BA0,BA1Input Level—Selects which bank is to be active.DQx InputOutputLevel—Data Input/Output pins operate in the same manner as on conventional DRAMs.DQM Input Pulse Active High The Data Input/Output mask places the DQ buffers in a high impedance state when sam-pled high.In Read mode,DQM has a latency of two clock cycles and controls the outputbuffers like an output enable.In Write mode,DQM has a latency of zero and operates asa word mask by allowing input data to be written if it is low but blocks the write operationif DQM is high.One DQM input is present in x4and x8DRAMs.VCC,VSS Supply Power and ground for the input buffers and the core logic.VCCQ VSSQ Supply——Isolated power supply and ground for the output buffers to provide improved noiseimmunity.Operation DefinitionAll of SDRAM operations are defined by states of control signals CS,RAS,CAS,WE,and DQM at the positive edge of the clock.The following list shows the thruth table for the operation commands.Notes:1.V =Valid ,x =Don ’t Care,L =Low Level,H =High Level2.CKEn signal is input level when commands are provided,CKEn-1signal is input level one clock before the commandsare provided.3.These are state of bank designated by BS0,BS1signals.4.Device state is Full Page Burst operation5.Power Down Mode can not entry in the burst cycle.When this command assert in the burst mode cycle device is clocksuspend mode.OperationDevice StateCKE n-1CKE nCSRASCASWEDQMA0-9,A11A10BS0BS1Row Activate Idle 3H X L L H H X V V V ReadActive 3H X L H L H X V L V Read w/Autoprecharge Active 3H X L H L H X V H V WriteActive 3H X L H L L X V L V Write with Autoprecharge Active 3H X L H L L X V H V Row Precharge Any H X L L H L X X L V Precharge All Any H X L L H L X X H X Mode Register Set Idle H X L L L L X V V V No Operation Any H X L H H H X X X X Device Deselect Any H X H X X X X X X X Auto Refresh Idle H H L L L H X X X X Self Refresh Entry Idle H L L L L H X X X X Self Refresh ExitIdle (Self Refr.)LHH X X X XXXXL H H X Power Down EntryIdle Active 5H LHX X X X X X XL H H X Power Down ExitAny (Power Down)L H HX X X X X X X L H H L Data Write/Output Enable Active H X X X X X L X X X Data Write/Output DisableActiveHXXXXXHXXXPower On and InitializationThe default power on state of the mode register is supplier specific and may be undefined.The following power on and initialization sequence guarantees the device is preconditioned to each users specific needs.Like a conventional DRAM, the Synchronous DRAM must be powered up and initialized in a predefined manner.During power on, all VCC and VCCQ pins must be built up simultaneously to the specified voltage when the input signals are held in the“NOP”state.The power on voltage must not exceed VCC+0.3V on any of the input pins or VCC supplies.The CLK signal must be started at the same time.After power on, an initial pause of200µs is required followed by a precharge of both banks using the precharge command.To prevent data contention on the DQ bus during power on,it is required that the DQM and CKE pins be held high during the initial pause period.Once all banks have been precharged,the Mode Register Set Command must be issued to initialize the Mode Register.A minimum of eight Auto Refresh cycles(CBR)are also required.These may be done before or after programming the Mode Register.Failure to follow these steps may lead to unpredictable start-up modes.Programming the Mode RegisterThe Mode register designates the operation mode at the read or write cycle.This register is di-vided into4fields.A Burst Length Field to set the length of the burst,an Addressing Selection bit to program the column access sequence in a burst cy-cle(interleaved or sequential),a CAS Latency Field to set the access time at clock cycle and a Opera-tion mode field to differentiate between normal op-eration(Burst read and burst Write)and a special Burst Read and Single Write mode.The mode set operation must be done before any activate com-mand after the initial power up.Any content of the mode register can be altered by re-executing the mode set command.All banks must be in pre-charged state and CKE must be high at least one clock before the mode set operation.After the mode register is set,a Standby or NOP command is re-quired.Low signals of RAS,CAS,and WE at the positive edge of the clock activate the mode set op-eration.Address input data at this timing defines pa-rameters to be set as shown in the previous table. Read and Write OperationWhen RAS is low and both CAS and WE are high at the positive edge of the clock,a RAS cycle starts. According to address data,a word line of the select-ed bank is activated and all of sense amplifiers as-sociated to the wordline are set.A CAS cycle is triggered by setting RAS high and CAS low at a clock timing after a necessary delay,t RCD,from the RAS timing.WE is used to define either a read (WE=H)or a write(WE=L)at this stage. SDRAM provides a wide variety of fast access modes.In a single CAS cycle,serial data read or write operations are allowed at up to a143MHz data rate.The numbers of serial data bits are the burst length programmed at the mode set operation, i.e.,one of1,2,4,8and full page.Column address-es are segmented by the burst length and serial data accesses are done within this boundary.The first column address to be accessed is supplied at the CAS timing and the subsequent addresses are generated automatically by the programmed burst length and its sequence.For example,in a burst length of8with interleave sequence,if the first ad-dress is‘2’,then the rest of the burst sequence is3, 0,1,6,7,4,and5.Full page burst operation is only possible using the sequential burst type and page length is a func-tion of the I/O organisation and column addressing. Full page burst operation do not self terminate once the burst length has been reached.In other words, unlike burst length of2,3or8,full page burst con-tinues until it is terminated using another command.Address Input for Mode Set (Mode Register Operation)Similar to the page mode of conventional DRAM ’s,burst read or write accesses on any col-umn address are possible once the RAS cycle latches the sense amplifiers.The maximum t RAS or the refresh interval time limits the number of random column accesses.A new burst access can be done even before the previous burst ends.The interrupt operation at every clock cycles is supported.When the previous burst is interrupted,the remaining ad-dresses are overridden by the new address with the full burst length.An interrupt which accompanies with an operation change from a read to a write is possible by exploiting DQM to avoid bus contention.When two or more banks are activated sequentially,interleaved bank read or write operations are possible.With the programmed burst length,alternate access and precharge operations on two or more banks can realize fast serial data access modes among many different pages.Once two or more banks are activated,column to column interleave operation can be done between different pages.A11A3A4A2A1A0A10A9A8A7A6A5Address Bus (Ax)BT Burst LengthCAS Latency Mode RegisterCAS LatencyA6A5A4Latency 000Reserve 001Reserve010201131004101Reserve 110Reserve 111ReserveBurst LengthA2A1A0LengthSequentialInterleave00011001220104401188100Reserve Reserve 101Reserve Reserve 110Reserve Reserve 111Full PageReserveBurst TypeA3Type 0Sequential 1InterleaveOperation ModeBA1BA0A11A10A9A8A7Mode 0Burst Read/BurstWrite 0000100Burst Read/SingleWriteOperation Mode BA0BA1Burst Length and Sequence:Refresh ModeSDRAM has two refresh modes,Auto Refresh and Self Refresh.Auto Refresh is similar to the CAS -before-RAS refresh of conventional DRAMs.All of banks must be precharged before applying any re-fresh mode.An on-chip address counter increments the word and the bank addresses and no bank infor-mation is required for both refresh modes.The chip enters the Auto Refresh mode,when RAS and CAS are held low and CKE and WE are held high at a clock timing.The mode restores word line after the refresh and no external precharge command is necessary.A minimum tRC time is re-quired between two automatic refreshes in a burst refresh mode.The same rule applies to any access command after the automatic refresh operation. The chip has an on-chip timer and the Self Re-fresh mode is available.It enters the mode when RAS,CAS,and CKE are low and WE is high at a clock timing.All of external control signals including the clock are disabled.Returning CKE to high en-ables the clock and initiates the refresh exit opera-tion.After the exit command,at least one t RC delay is required prior to any access command.DQM FunctionDQM has two functions for data I/O read and write operations.During reads,when it turns to “high”at a clock timing,data outputs are disabled and become high impedance after two clock delay (DQM Data Disable Latency t DQZ).It also provides a data mask function for writes.When DQM is acti-vated,the write operation at the next clock is prohib-ited(DQM Write Mask Latency t DQW=zero clocks). Suspend ModeDuring normal access mode,CKE is held high en-abling the clock.When CKE is low,it freezes the in-ternal clock and extends data read and write operations.One clock delay is required for mode entry and exit(Clock Suspend Latency t CSL). Power DownIn order to reduce standby power consumption,a power down mode is available.All banks must be precharged and the necessary Precharge delay (trp)must occur before the SDRAM can enter the Power Down mode.Once the Power Down mode is initiated by holding CKE low,all of the receiver cir-cuits except CLK and CKE are gated off.The Power Down mode does not perform any refresh opera-tions,therefore the device can’t remain in Power Down mode longer than the Refresh period(tref)of the device.Exit from this mode is performed by tak-ing CKE“high”.One clock delay is required for mode entry and exit.Auto PrechargeTwo methods are available to precharge SDRAMs.In an automatic precharge mode,the CAS timing accepts one extra address,CA10,to determine whether the chip restores or not after theoperation.If CA10is high when a Read Command is issued,the Read with Auto-Precharge function is initiated.The SDRAM automatically enters the precharge operation one clock before the last data out for CAS latencies2,two clocks for CAS laten-cies3and three clocks for CAS latencies 4.If CAS10is high when a Write Command is issued, the Write with Auto-Precharge function is initiat-ed.The SDRAM automatically enters the precharge operation a time delay equal to t WR(Write recovery time)after the last data in.Precharge CommandThere is also a separate precharge command available.When RAS and WE are low and CAS is high at a clock timing,it triggers the precharge op-eration.Three address bits,BA0,BA1and A10are used to define banks as shown in the following list. The precharge command can be imposed one clock before the last data out for CAS latency=2,two clocks before the last data out for CAS latency=3 and three clocks before the last data out for CAS la-tency=4.Writes require a time delay twr from the last data out to apply the precharge command.Bank Selection by Address Bits:Burst TerminationOnce a burst read or write operation has been ini-tiated,there are several methods in which to termi-nate the burst operation prematurely.These methods include using another Read or Write Com-mand to interrupt an existing burst operation,use a Precharge Command to interrupt a burst cycle and close the active bank,or using the Burst Stop Com-mand to terminate the existing burst operation but leave the bank open for future Read or Write Com-mands to the same page of the active bank.When interrupting a burst with another Read or Write Command care must be taken to avoid I/O conten-tion.The Burst Stop Command,however,has the fewest restrictions making it the easiest method to use when terminating a burst operation before it has been completed.If a Burst Stop command is issued during a burst write operation,then any residual data from the burst write cycle will be ignored.Data that is presented on the I/O pins before the Burst Stop Command is registered will be written to the memory.A10BA0BA1000Bank0 001Bank1 010Bank2 011Bank3 1X X all BanksAbsolute Maximum Ratings*Operating temperature range ..................0to 70°C Storage temperature range ...............-55to 150°C Input/output voltage..................-0.3to (V CC +0.3)V Power supply voltage ..........................-0.3to 4.6V Power dissipation .............................................1W Data out current (short circuit)......................50mA*Note:Stresses above those listed under “Absolute MaximumRatings ”may cause permanent damage of the device.Exposure to absolute maximum rating conditions for extended periods may affect device reliability.Recommended Operation and Characteristics for LV-TTLT A =0to 70°C;V SS =0V;V CC ,V CCQ =3.3V ±0.3VNote:1.All voltages are referenced to V SS .2.V IH may overshoot to V CC +2.0V for pulse width of <4ns with3.3V.V IL may undershoot to -2.0V for pulse width <4.0ns with3.3V.Pulse width measured at 50%points with amplitude measured peak to DC reference.ParameterSymbolLimit ValuesUnitNotesmin.max.Input high voltage V IH 2.0Vcc+0.3V 1,2Input low voltageV IL –0.30.8V 1,2Output high voltage (I OUT =–2.0mA)V OH 2.4–V Output low voltage (I OUT =2.0mA)V OL –0.4V Input leakage current,any input(0V <V IN <3.6V,all other inputs =0V)I I(L)–55µA Output leakage current(DQ is disabled,0V <V OUT <V CC )I O(L)–55µAMOSEL VITELICV54C365804VD(L)Operating Currents (T A =0to 70°C,V CC =3.3V ±0.3V)(Recommended Operating Conditions unless otherwise noted)Notes:7.These parameters depend on the cycle rate and these values are measured by the cycle rate under the minimum value of t CK andt RC .Input signals are changed one time during t CK .8.These parameter depend on output loading.Specified values are obtained with output open.SymbolParameter &Test ConditionMax.UnitNote-7-75-8PC-8ICC1Operating Currentt RC =t RCMIN.,t RC =t CKMIN .Active-precharge command cycling,without Burst Operation 1bank operation150140130130mA7ICC2P Precharge Standby Current in Power Down Mode CS =V IH ,CKE ≤V IL(max)t CK =min.2222mA 7ICC2PS t CK =Infinity 1111mA 7ICC2N Precharge Standby Current in Non-Power Down Mode CS =V IH ,CKE ≥V IL(max)t CK =min.45403535mA ICC2NS t CK =Infinity 5555mA ICC3No Operating Current t CK =min,CS =V IH(min)bank ;active state (4banks)CKE ≥V IH(MIN.)55504545mA ICC3P CKE <V IL(MAX.)(Power down mode)8888mA ICC4Burst Operating Current t CK =minRead/Write command cycling 120120110110mA7,8ICC5Auto Refresh Current t CK =minAuto Refresh command cycling 150140130130mA 7ICC6Self Refresh CurrentSelf Refresh Mode,CKE=<0.2V1111mA L-version500500500500µAMOSEL VITELIC V54C365804VD(L) AC Characteristics1,2,3T A=0to70°C;V SS=0V;V DD=3.3V±0.3V,t T=1ns#Symbol ParameterLimit ValuesUnit Note -7-75-8PC-8Min.Max.Min.Max.Min.Max.Min.Max.Clock and Clock Enable1t CK Clock Cycle TimeCAS Latency=3 CAS Latency=2710––7.510––810––812––snsns2t CK Clock FrequencyCAS Latency=3 CAS Latency=2––143100––133100––125100––12583MHzMHz3t AC Access Time from ClockCAS Latency=3 CAS Latency=2–_5.45.5–_5.46–_66–_77nsns2,44t CH Clock High Pulse Width 2.5– 2.5–3–3–ns5t CL Clock Low Pulse Width 2.5– 2.5–3–3–ns6t T Transition Tim0.3 1.20.3 1.20.5100.510nsSetup and Hold Times7t IS Input Setup Time 1.5– 1.5–2– 2.5–ns5 8t IH Input Hold Time0.8–0.8–1–1–ns5 9t CKS CKE Setup Time 1.5– 1.5–2– 2.5–ns5 10t CKH CKE Hold Time0.8–0.8–1–1–ns5 11t RSC Mode Register Set-up Time14–15–16–16–ns12t SB Power Down Mode Entry Time0707.50808ns Common Parameters13t RCD Row to Column Delay Time20–20–20–24–ns6 14t RP Row Precharge Time20–20–20–24–ns6 15t RAS Row Active Time42100K45100K45100k48100k ns6 16t RC Row Cycle Time60–60–60–72–ns617t RRD Activate(a)to Activate(b)CommandPeriod14–15–16–20–ns6 18t CCD CAS(a)to CAS(b)Command Period1–1–1–1–CLK Refresh Cycle19t REF Refresh Period(4096cycles)—64—64—64—64ms20t SREX Self Refresh Exit Time10101012nsRead Cycle21t OH Data Out Hold Time2.7– 2.7–3–3–ns 222t LZ Data Out to Low Impedance Time 1–1–0–0–ns 23t HZ Data Out to High Impedance Time – 5.4– 5.43838ns 724t DQZDQM Data Out Disable Latency–2–2–2–2CLKWrite Cycle25t WR Write Recovery Time 2–2–2–2–CLK 26t DQWDQM Write Mask Latency–––––CLK#SymbolParameterLimit ValuesUnitNote-7-75-8PC-8Min.Max.Min.Max.Min.Max.Min.Max.AC Characteristics (Cont ’d)Notes for AC Parameters:1.For proper power-up see the operation section of this data sheet.2.AC timing tests have V IL =0.8V and V IH =2.0V with the timing referenced to the 1.4V crossover point.The transitiontime is measured between V IH and V IL .All AC measurements assume t T =1ns with the AC output load circuit shown in Figure 1.4.If clock rising time is longer than 1ns,a time (t T /2–0.5)ns has to be added to this parameter.5.If t T is longer than 1ns,a time (t T –1)ns has to be added to this parameter.6.These parameter account for the number of clock cycle and depend on the operating frequency of the clock,asfollows:the number of clock cycle =specified value of timing period (counted in fractions as a whole number)Self Refresh Exit is a synchronous operation and begins on the 2nd positive clock edge after CKE returns high.Self Refresh Exit is not complete until a time period equal to tRC is satisfied once the Self Refresh Exit command is registered.7.Referenced to the time which the output achieves the open circuit condition,not to output voltage levelsCLKCOMMANDOUTPUT50pFI/O1.4V OhmFigure 1.Timing Diagrams1.Bank Activate Command Cycle2.Burst Read Operation3.Read Interrupted by a Read4.Read to Write Interval4.1Read to Write Interval4.2Minimum Read to Write Interval4.3Non-Minimum Read to Write Interval5.Burst Write Operation6.Write and Read Interrupt6.1Write Interrupted by a Write6.2Write Interrupted by Read7.Burst Write&Read with Auto-Precharge7.1Burst Write with Auto-Precharge7.2Burst Read with Auto-Precharge8.Burst Termination8.1Termination of a Full Page Burst Write Operation8.2Termination of a Full Page Burst Write Operation9.AC-Parameters9.1AC Parameters for a Write Timing9.2AC Parameters for a Read Timing10.Mode Register Set11.Power on Sequence and Auto Refresh(CBR)12.Clock Suspension(using CKE)12.1Clock Suspension During Burst Read CAS Latency=212.2Clock Suspension During Burst Read CAS Latency=312.3Clock Suspension During Burst Write CAS Latency=212.4Clock Suspension During Burst Write CAS Latency=313.Power Down Mode and Clock Suspend14.Self Refresh(Entry and Exit)15.Auto Refresh(CBR)Timing Diagrams(Cont’d)16.Random Column Read(Page within same Bank)16.1CAS Latency=216.2CAS Latency=317.Random Column Write(Page within same Bank)17.1CAS Latency=217.2CAS Latency=318.Random Row Read(Interleaving Banks)with Precharge18.1CAS Latency=218.2CAS Latency=319.Random Row Write(Interleaving Banks)with Precharge19.1CAS Latency=219.2CAS Latency=320.Full Page Read Cycle20.1CAS Latency=220.2CAS Latency=321.Full Page Write Cycle21.1CAS Latency=221.2CAS Latency=322.Precharge Termination of a Burst22.1CAS Latency=222.2CAS Latency=31.Bank Activate Command Cycle (CAS latency =3)2.Burst Read Operation(Burst Length =4,CAS latency =2,3,4)latency =t CK3,I/O ’slatency =t CK4,I/O ’sCAS latency =CLKT0T2T1T3T4T5T6T7T8t CK2,I/O ’s3.Read Interrupted by a Read(Burst Length =4,CAS latency =2,3,4)4.1Read to Write Interval(Burst Length =4,CAS latency =3)t CK2,I/O ’slatency =t CK3,I/O ’sCAS latency =t CK4,I/O ’slatency =CLKT0T2T1T3T4T5T6T7T84.2Minimum Read to Write Interval (Burst Length=4,CAS latency=2)4.3Non-Minimum Read to Write Interval (Burst Length=4,CAS latency=2,3,45.Burst Write Operation(Burst Length=4,CAS latency=2,3,or4)6.1Write Interrupted by a Write(Burst Length=4,CAS latency=2,3,or4)I/O’sCLK T0T2T1T3T4T5T6T7T86.2Write Interrupted by a Read(Burst Length=4,CAS latency=2,3,4)7.Burst Write with Auto-Precharge Burst Length=2,CAS latency=2,3,4)7.2Burst Read with Auto-Precharge Burst Length=4,CAS latency=2,3,4)8.1Termination of a Full Page Burst Read Operation (CAS latency =2,3,4)8.2Termination of a Full Page Burst Write Operation (CAS latency =2,3,4)t CK2,I/O ’sCAS latency =t CK3,I/O ’sCAS latency =t CK4,I/O ’sCAS latency =CLKT0T2T1T3T4T5T6T7T8The burst ends after a delay equal to the CAS latency.MOSEL VITELIC V54C365804VD(L) Complete List of Operation CommandsSDRAM Function Truth TableCURRENTSTATE1CS RAS CAS WE BS Addr ACTIONIdle HLLLLLLL XHHHLLLLXHHLHHLLXHLXHLHLXXBSBSBSBSXOp-XXXXRAAPXCodeNOP or Power DownNOPILLEGAL2ILLEGAL2Row(&Bank)Active;Latch Row AddressNOP4Auto-Refresh or Self-Refresh5Mode reg.Access5Row Active HLLLLLL XHHHLLLXHLLHHLXXHLHLXXXBSBSBSBSXXXCA,APCA,APXAPXNOPNOPBegin Read;Latch CA;DetermineAPBegin Write;Latch CA;DetermineAPILLEGAL2PrechargeILLEGALRead HLLLLLLL XHHHHLLLXHHLLHHLXHLHLHLXXXBSBSBSBSBSXXXXCA,APCA,APXAPXNOP(Continue Burst to End;>Row Active)NOP(Continue Burst to End;>Row Active)Burst Stop Command>Row ActiveTerm Burst,New Read,DetermineAP3Term Burst,Start Write,DetermineAP3ILLEGAL2Term Burst,PrechargeILLEGALWrite HLLLLLLL XHHHHLLLXHHLLHHLXHLHLHLXXXBSBSBSBSBSXXXXCA,APCA,APXAPXNOP(Continue Burst to End;>Row Active)NOP(Continue Burst to End;>Row Active)Burst Stop Command>Row ActiveTerm Burst,Start Read,DetermineAP3Term Burst,New Write,DetermineAP3ILLEGAL2Term Burst,Precharge3ILLEGALReadwithAuto Precharge HLLLLLLLXHHHHLLLXHHLLHHLXHLHLHLXXXBSBSXBSBSXXXXXXXAPXNOP(Continue Burst to End;>Precharge)NOP(Continue Burst to End;>Precharge)ILLEGAL2ILLEGAL2ILLEGALILLEGAL2ILLEGAL2ILLEGAL49V54C365804VD(L)Rev.0.9September2001。

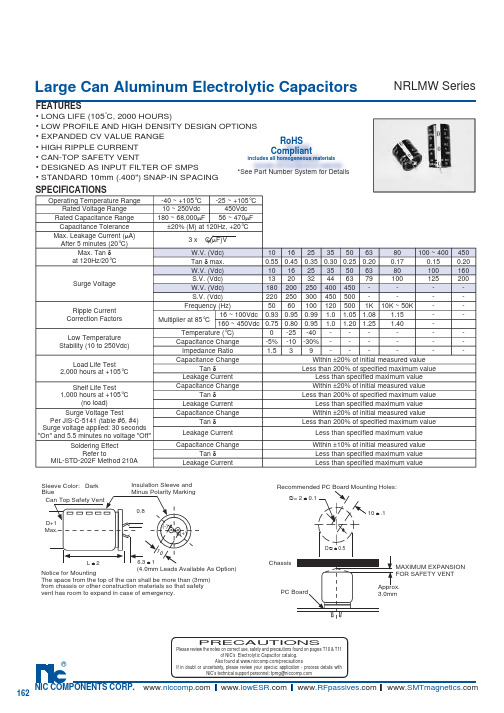

NRLMW223M250V25X50F中文资料

Large Can Aluminum Electrolytic CapacitorsFEATURES• LONG LIFE (105°C, 2000 HOURS)• LOW PROFILE AND HIGH DENSITY DESIGN OPTIONS • EXPANDED CV VALUE RANGE• HIGH RIPPLE CURRENT• CAN-TOP SAFETY VENT • DESIGNED AS INPUT FILTER OF SMPS• STANDARD 10mm (.400") SNAP-IN SPACING NRLMW SeriesSPECIFICATIONSNotice for MountingThe space from the top of the can shall be more than (3mm) from chassis or other construction materials so that safety vent has room to expand in case of emer g en c y.Sleeve Color: Dark BlueCan Top Safety VentInsulation Sleeve and Minus Polarity Marking(4.0mm Leads Available As Option)D+1Max.L ± 26.3 ± 10.810(-)(+)MAXIMUM EX P AN S IONFOR SAFETY VENT Approx. 3.0mmRecommended PC Board Mounting Holes:10 ± .1∅= 2 ± 0.1D ∅ ± 0.5ChassisPC BoardPRECAUTIONSPlease review the notes on correct use, safety and precautions found on pages T10 & T11of NIC’s Electrolytic Capacitor catalog . Operating Temperature Range-40 ~ +105°C -25 ~ +105°C Rated Voltage Range 10 ~ 250Vdc 450Vdc Rated Capacitance Range 180 ~ 68,000µF 56 ~ 470µF Capacitance Tolerance ±20% (M) at 120Hz, +20°CMax. Leakage Current (µA)After 5 minutes (20°C)3 x C(µF)VMax. Tan δat 120Hz/20°CW.V. (Vdc)10162535506380100 ~ 400450Tan δ max.0.550.450.350.300.250.200.170.150.20Surge VoltageW.V. (Vdc)10162535506380100160S.V. (Vdc)132032446379100125200W.V. (Vdc)180200250400450----S.V. (Vdc)220250300450500----Ripple Current Correction Factors Frequency (Hz)50601001205001K 10K ~ 50K --Multiplier at 85°C16 ~ 100Vdc0.930.950.99 1.0 1.05 1.08 1.15--160 ~ 450Vdc0.750.800.95 1.0 1.20 1.25 1.40-Low Temperature Stability (10 to 250Vdc)Temperature (°C)0-25-40------Capacitance Change -5%-10-30%------Impedance Ratio 1.539------Load Life Test 2,000 hours at +105°C Capacitance ChangeWithin ±20% of initial measured valueTan δLess than 200% of specifi ed maximum valueLeakage Current Less than specifi ed maximum value Shelf Life Test 1,000 hours at +105°C(no load)Capacitance ChangeWithin ±20% of initial measured value Tan δLess than 200% of specifi ed maximum valueLeakage Current Less than specifi ed maximum value Surge Voltage TestPer JIS-C-5141 (table #6, #4)Surge voltage applied: 30 seconds "On" and 5.5 minutes no voltage "Off"Capacitance ChangeWithin ±20% of initial measured value Tan δLess than 200% of specifi ed maximum valueLeakage Current Less than specifi ed maximum value Soldering EffectRefer toMIL-STD-202F Method 210ACapacitance ChangeWithin ±10% of initial measured valueTan δLess than specifi ed maximum value Leakage CurrentLess than specifi ed maximum valueRoHSCompliantincludes all homogeneous materials *See Part Number System for DetailsLarge Can Aluminum Electrolytic Capacitors NRLMW SeriesLarge Can Aluminum Electrolytic CapacitorsNRLMW SeriesNRLMW 471 M 250V 30X35 FRoHS compliant Case Size (mm) Voltage Rating Tolerance Code Capacitance Code SeriesPART NUMBER SYSTEM。

海尔 统帅

物料编码物料描述颜色备注发放标准适用机型事业部产品类别统帅电视ZC123C3262001铭牌1LC32MUK2,L3日日顺事业部统帅电视ZC511C2461S04按键板贴片组件1L32A8A-A1统日日顺事业部统帅电视ZC4031C326206说明书1L32A8A-A1统日日顺事业部统帅电视ZC523C1945M01电源开关线组件1L32A8A-A1统日日顺事业部统帅电视ZC30450210003电源线1L32A8A-A1统日日顺事业部941-0624-18103G电源板01LE23T6,日日顺事业部统帅电视统帅电视603-4502-40217G LVDS线1L26N1,L26N1日日顺事业部统帅电视PC00600010907按键黑色机器的12位、1L32N1统帅下日日顺事业部统帅电视715-0201-00422G透明塑胶支撑1LC42UT7,LC4日日顺事业部统帅电视715-2701-32001G遥控接收窗1LE32T6(N)统日日顺事业部统帅电视RTSWC477YA01001顶部保利龙1LE32UT8,日日顺事业部RTSWC477YA02001底部保利龙1LE32UT8,日日顺事业部统帅电视统帅电视721-42H2-12LEDG leader 中文纸箱1LC42ST7,LC4日日顺事业部统帅电视702-554B-51001G后壳黑色1L55R6统帅下日日顺事业部773-0810-52003G音箱1LC32UT7,LC3日日顺事业部统帅电视统帅电视CP010********I/O标贴5L32A8A-A1统日日顺事业部白色1L42A8A-A1统日日顺事业部统帅电视CP01500000110珍珠棉保护物统帅电视EL020********线材组机器的12位、1L32N1统帅下日日顺事业部统帅电视ME00000202758支架1L42A8A-A1统日日顺事业部PC00800010509导光件白色1L26A8A-A1统日日顺事业部统帅电视统帅电视941-0606-47001G电源板申请备件要提1L46A8A-A(N)日日顺事业部721-55F3-12LEDG leader 中文纸箱1L55R6统帅下日日顺事业部统帅电视统帅电视724-47H2-11LEDG leader中文说明书1L46A8A-A(N)日日顺事业部统帅电视715-2701-10328G遥控接收窗机器的12位、1L26N1统帅下日日顺事业部统帅电视CP00600000730后铭牌机器的12位、1L42N1统帅下日日顺事业部统帅电视CP01500000412珍珠棉保护物白色1L26A8A-A1统日日顺事业部统帅电视EN00231500702PANEL银色机器的12位、1L32A8A-A1统日日顺事业部MS020********螺丝机器的12位、30L42A8A-A1统日日顺事业部统帅电视统帅电视PC00300020545前壳UV黑1L42A8A-A1统日日顺事业部统帅电视PC01900010904垫片机器的12位、1L32N1统帅下日日顺事业部统帅电视CP01500000484保丽龙白色机器的12位、1L42N1统帅下日日顺事业部统帅电视EO00221500106电源线黑色机器的12位、5L26A8A-A1统日日顺事业部统帅电视ME00000202757支架1L32A8A-A1统日日顺事业部统帅电视ME00601014052端子板1L32A8A-A1统日日顺事业部统帅电视941-11T2-61923G主板机器十二位、1LC32UT7,LC3日日顺事业部统帅电视941-2001-96101G灯板组件机器的12位、1L26N1统帅下日日顺事业部EL020********线材组机器的12位、1L42A8A-A1统日日顺事业部统帅电视统帅电视ME00000300290壁挂支架机器的12位、1L42N1统帅下日日顺事业部MS00013008100螺丝30L42A8A-A1统日日顺事业部统帅电视统帅电视715-0201-00191G透明PC立柱1LE24T6统帅下日日顺事业部统帅电视CP00700000200条码标贴机器的12位、1L26A8A-A,L3日日顺事业部统帅电视CP0310*******标示贴白底黑字机器的12位、1L26A8A-A1统日日顺事业部统帅电视EL020********线材组机器的12位、1L42A8A-A1统日日顺事业部统帅电视ME00000202756支架1L42A8A-A1统日日顺事业部统帅电视MS020********螺丝机器的12位、30L26A8A-A1统日日顺事业部OG00800000100醋酸布黑色机器的12位、1L26A8A-A1统日日顺事业部统帅电视统帅电视PC00500010516底座UV黑1L26A8A-A1统日日顺事业部统帅电视941-11T7-64919G主板1LE42H86(N)统日日顺事业部统帅电视701-420D-46000G面壳黑色1LE42UL3,LE4日日顺事业部日日顺事业部统帅电视715-0201-00423G透明PC立柱1LE42H86(N)统统帅电视941-11T8-64904G主板1LE42TSA1,日日顺事业部统帅电视721-Z0BN-12LEDG纸箱1LE42TSA1,日日顺事业部统帅电视742-420L-04004G3D LCD硬屏1LC42ST7,LC4日日顺事业部统帅电视722-Z0BN-00112G保丽龙1LE42TSA1,日日顺事业部统帅电视702-324B-60004G后壳黑色1LC32UT7,LC3日日顺事业部统帅电视ME00601900251底座立板银色1L42A8A-A1统日日顺事业部统帅电视MS04003006100螺丝机器的12位、30L26A8A-A1统日日顺事业部PC00100020513后壳黑色1L42A8A-A1统日日顺事业部统帅电视统帅电视742-320L-C4006G LCD硬屏机器的12位、1LC32UT7,LC3日日顺事业部统帅电视941-0311-32L01G按键板组件1LE42H86,LE4日日顺事业部941-1619-T4201G遥控接收板组件1LC32UT7,LC3日日顺事业部统帅电视统帅电视742-420L-04006G屏1LE42TSA1,日日顺事业部统帅电视941-0617-13150G电源板1LE23T6,日日顺事业部统帅电视CP01500000542保丽龙白色机器的12位、1L32N1统帅下日日顺事业部统帅电视701-320F-U7000G面壳黑色1LE32T6(N)统日日顺事业部统帅电视702-264B-55004G后壳黑色1L26N1统帅下日日顺事业部统帅电视703-32U7-58011G底座黑色机器的12位、1L32N1统帅下日日顺事业部统帅电视MS020********螺丝机器的12位、30L32A8A-A1统日日顺事业部统帅电视RTSWC607YA03001底座1LE32UT8,日日顺事业部RTL010*******功能按键支架19F8(不带DVD)1LE19TF8,日日顺事业部统帅电视统帅电视CP00600000729后铭牌机器的12位、1L32N1统帅下日日顺事业部CP01500000249珍珠棉保护物统帅电视白色1L32A8A-A1统日日顺事业部统帅电视ME00201100291固定板机器的12位、1L42N1统帅下日日顺事业部统帅电视MS020********螺丝机器的12位、30L26A8A-A1统日日顺事业部统帅电视724-42H2-11LEDG leader 中文说明书1LC42ST7,LC4日日顺事业部统帅电视941-11T7-68410G主板DC1FP0002001LE23T6,LE24日日顺事业部统帅电视715-0201-00192G透明PC立柱1LE23T6,日日顺事业部统帅电视7002-32L31D-14B00001后壳01LE32KUH3,日日顺事业部7601-31T091-0144LED1遥控器01LE32KUH3,LE日日顺事业部统帅电视统帅电视RTL113070744主板绿色可用RTL01131LE46ZA1,日日顺事业部统帅电视110-0102-50805G1K电阻1L32N1,L32N1日日顺事业部RGJZJ320001支架1LE32PUV3,日日顺事业部统帅电视统帅电视RGJDZ390001底座1LE39PUV3,日日顺事业部统帅电视RGJHK460001后壳1LE46PUV1,日日顺事业部统帅电视RGJYJP46001液晶屏1LE46PUV1,日日顺事业部统帅电视941-11T7-61428G主板序列号为DC11LE24T6统帅下日日顺事业部统帅电视723-55F1-02102G整机包装袋1LE55TSA1,日日顺事业部统帅电视MS020********螺丝机器的12位、30L42A8A-A1统日日顺事业部统帅电视941-0617-15202G电源板可用941-0611LC32UT7,LC3日日顺事业部统帅电视RTSWC5425075021CN按键板1LE42WND2,日日顺事业部统帅电视RTSWC607YB07001CN底座1LE42WND2,日日顺事业部统帅电视941-0321-32L01G按键板组件1LE42TNC1,LE日日顺事业部统帅电视724-322L-13LEDG说明书1LE42TNC1,LE日日顺事业部统帅电视722-321L-00113G保丽龙1LE32TNC1,日日顺事业部统帅电视901-0104-45LEDG遥控器1LE32TA1,LC3日日顺事业部统帅电视773-0810-00009G喇叭1LE42TNC1,日日顺事业部统帅电视721-422L-12LEDG纸箱1LE42TNC1,日日顺事业部统帅电视RTL0113010467按键板组件 01LE55TS3,LE5日日顺事业部统帅电视7917-020001-000000013D偏光眼镜 (夹片)1LE42KCH1,LE日日顺事业部ZC4031C322005说明书1LC32MUK2,日日顺事业部统帅电视统帅电视ZC514C3207M04电源板组件1L32A8A-A1统日日顺事业部统帅电视7037-420L31-40041101透明立柱1LE42KUH1,日日顺事业部统帅电视ZC316Q420M002屏1LE42MUF1,日日顺事业部统帅电视RGJDYB42001电源板1LE42PUV1,日日顺事业部统帅电视703-PWU7-54011G底座1LE23T6,日日顺事业部724-32H2-19LEDG说明书1LC32TD11下乡统帅电视日日顺事业部统帅电视742-230P-42003G屏DC1FP0002001LE23T6,LE24日日顺事业部721-P0BF-14LEDG纸箱1LE23T6,日日顺事业部统帅电视统帅电视931-0005-01019G26-55 通用挂墙件组件1LC37UT7,LC3日日顺事业部统帅电视RTL101040430底座面板 40Z10H1LC39LUG1,日日顺事业部统帅电视ZC4031Q460101说明书1LE46MUF3,日日顺事业部统帅电视722-P0B0-00111G保丽龙1LE23T6,日日顺事业部统帅电视RTSWC427YB16001CN脖子1LE42WND2,日日顺事业部统帅电视RTL112010405遥控板光板 RMT1121LC39LUG1,日日顺事业部统帅电视RTL11542000139液晶显示屏 V390HJ1-L011LC39LUG1,LC日日顺事业部统帅电视RTSWC447YA01031包装箱1LE32UT8,日日顺事业部统帅电视RTSWC5607047291液晶屏1LE32UT8,日日顺事业部统帅电视292-6825-50805G贴片电容1L42N1统帅下日日顺事业部统帅电视ZC511C3276S02按键板贴片组件1LE32MUF1,LE日日顺事业部ZC515C2408M57主板组件1LE42MUF1,LE日日顺事业部统帅电视统帅电视RGJDYXTY001电源线1LE32PUV3,LE日日顺事业部统帅电视RGJZB420001主板1LE42PUV1,日日顺事业部统帅电视ZC102C3218111底座组件1LC32MUK2,L3日日顺事业部统帅电视RTSWC5604085011电源板1LE32UT8,日日顺事业部统帅电视601-2210-14105G电源线机器的12位、1L26N1统帅下日日顺事业部715-26F1-02002G底座支架1L26N1统帅下日日顺事业部统帅电视统帅电视ZC511C2641S03红外灯板贴片组件1LC32MUK2,L3日日顺事业部统帅电视941-0606-55001G电源板套件1L55R6统帅下日日顺事业部RTL010*******玻璃面板01LE55TS3,LE5日日顺事业部统帅电视统帅电视7030-320L11-4U711101排钮1LE55KCA1,日日顺事业部统帅电视ZC101Q3701111面壳1LE37MUF1,日日顺事业部统帅电视RTL010*******玻璃底座面板 22ZF1LE22BL1,日日顺事业部统帅电视RTL0113010496遥控板 RMT056-6(红绿)1LE22BL1,日日顺事业部统帅电视RTL0113050413LED驱动板组01LE22ZA1,LE2日日顺事业部统帅电视RTL0115340022液晶显示屏 TB215WU3 R113 B0331LE22BL1,日日顺事业部统帅电视ZC506C3268101底座组件1L32A8A-A1统日日顺事业部统帅电视702-324B-70002G后壳1LE32TNC1,日日顺事业部统帅电视941-2401-RTL05G USB模块小板1LE42TNC1,LE日日顺事业部日日顺事业部统帅电视702-324B-60006G后壳1LC32TD11下乡统帅电视日日顺事业部941-11T2-68911G主板用941-11T2-1LC32TD11下乡统帅电视941-12T8-64901G主板1LE42TNC1,日日顺事业部统帅电视941-2401-29902G网络板1LE42TNC1,LE日日顺事业部统帅电视941-11T8-68909G主板序列号为DH01LE32T6(N)统日日顺事业部统帅电视RTL101030696底座立柱(ABS新料) 40Z10H1LC39LUG1,日日顺事业部统帅电视724-W0FN-13LEDG说明书1LE42H86统帅日日顺事业部702-424B-61001G黑色后壳1LE42H86统帅日日顺事业部统帅电视统帅电视740-1201-N1822G3D眼镜1LE55TSA1,LE日日顺事业部统帅电视742-550L-O4007G屏1LE55TSA1,日日顺事业部ZC30443010523LVDS线1L32A8A-A1统日日顺事业部统帅电视统帅电视ZC30434020301LVDS线1LE42MUF1,日日顺事业部统帅电视ZC514C4205M04电源板1LE46MUF1,LE日日顺事业部统帅电视ZC316Q420M001屏序列号:6001LE42MUF1,日日顺事业部统帅电视RGJLBTY0001喇叭1LE32PUV3,LE日日顺事业部统帅电视MS010********螺丝机器的12位、30L32N1统帅下日日顺事业部统帅电视MS020********螺丝30L32A8A-A1统日日顺事业部统帅电视MS04003005100螺丝机器的12位、30L32N1统帅下日日顺事业部统帅电视PC00500010503底座UV黑1L42A8A-A1统日日顺事业部统帅电视PC00500010916底座UV黑机器的12位、1L32N1统帅下日日顺事业部统帅电视PC023********EVA垫机器的12位、5L32N1统帅下日日顺事业部统帅电视742-420L-I4008G LCD硬屏(16:9)机器的12位、1LC42UT7,LC4日日顺事业部统帅电视日日顺事业部941-0402-19501G指示灯板组件1LE24T6统帅下统帅电视941-0606-42201G电源板套件1LC42ST7,LC4日日顺事业部统帅电视CP01500000486保丽龙白色机器的12位、1L42N1统帅下日日顺事业部统帅电视ME00301200456转接件银色1L32A8A-A1统日日顺事业部统帅电视MS020********螺丝30L32A8A-A1统日日顺事业部MS020********螺丝机器的12位、30L42N1统帅下日日顺事业部统帅电视统帅电视PC00100010554后壳黑色1L32A8A-A1统日日顺事业部统帅电视PC01500010908橡胶垫黑色机器的12位、1L32N1统帅下日日顺事业部941-0319-L1101G按键板组件1LE24T6统帅下统帅电视日日顺事业部统帅电视RTSWC477YB04001CN底部保利壟1LE42WND2,日日顺事业部统帅电视RTSWC2340A1H011CN扬声器1LE42WND2,日日顺事业部RTL010*******前壳01LE55TS3,LE5日日顺事业部统帅电视统帅电视7311-420S31-101LED11说明书1LE42KCH1,日日顺事业部统帅电视6149-210063-30R11213LVDS线1LE24KUH1,日日顺事业部统帅电视6149-510063-51781221LVDS线1LE55KCA1,日日顺事业部统帅电视7423-550LG2-38000051屏1LE55KCA1,日日顺事业部统帅电视941-1621-42L01G遥控接收板1LE42TNC1,日日顺事业部统帅电视941-0609-262KTG电源板1LE32TA1下乡日日顺事业部统帅电视ZC4060Q370105外箱1LE37MUF1,日日顺事业部RGJZX390001纸箱1LE39PUV3,日日顺事业部统帅电视统帅电视RGJQK420001前框1LE42PUV1,日日顺事业部RGJHK320001后壳1LE32PUV3,日日顺事业部统帅电视统帅电视7311-320L31-101LED11说明书1LE42KUH1,日日顺事业部统帅电视9014-111L11-00001011按键板组件1LE55KCA1,日日顺事业部统帅电视9012-111A18-15002011电源板1LE42KCH1,日日顺事业部统帅电视ZC4031Q320121说明书1LE32MUF1,日日顺事业部统帅电视ZC103Q4601113后盖1LE46MUF3,日日顺事业部统帅电视702-324B-63001G后壳1LE32TA1,日日顺事业部统帅电视941-0607-2610KG电源板DH00J0M01001LE42TNC1,LE日日顺事业部统帅电视RTL0113010734遥控板组件01LE39LXZ1,日日顺事业部统帅电视9014-112L31-00001011按键板组件1LE42KCH1,LE日日顺事业部统帅电视7002-550L11-14B00001后壳1LE55KCA1,日日顺事业部统帅电视RTL0119010617纸箱(拆底座) 55Z12 两件套1LE55LXZ1,LE日日顺事业部721-26F3-12LEDG leader中文纸箱1L26N1统帅下日日顺事业部统帅电视统帅电视721-32H2-12LEDG leader中文纸箱1LC32UT7,LC3日日顺事业部统帅电视721-37F3-12LEDG leader中文纸箱1L37N1统帅下日日顺事业部统帅电视CM08000100004标识卡机器的12位、1L32N1统帅下日日顺事业部统帅电视CP0310*******标示贴白底黑字机器的12位、1L26A8A-A1统日日顺事业部统帅电视RTL113050494电源板组件 HTX-PI420201A B0901LE39LXZ1,日日顺事业部RGJAJBTY401按键板1LE42PUV1,LE日日顺事业部统帅电视统帅电视701-Z0FN-U7000G面壳黑色1LE42H86统帅日日顺事业部统帅电视941-0607-377KTG电源板1LC37UT7,日日顺事业部统帅电视RTSWC477YA04001底部保利龙1LE42UT8,日日顺事业部统帅电视RTSWC5607049081液晶屏可用RTSWC561LE42UT8,日日顺事业部统帅电视ZC30434020181LVDS线1LE37MUF1,日日顺事业部统帅电视RGJYKQTY001遥控器1LE32PUV3,LE日日顺事业部RTSWC607YA04001脖子1LE32UT8,日日顺事业部统帅电视统帅电视742-320S-04002G LED背光硬屏1LE32T6(N)统日日顺事业部统帅电视RTL0113010384PWR按键板组01LE55TS3,LE5日日顺事业部9012-111419-25005011电源板1LE55KCA1,日日顺事业部统帅电视统帅电视ZC506Q3901101底座组件1LE39MUF1,LE日日顺事业部统帅电视702-424B-54001G后壳黑色机器的12位、1L42N1统帅下日日顺事业部统帅电视CP01500000543保丽龙白色机器的12位、1L32N1统帅下日日顺事业部统帅电视ME00000204092支架机器的12位、1L32N1统帅下日日顺事业部统帅电视PC01900010903垫片机器的12位、1L32N1统帅下日日顺事业部统帅电视7711-22858A-50000011喇叭1LE42KUH1,日日顺事业部统帅电视ZC103Q3701112后盖1LE37MUF1,日日顺事业部统帅电视RTL011542001939液晶显示屏01LE39LXZ1,日日顺事业部统帅电视7001-550L11-0U700001前框1LE55KCA1,日日顺事业部ZC316Q315M004屏1LE32MUF1,LE日日顺事业部统帅电视统帅电视RTL011534003121.5液晶显示01LE22ZA1,LE2日日顺事业部统帅电视9011-11T822-333D2071主板1LE55KCA1,日日顺事业部ZC123C2662001铭牌1LU26T3,LE26日日顺事业部统帅电视统帅电视RTL010*******玻璃底座组件01LE39LXZ1,日日顺事业部统帅电视CM08000100008标识卡1L26A8A-A1统日日顺事业部统帅电视CP010********I/O标贴5L26A8A-A1统日日顺事业部统帅电视CP0370*******纸箱扣白色4L42A8A-A1统日日顺事业部统帅电视EL020********线材组机器的12位、1L26A8A-A1统日日顺事业部统帅电视ER020********遥控器黑色厂家不在提供1L26A8A-A,L3日日顺事业部统帅电视ME00000301110支架1L26A8A-A1统日日顺事业部统帅电视ME00500800153底座底板1L42A8A-A1统日日顺事业部统帅电视ME00601900157底座立板银色1L32A8A-A1统日日顺事业部统帅电视PC00100010923后壳黑色机器的12位、1L42N1统帅下日日顺事业部统帅电视742-320L-04002G LED背光硬屏1LE32T6(N)统日日顺事业部RTL0113010586遥控板组件01LE55TS3,LE5日日顺事业部统帅电视统帅电视7030-420L31-4U711201排钮1LE42KCH1,日日顺事业部统帅电视ZC4031C322006说明书1L32M1统帅,日日顺事业部统帅电视ZC4031C266206说明书1LU26T3,日日顺事业部统帅电视941-0624-17103G电源板1LE23T6,日日顺事业部统帅电视RTL010*******后盖 55Z1201LE55TS3,LE5日日顺事业部7311-550S11-101LED11说明书1LE55KCA1,日日顺事业部统帅电视统帅电视941-1621-42L06G遥控接收板1LE32TNC1,日日顺事业部统帅电视RGJIRTY3001IR板1LE32PUV3,LE日日顺事业部941-0302-42101G按键板组件机器的12位、1LC32UT7,LC3日日顺事业部统帅电视统帅电视941-0617-15206G电源板1L26N1统帅下日日顺事业部统帅电视RTSWC5425087031CN IR 板1LE42WND2,日日顺事业部统帅电视7711-22868A-02000011喇叭1LE42KCH1,日日顺事业部统帅电视7002-420L31-34B00001后壳1LE42KCH1,日日顺事业部统帅电视6264-250008-13210001开关1LE24KUH1,日日顺事业部统帅电视7711-20868A-51000011喇叭1LE55KCA1,日日顺事业部统帅电视9012-111A18-15002021电源板1LE42KUH1,日日顺事业部统帅电视7422-420LG2-38000011屏1LE42KUH1,日日顺事业部统帅电视ZC30450180001电源线1LE32MUF1,LE日日顺事业部统帅电视ZC103C2261116后盖1LU26T3,日日顺事业部统帅电视ZC515C2407M20主板组件1LE32MUF1,LE日日顺事业部RGJZJTY4001支架1LE42PUV1,LE日日顺事业部统帅电视统帅电视9011-11T71A-172F3011主板1LE24KUH1,日日顺事业部702-424B-63001G后壳1LE42TNC1,日日顺事业部统帅电视统帅电视ZC504MTC32611喇叭1L32A8A-A1统日日顺事业部统帅电视日日顺事业部601-1515-14101G电源线1LE24T6统帅下统帅电视715-32F1-03001G底座支撑机器的12位、1L32N1统帅下日日顺事业部统帅电视724-26F3-11LEDG leader中文说明书机器的12位、1L26N1统帅下日日顺事业部统帅电视EL020********线材组机器的12位、1L32A8A-A1统日日顺事业部统帅电视EL020********线材组机器的12位、1L42N1统帅下日日顺事业部统帅电视ME00000200697支架机器的12位、1L42N1统帅下日日顺事业部统帅电视ME00601000694端子板机器的12位、1L32N1统帅下日日顺事业部统帅电视MS04003008500螺丝30L26A8A-A1统日日顺事业部统帅电视715-2701-00425G遥控接收窗1LE42TNC1,LE日日顺事业部统帅电视722-421L-00113G保丽龙1LE42TNC1,日日顺事业部773-0810-90019G喇叭1LE32TNC1,日日顺事业部统帅电视统帅电视941-0617-15214G电源板可申请941-01LC32TD11下乡日日顺事业部统帅电视7001-420L31-0U700001前框1LE42KUH1,日日顺事业部7423-420LG2-38000051屏1LE42KCH1,日日顺事业部统帅电视统帅电视RTL01130602403D转接板组件01LE55TS3,LE5日日顺事业部统帅电视7917-014401-N1822NR13D偏光眼镜 黑色塑框1LE42KCH1,LE日日顺事业部统帅电视9011-11T822-333D2041主板1LE42KCH1,日日顺事业部统帅电视ZC103C3217111后盖1LC32MUK2,L3日日顺事业部统帅电视RTL010*******前壳 185Z3801LE19TF8,日日顺事业部统帅电视RTSWC447YB02061CN包装箱1LE42WND2,日日顺事业部统帅电视RTSWC5425088011CN机芯主板1LE42WND2,日日顺事业部统帅电视9015-111L11-21034021遥控接收板1LE55KCA1,日日顺事业部统帅电视7211-24L41E-101LED11纸箱1LE24KUH1,日日顺事业部统帅电视9030-248188-00021011网络USB模块小板1LE42KCH1,LE日日顺事业部统帅电视RGJDYXTY002电源线1LE42PUV1,LE日日顺事业部统帅电视ZC515C2207M46主板组件(包含电源板)1LU26T3,LE26日日顺事业部统帅电视RTL101010537前壳 39Z10H 喷涂详见墨稿,预装1LC39LUG1,日日顺事业部统帅电视RTL113050462电源板组件 HTX-PI390101A1LC39LUG1,日日顺事业部ZC506C2668101底座组件1LU26T3,LE26日日顺事业部统帅电视统帅电视RTL0113050549电源板组件01LE55TS3,LE5日日顺事业部统帅电视6149-450063-51711201LVDS线1LE42KCH1,LE日日顺事业部统帅电视ZC103Q3201117后盖1LE32MUF3,日日顺事业部统帅电视701-32H2-U7003G面壳黑色1LC32UT7,LC3日日顺事业部统帅电视703-37U7-52011G底座黑色1L37N1统帅下日日顺事业部715-0201-00324G透明底座立柱1LE32T6(N)统日日顺事业部统帅电视统帅电视715-2701-00424G遥控接收窗1LE42H86(N)统日日顺事业部统帅电视ZC103Q4601111后盖1LE46MUF1,日日顺事业部统帅电视9011-11T92A-173F2051主板01LE42KUH1,日日顺事业部统帅电视RTL010*******后壳 236Z2801LE24ZA1,日日顺事业部统帅电视RTL011535004223.6液晶显示01LE24ZA1,日日顺事业部统帅电视715-2701-00552G遥控接收窗1LE42H86统帅日日顺事业部统帅电视941-1619-L1104G遥控接收板1LE55TSA1,LE日日顺事业部773-0810-13A01G喇叭1LE55TSA1,日日顺事业部统帅电视统帅电视RGJDZ320001底座1LE32PUV3,日日顺事业部统帅电视RGJZB320001主板1LE32PUV3,日日顺事业部统帅电视RGJYJP42001液晶屏1LE42PUV1,日日顺事业部统帅电视RGJQK390001前框1LE39PUV3,日日顺事业部统帅电视721-32F3-12LEDG leader中文纸箱机器的12位、1L32N1统帅下日日顺事业部EL020********线材组1L26A8A-A1统日日顺事业部统帅电视统帅电视EL020********线材组机器的12位、1L32A8A-A1统日日顺事业部统帅电视ME00601000696端子板机器的12位、1L42N1统帅下日日顺事业部RTSWC497YA01021CN说明书1LE32UT8,LE4日日顺事业部统帅电视统帅电视RTSWC607YA17001前壳1LE42UT8,日日顺事业部统帅电视ZC4060C326203外箱1L32A8A-A1统日日顺事业部统帅电视ZC103Q4201112后盖1LE42MUF1,日日顺事业部统帅电视721-550B-12LEDG纸箱1LE55TSA1,日日顺事业部统帅电视7711-208035-41605011喇叭1LE24KUH1,日日顺事业部统帅电视9030-112918-00011021RK2918方案 网络板1LE42KCH1,LE日日顺事业部统帅电视ZC4060Q320115外箱1LE32MUF1,LE日日顺事业部统帅电视702-324B-61003G后壳黑色1LE32T6(N)统日日顺事业部统帅电视白色1L42A8A-A1统日日顺事业部CP01500000111珍珠棉保护物统帅电视CP01500000487保丽龙白色机器的12位、1L42N1统帅下日日顺事业部统帅电视EB010********电池机器的12位、10L26A8A-A1统日日顺事业部统帅电视EL020********线材组1L26A8A-A1统日日顺事业部统帅电视EP00040204300KEY板1L26A8A-A1统日日顺事业部统帅电视ME00200700452屏压片银色机器的12位、1L26A8A-A,L3日日顺事业部统帅电视PC00600010518按键黑色1L26A8A-A1统日日顺事业部统帅电视RTL0113050409LED驱动板组01LE19TF8,日日顺事业部RTL011536001746液晶显示屏01LE46ZA1,日日顺事业部统帅电视统帅电视7311-24L41E-101LED11说明书1LE24KUH1,日日顺事业部统帅电视6110-151422-01432101电源线1LE24KUH1,日日顺事业部7211-420S31-101LED11纸箱1LE42KCH1,日日顺事业部统帅电视统帅电视7002-420L31-14B00001后壳1LE42KUH1,日日顺事业部统帅电视7422-236BEK-28000021屏1LE24KUH1,日日顺事业部统帅电视7422-236CMK-28000031屏1LE24KUH1,日日顺事业部统帅电视ZC4060C266204外箱1LU26T3,LE26日日顺事业部统帅电视ZC316Q315M008屏序列号:6001LE32MUF1,日日顺事业部统帅电视ZC316Q460M001屏序列号:6001LE46MUF1,LE日日顺事业部统帅电视703-42U7-57011G底座黑色1LC42UT7,LC4日日顺事业部统帅电视ZC316Q390M001屏序列号:6001LE39MUF1,日日顺事业部日日顺事业部统帅电视黑色1LE24T6统帅下492-P0B0-01001G方形玻璃底座统帅电视ZC316MTC31563屏生产序列号:1L32A8A-A1统日日顺事业部统帅电视ZC514C3203M03电源驱动板组件1LC32MUK2,L3日日顺事业部统帅电视703-42U7-58011G底座1LE42TSA1,日日顺事业部统帅电视RGJHK390001后壳1LE39PUV3,日日顺事业部统帅电视ZC101C2661112面板1LU26T3,LE26日日顺事业部RTL113070807主板组件 T.MS6M182.21B-11LC39LUG1,日日顺事业部统帅电视统帅电视RTL101010562前壳46Z18A1LE46ZA1,日日顺事业部ZC316MTC31569屏1LE32MUK1,日日顺事业部统帅电视统帅电视728-0000-03LEDG LOGO1L42N1,L42N1日日顺事业部统帅电视6110-151522-01422101电源线1LE42KUH1,日日顺事业部统帅电视ZC504MTC32614喇叭(套)1LE32MUF1,LE日日顺事业部统帅电视ZC514C4205M03电源板1LE42MUF1,LE日日顺事业部统帅电视701-550B-U7000G面框1LE55TSA1,日日顺事业部统帅电视RGJAJBTY301按键板1LE32PUV3,LE日日顺事业部统帅电视RGJQK460001前框1LE46PUV1,日日顺事业部统帅电视RGJZB460001主板1LE46PUV1,日日顺事业部721-420F-12LEDG leader中文纸箱1LE42UL3,LE4日日顺事业部统帅电视统帅电视724-P0BF-11LEDG leader中文说明书1LE24T6统帅下日日顺事业部统帅电视CP01500000485保丽龙白色机器的12位、1L42N1统帅下日日顺事业部统帅电视EL020********线材组机器的12位、1L32N1统帅下日日顺事业部统帅电视ME00301200593连接件机器的12位、1L42N1统帅下日日顺事业部统帅电视MS04013010100螺丝机器的12位、30L42N1统帅下日日顺事业部统帅电视492-320B-01001G方形玻璃底座黑色1LE32T6(N)统日日顺事业部统帅电视日日顺事业部715-2701-00235G遥控接收窗1LE24T6统帅下统帅电视721-42H2-14LEDG leader中文纸箱1LC42UT7,LC4日日顺事业部统帅电视773-0805-50004G音箱1LE24T6统帅下日日顺事业部统帅电视CP01500000109珍珠棉保护物白色1L42A8A-A1统日日顺事业部统帅电视CP01700000556纸箱机器的12位、1L32N1统帅下日日顺事业部统帅电视EP00041100626POWER板机器的12位、1L32A8A-A1统日日顺事业部统帅电视ME00000300294壁挂支架机器的12位、1L32N1统帅下日日顺事业部统帅电视703-32U7-52001G底座1LE32TA1,日日顺事业部统帅电视701-422L-46001G前框1LE42TNC1,日日顺事业部ZC511C2461M01红外接收板组件1L32A8A-A1统日日顺事业部统帅电视统帅电视ZC30433020451LVDS线1LC32MUK2,L3日日顺事业部ZC511C2462S01按键板贴片组件1LU26T3,LE26日日顺事业部统帅电视统帅电视ZC4031Q420102说明书1LE42MUF1,LE日日顺事业部统帅电视ZC4060Q390106外箱1LE39MUF1,日日顺事业部ZC511C3262M03红外接收板组件1LE42MUF1,LE日日顺事业部统帅电视统帅电视601-1510-1D101G电源线1LE55TSA1,LE日日顺事业部统帅电视722-550B-00112G保丽龙1LE55TSA1,日日顺事业部统帅电视742-550L-O4006G屏1LE55TSA1,日日顺事业部统帅电视ZC4060C322003外箱1LC32MUK2,L3日日顺事业部统帅电视ZC504C3262102遥控器1L32M1统帅,L日日顺事业部941-11T2-64907G主板1LC42ST7,LC4日日顺事业部统帅电视统帅电视901-0111-44LEDG遥控器1LE42TNC1,LE日日顺事业部统帅电视701-322L-46002G前框1LE32TNC1,日日顺事业部统帅电视ZC103Q4201114后盖1LE42MUF1,日日顺事业部统帅电视715-0201-00323G透明塑胶支撑1LC32UT7,LC3日日顺事业部统帅电视721-420D-12LEDG leader中文纸箱1LE42UL3,LE4日日顺事业部CP01100000202纸箱标贴1L26A8A-A1统日日顺事业部统帅电视统帅电视CP0310*******标示贴白底黑字机器的12位、1L26A8A-A1统日日顺事业部统帅电视708-0100-76021G导光柱1LE24T6统帅下日日顺事业部统帅电视日日顺事业部黑色1LE42H86(N)统492-370B-01001G方形玻璃底座统帅电视702-374B-62001G后壳黑色1LC37UT7,LC3日日顺事业部统帅电视703-42U7-56011G底座黑色机器的12位、1L42N1统帅下日日顺事业部统帅电视ME00000300250支架1L42A8A-A1统日日顺事业部ME00301200452转接件银色1L42A8A-A1统日日顺事业部统帅电视统帅电视PC00800010500导光件白色1L32A8A-A1统日日顺事业部742-420U-04001G LED背光屏(倒立)1LE42H86(N)统统帅电视日日顺事业部统帅电视941-0402-32501G指示灯板组件1LE42H86统帅日日顺事业部统帅电视RTSWC5607049081CN液晶屏1LE42WND2,LE日日顺事业部ZC101C3217112面板1LC32MUK2,L3日日顺事业部统帅电视统帅电视CP03600000100手提扣白色1L26A8A-A1统日日顺事业部统帅电视EL020********线材组1L32A8A-A1统日日顺事业部统帅电视EL020********线材组1L32A8A-A1统日日顺事业部统帅电视ME00000300155支架1L26A8A-A1统日日顺事业部统帅电视RTL111100115扬声器 YDT513-09-8Ω/10W1LC39LUG1,日日顺事业部统帅电视RGJIRTY4001IR板1LE42PUV1,日日顺事业部721-42F3-12LEDG leader中文纸箱机器的12位、1L42N1统帅下日日顺事业部统帅电视统帅电视765-8003-25041G跷板电源开关1LE42H86(N)统日日顺事业部统帅电视ME00000204091支撑板机器的12位、1L32N1统帅下日日顺事业部统帅电视ME00201100290固定板机器的12位、1L42N1统帅下日日顺事业部统帅电视PC010********装饰条红色1L26A8A-A1统日日顺事业部统帅电视PC02600010901轴套黑色机器的12位、1L42N1统帅下日日顺事业部统帅电视RTSWC2701518Y21CN电源线1LE42WND2,日日顺事业部ZC4031C326205说明书1LE32MUK1,日日顺事业部统帅电视统帅电视ZC316MTC31553屏L32M1统帅序1L32A8A-A1统日日顺事业部统帅电视715-0201-00325G透明立柱1LE32TA1,日日顺事业部统帅电视701-37F3-U7000G面壳黑色1L37N1统帅下日日顺事业部统帅电视702-374B-53002G后壳黑色1L37N1统帅下日日顺事业部统帅电视CM06000100065底座安装指南机器的12位、1L26A8A-A1统日日顺事业部统帅电视RGJQK320001前框1LE32PUV3,日日顺事业部RGJHK420001后壳1LE42PUV1,日日顺事业部统帅电视统帅电视RGJZB390001主板1LE39PUV3,日日顺事业部统帅电视RTL0118010052电源适配器 插墙适配器 国标 DC1LE19TF8,LE2日日顺事业部RTL111100099扬声器YDT310-06-4Ω/3W1LE19TF8,日日顺事业部统帅电视统帅电视RTL0119010587纸箱1LE19ZA1,日日顺事业部统帅电视RTL010*********主板后盖后盖 185F8 CV181L-G方1LE19TF8,日日顺事业部统帅电视RTL0113010508遥控板 RMT062-1(红绿)1LE19TF8,LE1日日顺事业部统帅电视RGJIRB46001IR板1LE46PUV1,日日顺事业部统帅电视7030-420L31-4U711101排钮1LE42KUH1,日日顺事业部统帅电视ZC4031Q390119说明书1LE32MUF3,日日顺事业部统帅电视ZC316Q365M001屏1LE37MUF1,日日顺事业部统帅电视EL020********线材组机器的12位、1L42A8A-A1统日日顺事业部统帅电视EP00040503700IR板1L26A8A-A1统日日顺事业部ME00000201056支架1L32A8A-A1统日日顺事业部统帅电视统帅电视MS020********螺丝机器的12位、30L32N1统帅下日日顺事业部统帅电视MS04013006500螺丝机器的12位、30L42N1统帅下日日顺事业部PC00300020542前壳UV黑1L26A8A-A1统日日顺事业部统帅电视统帅电视941-0617-15205G电源板机器的12位、1LC32UT7,LC3日日顺事业部统帅电视941-1613-19L01G遥控接收板组件1LE42UL3,LE4日日顺事业部统帅电视RGJDYB46001电源板1LE46PUV1,日日顺事业部统帅电视941-0624-17119G电源板1LE23T6,日日顺事业部统帅电视702-474B-52003G后壳黑色1L46A8A-A(N)日日顺事业部统帅电视721-47H2-12LEDG leader中文纸箱1L46A8A-A(N)日日顺事业部统帅电视742-470L-04003G LCD硬屏1L46A8A-A(N)日日顺事业部日日顺事业部统帅电视702-424B-60001G后壳黑色1LE42H86(N)统统帅电视715-0202-00324G底座立柱盖1LE32T6(N)统日日顺事业部统帅电视CM03000100104快速安装指南机器的12位、1L26A8A-A1统日日顺事业部统帅电视EL020********线材组机器的12位、1L42A8A-A1统日日顺事业部统帅电视EP00040207400KEY板机器的12位、1L32N1统帅下日日顺事业部统帅电视ME00500800195底座底板机器的12位、1L32N1统帅下日日顺事业部统帅电视PC00300010952前壳UV黑机器的12位、1L32N1统帅下日日顺事业部PC00600010530按键黑色1L42A8A-A1统日日顺事业部统帅电视统帅电视RGJZX460001纸箱1LE46PUV1,日日顺事业部RGJDYB39001电源板1LE39PUV3,日日顺事业部统帅电视统帅电视RTSWC447YA02031包装箱1LE42UT8,日日顺事业部统帅电视941-0606-42215G电源板套件1LC42UT7,LC4日日顺事业部统帅电视RGJZX320001纸箱1LE32PUV3,日日顺事业部统帅电视RGJDYB32001电源板1LE32PUV3,日日顺事业部统帅电视941-11T8-68901G主板1LE42H86统帅日日顺事业部统帅电视715-0201-00426G透明PC立柱1LE42H86统帅日日顺事业部统帅电视715-3201-U7422G喇叭网1L42N1,L42N1日日顺事业部统帅电视715-0202-4B421G立柱盖1LE42H86统帅日日顺事业部统帅电视724-32H2-11LEDG leader中文说明书1LE32T6(N)统日日顺事业部统帅电视CP01100000200纸箱标贴1L42A8A-A1统日日顺事业部统帅电视白色机器的12位、1L42N1统帅下日日顺事业部CP01500000703珍珠棉保护物统帅电视EL020********线材组机器的12位、1L32A8A-A1统日日顺事业部统帅电视ME00000202451支架1L32A8A-A1统日日顺事业部统帅电视CP01700000555纸箱1L26A8A-A1统日日顺事业部统帅电视RTL0113070936主板组件 T.NT72557.A1B(亚洲版1LE39LXZ1,LE日日顺事业部RTL011538002955液晶显示屏01LE55TS3,LE5日日顺事业部统帅电视统帅电视9011-11T92A-173F4031主板1LE42KUH1,日日顺事业部EP00041100603POWER板1L26A8A-A1统日日顺事业部统帅电视统帅电视MS020********螺丝机器的12位、30L32N1统帅下日日顺事业部日日顺事业部统帅电视724-Q0B0-12LEDG leader说明书1LE42H86(N)统统帅电视CP00100000201PE袋白色机器的12位、5L26A8A-A1统日日顺事业部统帅电视CP01700000557纸箱机器的12位、1L42N1统帅下日日顺事业部ME00601800259屏框架1L26A8A-A1统日日顺事业部统帅电视统帅电视PC00100010568后壳黑色1L26A8A-A1统日日顺事业部PC00500010914底座UV黑机器的12位、1L42N1统帅下日日顺事业部统帅电视统帅电视742-230L-02006G LED背光屏(16:9)序列号为DC11LE24T6统帅下日日顺事业部统帅电视941-1605-32T01G遥控接收板组件机器的12位、1L26N1统帅下日日顺事业部941-1619-L1501G遥控接收板组件1LE42H86(N)统统帅电视日日顺事业部统帅电视773-0810-90001G音箱机器的12位、1L32N1统帅下日日顺事业部。

IT8282M中文脚位功能说明

脚位编号名称属性1VCORE_GD DI2VLDT_12AI3VDDA_25AI4VDIMM_STR AI5SB_PSON#DI6ACPI_S3DI9ATX_PSON#DIOD810RSTBTN#DI12VDIMM_STR_EN DOD813VCORE_EN DOD814VDDA_EN DOD815VLDT_EN DOD8 Table5-2.Pin(s) No.名称属性7ATX_PWRGD DI11CPU_PWRGD DOD16 Table5-2.Pin(s) No.名称属性8GND PWR165VSB PWR功能说明VCORE电源好。

高电平有效。

这个信号表明,此电源好信号来自CPU内核电压。

VLDT(1.2V)模拟输入。

VDDA(2.5V)模拟输入。

VDIMM DUAL STR(2.5V)模拟输入。

南桥PSON#信号。

低电平有效;此信号来自南桥或SUPER I/O 的PSON#,去控制ATX电源的开启和关闭。

A GPIO pin from S/B。

高电平有效。

此信号表明系统处于S3模式。

ATX Power PSON#。

低电平有效。

这个脚位的功能是开启和关闭ATX电源。

Reset Button input。

面板RESTER重启键的信号输入端。

VDIMM STR Enable。

高电平有效。

这个脚位的功能是VDIMM_STR(PWM)电压的使能。

外部需要接上拉电阻。

VCORE Enable。

高电平有效。

这个脚的功能是CPU_VCORE电压的使能。

外部需要接上拉电阻。

VDDA电压使能。

高电平有效。

这个脚位的功能是K8 CPU的VDDA电压的使能。

外部需要接上拉电阻。

VLDT电压使能。

高电平有效。

这个脚位的功能是VLDT电压的使能。

外部需要接上拉电阻。

功能说明ATX Power-good/GND。

高电平有效。

输入此信号表明ATX电源已经准备就绪。

CPU Power-good。

高电平有效。

输出此信号表明CPU Power-good已经准备就绪。

SV08中文资料

10 10 10 10 100 10 100 100 100 100 100 1000 100 100 100 100 1000

pF pF pF pF pF pF pF pF pF pF pF pF pF pF pF pF pF

/ 82 pF / 270 pF / 470 pF / 180 pF / 1200 pF / 560 pF / 2200 pF / 3900 pF / 6800 pF / 5600 pF / 8200 pF /0.015 µF / 820 pF / 1500 pF / 2700 pF / 6800 pF /0.012 µF

pF pF pF pF pF pF pF pF pF pF pF pF pF pF pF pFFra bibliotekX7R

100 pF / 1500 pF 100 pF / 5600 pF 1000 pF / 0.01 µF 100 pF / 3900 pF 1000 pF /0.027 µF 1000 pF /0.012 µF 1000 pF /0.047 µF 1000 pF /0.082 µF .01 µF / 0.12 µF .01 µF / 0.10 µF .01 µF / 0.18 µF .01 µF / 0.27 µF 1000 pF /0.012 µF 1000 pF /0.022 µF 1000 pF /0.033 µF .01 µF / 0.12 µF .01 µpF / 0.15 µF — 100 pF / 2700 pF 100 pF / 4700 pF 100 pF / 1800 pF 1000 pF /0.012 µF 100 pF / 6800 pF 1000 pF /0.027 µF 1000 pF /0.047 µF 1000 pF /0.068 µF 1000 pF /0.056 µF .01 µF / 0.10 µF .01 µF / 0.15 µF 100 pF / 6800 pF 1000 pF /0.015 µF 1000 pF /0.022 µF 1000 pF /0.068 µF 1000 pF /0.082 µF — — — — — pF / 1200 pF pF / 6800 pF pF /0.012 µF pF /0.018 µF pF /0.018 µF pF /0.027 µF pF /0.033 µF — — pF / 4700 pF pF /0.018 µF pF /0.027 µF

诺瓦科技LED显示屏联网播放器T2规格书

ii

Taurus 系列多媒体播放器 T2 规格书

目录

7.3.2 编码器 ..................................................................................................................................................... 15

1 安全说明..........................................................................................................................................1

1.1 存储和运输安全 ........................................................................................................................................... 1 1.2 安装和使用安全 ........................................................................................................................................... 1

是诺瓦科技的注册商标。

声明

欢迎您选用西安诺瓦电子科技有限公司(以下简称诺瓦科技)的产品,如果本文档为您了解和使用产品带 来帮助和便利,我们深感欣慰。我们在编写文档时力求精确可靠,随时可能对内容进行修改或变更,恕不 另行通知。如果您在使用中遇到任何问题,或者有好的建议,请按照文档提供的联系方式联系我们。对您 在使用中遇到的问题,我们会尽力给予支持,对您提出的建议,我们衷心感谢并会尽快评估采纳。

V302528S资料

Featuresn Built-in quartz with digital trimming for frequency tuning and temperature compensation facilities INTEL and MOTOROLA interface compatibility 15 ns typical access time at 5.0 Vtandby current at 3.0 V Integrated battery switch-overBattery voltage range, 2.0 4.0 V No busy stateNo external components required BCD format12 or 24 hour data formatTime to 1/100 of a secondTo external time reference synchronisation 50 Hz or nearest s/min synchronisation Tri-state bus capability when power fail (PFI = 0)User RAMO Temperature range - 40 to +85C Package SO28n n n 1.2 m A typical s n Wide supply voltage range, 2.0 £ V £ 5.5 V DD n n £ V £ BAT n n n n Frequency measurements n Time set lock moden Week number calculation n Clock counts up to 99 years n Leap year correction n n Output programmable interruptsn Alarm interrupt, programmable up to one monthn Timer interrupt, programmable up to 24 hoursn n n n Power fail input PFIn Power fail output or Reset output PFOn n n n DescriptionThe V3025 is a low power CMOS real time clock with anintegrated battery switch-over. The standby current is typically 2.5 m A and the access time is 50 ns. The interface is a multiplexed address and data 8 bits bus. Multiplexing of address and data is handled by the input line A/D. There are no busy flags in the V3025, internal time update cycles are invisible to the user’s software. Time data can be read from the V3025 in 12 or 24 hour data formats. An external signal puts the V3025 in standby mode. Even in standby, the V3025 pulls the IRQ pin active low on an internal alarm interrupt. Calendar functions include leap year correction and week number calculation. The V3025 can be synchronized to an external 50 Hz signal or to the nearest second or minute. The integrated battery switch-over supply the real time clock part by as long as is higher than . When decreases under , the output PFO comes active and the real clock is supplied by the battery or the supercap.V V DD DD V V V BAT DD BAT Very Low Power 8-Bit 32 kHz RTC Module with Digital Trimming, User RAM and Battery Switch-overApplicationsn Industrial controllersAlarm systems with periodic wake up PABX and telephone systems Point of sale terminals Automotive electronics n n n n nPersonal ComputersPin AssignmentTypical Operating ConfigurationV3025EM MICROELECTRONIC-MARIN SA1)With PFO = 0 (V ) all I/O pads can be tri-state, tested.SS With PFO = 1 (V ), CS = 1 (V ) and all other I/O pads fixed to V or to V : same standby current, not tested.SUP DD SUP SS 2)3)4)All other inputs to V and all outputs open.At a given temperature.See Fig. 5DD Stresses above these listed maximum ratings may cause permanent damage to the device. Exposure beyond specified operating conditions may affect device reliability or cause malfunction.Absolute Maximum RatingsTable 1ParameterMaximum voltage at V and V DD BAT Max. voltage at remaining pins Min. voltage on all pinsMaximum storage temperature Minimum storage temperature Maximum electrostatic discharge to MIL-STD-883C method 3015Maximum soldering conditions Shock resistanceV SUPmax V SUP V minT STOmin T STOmax V Smax T SmaxV + 7.0V SS V + 0.3V DD V - 0.3V SS 0-55C O +125C 1000V O250C x 10s 5000 g.10.3ms,/sine2Symbol ConditionsHandling ProceduresThis device has built-in protection against high static voltages or electric fields; however, anti-static precautions must be taken as for any other CMOS component. Unless otherwise specified, proper operation can only occur when all terminal voltages are kept within the supply voltage range. Unused inputs must always be tied to a defined logic voltage level.Operating ConditionsT A V DD V BAT -40+85OC ParameterSymbol Min.Typ.Max.UnitsOperating temperature Main supply votage Battery supply voltage 2.05.0VV/m s nF 5.56100V SUP dv/dtLogic supply voltage Supply voltage dv/dt (power-up & down)Decoupling capacitor2 5.5V V 42Table 2Electrical CharacteristicsOV = 5.0V ± 10%, V = 3 V , V = 0 V , T = -40 to +85C, unless otherwise specifiedTable 3V30251)t starts from RD (DS) or CS, whichever activates lastACC Typically , t = 5 + 0.9 C in ns; where C (external parasitic capacitance) is in pF ACC EXT EXT 2)t starts from RD (DS) or CS, whichever deactivates first DF 3)t ends at WR (R/W) or CS, whichever deactivates first DW 4)t starts from WR (R/W) or CS, whichever deactivates first DH 5)A/D must come before a CS and RD or a CS and WR combination. The user has to guarantee this.Timing Characteristics0V = 5.0 ± 10%, V = 0 V , V = 0 V , and T = - 40 to +85C DD BAT SS ATable 5Typical V Current vs. T emperatureDDSwitch-over Electrical Characteristics0T = - 40 to 85C, inputs to V , outputs not connected, unless otherwise specified A DDTable 4V3025Typical Frequency on IRQD F F 0ppm0T[C]A Address 10 hex = 00 hex250200150100500-50 -30 -10 10 30 50 70 90Fig. 5Typical V Current vs. T emperatureBATModule CharacteristicFig. 6=the ratio of the change in frequency to the nominal value expressed in ppm (It can be thought of as the frequency deviation at any temperature.)o =the temperature of interest in C O =the turnover temperature (25 ±5C)To determine the clock error (accuracy) at a given temperature, addO the frequency tolerance at 25C to the value obtained from the formula above.[ppm]F r e q u e n c y r a t i o [pp m ]-100-200-300-400T - 100O T - 50O OT emperature [C]O T [C]T OT +50 O T +100O D F F 0D F/F O TT Om i n .m a x .D F F 0ppm 2O C= - 0.0382(T - T ) ±10%ORead Timing for Intel (RD and WR pulse) and Motorola (DS or RD pin tied to CS, and R/W)Timing WaveformsTypical V Switch Resistance vs. T emperatureDDTypical Battery Switch Resistance vs. T emperatureIntel Interface Write TimingWriteReadMotorola Interface Motorola WriteWriteReadGeneral Block DiagramFunctional DescriptionPower Supply, Data Retention and StandbyThe V3025 is put in standby mode by activating the PFI input. When pulled logic low, PFI will disable the input lines, and immediately take to high impedance the lines AD 0-7. Input states must be under control whenever PFI is deactivated. If no specific power fail signal can be provided, PFI can be tied to the system RESET. Even in standby the interrupt request pin IRQ will pull to ground upon an unmasked alarm interrupt occurring.Switch-overThe switch-over supplies the core of the RTC. The I/O pads are supplied by V , except for IRQ and SYNC. The DD SYNC input is internally pulled-up to V , IRQ can be externally pulled-up OUT between 2 and 5.5 V . The switch-over circuitry works in recovery mode. During switching, both transistors (V to V and V DD OUT BAT to V ) are ON. This is the guarantee that the RTC is always OUT supplied. The power fail signal becomes active (PFO = 0) when V < V (see Table 4).DD BAT InitialisationWhen power is first applied to the V3025 all registers have a random value.To initialise the V3025, software must first write a 1 to the initialisation bit (addr. 2 bit 4) and then a 0. This sets the Frequency Tuning bit and clears all other status bits.The time and date parameters should then be loaded into the RAM (addr. 20 to 28 hex) and then transferred to the reserved clock area using the clock command followed by a write.The digital trimming register must then be initialised by writing 210 (D2hex) to it, if Frequency Tuning is not required. After having written a value to the digital trimming register the frequency tuning mode bit can be cleared.RAM ConfigurationThe RAM area of the V3025 has a reserved clock and time area, a data space, user RAM and an address command space (see Table 10 or Fig. 10). The reserved clock and timer area is not directly accessible to the user, it is used for internal time keeping and contains the current time and date plus the timer parameters.Data SpaceAll locations in the data space are Read/Write. The data space is directly accessible to the user and is divided into five areas :Status Registers - three registers used for status and control data for the device (see Table 7,8 and 9).Reserved bits must be set to 0.Digital Trimming Register - a special function described under “Frequency Tuning”.Time and Date Registers - 9 time and date locations which are loaded with, either the current time and date parameters from the reserved clock area or the time and date parameters to be transferred to the reserved clock area.Alarm Registers - 5 locations used for setting the alarm parameters.Timer Registers - 4 locations which are loaded with either the timer parameters from the reserved timer area or the timer parameters to be transferred to the reserved timer area.User RAMThe V3025 has 16 bytes of general purpose RAM available for the users applications. This RAM block is located at addresses 50 to 5F hex and is maintained even in the standby mode (PFI active). The commands, or the time set lock bit, have no effect on the user RAM block. Reading or writing to the user RAM is similar to reading or writing to any system RAM address.Pin DescriptionSO28 PackageTable 61)The MSB (bit 7) of the hours byte (addr. 23 hex for the clock and 33 hex for the alarm) are used as AM/PM indicators in the 12 hour time data format and reading of the hours byte must be preceded by masking of the AM / PM bit. A setStatus WordsTable 7Status 0 - Address 00 Hex Read / Write bitsfrequency tuning mode pulse enable / disable alarm enable / disable timer enable / disable1)24 hour / 12 hour time set lock test bit 0test bit 10 - disabled / 24 hour 1 - enabled / 12 hour 7 6 5 4 3 2 1 0Table 8Status 1 - Address 01 Hex Read / Write bitspulse mask alarm mask timer mask reserved pulse flag alarm flag timer flag reserved0 - masked / no event 1 - unmasked / event 7 6 5 4 3 2 1 0Table 9Status 2 - Address 02 Hex Read / Write bitspulse every 10 ms pulse every 100 ms pulse every second pulse every minute initialisation bit SYNC 50 Hz SYNC second SYNC minute0 - disabled 1 - enabled 7 6 5 4 3 2 1 0Address Command SpaceThis space contains the three commands used for carrying out the transfers between the Time and Date Register and / or the Timer Registers and the reserved clock and timer area.RAM MapAM/PM bit indicates PM. In the 24 hour time data format the bit will always be zero.2)The alarm hours, addr. 33 hex, must always be rewritten after a change between 12 and 24 hour modes.CommunicationData transfer is in 8 bit parallel form. All time data is in packed BCD format with tens data on lines AD 7 - 4 and units on lines AD 3 - 0. To access information within the RAM (see Fig. 10) first write the RAM address, then read or write from or to this location. Fig. 11 shows the two steps needed.The lines AD 0 - 7 will be treated as an address when pin A/D is low, and as data when /D is high. Pin /D must not change state during any single read or write access. One line of the address bus (e.g. A0) can be used to implement the /D signal (see "Typical Operating Configuration", Fig. 1). Until a new address is written, data accesses (/D high) will always be to the same RAM munication SequenceA A A A Access ConsiderationsThe communication sequence shown in Fig. 11 is re-entrant. When the address is written to the V3025 (ie. first step of the communication sequence) it is stored in an internal address latch. Software can read the internal address latch at any time by holding the A/D line low during a read from the V3025. So, for example, an interrupt routine can read the address latch and push it onto a stack, popping it when finished to restore the V3025.NB. Alarm and timer interrupt routines can reprogram the alarm and timer without it being necessary to read or reprogram the clock.CommandsThe commands allow software to transfer the clock and timer parameters in a sequence (eg. seconds, minutes, hours, etc.) without any danger of an internal time update with carry over corrupting the data. They also avoid delaying internal time updates while using the V3025, as updates occuring in the reserved clock and timer area are invisible to software. Software writes or reads parameters to or from the RAM only.There are three commands that occupy the command addressspace in the RAM. The function of these commands is to transfer data from the reserved clock and timer area to the RAM or to transfer data in the opposite direction, from the RAM to the reserved clock and timer area.The commands take place in two steps as do all other communications. The command address is sent with /D low. This is followed by either a read (RD) or a write (WR), with A/D high, to determine the direction of the transfer. If the second step is a read then the data is transferred from the reserved clock and timer area to the RAM and if the second step is a write then the data that has already been loaded into the RAM clock and/or timer locations is transferred to the reserved clock and/or timer area.Clock and CalendarThe time and date locations in RAM (see Table 10) provide access to the 1/100 seconds, seconds, minutes, hours, date, month, year, week day , and week number. These parameters have the ranges indicated in Table 10. The V3025 may be programmed for 12 or 24 hour time format (see section "12/24 Data Format"). If a parameter is found to be out of range, it will be cleared when the units value on its being next incremented is equal to or greater than 9 eg. B2 will be set to 00 after the units have incremented to 9 (ie. B9 to 00). The device incorporates leap year correction and week number calculation at the beginning of a year. If the first day of the year is day 05, 06 or 07 of the week, then it is given a zero week number, otherwise it becomes week one. Week days are numbered from 1 to 7 with Monday as day 1.Reading of the current time and date must be preceded by a clock command. The time and date from the last clock command is held unchanged in RAM.When transferring data to the reserved clock and timer area remember to clear the time set lock bit first.TimerThe timer can be used either for counting elapsed time, or for giving an interrupt (IRQ) on being incremented from 23:59:59:99 to 00:00:00:00. The timer counts up with a resolution of 1/100 second in the timer reserved areas. The timer enable / disable bit (addr. 00 hex, bit 3) must be set by software to allow the timer to be incremented. The timer is incremented in the reserved timer area, every internal time update (10 ms). The timer flag (addr. 01 hex, bit 6) is set when the timer rolls over from 23:59:59:99 to 00:00:00:00 and the becomes active if the timer mask bit (addr. 01, bit 2) is set. The will remain active until software acknowledges the interrupt by clearing the timer flag. The timer is incremented in the standby mode, however it will not cause to become active until power (V ) has been restored.DD Note: The user should ensure that a time lapse of at least 60 microseconds exists between the falling edge of the and the clearing of the timer flag.A IRQ IRQ IRQ IRQReading the ClockNote : Commands are only valid as commands when the A/D line is low. Writing F2 hex with the A/D line high, as in the last box of Fig.11, serves only to activate the V3025 write pin which determines the direction of transfer.Setting the Timer ( Time Set Lock Bit = 0)AlarmAn alarm date and time may be preset in RAM addresses 30 to 34 hex. The alarm function can be activated by setting the alarm enable / disable bit (addr. 00 hex, bit 2). Once enabled the preset alarm time and date are compared, every internal time update cycle (10 ms), with the clock parameters in the reserved clock area. When the clock parameters equal the alarm parameters the alarm flag (addr. 01 hex, bit 5) is set. If the alarm mask bit (addr. 01 hex, bit 1) is set, the IRQ pin goes active. The alarm flag indicates to software the source of the interrupt. IRQ will remain active until software acknowledges the interrupt by clearing the alarm flag. If the alarm is enabled, and an alarm address set to FF hex, this parameter is not compared with the associated clock parameter. Thus it is possible to achieve a repeat feature where an alarm occurs every programmed number of seconds, or seconds and minutes, or seconds, minutes and hours. The V3025 pulls the open drain IRQ line active low during standby when an alarm interrupt occurs.If the 12/24 hour mode is changed then the alarm hours must be re-initialised.Note: The user should ensure that a time lapse of at least 60 microseconds exists between the falling edge of the IRQ and the clearing of the alarm flag.IRQThe IRQ output is used by 4 of the V3025's features. These are:1)Pulse, to provide periodic interrupts to the microprocessorat preprogrammed intervals;2)Alarm to provide an interrupt to the microprocessor at apreprogrammed time and date;3)Timer, to provide an interrupt to the microprocessor whenthe timer rolls over from 23:59:59:99 to 00:00:00:00; and 4)Frequency trimming (see section "Frequency Trimming").The first 3 features listed are similar in the way they provide interrupts to the microprocessor. Each of the 3 has an enable / disable bit, a flag bit, and an interrupt mask bit. The enable / disable bit allows software to select a feature or not. A set flag bit indicates that an enable feature has reached its interrupt condition. Software must clear the flag bit. The interrupt mask bit allows or disallows the IRQ output to become active when the flag bit is set. The output becomes active whenever any interrupt flag is set which also has its mask bit set. For all sources of maskable interrupts within the V3025, the output will remain active until software clears the interrupt flag. The output is the logical OR of all the unmasked interrupt flags. The output is open drain so an external pullup to V is needed. DD In standby (PF active) the output will be active if the alarm mask bit (addr. 01 hex, bit 1) is set and the alarm flag is also set. The timer or the pulse feature cannot cause the output to become active while in standby.SynchronizationThere are 3 ways to synchronize the V3025. It can be synchronized to 50 Hz, the nearest second, or the nearest minute. Synchronization mode is selected by setting one of theIRQ IRQ IRQ IRQ IRQ IRQ bits 5 to 7 at addr. 02 hex, in accordance with Table 9. If more than one bit is set then all the synchronization bits are disabled. If the SYNC input is set low for longer than 200 m s, while in the synchronization mode, the clock will synchronize to the falling edge of the signal. Synchronization to the nearest second implies that the 1/100 seconds are cleared to zero and if the contents were > 50, the seconds register is incremented. Synchronization to the nearest minute implies that the seconds are cleared to zero and if the contents were > 30, the minutes register is incremented. Fractions of seconds are cleared.PulseThere are 4 programmable pulse frequencies available on the V3025, these are every 10 ms, 100 ms, second or minute. The pulse feature is activated by setting the pulse enable / disable bit at address 00, bit 1. The pulse frequency is selected by setting one of the bits 0 to 3 at address 02 hex (see Table 9). If more than one of the pulse bits are set then the feature is disabled. At the selected interval the pulse flag bit (addr. 01 hex, bit 4) is set. If the pulse mask bit (addr. 01 hex, bit 0) is set then the pin goes active. The pulse flag indicates to software the source of the interrupt. will remain active until software acknowledges the interrupt by clearing the pulse flag. The pulse feature is disabled while in standby. Upon power restoration the pulse feature is enabled if enabled prior to standby. See also the section "Frequency T uning".Note: The user should ensure that a time lapse of at least 60 microseconds exists between the falling edge of the and the clearing of the pulse flag.Time Set LockThe time set lock control bit is located at address 00 hex, bit 5 (see Table 7). When set by software, this bit disables any transfer from the RAM to the reserved clock and timer area as well as inhibiting any write to the digital trimming register at address 10 hex. When the time set lock bit is set the following transfer operations are disabled:The clock command followed by write,the timer command followed by write,the clock and timer command followed by write, and writing to the digital trimming register.A set bit prevents unauthorized overwriting of the reserved clock and timer area. Reading of the reserved clock and timer area, using the commands, is not affected by the time set lock bit. Clearing the time set lock bit by software will re-enable the above listed commands. On initialisation the time set lock bit is cleared. The time set lock bit does not affect the user RAM (addr. 50 to 5F hex).Frequency TuningThe V3025 offers a key feature called "Digital Trimming", whichis used for the clock accuracy adjustment. Unlike the traditional capacitor trimming method, which tunes the crystal oscillator, the digital trimming acts on the divider chain, allowing the clock adjustment by software. The oscillator frequency itself is not affected.IRQ IRQ IRQThe Principle of Digital TrimmingWith the digital trimming disabled (i.e. digital trimming register set to 00 hex), the oscillator and the first stages of the divider chain will run slightly too fast (typ. 210 ppm: ppm = parts per million), and will generate a 100 Hz signal with a frequency of typically 100.021 Hz. T o correct this frequency, the digital trimming logic will inhibit every 31 seconds, a number of clock pulses, as set in the digital trimming register. Since the duration of 31 seconds corresponds to 1'015'808 oscillator cycles, the digital trimming has a resolution of 0.984 ppm. In other words every increment by1 of the digital trimming value will slow down the clock by 0.984 ppm, which permits the accuray of ±0.5 ppm to be reached. Note that a 1 ppm error will result in a 1 second difference after 11.5 days, or a 1 minute difference after 694 days! The trimming range of the V3025 is from 0 to 251 ppm. The 251 ppm correction is obtained by writing 255 (FFhex) into the digital trimming register.How to Determine the Digital Trimming ValueThe value to write into the digital trimming register has to be determined by the following procedure:1.Initialise the V3025 by writing a 1 and then a 0 into the"Initialisation Bit" of the status register 2 (addr. 02 hex, bit 4). This activates the frequency tuning mode in status register 0 (addr. 00 hex, bit 1) and clears the other status bits.2.3.4.5.6.7.209.97 ms at room temperature. The frequency error is:(210 - 209.97) / 210 x 1E + 06 = 142.857 ppm.The value for the digital trimming register is:142.857 / 0.984 = 145.18, rounded to 145 ppm (91 hex).Time Correction with Change of T emperatureoIf the mean temperature on site is known to be 45 C, the frequency error determined at room temperature has to be modified, using the graphs or the equation on Fig. 6.2D f/f = - 0.038 x (45 - 25) = 15.2 ppm 0The trimming value for 45 C will be(142.857 ppm - 15.2 ppm) / 0.984 = 129.73, rounded to 130 (82 hex).12 / 24 Hour Data FormatThe V3025 can run in 12 hour or 24 hour data format. On initialisation the 12/24 hour bit ad addr. 00 bit 4 is cleared putting the V3025 in 24 hour data format. If the 12 hour data format is required then bit 4 at addr. 00 must be set. In the 12 hour data format the AM/PM indicator is the MSB of the hours register addr. 23 bit 7. A set bit indicates PM. When reading the hours in the 12 hour data format software should mask the MSB of the hours register. In the 24 hour data format the MSB is always zero.The internal clock registers change automatically between 12 and 24 hour mode when the 24/12 hour bit is changed. The alarm hours however must be rewritten.T estFrom the various test features added to the V 3025 some may be activated by the user. T able 7 shows the test bits. T able 11 shows the three available modes and how they may be activated.The first accelerates the incrementing of the parameters in the reserved clock and timer area by 32.The second causes all clock and timer parameters, in the reserved clock and timer area, to be incremented in parallel at 100 Hz with no carry over, ie. independently of each other .The third test mode combines the previous two resulting in parallel incrementing at 3.2 kHz.While test bit 1 is set (addr. 00 hex, bit 7) the digital trimming action is disabled and no pulses are removed from the divider chain. Test bit 0 (addr. 00 hex, bit 6) can be combined with digital trimming (see section "Frequency Tuning"). T o leave test, the test bits (addr. 00 hex, bits 6 and 7) must be cleared by software. Test corrupts the clock and timer parameters and so all parameters should be re-initialised after a test session. Table 11Normal Operation Acceleration by 32Parallel increment of all clock and timer parameters at 100 Hz with no carry over; dependent on the status of bit 3 at address 00 hexParallel increment of all clock and timer parameters at 3.2 kHz with no carry over; dependent on the status of bit 3 at address 00 hex01010011Addr.00hex bit 7Addr.00hex bit 6FunctionTest ModesProcess Application-The formula in Fig. 5 is used by software to continually update the digital trimming register and so compensate the V 3025 for the ambient temperature.-The timer is used to measure the duration the valve is on.-The alarm feature is used to turn the controller power on and off at the time programmed by software. The V3025 pulls IRQ active low on an alarm even in standby and thus can control the power on/off switch for the controller.Typical Operating ConfigurationV 3025 Interfaced with Motorola CPU (DS or RD pin tied to CS, and R/W)V 3025 Interfaced with Intel CPU (RD and WR pulse)Typical ApplicationsOrdering InformationThe V3025 is available in the following package:SO28 pin plastic packageV3025 28SWhen ordering, please specify the complete part number and package.EM Microelectronic-Marin SA cannot assume responsibility for use of any circuitry described other than circuitry entirely embodied in an EM Microelectronic-Marin SA product. EM Microelectronic-Marin SA reserves the right to change the circuitry and specifications without notice at any time. You are strongly urged to ensure that the information given has not been superseded by a more up-to-dateÓ 2000 EM Microelectronic-Marin SA, 10/00, Rev. C/322。

MIW3025中文资料