ADD-55中文资料

AMZ-55中文资料

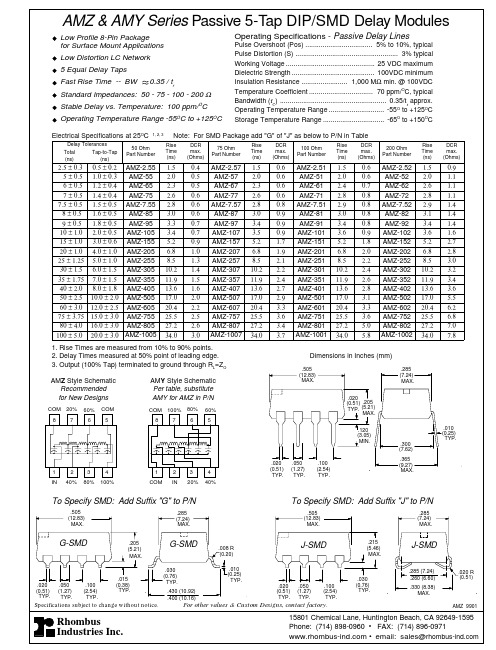

15801 Chemical Lane, Huntington Beach, CA 92649-1595Phone: (714) 898-0960 • FAX: (714) 896-0971 • email: sales@RhombusIndustries Inc.For other values & Custom Designs, contact factory.Specifications subject to change without notice.AMZ 9901AMZ & AMY Series Passive 5-T ap DIP/SMD Delay Modules1. Rise Times are measured from 10% to 90% points.2. Delay Times measured at 50% point of leading edge.3. Output (100% Tap) terminated to ground through R L =Z O Low Profile 8-Pin Package for Surface Mount Applications Low Distortion LC Network 5 Equal Delay TapsFast Rise Time -- BW 0.35 / t rStandard Impedances: 50 - 75 - 100 - 200 ΩStable Delay vs. Temperature: 100 ppm/O C Operating Temperature Range -55O C to +125O CAM Y Style Schematic Per table, substitute AMY for AMZ in P/N100%81IN380%20%560%640%7COM42COM 100%81IN320%40%560%680%7COM 42COM AM Z Style Schematic Recommended for New DesignsDimensions in Inches (mm).300(7.62) .285(7.24) MAX..010(0.25) TYP..365(9.27) MAX..505(12.83) MAX..120 MIN.(3.05) MAX..205(5.21).100(2.54) TYP..050(1.27) TYP. .020(0.51) TYP. .020(0.51)TYP.J-SMD .330 (8.38) MAX..020 R (0.51).285(7.24) MAX..285 (7.24).260 (6.60) MAX..215(5.46) .030(0.76) TYP..505(12.83) MAX..100(2.54) TYP..020(0.51) TYP..050(1.27) TYP.To Specify SMD: Add Suffix "J" to P/NG-SMDG-SMD.400 (10.16).430 (10.92) .285(7.24) MAX..030(0.76) TYP. .010(0.25) TYP..008 R (0.20).505(12.83) MAX..205(5.21) MAX..015(0.38) TYP..020(0.51) TYP. .050(1.27) TYP. .100(2.54) TYP.To Specify SMD: Add Suffix "G" to P/NJ-SMDDelay Tolerances 50 Ohm Part NumberRise Time (ns)DCR max.(Ohms)75 Ohm Part NumberRise Time (ns)DCR max.(Ohms)100 Ohm Part NumberRise Time (ns)DCR max.(Ohms)200 Ohm Part NumberRise Time (ns)DCR max.(Ohms)Total (ns)Tap-to-Tap(ns)2.5 ± 0.30.5 ± 0.2AMZ-2.551.50.4AMZ-2.57 1.50.6AMZ-2.51 1.50.6AMZ-2.52 1.50.9 5 ± 0.5 1.0 ± 0.3AMZ-55 2.00.5AMZ-57 2.00.6AMZ-51 2.00.6AMZ-52 2.0 1.1 6 ± 0.5 1.2 ± 0.4AMZ-65 2.30.5AMZ-67 2.30.6AMZ-61 2.40.7AMZ-62 2.6 1.1 7 ± 0.5 1.4 ± 0.4AMZ-75 2.60.6AMZ-77 2.60.6AMZ-71 2.80.8AMZ-72 2.8 1.1 7.5 ± 0.5 1.5 ± 0.5AMZ-7.552.80.6AMZ-7.57 2.80.8AMZ-7.51 2.90.8AMZ-7.52 2.9 1.4 8 ± 0.5 1.6 ± 0.5AMZ-85 3.00.6AMZ-87 3.00.9AMZ-81 3.00.8AMZ-82 3.1 1.4 9 ± 0.5 1.8 ± 0.5AMZ-95 3.30.7AMZ-97 3.40.9AMZ-91 3.40.8AMZ-92 3.4 1.4 10 ± 1.0 2.0 ± 0.5AMZ-105 3.40.7AMZ-107 3.50.9AMZ-101 3.60.9AMZ-102 3.6 1.6 15 ± 1.0 3.0 ± 0.6AMZ-155 5.20.9AMZ-157 5.2 1.7AMZ-151 5.2 1.8AMZ-152 5.2 2.7 20 ± 1.0 4.0 ± 1.0AMZ-205 6.8 1.0AMZ-207 6.8 1.9AMZ-201 6.8 2.0AMZ-202 6.8 2.8 25 ± 1.25 5.0 ± 1.0AMZ-2558.5 1.3AMZ-2578.5 2.1AMZ-2518.5 2.2AMZ-2528.5 3.0 30 ± 1.5 6.0 ± 1.5AMZ-30510.2 1.4AMZ-30710.2 2.2AMZ-30110.2 2.4AMZ-30210.2 3.2 35 ± 1.757.0 ± 1.5AMZ-35511.9 1.5AMZ-35711.9 2.4AMZ-35111.9 2.6AMZ-35211.9 3.4 40 ± 2.08.0 ± 1.8AMZ-40513.6 1.6AMZ-40713.6 2.7AMZ-40113.6 2.8AMZ-40213.6 3.6 50 ± 2.510.0 ± 2.0AMZ-50517.0 2.0AMZ-50717.0 2.9AMZ-50117.0 3.1AMZ-50217.0 5.5 60 ± 3.012.0 ± 2.5AMZ-60520.4 2.2AMZ-60720.4 3.3AMZ-60120.4 3.3AMZ-60220.4 6.2 75 ± 3.7515.0 ± 3.0AMZ-75525.5 2.5AMZ-75725.5 3.6AMZ-75125.5 3.6AMZ-75225.5 6.8 80 ± 4.016.0 ± 3.0AMZ-80527.2 2.6AMZ-80727.2 3.4AMZ-80127.2 5.0AMZ-80227.27.0100 ± 5.020.0 ± 3.0AMZ-100534.0 3.0AMZ-100734.0 3.7AMZ-100134.0 5.8AMZ-100234.07.8Electrical Specifications at 25O C 1, 2, 3 Note: For SMD Package add "G" of "J" as below to P/N in TableOperating Specifications - Passive Delay LinesPulse Overshoot (Pos)................................... 5% to 10%, typical Pulse Distortion (S)..................................................... 3% typical Working Voltage.............................................. 25 VDC maximum Dielectric Strength........................................... 100VDC minimum Insulation Resistance ........................ 1,000 M Ω min. @ 100VDC Temperature Coefficient................................. 70 ppm/O C, typical Bandwidth (f C )....................................................... 0.35/t r approx.Operating Temperature Range............................. -55O to +125O C Storage Temperature Range................................ -65O to +150O C元器件交易网。

EMVY6R3ADA470ME55G中文资料(Nippon Chemi-Con)中文数据手册「EasyDatasheet - 矽搜」

请参考“产品代码指南(表面贴装型)”

◆标记

D55 to JA0 EX) 6.3V100µF

7hY

100 6.3V

KE0 to MN0

EX) 16V1,000µF

0V MVY

1000 16V

(1/2)

芯片中文手册,看全文,戳

表面安装铝电解电容器

1.8

95 EMVY6R3ADA330ME55G

47 E55

1.8

95 EMVY6R3ADA470ME55G

100 F55

1.0

140 EMVY6R3ADA101MF55G

220 F55

1.0

140 EMVY6R3ADA221MF55G

330 F80

0.34

280 EMVY6R3ADA331MF80G

≦The initial specified value

≦The initial specified value

Shelf Life

The following specificationsshall be satisfied when the capacitorsare restored to 20℃ after exposing them for 1,000 hoursat 105℃ without

Lower Z MVE

◆技术指标

Items

特点

Category Temperature Range

-55 to +105℃ (6.3 to 63V dc ) -40 to +105℃ (80 & 100V dc )

Rated Voltage Range 6.3 to 100V dc

EN1T11中文资料

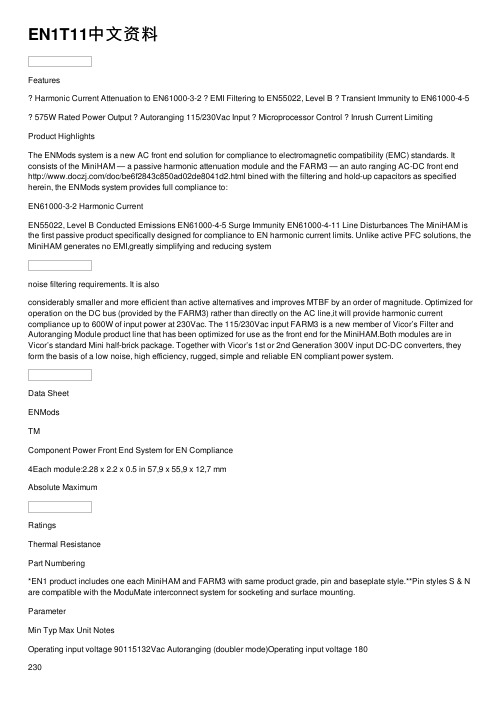

EN1T11中⽂资料FeaturesHarmonic Current Attenuation to EN61000-3-2 EMI Filtering to EN55022, Level B Transient Immunity to EN61000-4-5 575W Rated Power Output Autoranging 115/230Vac Input Microprocessor Control Inrush Current LimitingProduct HighlightsThe ENMods system is a new AC front end solution for compliance to electromagnetic compatibility (EMC) standards. It consists of the MiniHAM — a passive harmonic attenuation module and the FARM3 — an auto ranging AC-DC front end /doc/be6f2843c850ad02de8041d2.html bined with the filtering and hold-up capacitors as specified herein, the ENMods system provides full compliance to:EN61000-3-2 Harmonic CurrentEN55022, Level B Conducted Emissions EN61000-4-5 Surge Immunity EN61000-4-11 Line Disturbances The MiniHAM is the first passive product specifically designed for compliance to EN harmonic current limits. Unlike active PFC solutions, the MiniHAM generates no EMI,greatly simplifying and reducing systemnoise filtering requirements. It is alsoconsiderably smaller and more efficient than active alternatives and improves MTBF by an order of magnitude. Optimized for operation on the DC bus (provided by the FARM3) rather than directly on the AC line,it will provide harmonic current compliance up to 600W of input power at 230Vac. The 115/230Vac input FARM3 is a new member of Vicor’s Filter and Autoranging Module product line that has been optimized for use as the front end for the MiniHAM.Both modules are in Vicor’s standard Mini half-brick package. Together with Vicor’s 1st or 2nd Generation 300V input DC-DC converters, they form the basis of a low noise, high efficiency, rugged, simple and reliable EN compliant power system.Data SheetENModsTMComponent Power Front End System for EN Compliance4Each module:2.28 x 2.2 x 0.5 in 57,9 x 55,9 x 12,7 mmAbsolute MaximumRatingsThermal ResistancePart Numbering*EN1 product includes one each MiniHAM and FARM3 with same product grade, pin and baseplate style.**Pin styles S & N are compatible with the ModuMate interconnect system for socketing and surface mounting.ParameterMin Typ Max Unit NotesOperating input voltage 90115132Vac Autoranging (doubler mode)Operating input voltage 180230264Vac Autoranging (bridge mode)Input undervoltage 90Vac No damageAC line frequency 4763HzC-,T-, H- and M-Grade Power factor 0.680.72Typical line Inrush current 30Amps 264Vac line voltage Efficiency 9496%Full loadAC Bus OK (BOK)Low state resistance 15?To negative output - Bus normal Low state current 50mA Bus normalHigh state voltage 14.815.015.2Vdc Bus abnormal, 27k internal pull up to 15Vdc (see Figure12)BOK true threshold 235240245Vdc Output Bus voltage BOK false threshold 200205210VdcOutput Bus voltageModule Enable (EN)Low state resistance 15?To negative output - Converters disabledLow state current 50mA High state voltage 14.815.015.2Vdc 150k internal pull up to 15Vdc (see Figure 11)Enable threshold 235240Vdc Output bus voltage Disable threshold 185190195Vdc Output bus voltageAC Bus OK - Module Enable, differential error*151720VdcAC Bus OK and Module Enable thresholds track FARM3 MODULE SPECIFICATIONS (see Figure 3 thru Figure 7 for operating characteristics)MINIHAM MODULE SPECIFICATIONS (when used in accordance with Figure 1a)Electrical CharacteristicsElectrical characteristics apply over the full operating range of input voltage, output power and baseplate temperature, unless otherwise specified. All temperatures refer to the operating temperature at the center of the baseplate. Performance specifications are based on the ENMods system as shown in Figure 1a.*Tracking error between BUS OK and Enable thresholdsELECTROMAGNETIC COMPATIBILITY (configured as illustrated in Figures 1a and 1b)Harmonic currents EN61000-3-2, Amendment 1450-625W, 230Vac input 575W output (see Figure 2)Input line disturbances EN61000-4-11Input surge withstand EN61000-4-52kV–50 µs common mode 1kV–50 µs differential mode Conducted emissionsEN55022, Level B(See Figures 8a thru 8c)Electrical Characteristics (continued)MODULE GENERAL SPECIFICATIONSParameter Min Typ Max Unit NotesSafety approvalsFARM3TüV + VDE EN60950, CE Marked (pending) MiniHAM CE Marked (pending)Isolation (in to out)None Isolation provided by DC-DC converter(s) Dielectric withstand (I/O to baseplates)1500Vrms Baseplate earthedLeakage current 2.5mA264VacMTBF>1,000,000Hours25?C, Ground BenignBaseplate material AluminumCover Dupont Zenite / AluminumPin material–Style 1 & 2Copper, Tin/Lead solder dipped–Style S & N (ModuMate compatible)Copper, Nickel/Gold platingWeightFARM3 3.1(88)Ounces (grams)MiniHAM 5.1(145)Ounces (grams)Size 2.25 x 2.2 x 0.5Inches Vicor’s standard mini half-brick package57,9 x 55,9 x 12,7mmStorage temperature(C-, T-Grade)-40+125°C(H-Grade)-55+125°C(M-Grade)-65+125°COperating temperature(C-Grade)-20+100°C Baseplate(T-, H-Grade)-40+100°C Baseplate(M-Grade)-55+100°C BaseplateFigure 1a—ENMods system and DC-DC converter interconnection drawingOperating Characteristics— Input EMI filter for EN55022, Level B complianceFigure 1b ArrayFigure 2 —Measured harmonic current at 230VAC, 575W vs. EN spec limits *Measured values of even harmonics are below 0.01AOperating Characteristics (FARM3)Figure 3—Start-up at 120Vac input Figure 6—Power-down from 240VacFigure 4—Start-up at 240Vac inputVdc outputStrap EngagedI ac input @2A / mVI ac input @2A / mVEnable Enable B OKVdc outputB OKVdc output Enable B OKVdc outputEnableB OKFigure 7—Output overvoltage protection 240Vac rangeVdc outputEnableB OKOperating Characteristics (Conducted emissions relative to EN55022 Reference Figure 1a)Quasi Peak and Average LimitsFigure 8a —Peak detectionFigure 8b —Quasi peak detectionFigure 8c —Average detectionThe ENMods system provides an effective solution for the AC front end of a power supply built with Vicor DC-DC converters.This high performance power system building block satisfies a broad spectrum of requirements and agency standards.The ENMods system provides transient/surge immunity, harmonic current attenuation and EMI filtering, in addition to all of the power switching and control circuitry necessary for autoranging rectification, inrush current limiting, and overvoltage protection.Converter enable and status functions for orderly power up/down control or sequencing are also provided. To complete the AC front end configuration, the user only needs to add hold-up capacitors,a simple EMI filter, and a few discrete components (Fig 1A).Functional Description (F ARM3, see Figures 9 & 10)Power-Up Sequence.Upon application of input power, the hold-up capacitorsbegin to charge. The thermistor limits the charge current,and the exponential time constant is determined by the hold-up capacitor value and the thermistor cold resistance.The slope (dv/dt) of the capacitor voltage versus time approaches zero as the capacitors become charged to the peak of the AC line voltage.The switch that bypasses the inrush limiting PTC (positive temperature coefficient) thermistor is open when power is applied, as is the switch that engages the strap for voltage doubling. In addition, the converter modules are disabled via the Enable (EN) line, and Bus-OK (BOK) is high.If the bus voltage is less than 200V as the slope nearszero, the voltage doubler is activated, and the bus voltage climbs exponentially to twice the peak line voltage. If the bus voltage is greater than 200V , the doubler is not activated.If the bus voltage is greater than 235V as the slopeapproaches zero, the inrush limiting thermistor is bypassed. Below 235V , it is not bypassed.The converters are enabled 50 milliseconds after thethermistor bypass switch is closed.Bus-OK is asserted after an additional 50 milliseconddelay to allow the converter outputs to settle within specification.Power-Down Sequence.When input power is turned off or fails, the following sequence occurs as the bus voltage decays:Bus-OK is deasserted when the bus voltage falls below210Vdc.The converters are disabled when the bus voltage fallsbelow 190Vdc. If power is reapplied after the converters are disabled, the entire power-up sequence is repeated. If a momentary power interruption occurs and power is reestablished before the bus reaches the disable threshold, the power-up sequence is not repeated, i.e., the power conversion system “rides through” the momentary interruption.Application NoteFigure 9—Functional block diagram: FARM3 module Figure 10—Timing diagram: power-up/down sequence1.12.13.14.15.11.22.2Off-Line Power Supply ConfigurationThe ENMods system maintains the DC output bus voltage between 250 and 370Vdc over the entire input voltage range, which is compatible with all Vicor 300V input converters. Autoranging automatically switches to the proper bridge or doubler mode at startup depending on the input voltage, eliminating the possibility of damage due to improper line connection. The ENMods system is rated at 575W output power. These modules can serve as the AC front end for any number and combination of compatible converters as long as the maximum power rating is not exceeded.Pin Descriptions (see Figure 1a)Strap (ST) Pin.In addition to input and output power pin connections, it is necessary to connect the Strap pin to the center junction of the series hold-up capacitors (C1, C2)for proper (autoranging) operation. Varistors V1 and V2 provide capacitor protection. The bleeder resistors (R1, R2)discharge the hold-up capacitors when power is switched off. Capacitors C7 and C8 are recommended if the hold-up capacitors are located more than 3 inches from the output pins.Enable (EN) Pin.The Enable pin must be connected to the PC or Gate-In pin of all converter modules to disable the converters during power-up. Otherwise, the converters would attempt to start while the hold-up capacitors are being charged through the current limiting thermistor,preventing the bus voltage from reaching the thermistor bypass threshold, thus disabling the power supply. The Enable output (the drain of an N channel MOSFET) is internally pulled up to 15V through a 150k?resistor. (see Figure 11)A signal diode should be placed close to and in series with the PC or (Gate-In) pin of each converter to eliminate the possibility of control interference between converters.The Enable pin switches to the high state (15V) with respectto the SR pin to turn on the converters after the power-up inrush is over. The Enable function also provides input overvoltage protection for the converters by turning off the converters if the DC bus voltage exceeds 400Vdc. The thermistor bypass switch opens if this condition occurs, placing the thermistor in series with the input voltage, which reduces the bus voltage to a safe level while limiting input current in case the varistors conduct. The thermistor bypass switch also opens if a fault or overload reduces the bus voltage to less than 180Vdc. (see Figure 9)Bus-OK (BOK) Pin.(see Figure 12)The Bus-OK pin is intended to provide early-warning power fail information and is also referenced to the SR pin.Caution: There is no input to output isolation in the ENMods.It is necessary to monitor Bus-OK via an optoisolator if it is to beused on the secondary (output) side of the converters. A line isolation transformer should be used when performing scope measurements. Scope probes should never be applied simultaneously to the input and output as this will destroy the unit.L, N Pins.Line and neutral input.+, – Pins. Positive and negative outputs.SR Pin. Signal return for BOK and EN outputsFilter(see Figure 1b)The input EMI filter consists of differential and common mode chokes,Y– rated capacitors (line-ground) and X– rated capacitors (line-line). This filter configuration provides sufficient common mode and differential mode insertion loss in the frequency range between 100kHz and 30MHz to comply with the Level B conducted emissions limit, as illustrated in Figures 8a thru 8c.Hold-up CapacitorsHold-up capacitor values should be determined according to output bus voltage ripple, power fail hold-up time, and ride-through time (see Figure 13). Many applications require the power supply to maintain output regulation during a momentary power failure of specified duration, i.e., the converters must hold-up or ride through such an event while maintaining undisturbed output voltage regulation. Similarly, many of these same systems require notification of an impending power failure in order to allow time to perform an orderly shutdown.The energy stored on a capacitor which has been charged to voltage V is:ε= 1/2(CV2) (1) Where:ε= stored energyC = capacitanceV = voltage across the capacitorEnergy is given up by the capacitors as they are discharged by the converters. The energy expended (the power-time product) is:ε= P?t = C(V12–V22) / 2 (2) Where: P = operating powert = discharge intervalV1= capacitor voltage at the beginning of ?tV2= capacitor voltage at the end of ?t Rearranging Equation 2 to solve for the required capacitance:C = 2P?t / (V12–V22) (3)Figure 16—Ripple voltage vs. operating power and bus capacitance, series combination of C1, C2 (see Figure 1a)Figure 15—Ride-through time vs. operating powerFigure 13—Hold-up timeFigure 12—Bus OK (BOK) isolated power status indicatorFigure 11—Enable (EN) functionCalculated values of bus capacitance for various hold-up time,ride-through time, and ripple voltage requirements are given as a function of operating power level in Figures 14, 15, and 16, respectively.ExampleIn this example, the output required from the DC-DC converter at the point of load is 12Vdc at 320W. Therefore, the output power from the ENMods would be 375W (assuming a converter efficiency of 85%). The desired hold-up time is 9ms over an input range of 90 to 264Vac.Determining Required Capacitance for Power Fail Warning.Figure 14 is used to determine capacitance for a given power fail warning time and power level, and shows that the total bus capacitance should be at least 820µF. Since two capacitors are used in series, each capacitor should be at least 1,640µF. Note that warning time is not dependent on line voltage. A hold-up capacitor calculator is available on the Vicor website, at /doc/be6f2843c850ad02de8041d2.html .Determining Ride-through Time.Figure 15 illustrates ride-through time as a function of line voltage and output power,and shows that at a nominal line of 90Vac, ride-through would be 68ms. Ride-through time is a function of linevoltage.Determining Ripple Voltage on the Hold-up Capacitors.Figure 16 is used to determine ripple voltage as a function of operating power and bus capacitance, and shows that the ripple voltage across the hold-up capacitors will be 12V p-p.Determining the Ripple on the Output of theDC-DC Converter.Figure 17 is used to determine the ripple rejection of the DC-DC converter and indicates a ripplerejection of approximately 60 dB for a 12V output. Since the ripple on the bus voltage is 12Vac and the ripple rejection of the converter is 60 dB, the output ripple of the converter due to ripple on its input (primarily 120 Hz) will be 12mV p-p. Note that 2nd Generation converters have greater ripple rejection then either VI-200s or VI-J00s.A variety of hold-up capacitor assemblies (HUBs) areavailable. Please visit the Vicor website @ /doc/be6f2843c850ad02de8041d2.html .For more information about designing an autorangingAC input power supply using the ENMods and Vicor DC-DC converter modules, contact Vicor Applications Engineering at the nearest Vicor Technical Support Center, or send E-mail toapps@/doc/be6f2843c850ad02de8041d2.html .The power fail warning time (?t) is defined as the interval between BOK and converter shutdown (EN) as illustrated in Figure 13. The Bus-OK and Enable thresholds are 205V and 185V, respectively. A simplified relationship between hold-up time, operating power, and bus capacitance is obtained by inserting these constants in equation (3):C = 2P ?t / (2052– 1852)C = 2P ?t / (7,800)It should be noted that the series combination (C1, C2, see Figure 1a)requires each capacitor to be twice the calculated value, but the required voltage rating of each capacitor is reduced to 200V.Allowable ripple voltage on the bus (or ripple current in the capacitors) may define the capacitance requirement. Consideration should be given to converter ripple rejection and resulting output ripple voltage. The ripple rejection (R) of Vicor converters is specified as a function of the input/output voltage ratio:R = 30 + 20log(Vin / Vout)(4)For example, a converter whose output is 15V and nominal input is 300V will provide 56dB ripple rejection, i.e., 10V p-p of input ripple will produce 15mV p-p of output ripple (see Figure 17). Equation 3 is again used to determine the required capacitance. In this case, V 1and V 2are theinstantaneous values of bus voltage at the peaks and valleys (see Figure 13)of the ripple, respectively. The capacitors must holdup the bus voltage for the time interval (?t) between peaks of the rectified line as given by:t = (π– θ) / 2πf(5)Where:f = line frequencyθ= rectifier conduction angleThe approximate conduction angle is given by:θ= Cos -1(V 2/V 1)(6)Another consideration in hold-up capacitor selection is their ripple current rating. The capacitors’ rating must be higher than the maximum operating ripple current. The approximate operating ripple current (rms) is given by:I rms = 2P/V ac (7)Where: P = total output powerV ac = operating line voltageMechanical DiagramINBOARDSOLDER ONBOARD SOLDER ALUMINUM BASEPLA TEVicor’s comprehensive line of power solutions includes modular, high density DC-DC converters and accessory components, configurable power supplies, and custom power systems.Information furnished by Vicor is believed to be accurate and reliable. However, no responsibility isassumed by Vicor for its use. No license is granted by implication or otherwise under any patent or patent rights of Vicor. Vicor components are not designed to be used in applications, such as life support systems,wherein a failure or malfunction could result in injury or death. All sales are subject to Vicor’s Terms and Conditions of Sale, which are available upon request.Specifications are subject to change without notice.Vicor Corporation 25 Frontage Road Andover, MA, USA 01810Tel: 800-735-6200Fax: 978-475-6715EmailVicor Express: vicorexp@/doc/be6f2843c850ad02de8041d2.html Technical Support: apps@/doc/be6f2843c850ad02de8041d2.htmlComponent Solutions for Your Power System4元器件交易⽹/doc/be6f2843c850ad02de8041d2.html。

AZ9831-1A-12D中文资料

COIL

Power At Pickup Voltage (typical) Max. Continuous Dissipation Temperature Rise Temperature 0.80 W 3.2 W at 20°C (68°F) 68°C (122°F) at nominal coil voltage Max.155°C (311°F)

.669 [17.0]

2 x .058 [1.5]

2 x .059 [1.5] 2 x .116 [2.9] 2 x .059 [1.5] 2 x .248 [6.3] 2 x .032 [0.8] 2 x .150 [3.8]

2 x .300 [7.6] 6 x ø .086 ± .003 [ø 2.18 ± .076] .705 [17.90]

MECHANICAL DATA

PC BOARD LAYOUT

1.043 [26.5]

(2X)

2 x ø .076 ± .003 [ø 1.93 ± .076] .335 [8.5]

.331 [8.4] .137 [3.5] .418 [10.6] 2 x .150 [3.8]

0.984 [RMINALS

WIRING DIAGRAMS

6 x .063 [1.6]

86 87 30

2 x .374 [9.5] 2 x .047 [1.2]

85

1 FORM A

VIEWED TOWARD TERMINALS

Dimensions in inches with millimeters in brackets below. Tolerance: ± .010"

GENERAL DATA

ISL6722、ISL6723中文资料

VREF

BG

+ -

VREF 20K 3.0V 1.5V

+ 12K ON BLANKING COMPARATOR + OSCILLATOR COMPARATOR + 3.0V

+ -

OV 2.50V UV 1.45V

+ + -

30K

S

Q Q

VC

RTCT 1mA VREF ON

+

Bi-Directional Synchronization

+ -

VREF

BG

+ -

VREF 20K 3.0V/ 1.5V

+ 12K ON BLANKING COMPARATOR + OSCILLATOR COMPARATOR + 3.0V

+ -

OV 2.50V UV 1.45V

+ + -

30K

S R

Q Q

VC

RTCT 1mA ON

+

GATE

36K

Hale Waihona Puke PGND21

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures. 1-888-INTERSIL or 1-888-468-3774 |Intersil (and design) is a registered trademark of Intersil Americas Inc. Copyright © Intersil Americas Inc. 2006. All Rights Reserved All other trademarks mentioned are the property of their respective owners

LTC6912IDE-1中文资料

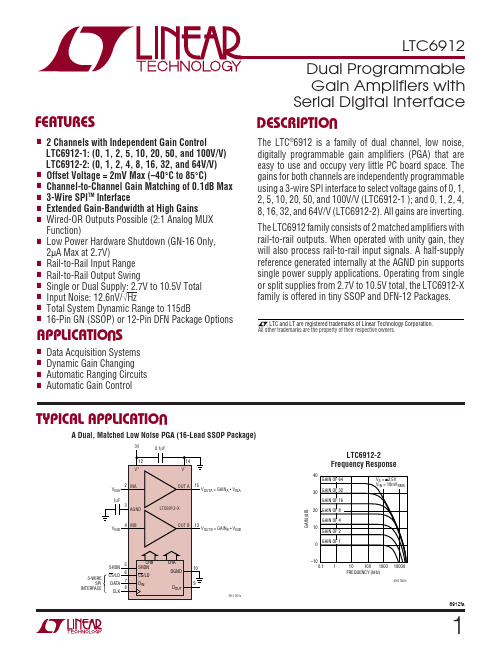

12UUUGAI SETTI GS A D PROPERTIESTable 1. LTC6912-1 GAIN SETTINGS AND PROPERTIESUPPER/LOWER NOMINALNIBBLE VOLTAGE GAIN MAXIMUM LINEAR INPUT RANGE (V P-P)Q7Q6Q5Q4Dual 5V Single 5V Single 3V NOMINAL INPUT NOMINAL OUTPUT Q3Q2Q1Q0Volts/Volt dB Supply Supply Supply IMPEDANCE (kΩ) IMPEDANCE (Ω) 00000–1201053(Open)0.4 0001–101053100.7 0010–265 2.5 1.55 3.4 0011–514210.62 3.4 0100–102010.50.31 3.4 0101–20260.50.250.151 6.4 0110–50340.20.10.06115 0111–100400.10.050.03130 10X X0–1201053(Open)(Open) 11X X Not Used (Note 11)Not UsedTable 2. LTC6912-2 GAIN SETTINGS AND PROPERTIESUPPER/LOWER NOMINALNIBBLE VOLTAGE GAIN MAXIMUM LINEAR INPUT RANGE (V P-P)Q7Q6Q5Q4Dual 5V Single 5V Single 3V NOMINAL INPUT NOMINAL OUTPUT Q3Q2Q1Q0Volts/Volt dB Supply Supply Supply IMPEDANCE (kΩ) IMPEDANCE (Ω) 00000–1201053(Open)0.4 0001–101053100.7 0010–265 2.5 1.55 3.4 0011–412 2.5 1.250.75 2.5 3.4 0100–818.1 1.250.6250.375 1.25 3.4 0101–1624.10.6250.31250.188 1.25 6.4 0110–3230.10.31250.1560.094 1.2515 0111–6436.10.1560.0780.047 1.2530 10X X0–1201053(Open)(Open) 11X X Not Used (Note 11)Not Used36912fa4567891011121314151617181920216912faAPPLICATIO S I FOR ATIOW UUU Offset Voltage vs Gain SettingThe electrical tables list DC offset (error), V OS(OA), at the inputs of the internal op amp (See Figure 1). The electrical tables also show the resulting, gain dependent offset voltage referred to the INA, or INB pins, V OS(IN). The two measures are related through the feedback/input resistor ratio, which equals the nominal gain-magnitude setting,|GAIN|:V OS(IN) = (1 + 1/|GAIN|) V OS(OA)Offset voltages at any gain setting can be inferred from this relationship. For example, an internal amplifier offset V OS(OA) of 1mV will appear referred to the INA, INB pins as 2mV at a gain setting of 1, or 1.5mV at a gain setting of 2.At high gains, V OS(IN) approaches V OS(OA). (Offset voltage is random and can have either polarity centered on 0V).The MOS input circuitry of the internal op amp in Figure 1draws negligible input currents (less than 10µA), so only V OS(OA) and the GAIN affect the overall amplifier’s offset.AC-Coupled OperationAdding capacitors in series with the INA and INB pins converts the LTC6912-X into a dual AC-coupled inverting amplifier, suppressing the input signal’s DC level (and also adding the additional benefit of reducing the offset voltage from the LTC6912-X’s amplifier itself). No further compo-nents are required because the input of the LTC6912-X biases itself correctly when a series capacitor is added.The INA and INB analog input pins connect internally to a resistor whose nominal value varies between 10k Ω and 1k Ω depending on the version of LTC6912 used (see the rightmost column of Tables 1 and 2). Therefore, the low frequency cutoff will vary with capacitor and gain setting.If, for example, a low frequency corner of 1kHz (or lower)on the LTC6912-1 is desired, use a series capacitor of 0.16µF or larger. 0.16µF has a reactance of 1k Ω at 1kHz,giving a 1kHz lower –3dB frequency for gain settings of 10V/V through 100V/V. If the LTC6912-1 is operated at lower gain settings with a 0.16µF capacitor, the higher input resistance will reduce the lower corner frequency down to 100Hz at a gain setting of 1V/V. These frequencies scale inversely with the value of input capacitor used.Note that operating the LTC6912 family in “zero” gain mode (digital state 0000) open circuits both the INA and INB pins and this demands some care if employed with a series AC coupling input capacitor. When the chip enters the zero gain mode, the opened INA or INB pin tends to sample and freeze the voltage across the capacitor to the value it held just before the zero gain state. This can place the INA or INB pin at or near the DC potential of a supply rail. (The INA or INB pin may also drift to a supply potential in this state due to small leakage currents.) To prevent driving the INA or INB pin outside the supply limit and potentially damaging the chip, avoid AC input signals in the zero gain state with an AC coupling capacitor. Also,switching later to a non-zero gain value will cause a transient pulse at the output of the LTC6912-1 (with a time constant set by the capacitor value and the new LTC6912-1input resistance value). This occurs because the INA and INB pins return to the AGND potential forcing transient current sourced by the amplifier output to charge the AC coupling capacitor to its proper DC blocking value.SNR and Dynamic RangeThe term “dynamic range” is much used (and abused)with signal paths. Signal-to-noise (SNR) is an unambigu-ous comparison of signal and noise levels, measured in the same way and under the same operating conditions. In a variable gain amplifier, however, further characterization is useful because both noise and maximum signal level in the amplifier will vary with the gain setting, in general. In the LTC6912-X, maximum output signal is independent of gain (and is near the full power supply voltage, as detailed in the swing sections of the Electrical Characteristics table). The maximum input level falls with increasing gain,and the input-referred noise falls as well (listed also in the table). To summarize the useful signal range in such an amplifier, we define dynamic range (DR) as the ratio of maximum input (at unity gain) to minimum input-referred noise (at maximum gain). This DR has a physical interpre-tation as the range of signal levels that will experience an SNR above unity V/V or 0dB. At a 10V total power supply,DR in the LTC6912-X (gains 0V/V to 100V/V), the DR is typically 115dB (the ratio of 9.9 V P-P , or 3.5V RMS , maxi-mum input to the 6.3µV RMS high gain input noise). The2223Information furnished by Linear Technology Corporation is believed to be accurate and reliable.However, no responsibility is assumed for its use. Linear Technology Corporation makes no represen-tation that the interconnection of its circuits as described herein will not infringe on existing patent rights.24Linear Technology Corporation1630 McCarthy Blvd., Milpitas, CA 95035-7417(408) 432-1900 ● FAX: (408) 434-0507 ● © LINEAR TECHNOLOGY CORPORA TION 2004LT/LT 1005 REV A • PRINTED IN USA。

BS62LV1600FI55中文资料

BS62LV1600FI55中⽂资料Very Low Power CMOS SRAM 2M X 8 bitBS62LV1600Pb-Free and Green package materials are compliant to RoHSn FEATURESWide V CC operation voltage : 2.4V ~ 5.5V Very low power consumption : V CC = 3.0V Operation current : 46mA (Max.) a t 55ns 2mA (Max.) at 1MHz Standby current : 1.5uA (Typ.) at 25 O C V CC = 5.0V Operation current : 115mA (Max.) a t 55ns 10mA (Max.) a t 1MHz Standby current : 6.0uA (Typ.) at 25O C ? High speed access time : -55 55ns (Max.) at V CC :3.0~5.5V -70 70ns (Max.) at V CC : 2.7~5.5V ? Automatic power down when chip is deselected ? Easy expansion with CE1, CE2 and OE options ? Three state outputs and TTL compatible ? Fully static operation ? Data retention supply voltage as low as 1.5V n DESCRIPTIONThe BS62LV1600 is a high performance, very low power CMOS Static Random Access Memory organized as 2048K by 8 bits and operates form a wide range of 2.4V to 5.5V supply voltage.Advanced CMOS technology and circuit techniques provide both high speed and low power features with typical CMOS standby current of 1.5uA at 3.0V/25O C and maximum access time of 55ns at 3.0V/85O C.Easy memory expansion is provided by an active LOW chip enable (CE1), an active HIGH chip enable (CE2), and active LOW output enable (OE) and three-state output drivers.The BS62LV1600 has an automatic power down feature, reducing the power consumption significantly when chip is deselected. The BS62LV1600 is available in JEDEC standard 44-pin TSOP II and 48-ball BGA package.n POWER CONSUMPTIONPOWER DISSIPATIONSTANDBY(I CCSB1, Max)Operating(I CC , Max)V CC =5.0V V CC =3.0V PRODUCT FAMILYOPERATING TEMPERATUREV CC =5.0V V CC =3.0V1MHz10MHzf Max. 1MHz10MHzf Max.PKG TYPEBS62LV1600EC TSOP II-44 BS62LV1600FC Commercial +0O C to +70O C 50uA 8.0uA 9mA 48mA 113mA 1.5mA 19mA 45mABGA-48-0912 BS62LV1600EITSOP II-44 BS62LV1600FIIndustrial -40O C to +85O C100uA 16uA 10mA 50mA 115mA 2mA 20mA 46mABGA-48-0912n PIN CONFIGURATIONSn BLOCK DIAGRAMBrilliance Semiconductor, Inc. reserves the right to change products and specifications without notice.G H F E D C B A 1 2 3 4 5 6 A9 A11 A10 A19A12 A14 A13 A15 WE NC NC NC DQ7 A17 A16 A7 VSS VCC DQ2 DQ1 DQ6 DQ5 NC A5 OE A3 A0 A6 A4 A1A2CE2 NC NC NCCE1 DQ4 NC 48-ball BGA top view NC NC DQ0 VSS VCC DQ3 NC A18 A20 A8n TRUTH TABLEn ABSOLUTE MAXIMUM RATINGS (1)SYMBOL PARAMETER RATING UNITSV TERM Terminal Voltage withRespect to GND-0.5(2) to 7.0 VT BIAS Temperature UnderBias-40 to +125 O CT STG Storage Temperature -60 to +150 O CP T Power Dissipation 1.0 WI OUT DC Output Current 20 mA1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.2. –2.0V in case of AC pulse width less than 30 ns. n OPERATING RANGERANGAMBIENTTEMPERATUREV CC Commercial 0O C to + 70O C 2.4V ~ 5.5VIndustrial -40O C to + 85O C 2.4V ~ 5.5Vn CAPACITANCE (1) (T A = 25O C, f = 1.0MHz) SYMBOL PAMAMETER CONDITIONS MAX. UNITS C INInputCapacitanceV IN = 0V 10 pFC IOInput/OutputCapacitanceV I/O = 0V 12 pF1. This parameter is guaranteed and not 100% tested.n DC ELECTRICAL CHARACTERISTICS (T A =-40O C to +85OC)1. Typical characteristics are at T A =25O C and not 100% tested.2. Undershoot: -1.0V in case of pulse width less than 20 ns.3. Overshoot: V CC +1.0V in case of pulse width less than 20 ns.4. F MAX =1/t RC.5. I CC(MAX.) is 45mA/113mA at V CC =3.0V/5.0V and T A =70O C.6. I CCSB1(MAX.) is 8.0uA/50uA at V CC =3.0V/5.0V and T A =70O C.n DATA RETENTION CHARACTERISTICS (T A = -40O C to +85OC)1. V CC =1.5V, T A =25O C and not 100% tested.2. t RC = Read Cycle Time.3. I CCRD(Max.) is4.0uA at T A =70O C.n LOW V CC DATA RETENTION WAVEFORM (1) (CE1 Controlled)Data Retention Mode V CCt CDRV CC t RV IHV IHCE1≧V CC - 0.2V V DR ≧1.5V CE1V CCn LOW V CC DATA RETENTION WAVEFORM (2) (CE2 Controlled)n AC TEST CONDITIONS (Test Load and Input/Output Reference)Input Pulse Levels Vcc / 0V Input Rise and Fall Times 1V/ns Input and Output Timing Reference Level 0.5Vcc t CLZ , t OLZ , t CHZ , t OHZ , t WHZ C L = 5pF+1TTL Output LoadOthersC L = 30pF+1TTL1. Including jig and scope capacitance.n KEY TO SWITCHING WAVEFORMSn AC ELECTRICAL CHARACTERISTICS (T A = -40O C to +85OC)READ CYCLECE2 Data Retention Mode V CC t CDR V CC t R V ILV IL V CCV DR ≧1.5V CE2≦0.2V 1 TTL ALL INPUT PULSES→← 90%V CC GND Rise Time : 1V/ns Fall Time : 1V/ns90%→← 10%10%n SWITCHING WAVEFORMS (READ CYCLE)READ CYCLE 1 (1,2,4)READ CYCLE 2 (1,3,4)READ CYCLE 3 (1, 4)NOTES:1. WE is high in read Cycle.2. Device is continuously selected when CE1 = V IL and CE2= V IH .3. Address valid prior to or coincident with CE1 transition low and/or CE2 transition high.4. OE = V IL .5. Transition is measured ± 500mV from steady state with C L = 5pF. The parameter is guaranteed but not 100% tested. t RC t OHt AA D OUT ADDRESS t OHD OUTCE2 CE1D OUTCE2 CE1 OE ADDRESSn AC ELECTRICAL CHARACTERISTICS (T A = -40OC to +85OC)WRITE CYCLEn SWITCHING WAVEFORMS (WRITE CYCLE)WRITE CYCLE 1 (1)t WCt WR1(3)t CW(11)t CW(11)t WP(2)t AWt OHZ(4,10)t AS t WR2(3)t DHt DWD IND OUTWECE2CE1OEADDRESS(5)(5)WRITE CYCLE 2 (1,6)NOTES:1. WE must be high during address transitions.2. The internal write time of the memory is defined by the overlap of CE1 and CE2 active and WE low. All signals must be active to initiate a write and any one signal can terminate a write by going inactive. The data input setup and hold timing should be referenced to the second transition edge of the signal that terminates the write.3. t WR is measured from the earlier of CE1 or WE going high or CE2 going low at the end of write cycle.4. During this period, DQ pins are in the output state so that the input signals of opposite phase to the outputs must not be applied.5. If the CE1 low transition or the CE2 high transition occurs simultaneously with the WE low transitions or after the WE transition, output remain in a high impedance state.6. OE is continuously low (OE = V IL ).7. D OUT is the same phase of write data of this write cycle. 8. D OUT is the read data of next address.9. If CE1 is low and CE2 is high during this period, DQ pins are in the output state. Then the data input signals of opposite phase to the outputs must not be applied to them. 10. T ransition is measured ± 500mV from steady state with C L = 5pF. The parameter is guaranteed but not 100% tested. 11. t CW is measured from the later of CE1 going low or CE2 going high to the end of write.D IND OUTWE CE2 CE1ADDRESSn ORDERING INFORMATIONBSI (Brilliance Semiconductor Inc.) assumes no responsibility for the application or use of any product or circuit described herein. BSI does not authorize its products for use as critical components in any application in which the failure of the BSI product may be expected to result in significant injury or death, including life-support systems and critical medical instruments.n PACKAGE DIMENSIONSTSOP II-44n PACKAGE DIMENSIONS (continued)3: SYMBOL "N" IS THE NUMBER OF SOLDER BALLS.1: CONTROLLING DIMENSIONS ARE IN MILLIMETERS. 2: PIN#1 DOT MARKING BY LASER OR PAD PRINT.N EDNOTES:4812.09.0E1D1e3.755.250.75 48 mini-BGA (9mm x 12mm)n Revision HistoryRevision No. History Draft Date Remark2.2 Add Icc1 characteristic parameter Jan. 13, 2006Improve Iccsb1 spec.I-grade from 220uA to 100uA at 5.0V20uA to 16uA at 3.0VC-grade from 110uA to 50uA at 5.0V10uA to 8.0uA at 3.0V2.3 Change I-grade operation temperature range May. 25, 2006 - from –25O C to –40O C。

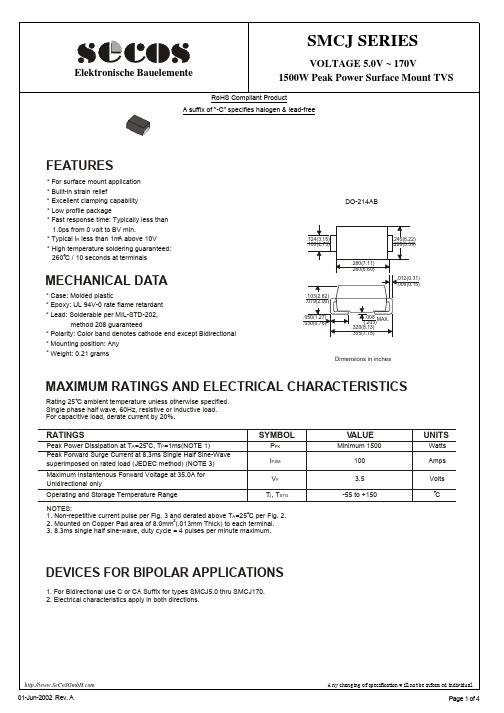

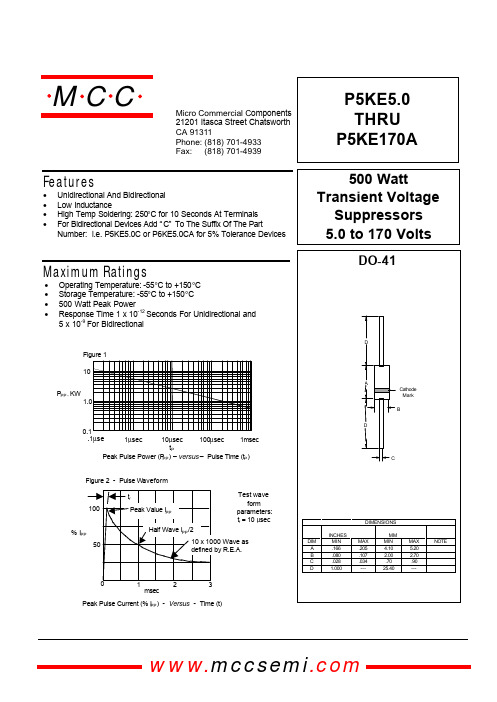

SMCJ中文资料

6.40 6.40 6.67 6.67 7.22 7.22 7.78 7.78 8.33 8.33 8.89 8.89 9.44 9.44 10.0 10.0 11.1 11.1 12.2 12.2 13.3 13.3 14.4 14.4 15.6 15.6 16.7 16.7 17.8 17.8 18.9 18.9 20.0 20.0 22.2 22.2 24.4 24.4 26.7 26.7 28.9 28.9 31.1 31.1 33.3 33.3 36.7 36.7 40.0 40.0 44.4 44.4 47.8 47.8 50.0 50.0 53.3 53.3 56.7 56.7 60.0 60.0 64.4 64.4

TA, AMBIENT TEMPERATURE ( C)

FIG.3-PULSE WAVE FORM

150 IPPM, PEAK PULSE CURRENT, %

tf=10us Peak Value IPPM TA=25 C Pulse Width (td) is defined as the point where the Peak Current Deacys to 50% of Ipp 10,000

RATINGS

Peak Power Dissipation at TA =25 C, TP=1ms(NOTE 1) Peak Forward Surge Current at 8.3ms Single Half Sine-Wave superimposed on rated load (JEDEC method) (NOTE 3) Maximum Instantenous Forward Voltage at 35.0A for Unidirectional only

ADC0809中文资料

PDF pdfFactory

图 11.19 ADC0808/0809 内部结构框图

(1)IN0~IN7——8 路模拟输入,通过 3 根地址译码线 ADDA、ADDB、ADDC 来选通 一路。

(2)D7~D0——A/D 转换后的数据输出端,为三态可控输出,故可直接和微处理器数 据线连接。8 位排列顺序是 D7 为最高位,D0 为最低位。

1

(2)总的不可调误差: ADC0808 为± 2 LSB,ADC 0809 为±1LSB。

(3)转换时间: 取决于芯片时钟频率,如 CLK=500kHz 时,TCONV=128μs。 (4)单一电源: +5V。 (5)模拟输入电压范围: 单极性 0~5V;双极性±5V,±10V(需外加一定电路)。 (6)具有可控三态输出缓存器。 (7)启动转换控制为脉冲式(正脉冲),上升沿使所有内部寄存器清零,下降沿使 A/D 转换开始。 (8)使用时不需进行零点和满刻度调节。 2) 内部结构和外部引脚 ADC0808/0809 的内部结构和外部引脚分别如图 11.19 和图 11.20 所示。内部各部分的 作用和工作原理在内部结构图中已一目了然,在此就不再赘述,下面仅对各引脚定义分述如 下:

×

无操作

0

×

0

启动一次 12 位转换

0

×

1

启动一次 8 位转换

1

+5V

×

并行读出 12 位

1

DGND

0

读出高 8 位(A 段和 B 段)

1

DGND

1

读出 C 段低 4 位,并自动后跟 4 个 0

(8)AGND——模拟地。 (9)GND——数字地。 (10)Vi(R)——参考电压输入端。 (11)VEE——负电源,可选加-11.4V~-16.5V 之间的电压。 (12)BIP OFF——双极性偏移端,用于极性控制。单极性输入时接模拟地(AGND), 双极性输入时接 Vo(R)端。 (13)Vi(10)——单极性 0~+10V 范围输入端,双极性±5V 范围输入端。 (14)Vi(20)——单极性 0~+20V 范围输入端,双极性±10V 范围输入端。 (15)STS——转换状态输出端,只在转换进行过程中呈现高电平,转换一结束立即返 回到低电平。可用查询方式检测此端电平变化,来判断转换是否结束,也可利用它的负跳变

电子器件中文资料

下边资料的次序是纳米盘上的自动排列,请需要者自己看着找吧。

最后还有07年全年的《读者》E书下载,及几个小游戏。

4000系列数字集成电路资料大全.4000.rar/d/7d8425c10a0ff161c3e0e00037737a69c5d3980411432404AD620中文资料.pdf/d/b1961b23b272d8531b9f390fa570ae2c71c2d45024a6050074系列数字集成电路手册大全.pdf/d/b4c283d67d1af4aacf7b7c19d3d5aa3b71a8c58d7692c801速查速用世界可控硅代换手册.pdf/d/be70c47f9fc76db61c62e1caf90d0f4a87d1a68459699901最新集成电路应用300例.rar/d/365971ce99cae66629dd2d76d45b0307e83a21d461b83900怎样使用运算放大器.pdf/d/8ca6ba96b0a2d9d8ed0023ecde54908c909fb5cc8c8e2900新型实用电路制作200例.rar/d/b9f585eb5512f27c380fc3e01ce465e105592c00548f7d00新型电子电路应用实例精选.rar/d/2cd40d687adff1a0031927956c3ae4b16bd41b6489d48e00电子线路设计应用手册.rar/d/86601a2c9c3d346da2b7582806c525fc91e3cf55109a6301新编电子电路大全.rar/d/0ed4b1cba5ad94a5bdfabd410aae1c058c2bbd65aa8f6e00电子电路及电子器件.rar/d/0856a0265ffdc5947a7a4fe93ea34fa53539165b851ea700数字电路.rar/d/00fca0f91805c0f137bcfdc966caba0297c0e6d7dd4c3b00实用双向可控硅应用500例.rar/d/3ebb740d73718fb3cda67b20cb2d50620430f264cc2d6a00实用电子线路集.rar/d/4873ecc0445c91c3d7b444d6b71056bd6b45dc89ef6b8100实用电子电路大全.rar/d/2ca46fb365cedaee9451b79c697e8ff474d22aa6c5ebaf00实用单元电路及其应用.rar/d/3c77fff6e45fddf87dee1bf7788a1c242b1d1c4ef9119600三极管资料大全.rar/d/00de8710ba6c1e8c289ecaf61208d6b6ea32504677a90000绝对精品的硬件设计方面资料.rar/d/c8d1606af74af0a6f7a7f414376c7137e200fb588e460600简易可控硅整流电源电路.pdf/d/28430231e150b19c1d91d1a52f0104a8fef4b07eee510000电子电路大全(合订本).rar/d/7c041e86b457278bc289756622eca10562b31d68f6ba7a01电子电路集.pdf/d/cc133c04fb2ebe2abc1ed4b2a363046e6bff0d2bf8c04100电子电路百科全书(第五卷).rar/d/18148ed5200f99e6176c888024eb8e72d323fcf3e2007900电子电路.pdf/d/f1836309214f28fd8227efa0969e0d39c5261f29c88d4400电子爱好者实用电子制作.rar/d/05edad0c1b9b9c98eabc2847ca8a5d4cfa4fea48d9331f00常用电子元气件手册.pdf/d/f42c221af44585fee096c2b2c3f5d5da87591f3a7a143600常用电子元器件图片.pdf/d/90f6611e31ac9f60a761abb7af0ba31f50fb5a2a781f1c00常用稳压芯片篇.txt/d/6224bdf4fe9e168d36f3ef223422b6add262a8ed810c0000常用电子元器件简明手册.rar/d/00b9d1eedddd798047798152c65d916e257ff4e277702300常用电子元气件命名.pdf/d/3c89dc7fbb8fd14f64b93d946f16583a5c0c3848ce720800P8xC591_cn.pdf/d/8e6c43250690dc6baee98e3865798ee4fc85f5724ba14d00MAX485中文资料.pdf/d/15b701ca1ffd126726fdf070ea1f018d8344aa8bf19c0d00MAX280中文资料.pdf/d/12a35473a7bb0afbb25d41f079b2cbd5af770460877b0100MAX194中文资料.pdf/d/c4a65303e4422f2b661ee713c44e3000ab1ec8baf34b0100T8变压器.pdf/d/86d97d9ca03ec16cb94e885a63912561864f0dfb384d0200NE555.pdf/d/6eeb2db556192e988d3f45d6fc6a976d3743a54695d40300LM7805中文资料.pdf/d/20ade1675d2aebb22a5b7e8596cf421ad74fb6e0bc680400NE555中文资料.pdf/d/4437cbafdb450d9803022a7f145806736178b2647d8e0000MC1413.pdf/d/a8b41856cce7d8c13e68d7be0f7eba717d00bcc2be460100MCP3202中文资料.pdf/d/e6652d4504073a352f4a6e628575bcb68cd4b7bac3ed0b00MC3423.PDF/d/1856c527d115fecf23c7cc792b2df521f434795f4ad80100LM358中文资料.pdf/d/01055a8e69fd7f39469037ab678f9ed4a2807672378c0100LM339.rar/d/8c8b06f70cccad70c338f9f8bb9bf85745f5340af9480000lm2596.pdf/d/67de0105031f80ad657a9558635c3a8b38140cc53ada0c00LM2576中文资料.pdf/d/fc5567b2fa37f7ce88b5272536b2d817eb231c50971e0400lm1117中文资料.pdf/d/f24586db9afc12e7f9bf32371f24b389452a1cc4a7bb0b00LM393中文资料.pdf/d/1961b1559934b7bf617ae57027e87ebb7d12aea50a9a0300LM363中文资料.pdf/d/7e83da8b44365c274829b181ecf725a2291407804cb40100LM7909中文资料.pdf/d/8ce4617cb1123fda1ad10ad38d4493a6480e86f5d4bf0000LMD18200.doc/d/a7e301b93175eb71345299272395fce9e06a30a8009c0100lm324中文资料.pdf/d/cc590a103a433200fdfb3a57f44f5f383d2ee0b4557d0a00LM317中文资料.pdf/d/686a9606b1dd1cca239d8a6bcc8e27d4b45c1f8c24d50d00lm211lm311中文资料.pdf/d/eb9f6ebac497c099445f95a4ad95a0a44730341a715d0b00LM140.pdf/d/3876aea02373e492cdb7da633c9ba26d5f250e06d8e10200LM358.pdf/d/7816ffab592a9e37d9c493dd238fc6b6e55397be8e5e0100LM109.pdf/d/a70eaf6138bb71be74d0431224cbd5d0c7f1136a55740100lm3s317_ds_cn.pdf/d/bd34bf2a2ab69f935911e60206bd5e1a67e6f06ca0215d00 LF398中文资料.pdf/d/bcd8edd55f76babe047e7e1e8e61045af8129ab1866e0100L290-L291-L292.pdf/d/2e0ab9638f84016c18a6ff0fc817b8dbf1043857e30b0400ICL7135中文资料.pdf/d/71e1b23dbc5dff6f6fef9c002be6420f5968745750710800ICL7104中文资料.pdf/d/e07abec1e557ad53c159d7156237bfa86e842cb549820100fm3135_ds.pdf/d/fc97032bc0142c568bdd39f8140d82c6ae4ee9b175260400cd40161中文资料pdf.pdf/d/40230b71ccbbc78b9355e8946d1e4391efecf2199da10200最新世界三极管特性代换手册.r/d/6605148cde3dddb2a4bb9123eb0dcdb6721a053f286c7601lm3s310_ds_cn.pdf/d/bb01eb82cbddbc6fabae95b5a3f631f1d32d3331750e5700cmos4000器件中文资料.pdf/d/bde8cef1903e5f776ddae591fe4b9fe4dd41fa2023074800cd40109中文资料pdf.pdf/d/202883c137a9443ae5aad82ac01c0c5d5b027bfceeb50100cd40105中文资料pdf.pdf/d/b56e06f4a9b172b10908429505b829f1b06b46934bca0100ds1302中文资料.pdf/d/8ffe86b97d76a8cc3fffe2b8b7d7d411ea84ad0bac730300cd40163中文资料pdf.pdf/d/305f9eca8225b8333aafa3a1bd0c4c3c1c3ac34338a10200cd40147中文资料pdf.pdf/d/e3380153eb1198bc857e579999fc3dddb55b460294f20100cd4076中文资料.pdf/d/d000f62e7c0c80c37332f73d5a9200afa8a7f4b572f30200cd4071中文资料.pdf/d/49f8cce83e6ab3e4d593fa45e1f0e685dcbb5186db3a0200cd4070中文资料.pdf/d/82edf36cc8617e3356612ac573e356ba89959470a3420200cd4068中文资料.pdf/d/18c87ad5f8690c9cd1a33121bfd1ba3040256c7d8f490200cd4067中文资料.pdf/d/e6966eea3a191a3186dd7bfb5f19f031b430ea7121530200cd4055中文资料.pdf/d/33d92d1285e92130dbb263df34bebe04f1418d98e29f0300cd4038中文资料.pdf/d/bebc590afbebe766436886d23fbc5205344cbe07d5690300cd4029中文资料pdf.pdf/d/0d4dc7d75ded5885fd3e475e8071f438921d796cbd750400cd4048中文资料.pdf/d/846d38f344ce9ef88598d6e69a542300fed3c3d7d33f0200cd4047中文资料.pdf/d/36a5eec356ffc0baf497d07e71f28081732d28bc145e0200cd4035中文资料.pdf/d/c7b4075b5bda2910cbfdc61bd13730a2d7ab41f161a10300cd4034中文资料.pdf/d/b6dadf2ee2883540208c0f0e06d930fbbf0812016faf0400cd4028中文资料pdf.pdf/d/557cd672fe94a58e1e0c7b508bd095c74c7851d7fb820300cd4024中文资料pdf.pdf/d/c2196481f081938dbb92ed67395098e681fac3206cf10300cd4027中文资料pdf.pdf/d/348e802290198d2503df1013653fd744b97ccdba31ef0200 AT89S51.pdf/d/dccdecb6e6192d5581e790a27bf787eb9a354e1335350900cd4053.pdf/d/404342f322a3a932c98775f207d3ebfd4086551dacb10200cd4034中文资料.pdf/d/49106b6ade07c448f2e9f0d4c232dd8f818961bf6faf0400cd4028中文资料pdf.pdf/d/21e60f5ad93242cad1720458dce6b23333765ec7fb820300cd4027中文资料pdf.pdf/d/60d154cb4a834783bdc59afd3385cd025*********ef0200cd4022中文资料pdf.pdf/d/1057c76c8deff8300c6a6db430ba3282d53d9dbfc70d0400att7021cn.pdf/d/0e5d65285c35682e713bddf0a405e0326a64aba2c6c20a00BA5101BA5201.pdf/d/5d16c3c4e4ac5e156c4241ea590dba00ef7246403acf0400AT89S51.pdf/d/237f01593ba5bddc8665e29116ff139e19c340d435350900AT89LV52.pdf/d/5879e4ac095f60ca5e2b92beb242eaac1c5665cedf300800ad9850中文资料.pdf/d/38a283d55c2c6ceb04694c7a5534c3ae16ab96a6dc6e1c00AT89C1051U.pdf/d/559f6cf5bc2aefa3bbaf4bc6d6f9dd17042dcba1f8d40400 AD673.pdf/d/559f6cf5bc2aefa3bbaf4bc6d6f9dd17042dcba1f8d40400AD620中文资料.pdf/d/145656a8efc258c014c5330ed03482a33a04ea6524a60500AD594_595.pdf/d/6028f9ccfdf02af289e312c94ef8cfc0d9275efdb6220200AD346中文资料.pdf/d/7bd0a4417a8213a7dc982986fbcdae8ce53d9e53fa4401009013.pdf/d/9057c57766e0d1fded4e6a49804e23949c2177bc6d9501008050.pdf/d/24e3b9655ebf0b2f019abd07baaa995fa98f45bf31a1020078xx.pdf/d/af10e44a0a8b804bdd6336b88e2188cf195375644b1c010074LS164中文资料.pdf/d/201383c7b23d7057d102cfc148946d045797b4a88914030074ls245中文资料.pdf/d/37f26e3d5349c02dc216bdc7a487060d1332e94f7501030074LS138中文资料.pdf/d/52f4c8c7b39181704008ceb6e89ea8095faaab98cbbe030074ls138.PDF/d/7aa7e214ce5dfe4c5dce8d9c78ab396289ca517377b9030074ls74.PDF/d/9e1051ab95e509fe3414830be349e6d7d6f56374297a060074ls04.PDF/d/e8a4bad83b00a61a514f295ef7d36aa064801b744472040074LS14中文资料.pdf/d/8938dbc43cdb1a232112a8f69e0b0f7e50357cb54389030074HC245中文资料.pdf/d/d045498e1b5a8b831fb554e3059f7c9c6a3ed92d1701030024c02中文官方资料手册pdf.pdf/d/5463179db3bbb8a494d38f0ab48c8cbb9cf6aece299c090074ALS245.pdf/d/b4c462102ac87887e8e5059e001f16647c213459b13f01004N25中文资料.pdf/d/c818ecf73638d05fb5489690e28b91c94c0976af7ccb0100USB DISK EJECT.EXE/d/4102ee837c5b11d7d7e3d40c759bd5b384154f33007c0d00TEA1062.pdf/d/569c7b2bf61ebf2e2c01d7fcb3bdb0a3f1b83a0d8b4e030078xx.pdf/d/dc3547b7951a28c30c447002adfc743b2cd8174a4b1c010074ls245中文资料.pdf/d/f0fd2d9a704cfc09571d7f694b8e5625ea2577f57501030074LS138中文资料.pdf/d/8df689b9e0e1157387ae34ffb186587654607dc5cbbe030074ls138.PDF/d/906f5068200722722dd009f2c0558d2ca954855d77b9030074ls74.PDF/d/d4ce35981359c38e4e10a143913dbc77ec41b17c297a060074LS14中文资料.pdf/d/500d0dd2c24ca57fdd5f81887ce014ee383cf15f4389030074ls04.PDF/d/00b330534fc4824625e3f5aadb970e2cb07c17204472040024c02中文官方资料手册pdf.pdf/d/0dfded751578a730e85acec4fecb3ff3ecb3e344299c090074HC245中文资料.pdf/d/ff5c91227f1bf663c1326fc19d5295f02035768b1701030074ALS245.pdf/d/0347de88ba42c7981ec9d8cb0829ed27dee125a8b13f01001N4148smd.pdf/d/885391bb8724b237c52840be7996214047193380cfa008002n4403.PDF/d/20bc155264d25b57a981c63afab4b0be6bb806f2b4f700002n4401.PDF/d/40c749e3a06284cca55f4964a1322308e344b26651f70000LMD18200.doc/d/58c3a544b3cc4481889d5c85b54087756849a92e009c0100。

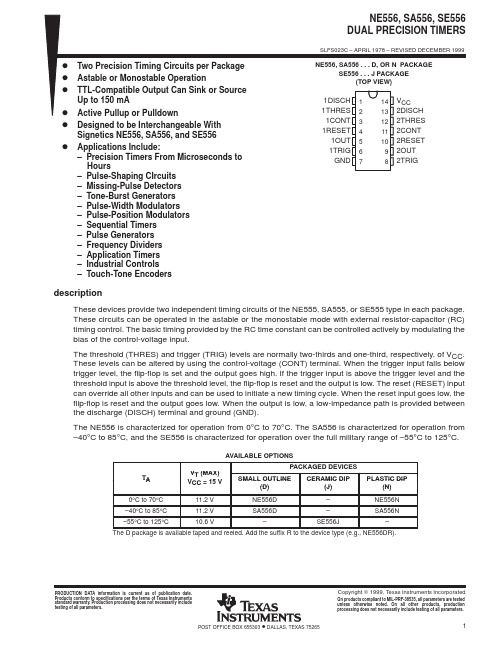

SA556中文资料

元器件交易网IMPORTANT NOTICETexas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinueany product or service without notice, and advise customers to obtain the latest version of relevant informationto verify, before placing orders, that information being relied on is current and complete. All products are soldsubject to the terms and conditions of sale supplied at the time of order acknowledgement, including thosepertaining to warranty, patent infringement, and limitation of liability.TI warrants performance of its semiconductor products to the specifications applicable at the time of sale inaccordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extentTI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarilyperformed, except those mandated by government requirements.CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OFDEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICALAPPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, ORWARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHERCRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TOBE FULLY AT THE CUSTOMER’S RISK.In order to minimize risks associated with the customer’s applications, adequate design and operatingsafeguards must be provided by the customer to minimize inherent or procedural hazards.TI assumes no liability for applications assistance or customer product design. TI does not warrant or representthat any license, either express or implied, is granted under any patent right, copyright, mask work right, or otherintellectual property right of TI covering or relating to any combination, machine, or process in which suchsemiconductor products or services might be or are used. TI’s publication of information regarding any thirdparty’s products or services does not constitute TI’s approval, warranty or endorsement thereof.Copyright © 1999, Texas Instruments Incorporated。

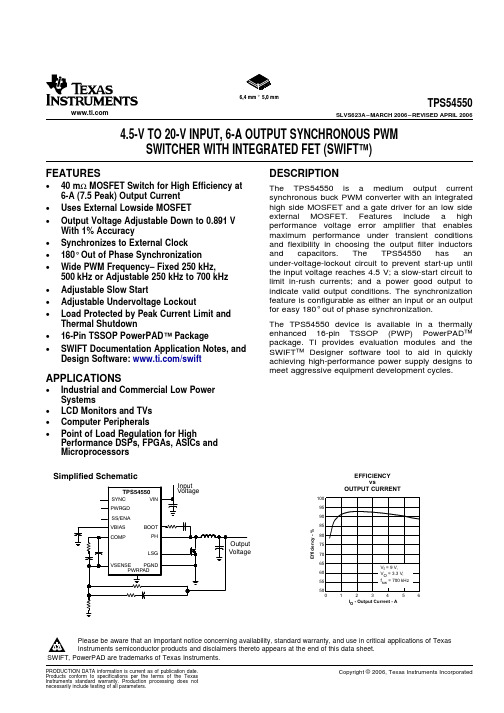

TPS54550PWPRG4资料

6,4 mm 55,0 mmFEATURES DESCRIPTIONAPPLICATIONSI- Output Current -AOEfficiency-%EFFICIENCYvsOUTPUT CURRENTSimplified SchematicTPS54550SLVS623A–MARCH2006–REVISED APRIL20064.5-V TO20-V INPUT,6-A OUTPUT SYNCHRONOUS PWMSWITCHER WITH INTEGRATED FET(SWIFT™)•40mΩMOSFET Switch for High Efficiency at The TPS54550is a medium output current 6-A(7.5Peak)Output Current synchronous buck PWM converter with an integratedhigh side MOSFET and a gate driver for an low side •Uses External Lowside MOSFETexternal MOSFET.Features include a high •Output Voltage Adjustable Down to0.891Vperformance voltage error amplifier that enables With1%Accuracy maximum performance under transient conditions•Synchronizes to External Clock and flexibility in choosing the output filter inductorsand capacitors.The TPS54550has an •180°Out of Phase Synchronizationunder-voltage-lockout circuit to prevent start-up until •Wide PWM Frequency–Fixed250kHz,the input voltage reaches4.5V;a slow-start circuit to500kHz or Adjustable250kHz to700kHz limit in-rush currents;and a power good output to •Adjustable Slow Start indicate valid output conditions.The synchronizationfeature is configurable as either an input or an output •Adjustable Undervoltage Lockoutfor easy180°out of phase synchronization.•Load Protected by Peak Current Limit andThe TPS54550device is available in a thermally Thermal Shutdownenhanced16-pin TSSOP(PWP)PowerPAD™•16-Pin TSSOP PowerPAD™Packagepackage.TI provides evaluation modules and the •SWIFT Documentation Application Notes,and SWIFT™Designer software tool to aid in quickly Design Software:/swift achieving high-performance power supply designs tomeet aggressive equipment development cycles.•Industrial and Commercial Low PowerSystems•LCD Monitors and TVs•Computer Peripherals•Point of Load Regulation for HighPerformance DSPs,FPGAs,ASICs andMicroprocessorsPlease be aware that an important notice concerning availability,standard warranty,and use in critical applications of TexasInstruments semiconductor products and disclaimers thereto appears at the end of this data sheet.SWIFT,PowerPAD are trademarks of Texas Instruments.PRODUCTION DATA information is current as of publication date.Copyright©2006,Texas Instruments Incorporated Products conform to specifications per the terms of the TexasInstruments standard warranty.Production processing does notnecessarily include testing of all parameters.PACKAGE DISSIPATION RATINGS (1)TPS54550SLVS623A–MARCH 2006–REVISED APRIL 2006These devices have limited built-in ESD protection.The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.ORDERING INFORMATIONT jOUTPUT VOLTAGE PACKAGE PART NUMBER (1)-40°C to 125°CAdjustable to 0.891VPlastic HTSSOP (PWP)TPS54550PWP (2)(1)For the most current package and ordering information,see the Package Option Addendum at the end of this document,or see the TI website at .(2)The PWP package is also available taped and reeled.Add an R suffix to the device type (i.e.,TPS54550PWPR).THERMAL IMPEDANCE T A =25°C T A =70°C T A =85°C PACKAGEJUNCTION-TO-AMBIENTPOWER RATINGPOWER RATINGPOWER RATING16-Pin PWP with solder (2)40.1°C/W2.491.371.00(1)See Figure 22for power dissipation curves.(2)Test Board Conditions a.3inch x 3inchb.Thickness:0.062inchc.2PCB layersd.2oz.Coppere.See Figure 26,Figure 27and TPS54550evaluation module user's guide for layout suggestions.2Submit Documentation FeedbackABSOLUTE MAXIMUM RATINGSELECTROSTATIC DISCHARGE RECOMMENDED OPERATING CONDITIONSTPS54550 SLVS623A–MARCH2006–REVISED APRIL2006over operating free-air temperature range unless otherwise noted(1)UNITVIN-0.3V to21.5VVSENSE-0.3V to8.0VUVLO-0.3V to8.0VV I Input voltage rangeSYNC-0.3V to4.0VSSENA-0.3V to4.0VBOOT VI(PH)+8.0VVBIAS-0.3to8.5VLSG-0.3to8.5VSYNC-0.3to4.0VV O Output voltage range RT-0.3to4.0VPWRGD-0.3to6.0VCOMP-0.3to4.0VPH-1.5V to22VPH Internally Limited(A)I O Source current LSG(Steady State Current)10mACOMP,VBIAS3mASYNC5mALSG(Steady State Current)100mAI S Sink current,PH(Steady State Current)500mACOMP3mASSENA,PWRGD10mA Voltage differential AGND to PGND±0.3VT J Junction temperature+150°CT stg Storage temperature-65°C to+150°C Lead temperature1,6mm(1/16inch)from case for10seconds260°C(1)Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device.These are stress ratingsonly,and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied.Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.MIN TYP MAX UNIT Human Body Model HBM JESD22-A114 1.5kV Charged Device Model CDM JESD22-C101 1.5kVMIN NOM MAX UNIT V I Input voltage range 4.520VT J Operating junction temperature-40125°C3Submit Documentation FeedbackELECTRICAL CHARACTERISTICSTPS54550SLVS623A–MARCH 2006–REVISED APRIL 2006T J =-40°C to 125°C,VIN =4.5V to 20V (unless otherwise noted)PARAMETERTEST CONDITIOINSMIN TYP MAX UNITSUPPLY CURRENT Operating Current,PH pin open,10.3mA No external low side MOSFET,RT =Hi-Z I QQuiescent current Shutdown,SSENA =0V1.1mA Start threshold voltage4.324.49V VINStop threshold voltage 3.693.97V Hysteresis350mV UNDER VOLTAGE LOCK OUT (UVLO PIN)Start threshold voltage1.201.24V UVLOStop threshold voltage 1.021.10V Hysteresis100mVBIAS VOLTAGE (VBIAS PIN)I VBIAS =1mA,VIN ≥12V 7.57.88.0VBIASOutput voltageVI VBIAS =1mA,VIN =4.5V 4.4 4.47 4.5REFERENCE SYSTEM ACCURACYT J =25°C0.8880.8910.894V Reference voltage0.8820.8910.899VOSCILLATOR (RT PIN)RT Grounded 200250300Internally set PWM switching frequency kHz RT Open400500600Externally set PWM switching frequency RT =100k Ω(1%resistor to AGND)425500575kHz FALLING EDGE TRIGGERED BIDIRECTIONAL SYNC SYSTEM (SYNC PIN)SYNC out low-to-high rise time (10%/90%)(1)25pF to ground 200500ns SYNC out high-to-low fall time (90%/10%)(1)25pF to ground510ns Delay from rising edge to rising edge of Falling edge delay time (1)180°PH pins Minimum input pulsewidth (1)RT =100k Ω100ns Delay (falling edge SYNC to rising edge PH)(1)RT =100k Ω360ns 50k Ωresistor to ground,SYNC out high level voltage 2.5V No pullup resistorSYNC out low level voltage 0.6V SYNC in low level threshold 0.8V SYNC in high level threshold 2.3V Percentage of programmed frequency-10%10%SYNC in frequency range (1)225770kHz FEED-FORWARD MODULATOR (INTERNAL SIGNAL)Modulator gainVIN =12V,T J =25°C8V/VModulator gain variation -25%25%Minimum controllable ON time (1)180nsMaximum duty factor (1)VIN =4.5V80%86%ERROR AMPLIFIER (VSENSE and COMP PINS)Error amplifier open loop voltage gain (1)6080dB Error amplifier unity gain bandwidth (1) 1.02.8MHz Input bias current,VSENSE pin500nA COMPOutput voltage slew rate (symmetric)(1)1.5V/µs (1)Specified by design,not production tested.4Submit Documentation FeedbackTPS54550 SLVS623A–MARCH2006–REVISED APRIL2006ELECTRICAL CHARACTERISTICS(continued)T J=-40°C to125°C,VIN=4.5V to20V(unless otherwise noted)PARAMETER TEST CONDITIOINS MIN TYP MAX UNIT Slow Start/ENABLE(SSENA PIN)Disable low level input voltage0.5Vf s=250kHz,RT=ground(2) 4.6Internal slow-start time(10%to90%)msf s=500kHz,RT=Hi-Z(2) 2.3Pullup current source 1.8510µAPulldown MOSFET II(SSENA)=1mA0.1V POWER GOOD(PWRGD PIN)Power good threshold Rising voltage97%f s=250kHz4Rising edge delay(2)msf s=500kHz2Output saturation voltage I sink=1mA,VIN>4.5V0.05V PWRGD Output saturation voltage I sink=100µA,VIN=0V0.76V Open drain leakage current Voltage on PWRGD=6V3µA CURRENT LIMITCurrent limit VIN=12V7.58.59.5ACurrent limit Hiccup Time(2)f s=500kHz 4.5ms THERMAL SHUTDOWNThermal shutdown trip point165°CThermal shutdown hysteresis(2)7°C LOW SIDE MOSFET DRIVER(LSG PIN)VIN=4.5V,Capacitive load=1000pF15 Turn on rise time,(10%/90%)(2)nsVIN=8V,Capacitive load=1000pF12 Deadtime(2)VIN=12V60nsVIN=4.5V sink/source7.5 Driver ON resistanceΩVIN=12V sink/source5OUTPUT POWER MOSFETS(PH PIN)Phase node voltage when disabled DC conditions and no load,SSENA=0V0.5VVIN=4.5V,Idc=100mA 1.13 1.42 Voltage drop,low side FET and diode VVIN=12V,Idc=100mA 1.08 1.38VIN=4.5V,BOOT-PH=4.5V,I O=0.5A60r DS(ON)High side power MOSFET switch(3)mΩVIN=12V,BOOT-PH=8V,I O=0.5A40(2)Specified by design,not production tested.(3)Resistance from VIN to PH pins.5Submit Documentation FeedbackPIN ASSIGNMENTSVIN VIN UVLO PWRGDRT SYNC SSENA COMPBOOT PH PH LSG VBIAS PGND AGND VSENSEPWP PACKAGE (TOP VIEW)NOTE:If there is not a Pin 1 indicator, turn device to enable reading the symbol from left to right. Pin 1 is at the lower left corner of the device.TPS54550SLVS623A–MARCH 2006–REVISED APRIL 2006Terminal FunctionsTERMINAL DESCRIPTION 1,2VIN Input supply voltage,4.5V to 20V.Must bypass with a low ESR 10-µF ceramic capacitor.3UVLO Undervoltage lockout pin.Connecting an external resistive voltage divider from VIN to the pin will override the internal default VIN start and stop thresholds.4PWRGD Power good output.Open drain output.A low on the pin indicates that the output is less than the desired output voltage.There is an internal rising edge filter on the output of the PWRGD comparator.5RT Frequency setting pin.Connect a resistor from RT to AGND to set the switching frequency.Connecting the RT pin to ground or floating will set the frequency to an internally preselected frequency.6SYNCBidirectional synchronization I/O pin.SYNC pin is an output when the RT pin is floating or connected low.The output is a falling edge signal out of phase with the rising edge of PH.SYNC may be used as an input tosynchronize to a system clock by connecting to a falling edge signal when an RT resistor is used.See 180°Out of Phase Synchronization operation in the Application Information section.7SSENASlow Start/Enable.The SSENA pin is a dual function pin which provides a logic enable/disable and a slow start time set.Below 0.5V,the device stops switching.Float pin to enable.Capacitor to ground adjusts the slow start time.See Extending Slow Start Time section.8COMP Error amplifier output.Connect frequency compensation network from COMP to VSENSE pins.9VSENSE Inverting node error amplifier.10AGND Analog ground—internally connected to the sensitive analog ground circuitry.Connect to PGND and PowerPAD.11PGND Power Ground—Noisy internal ground—Return currents from the LSG driver output return through the PGND pin.Connect to AGND and PowerPAD.12VBIAS Internal 8.0V bias voltage.A 1.0µF ceramic bypass capacitance is required on the VBIAS pin.13LSG Gate drive for low side MOSFET.Connect gate of n-channel MOSFET.14,15PH Phase node—Connect to external L-C filter.16BOOT Bootstrap for high side gate driver.Connect 24Ohm and 0.1µF ceramic capacitor from BOOT to PH pins.17PowerPADPGND and AGND pins must be connected to the exposed pad for proper operation.See Figure 26for an example PCB layout.6Submit Documentation FeedbackFUNCTIONAL BLOCK DIAGRAMPHLSGPWRGDAGNDPGNDVBIASPOWERPADTPS54550SLVS623A–MARCH 2006–REVISED APRIL 20067Submit Documentation FeedbackDETAILED DESCRIPTIONUndervoltage Lockout(UVLO)Slow Start Enable(SSENA)and Internal SlowT SS_INTERNAL(ms) 1.15kƒs(kHz)(3)Input Voltage SupplyExtending Slow Start TimeR1 VIN(start)1k p1.24V)1k p(1)VIN(stop) (R1)1k p) 1.02V1k p(2)TPS54550SLVS623A–MARCH2006–REVISED APRIL2006StartThe undervoltage lockout(UVLO)system has aninternal voltage divider from VIN to AGND.The Once the SSENA pin voltage exceeds0.5V,the defaults for the start/stop values are labeled VIN and TPS54550starts operation.The TPS54550has an given in Table1.The internal UVLO threshold can be internal digital slow start that ramps the reference overridden by placing an external resistor divider from voltage to its final value in1150switching cycles.The VIN to ground.The internal divider values are internal slow start time(10%-90%)is approximated approximately320kΩfor the high side resistor and by the following expression:125kΩfor the low side resistor.The divider ratio(andtherefore the default start/stop values)is quiteaccurate,but the absolute values of the internalresistors may vary as much as15%.If high accuracy Once the TPS54550device is in normal regulation, is required for an externally adjusted UVLO threshold,the SSENA pin is high.If the SSENA pin is pulled select lower value external resistors to set the UVLO below the stop threshold of0.5V,switching stops ing a1-kΩresistor for the low side and the internal slow start resets.If an application resistor R2(see Figure1)is recommended.Under no requires the TPS54550to be disabled,use open circumstances should the UVLO pin be connected drain or open collector output logic to interface to the directly to VIN.SSENA pin(see Figure2).The SSENA pin has aninternal pullup current source.Do not use external Table1.Start/Stop Voltage Threshold pullup resistors.START VOLTAGE STOP VOLTAGETHRESHOLD THRESHOLDVIN(Default) 4.49 3.69UVLO 1.24 1.02Figure2.Interfacing to the SSENA Pin Figure1.Circuit Using External UVLO FunctionThe equations for selecting the UVLO resistors are:In applications that use large values of outputcapacitance there may be a need to extend the slowstart time to prevent the startup current from trippingthe current limit.The current limit circuit is designedto disable the high side MOSFET and reset theinternal voltage reference for a short amount of time For applications which require an undervoltage lockwhen the high side MOSFET current exceeds the out(UVLO)threshold greater than4.49V,externalcurrent limit threshold.If the output capacitance and resistors may be implemented,see Figure1,to adjustload current cause the startup current to exceed the the start voltage threshold.For example,ancurrent limit threshold,the power supply output will application needing an UVLO start voltage ofnot reach the desired output voltage.To extend the approximately7.8V using the equation(1),R1isslow start time and to reduce the startup current,an calculated to the nearest standard resistor value ofexternal capacitor can be added to the SSENA pin.5.36kΩ.Using Equation2,the input voltage stopThe slow start capacitance is calculated using the threshold is calculated as6.48V.following equation:C SS(µF)=5.55x10-3T ss(ms)8Submit Documentation FeedbackSwitching Frequency(RT)RT(k p)46000ƒs(kHz)–35.9(4)V I(SYNC) V O(PH)TPS54550 SLVS623A–MARCH2006–REVISED APRIL2006The TPS54550has an internal oscillator thatoperates at twice the PWM switching frequency.TheThe RT pin controls the SYNC pin functions.If the RT internal oscillator frequency is controlled by the RTpin is floating or grounded,SYNC is an output.If the pin.Grounding the RT pin sets the PWM switchingswitching frequency has been programmed using a frequency to a default frequency of250kHz.Floatingresistor from RT to AGND,then SYNC functions as the RT pin sets the PWM switching frequency toan input.500kHz.The internal voltage ramp charging current increases Connecting a resistor from RT to AGND sets thelinearly with the set frequency and keeps the feed frequency according to Equation4(see Figure13).forward modulator constant(Km=8)regardless ofthe frequency set point.Table2.Switching Frequency,SYNC and RT PinsSWITCHING FREQUENCY SYNC PIN RT PIN250kHz,internally set Generates SYNC output signal AGND500kHz,internally set Generates SYNC output signal Float Externally set to250kHz to700kHz Terminate to quiet ground with10-kΩR=215kΩto69kΩresistor.Externally synchronized frequency Synchronization Signal Use110kΩwhen RT floats and237kΩwhen RT isgrounded and using the sync out signal of anotherTPS54550.Set RT resistor equal to90%to110%ofexternal synchronization frequency.180°Out of Phase Synchronization(SYNC)When operating the two TPS54550devices180°outof phase,the total RMS input current is reduced. The SYNC pin is configurable as an input or as an Thus reducing the amount of input capacitance output,per the description in the previous section.needed and increasing efficiency.When operating as an input,the SYNC pin is afalling-edge triggered signal(see Figure3and When synchronizing a TPS54550to an external Figure4).When operating as an output,the signal's signal,the timing resistor on the RT pin must be set falling edge is approximately180°out of phase with so that the oscillator is programmed to run at90%to the rising edge of the PH pins.Thus,two TPS54550110%of the synchronization frequency.devices operating in a system can share an inputNOTE:Do not use synchronization input for designs capacitor and draw ripple current at twice thewith output voltages>10V.frequency of a single unit.Figure3.SYNC Input Waveform9Submit Documentation FeedbackInternal OscillatorV O(PH)V O(SYNC)Power Good (PWRGD)Bootstrap Voltage (BOOT)Error AmplifierVoltage ReferenceT delay 1000ƒs(kHz)ms (5)Bias Voltage (VBIAS)TPS54550SLVS623A–MARCH 2006–REVISED APRIL 2006Figure 4.SYNC Output WaveformUp to 1mA of current can be drawn for use in anexternal application circuit.The VBIAS pin must have a bypass capacitor value of 1.0µF.X7R or X5R The VSENSE pin is compared to an internal grade dielectric ceramic capacitors are recommended reference signal,if the VSENSE is greater than 97%because of their stable characteristics over and no other faults are present,the PWRGD pin temperature.presents a high impedance.A low on the PWRGD pin indicates a fault.The PWRGD pin has been designed to provide a weak pull-down and indicates a fault even when the device is unpowered.If the TPS54550The BOOT capacitor obtains its charge cycle by cycle has power and has any fault flag set,the TPS54550from the VBIAS capacitor.A capacitor and small indicates the power is not good by driving the value resistor from the BOOT pin to the PH pins is PWRGD pin low.The following events,singly or in required for operation.The bootstrap connection for combination,indicate power is not good:the high side driver must have a bypass capacitor of 0.1µF and resistor 24Ohm.•VSENSE pin out of bounds •Overcurrent•Thermal shutdown The VSENSE pin is the error amplifier inverting input.•UVLO undervoltageThe error amplifier is a true voltage amplifier with 1.5•Input voltage not present (weak pull-down)mA of drive capability with a minimum of 60dB of •Slow-startingopen loop voltage gain and a unity gain bandwidth of •VBIAS voltage is low2MHz.Once the PWRGD pin presents a high impedance (i.e.,power is good),a VSENSE pin out of bounds condition forces PWRGD pin low (i.e.,power is bad)The voltage reference system produces a precision after a time delay.This time delay is a function of the reference signal by scaling the output of a switching frequency and is calculated using temperature stable bandgap circuit.During production Equation 5:testing,the bandgap and scaling circuits are trimmed to produce 0.891V at the output of the error amplifier,with the amplifier connected as a voltage follower.The trim procedure improves the regulation,since it cancels offset errors in the scaling and error amplifier circuits.The VBIAS regulator provides a stable supply for the internal analog circuits and the low side gate driver.10Submit Documentation FeedbackPWM Control and Feed ForwardDeadtime ControlLow Side Gate Driver(LSG)Thermal Shutdown TPS54550SLVS623A–MARCH2006–REVISED APRIL2006reference ramps from0V to0.891V.During theinitial slow-start interval,the internal reference voltage Signals from the error amplifier output,oscillator,and is very small resulting in a couple of skipped pulses current limit circuit are processed by the PWM control because the minimum on time causes the actual logic.Referring to the internal block diagram,the output voltage to be slightly greater than the preset control logic includes the PWM comparator,PWM output voltage until the internal reference ramps up. latch,and the adaptive dead-time control logic.During steady-state operation below the current limitthreshold,the PWM comparator output and oscillatorpulse train alternately reset and set the PWM latch.Adaptive dead time control prevents shoot throughcurrent from flowing in the integrated high-side Once the PWM latch is reset,the low-side driver andMOSFET and the external low-side MOSFET during integrated pull-down MOSFET remain on for athe switching transitions by actively controlling the minimum duration set by the oscillator pulse width.turn on times of the drivers.The high-side driver does During this period,the PWM ramp discharges rapidlynot turn on until the voltage at the gate of the to the valley voltage.When the ramp begins tolow-side MOSFET is below1V.The low-side driver charge back up,the low-side driver turns off and thedoes not turn on until the voltage at the gate of the high-side FET turns on.The peak PWM ramp voltagehigh-side MOSFET is below1V.varies inversely with input voltage to maintain aconstant modulator and power stage gain of8V/V.As the PWM ramp voltage exceeds the error amplifierLSG is the output of the low-side gate driver.The output voltage,the PWM comparator resets the latch,100-mA MOSFET driver is capable of providing gate thus turning off the high-side FET and turning on thedrive for most popular MOSFETs suitable for this low-side FET.The low-side driver remains on untile the SWIFT Designer Software Tool the next oscillator pulse discharges the PWM ramp.to find the most appropriate MOSFET for the During transient conditions,the error amplifier output application.Connect the LSG pin directly to the gate can be below the PWM ramp valley voltage or above of the low-side MOSFET.Do not use a gate resistor the PWM peak voltage.If the error amplifier is high,as the resulting turn-on time may be too slow.the PWM latch is never reset and the high-side FETremains on until the oscillator pulse signals thecontrol logic to turn the high-side FET off and theThe device uses the thermal shutdown to turn off the internal low-side FET and driver on.The deviceMOSFET drivers and controller if the junction operates at its maximum duty cycle until the outputtemperature exceeds165°C.The device is restarted voltage rises to the regulation set point,settingautomatically when the junction temperature VSENSE to approximately the same voltage as thedecreases to7°C below the thermal shutdown trip internal voltage reference.If the error amplifier outputpoint and starts up under control of the slow-start is low,the PWM latch is continually reset and thecircuit.high-side FET does not turn on.The internal low-sideFET and low side driver remain on until the VSENSEvoltage decreases to a range that allows the PWMcomparator to change states.The TPS54550iscapable of sinking current through the external lowside FET until the output voltage reaches theregulation set point.The minimum on time is designed to be180ns.During the internal slow-start interval,the internalOvercurrent ProtectionOutput Voltage LimitationsT HICCUP(ms) 2250ƒs(kHz)(6)Setting the Output VoltageR2 R1 0.891V O )0.891(7)TPS54550SLVS623A–MARCH 2006–REVISED APRIL 2006OUTPUT VOLTAGE (V)R2VALUE (k Ω)1.228.7Overcurrent protection is implemented by sensing the 1.514.7drain-to-source voltage across the high-side 1.89.76MOSFET and compared to a voltage level which represents the overcurrent threshold limit.If the2.5 5.49drain-to-source voltage exceeds the overcurrent3.33.74threshold limit for more than 100ns,the high-side MOSFET is disable,the SSENA pin is pulled low,and the internal digital slow-start is reset to 0V.SSENA is held low for approximately the time that is calculated Due to the internal design of the TPS54550there are by Equation 6:both upper and lower output voltage limits for any given input voltage.Additionally,the lower boundary of the output voltage set point range is also dependent on operating frequency.The upper limit of the output voltage set point is constrained by the Once the hiccup time is complete,the SSENA pin ismaximum duty cycle of the device and is shown in released and the converter initiates the internal Figure 12.The lower limit is constrained by the slow-start.minimum controllable on time which may be as high as 220ns.The approximate minimum output voltage for a given input voltage and range of operating The output voltage of the TPS54550can be set by frequencies is shown in Figure 8while the maximum feeding back a portion of the output to the VSENSE operating frequency versus input voltage for some pin using a resistor divider network.In the application common output voltages is shown in Figure 10.circuit of Figure 29,this divider network is comprised The curves shown in these two figures are valid for of resistors R1and R2.To calculate the resistor output currents greater than 0.5A.As output currents values to generate the required output voltage use decrease towards no load (0A),the minimum output the following equation:voltage decreases.For applications where the load current is less than 100mA,the curves shown in Figure 9and Figure 11are applicable.All of the data plotted in these curves are approximate and take into Start with a fixed value of R1and calculate theaccount a possible 20percent deviation in actual required R2value.Assuming a fixed value of 10k Ωoperating frequency relative to the intended set point.for R1,the following table gives the appropriate R2value for several common output voltages:TYPICAL CHARACTERISTICS0102030405060708090T - Junction Temperature - °CJ O n R e s i s t a n c e - m W0.89120.89100.89080.89060.89040.89020.89000.8898−50−250255075100125150V r e f − I n t e r n a l V o l t a g e R e f e r e n ce − VT J − Junction Temperature − 5CV - Input Voltage - VI C u r r e n t L i m i t -AM i n i m u m O u t p u t V o l t a g e − VV I − Input Voltage − V100200300400500600700800M a x i m u m S w i t c h i n g F r e q u e n c y − k H zV I − Input Voltage − VM i n i m u m O u t p u t V o l t a g e − VV I − Input Voltage − VM a x i m u m S w i t c h i n g F r e q u e n c y − k H zV I − Input Voltage − V5075100125150175200225200300400500600700R T R e s i s t a n c e − k WSwitching Frequency − kHz02468101214510152025− O u t p u t V o l t a g e − VV O V I − Input Voltage − VTPS54550SLVS623A–MARCH 2006–REVISED APRIL 2006ON RESISTANCECURRENT LIMITINTERNAL VOLTAGE REFERENCEvsvsvsJUNCTION TEMPERATUREINPUT VOLTAGEJUNCTION TEMPERATUREFigure 5.Figure 6.Figure 7.MINIMUM OUTPUT VOLTAGEMINIMUM OUTPUT VOLTAGEMAXIMUM SWITCHING FREQUENCYvsvsvsINPUT VOLTAGEINPUT VOLTAGEINPUT VOLTAGEFigure 8.Figure 9.Figure 10.MAXIMUM SWITCHING FREQUENCYMAXIMUM OUTPUT VOLTAGERT RESISTANCEvsvsvsINPUT VOLTAGEINPUT VOLTAGESWITCHING FREQUENCYFigure 11.Figure 12.Figure 13.。

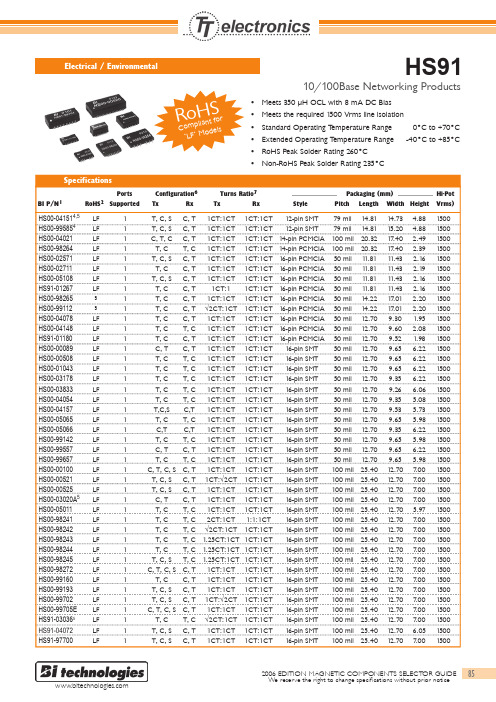

HS00-99557中文资料

Packaging (mm) Hi-Pot Pitch Length Width Height Vrms) 79 mil 79 mil 100 mil 100 mil 50 mil 50 mil 50 mil 50 mil 50 mil 50 mil 50 mil 50 mil 50 mil 50 mil 50 mil 50 mil 50 mil 50 mil 50 mil 50 mil 50 mil 50 mil 50 mil 50 mil 50 mil 100 mil 100 mil 100 mil 100 mil 100 mil 100 mil 100 mil 100 mil 100 mil 100 mil 100 mil 100 mil 100 mil 100 mil 100 mil 100 mil 100 mil 100 mil 14.81 14.81 20.32 20.32 11.81 11.81 11.81 11.81 14.22 14.22 12.70 12.70 12.70 12.70 12.70 12.70 12.70 12.70 12.70 12.70 12.70 12.70 12.70 12.70 12.70 25.40 25.40 25.40 25.40 25.40 25.40 25.40 25.40 25.40 25.40 25.40 25.40 25.40 25.40 25.40 25.40 25.40 25.40 14.73 15.20 17.40 17.40 11.43 11.43 11.43 11.43 17.01 17.01 9.30 9.60 9.52 9.65 9.65 9.65 9.35 9.26 9.35 9.53 9.65 9.35 9.65 9.65 9.65 12.70 12.70 12.70 12.70 12.70 12.70 12.70 12.70 12.70 12.70 12.70 12.70 12.70 12.70 12.70 12.70 12.70 12.70 4.88 4.88 2.49 2.39 2.16 2.19 2.16 2.16 2.20 2.20 1.95 2.08 1.98 6.22 6.22 6.22 6.22 6.06 5.08 5.73 5.98 6.22 5.98 6.22 5.98 7.00 7.00 7.00 7.00 5.97 7.00 7.00 7.00 7.00 7.00 7.00 7.00 7.00 7.00 7.00 7.00 6.05 7.00 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500 1500

ADS中文教程第4章55-71

实验四、交流(AC)仿真概述该实验继续amp_1900任务并与上一实验使用相同子电路。

这个练习交流(AC)仿真的基础,包括小信号增益和噪声,也给出了许多数据显示中控制和操作数据的许多细节特性。