ADPCM模块电路设计规范标准[详]

电路板设计规范

电路板设计规范电路板设计是现代电子技术的重要组成部分,设计规范的制定能够提高电路板的质量和可靠性。

电路板设计规范通常包括以下几个方面:1. 尺寸规范:电路板的尺寸要符合实际应用的需求,同时要考虑到安装空间和制造工艺的限制。

通常会规定电路板的最小尺寸、最大尺寸和间距要求。

2. 材料规范:电路板的材料要选用高质量、可靠性较高的材料。

通常会规定电路板的基板材料、覆盖层材料、插针材料等,并对其性能、热稳定性、机械强度等进行要求。

3. 路径规范:电路板的路径设计是电路板设计中最关键的一环,路径的设计要满足电路板的功能需求、信号传输和电源供应的要求。

通常会规定路径的宽度、间距、走线的弯曲、直角和斜45度等要求。

4. 焊盘规范:焊盘是电子元器件与电路板之间的连接部分,焊盘的设计要考虑到焊接工艺和可靠性。

通常会规定焊盘的形状、尺寸、间距等要求。

同时还要规定焊盘与插针的匹配要求,以确保焊接质量和可靠性。

5. 敏感元件规范:对于一些敏感元件,如高频、高速或特殊要求的元件,需要特别注意其布局和线路的设计。

通常规定相应的设计要求,如禁止穿插布线、尽量避开干扰源等。

6. 接地规范:良好的接地系统是电路板设计中非常重要的一环,能够提高电路板的抗干扰能力和可靠性。

通常会规定接地的布局要求、接地线的宽度和间距、接地线与其他信号线的交叉等要求。

7. 散热规范:电路板的散热设计要考虑到元器件的功耗和工作环境温度等因素,通常会规定散热器的尺寸、位置和材料要求,以确保电路板的稳定和可靠工作。

8. 标志规范:对于电路板上的标志、编号和文字,通常会规定其大小、字体、位置和颜色要求,以便于制造和维护操作。

总之,电路板设计规范的制定对于保证电路板的质量和可靠性非常重要。

通过制定规范,可以确保电路板的设计符合实际应用的需求和制造工艺的要求,提高电路板的性能和可靠性,从而提高整个电子产品的质量。

自适应差值脉冲编码调制(ADPCM)基本原理

自适应差值脉冲编码调制(ADPCM)基本原理目前,脉冲编码调制(PCM)的数字通信系统已经在大容量数字微波、光纤通信系统,以及市话网局间中继传输系统中获得广泛的应用。

但是现有的PCM编码必须采用64Kbit/s的A律或μ律对数压扩的方法,才能符合长途电话传输语音的质量指标,其占用频带要比模拟单边带通信系统宽很多倍。

这样,对于费用昂贵的长途大容量传输,尤其是对于卫星通信系统,采用PCM数字通信方式时的经济性很难和模拟相比拟。

因此,人们一直致力于研究压缩数字化语音占用频带的工作,也就是努力在相同质量指标的条件下,降低数字化语音数码率,以提高数字通信系统的频带利用率。

自适应差值编码调制(ADPCM)是在差值脉冲编码调制(DPCM)基础上逐步发展起来的,DPCM 的工作原理参见原理教材有关章节。

它在实现上采用预测技术减少量化编码器输入信号的多余度,将差值信号编码以提高效率、降低编码信号速率,这广泛应用于语音和图像信号数字化。

CCITT近几年确定了64Kb/s—32kb/s的变换体制,将标准的PCM码变换为32kb/s的ADPCM码,传输后再恢复为64Kb/s的PCM信号,从而使64Kb/s数字话音压缩速率一倍,使传输信道的容易扩大一倍。

ADPCM中的量化器与预测器均采用自适应方式,即量化器与预测器的参数能根据输入信号的统计特性自适应于最佳参数状态。

通常,人们把低于64Kb/s数码率的语音编码方法称为语音压缩编码技术,语音压缩编码方法很多,自适应差值脉冲调制(ADPCM)是语音压缩编码中复杂程度较低的一种方法。

它能在32kbit/s数码率上达到符合64kbit/s数码率的语音质量要求,也就是符合长途电话的质量要求。

当以高于奈奎斯特速率对话音或视频信号抽样时,在前后样值间可以看到有明显的相关性,将这些相关样值按通常PCM系统的方式加以编码时会使得编码信号含有多余信息。

如在编码前将这种多余信息去掉,。

光模块电路设计规范

电路设计规范(Circuit Design Specification)Horse Premieropto 2007-08-15目录1. 目的 (3)2. 适用范围 (3)3. 定义 (3)4. 职责 (3)5. 工作程序 (3)1. 目的对研发过程中的电路设计进行规范,降低设计风险,缩短设计周期。

确保最终设计满足设计意图和需求定义。

2. 适用范围公司光电转换产品电路设计。

3. 定义ES:电原理图,Electrical Scheme DesignAPD:雪崩光电二极管,Avalanche PhotodiodeEDA:电子辅助设计,Electronic Design AutomationPRD:产品需求定义,Product Requirement DefinitionSFP:Small Form-Factor Pluggable TransceiversXFP:10 Gigabit Small Form Factor Pluggable Module4. 职责硬件工程师在进行电子线路设计时可参照本规范。

5. 工作程序电子线路的设计主要包括以下几个方面的工作:电子器件库的建立和维护;电原理图的录入;电原理图的原理验证和设计规则检测;设计评审;5.1 电子器件库电子器件库一般来说EDA工程师统一建立,管理和维护,以确保原理器件库和封装器件的正确对应,及电气特性、器件封装的确定性和完整性。

如果有必要,要求电子工程师一起讨论,并最终建立完整的封装库,有新的封装要求不断加入。

5.2 电原理图的录入产品需求定义以及产品的详细设计说明书可作为原理图设计的依据与输入。

按照功能可将光电转换模块分解为以下部分:电接口部分激光器驱动电路数字监控电路自动光功率控制电路直流升压电路电路设计规则按照以上划分进行细化,可作为设计参考。

不同的光电转换产品有不同的需求,进行电路设计时应根据产品需求定义或产品详细设计说明书灵活处理。

华为公司CAD设计的所有印制电路板规范

华为公司CAD设计的所有印制电路板规范华为公司是一家全球领先的信息与通信技术(ICT)解决方案提供商,不仅在手机和通信领域占有重要地位,还在未来智慧城市、云计算、大数据等领域进行了大量的研发和创新。

在产品研发过程中,电子CAD设计在不可或缺的地位,其中印制电路板(PCB)是设计中最重要的元件之一。

华为公司CAD设计的所有印制电路板规范是由一系列的设计标准和规范所组成的,以下将详细介绍这些规范。

首先,针对PCB的设计标准,华为公司既参考了国内的相关规范,也参考了国际上通用的设计标准。

主要包括:《电子器件应用规范》、IPC 2221/2222、GB 50158、UL PCB样板驱动程序等标准。

针对涉及到物理设计的主要问题,如PCB战斗的尺寸、穴孔引出、线路走向、安装孔、保留边、接地等,华为制定了严格的设计标准,以确保PCB在数据采集、信号处理、精度测量等环节的可靠性和稳定性。

其次,在PCB的材质方面,华为公司在选用材料时要考虑到精度、电性能、可靠性、成本等多方面因素。

为了满足产品设计、热管理、环境、EMC/EMI防护、放置等多方面的要求,华为公司在材料的选择上采取多种选择,包括FR-4、高TG、混合材料和碳纤维增强材料等。

此外,对于同时使用不同材料的项目,还有特定的设计标准和规范。

另外,华为公司在PCB设计的焊接和组装方面也有一系列的标准和规范进行约束。

其中主要涉及到焊盘设计、器件放置、引脚和焊盘的对位、阻抗和耦合等问题。

通过这些规范的制定和执行,华为公司能够确保PCB在使用过程中高精度地传输信号,保证电子设备的稳定性和安全性。

同时,为了提高PCB的设计效率和质量,华为公司在CAD 软件的使用和开发方面也有所投入。

公司的CAD系统被整合到公司的产品生命周期管理系统中,从设计到生产和销售形成一体化管理模式。

同时,将持续研发和优化CAD工具,优化其使用和功能,为PCB的设计提供更好的支持和保障。

综上所述,华为公司CAD设计的所有印制电路板规范是由公司严格制定和执行的,旨在保证产品的可靠性、稳定性和安全性。

ADPCM语音编解码电路设计及FPGA实现

ADPCM语音编解码电路设计及FPGA实现【摘要】本文章主要介绍了ADPCM语音编解码电路设计及FPGA实现的相关内容。

在我们探讨了研究背景、研究意义和研究目的,提出了对ADPCM技术的重要性和研究动机。

在我们详细阐述了ADPCM语音编解码的原理,以及编解码电路的设计过程。

通过FPGA实现设计的讨论,我们展示了如何将理论转化为实际应用,并进行了实验结果的分析。

最后在总结了ADPCM语音编解码电路设计及FPGA实现的整体结论,并展望了未来的发展方向。

这篇文章旨在为相关领域的研究者提供参考,并为ADPCM技术的应用和发展做出一定的贡献。

【关键词】ADPCM, 语音编解码, 电路设计, FPGA实现, 研究背景, 研究意义, 研究目的, 原理, 编码电路设计, 解码电路设计, 实验结果分析, 总体结论, 未来展望1. 引言1.1 研究背景ADPCM(自适应差分脉冲编码调制)是一种常用的语音编解码技术,其核心是通过采样率降低和差分编码来实现语音信号的压缩和传输。

随着信息技术的迅速发展,对语音质量和传输效率的要求越来越高,因此研究ADPCM语音编解码技术具有重要意义。

在传统的ADPCM编解码电路设计中,通常使用基于传统的硬件电路或者嵌入式系统来实现,但是这种方式存在着成本高、功耗大、灵活性差等问题。

1.2 研究意义ADPCM语音编解码技术在现代通信系统和数字音频处理中具有重要的应用价值。

通过对语音信号进行压缩和解压缩处理,可以有效地减少数据传输量,提高通信效率,节省带宽资源。

ADPCM编解码技术在实时语音通信、语音识别和语音合成等领域也发挥着重要作用。

研究ADPCM语音编解码电路设计及FPGA实现的意义在于深入探究该技术的原理和实现方法,为提高音频数据处理和传输的效率提供技术支持。

通过设计高性能的ADPCM编解码电路,并将其实现在FPGA芯片上,可以实现高速、低功耗的语音处理系统。

这对于提高通信质量、降低系统成本具有重要意义。

PCB电路设计规范与要求内容

PCB电路设计规及要求板的布局要求一、印制线路板上的元器件放置的通常顺序:1、放置与结构有紧密配合的固定位置的元器件,如电源插座、指示灯、开关、连接件之类,这些器件放置好后用软件的LOCK 功能将其锁定,使之以后不会被误移动;2、放置线路上的特殊元件和大的元器件,如发热元件、变压器、IC 等;3、放置小器件。

二、元器件离板边缘的距离:1、画定布线区域距PCB板边≤1mm的区域,以及安装孔周围1mm,禁止布线;2、可能的话所有的元器件均放置在离板的边缘3mm以或至少大于板厚,这是由于在大批量生产的流水线插件和进行波峰焊时,要提供给导轨槽使用,同时也为了防止由于外形加工引起边缘部分的缺损,如果印制线路板上元器件过多,不得已要超出3mm围时,可以在板的边缘加上3mm的辅边,辅边开V 形槽,在生产时用手掰断即可。

三、高低压之间的隔离:在许多印制线路板上同时有高压电路和低压电路,高压电路部分的元器件与低压部分要分隔开放置,隔离距离与要承受的耐压有关,通常情况下在2000kV时板上要距离2mm,在此之上以比例算还要加大,例如若要承受3000V的耐压测试,则高低压线路之间的距离应在3.5mm以上,许多情况下为避免爬电,还在印制线路板上的高低压之间开槽。

四、元件布局基本规则1. 按电路模块进行布局,实现同一功能的相关电路称为一个模块,电路模块中的元件应采用就近集中原则,同时数字电路和模拟电路分开;2.定位孔、标准孔等非安装孔周围1.27mm 不得贴装元器件,螺钉等安装孔周围3.5mm〔对于M2.5〕、4mm〔对于M3〕不得贴装元器件;3. 卧装电阻、电感〔插件〕、电解电容等元件的下方避免布过孔,以免波峰焊后过孔与元件壳体短路;4. 元器件的外侧距板边的距离为5mm;5. 贴装元件焊盘的外侧与相邻插装元件的外侧距离大于2mm;6. 金属壳体元器件和金属件〔屏蔽盒等〕不能与其它元器件相碰,不能紧贴印制线、焊盘,其间距应大于2mm。

浅析PCB电路板设计规范

浅析PCB电路板设计规范在PCB电路板设计中,设计规范是非常重要的,它可以确保电路板的性能和可靠性。

设计规范包括电路板外形尺寸、元件、布线、层次结构、电源和接地等方面,本文将从这些方面简要地浅析PCB电路板设计规范。

一、电路板外形尺寸设计规范基本上,电路板的长宽比应该不超过4:3,而且两边的长度不能超过455mm,这样可使电路板方便快捷地制造。

在设计电路板布局时,应注意保持元器件之间的正确位置和间距。

对于大型的元器件或高功率器件,需要更多的空间来散热,这样可以有效地防止限制热量的堵塞,导致设备出现故障。

此外,在布线时,应注意避免元器件之间的相互干扰和短路现象,确保电路板的可靠性和稳定性。

二、PCB电路板元器件规范在元器件规范中,应该注意以下几点:1. 保证元器件的排列合理:在PCB电路板设计中,排列合理的元器件布局可以减少电路板的面积,还可以减少电路板上电路的数量,这样可以提高电路板的可靠性和性能。

2. 保证元器件的可替换性:在设计PCB电路板时,应该留出足够的空间,以便更换故障器件或升级电路。

3. 元器件的选取和使用应符合国家和行业标准,使电路工作安全可靠。

在选择元器件时,应注意材料的质量和厚度,以保证电路板的耐用性和可靠性。

三、PCB电路板布线规范1.保持布线的整洁:在电路板设计中,布线的整洁很重要,可以使电路板更加安全可靠,也可以使电路工作更加稳定。

同时,整洁的布线可以使电路板的维修和改装更加方便。

2.分层布线:分层布线可以有效地降低电路板的干扰和噪声,在布线时应注意避免信号线和电源线的干扰,并保持正确的距离。

3.应避免长路径线和盲孔:长路径线和盲孔是可能引起电路噪声和干扰的因素之一,因此,应该尽量避免使用和布线这种类型的电路。

四、层次结构、信号质量和电源/接地规范在电路板设计时,应注意以下几点:1.层次结构:层次结构是一种设计布局的方法,可以使电路板更加规范化、易于布线和易于组装。

在设计PCB电路板时,应考虑实际情况,选择最适合的层次结构布局方法。

AD详细的设计规范

AD详细的设计规范Design Explorer (DXP)平台及设计环境•各种用户定制GUI的编辑器和浏览器•具有全面设计错误校验功能的设计编译器•支持SCG CVS和SVN的标准版控制接口•支持DelphiScript 、语法感知编码编辑器和形式设计器的脚本引擎•Smart PDF for generation of PDF documents that contain component- and net-navigable views of project PCB and schematics.原理图浏览器•打开浏览原理图•浏览任何对象/器件的属性•预览/打印项目单个图案/所有原理图原理图编辑•所有原理图浏览器功能,以及•最大页面尺寸:64x64英寸•Supported measurement units: Mils, Inches, DXP default units, mms, cms, ms•每个项目最大页面数:不限•页面级别:深度不限•支持的字体:所有Windows支持的字体•支持的输出设备:所有Windows输出设备•网络表输出格式::Protel; PCB 的EDIF 2.0 ; FPGA 的EDIF 2.0 ; CUPL PLD;MultiWire; Spice3F5; VHDL; P-CAD 的PCB;•每页最大器件数:不限•每个器件最大管脚数:不限•每库最大器件数:不限•同时打开的最大库数:不限•电子制表工具:总线;总线输入;器件零件;接头;电源端口;导线;网络标签;端口;页面符号、页面条目•设计指示:没有ERC PCB规则•非电子制表工具:文本注释;文本框;标注;圆弧;椭圆弧;椭圆;饼图;直线;矩形;圆矩形;多边形;4点贝赛尔曲线;图形;椭圆、矩形和多边形注释•可分配的器件管脚电子类型:输入;输出;输入 /输出;开放连接器;无源;高阻;发送器;电源;VHDL>冲器;VHDL^口•用户可定义的器件参数:库编辑器及原理图页均不限•生成报告:材料清单;项目等级;交叉索引. 导入文件格式:所有的Protel原理图格式;最高支持2000版本的AutoCADDXF/DWG P-CAD 原理图ASCII (V15 和V16) ; Orcad 输入(V7 和V9)•导出文件格式:Orcad DOS版本格式原理图;Protel V4 格式原理图;Protel ASCII 格式;ASCII 和二进制Protel原理图模板•数据库链接:原理图器件与Windows操作系统支持的任一OLE数据源供应商之间的在线连接,支持多重关键域支持多通道设计•包含了所有多通道设计管理的功能,从而现在您一旦完成对单个通道的原理图设计,无须改变层次关系系统就可以维护原理图的通道信息,允许用户在任何时候均可更新设计或通道的数量。

ADPCM原理与应用简介

ADPCM原理与应用简介ADPCM原理与应用简介摘要:本文介绍了PCM、DPCM、DM、ADM以及ADPCM的基本原理,并以ADPCM为文章的重点,对它的编解码原理及算法实现的流程框图进行了的讨论。

最后以ADPCM在通信中的应用为例讨简单介绍了在实际通信中的应用。

关键字:ADPCM PCM ADM编码原理Abstract:This article introduce the basic principle of PCM、DPCM、DM、ADM and ADPCM. We take emphasis on ADPCM ,and discuss the theorem of coding and decoding of ADPCM,then introduce the flow char of the theorem. At last we take ADPCM as example to see the use in communication system.Keyword: ADPCM PCM ADM theory of coding一、引言近几十年来对语音数字化和数字化压缩进行了许多研究工作,并取得了丰硕的成果。

1982年CCITT制定了64kb/s压扩PCM语音编码标准G.711。

1986年CCITT又制定了32kb/s ADPCM语音压缩编码标准G.721。

ADPCM是波形编码中非常有效的一种数字编码方式。

在ADPCM 系统中量化器和预测器均采用自适应方式,即量化器和预测器的参数能随输入信号的统计特性自适应于或接近于最佳的参数状态。

与PCM 系统相比,ADPCM的量化器和预测器都是根据前面出现的PCM抽样值并对下一个抽样值进行预测,将当前的抽样值和预测值进行求差,然后对差值进行编码。

对差值编码需要的位数要比直接对原始语音信号编码所需的位数少,从而达到对信号压缩的目的,在这里编码所包含的信息从原来的原始语音信号变为语音信号之间的变化。

adpcm课程设计

adpcm课程设计一、教学目标本课程的学习目标包括知识目标、技能目标和情感态度价值观目标。

知识目标要求学生掌握ADPCM(自适应差分脉冲编码调制)的基本原理及其在数字通信中的应用。

技能目标要求学生能够使用matlab等工具进行ADPCM编解码算法的仿真实验,并分析实验结果。

情感态度价值观目标则是通过学习ADPCM技术,培养学生对通信技术的兴趣和责任感,提高学生解决实际问题的能力。

二、教学内容本课程的教学内容主要包括ADPCM的基本原理、编码算法、解码算法及其在数字通信中的应用。

教学大纲安排如下:1.第1-2课时:ADPCM的基本原理,包括差分脉冲编码调制的发展历程、原理及其特点。

2.第3-4课时:ADPCM的编码算法,包括自适应预测、量化等步骤,以及各种编码算法的比较和性能分析。

3.第5-6课时:ADPCM的解码算法,包括自适应预测的实现、量化逆过程等,以及解码算法的性能评估。

4.第7-8课时:ADPCM在数字通信中的应用,包括语音通信、视频通信等领域,以及ADPCM在现代通信系统中的地位和作用。

三、教学方法本课程的教学方法包括讲授法、讨论法、案例分析法和实验法。

1.讲授法:用于讲解ADPCM的基本原理、编码算法和解码算法,以及其在数字通信中的应用。

2.讨论法:通过分组讨论,让学生深入理解ADPCM技术的原理,提高学生的思考和分析能力。

3.案例分析法:分析实际应用中的ADPCM案例,让学生了解ADPCM技术在实际通信系统中的作用。

4.实验法:使用matlab等工具进行ADPCM编解码算法的仿真实验,培养学生动手能力和实际问题解决能力。

四、教学资源本课程的教学资源包括教材、参考书、多媒体资料和实验设备。

1.教材:选用《数字通信原理》等教材,系统地介绍ADPCM技术。

2.参考书:提供《自适应差分脉冲编码调制技术》等参考书,供学生深入研究。

3.多媒体资料:制作PPT、视频等多媒体资料,生动展示ADPCM技术的基本原理和应用。

ADPCM语音编解码电路设计及FPGA实现 计算机应用研究论文

ADPCM语音编解码电路设计及FPGA实现计算机应用研究论文近年来,多媒体技术逐渐深入到人们的生活中。

MP3播放器已经成为流行的便携式音频播放设备,由于MP3编码算法非常复杂,目前,一部分MP3播放器的录音功能主要基于ADPCM算法和DSP来实现。

本文阐述了ADPCM语音编解码VLSI 芯片的设计方法以及利用FPGA的硬件实现。

ADPCM算法及其编解码器原理ADPCM(AdaptiveDifferentialPulseCodeModulation,自适应差分脉冲编码调制)综合了APCM的自适应特性和DPCM系统的差分特性,是一种性能较好的波形编码。

它的核心思想是:利用自适应改变量化阶的大小,即使用小的量化阶去编码小的差值,使用大的量化阶去编码大的差值,使用过去的样本值估算下一个输入样本的预测值,使实际样本值和预测值之间的差值总是最小。

ADPCM记录的量化值不是每个采样点的幅值,而是该点的幅值与前一个采样点幅值之差。

ADPCM是利用样本与样本之间的高度相关性和量化阶自适应来压缩数据的一种波形编码技术。

ADPCM标准是一个代码转换系统,它使用ADPCM转换技术实现64Kb/sA律或u律PCM(脉冲编码调制)速率和32Kb/s速率之间的相互转换。

ADPCM的简化框图如图1所示。

ADPCM编解码器的输入信号是G.711PCM代码,采样率是8kHz,每个代码用8位表示,因此它的数据率为64Kb/s。

而ADPCM的输出代码是“自适应量化器”的输出,该输出是用4位表示的差分信号,它的采样率仍然是8kHz,它的数据率为32Kb/s,这样就获得了2:1的数据压缩。

540)this.width=540"vspace=5>电路的整体结构基于ADPCM算法,可将语音编解码VLSI芯片分成编码、解码、存储、控制和时钟几个模块。

编码模块实现数据压缩功能,将输入的PCM信号转换成ADPCM码,存储模块在控制模块的作用下,保存编码所得的ADPCM码,解码模块实现解压缩功能,将ADPCM码转换得到PCM码;控制模块的作用是控制其他模块的协调工作;时钟模块主要实现对外部晶振的原始时钟信号进行分频,以得到电路系统实际所需的时钟信号。

adPCM5s5隔离型电源和通信模块技术说明书

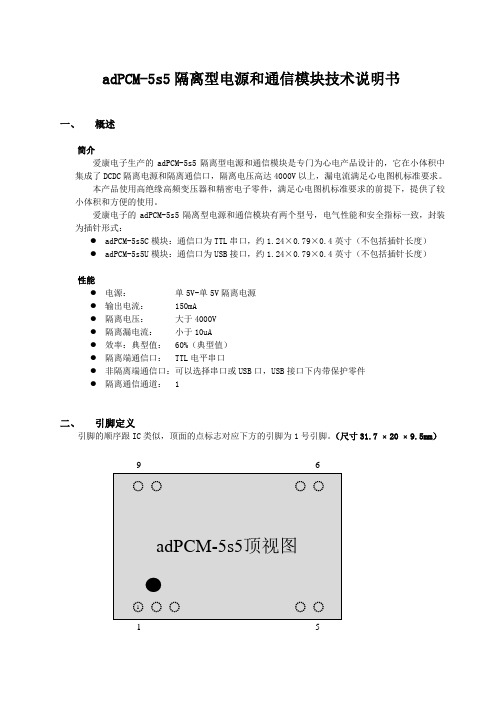

adPCM-5s5隔离型电源和通信模块技术说明书一、概述简介爱康电子生产的adPCM-5s5隔离型电源和通信模块是专门为心电产品设计的,它在小体积中集成了DCDC隔离电源和隔离通信口,隔离电压高达4000V以上,漏电流满足心电图机标准要求。

本产品使用高绝缘高频变压器和精密电子零件,满足心电图机标准要求的前提下,提供了较小体积和方便的使用。

爱康电子的adPCM-5s5隔离型电源和通信模块有两个型号,电气性能和安全指标一致,封装为插针形式:●adPCM-5s5C模块:通信口为TTL串口,约1.24×0.79×0.4英寸(不包括插针长度)●adPCM-5s5U模块:通信口为USB接口,约1.24×0.79×0.4英寸(不包括插针长度)性能●电源:单5V-单5V隔离电源●输出电流: 150mA●隔离电压:大于4000V●隔离漏电流:小于10uA●效率:典型值: 60%(典型值)●隔离端通信口: TTL电平串口●非隔离端通信口:可以选择串口或USB口,USB接口下内带保护零件●隔离通信通道: 1二、引脚定义引脚的顺序跟IC类似,顶面的点标志对应下方的引脚为1号引脚。

(尺寸31.7 ×20 ×9.5mm)9615三、参数模块的供电应该在下表范围内,否则可能引起永久性损坏。

除非另外说明,下列参数的测试条件为:常温、+5V供电。

四、SDK配套说明为了方便用户使用,爱康电子提供心电产品的配套SDK方案,采用该方案,无需用户了解心电产品的软硬件细节,只需要组合硬件模块、操作编程、SDK调用软件包等简单的工作即可实现自己的心电产品:配套情况如下,具体资料见相应说明书:●心电采样模块: adECG-12(标准体积)或 adECG-12s(小体积)●隔离型电源和通信模块:adPCM-5s5C(串口)或 adPCM-5s5C(USB可选)●防除颤模块: adAF-10 (10通道)●SDK开发软件包:见“SDK开发软件包说明书”。

ADPCM编译码器系统

ADPCM编译码器系统一、实验原理和电路说明ADPCM编译码模块将来自用户接口模块的模拟信号进行ADPCM编译码,该模块采用MC145540集成电路完成ADPCM编译码功能。

该器件具有多种工作模式和功能,开机时通过显示控制模块将其配置成ADPCM模式(直接将ADPCM码进行打包传输),使其具有以下功能:1、对接口模块送来的发支路模拟信号进行ADPCM编码输出。

2、将输入的ADPCM码字进行译码(即通话对方的ADPCM码字),并将译码之后的模拟信号送入用户接口模块。

在通信原理实验平台中,有二套完全一致的ADPCM编译码模块,这二个模块与相应的电话用户接口模块相连。

本教程仅以第一路ADPCM编译码原理进行说明,另个模块原理与第一路模块相同,不再重述。

ADPCM编译码模块使用PCM编译码模块相同电路,ADPCM编译码器收、发两支路组成由编码集成电路U502(MC145540)、运放U501(TL082)、晶振U503(20.48MHz)及相应的跳线器、电位器组成。

发送支路的发送信号经U501A运放后放大后,送入U502的2脚进行ADPCM编码。

编码的输出时钟为BCLK(256KHz),编码数据从U502的20脚输出(DT_ADPCM1),FSX为编码抽样时钟信号(8KHz)。

编码之后的数据结果送入后续数据复接模块进行处理,或直接送到对方ADPCM译码单元。

在接收支路中,收数据是来自解数据复接模块的信号(DT_ADPCM_MUX),或是直接来自对方ADPCM编码单元信号(DT_ADPCM2),在接收帧同步时钟FSX与接收输入时钟BCLK(256KHz)的共同作用下,将接收数据送入U502中进行ADPCM译码。

译码之后的模拟信号经运放U501B放大缓冲输出,送到用户接口模块中。

ADPCM编译码模块中的各跳线功能如下(测试点与PCM编译码模块相同):1、跳线开关K501是用于选择输入信号,当K501置于N(正常)位置时,选择来自用户接口单元的话音信号;当K501置于T(测试)位置时选择测试信号。

ADPCM语音编解码电路设计及FPGA实现

ADPCM语音编解码电路设计及FPGA实现ADPCM算法及其解码器原理ADPCM综合了APCM的自适应特性和DPCM统的差分特性,是一性能较好的波形编码。

它的心思想是:利用自适改变量化阶的大小,即使用小的化阶去编码小的差值,用大的量化阶去编码大的值,使用过去的样本值估算一个输入样本的预测值,使实际样值和预测值之间的差总是最小。

ADPCM记录量化值不是每个采点的幅值,而是该点的幅值与前一采样点幅值之差。

ADPCM是利用样本与样本之的高度相关性和量化阶自适应来压数据的一种波形编码技术。

ADPCM标准是一个代转换系统,它使用ADPCM转技术实现64Kb/sA律或u律PCM速率32Kb/s速率间的相互转换。

ADPCM的简框图如图1所示。

ADPCM编解码器的入信号是G.711PCM代,采样率是8kHz,每个代码8位表示,因此它的据率为64Kb/s。

ADPCM的输出码是“自适应量化器”的输出,该出是用4位表示的差分号,它的采样率仍是8kHz,它的据率为32Kb/s,这样就获得了2:1的数据缩。

电路的整体结基于ADPCM算法,可将语音编解码VLSI芯片分成码、解码、存储、控和时钟几个模块。

编码模块实数据压缩功能,将入的PCM信号转换成ADPCM码,存储块在控制模块的作用下,保编码所得的ADPCM 码,解模块实现解压缩功,将ADPCM码转得到PCM码;控制模的作用是控制其他块的协调工作;时钟模块要实现对外部晶振的原始时钟号进行分频,以得到路系统实际所需的时钟信。

电路整体构如图2所示,其中En_enEn_de分别是编码解码的使能信号,RST则为复位信号。

当写有效,而当读有效,CS“1”时,RAM可进写或者读操作。

电路设计过程本文采用Top-doodelSimSE中,并加入所选器件相的器件库进行时序仿真,时序仿通过后,将QuartusII得到的“*.sof”文件通过JTAG配置式下载到FPGA中进不可掉电的实际测试,也可将*.pof”文件通过AS 配置式下载到FPGA中进行掉电的实际测试。

ADPCM语音编解码电路设计及FPGA实现

ADPCM语音编解码电路设计及FPGA实现摘要:ADPCM(自适应差分脉冲编码调制)是一种数字语音编码技术,常用于语音通信和存储领域。

本论文提出了一种基于FPGA实现的ADPCM语音编解码电路设计,该设计采用基于FPGA的高速DSP器件,实现了低时延、高精度的语音编解码,具有编码率可变、降噪功能等优点。

由实验结果可知,本设计能够实现高质量的语音压缩和还原,具有良好的应用前景。

关键词:ADPCM;语音编解码;FPGA;DSP;降噪正文:ADPCM编码是以低码率、高保真度为目标的数字语音压缩技术,广泛应用于电信、广播、铁路等领域。

本论文提出了一种基于FPGA实现的ADPCM语音编解码电路设计,该设计采用了基于FPGA的高速DSP器件,结合了ADPCM编码特点和客户需求,实现了低时延、高精度的语音编解码,具有编码率可变、降噪功能等优点。

本设计采用SPARTAN-6系列FPGA作为硬件平台,结合Verilog语言进行编程,设计了一套完整的ADPCM语音编解码系统。

其中,编码部分主要实现了信号采样、量化、差分处理、编码等功能,解码部分则实现了解码、差分判决、还原等功能。

在此基础上,本文还提出了一种全数字降噪方法,通过采用LMS算法进行信号处理,实现了良好的语音降噪效果。

为了验证本论文所提出的ADPCM编解码电路设计的有效性和准确性,本文进行了丰富的实验测试。

实验结果表明,本设计能够实现高质量的语音压缩和还原,其编码比和信噪比达到了较为理想的水平,具有广阔的应用潜力。

综上所述,本文提出的基于FPGA实现的ADPCM语音编解码电路设计是一种高效、稳定、可靠的语音编解码方案,可广泛应用于语音通信、存储、音频视频等领域。

ADPCM(自适应差分脉冲编码调制)是一种数字语音编码技术,可以将模拟语音信号转换为数字信号进行传输和存储。

ADPCM技术具有低码率、高保真度的优点,广泛应用于语音通信、存储、音频视频等领域。

下面将从几个应用场景分别探讨ADPCM技术的应用。

电路板设计要求

电路板设计要求1.多功能环境监控电路板尺寸为:95mm×125mm,FPGA电路板尺寸为:82mm×105mm。

2.确定安装孔位置与大小(采用过孔、内外径一致,3mm或5mm)并予以Locked3.确定通讯接口、显示器件、指示灯、键盘等与结构密切相关的元器件的位置与方向并予以Locked4.放置电源焊盘,VCC:方型外径200、内径60,GND:八角型外径200、内径60,电源焊盘旁应有标识、电源焊盘尽量靠近电流中心5.设置规则:单片机电路板安全间距为10mil,FPGA为9mil。

过孔大小统一设置为焊盘40mil,过孔20mil,线宽设置,主干VCC不得小于60mil,GND最小不得小于20mil。

6.为VCC建立骨架结构,或连线、或规划,就是说要有概念、心中有线,VCC为树干结构,主干——次干——分支——树杈,它的走线简洁明快、穿孔少7.在连线时各个局部采用正交法则,尤其在很空旷的地方也是如此。

这样后面敷铜时地线才能直接连通、而不需要再重新改线(目的可以改善电路板的电磁兼容性)8.所有信号连线连完经DRC检验无误后,在T ools栏选择添加泪滴焊盘(T eardrops)(目的为了插件器件的引脚连接更牢靠)9.敷铜前将单片机电路板安全间距改为20mil或以上,FPGA电路板改为15mil或以上。

(目的为了防止因腐蚀不开而造成的短路)10.双面敷铜。

11.调整标号位置。

按照规范,PCB板上每个元器件必须有标号,而可以略去型号、阻值、容量等。

每个标号应该一目了然指向所对应的元器件而不能产生歧义,并且不能放在焊盘上。

对于过于稠密且功能相同的元件,可将所有标号隐藏而另加字符串标明。

(目的为了方便焊接)补充:画线步骤:优先规划电源线,期间不一定要布通,其次画总线。

整个画线过程中可以暂时不考虑地线。

最后用大面积覆铜的方式把地线连通。

ADPCM语音解码合成输出系统的设计

1. 1 ADPCM 解码算法的原理 ADP CM 是利用样本与样本之间的高度相关性 和量化阶自适应来压缩数据的一种性能比较好的波 形编码技术。该技术首先是计算出每个当前采样与 一个预测值之间的差值 , 然后计算出下一个预测值 用于计算下一个差值, 并对差值进行编码 , 所以这种 编码需要的位数相对于对整个采样值进行编码所需 要的位数要少很多, 编码时利用自适应改变量化阶 距的大小, 并且根据当前值进 行预测, 用于下次编 码 , 使实际样本值和预测 值之间的差值总 是最小。 ADPCM 的编码简化框图如图 1 所示。

光通信研究

S TU D Y O N OPT ICA L CO M M U N ICA TIO N S

2009. 02 ( Su m. N o. 151)

通信系统与网络技术

ADPCM 语音解码合成输出系统的设计

杨 白, 唐 宁, 汪 洋, 屈 星

( 桂林电子科技大学 信息与通 信学院 , 广西 桂林 541004) 摘要 : 文章介绍了自适应差分脉冲编码调制 ( A DPCM ) 技术的编解码和脉冲宽度调 制 ( PWM ) 技 术的基本 原理 , 研究在现场 可 编程门阵列 ( F PG A) 上通过有限状态机方式实 现 AD PCM 语音解 码算 法 , 利用 PW M 技 术将 解码 后的数 字语 音信号 转化 为 PWM 波 , 以此直接驱动喇 叭发出声音 , 输出的合成语音质量良好 。 关键词 : 现场可编程门阵列 ; 自适应差分脉冲编码调制 ; 语音解码器 ; 脉冲宽度调制 ; 状态机 中图分类号 : T N911 文献标识码 : A 文章编号 : 1005 8788( 2009) 01 0033 03

是相应的数字合成语音样点值, 为二进制数。根据 PWM 的原理可 以得到 实现 数字 PWM 的 系统 框 图, 如 图 5 所 示。由 于 语 音 信 号 的 采 样 频 率 是 8 kH z, 为 了 使 输出 信号 占 空 比为 256 级 的 变化 , 采用 8 位 图5 数字 PWM 器的构成 计数 器来 实 现 0 到 256 的 计

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

目录

1概述 (2)

1.1任务 (2)

1.2说明 (2)

2顶层模块设计 (2)

2.1 电路整体结构 (2)

2.2 顶层模块描述 (3)

3子模块设计 (4)

3.1 编码电路设计 (4)

3.2 解码电路设计 (5)

3.3 其他模块设计 (5)

1概述

1.1任务

本模块可通过部的编码器完成16位PCM数据的IMA-ADPCM格式编码,压缩比为4:1,并可通过部的解码器将其重新解码为PCM数据。

1.2说明

●端口变量使用大写,如AAA

●模块部信号使用小写,如aaa

●同一类的不同信号使用下划线分割,如PCM_IN

2顶层模块设计

2.1 电路整体结构

基于ADPCM算法,可将语音编解码芯片分成编码、解码、存储、控制和时钟几个模块。

编码模块实现数据压缩功能,将输入的PCM信号转换成ADPCM码;存储模块在控制模块的作用下,保存编码所得的ADPCM码;解码模块实现解压缩功能,将ADPCM码转换得到PCM 码;控制模块的作用是控制其他模块的协调工作;时钟模块主要实现对外部晶振的原始时钟信号进行分频,以得到电路系统实际所需的时钟信号。

电路整体结构如图1所示,其中En_en、En_de分别是编码和解码的使能信号,RST则为复位信号。

当WE为“1”时,RAM写有效,而当WE为“0”时,RAM读有效,CS为“l”时,RAM可进行写或者读操作。

图1 电路整体结构图

2.2 顶层模块描述

本设计采用自顶向下的设计思想,其顶层模块描述如下:

module ADPCM_TOP(PCM_OUT, PCM_IN, RECORD, PLAY, CLK, CLK8K);

parameter ADDR_WIDTH=16;

parameter PCM_WIDTH=16;

input [PCM_WIDTH-l:0] PCM_IN;

wire [PCM_WIDTH-1:0] PCM_IN;

output [PCM_WIDTH-1:0] PCM_OUT;

wire [PCM_WIDTH-1:0] PCM_OUT;

input CLK, RECORD, PLAY;

output CLK8K;

wire [3:0] code_in, code_out;

wire en_encoder, en_decoder,re_rst, pl_rst, we,cs;

wire [ADDR_WIDTH-1:0] address;

assign CLK8K=CLK_8K;

CLOCK_GE U0(CLK, RECORD, CLK_8K);

encoder U1(PCM_IN, re_rst, en_encoder, CLK_8K, code_in);

RAM U2(address, we, cs, CLK_8K, code_in, code_out);

decoder U3(pl_rst, CLK_8K, code_out, en_decoder, PCM_OUT);

CONTROL U4(cs, re_rst, pl_rst, en_encoder, en_decoder, we, address, RECORD, PLAY, CLK_8K);

Endmodule

其接口图见下图2:

图2 ADPCM接口图

表1 ADPCM_TOP 模块端口描述

3子模块设计

3.1 编码电路设计

编码电路实现数据压缩功能,将输入的PCM 信号转换成均匀的PCM 码,然后与预测信号进行差分,得到的差分信号经过“自适应量化器”进行压缩编码得到ADPCM 码,ADPCM 码被返回经过“逆自适应量化器”以及“自适应预测器”用来构建下一个预测信号PCM_IN 为编码器输入信号

(PCM 码),CODE 为编码后得到的输出信号(ADPCM 码)。

其简化框图如下图3所示:

图3 ADPCM 编码框图

编码电路模块描述:

模块定义为:encoder(PCM_IN, RST, EN, CLK, CODE);

表2 编码器端口描述

编码模块的状态转换图见下图4所示:

图4 ADPCM编码状态转换图

3.2 解码电路设计

解码电路实现解压缩功能,将ADPCM码经过“逆自适应量化器”得到量化差分信号,量化差分信号与预测值相加得到重构信号,然后转换成PCM码。

其简化框图如下图5所示:

图5 ADPCM解码框图

解码器模块定义为:decoder(RST, CLK, CODE, EN, PCM_OUT);

表3 解码器端口描述

ADPCM解码模块状态转换图见下图6所示:

3.3 其他模块设计

控制电路控制其他电路模块的协调工作,在编码的同时使能存储器写入信号,使编码电路输出数据可以及时存入存储器;在解码的同时使能存储器读出信号,编码和解码不能同时进行。

时钟电路主要实现对外部晶振的原始时钟信号进行分频,以得到电路系统实际所需的时钟信号。

存储器模块定义为:RAM(ADDRESS, WE, CS, CLK_8K, CODE_IN, CODE_OUT);

其端口描述见下表4:

图6 ADPCM解码状态转换图。