MT90880中文资料

MT9090中文资料

Mainframe

µOTDR Module

外 彩色显示屏 2) 执行任务用的专用功能键

66) Menu 键容易进入设置和大容量 存储

7 可视激光二极管 ( 选项 )

3 Start 键是真正一键测试

88) OTDR 接口

4

4 箭头键用于缩放,光标移动和

( 集成功率计选项 ) 99) 双 USB 接口用于快速容易的数据

5

菜单导航

传送

78

2 Product Brochure l MU909014x/15x

一台真正创新型 OTDR!

介绍第一台没有牺牲性能的手持光时域反射仪 – 来自安立的新型 µOTDR 模块™ ! 其性能与尺寸大 4 倍、价格贵 2 倍的传统 OTDR 匹敌, Network Master MT9090A µOTDR 成为新一代测试仪表。其特点 :5 cm 的分辨率用于事件的精确定位,小于 1 米(3 英尺)的盲区和 37dB 的 动态范围 – 能测试超过 150 km (90 以上英里 ) 光纤。MT9090A µOTDR 是第一台真正手掌尺寸的手持 OTDR,将便携性提高到新的水平。.

±2 dB

±1 m ±3 × 测量距离 × 10–5 ± 标记分辨率 ( 不包括 IOR 不确定度 )

内存 : 20 MB (<1,000 条曲线 )

外部 (USB 存储器 ): 1 GB (<30,000 条曲线 )

AT90PWM2_08资料

Features•High Performance, Low Power AVR ® 8-bit Microcontroller •Advanced RISC Architecture–129 Powerful Instructions - Most Single Clock Cycle Execution –32 x 8 General Purpose Working Registers–Fully Static Operation–Up to 1 MIPS throughput per MHz–On-chip 2-cycle Multiplier•Data and Non-Volatile Program Memory–8K Bytes Flash of In-System Programmable Program Memory•Endurance: 10,000 Write/Erase Cycles–Optional Boot Code Section with Independent Lock Bits•In-System Programming by On-chip Boot Program•True Read-While-Write Operation–512 Bytes of In-System Programmable EEPROM•Endurance: 100,000 Write/Erase Cycles–512 Bytes Internal SRAM–Programming Lock for Flash Program and EEPROM Data Security•On Chip Debug Interface (debugWIRE)•Peripheral Features–Two or three 12-bit High Speed PSC (Power Stage Controllers) with 4-bitResolution Enhancement•Non Overlapping Inverted PWM Output Pins With Flexible Dead-Time•Variable PWM duty Cycle and Frequency•Synchronous Update of all PWM Registers•Auto Stop Function for Event Driven PFC Implementation•Less than 25 Hz Step Width at 150 kHz Output Frequency•PSC2 with four Output Pins and Output Matrix–One 8-bit General purpose Timer/Counter with Separate Prescaler and Capture Mode–One 16-bit General purpose Timer/Counter with Separate Prescaler, Compare Mode and Capture Mode–Programmable Serial USART•Standard UART mode•16/17 bit Biphase Mode for DALI Communications–Master/Slave SPI Serial Interface–10-bit ADC•Up To 11 Single Ended Channels and 2 Fully Differential ADC Channel Pairs •Programmable Gain (5x, 10x, 20x, 40x on Differential Channels)•Internal Reference Voltage–10-bit DAC–Two or three Analog Comparator with Resistor-Array to Adjust ComparisonVoltage–4 External Interrupts–Programmable Watchdog Timer with Separate On-Chip Oscillator•Special Microcontroller Features–Low Power Idle, Noise Reduction, and Power Down Modes–Power On Reset and Programmable Brown Out Detection–Flag Array in Bit-programmable I/O Space (4 bytes)Microcontroller with 8K Bytes In-System Programmable AT90PWM2AT90PWM3AT90PWM2B AT90PWM3B Summary24317IS–AVR–01/08AT90PWM2/3/2B/3B–In-System Programmable via SPI Port –Internal Calibrated RC Oscillator ( 8 MHz)–On-chip PLL for fast PWM ( 32 MHz, 64 MHz) and CPU (16 MHz)•Operating Voltage: 2.7V - 5.5V •Extended Operating Temperature:–-40°C to +105°1.HistoryThis datasheet deals with product characteristics of AT90PW2 and AT90WM3. It will be updated as soon as characterization will be done.2.DisclaimerTypical values contained in this datasheet are based on simulations and characterization of other AVR microcontrollers manufactured on the same process technology. Min and Max val-ues will be available after the device is characterized.Product Package 12 bit PWM with deadtime ADC Input ADC Diff Analog Compar ApplicationAT90PWM2AT90PWM2B SO24 2 x 2812One fluorescent ballast AT90PWM3AT90PWM3BSO32, QFN323 x 21123HID ballast, fluorescent ballast, Motor controlProduct RevisionAT90PWM2AT90PWM3First revision of parts, only for running production.AT90PWM2B AT90PWM3BSecond revision of parts, for all new developments.The major changes are :•complement the PSCOUT01, PSCOUT11, PSCOUT21 polarity in centered mode - See “PSCn0 & PSCn1 Basic Waveforms in Center Aligned Mode” on page 139.•Add the PSC software triggering capture - See “PSC 0 Input Capture Register – PICR0H and PICR0L” on page 170.•Add bits to read the PSC output activity - See “PSC0 Interrupt Flag Register – PIFR0” on page 172.•Add some clock configurations - See “Device Clocking Options Select AT90PWM2B/3B” on page 31.•Change Amplifier Synchonization - See “Amplifier” on page 252. and See “” on page 254.•Correction of the Errata - See “Errata” on page 23.34317IS–AVR–01/08AT90PWM2/3/2B/3B3.Pin Configurations44317IS–AVR–01/08AT90PWM2/3/2B/3BFigure 3-3.QFN32 (7*7 mm) Package.3.1Pin Descriptions:Table 3-1.Pin out descriptionS024 Pin NumberSO32 Pin NumberQFN32 Pin NumberMnemonic Type Name, Function & Alternate Function795GND Power Ground: 0V reference182420AGNDPowerAnalog Ground: 0V reference for analog part54317IS–AVR–01/08AT90PWM2/3/2B/3B684VCCpowerPower Supply:172319AVCC PowerAnalog Power Supply: This is the power supply voltage for analog partFor a normal use this pin must be connected.192521AREF PowerAnalog Reference : reference for analog converter . This is the reference voltage of the A/D converter. As output, can be used by external analog8128PBO I/OMISO (SPI Master In Slave Out)PSCOUT20 output9139PB1I/OMOSI (SPI Master Out Slave In)PSCOUT21 output162016PB2I/O ADC5 (Analog Input Channel5 )INT1202723PB3I/O AMP0- (Analog Differential Amplifier 0 Input Channel )212824PB4I/O AMP0+ (Analog Differential Amplifier 0 Input Channel )223026PB5I/OADC6 (Analog Input Channel 6)INT 2233127PB6I/O ADC7 (Analog Input Channel 7)ICP1B (Timer 1 input capture alternate input)PSCOUT11 output (see note 1)243228PB7I/O PSCOUT01 outputADC4 (Analog Input Channel 4)SCK (SPI Clock)NA230PC0I/OPSCOUT10 output (see note 1) INT373PC1I/OPSCIN1 (PSC 1 Digital Input) OC1B (Timer 1 Output Compare B)106PC2I/OT0 (Timer 0 clock input)PSCOUT22 output 117PC3I/O T1 (Timer 1 clock input)PSCOUT23 output2117PC4I/OADC8 (Analog Input Channel 8)AMP1- (Analog Differential Amplifier 1 Input Channel )2218PC5I/OADC9 (Analog Input Channel 9)AMP1+ (Analog Differential Amplifier 1 Input Channel )2622PC6I/O ADC10 (Analog Input Channel 10)ACMP1 (Analog Comparator 1 Positive Input )2925PC7I/OD2A : DAC outputTable 3-1.Pin out description (Continued)S024 Pin NumberSO32 Pin NumberQFN32 Pin NumberMnemonic Type Name, Function & Alternate Function64317IS–AVR–01/08AT90PWM2/3/2B/3B1.PSCOUT10 & PSCOUT11 are not present on 24 pins package4.OverviewThe AT90PWM2/2B/3/3B is a low-power CMOS 8-bit microcontroller based on the AVR enhanced RISC architecture. By executing powerful instructions in a single clock cycle, the AT90PWM2/2B/3/3B achieves throughputs approaching 1 MIPS per MHz allowing the system designer to optimize power consumption versus processing speed.1129PD0I/O PSCOUT00 outputXCK (UART Transfer Clock)SS_A (Alternate SPI Slave Select)3432PD1I/OPSCIN0 (PSC 0 Digital Input )CLKO (System Clock Output)451PD2I/O PSCIN2 (PSC 2 Digital Input)OC1A (Timer 1 Output Compare A)MISO_A (Programming & alternate SPI Master In Slave Out)562PD3I/OTXD (Dali/UART Tx data)OC0A (Timer 0 Output Compare A)SS (SPI Slave Select)MOSI_A (Programming & alternate Master Out SPI Slave In)121612PD4I/OADC1 (Analog Input Channel 1)RXD (Dali/UART Rx data)ICP1A (Timer 1 input capture)SCK_A (Programming & alternate SPI Clock)131713PD5I/OADC2 (Analog Input Channel 2)ACMP2 (Analog Comparator 2 Positive Input )141814PD6I/O ADC3 (Analog Input Channel 3 )ACMPM reference for analog comparators INT0151915PD7I/O ACMP0 (Analog Comparator 0 Positive Input )2331PE0I/O or IRESET (Reset Input)OCD (On Chip Debug I/O)101410PE1I/OXTAL1: XTAL InputOC0B (Timer 0 Output Compare B)111511PE2I/OXTAL2: XTAL OuTputADC0 (Analog Input Channel 0)Table 3-1.Pin out description (Continued)S024 Pin NumberSO32 Pin NumberQFN32 Pin NumberMnemonicTypeName, Function & Alternate Function74317IS–AVR–01/08AT90PWM2/3/2B/3B4.1Block DiagramFigure 4-1.Block DiagramThe AVR core combines a rich instruction set with 32 general purpose working registers. All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle. The resulting architecture is more code efficient while achieving throughputs up to ten times faster than con-ventional CISC microcontrollers.The AT90PWM2/2B/3/3B provides the following features: 8K bytes of In-System Programmable Flash with Read-While-Write capabilities, 512 bytes EEPROM, 512 bytes SRAM, 53 general purpose I/O lines, 32 general purpose working registers,three Power Stage Controllers, two flex-ible Timer/Counters with compare modes and PWM, one USART with DALI mode, an 11-channel 10-bit ADC with two differential input stage with programmable gain, a 10-bit DAC, a programmable Watchdog Timer with Internal Oscillator, an SPI serial port, an On-chip Debug system and four software selectable power saving modes.84317IS–AVR–01/08AT90PWM2/3/2B/3BThe Idle mode stops the CPU while allowing the SRAM, Timer/Counters, SPI ports and interrupt system to continue functioning. The Power-down mode saves the register contents but freezes the Oscillator, disabling all other chip functions until the next interrupt or Hardware Reset. The ADC Noise Reduction mode stops the CPU and all I/O modules except ADC, to minimize switch-ing noise during ADC conversions. In Standby mode, the Crystal/Resonator Oscillator is running while the rest of the device is sleeping. This allows very fast start-up combined with low power consumption.The device is manufactured using Atmel’s high-density nonvolatile memory technology. The On-chip ISP Flash allows the program memory to be reprogrammed in-system through an SPI serial interface, by a conventional nonvolatile memory programmer, or by an On-chip Boot program running on the AVR core. The boot program can use any interface to download the application program in the application Flash memory. Software in the Boot Flash section will continue to run while the Application Flash section is updated, providing true Read-While-Write operation. By combining an 8-bit RISC CPU with In-System Self-Programmable Flash on a monolithic chip,the Atmel AT90PWM2/3 is a powerful microcontroller that provides a highly flexible and cost effective solution to many embedded control applications.The AT90PWM2/3 AVR is supported with a full suite of program and system development tools including: C compilers, macro assemblers, program debugger/simulators, in-circuit emulators,and evaluation kits.4.2Pin Descriptions4.2.1VCCDigital supply voltage.4.2.2GNDGround.4.2.3Port B (PB7..PB0)Port B is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port B output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port B pins that are externally pulled low will source current if the pull-up resistors are activated. The Port B pins are tri-stated when a reset condition becomes active,even if the clock is not running.Port B also serves the functions of various special features of the AT90PWM2/2B/3/3B as listed on page 69.4.2.4Port C (PC7..PC0)Port C is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port C output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port C pins that are externally pulled low will source current if the pull-up resistors are activated. The Port C pins are tri-stated when a reset condition becomes active,even if the clock is not running.Port C is not available on 24 pins package.Port C also serves the functions of special features of the AT90PWM2/2B/3/3B as listed on page 71.94317IS–AVR–01/08AT90PWM2/3/2B/3B4.2.5Port D (PD7..PD0)Port D is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port D output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port D pins that are externally pulled low will source current if the pull-up resistors are activated. The Port D pins are tri-stated when a reset condition becomes active,even if the clock is not running.Port D also serves the functions of various special features of the AT90PWM2/2B/3/3B as listed on page 74.4.2.6Port E (PE2..0) RESET/ XTAL1/XTAL2Port E is an 3-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port E output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port E pins that are externally pulled low will source current if the pull-up resistors are activated. The Port E pins are tri-stated when a reset condition becomes active,even if the clock is not running.If the RSTDISBL Fuse is programmed, PE0 is used as an I/O pin. Note that the electrical char-acteristics of PE0 differ from those of the other pins of Port C.If the RSTDISBL Fuse is unprogrammed, PE0 is used as a Reset input. A low level on this pin for longer than the minimum pulse length will generate a Reset, even if the clock is not running.The minimum pulse length is given in Table 9-1 on page 47. Shorter pulses are not guaranteed to generate a Reset.Depending on the clock selection fuse settings, PE1 can be used as input to the inverting Oscil-lator amplifier and input to the internal clock operating circuit.Depending on the clock selection fuse settings, PE2 can be used as output from the inverting Oscillator amplifier.The various special features of Port E are elaborated in “Alternate Functions of Port E” on page 77 and “Clock Systems and their Distribution” on page 29.4.2.7AVCCAVCC is the supply voltage pin for the A/D Converter. It should be externally connected to V CC ,even if the ADC is not used. If the ADC is used, it should be connected to V CC through a low-pass filter.4.2.8AREFThis is the analog reference pin for the A/D Converter.4.3About Code ExamplesThis documentation contains simple code examples that briefly show how to use various parts of the device. These code examples assume that the part specific header file is included before compilation. Be aware that not all C compiler vendors include bit definitions in the header files and interrupt handling in C is compiler dependent. Please confirm with the C compiler documen-tation for more details.104317IS–AVR–01/08AT90PWM2/3/2B/3B5.Register SummaryAddressNameBit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0Page(0xFF)PICR2H page 170(0xFE)PICR2L page 170(0xFD)PFRC2B PCAE2B PISEL2B PELEV2B PFLTE2B PRFM2B3PRFM2B2PRFM2B1PRFM2B0page 169(0xFC)PFRC2A PCAE2A PISEL2A PELEV2A PFLTE2A PRFM2A3PRFM2A2PRFM2A1PRFM2A0page 168(0xFB)PCTL2PPRE21PPRE20PBFM2PAOC2B PAOC2A PARUN2PCCYC2PRUN2page 167(0xFA)PCNF2PFIFTY2PALOCK2PLOCK2PMODE21PMODE20POP2PCLKSEL2POME2page 164(0xF9)OCR2RBH page 164(0xF8)OCR2RBL page 164(0xF7)OCR2SBH page 163(0xF6)OCR2SBL page 163(0xF5)OCR2RAH page 163(0xF4)OCR2RAL page 163(0xF3)OCR2SAH page 163(0xF2)OCR2SAL page 163(0xF1)POM2POMV2B3POMV2B2POMV2B1POMV2B0POMV2A3POMV2A2POMV2A1POMV2A0page 171(0xF0)PSOC2POS23POS22PSYNC21PSYNC20POEN2DPOEN2BPOEN2CPOEN2Apage 162(0xEF)PICR1H page 170(0xEE)PICR1L page 170(0xED)PFRC1B PCAE1B PISEL1B PELEV1B PFLTE1B PRFM1B3PRFM1B2PRFM1B1PRFM1B0page 169(0xEC)PFRC1A PCAE1A PISEL1A PELEV1A PFLTE1A PRFM1A3PRFM1A2PRFM1A1PRFM1A0page 168(0xEB)PCTL1PPRE11PPRE10PBFM1PAOC1B PAOC1A PARUN1PCCYC1PRUN1page 166(0xEA)PCNF1PFIFTY1PALOCK1PLOCK1PMODE11PMODE10POP1PCLKSEL1-page 164(0xE9)OCR1RBH page 164(0xE8)OCR1RBL page 164(0xE7)OCR1SBH page 163(0xE6)OCR1SBL page 163(0xE5)OCR1RAH page 163(0xE4)OCR1RAL page 163(0xE3)OCR1SAH page 163(0xE2)OCR1SAL page 163(0xE1)Reserved ––––––––(0xE0)PSOC1––PSYNC11PSYNC10–POEN1B–POEN1Apage 162(0xDF)PICR0H page 170(0xDE)PICR0L page 170(0xDD)PFRC0B PCAE0B PISEL0B PELEV0B PFLTE0B PRFM0B3PRFM0B2PRFM0B1PRFM0B0page 169(0xDC)PFRC0A PCAE0A PISEL0A PELEV0A PFLTE0A PRFM0A3PRFM0A2PRFM0A1PRFM0A0page 168(0xDB)PCTL0PPRE01PPRE00PBFM0PAOC0B PAOC0A PARUN0PCCYC0PRUN0page 165(0xDA)PCNF0PFIFTY0PALOCK0PLOCK0PMODE01PMODE00POP0PCLKSEL0-page 164(0xD9)OCR0RBH page 164(0xD8)OCR0RBL page 164(0xD7)OCR0SBH page 163(0xD6)OCR0SBL page 163(0xD5)OCR0RAH page 163(0xD4)OCR0RAL page 163(0xD3)OCR0SAH page 163(0xD2)OCR0SAL page 163(0xD1)Reserved ––––––––(0xD0)PSOC0––PSYNC01PSYNC00–POEN0B–POEN0Apage 162(0xCF)Reserved ––––––––(0xCE)EUDR EUDR7EUDR6EUDR5EUDR4EUDR3EUDR2EUDR1EUDR0page 221(0xCD)MUBRRH MUBRR15MUBRR014MUBRR13MUBRR12MUBRR011MUBRR010MUBRR9MUBRR8page 226(0xCC)MUBRRL MUBRR7MUBRR6MUBRR5MUBRR4MUBRR3MUBRR2MUBRR1MUBRR0page 226(0xCB)Reserved ––––––––(0xCA)EUCSRC ––––FEM F1617STP1STP0page 225(0xC9)EUCSRB –––EUSART EUSBS –EMCH BODR page 224(0xC8)EUCSRA UTxS3UTxS2UTxS1UTxS0URxS3URxS2URxS1URxS0page 223(0xC7)Reserved ––––––––(0xC6)UDR UDR07UDR06UDR05UDR04UDR03UDR02UDR01UDR00page 221 & page 202(0xC5)UBRRH ––––UBRR011UBRR010UBRR09UBRR08page 207(0xC4)UBRRL UBRR07UBRR06UBRR05UBRR04UBRR03UBRR02UBRR01UBRR00page 207(0xC3)Reserved ––––––––(0xC2)UCSRC –UMSEL0UPM01UPM00USBS0UCSZ01UCSZ00UCPOL0page 205(0xC1)UCSRB RXCIE0TXCIE0UDRIE0RXEN0TXEN0UCSZ02RXB80TXB80page 204(0xC0)UCSRA RXC0TXC0UDRE0FE0DOR0UPE0U2X0MPCM0page 203(0xBF)Reserved––––––––AT90PWM2/3/2B/3BAddress Name Bit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0Page(0xBE)Reserved––––––––(0xBD)Reserved––––––––(0xBC)Reserved––––––––(0xBB)Reserved––––––––(0xBA)Reserved––––––––(0xB9)Reserved––––––––(0xB8)Reserved––––––––(0xB7)Reserved––––––––(0xB6)Reserved––––––––(0xB5)Reserved––––––––(0xB4)Reserved––––––––(0xB3)Reserved––––––––(0xB2)Reserved––––––––(0xB1)Reserved––––––––(0xB0)Reserved––––––––(0xAF)AC2CON AC2EN AC2IE AC2IS1AC2IS0AC2SADE-AC2M2AC2M1AC2M0page 230(0xAE)AC1CON AC1EN AC1IE AC1IS1AC1IS0AC1ICE AC1M2AC1M1AC1M0page 229(0xAD)AC0CON AC0EN AC0IE AC0IS1AC0IS0-AC0M2AC0M1AC0M0page 228(0xAC)DACH- / DAC9- / DAC8- / DAC7- / DAC6- / DAC5- / DAC4DAC9 / DAC3DAC8 / DAC2page 262(0xAB)DACL DAC7 / DAC1DAC6 /DAC0DAC5 / -DAC4 / -DAC3 / -DAC2 / -DAC1 / -DAC0 / page 262(0xAA)DACON DAATE DATS2DATS1DATS0-DALA DAOE DAEN page 261(0xA9)Reserved––––––––(0xA8)Reserved––––––––(0xA7)Reserved––––––––(0xA6)Reserved––––––––(0xA5)PIM2--PSEIE2PEVE2B PEVE2A--PEOPE2page 172(0xA4)PIFR2--PSEI2PEV2B PEV2A PRN21PRN20PEOP2page 172(0xA3)PIM1--PSEIE1PEVE1B PEVE1A--PEOPE1page 171(0xA2)PIFR1--PSEI1PEV1B PEV1A PRN11PRN10PEOP1page 172(0xA1)PIM0--PSEIE0PEVE0B PEVE0A--PEOPE0page 171(0xA0)PIFR0--PSEI0PEV0B PEV0A PRN01PRN00PEOP0page 172(0x9F)Reserved––––––––(0x9E)Reserved––––––––(0x9D)Reserved––––––––(0x9C)Reserved––––––––(0x9B)Reserved––––––––(0x9A)Reserved––––––––(0x99)Reserved––––––––(0x98)Reserved––––––––(0x97)Reserved––––––––(0x96)Reserved––––––––(0x95)Reserved––––––––(0x94)Reserved––––––––(0x93)Reserved––––––––(0x92)Reserved––––––––(0x91)Reserved––––––––(0x90)Reserved––––––––(0x8F)Reserved––––––––(0x8E)Reserved––––––––(0x8D)Reserved––––––––(0x8C)Reserved––––––––(0x8B)OCR1BH OCR1B15OCR1B14OCR1B13OCR1B12OCR1B11OCR1B10OCR1B9OCR1B8page 127(0x8A)OCR1BL OCR1B7OCR1B6OCR1B5OCR1B4OCR1B3OCR1B2OCR1B1OCR1B0page 127(0x89)OCR1AH OCR1A15OCR1A14OCR1A13OCR1A12OCR1A11OCR1A10OCR1A9OCR1A8page 127(0x88)OCR1AL OCR1A7OCR1A6OCR1A5OCR1A4OCR1A3OCR1A2OCR1A1OCR1A0page 127(0x87)ICR1H ICR115ICR114ICR113ICR112ICR111ICR110ICR19ICR18page 128(0x86)ICR1L ICR17ICR16ICR15ICR14ICR13ICR12ICR11ICR10page 128(0x85)TCNT1H TCNT115TCNT114TCNT113TCNT112TCNT111TCNT110TCNT19TCNT18page 127(0x84)TCNT1L TCNT17TCNT16TCNT15TCNT14TCNT13TCNT12TCNT11TCNT10page 127(0x83)Reserved––––––––(0x82)TCCR1C FOC1A FOC1B––––––page 127(0x81)TCCR1B ICNC1ICES1–WGM13WGM12CS12CS11CS10page 126(0x80)TCCR1A COM1A1COM1A0COM1B1COM1B0––WGM11WGM10page 123(0x7F)DIDR1––ACMP0D AMP0PD AMP0ND ADC10D/ACMP1D ADC9D/AMP1PD ADC8D/AMP1ND page 252(0x7E)DIDR0ADC7D ADC6D ADC5D ADC4D ADC3D/ACMPMD ADC2D/ACMP2D ADC1D ADC0D page 251(0x7D)Reserved––––––––Address Name Bit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0Page (0x7C)ADMUX REFS1REFS0ADLAR–MUX3MUX2MUX1MUX0page 247 (0x7B)ADCSRB ADHSM––ADASCR ADTS3ADTS2ADTS1ADTS0page 249 (0x7A)ADCSRA ADEN ADSC ADATE ADIF ADIE ADPS2ADPS1ADPS0page 248 (0x79)ADCH- / ADC9- / ADC8- / ADC7- / ADC6- / ADC5- / ADC4ADC9 / ADC3ADC8 / ADC2page 251 (0x78)ADCL ADC7 / ADC1ADC6 / ADC0ADC5 / -ADC4 / -ADC3 / -ADC2 / -ADC1 / -ADC0 / page 251 (0x77)AMP1CSR AMP1EN-AMP1G1AMP1G0-AMP1TS2AMP1TS1AMP1TS0page 257 (0x76)AMP0CSR AMP0EN-AMP0G1AMP0G0-AMP0TS2AMP0TS1AMP0TS0page 256 (0x75)Reserved––––––––(0x74)Reserved––––––––(0x73)Reserved––––––––(0x72)Reserved––––––––(0x71)Reserved––––––––(0x70)Reserved––––––––(0x6F)TIMSK1––ICIE1––OCIE1B OCIE1A TOIE1page 128 (0x6E)TIMSK0–––––OCIE0B OCIE0A TOIE0page 101 (0x6D)Reserved––––––––(0x6C)Reserved––––––––(0x6B)Reserved––––––––(0x6A)Reserved––––––––(0x69)EICRA ISC31ISC30ISC21ISC20ISC11ISC10ISC01ISC00page 81 (0x68)Reserved––––––––(0x67)Reserved––––––––(0x66)OSCCAL–CAL6CAL5CAL4CAL3CAL2CAL1CAL0page 34 (0x65)Reserved––––––––(0x64)PRR PRPSC2PRPSC1PRPSC0PRTIM1PRTIM0PRSPI PRUSART PRADC page 43 (0x63)Reserved––––––––(0x62)Reserved––––––––(0x61)CLKPR CLKPCE–––CLKPS3CLKPS2CLKPS1CLKPS0page 39 (0x60)WDTCSR WDIF WDIE WDP3WDCE WDE WDP2WDP1WDP0page 540x3F (0x5F)SREG I T H S V N Z C page 130x3E (0x5E)SPH SP15SP14SP13SP12SP11SP10SP9SP8page 150x3D (0x5D)SPL SP7SP6SP5SP4SP3SP2SP1SP0page 150x3C (0x5C)Reserved––––––––0x3B (0x5B)Reserved––––––––0x3A (0x5A)Reserved––––––––0x39 (0x59)Reserved––––––––0x38 (0x58)Reserved––––––––0x37 (0x57)SPMCSR SPMIE RWWSB–RWWSRE BLBSET PGWRT PGERS SPMEN page 2710x36 (0x56)Reserved––––––––0x35 (0x55)MCUCR SPIPS––PUD––IVSEL IVCE page 60 & page 68 0x34 (0x54)MCUSR––––WDRF BORF EXTRF PORF page 500x33 (0x53)SMCR––––SM2SM1SM0SE page 410x32 (0x52)MSMCR Monitor Stop Mode Control Register reserved0x31 (0x51)MONDR Monitor Data Register reserved0x30 (0x50)ACSR ACCKDIV AC2IF AC1IF AC0IF–AC2O AC1O AC0O page 2310x2F (0x4F)Reserved––––––––0x2E (0x4E)SPDR SPD7SPD6SPD5SPD4SPD3SPD2SPD1SPD0page 1810x2D (0x4D)SPSR SPIF WCOL–––––SPI2X page 1810x2C (0x4C)SPCR SPIE SPE DORD MSTR CPOL CPHA SPR1SPR0page 1790x2B (0x4B)Reserved––––––––0x2A (0x4A)Reserved––––––––0x29 (0x49)PLLCSR-----PLLF PLLE PLOCK page 370x28 (0x48)OCR0B OCR0B7OCR0B6OCR0B5OCR0B4OCR0B3OCR0B2OCR0B1OCR0B0page 1010x27 (0x47)OCR0A OCR0A7OCR0A6OCR0A5OCR0A4OCR0A3OCR0A2OCR0A1OCR0A0page 1000x26 (0x46)TCNT0TCNT07TCNT06TCNT05TCNT04TCNT03TCNT02TCNT01TCNT00page 1000x25 (0x45)TCCR0B FOC0A FOC0B––WGM02CS02CS01CS00page 990x24 (0x44)TCCR0A COM0A1COM0A0COM0B1COM0B0––WGM01WGM00page 960x23 (0x43)GTCCR TSM ICPSEL1–––––PSRSYNC page 840x22 (0x42)EEARH––––EEAR11EEAR10EEAR9EEAR8page 210x21 (0x41)EEARL EEAR7EEAR6EEAR5EEAR4EEAR3EEAR2EEAR1EEAR0page 210x20 (0x40)EEDR EEDR7EEDR6EEDR5EEDR4EEDR3EEDR2EEDR1EEDR0page 220x1F (0x3F)EECR––––EERIE EEMWE EEWE EERE page 220x1E (0x3E)GPIOR0GPIOR07GPIOR06GPIOR05GPIOR04GPIOR03GPIOR02GPIOR01GPIOR00page 270x1D (0x3D)EIMSK––––INT3INT2INT1INT0page 820x1C (0x3C)EIFR––––INTF3INTF2INTF1INTF0page 820x1B (0x3B)GPIOR3GPIOR37GPIOR36GPIOR35GPIOR34GPIOR33GPIOR32GPIOR31GPIOR30page 28AT90PWM2/3/2B/3BAddress Name Bit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0Page 0x1A (0x3A)GPIOR2GPIOR27GPIOR26GPIOR25GPIOR24GPIOR23GPIOR22GPIOR21GPIOR20page 27 0x19 (0x39)GPIOR1GPIOR17GPIOR16GPIOR15GPIOR14GPIOR13GPIOR12GPIOR11GPIOR10page 27 0x18 (0x38)Reserved––––––––0x17 (0x37)Reserved––––––––0x16 (0x36)TIFR1––ICF1––OCF1B OCF1A TOV1page 129 0x15 (0x35)TIFR0–––––OCF0B OCF0A TOV0page 101 0x14 (0x34)Reserved––––––––0x13 (0x33)Reserved––––––––0x12 (0x32)Reserved––––––––0x11 (0x31)Reserved––––––––0x10 (0x30)Reserved––––––––0x0F (0x2F)Reserved––––––––0x0E (0x2E)PORTE–––––PORTE2PORTE1PORTE0page 79 0x0D (0x2D)DDRE–––––DDE2DDE1DDE0page 80 0x0C (0x2C)PINE–––––PINE2PINE1PINE0page 80 0x0B (0x2B)PORTD PORTD7PORTD6PORTD5PORTD4PORTD3PORTD2PORTD1PORTD0page 79 0x0A (0x2A)DDRD DDD7DDD6DDD5DDD4DDD3DDD2DDD1DDD0page 79 0x09 (0x29)PIND PIND7PIND6PIND5PIND4PIND3PIND2PIND1PIND0page 79 0x08 (0x28)PORTC PORTC7PORTC6PORTC5PORTC4PORTC3PORTC2PORTC1PORTC0page 79 0x07 (0x27)DDRC DDC7DDC6DDC5DDC4DDC3DDC2DDC1DDC0page 79 0x06 (0x26)PINC PINC7PINC6PINC5PINC4PINC3PINC2PINC1PINC0page 79 0x05 (0x25)PORTB PORTB7PORTB6PORTB5PORTB4PORTB3PORTB2PORTB1PORTB0page 78 0x04 (0x24)DDRB DDB7DDB6DDB5DDB4DDB3DDB2DDB1DDB0page 78 0x03 (0x23)PINB PINB7PINB6PINB5PINB4PINB3PINB2PINB1PINB0page 79 0x02 (0x22)Reserved––––––––0x01 (0x21)Reserved––––––––0x00 (0x20)Reserved––––––––Note: 1.For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory addresses should never be written.2.I/O Registers within the address range 0x00 - 0x1F are directly bit-accessible using the SBI and CBI instructions. In theseregisters, the value of single bits can be checked by using the SBIS and SBIC instructions.3.Some of the status flags are cleared by writing a logical one to them. Note that, unlike most other AVRs, the CBI and SBIinstructions will only operate on the specified bit, and can therefore be used on registers containing such status flags. The CBI and SBI instructions work with registers 0x00 to 0x1F only.4.When using the I/O specific commands IN and OUT, the I/O addresses 0x00 - 0x3F must be used. When addressing I/ORegisters as data space using LD and ST instructions, 0x20 must be added to these addresses. The AT90PWM2/2B/3/3B isa complex microcontroller with more peripheral units than can be supported within the 64 location reserved in Opcode forthe IN and OUT instructions. For the Extended I/O space from 0x60 - 0xFF in SRAM, only the ST/STS/STD and LD/LDS/LDD instructions can be used.6.Instruction Set SummaryMnemonics Operands Description Operation Flags#Clocks ARITHMETIC AND LOGIC INSTRUCTIONSADD Rd, Rr Add two Registers Rd ← Rd + Rr Z,C,N,V,H1 ADC Rd, Rr Add with Carry two Registers Rd ← Rd + Rr + C Z,C,N,V,H1 ADIW Rdl,K Add Immediate to Word Rdh:Rdl ← Rdh:Rdl + K Z,C,N,V,S2 SUB Rd, Rr Subtract two Registers Rd ← Rd - Rr Z,C,N,V,H1 SUBI Rd, K Subtract Constant from Register Rd ← Rd - K Z,C,N,V,H1 SBC Rd, Rr Subtract with Carry two Registers Rd ← Rd - Rr - C Z,C,N,V,H1 SBCI Rd, K Subtract with Carry Constant from Reg.Rd ← Rd - K - C Z,C,N,V,H1 SBIW Rdl,K Subtract Immediate from Word Rdh:Rdl ← Rdh:Rdl - K Z,C,N,V,S2 AND Rd, Rr Logical AND Registers Rd ← Rd • Rr Z,N,V1 ANDI Rd, K Logical AND Register and Constant Rd ← Rd • K Z,N,V1 OR Rd, Rr Logical OR Registers Rd ← Rd v Rr Z,N,V1 ORI Rd, K Logical OR Register and Constant Rd ← Rd v K Z,N,V1 EOR Rd, Rr Exclusive OR Registers Rd ← Rd ⊕ Rr Z,N,V1 COM Rd One’s Complement Rd ← 0xFF − Rd Z,C,N,V1 NEG Rd Two’s Complement Rd ← 0x00 − Rd Z,C,N,V,H1 SBR Rd,K Set Bit(s) in Register Rd ← Rd v K Z,N,V1 CBR Rd,K Clear Bit(s) in Register Rd ← Rd • (0xFF - K)Z,N,V1 INC Rd Increment Rd ← Rd + 1Z,N,V1 DEC Rd Decrement Rd ← Rd − 1 Z,N,V1 TST Rd Test for Zero or Minus Rd ← Rd • Rd Z,N,V1 CLR Rd Clear Register Rd ← Rd ⊕ Rd Z,N,V1 SER Rd Set Register Rd ← 0xFF None1 MUL Rd, Rr Multiply Unsigned R1:R0 ← Rd x Rr Z,C2 MULS Rd, Rr Multiply Signed R1:R0 ← Rd x Rr Z,C2 MULSU Rd, Rr Multiply Signed with Unsigned R1:R0 ← Rd x Rr Z,C2 FMUL Rd, Rr Fractional Multiply Unsigned R1:R0 ← (Rd x Rr) << 1Z,C2 FMULS Rd, Rr Fractional Multiply Signed R1:R0 ← (Rd x Rr) << 1Z,C2 FMULSU Rd, Rr Fractional Multiply Signed with Unsigned R1:R0 ← (Rd x Rr) << 1Z,C2 BRANCH INSTRUCTIONSRJMP k Relative Jump PC ← PC + k + 1None2 IJMP Indirect Jump to (Z)PC ← Z None2 RCALL k Relative Subroutine Call PC ← PC + k + 1None3 ICALL Indirect Call to (Z)PC ← Z None3 RET Subroutine Return PC ← STACK None4 RETI Interrupt Return PC ← STACK I4 CPSE Rd,Rr Compare, Skip if Equal if (Rd = Rr) PC ← PC + 2 or 3None1/2/3 CP Rd,Rr Compare Rd − Rr Z, N,V,C,H 1 CPC Rd,Rr Compare with Carry Rd − Rr − C Z, N,V,C,H1 CPI Rd,K Compare Register with Immediate Rd − K Z, N,V,C,H1 SBRC Rr, b Skip if Bit in Register Cleared if (Rr(b)=0) PC ← PC + 2 or 3 None1/2/3 SBRS Rr, b Skip if Bit in Register is Set if (Rr(b)=1) PC ← PC + 2 or 3None1/2/3 SBIC P, b Skip if Bit in I/O Register Cleared if (P(b)=0) PC ← PC + 2 or 3 None1/2/3 SBIS P, b Skip if Bit in I/O Register is Set if (P(b)=1) PC ← PC + 2 or 3None1/2/3 BRBS s, k Branch if Status Flag Set if (SREG(s) = 1) then PC←PC+k + 1None1/2 BRBC s, k Branch if Status Flag Cleared if (SREG(s) = 0) then PC←PC+k + 1None1/2 BREQ k Branch if Equal if (Z = 1) then PC ← PC + k + 1None1/2 BRNE k Branch if Not Equal if (Z = 0) then PC ← PC + k + 1None1/2 BRCS k Branch if Carry Set if (C = 1) then PC ← PC + k + 1None1/2 BRCC k Branch if Carry Cleared if (C = 0) then PC ← PC + k + 1None1/2 BRSH k Branch if Same or Higher if (C = 0) then PC ← PC + k + 1None1/2 BRLO k Branch if Lower if (C = 1) then PC ← PC + k + 1None1/2 BRMI k Branch if Minus if (N = 1) then PC ← PC + k + 1None1/2 BRPL k Branch if Plus if (N = 0) then PC ← PC + k + 1None1/2 BRGE k Branch if Greater or Equal, Signed if (N ⊕ V= 0) then PC ← PC + k + 1None1/2 BRLT k Branch if Less Than Zero, Signed if (N ⊕ V= 1) then PC ← PC + k + 1None1/2 BRHS k Branch if Half Carry Flag Set if (H = 1) then PC ← PC + k + 1None1/2 BRHC k Branch if Half Carry Flag Cleared if (H = 0) then PC ← PC + k + 1None1/2 BRTS k Branch if T Flag Set if (T = 1) then PC ← PC + k + 1None1/2 BRTC k Branch if T Flag Cleared if (T = 0) then PC ← PC + k + 1None1/2 BRVS k Branch if Overflow Flag is Set if (V = 1) then PC ← PC + k + 1None1/2 BRVC k Branch if Overflow Flag is Cleared if (V = 0) then PC ← PC + k + 1None1/2 BRIE k Branch if Interrupt Enabled if ( I = 1) then PC ← PC + k + 1None1/2 BRID k Branch if Interrupt Disabled if ( I = 0) then PC ← PC + k + 1None1/2。

单级圆柱齿轮减速器(附装配图)

《机械设计基础》课程设计说明书题目:带传动及单级圆柱齿轮减速器的设计学院:机械与电子学院专业:机械制造与自动化班级:机制19-1班学号:姓名:李俊指导教师:周海机械与电子学院2019年11月-12月目录一、课程设计任务要求 (3)二、电动机的选择 (4)三、传动比的计算设计 (5)四、各轴总传动比各级传动比 (6)五、V带传动设计 (8)六、齿轮传动设计 (11)七、轴的设计 (19)八、轴和键的校核 (30)九、键的设计 (32)十、减速器附件的设计 (34)十一、润滑与密封 (36)十二、设计小结 (37)十三、参考资料 (37)一、课程设计任务要求1. 用CAD设计一张减速器装配图(A0或A1)并打印出来。

2. 轴、齿轮零件图各一张,共两张零件图。

3.一份课程设计说明书(电子版)并印出来传动系统图如下:传动简图输送机传动装置中的一级直齿减速器。

运动简图工作条件冲击载荷,单向传动,室内工作。

三班制,使用5年,工作机速度误差±5%。

原始数据如下:二、电动机的选择三、传动比的计算设计四、各轴总传动比各级传动比计算结果汇总如下表,以供参考五、传动设计六、齿轮传动设计根据数据:传递功率P1=5.02KW电动机驱动,小齿轮转速n1=480r/min,大齿轮转速n2=166r/min,传递比i=2.90,单向运转,载荷变化不大,使用期限五年,三班制工作。

七、轴的设计主动抽1轴传动功率P2=4.77KW,转速n2=166r/min,工作单向转动轴采用深沟球轴承支撑。

八、轴和键的校核九、键的设计十、减速器附件的设计十一、润滑与密封十二、设计小结这次的课程设计,对于培养我们理论联系实际的设计思想;训练综合运用机械设计和有关先修课程的理论,结合生产实际反系和解决工程实际问题的能力;巩固、加深和扩展有关机械设计方面的知识等方面有重要的作用。

此次减速器,经过两个月的努力,终于将机械设计课程设计作业完成了。

富士通830mt 使用 中文 说明书

1部件名称和功能车身电脑1.门闩无意中锁打开显示器。

当您打开液晶显示器,删除锁定滑动到右侧。

2.液晶显示这台计算机屏幕显示。

该模型是配备触摸屏幕,触摸屏已被粘贴。

“硬件” - “在触摸”o液晶显示器的特点以下是LCD的特性。

这些都不是有瑕疵,请注意。

▪液晶显示技术,使我们非常准确,而不是光点在屏幕上的一些不,有可能点燃所有的点。

▪液晶显示器已经在这台电脑上使用,制造过程,产品的不同颜色可能会为每个。

底纹的颜色可能会出现一些其它温度。

▪后像可以继续使用相同的长远的眼光。

后像会消失,一段时间后。

为了防止这种行为,关闭显示器或使用省电功能,我们建议使用屏幕保护程序。

▪这种状况可能会出现轻微的显着点和不平衡的。

3.佩恩(触摸屏型号)存储一直与触摸笔。

“硬件” - “在触摸”4.LCD状态显示显示计算机的状态这一点。

名称“零件” - “关于LCD状态显示”5.安全按钮附加应用“安全按钮”或“一触式按键设置”可用于安装(→“软件”- “软件目录”)。

附加应用程序通过设置密码“安全按钮”,用户认证可以做到的。

陪同的应用,“一触式按键配置通过使用功能,您可以调用,只需按下一个按钮,您的电脑”。

“安全” - “按钮”安全6.电源按钮打开控制台或个人电脑,待机(挂起)/恢复(恢复)是使按钮。

o请按从04秒电源按钮。

按住〇四秒电源按钮,计算机将关闭电源。

7.扬声器PC音频书籍印刷。

“函数” - “音量设置”o音量,请调整范围从扬声器Hizumanai声音设置和声音。

造成损坏扬声器。

8.键盘键入字符可以号令到PC。

“硬件” - “在键盘上”9.无线交换机(无线局域网模式只)无线局域网通信ON和OFF。

医院和飞机,在那里,请在设备限制使用其他电子开关为OFF。

o对于无线局域网,“Kasutamumeidoopushon”手册中请。

10. 平特操纵鼠标指针。

“硬件” - “为指针。

”体表电脑1.集成无线局域网天线(无线局域网模式只)内置的无线局域网天线。

炭黑牌号分类及应用

炭黑牌号分类及应用橡胶用炭黑原来是按粒径大小来分类的,但后来改为按氮表面积分类。

此外,命名时把炭黑颜料的硫化速度和结构等因素也考虑进去了,由4个系统构成。

第一个英文字母代表胶料的硫化速度,以N代表正常硫化速度,S代表缓慢硫化速度。

后面3个为阿拉伯数字。

第一个数字代表炭黑氮表面积范围,共列为0~9个等级。

第二和第三个数字则由美国材料试验协会负责炭黑和术语的D24.41委员会指定的,反映不同的结构程度。

一、1系列ASTM名称英文缩写中文名称N110 SAF 超耐磨炉黑N121 SAF-HS-NT 新工艺高结构超耐磨炉黑N166 SAF-HS 高结构超耐磨炉黑基本特性:粒径小,表面积和着色度最高,最好的耐磨性,但加工性能差,抗龟裂及耐热性能不好,成本高,基本少用与不用应用与配合:胎面,一般在子午胎中使用较多,混炼时应注意分散和焦烧二、2系列ASTM名称英文缩写中文名称S212 ISAF-LS-SC 代槽炉黑N219 ISAF-LS 低结构中超耐磨炉黑N220 ISAF-HM 高定伸中超耐磨炉黑N231 ISAF-LM 低定伸中超耐磨炉黑N234 ISAF-HS-NT 新工艺高结构中超耐磨炉黑N242 ISAF-HS 高结构中超耐磨炉黑N270 IISAF-HS-NT 新工艺高结构中中超耐磨炉黑N285 IISAF-HS 高结构中中超耐磨炉黑N293 CF 导电炉黑N294 SCF 超导电炉黑N299 GPT 通用胎面炉黑基本特性N219能提高拉伸强度、撕裂强度和伸长率,且生热低、弹性高,但定伸应力和耐磨性有所下降。

N220有较高的综合性能。

N231定伸应力低,但有较高的拉伸强度、撕裂强度和伸长率。

N234 耐磨性本系列中最高。

N299高结构高定伸碳黑,耐磨性与N234接近,主要代替N220使用,有较好的牵引性能、较低的滚动阻力和较高的耐磨性,特别适合胎面。

应用与配合N219适用于胎面,尤其越野轮胎,以改善崩花、裂口。

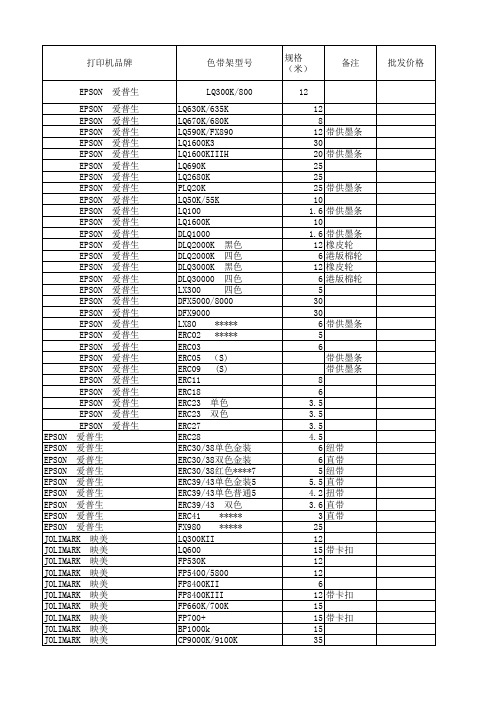

色带通用对照表

批发价格

JOLIMARK 映美 JOLIMARK 映美 JOLIMARK 映美 JOLIMARK 映美 JOLIMARK 映美 JOLIMARK 映美 JOLIMARK 映美 FUJITSU 富士通 FUJITSU 富士通 FUJITSU 富士通 FUJITSU 富士通 FUJITSU 富士通 FUJITSU 富士通 FUJITSU 富士通 FUJITSU 富士通 FUJITSU 富士通 FUJITSU 富士通 FUJITSU 富士通 FUJITSU 富士通 FUJITSU 富士通 FUJITSU 富士通 FUJITSU 富士通 FUJITSU 富士通 FUJITSU 富士通 FUJITSU 富士通 FUJITSU 富士通 FUJITSU 富士通 FUJITSU 富士通 FUJITSU 富士通 DASCOM 得实 DASCOM 得实 DASCOM 得实 DASCOM 得实 DASCOM 得实 DASCOM 得实 DASCOM 得实 DASCOM 得实 DASCOM 得实 DASCOM 得实 DASCOM 得实 DASCOM 得实 DASCOM 得实 DASCOM 得实 DASCOM 得实 DASCOM 得实 DASCOM 得实 DASCOM 得实 DASCOM 得实 DASCOM 得实 DASCOM 得实 DASCOM 得实 DASCOM 得实 DASCOM 得实 OKI 冲电气

打印机品牌

EPSON 爱普生

EPSON 爱普生 EPSON 爱普生 EPSON 爱普生 EPSON 爱普生 EPSON 爱普生 EPSON 爱普生 EPSON 爱普生 EPSON 爱普生 EPSON 爱普生 EPSON 爱普生 EPSON 爱普生 EPSON 爱普生 EPSON 爱普生 EPSON 爱普生 EPSON 爱普生 EPSON 爱普生 EPSON 爱普生 EPSON 爱普生 EPSON 爱普生 EPSON 爱普生 EPSON 爱普生 EPSON 爱普生 EPSON 爱普生 EPSON 爱普生 EPSON 爱普生 EPSON 爱普生 EPSON 爱普生 EPSON 爱普生 EPSON 爱普生 EPSON 爱普生 EPSON 爱普生 EPSON 爱普生 EPSON 爱普生 EPSON 爱普生 EPSON 爱普生 EPSON 爱普生 EPSON 爱普生 EPSON 爱普生 JOLIMARK 映美 JOLIMARK 映美 JOLIMARK 映美 JOLIMARK 映美 JOLIMARK 映美 JOLIMARK 映美 JOLIMARK 映美 JOLIMARK 映美 JOLIMARK 映美 JOLIMARK 映美

MT90883中文资料

1Features•WAN interface, consisting of 32 input and output streams at 2.048 or 8.192Mbs •Up to 1024 bi-directional 64Kbs channels •N * 64Kbs trunking of channels across any stream and channel •1K by 1K non-blocking TDM switch •Local TDM interface, with 32 streams at 2.048, 4.096 and 8.192Mbs •Flexible, multi-protocol packet encapsulation •Dual 100Mbs MII interfaces for redundancy or for load balancing •Quality of service features, including weighted fairqueuing, strict priority and queue size limitthresholds•High performance 33MHz / 66MHz 32 bit PCIbus•Integral Stratum 4E PLL for synchronisation to theTDM domain•Power consumption of less than 0.75W Applications •Packet backplane interconnection •Circuit Emulation over packet domain •Internet Off-load •Remote Access Concentrators •H.100/H.110 extension and expansion December 2004Ordering Information MT90880B/IG/BP1N 456 ball PBGA MT90881A/IG/BP1N 456 ball PBGA MT90882B/IG/BP1N 456 ball PBGA MT90883A/IG/BP1N 456 ball PBGA -40°C to +85°C MT90880/1/2/3TDM to Packet ProcessorsData SheetFigure 1 - MT90880 High Level OverviewDescription The MT9088x is a family of highly functional TDM to Packet bridging devices. It provides a bridge between a WAN environment based on constant bit rate TDM streams and a packet domain based on Ethernet technology.It is capable of assembling user-defined packets of TDM traffic from the WAN Access Interface and transmitting them from the Ethernet interfaces using a variety of protocols. If external processing is required (e.g., HDLC or modem termination) the traffic can be switched to a local interface using the internal TDM switch.Packets received from the Ethernet interfaces are parsed to determine the egress destination, and are appropriately queued either to the WAN Access Interface or to the PCI interface. An integrated DMA controller is used to transfer packets to and from the PCI interface with a minimum of CPU intervention.VariantsThere are four device variants in the MT9088x family:•MT908801024 bi-directional channels, integral TDM switch •MT908811024 bi-directional channels, no TDM switch •MT90882256 bi-directional channels, integral TDM switch •MT90883256 bi-directional channels, no TDM switchTable 1 - Variant OptionsRelated DocumentsThis data sheet should be read in conjunction with the following related documents and application notes:Table 2 - Related Documents FeatureMT90880MT90881MT90882MT90883No. of WAN streams323288Local PortYes No Yes No No. of Available Channels10241024256256TDM Switch AvailabilityMaster mode only Not Available Master mode only Not Available PCI Interface33 / 66 MHz 33 / 66 MHz 33 / 66 MHz 33 / 66 MHz MII InterfaceYes Yes Yes Yes RMII InterfaceYes Yes Yes Yes JTAG Yes Yes Yes YesTitleAuthor Document Number Issue / Date 1. MT9088x Programmers ModelZarlink DM5708 1.0, Aug. 20022. MT9088x API User GuideZarlink DM5805 1.0, Sept. 20023. MSAN-198 - Performing Clock Recovery for CircuitEmulation when using the MT90880Zarlink AN57891, Aug. 20024. MSAN-199 - Unstructured Circuit Emulation Using theMT90880Zarlink AN57901, Aug. 20025. MSAN-200 - MT90880 TDM Replacement PacketBackplane Zarlink AN57911, Aug. 2002The following external documents and standards are referenced in this data sheet:Table 3 - Referenced Documents TitleAuthor Document Number Issue / Date 1.Local and Metropolitan Area Networks, Part 3: Carriersense multiple access with collision detection(CSMA/CD) access method and physical layer specifi-cationsIEEE IEEE 802.3u 19952.PCI Local Bus SpecificationPCI SIG 2.23.RMII TM SpecificationRMII consortium Rev 1.2, March 19984.Test Access Port and Boundary Scan ArchitectureIEEE IEEE 1149.119905.Circuit Emulation Service Interoperability SpecificationATM Forum af-vtoa-0078Ver 2.0, Jan. 19976.Specifications of (DBCES) Dynamic Bandwidth Utiliza-tion - in 64 KBPS Time Slot Trunking over ATM - UsingCESATM Forum af-vtoa-0085July 19977.ST-BUS Generic Device SpecificationMitel MSAN-126Rev. B, June 19958.H.110 Hardware Compatibility Specification: CT BusECTF Rev. 1.0, 19979.H-MVIP StandardGO-MVIP Rel. 1.1a, Jan. '9710.Clocks for the Synchronized Network: Common Generic Cri-teria TelcordiaGR-1244-CORE Iss. 2, Dec. 200011.The Control of Jitter and Wander within digital networks which are based on the 2048 Kbs hierarchy ITU-TG.823200012.The Control of Jitter and Wander within digital networkswhich are based on the 1544 Kbs hierarchy ITU-T G.82420001.0 Changes Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .102.0 Physical Specification. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .113.0 External Interface Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .123.1 WAN Access Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .123.2 Local TDM Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .133.3 Packet Interfaces. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .143.3.1 MII Interfaces. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .143.3.2 RMII Interfaces. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .153.4 PCI Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .163.5 External Memory Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .173.6 System Control Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .183.7 Test Facilities. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .183.7.1 JTAG Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .183.7.2 Test Facility . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .183.7.3 Test Operating Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .193.8 Power and Ground Connections. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .204.0 Typical Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .204.1 Packet Backplane Interconnection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .204.2 Circuit Emulation Services. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .214.3 Internet Off-load. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .224.4 Remote Access Concentration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .234.5 Local Resource Pool Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .244.6 H.100/H.110 Extension . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .254.7 H.100/H.110 Expansion. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .255.0 Functional Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .265.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .265.2 Basic Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .285.2.1 WAN Access Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .285.2.2 Packet Transmission . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .295.2.3 CPU Packet Generation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .295.2.4 Packet Reception. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .295.2.5 Call Setup and Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .295.3 Data and Control Flows. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .305.4 Packet Assembly. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .345.4.1 Payload Order . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .345.4.2 Packet Structure. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .355.4.3 Context Descriptor Protocol. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .365.5 Context Negotiation and Establishment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .365.5.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .365.5.2 New Context Establishment. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .375.5.3 Context Modification (Addition or deletion of physical channels). . . . . . . . . . . . . . . . . . . . . . . . . . .385.5.4 Context Removal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .395.5.5 Context Cleardown. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .396.0 Functional Block Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .406.1 WAN Interface and Multiplexers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .406.1.1 Port Data Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .406.1.2 Operational Modes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .416.2 TDM Cross-Connect Switch . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .456.2.1 Multiplexing and Blocking. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .466.2.2 Re-ordering Timeslots . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .466.2.3 Channel Broadcast. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .476.3 WAN Receive and Transmit Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .476.4 Operation of the WAN Receive Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .486.4.1 Context Control in the WAN Receive/Transmit Controllers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .486.4.2 Jitter Buffer Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .506.5 Queue Manager. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .526.5.1 Queues to the Packet Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .526.5.2 Queues to PCI Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .546.5.3 Queues to WAN Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .546.6 Packet Transmit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .556.6.1 Protocol Stacks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .556.6.2 Shadow Headers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .566.7 Ethernet MAC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .566.8 Packet Classification. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .576.8.1 Pattern Matching . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .576.8.2 Example Classification Scheme. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .596.9 Memory Management Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .636.9.1 External Memory Requirements. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .646.9.2 Granule Structure. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .646.9.3 Connecting the MT9088x to External Memory. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .646.9.4 External Memory Interface Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .676.10 PCI Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .686.10.1 Address and Data Width support. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .686.10.2 Target Transaction Support. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .696.10.3 Master Support. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .696.10.4 Configuration and Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .696.10.5 Signalling Environment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .706.10.6 Open Drain Circuitry. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .716.11 DMA Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .716.11.1 DMA Descriptor Rings and Lists . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .726.11.2 Data Transfer from CPU to MT90880 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .736.11.3 Data Transfer from MT90880 to CPU . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .736.12 Board Level Test Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .746.12.1 JTAG Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .746.12.2 Test Access Port (TAP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .756.12.3 Test Access Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .756.13 DPLL Specification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .766.13.1 Master Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .766.13.2 Slave Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .786.13.3 Free-run Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .786.13.4 DPLL Performance Parameters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .797.0 Memory Map and Register definitions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .798.0 Special Note to Users: MT9088x handling of received corrupted Ethernet packets and dealing with the next valid packet . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .798.1 Issue . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .798.2 Recommendation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .809.0 DC Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .809.0.1 Input Levels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .829.0.2 Output Levels. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8210.0 AC Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8310.1 WAN Access Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8310.1.1 Slave Clock Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8310.1.2 Clock Master Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8510.2 Local TDM Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8610.3 Packet Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8810.3.1 MII Transmit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8810.3.2 MII Receive . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8910.3.3 RMII Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9010.4 External Memory Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9010.5 System Control Port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9310.6 JTAG Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9311.0 Glossary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .95Figure 1 - MT90880 High Level Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Figure 2 - Package View and Ball Positions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Figure 2 - Multiservice Access Platform using the MT90880. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21 Figure 3 - Circuit Emulation Services over the packet network . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22 Figure 4 - Internet Off-load solution using the MT90880 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22 Figure 5 - Remote Access Concentrator using the MT90880 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23 Figure 6 - Use of a Local Resource Pool. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24 Figure 7 - H.100/H.110 Extension over Ethernet link. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25 Figure 8 - H.100/H.110 Expansion using Ethernet Switching Fabric. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26 Figure 9 - MT9088x Family Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27 Figure 10 - MT90880 Data and Control Flows. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28 Figure 11 - WAN to Packet Data and Control Flow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30 Figure 12 - Packet to WAN Data Flow. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31 Figure 13 - WAN to Packet Data Flow via Local Resource . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32 Figure 14 - Packet to WAN Data Flow via Local Resource . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33 Figure 15 - PCI to Packet Data Flow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33 Figure 16 - Packet to PCI Data Flow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34 Figure 17 - Channel and stream order for packet formation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35 Figure 18 - Packet Structure for MT9088x Family. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36 Figure 19 - Context Descriptor Field . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36 Figure 20 - Connecting to Framers in Synchronous Master Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42 Figure 21 - Connecting to an H.100/H.110 Backplane in Synchronous Slave Mode. . . . . . . . . . . . . . . . . . . . . . . 43 Figure 22 - Connecting Framers to the MT90880 in Asynchronous Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44 Figure 23 - TDM Switch Access Multiplexers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45 Figure 24 - Operation of the WAN Receive Controller. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48 Figure 25 - Context Look-Up Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49 Figure 26 - Packet Classification Process. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58 Figure 27 - PDV Supported for Different Memory and Packet Payload Sizes. . . . . . . . . . . . . . . . . . . . . . . . . . . . 64 Figure 28 - Connecting the MT90880 to a Single External Memory Device . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65 Figure 29 - Connecting the MT90880 to Multiple External Memory Devices. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67 Figure 30 - MT90880 Memory and Register Space Organization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70 Figure 31 - pci_serr#, pci_inta# Open Drain Circuitry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71 Figure 32 - DMA Transfer to/from System Memory. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71 Figure 33 - Descriptor Ring Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72 Figure 34 - Descriptor List Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73 Figure 35 - DMA Operation from CPU Packet Queues . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74 Figure 36 - DPLL Jitter Transfer Function Diagram Across a Wide Range of Frequencies. . . . . . . . . . . . . . . . . . 77 Figure 37 - Detailed DPLL Jitter Transfer Function Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78 Figure 38 - WAN Bus Slave Mode Timing at 2.048 Mbs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83 Figure 39 - WAN Bus Slave Mode Timing at 2.048 Mbs Generic E1 Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84 Figure 40 - WAN Bus Slave Timing at 8.192 Mbs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84 Figure 41 - WAN Bus Clock Master Mode Timing at 2.048 Mbs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85 Figure 42 - WAN Bus Clock Master Mode at 2.048 Mbs - Generic E1 Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86 Figure 43 - WAN Bus Clock Master Mode Timing at 8.192Mbs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86 Figure 44 - Local Bus Timing at 2.048 Mbs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87 Figure 45 - Local Bus Timing at 4.096Mbs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87 Figure 46 - Local Bus Timing at 8.192 Mbs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88 Figure 48 - MII Port Receive Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89。

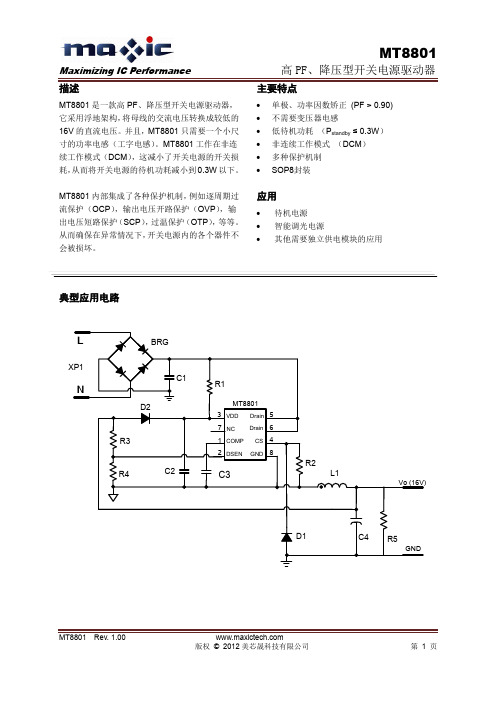

MT8801规格书-中文_Rev1.00

芯片标记:

MT8801 YY WW xxxx

生产内部代码 生产周代码 生产年代码

管脚描述

Name Pin No.

COMP

1

DSEN

2

VDD

3

CS

4

DRAIN 5,6

NC

7

GND

8

Description 内部误差放大器的输出引脚。用一个电容将其与地串联实现频率补偿。 输出电压的反馈引脚。 供给电压引脚。 内部 MOSFET 的源极,同时用来检测源极电流。 内部 MOSFET 的漏极。 无连接。 芯片地。

应用

待机电源 智能调光电源 其他需要独立供电模块的应用

典型应用电路

L

XP1

N

BRG

C1 D2

R3

R4

C2

R1

MT8801 3 VDD Drain 5 7 NC Drain 6 1 COMP CS 4 2 DSEN GND 8

C3

R2 L1

Vo (16V)

D1

C4 R5

GND

MT8801 Rev. 1.00

第6页

Maximizing IC Performance

MT8801

高 PF、降压型开关电源驱动器

索取产品详细信息及样片申请,请联系:

美芯晟科技有限公司 (北京办公室) 北京市海淀区知春路 106 号,皇冠假日酒店写字楼 1006。邮政编码 100086 电话: 86-10-62662828 传真: 86-10-62662951

版权 © 2012 美芯晟科技有限公司

第1页

Maximizing IC Performance 极限参数

VDD 引脚电压 Drain 引脚电压 COMP/CS/DSEN 引脚电压 焊接温度 (10 秒) 存储温度

MT9082 系列中文资料安立

电池工作时间长 在任何您需要电源的地方,特别是在光纤架

上,MT9082在一次充电后一般可连续工作至少 8小时。从而保证MT9082可在任何您需要的时 候做好准备。

便携性 MT9082 的 轻 便 设 计 和 友 好 的 用 户 尺 寸 非

常适合于室外现场的工作环境,并且方便单手的 控制。当客户需要乘车到测试现场时,仪表的背 包提供了良好 的便携性。

网络的验收测试和一般网络的测试有以下两个区别:

1)由于 PON 网络比一般的光纤网络多了一个 1490nm 的波长,因此和一般的光纤验收测

试的区别之一是 1490nm 波长的测试;由于 1490nm 波长(0.21dB/Km)和 1550nm 波长的损

耗(0.19dB/Km)差别比较小,因此一些地方并不要求 1490nm 波长的测试,目前国内在验收测

7

2)测试是从 OLT 或是 ONU 端来进行 从目前的测试情况来看,可以从 OLT 或从 ONU 来进行维护测试,从 OLT 端进行测试,需 要事先在 OLT 侧集成光耦合器,其好处是可以从整体上来判断光纤线路的状况,如下图,每 一个反射峰代表一个光分路器的分支。

如果从 ONU 侧进行测试,需要在 OLT 端集成滤波器,能够过滤掉 1650nm 或 1625nm 波长 的光。在 ONU 端测试的好处是可以比较好的测试接入光纤的状况,测试更具有针对性。

试时是否要测试 1490nm 的波长还没有统一的标准,很多地方都使用 1310/1550nm 双波长的

OTDR 进行测试。

2)由于 PON 网络比一般的网络增加了光分路器,在测试时,需要穿透光分路器进行测

试,就需要有专门的测试模式支持光分路器的测试。目前从 OLT 到分路器 的光纤的长度一

MB89890资料

s PRODUCT LINEUP

Part number Item

MB89898

MB89899

MB89P899 One-time product OTPROM product 60 K × 8 bits (internal OTPROM) 2.0 K × 8 bits 8 bits 1 to 3 bytes 1, 8, 16 bits 136 Internal

approximately 1208 bps, approximately 2415 bps modem output 16 21 bits 15 bits Watch mode, subclock mode, sleep mode, stop mode CMOS 2.2 V to 6.0 V 2.7 V to 6.0 V MBM27C512-20TV

P97/INT27 P96/INT26 P95/INT25 P94/INT24 P93/INT23 P92/INT22 P91/INT21 P90/INT20 P87 P86 P85 P84 P83 P82 P81 P80 P77 P76 P75/BSO2 P74/BSI2 P73/BSK2 VSS P72/SO2 P71/SI2 P70/SK2 P67/BSO1 P66/BSI1 P65/BSK1 P64 P63/MSKO

s FEATURES

• • • • • • • • • • • • F2MC-8L family CPU core Dual clock control system Maximum memory size: 64 Kbytes Minimum execution time: 0.5 µs at 8 MHz Interrupt processing time: 4.5 µs at 8 MHz I/O ports: Max 85 ports 21-bit time-base counter 8-bit PWM timer DTMF generator 8/16-bit timer 8-bit serial I/O Serial I/O with 1-byte buffer

MD随身听最全解读

末代MD传序(参考了墨索里尼传记写法)在20世纪末至21世纪初的随身音频产品中,有哪一种随身听可以让看过它的人对于它的外观赞不绝口?有哪一种随身听引来了无数的口水,无论是批判还是追捧?有哪一种随身听能轻易的播放上百小时甚至数百小时的音乐?有哪一种随身听敢同时号称“世界最小”、“世界最轻量”、“播放时间世界最长”、“世界最薄”、“日本制造”、“播放时间宇宙最长”、“高音质”等诸多称号?有哪一种随身听能与任何音频设备都建立(模拟或者数字)连接?有哪一种随身听同时又用磁头又用光头?有哪一种随身听有数十种、数十类纪念版本?有哪一种随身听备有七彩灯?有哪一种随身听总是不乏新品(至少是在那段时间)?哪一种随身听敢直接从素质上蔑视其他一切对手(NET MD曾被称为MP3的终结者)?哪一种随身听在最繁荣的时期都却乏唱片的支持?哪一种随身听的音乐都是自己精心制作出来的?这些问题可能有些令人感到惊讶,但是所有这些问题的答案都是——MiniDisc,MD!从1992年(又或者说是1999年,这个时候MD才在大陆兴起)到2006年,它是市场上一枝独秀。

总是有些人认为MD其实是一个失败品,正如一些“标准”的随身听发烧友所说的:“MD音质比不过CD,体积比不过MP3。

” 但是,我可以告诉这些人,你们的观点是完全错误的。

不仅仅只是你们以长比短(请问您怎么不拿MD和CD比体积,或者和MP3比音质呢),更因为你们的说法彻底错误!“MD在随身听上的音质足以压倒一切CD随身听(不包括砖块),在体积方面虽然大于闪存MP3,但比硬盘MP3还是要小的多(直到今天也是)!”正文很早就想写篇关于MD的帖子,但由于本人的惰性,一直拖到了2007年7月,后来由于在论坛发生意外,故直到今天才算是初步完工,在接下来的一个月里,本人将继续对此帖完善和更新(主要针对MD的照片,JVC MD和同时代日本市场上的MP3)。

希望本帖能弥补网上关于MD资料的不足,并给MD爱好者一个参考。

铃流检测、模拟摘挂机及DTMF收号器电路板制作

铃流检测、模拟摘挂机及DTMF收号器电路板制作生产实习报告1.实习意义作为计算机专业的学生,不光对软件知识有深度的掌握,拥有过强的编程能力,同时还要把硬件知识学好,因为软件是基于硬件的基础上发挥其作用,学好硬件使我们对软件的认识将更深一步。

大一大二我们更多的在学习理论知识,而比较少实践,这不利于我们的动手能力提高,所以这学期开设的这门课,不管是从专业知识还是从动手能力来看都会让我们收获很多,我们有必要把这门课学好:(1)通过生产实习,可激发对专业课学习的迫切要求,增强学生的学习积极性,培养学生针对实际生产过程的思维、观察能力,达到知识点的融会贯通。

(2)该课程可以使学生接触生产、科研、企业管理等实际业务,达到理论与实践相结合,加深对专业的认识,拓宽知识面,提高分析问题和解决问题的实际能力。

(3)生产实习是计算机科学与技术专业教学计划中十分重要的实践性教学环节,是在学生已学习了部分专业课后进行的一个理论联系实际的实践性教学环节,也是学生从学校走向生产岗位的第一步。

2. 总体设计2.1 主要解码芯片MT8870DTMF信号的解码模块是将接收的两个叠加的正弦波模拟信号通过解码变成二进制信号,同时解码电路还具有判断功能,判断DTMF信号是否发送,再将解码的二进制信号传送到单片机。

MT8870主要用于程控交换机、遥控、无线通信及通播系统,实现DTMF信号的分离滤波和译码功能,输出16种频率组合而成的四位并行二进制码。

MT8870具有拨号音抑制和模拟信号输入可调功能,所以在设计MT8870 DTMF解码电路时候,只需外加一些阻容元件即可。

MT8870是一种带呼叫进展过滤器的单片双音多频收发器。

它包括一个带增益可调放大器的DTMF 接收器和一个DTMF 发送器。

其中滤波电路采用高频群和低频群两个六阶开关电容通滤波器,解码采用数字计数器技术来确定输入的DTMF 音频的频率,并将其译成标准的四位二进制码。

发送器采用开关电容D/A 变换器。

MT8880中文资料及其应用程序,应用电路

MT8880中文资料及其应用程序,应用电路双音多频信号(DTMF)是由一组低音频信号和一组高音频信号以一定方式的组合构成,每组音频信号各有4个音频信号,而每种组合有一个高音频信号和一个低音频信号,共16种组合。

过去主要用于电话拨号信息传输,具有很强的抗干扰能力。

目前市场上销售的DTM F专用芯片集编解码于一体,MT8880具有收发功能。

本文通过89C51单片机控制MT8880实现计算机间的远距离数据传输。

1DTMF技术介绍1.1DTMF信号介绍DTMF信号的产生原理:双音频信号是2个正弦波信号的叠加,选定2个频率f1和f2后可得到这种信号的数学表达式:f(t)=A.sin(2.pi.f1.t)+A.sin(2.pi.f2.t)如果用合适的采样频率对这个信号进行A/D转换,则很容易计算出每一个采样点的A/D 值,而如果将这些采样值形成一张表,在单片机里用同样的采样频率将这张表中的数值用D /A转换器输出,就是双音频信号。

在实际应用中常用1 b的DM编码来实现A/D和D /A过程,其中A/D过程可以在PC机上完成,用程序生成对应每一个DTMF信号的D M编码表,D/A过程在单片机上完成。

与单音编码不同,DTMF信号是采用八中取二的方式来构成一个音频信号,由虚假信号的干扰,所以应用范围特别广泛。

对照表1可以发现DTMF信号由2个不同的频率信号合成。

分为高频组和低频组,包各含有4个频率,可以构成16种不同的信号,依次对应着16个不同的BCD码。

1.2MT8880介绍MT8880C是一个带有呼叫处理滤波器的单片DTMF信号收发器。

他的制造采用MITEL公司的低功耗、高稳定性的ISO-CMOS技术。

DTMF信号的接收部分采用DTMF信号接收单片机MT8870的工业制造标准;发送部分采用开关电容进行D/A转换发送高精度、低畸变的DTMF信号。

内部寄存器提供一个群模式。

在双音频群模式下DTMF信号可以通过精确的时序被发送出去。

880NM中文资料

430

470

525

555

565

590

595

nm

Spectral line half-width

IF=20mA

65

30

40

30

30

35

15

nm

Capacitance

VF=0V, f=1MHz

100

50

50

45

45

10

33

pF

Telephone: 781-935-4442 Fax: 781-938-5867

ቤተ መጻሕፍቲ ባይዱ

2.6

2.5

2.5

2.5

2.5

1.7

1.5

V

Reverse Current

VR=5V

10

10

10

10

10

10

10

uA

Wavelength at Peak Emmission

IF=20mA

610

620

625

660

700

880

940

nm

Spectral line half-width

IF=20mA

35

15

45

20

45

50

50

nm

Capacitance

VF=0V, f=1MHz

15

40

12 LEDs

95

40

90

90

pF

86

Telephone: 781-935-4442 Fax: 781-938-5867

sales@ Engineering Catalog 169

625nm (GaAsP/ GaP)

MD随身听最全解读

末代MD传序(参考了墨索里尼传记写法)在20世纪末至21世纪初的随身音频产品中,有哪一种随身听可以让看过它的人对于它的外观赞不绝口?有哪一种随身听引来了无数的口水,无论是批判还是追捧?有哪一种随身听能轻易的播放上百小时甚至数百小时的音乐?有哪一种随身听敢同时号称“世界最小”、“世界最轻量”、“播放时间世界最长”、“世界最薄”、“日本制造”、“播放时间宇宙最长”、“高音质”等诸多称号?有哪一种随身听能与任何音频设备都建立(模拟或者数字)连接?有哪一种随身听同时又用磁头又用光头?有哪一种随身听有数十种、数十类纪念版本?有哪一种随身听备有七彩灯?有哪一种随身听总是不乏新品(至少是在那段时间)?哪一种随身听敢直接从素质上蔑视其他一切对手(NET MD曾被称为MP3的终结者)?哪一种随身听在最繁荣的时期都却乏唱片的支持?哪一种随身听的音乐都是自己精心制作出来的?这些问题可能有些令人感到惊讶,但是所有这些问题的答案都是——MiniDisc,MD!从1992年(又或者说是1999年,这个时候MD才在大陆兴起)到2006年,它是市场上一枝独秀。

总是有些人认为MD其实是一个失败品,正如一些“标准”的随身听发烧友所说的:“MD音质比不过CD,体积比不过MP3。

” 但是,我可以告诉这些人,你们的观点是完全错误的。

不仅仅只是你们以长比短(请问您怎么不拿MD和CD比体积,或者和MP3比音质呢),更因为你们的说法彻底错误!“MD在随身听上的音质足以压倒一切CD随身听(不包括砖块),在体积方面虽然大于闪存MP3,但比硬盘MP3还是要小的多(直到今天也是)!”正文很早就想写篇关于MD的帖子,但由于本人的惰性,一直拖到了2007年7月,后来由于在论坛发生意外,故直到今天才算是初步完工,在接下来的一个月里,本人将继续对此帖完善和更新(主要针对MD的照片,JVC MD和同时代日本市场上的MP3)。

希望本帖能弥补网上关于MD资料的不足,并给MD爱好者一个参考。

技能培训常用模拟器件介绍

技能培训常用模拟器件介绍

MOS管全桥驱动电路

技能培训常用模拟器件介绍

光耦

光耦合器一般由三部分组成:光的发射、光的接 收及信号放大。输入的电信号驱动发光二极管 (LED),使之发出一定波长的光,被光探测器 接收而产生光电流,再经过进一步放大后输出。 这就完成了电—光—电的转换,从而起到输入、 输出、隔离的作用。由于光耦合器输入输出间互 相隔离,电信号传输具有单向性等特点,因而具 有良好的电绝缘能力和抗干扰能力。又由于光耦 合器的输入端属于电流型工作的低阻元件,因而 具有很强的共模抑制能力。所以,它在长线传输 信息中作为终端隔离元件可以大技能大培训常提用模高拟器件信介绍噪比。

• 可以用于升压、降压,小功率场合。包括电路里 的高转低等

• 基准为1.25V • 设计输出电压时, • 5脚按1.25V计算 • DIP8封装

技能培训常用模拟器件介绍

MC34063应用

技能培训常用模拟器件介绍

运放类

• 1、NE5534(双好) • 2、NE5532(双好) • 3、LM358(双) • 4、LM353(双) • 5、UA741(普通单) • 6、TL082(TL084)(双、四高阻) • 7、LM324(最常用四运放) • 8、仪表放大器

技能培训常用模拟器件介绍

常用三极管

• S9012 通用三极管 PNP,0.5A,25V,0.625W,150MHz,β=64~300 S9013 通用三极管 NPN,0.5A,25V,0.625W,150MHz,β=64~300 S9014 通用三极管 NPN,0.1A,45V,0.4W,150MHz,β=60~1000 S9015 通用三极管 PNP,0.1A,45V,0.4W,150MHz,β=60~1000 C1815 通用三极管 NPN,0.15A,50V,0.4W,80MHz,β=70~700 C945 通用三极管 NPN,0.15A,50V,0.4W,200MHz,β=70~700 S8550 通用三极管 PNP,0.5A,25V,0.625W,150MHz,β=85~300 S8050 通用三极管 NPN,0.5A,25V,0.625W,150MHz,β=85~300 2N5401 通用三极管 PNP,0.6A,150V,100MHz,β=80~250 2N5551 通用三极管 NPN,0.3A,160V,300MHz,β=80~250 D882 通用三极管 NPN,3A,30V,90MHz,β=60~400 IRF840 通用场效应管 N沟道增强型,8A,550V,125W,0.85Ω,TO-220封装 IRFP440 通用场效应管 N沟道增强型,8A,550V,125W,0.85Ω,TO-3P封装 37 IRF9642 通用场效应管 P沟道增强型,9A,200V,125W,0.7Ω,TO-220封装 IRFP9242 通用场效应管 P沟道增强型,9A,200V,125W,0.7Ω,,TO-3P封装

MB90F883S资料