AD401M42VSB-5中文资料

LED Strobe USER MANUAL ST-401说明书

LED Strobe USER MANUALST-401CATALOG1.Safety Warning (1)2. Technical Specification (4)3. Hanger Installation (5)4. Dimension (5)5. Channel function (6)6.Technical Specification (9)1.Safety WarningWarning : This product is only for professional use, not for domestic use!ST-401 Causes of injury or severe trauma may be caused by light, heat,collision, ultraviolet or falling.lmportant statementsEvery person involved with the installation, operation and maintenance of this devicehas to know:1)This product must be installed by a qualified professional.2)This product left the place of manufacture in perfect condition. In order tomaintain this condition and for safe operation, the user must always follow theinstructions and safety warnings described in this user manual.3)Manufacturer will not with responsibility for those operations not according to thisInstruction.4)Do not connect power cable of other electric products with this unit.5)Do not connect DMX512 Signal cable of other electric products with this unit.6)Always make sure that you are connecting to the proper voltage, and that the linevoltage you are connecting to is not higher than that stated on the decal or rear panel of the fixture.7)Always ground (earth) the fixture electrically.8)During long periods of non-use, disconnect the unit’s main power.9)Do not place the lamp in a damp place.10)Lamp damage or life expires, to replace the lamp in time. Before replacing the lampor fuse, turn off the power for 1 minute.11)Before opening the lamp or servicing it, make sure that the power is disconnectedand wait about fifteen minutes until the fixture is complete12)cool down.13)Do not bypass the fuse, replace the broken fuse, the fuse must be the same size fuse.14)Make sure the power cord is not curled or broken by sharp objects.15)Always check the equipment and power cord.16)Do not use the lamps and lanterns when the lightning strikes, and disconnect thepower,17)Do not open the back cover, there is no available accessories18)Maximum operating ambient temperature 40 ° C (104 ° F). Do not use the lamp whenthe glass front cover is open or damaged.19)Where to use lamps must be well ventilated. Do not look directly at the light source,because sensitive people may cause epilepsy (especially for patients with epilepsy).20)Please do not use the staircase near the use of the need to inform the strobe lightis to make use of its harmful.21)Make sure there are no items in the range of 1 M (39 in.) Of the lamp. Nopermissible items (such as cloth, wood, paper, etc.) in the range of 0.5M (20 inches) are allowed to reach a maximum temperature of 120 ° C (248 ° F), allow the lamp to cool for at least 15 minutes before touching the lamp.22)Lamps can not be covered by objects within 0.3 meters. When the lamp hanging on topof the ground, you must verify that the above can withstand 10 times the weight of the device hanging. To ensure that the external protection, rope, hardware safe and secure, and then use one or more protective measures to be protected. Installation:WARNING: Please read the safety instructions carefully before installation1.Put the light hook on the hole of the lamp handle.2.Install the light hook with light on the truss and lock it.e safety rope to hold the lamp and and truss to prevent the lamp from falling。

四門控制器 RC5401 快速安裝指南说明书

面板LED 燈號 PCB 接點及Jumper跳線LED 燈號 顯示說明Jumper 跳線說明出廠設定 PWR 正常情況持續閃爍表CPU 有在正常運作 JP5 DI 外部或控制器內部供電切換 控制器內部供電 COM 未接卡機約每秒閃爍一次,接卡機閃爍速度變快JP6 設定繼電器(RELAY)是否由控制器供電控制器不供電 10M 當網路(LAN)通訊速率為10Mbps 時會亮燈 閉路(Close)表示由控制器供12VDC 電源100M 當網路(LAN)通訊速率為100Mbps 時會亮燈 JP7~JP12 繼電器(RELAY) NC 或NO 切換Normal Open DI1~DI8 當燈亮時表示該輸入接點導通JP15 韌體AP 是否啟用,開路(Open)表示啟用 韌體AP 啟用 RY1~RY6當燈亮時表示其對應之輸出接點繼電器作動後側板接點 接線說明接點及按鈕 接線說明C+ DI 外部電源輸入 (注意事項8) RESET 長按10秒控制器重置回出廠設定 DI1~DI4 出門按鈕接點對應1~4門點 預設IP 位址:10.0.50.100 DI5~DI8 火災發報接點對應1~4門點 COM RS485(2線/4線)串接讀卡機使用 G控制器共地接點 (注意事項8) LAN RJ45網路接線RY1+~RY4+ 外部電源輸入接點對應1~4門的電鎖使用DC JACK 控制器電源輸入(12VDC) RY1-~RY4-電源輸出至1~4門的電鎖使用PWR控制器電源輸入(12VDC)注意事項1. 控制器請使用12VDC 供電,允許的輸入電壓為9VDC~13VDC;控制器輸入電源,DC JACK 與端子接點(PWR)兩者擇一2. 控制器若斷電超過24小時,系統時鐘需重新設定3. 控制器韌體版本必須與讀卡機相符方可正常使用;版本ATOP 4Door ATT 是Atop 讀卡機使用,ATOP 4Door SOYAL 是Soyal 讀卡機使用4. 讀卡機RS-485 ID1~ID4為進入卡機,ID5~ID8為出門卡機5. 讀卡機的通訊線路建議使用22AWG 具Shielding 防護之雙絞線材;以一進一出方式串接卡機6. 電鎖的電源與控制器的電源分開供電,避免電鎖作動瞬間影響控制器7. 訊號傳輸線與電源線建議分開配管,避免訊號干擾8.當JP5切換使用"C+"外部電源時,勿使用"G"接點作為共地接點,應使用DI 外部電源之地電壓當迴路地控制器與HID卡機、AR1200韋根轉換器、電鎖建議接線圖控制器與卡機、電鎖建議接線圖電鎖由卡機控制接線圖控制器進出管制接線圖注意事項1. 電鎖及出門按鈕由控制器直接控制,安全性較高2. 若為節省佈線,可將電鎖及出門按鈕由轉換器控制3. 電鎖繼電器的NC/NO依電鎖型式決定,一般的陽極鎖或磁力鎖為NC4. 電鎖的電源建議獨立供電5. 電鎖建議外加一個反向二級體(1N4001)保護電路注意事項1. 進讀卡機的RS-485 ID為1~4,出讀卡機的RS-485 ID為5~82. 電鎖及出門按鈕由控制器直接控制,安全性較高3. 若為節省佈線,可將電鎖及出門按鈕由進讀卡機控制4. 電鎖繼電器的NC/NO依電鎖型式決定,一般的陽極鎖或磁力鎖為NC5. NC/NO使用控制器PCB之JUMPER JP7~JP10跳線6. 電鎖的電源建議獨立供電7. 電鎖建議外加一個反向二級體(1N4001)保護電路RS485 D+RS485 D-出門按鈕V+DI1DI COMVIN+NC1COM1To Vout+To Vout-控制器Wiegand注意事項1. 電鎖及出門按鈕由卡機控制,可節省佈線,但安全性較低2. 電鎖繼電器的NC/NO依電鎖型式決定,一般的陽極鎖或磁力鎖為NC3. 電鎖的電源建議獨立供電4. 電鎖建議外加一個反向二級體(1N4001)保護電路注意事項1. 電鎖及出門按鈕由控制器直接控制,安全性較高2. 電鎖繼電器的NC/NO依電鎖型式決定,一般的陽極鎖或磁力鎖為NC3. NC/NO使用控制器PCB之JUMPER JP7~JP10跳線4. 電鎖的電源建議獨立供電5. 電鎖建議外加一個反向二級體(1N4001)保護電路磁簧DI_GDIPCB跳線控制器出門按鈕警報器V+外部電源V-Pin6PCB跳線參見注意事項Pin7Pin8Pin1Pin2GND控制器電源供應器(For 控制器&卡機)出門按鈕V-RS485 D+DI_GDIGND V+(12V)電源供應器(For 電鎖)GNDID=1控制器警報器磁簧外部電源V+V+Pin5Pin6Pin9Pin7。

AD4001 AD4005 数据手册说明书

16位、2 MSPS/1 MSPS 、精密差分SAR ADC数据手册AD4001/AD4005Rev. ADocument FeedbackInformation furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks andregistered trademarks are the property of their respective owners.One Technology Way, P .O. Box 9106, Norwood, MA 02062-9106, U.S.A.Tel: 781.329.4700 ©2017 Analog Devices, Inc. All rights reserved. Technical Support /cnADI 中文版数据手册是英文版数据手册的译文,敬请谅解翻译中可能存在的语言组织或翻译错误,ADI 不对翻译中存在的差异或由此产生的错误负责。

如需确认任何词语的准确性,请参考ADI 提供的最产品特性吞吐速率:2 MSPS/1 MSPS 可选INL :±0.4 LSB (最大值) 保证16位无失码 低功耗9.5 mW (2 MSPS),4.9 mW (1 MSPS)(仅VDD ) 80 μW (10 kSPS),16 mW (2 MSPS)(总计)SNR :典型值96.2 dB (1 kHz, V REF = 5 V);典型值95.5 dB (100 kHz) THD :典型值−123 dB (1 kHz, V REF = 5 V);典型值−99 dB (100 kHz) 易用特性可降低系统功耗和复杂性 输入过压箝位电路减少了非线性输入电荷反冲 高阻态模式 长采集阶段 输入范围压缩快速转换时间支持很低的SPI 时钟速率 SPI 可编程模式、读/写能力、状态字 差分模拟输入范围:±V REF0 V 至V REF (V REF 在2.4 V 至5.1 V 之间)单电源工作:1.8 V ,逻辑接口电压:1.71 V 至5.5 V SAR 架构:无延迟/流水线延迟,首次转换有效 精确的首次转换保证工作:−40°C 至+125°CSPI/QSPI/MICROWIRE/DSP 兼容串行接口以菊花链形式连接多个ADC ,并能提供繁忙指示10引脚封装:3 mm × 3 mm LFCSP 、3 mm × 4.90 mm MSOP 封装应用自动测试设备 机器自动化 医疗设备 电池供电设备 精密数据采集系统概述AD4001/AD4005是低噪声、低功耗、高速、16位精密逐次逼近型寄存器(SAR)模数转换器(ADC)。

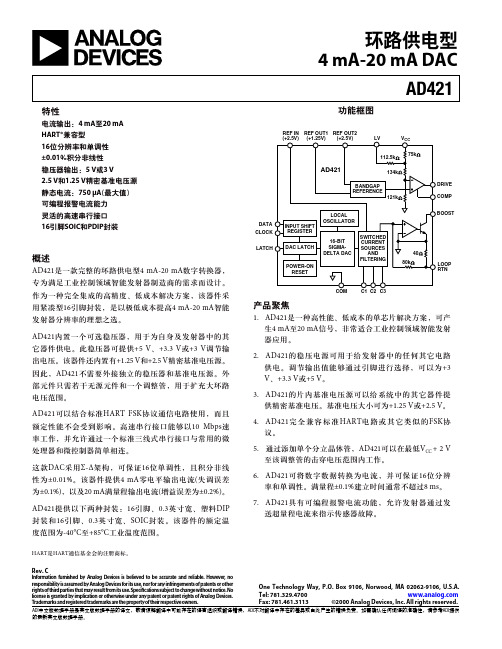

AD421中文资料

这款DAC采用Σ-Δ架构,可保证16位单调性,且积分非线 性为±0.01%。该器件提供4 mA零电平输出电流(失调误差 为±0.1%),以及20 mA满量程输出电流(增益误差为±0.2%)。

单位

条件/注释

精度 分辨率 单调性 积分非线性 失调(4 mA)(+25°C时)4 失调漂移 典型输出误差(20 mA) (+25°C时)4 总输出漂移 VCC电源灵敏度

16 16 ± 0.01 ± 0.1 ± 25 ± 0.2 ± 50 50

位 位(最小值) % FS(最大值) % FS(最大值) ppm FS/°C(最大值) % FS(最大值) ppm FS/°C(最大值) nA/mV(最大值)

FS = 满量程输出电流 VCC = 5 V 包括片内基准电压漂移 VCC = 5 V 包括片内基准电压漂移 25 nA/mV(典型值)

基准电压源 REF OUT2 输出电压 温漂

外部电流 VCC电源灵敏度 输出阻抗 噪声(0.1 Hz–10 Hz) REF OUT1

输出电压 温漂

外部电流 VCC电源灵敏度 输出阻抗 噪声(0.1 Hz–10 Hz) REF IN 输入电阻

7. AD421具有可编程报警电流功能,允许发射器通过发 送超量程电流来指示传感器故障。

HART是HART通信基金会的注册商标。

Rev. C

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rightsofthirdpartiesthatmayresultfromitsuse.Speci cationssubjecttochangewithoutnotice.No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

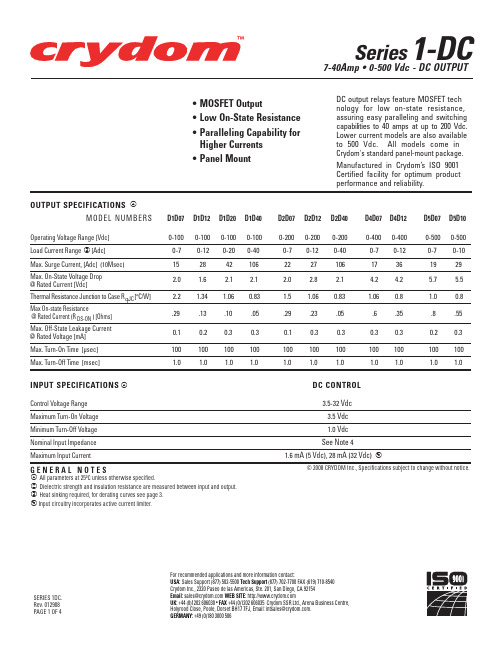

D1D40中文资料

Max. Surge Current, [Adc] (10Msec) Max. On-State Voltage Drop @ Rated Current [Vdc] Thermal Resistance Junction to Case RqJC[°C/W] Max On-state Resistance @ Rated Current (R DS-ON ) [Ohms] Max. Off-State Leakage Current @ Rated Voltage [mA] Max. Turn-On Time [µsec]

MAX. SURGE CURRENT (Amps)

Transient Protection

All loads are inductive, even ones that are not so labeled. An inductive load will produce harmful transient voltages when it is turned off. The more perfect the switch, the larger the transient voltages; the MOSFET output is so nearly an ideal switch that the transient voltages produced by seemingly "non-inductive" loads can cause damage if not suppressed. Diodes should be fast recovery type with PIV rated greater than supply voltage.

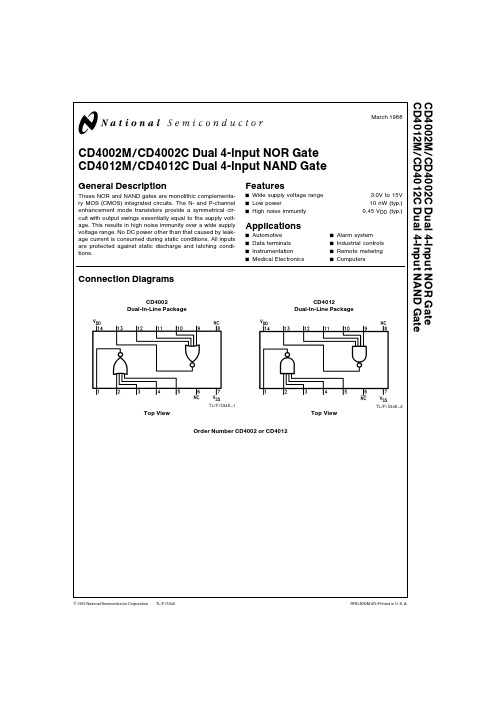

CD4019中文资料

TL F 5940CD4002M CD4002C Dual 4-Input NOR Gate CD4012M CD4012C Dual 4-Input NAND GateMarch 1988CD4002M CD4002C Dual 4-Input NOR Gate CD4012M CD4012C Dual 4-Input NAND GateGeneral DescriptionThese NOR and NAND gates are monolithic complementa-ry MOS (CMOS)integrated circuits The N-and P-channel enhancement mode transistors provide a symmetrical cir-cuit with output swings essentially equal to the supply volt-age This results in high noise immunity over a wide supply voltage range No DC power other than that caused by leak-age current is consumed during static conditions All inputs are protected against static discharge and latching condi-tionsFeaturesY Wide supply voltage range 3 0V to 15V Y Low power10nW (typ )YHigh noise immunity0 45V DD (typ )ApplicationsY Automotive Y Alarm system Y Data terminals Y Industrial controls Y Instrumentation Y Remote metering YMedical ElectronicsYComputersConnection DiagramsCD4002Dual-In-Line PackageTL F 5940–1Top ViewCD4012Dual-In-Line PackageTL F 5940–2Top ViewOrder Number CD4002or CD4012C 1995National Semiconductor Corporation RRD-B30M105 Printed in U S AAbsolute Maximum Ratings(Note1)If Military Aerospace specified devices are required please contact the National Semiconductor Sales Office Distributors for availability and specifications Voltage at Any Pin V SS b0 3V to V DD a0 3V Operating Temperature RangeCD4002M CD4012M b55 C to a125 C CD4002C CD4012C b40 C to a85 C Storage Temperature Range(T S)b65 C to a150 C Power Dissipation(P D)Dual-In-Line700mW Small Outline500mW Operating Range(V DD)V SS a3 0V to V SS a15V Lead Temperature(T L)(Soldering 10seconds)260 CDC Electrical Characteristics CD4002M CD4012MLimitsSymbol Parameter Conditions b55 C a25 C a125 C UnitsMin Max Min Typ Max Min MaxI DD Quiescent V DD e5 0V0 050 0010 053 0m ADevice Current V DD e10V0 10 0010 16m A P D Quiescent Device V DD e5 0V0 250 0050 2515m W Dissipation Package V DD e10V1 00 011 060m W V OL Output Voltage V DD e5 0V V I e V DD I O e0A0 0500 050 05V Low Level V DD e10V V I e V DD I O e0A0 0500 050 05V V OH Output Voltage V DD e5 0V V I e V SS I O e0A4 954 955 04 95V High Level V DD e10V V I e V SS I O e0A9 959 95109 95V V NL Noise Immunity V DD e5 0V V O e3 6V I O e0A1 51 52 251 4V (All Inputs)V DD e10V V O e7 2V I O e0A3 03 04 52 9V V NH Noise Immunity V DD e5 0V V O e0 95V I O e0A1 41 52 251 5V (All Inputs)V DD e10V V O e2 9V I O e0A2 93 04 53 0V I D N Output Drive Current V DD e5 0V V O e0 4V V I e V DD0 50 401 00 28mAN-Channel(4002)V DD e10V V O e0 5V V I e V DD1 10 92 50 65mA (Note2)I D P Output Drive Current V DD e5 0V V O e2 5V V I e V SS b0 62b0 5b2 0b0 35mAP-Channel(4002)V DD e10V V O e9 5V V I e V SS b0 62b0 5b1 0b0 35mA (Note2)I D N Output Drive Current V DD e5 0V V O e0 4V V I e V DD0 310 250 50 175mAN-Channel(4012)V DD e10V V O e0 5V V I e V DD0 630 50 60 35mA (Note2)I D P Output Drive Current V DD e5 0V V O e2 5V V I e V SS b0 31b0 25b0 5b0 175mAP-Channel(4012)V DD e10V V O e9 5V V I e V SS b0 75b0 6b1 2b0 4mA (Note2)I I Input Current10pANote1 ‘‘Absolute Maximum Ratings’’are those values beyond which the safety of the device cannot be guaranteed Except for‘‘Operating Temperature Range’’they are not meant to imply that the devices should be operated at these limits The table of‘‘Electrical Characteristics’’provides conditions for actual device operationNote2 I D N and I D P are tested one output at a time2DC Electrical Characteristics CD4002C CD4012CLimitsSymbol Parameter Conditions b55 C a25 C a85 C UnitsMin Max Min Typ Max Min MaxI DD Quiescent V DD e5 0V0 50 0050 515m ADevice Current V DD e10V5 00 0055 030m A P D Quiescent Device V DD e5 0V2 50 0252 575m W Dissipation Package V DD e10V500 0550300m W V OL Output Voltage V DD e5 0V V I e V DD I O e0A0 0500 050 05V Low Level V DD e10V V I e V DD I O e0A0 0500 050 05V V OH Output Voltage V DD e5 0V V I e V SS I O e0A4 954 955 04 95V High Level V DD e10V V I e V SS I O e0A9 959 95109 95V V NL Noise Immunity V DD e5 0V V O t3 6V I O e0A1 51 52 251 4V (All Inputs)V DD e10V V O t7 2V I O e0A3 03 04 52 9V V NH Noise Immunity V DD e5 0V V O s0 95V I O e0A1 41 52 251 5V (All Inputs)V DD e10V V O s2 9V I O e0A2 93 04 53 0V I D N Output Drive Current V DD e5 0V V O e0 4V V I e V DD0 350 31 00 24mAN-Channel(4002)V DD e10V V O e0 5V V I e V DD0 720 62 50 48mA (Note2)I D N Output Drive Current V DD e5 0V V O e0 4V V I e V DD0 1450 120 50 095mAN-Channel(4012)V DD e10V V O e0 5V V I e V DD0 30 250 60 2mA (Note2)I D P Output Drive Current V DD e5 0V V O e2 5V V I e V SS b0 35b0 3b2 0b0 24mAP-Channel(4002)V DD e10V V O e9 5V V I e V SS b0 3b0 25b1 0b0 2mA (Note2)I D P Output Drive Current V DD e5 0V V O e2 5V V I e V SS b0 145b0 12b0 5b0 095mAP-Channel(4012)V DD e10V V O e9 5V V I e V SS b0 35b0 3b1 2b0 24mA (Note2)I I Input Current10pANote1 ‘‘Absolute Maximum Ratings’’are those values beyond which the safety of the device cannot be guaranteed Except for‘‘Operating Temperature Range’’they are not meant to imply that the devices should be operated at these limits The table of‘‘Electrical Characteristics’’provides conditions for actual device operationNote2 I D N and I D P are tested one output at a time3AC Electrical Characteristics T A e25 C C L e15pF and input rise and fall times e20ns Typical temperature coefficient for all values of V DD e0 3% CSymbol Parameter Conditions Min Typ Max Units CD4002Mt PHL Propagation Delay Time V DD e5 0V3550ns High to Low Level V DD e10V2540ns t PLH Propagation Delay Time V DD e5 0V3550ns Low to High Level V DD e10V2540ns t THL Transition Time High V DD e5 0V65175ns to Low Level V DD e10V3575ns t TLH Transition Time Low V DD e5 0V65125ns to High Level V DD e10V3570nsC IN Input Capacitance Any Input5 0pFCD4002Ct PHL Propagation Delay Time V DD e5 0V35120ns High to Low Level V DD e10V2565ns T PLH Propagation Delay Time V DD e5 0V3580ns Low to High Level V DD e10V2555ns t THL Transition Time High V DD e5 0V65300ns to Low Level V DD e10V35125ns t TLH Transition Time Low V DD e5 0V65200ns to High Level V DD e10V35115nsC IN Input Capacitance Any Input5 0pFAC Parameters are guaranteed by DC correlated testingAC Electrical Characteristics T A e25 C C L e15pF and input rise and fall times e20ns Typical temperature coefficient for all values of V DD e0 3% CSymbol Parameter Conditions Min Typ Max Units CD4012Mt PHL Propagation Delay Time V DD e5 0V5075ns High to Low Level V DD e10V2540ns t PLH Propagation Delay Time V DD e5 0V5075ns Low to High Level V DD e10V2540ns t THL Transition Time High V DD e5 0V75125ns to Low Level V DD e10V5075ns t TLH Transition Time Low V DD e5 0V75100ns to High Level V DD e10V4060nsC IN Input Capacitance Any Input5 0pFCD4012Ct PHL Propagation Delay Time V DD e5 0V50100ns High to Low Level V DD e10V2550ns T PLH Propagation Delay Time V DD e5 0V50100ns Low to High Level V DD e10V2550ns t THL Transition Time High V DD e5 0V75150ns to Low Level V DD e10V50100ns t TLH Transition Time Low V DD e5 0V75125ns to High Level V DD e10V4075nsC IN Input Capacitance Any Input5 0pFAC Parameters are guaranteed by DC correlated testingNote1 ‘‘Absolute Maximum Ratings’’are those values beyond which the safety of the device cannot be guaranteed Except for‘‘Operating Temperature Range’’they are not meant to imply that the devices should be operated at these limits The table of‘‘Electrical Characteristics’’provides conditions for actual device operation4Physical Dimensions inches(millimeters)Ceramic Dual-In-Line Package(J)Order Number CD4002MJ CD4002CJ CD4012MJ or CD4012CJNS Package Number J14A5C D 4002M C D 4002C D u a l 4-I n p u t N O R G a t e C D 4012M C D 4012C D u a l 4-I n p u t N A N D G a t ePhysical Dimensions inches (millimeters)(Continued)Molded Dual-In-Line Package (N)Order Number CD4002MN CD4002CN CD4012MN or CD4012CNNS Package Number N14ALIFE SUPPORT POLICYNATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION As used herein 1 Life support devices or systems are devices or 2 A critical component is any component of a life systems which (a)are intended for surgical implant support device or system whose failure to perform can into the body or (b)support or sustain life and whose be reasonably expected to cause the failure of the life failure to perform when properly used in accordance support device or system or to affect its safety or with instructions for use provided in the labeling can effectivenessbe reasonably expected to result in a significant injury to the userNational Semiconductor National Semiconductor National Semiconductor National Semiconductor CorporationEuropeHong Kong LtdJapan Ltd1111West Bardin RoadFax (a 49)0-180-530858613th Floor Straight Block Tel 81-043-299-2309。

施耐德宝光微机保护产品选型手册说明书

Schneider Baoguang关于施耐德宝光施耐德(陕西)宝光电器有限公司(简称SSBEA或施耐德宝光)是施耐德电气有限公司与陕西宝光集团有限公司共同组建的一家专业从事中、系统及相关产品研发、生产和销售的中外合资企业。

高新科技园区。

在世界五百强企业与中国中压电器龙头企业的通力合作下,作为国内中压行业著名的“宝光”品牌真空断路器的唯一合法生产商,施耐德宝光秉承精益生产科学理念,凭借品质过硬、安全可靠的全系列高品质产品和覆盖用户全生命周期的完善服务,帮助用户实现卓越的生产运营绩效和市场竞争力,用品质的“不妥协”实现可持续发展之道。

我们致力于将施耐德宝光打造成为中国卓越和高效的中压断路器和系统的制造平台,依托自身的专业优势,为广大用户和合作伙伴提供领先的总成本和长期全面的安心保障。

目录V5系列新一代微机保护测控装置 (1)产品概述 (1)产品特点 (2)型号及功能说明 (3)保护功能 (4)测控功能 (6)技术参数 (7)典型接线图 (8)外形尺寸及面板开孔尺寸 (11)V5订货选型表 (12)V3系列微机保护测控装置 (13)产品概述 (13)产品特点 (14)型号及功能说明 (15)保护功能 (16)测控功能 (17)技术参数 (18)典型接线图 (19)外形尺寸及面板开孔尺寸 (21)V3订货选型表 (22)V3U微机综合保护装置 (23)产品概述 (23)型号及功能说明 (24)保护功能 (25)测控功能 (26)技术参数 (27)外形尺寸图/典型接线图 (28)后台系统 (29)系统总体结构 (30)V5系列新一代微机保护测控装置是一种用于测量、控制、保护、通讯一体化的智能设备,产品主要用于工业及能源领域对线路、变压器、电动机及电容器的保护测控。

此产品外观时尚、结构精巧、大屏幕液晶显示,图形化中文菜单,四位方向导航盘,操作快捷方便。

内部基于SOC芯片软件方案,32位处理器,并根据硬件进行深度改良优化的嵌入式操作系统,使CPU运行效率更高。

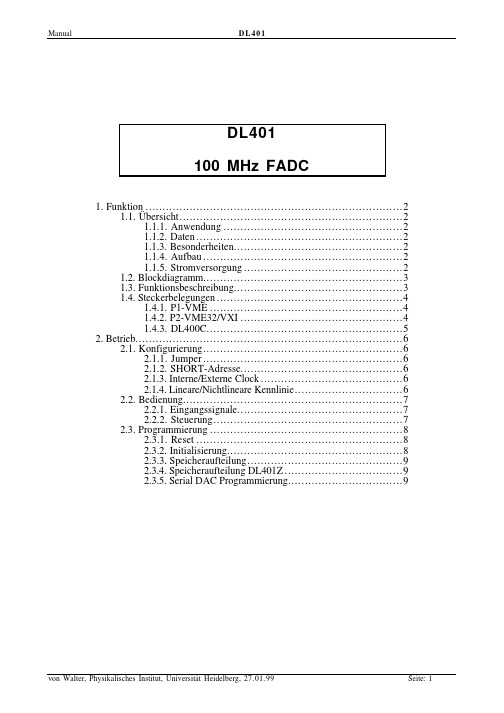

DL401中文资料

Manual D L401DL401100 MHz FADC1. Funktion (2)1.1. Übersicht (2)1.1.1. Anwendung (2)1.1.2. Daten (2)1.1.3. Besonderheiten (2)1.1.4. Aufbau (2)1.1.5. Stromversorgung (2)1.2. Blockdiagramm (3)1.3. Funktionsbeschreibung (3)1.4. Steckerbelegungen (4)1.4.1. P1-VME (4)1.4.2. P2-VME32/VXI (4)1.4.3. DL400C (5)2. Betrieb (6)2.1. Konfigurierung (6)2.1.1. Jumper (6)2.1.2. SHORT-Adresse (6)2.1.3. Interne/Externe Clock (6)2.1.4. Lineare/Nichtlineare Kennlinie (6)2.2. Bedienung (7)2.2.1. Eingangssignale (7)2.2.2. Steuerung (7)2.3. Programmierung (8)2.3.1. Reset (8)2.3.2. Initialisierung (8)2.3.3. Speicheraufteilung (9)2.3.4. Speicheraufteilung DL401Z (9)2.3.5. Serial DAC Programmierung (9)1. F UNKTION1.1. Übersicht1.1.1. AnwendungDriftkammern, Transient Recording1.1.2. DatenParameter WertKanalzahl4Abtastrate / Kanal≤ 100 MHz Speichertiefe1024 Samples Amplitudenauflösung linear8 BitAmplitudenauflösung nichtlinear10 BitEingangsempfindlichkeit (im unteren Bereich)195 µV/LSB Verstärkung (Anpaßverstärker)10Pedestal Korrektur 6 Bit1.1.3. Besonderheiten-COMMONSTART-COMMONSTOP, Addresscounter lesbar-AUTOSTOP bei Memory Overflow-START und STOP per Software-RUN und EOC (EndOfConversion) per Software lesbar-Multiple Event Speicherung-Auslese wahlfrei-100 MHz Quartzclock wahlweise1.1.4. AufbauDL400 Application-Module, VME-Doppeleuropa, Breite 3TE, Höhe 6HE1.1.5. StromversorgungSpannung Strom Leistung+5V.45 A 2.15 W-5.2V 4.6 A24 W+12V0.125 A 1.5 W-12V25 mA.3 WGesamt28.05 W1.2. Blockdiagramm1.3. FunktionsbeschreibungVon einem Frontstecker werden die differentiellen Analogsignale von 4 Kanälen über Anpaßverstärker um den Faktor 10 verstärkt und können für eine optimale Ausnutzung desdynamischen Bereichs im Pedestal verschoben werden. Die Pedestalwerte werden für alle Kanäle unabhängig in einem 4 Kanal DAC mit 6 Bit Auflösung erzeugt.Die Amplitudenauflösung der nachfolgenden FADCs beträgt 8 Bits. Durch ein vorgeschaltetes Netzwerk (NL) kann der dynamische Bereich um den Faktor 4 erweitert werden, so daß eine nichtlineare Übertragungsfunktion mit einer effektiven Amplitudenauflösung von 10 Bits (im unteren Bereich) erreicht wird.Das GATE-Signal über einen Frontstecker, bzw. über Software gesetzt, bestimmt Beginn und Ende der Aufzeichnung. Auf jeden CONVERT-Impuls werden die momentanen Analogwerte an allen 4 Kanälen gleichzeitig digitalisiert und anschließend in die Speicher eingeschrieben. Der Impuls kann wiederum von der Frontplatte oder per Software generiert werden. Als Quelle kann auch ein 100 MHz Quartzoszillator auf dem Board verwendet werden.Nach dem Einschreiben wird der Adresszähler um 1 erhöht. In der Betriebsart 'AutoStop' wird bei einem Überlauf des Zählers (>1023) die Aufzeichnung gestoppt, im anderen Modus(CommonStop) beginnt die Aufzeichnung immer wieder bei 0!Die Digitalisierung wird normalerweise durch Wegnahme des GATE-Signals beendet. Zu diesem Zeitpunkt wird ein Bit gesetzt und das Modul generiert (falls ermöglicht) einen Interrupt.Der Addresscounter wird dann gegebenenfalls ausgelesen und das wahlfreie Auslesen der Daten kann erfolgen.Falls die Tiefe der Memories dies erlaubt kann nach einem Stop auch die Wiederaufnahme der Aufzeichnung ohne Zwischenauslese erfolgen (Multi event storage). Bei einem RESET wird der Addresscounter auf 0 gesetzt.1.4. Steckerbelegungen1.4.1. P1-VME1.4.2. P2-VME32/VXI1.4.3. DL400C2. B ETRIEB2.1. Konfigurierung2.1.1. JumperBetriebsart Jumper BemerkungInternal Clock J3,/J4Quartz ClockExternal Clock J4,/J3NIM-InputDelay Delay do not changeDebug J1, J2do not change2.1.2. SHORT-AdresseUm das Modul im SHORT-Adressraum von VME ansprechen zu können, muß die gewünschte Adresse des Moduls mit den Rotary-HEX-Schaltern auf der DL400 Basisplatine eingestellt werden (siehe weiter unter 2.3. Programmierung).2.1.3. Interne/Externe ClockFalls die interne Clock mit 100 MHz benutzt werden soll, muß Internal Clock gesetzt werden.2.1.4. Nichtlineare/Lineare KennlinieBei nichtlinearer Eingangsbeschaltung der FADCs ist der Zusammenhang zwischen dem FADC-Code (C) und der Eingangsspannung (U i) am Modul nach folgender Formel gegeben:U i =C256 - a * C * U o / K;K (=10) kennzeichnet die Verstärkung des Anpaßverstärkers.a (=0.75) ist der Expansionsfaktor.U o (=0.5V) ist die Referenzspannung bei U i =0;ACHTUNG: Bei linearer Eingangsbeschaltung des FADC müssen die Widerstände R79…R82 (=15.4 Ω) unter den FADC chips entfernt werden (a=0, U o = 2V).2.2. Bedienung2.2.1. EingangssignaleDie analogen Signale für 4 Kanäle werden als differentielle Signale von der Frontseite zugeführt. Die Eingangsimpedanz zwischen den Eingangspins ±Cn beträgt 100Ω. Die Spannung für Vollaussteuerung beträgt 160mV.2.2.2. SteuerungZur externen Steuerung dienen im wesentlichen die 2 NIM-Signale GATE und CONVERT:•CONVERT: Dieses Signal stellt die Clock für die Konvertierung dar.•GATE: Dieses Signal bestimmt die Dauer der Konvertierung.2.3. Programmierung über DL400Das Modul ist ohne Programmierung zunächst nur im Short-Addressbereich (AM=$2D oder $29) ansprechbar. Die Bezeichnung "ss" in den folgenden Adressangaben steht für dieEinstellung der HEX-Schalter!2.3.1. ResetWRITE:SHORT.$ss20RESETD31D15D0HighWord LowWordLongWord2.3.2. InitialisierungFür die Festlegung der Standard-Basisadresse des Moduls, der Modulgröße, der gewünschten Addressmodifier und der Parameter für einen Interrupt müssen verschiedene Register (im Short-bereich) auf der DL400 Basisplatine geladen werden!WRITE:SHORT.$ss50D0…D15: Address Std-BaseaddressSHORT.$ss60D0…D3: MaskD8…D13: AMD15: Enable Mask for Submodule Size Address Modifierenable STD-accessSHORT.$ss70 (auch READ)D0…D7: IntVectorD8…D10: IntPrioD11: IntModeInterrupt VectorInterrupt Priority (0=Disable)0=RORA, 1=ROACD31D15D0HighWord LowWordLongWordFestlegung der Modulgröße:ModuleSize Mask64KB$0128KB$1256KB$3512KB$71MB$FACHTUNG:•D0…D3 in Address muß genauso wie D0…D3 in Mask gesetzt werden!•D8…D15 in Address bei Standard-Zugriff auf HIGH setzen!2.3.3. SpeicheraufteilungREAD:SHORT.$ss00Convert Convert do Internal ConvertSHORT.$ss70D12: RunD13: InterruptD14: DACRead test RUNtest INTERRUPT FLAG read Serial DACSHORT.$ss90D16…D25: Counter Read Address CounterSTD.$rAddr Ch3Ch2Ch1Ch0Sample 0 ……Ch3Ch2Ch1Ch0Sample 1023WRITE:SHORT.$ss00ClearInterrupt ClearInterrupt Clear Interrupt FlagSHORT.$ss10D0: DACWrite Shift DAC and Serial Write SHORT.$ss20RESET RESET Module RESETSHORT.$ss70D12: InternalD13: Gate/D14: DACEnableD15: AutoStop set internal Mode set internal Gate enable Serial DAC enable AutoStopD31D15D0HighWord LowWordLongWord2.3.4. Speicheraufteilung DL401ZREAD:SHORT.$ss90D0…D15: Counter Read Address CounterSTD.$rAddr Ch1Ch0Digital Sample 0 ……Ch1Ch0Digital Sample 32KD31D15D0HighWord LowWordLongWord2.3.5. Serial DAC ProgrammierungFür die volle Ausnutzung der Dynamik kann von jedem Kanal die Schwelle unabhängig calibriert werden. Zu diesem Zweck wird ein 4 Kanal DAC mit 6 bit Amplitudenauflösung programmiert. Bei einer Eingangsspannung von 0V am FADC ergeben sich etwa folgende Werte: DAC=0:FADC pedestal < 0DAC≈25:FADC pedestal ≈ 0DAC=63:FADC pedestal ≈ 50Die DACs müssen seriell gelesen bzw. beschrieben werden. Die Reihenfolge für die Datenbits ist von D5 nach D0 über Kanal 3 nach Kanal 0!SCHEMA für Lesen (und Setzen) der DACs:1)Enable DAC2)for ChannelNr:=3 downto 0 dofor DataBit:=5 downto 0 doRead Bit at D14 of DACReadWRITE Bit at D0 to DACWrite3)Disable DAC。

AD408M182VBB-5中文资料

ASCEND Semiconductor 4Mx4 EDO Data sheetDescriptionThe device CMOS Dynamic RAM organized as 4,194,304 words x 4 bits with extended data out access mode. It is fabricated with an advanced submicron CMOS technology and designed to operate from a single 3.3V oniy power supply. Low voltage operation is more suitable to be used on battery backup, portable elec-tronic application. lt is packaged in JEDEC standard 26/24-pin plastic SOJ or TSOP(II).Features• Single 3.3V(%) only power supply • High speed t RAC acess time: 50/60ns • Low power dissipation- Active mode : 432/396 mW (Mas) - Standby mode: 0.54 mW (Mas)• Extended - data - out(EDO) page mode access • I/O level: CMOS level (Vcc = 3.3V)• 2048 refresh cycle in 32 ms(Std.) or 128 ms(S-version)• 4 refresh modesh: - RAS only refresh- CAS - before - RAS refresh - Hidden refresh - Self-refresh(S-version)10±Pin Name FunctionA0-A10Address inputs- Row address - Column address - Refresh address DQ1~DQ4Data-in / data-out RAS Row address strobe CAS Column address strobe WE Write enable OE Output enable Vcc Power (+ 3.3V)VssGroundVCC 1DQ12DQ23DQ34DQ45VCC6891011 NC 12 WE 13A0 A117 A218 A319VSS RAS CAS OE A8A7A6A5A4VSSAD404M42VSPin Description Pin Configuration21222324 2526151416 A1026/24-PIN 300mil Plastic SOJA9VCC 1DQ12DQ23DQ34DQ45VCC6891011 NC 12 WE 13A0 A117 A218 A319VSS RAS CAS OE A8A7 A6A5 A4VSSAD404M42VT212223242526151416 A1026/24-PIN 300mil Plastic TSOP (ll)A9A0-A10A0-A10A0-A10WECASNO. 2 CLOCK GENERATORCOLUMN ADDRESS BUFFERS (11)REFRESH CONTROLLERREFRESH COUNTERBUFFERS (11)ADDRESS ROW NO. 1 CLOCK GENERATORA0RASA1A2A3A4A5A6A7A8CONTROLLOGICDATA-IN BUFFERDATA-OUT BUFFEROEDQ1.DQ4.COLUMN DECODER2048SENSE AMPLIFIERSI/O GATING2048x42048x2048x4MEMORY ARRAY2048R O W D E C O D E RVcc VssBlock DiagramA9A10TRUTH TABLENotes: 1. EARLY WRITE only.FUNCTIONRASCAS WE OE ADDRESSESDQ SNotesROW COL STANDBY H X X X X High-Z READL L H L ROW COL Data-Out WRITE: (EARLY WRITE )L L L X ROW COL Data-lnREAD WRITE L L ROW COL Data-Out,Data-ln EDO-PAGE-MODE READ1st Cycle L H L ROW COL Data-Out 2nd CycleL H L n/a COL Data-Out EDO-PAGE MODE WRITE1st CycleL L X ROW COL Data-In 2nd Cycle L L Xn/a COL Data-InEDO-PAGE-MODEREAD-WRITE 1st Cycle L ROW COL Data-Out, Data-In 2nd Cycle L n/a COL Data-Out, Data-In HIDDEN REFRESHREAD L H L ROW COL Data-Out WRITEL L X ROW COL Data-In 1RAS-ONLY REFRESH L H X X ROW n/a High-Z CBR REFRESHLHXXXHigh-ZH X →H L →L H →H L →H L →H L →H L →H L →H L →L H →H L →H L →L H→L H L →→L H L→→H L→Absolute Maximum RatingsRecommended DC Operating ConditionsCapacitanceTa = 25°C, V CC = 3.3V%, f = 1MHz Note: 1. Capacitance measured with effective capacitance measuring method. 2. RAS, CAS = V IH to disable Dout.ParameterSymbol Value Unit Voltage on any pin relative to Vss V T -0.5 to + 4.6V Supply voltage relative to Vss V CC -0.5 to + 4.6V Short circuit output current I OUT 50mA Power dissipation P D 1.0WOperating temperature T OPT 0 to + 70°C Storage temperatureT STG-55 to + 125°CParameter/Condition Symbol3.3 Volt VersionUnitMinTyp MaxSupply VoltageV CC 3.0 3.33.6V Input High Voltage, all inputs V IH 2.0-V CC + 0.3V Input Low Voltage, all inputsV IL-0.3-0.8VParameterSymbol Typ Max Unit Note Input capacitance (Address)C I1 -5pF 1Input capacitance (RAS, CAS, OE, WE)C I2-7pF 1Output capacitance(Data-in, Data-out)C I/O-7pF1, 210±DC Characteristics :(T a = 0 to 70°C, V CC = + 3.3V%, V SS = 0V)Parameter Symbol Test Conditions AD404M42V Unit Notes-5-6Min Max Min MaxOperating current I CC1RAS cyclingCAS, cyclingt RC = min-120-110mA1, 2Standby Current LowpowerS-versionI CC2LVTTL interfaceRAS, CAS = V IHDout = High-Z-0.5-0.5mACMOS interfaceRAS, -0.2VDout = High-Z-0.15-0.15mAStandardpowerversionLVTTL interfaceRAS, CAS = V IHDout = High-Z-2-2mACMOS interfaceRAS,-0.2VDout = High-Z-0.5-0.5mARAS- only refresh current I CC3RAS cycling, CAS = V IHt RC = min-120-110mA1, 2 EDO page mode current I CC4t PC = min-90-80mA1, 3CAS- before- RAS refresh current I CC5t RC = minRAS, CAS cycling-120-110mA1, 2Self- refresh current (S-Version)I CC8 - 550 - 55010±CAS V CC≥CAS V CC≥t RASS100µs≥µADC Characteristics :(T a = 0 to 70°C , V CC = +3.3V %, V SS = 0V)Notes:1. I CC is specified as an average current. It depends on output loading condition and cycle rate when the device is selected. I CC max is specified at the output open condition.2. Address can be changed once or less while RAS = V IL .3. For I CC4, address can be changed once or less within one EDO page mode cycle time.Parameter Symbol Test Conditions AD404M42VUnitNotes-5-6Min MaxMin MaxInput leakage current I LI + 0.3V -55-55Output leakage current I LO + 0.3V Dout = Disable -55-55Output high Voltage V OH I OH = -2mA 2.4- 2.4-V Output low voltage V OLI OL = +2mA-0.4-0.4V10±0V Vin V CC ≤≤µA 0V Vout V CC ≤≤µAAC Characteristics(T a = 0 to + 70°C , V cc = 3.3V %, V ss = 0V) *1, *2, *3, *4Test conditions• Output load: one TTL Load and 100pF (V CC = 3.3V %)• Input timing reference levels:V IH = 2.0V, V IL = 0.8V (V CC = 3.3V %)• Output timing reference levels:V OH = 2.0V, V OL = 0.8V10±10±10±Read, Write, Read- Modify- Write and Refresh Cycles (Common Parameters)ParameterSymbol AD404M42V UnitNotes-5-6Min MaxMin MaxRandom read or write cycle time t RC 84-104-ns RAS precharge timet RP 30-40-ns CAS precharge time in normal mode t CPN 10-10-ns RAS pulse width t RAS 50100006010000ns 5CAS pulse width t CAS 8100001010000ns 6Row address setup time t ASR 0-0-ns Row address hold time t RAH 8-10-ns Column address setup time t ASC 0-0-ns 7Column address hold time t CAH 8-10-ns RAS to CAS delay timet RCD 12371445ns 8RAS to column address delay time t RAD 10251230ns 9Column address to RAS lead time t RAL 25-30-ns RAS hold time t RSH 8-10-ns CAS hold timet CSH 38-40-ns CAS to RAS precharge time t CRP 5-5-ns 10OE to Din delay time t OED 12-15-ns Transition time (rise and fall)t T 150150ns 11Refresh periodt REF -32-32ms Refresh period (S- Version)t REF -128-128ms CAS to output in Low- Z t CLZ 0-0-ns CAS delay time from Din t DZC 0-0-ns OE delay time from Dint DZO-0-nsRead CycleWrite Cycle Parameter SymbolAD404M42V Unit Notes-5-6Min Max Min MaxAccess time from RAS t RAC-50-60ns12 Access time from CAS t CAC-14-15ns13, 14 Access time from column address t AA-25-30ns14, 15 Access time from OE t OEA-12-15nsRead command setup time t RCS0-0-ns7 Read command hold time to CAS t RCH0-0-ns10, 16 Read command hold time to RAS t RRH0-0-ns16 Output buffer turn-off time t OFF012015ns17 Output buffer turn-off time from OE t OEZ012015ns17Parameter SymbolAD404M42V Unit Notes -5-6Min Max Min MaxWrite command setup time t WCS0-0-ns7, 18 Write command hold time t WCH8-10-nsWrite command pulse width t WP8-10-nsWrite command to RAS lead time t RWL13-15-nsWrite command to CAS lead time t CWL8-10-nsData-in setup time t DS0-0-ns19 Data-in hold time t DH8-10-ns19 WE to Data-in delay t WED10-10-nsRead- Modify- Write CycleRefresh Cycle Parameter SymbolAD404M42V Unit Notes-5-6Min Max Min MaxRead-modify- write cycle time t RWC108-133-nsRAS to WE delay time t RWD64-77-ns18 CAS to WE dealy time t CWD26-32-ns18 Column address to WE delay time t AWD39-47-ns18 OE hold time from WE t OEH8-10-nsParameter SymbolAD404M42VUnit Notes -5-6Min Max Min MaxCAS setup time (CBR refresh) t CSR5-5-nsCAS hold time (CBR refresh)t CHR8-10-ns10 RAS precharge to CAS hold time t RPC5-5-ns7 RAS pulse width (self refresh)t RASS100-100-RAS precharge time (self refresh)t RPS90-110-nsCAS hold time (CBR self refresh)t CHS-50--50-nsWE setup time t WSR0-0-nsWE hold time t WHR10-10-nsµsEDO Page Mode CycleEDO Page Mode Read Modify Write CycleParameterSymbol AD404M42VUnit Notes-5-6Min MaxMin MaxEDO page mode cycle timet PC 20-25-ns EDO page mode CAS precharge time t CP 10-10-ns EDO page mode RAS pulse width t RASP 5010560105ns 20Access time from CAS precharge t CPA -30-35ns 10, 14RAS hold time from CAS precharge t CPRH 30-35-ns OE high hold time from CAS high t OEHC 5-5-ns OE high pulse widtht OEP 10-10-ns Data output hold time after CAS low t COH 5-5-ns Output disable delay from WEt WHZ 310310ns WE pulse width for output disable whenCAS hight WPZ7-7-nsParameterSymbol AD404M42V Unit Notes -5-6Min MaxMin MaxEDO page mode read- modify- write cycle CAS precharge to WE delay timet CPW 45-55-ns 10EDO page mode read- modify- write cycle timet PRWC56-68-nsNotes :1. AC measurements assume t T = 2ns.2. An initial pause of 100 is required after power up, and it followed by a minimum of eightinitialization cycles (RAS - only refresh cycle or CAS - before - RAS refresh cycle). If the internal refresh counter is used, a minimun of eight CAS - before - RAS refresh cycles are required.3. In delayed write or read-modify-write cycles, OE must disable output buffer prior to applying data to the device.4. All the V CC and V SS pins shall be supplied with the same voltages.5. t RAS (min) = t RWD (min)+t RWL (min)+t T in read-modify-write cycle.6. t CAS (min) = t CWD (min)+t CWL (min)+t T in read-modify-write cycle.7. t ASC (min), t RCS (min), t WCS (min), and t RPC are determined by the falling edge of CAS .8. t RCD (max) is specified as a reference point only, and t RAC (max) can be met with the t RCD (max) limit.Otherwise, t RAC is controlled exclusively by t CAC if t RCD is greater than the specified t RCD (max) limit. 9. t RAD (max) is specified as a reference point only, and t RAC (max) can be met with the t RAD (max) limit.Otherwise, t RAC is controlled exclusively by t AA if t RAD is greater than the specified t RAD (max) limit. 10. t CRP , t CHR , t RCH , t CPA and t CPW are determined by the rising edge of CAS .11. V IH (min) and V IL (max) are reference levels for measuring timing or input signals. Therefore, transitiontime is measured between V IH and V IL .12. Assumes that t RCD tRCD (max) and t RAD t RAD (max). If t RCD or t RAD is greater than the maximum recommended value shown in this table, t RAC exceeds the value shown. 13. Assumes that (max) and (max).14. Access time is determined by the maximum of t AA , t CAC , t CPA . 15. Assumes that (max) and (max). 16. Either t RCH or t RRH must be satisfied for a read cycle.17. t OFF (max) and t OEZ (max) define the time at which the output achieves the open circuit condition (highimpedance). t OFF is determined by the later rising edge of RAS or CAS.18. t WCS , t RWD , t CWD , and t AWD are not restrictive operating parameters. They are included in the datasheet as electrical characteristics only. If (min), the cycle is an early write cycle and the data out will remain open circuit (high impedance) throughout the entire cycle. If (min),(min), (min) and (min), the cycle is a read-modify-write and the data output will contain data read from the selected cell. If neither of the above sets of conditions is satisfied, the condition of the data output (at access time) is indeterminate.19. These parameters are referenced to CAS separately in an early write cycle and to WE edge in adelayed write or a read-modify-write cycle.20. t RASP defines RAS pulse width in EDO page mode cycles.µs ≤≤t RCD t RCD ≥t RADt RAD ≤t RCD t RCD ≤t RAD t RAD ≥t WCS t WCS ≥t RWD t RWD ≥t CWDt CWD ≥t AWD t AWD ≥t CPW t CPW≥Timing Waveforms• Read Cyclet RC t RASt RPtCRPtCPNtRRHtRCHt OEZ t OFF tOEA tCACt AAtRACt CLZD OUTtRCS t ASR tRAH tASC tCAH tRAD t RALtCAStRSH tRCDt TtCSHRASCASADDRESSWEDQ1~DQ4Note : = don’t care OEt OFFRowColumn= Invalid Dout•Early Write CycletRC t RASt RPt WCHt DSt DHt WCS t RALtCAStRSH tRCDt TtCSHRASCASWEDQ1~DQ4tCRPtASRtRAH tASCtCAH ADDRESSColumnRowtCPND INtRADt RAL• Delayed Write CycletRC t RASt RPt RWL t RCSt CAStRSH tRCDt TtCSHRASCAStASR tRAH tCAHADDRESSColumnRow tASC D INDQ1~DQ4WEtCRPtCPNt DHt DSt OEHt OEDOEt DSOPENt WPt CWL• Read - Modify - Write CycletRWC t RASt RPtRWDt WPtRADtRWL tCAStCWL tRCDt TtCPNRASCASWEtCRP t ASRtRAHtASCtCAHADDRESS Column RowDQ1~DQ4t DHt DSOEtRCStAWD tCWD D INt OEDt OEHt OEZt OEA t CAC t RACt AADQ1~DQ4D OUTOPENtDZCtDZO• EDO Page Mode Read CycletRASPtCPRHt RCStCAStRSH tRCDt OEAtCSHRASCAStASRtRAHtCAHADDRESStCASWEtCRPt CPOEDQ1~DQ4OPENtOEPD OUT 1t PCt CPtCAStCPNtCRPtRADtCAHtASCt ASCtCAHt ASCt RAL Row Column 1t OEAt OEHCtRRH tRCHt RACt AAt AAt AA t CPA t CPA t OEZt OFFt OFFt CACt OEZt CAC t CACt COHD OUT NWE OE Column 2Column N Rowt RPD OUT 2• EDO Page Mode Early Write CycletRASPtRPt WCSt CAStRSH tRCDRASCAStASRtRAHtCAHADDRESStCASWEt CPDQ1~DQ4t PCt CPt CAStCPNtCRP tCAH tASCtASC tCAH tASC Row Column 1t DS WE Column 2Column Nt WCH t WCS t WCH t WCS t WCHt DH t DS t DH t DS t DHD IN 1D IN 2D IN Nt TtCSH• EDO Page Mode Read-Early-Write Cyclet RASPtCPRHt RCStCAStRSH tRCDt OEAtCSHRASCAStASRtRAHtCAHADDRESStCASWEtCRPt CPOEDQ1~DQ4OPENtWEDt PCt CPtCAStCPNtCRPtRADtRAHtASCt ASCtCAHt ASCt RAL Row Column 1tWCStRCHt RACt AAt AAt CPA t DHt WHZt CACt CACt COHWE OE Column 2Column N Rowt RPt CAL tWCHDataDoutput 2Data Input NDataDoutput 1t DStCSH• EDO Page Mode Read-Modify-Write Cyclet RASPt CPRHt RCStCASt WP RASCASt ASRtRAHtCAHADDRESSt CASWEtRCDCPDQ1~DQ4tPRWCt CPtCAStCRPtRADtCAHtASCt ASCtCAH tASC Row Column 1tRWLtRCSt OEDt DZOt CAC WE OEt RPt RAL D OUT 2D OUT ND OUT 1tTt Column NColumn 2Column 1tRWD tAWD tCWDtCWLtRCStCWDtAWD tCPW tCWL tCPW tAWD tCWDtCWL t OEDt OEDt OEHt OEHt OEHt CAC t CAC t OEA t AAt RACt OEZt OEAt AA t CPAt OEZt OEAt AA t CPAt OEZ t DSt DHt WP t DSt DHt WP t DSt DHOPENOPENOPEN D IN 1D IN ND IN 2DQ1~DQ4t DZCt DZOt DZCt DZCt DZO• Read Cycle with WE Controlled Disablet WPZt RCStCAStRCDt TtCSHRASCASt ASRtRAHtCAHADDRESSColumnRow tASCD DQ1~DQ4WEt OEZt DSt WHZOEt RCH t OEA t CACt AAt RACt CLZOUTtRADRASADDRESSt RC t CRPt ASRt RAHt Tt RPCROWt OFFCAS t RASt RPOPENt CRPDQ1~DQ4RASt CSRt WSRt RPt T t RPCt OFFCAS t RASt RPOPENt CRPDQ1~DQ4t RPCt CHRt RASt RPt RCt RCt CHRt CSRt WHRt WSRt WHRWECAS-Before-RAS Refresh CycleRASWEt RPCt OFFt CSRt CHSt WSRCASt RASS t RPSOPENDQ1~DQ4t WHRHigh lmpedance• Hidden Refresh Cyclet RPt RASRASt RCDt CRPADDRESSWEt CHRt CASt RSHt RAHt ASRt ASCt CAHt RAL ROW t RCHt OEZCASDQ1~DQ4t Tt RCSD t RASt RASt RPt RPt RC t RCt RCt RADt RRHt OFF t OFFt OEA t CACt AAt RACCOlumnOUTOE(READ)(REFRESH)(REFRESH)Ordering informationAD404M42VSA-5• AD• Ascend Memory Product • 40 • Device Type• 4M4 • Density and Organization • 2• Refresh Rate, 2: 2K Refresh • V• T: 5V, V: 3.3V• S • Package Type (S : SOJ, T : TSOP II)• A• Version• 5• Speed (5: 50 ns, 6: 60 ns)Part Number Access time PackageAD404M42VSA-5AD404M42VSA-6AD404M42VTA-5AD404M42VTA-650 ns 60 ns 50 ns 60 ns300mil 26/24-Pin Plastic SOJTSOP IIPackaging information • 300 mil, 26/24-Pin Plastic SOJ• 300 mil, 26/24-Pin TSOP II。

FB41-FB42参数详细说明 S7-300 西门子

用Step7 中SFB41/FB 41,SFB42/FB42,SFB43/FB43实现PID控制SLC A&D CSMay 2004目录1概述 (3)1.1应用 (3)1.2控制系统分析 (4)2PID系统控制器的选择 (7)2.1连续控制器、开关控制器 (7)2.2固定值控制器 (8)2.3级联控制器 (8)2.4混合控制器 (8)2.5比例控制器 (9)2.5.1单循环比例控制器 (9)2.5.2多循环比例控制器 (9)2.6二级控制器 (9)2.7三级控制器 (10)3布线 (10)3.1布线规则 (10)3.1.1连接电缆 (10)3.1.2屏蔽端接元件 (10)3.1.3警告 (10)3.1.4其它信息 (10)4参数赋值工具介绍 (10)4.1调试PID参数的用户界面 (11)4.2获取在线帮助的途径 (12)5在用户程序中实现 (12)5.1调用功能块 (12)5.2背景数据块 (13)5.3程序结构 (13)6功能块介绍 (13)6.1连续调节功能SFB 41/FB 41 “CONT_C” (13)6.1.1简介 (13)6.1.2应用程序 (14)6.1.3说明 (14)6.2步进控制功能SFB 42/FB 42“CONT_S” (26)6.2.1简介 (26)6.2.2应用程序 (26)6.2.3说明 (27)6.3脉冲宽度调制器SFB 43/FB 43“PULSEGEN” (36)6.3.1简介 (36)6.3.2应用程序 (36)6.3.3说明 (36)7功能块举例 (49)1 概述本文中所讨论的功能块(SFB41/FB41,SFB42/FB42,SFB43/FB43)仅仅是使用于S7和C7的CPU中的循环中断程序中。

该功能块,定期计算所需要的数据,保存在指定的DB中(背景数据块)。

允许多次调用该功能块。

CONT_C块与PULSEGEN块组合使用,可以获得一个带有比例执行机构脉冲输出的控制器(例如,加热和冷却装置)。

xl4015中文资料_数据手册_参数

Pin Number 1

2 3 4 5

Pin Name GND

FB SW VC VIN

Description

Ground Pin. Care must be taken in layout. This pin should be placed outside of the Schottky Diode to output capacitor ground path to prevent switching current spikes from inducing voltage noise into XL4015. Feedback Pin (FB). Through an external resistor divider network, FB senses the output voltage and regulates it. The feedback threshold voltage is 1.25V. Power Switch Output Pin (SW). SW is the switch node that supplies power to the output. Internal Voltage Regulator Bypass Capacity. In typical system application, The VC pin connect a 1uf capacity to VIN. Supply Voltage Input Pin. XL4015 operates from a 8V to 36V DC voltage. Bypass Vin to GND with a suitably large capacitor to eliminate noise on the input.

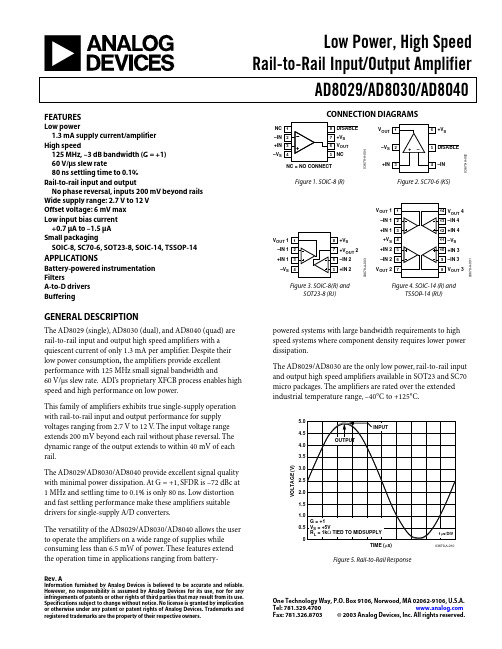

AD8040资料

VOUT 2 7

14 VOUT 4 13 –IN 4 12 +IN 4 11 –VS 10 +IN 3 9 –IN 3 8 VOUT 3

Figure 4. SOIC-14 (R) and TSSOP-14 (RU)

powered systems with large bandwidth requirements to high speed systems where component density requires lower power dissipation.

High speed 125 MHz, –3 dB bandwidth (G = +1) 60 V/µs slew rate 80 ns settling time to 0.1%

Rail-to-rail input and output No phase reversal, inputs 200 mV beyond rails

Absolute Maximum Ratings............................................................ 6 Maximum Power Dissipation ..................................................... 6

VGC401 中文手册

单通道控制器VGC 401使用说明书产品标识与INFICON联系时,请告知产品名牌上的信息。

为便于参考,现将名牌上的信息表示如下:有效性本说明书用于件号为398-010的产品。

件号(PN)可从产品名牌上看到。

本说明书件基于固件版号302-519-A。

如你的仪器工作与本文件的说明不符,请检查是否与上述固件版号(48)相符。

我们保留本说明书不事先通知的技术修改权。

全部尺寸均用毫米表示。

用途V GC401与INFICON生产的规管同时使用,用于真空系统的总压强测量。

全部产品必须按产品说明书使用。

供货范围1件单通道控制器1根电源电缆1根橡皮条2个橡皮脚4个凹槽螺丝4个塑料套管产品标识有效性用途供货范围1 安全1.1 使用符号1.2 人员要求1.3 一般安全规则1.4 责任与保修2 技术参数3 安装3.1 人员3.2 安装,设置3.2.1 机架安装3.2.2 安装在控制屏内3.2.3 用作桌上式仪器3.3 电源连接3.4 传感器连接3.5 控制器连接3.6 RS232接口连接4 运行4.1 面板4.2 VGC401的On和Off 4.3 工作模式4.4 测量模式4.5 参数模式4.5.1 参数4.6 测试模式4.6.1 参数4.6.2 测试程序5 维护6 故障查找7 检修8 附件9 储存10 废物处理附录A. 转换表提供的压强传感器B. 缺省参数C. 软件升级D. 文献E. 索引质量保证书参考在本说明书内的内容使用符号(XY)。

参考“文献”中的内容使用符号([Z])。

1.1 使用符号其它符号灯亮灯闪灯黑按此键(例:’para’键)不要按任何键.1.2 人员要求1.3 一般安全规则对于全部要进行的工作,必须遵守规章制度和采取必要的预防措施和考虑本说明书中的安全规则。

向所有其他用户通报安全信息。

1.4 责任与保修如最终用户或第三方发生以下情况,INFICON将不承担赔偿责任和保修将不再有效。

●不顾本说明书中的信息。

AD401M162VSB-5中文资料

ASCEND Semiconductor 4Mx4 EDO Data sheetDescriptionThe device CMOS Dynamic RAM organized as 4,194,304 words x 4 bits with extended data out access mode. It is fabricated with an advanced submicron CMOS technology and designed to operate from a single 3.3V oniy power supply. Low voltage operation is more suitable to be used on battery backup, portable elec-tronic application. lt is packaged in JEDEC standard 26/24-pin plastic SOJ or TSOP(II).Features• Single 3.3V(%) only power supply • High speed t RAC acess time: 50/60ns • Low power dissipation- Active mode : 432/396 mW (Mas) - Standby mode: 0.54 mW (Mas)• Extended - data - out(EDO) page mode access • I/O level: CMOS level (Vcc = 3.3V)• 2048 refresh cycle in 32 ms(Std.) or 128 ms(S-version)• 4 refresh modesh: - RAS only refresh- CAS - before - RAS refresh - Hidden refresh - Self-refresh(S-version)10±Pin Name FunctionA0-A10Address inputs- Row address - Column address - Refresh address DQ1~DQ4Data-in / data-out RAS Row address strobe CAS Column address strobe WE Write enable OE Output enable Vcc Power (+ 3.3V)VssGroundVCC 1DQ12DQ23DQ34DQ45VCC6891011 NC 12 WE 13A0 A117 A218 A319VSS RAS CAS OE A8A7A6A5A4VSSAD404M42VSPin Description Pin Configuration21222324 2526151416 A1026/24-PIN 300mil Plastic SOJA9VCC 1DQ12DQ23DQ34DQ45VCC6891011 NC 12 WE 13A0 A117 A218 A319VSS RAS CAS OE A8A7 A6A5 A4VSSAD404M42VT212223242526151416 A1026/24-PIN 300mil Plastic TSOP (ll)A9A0-A10A0-A10A0-A10WECASNO. 2 CLOCK GENERATORCOLUMN ADDRESS BUFFERS (11)REFRESH CONTROLLERREFRESH COUNTERBUFFERS (11)ADDRESS ROW NO. 1 CLOCK GENERATORA0RASA1A2A3A4A5A6A7A8CONTROLLOGICDATA-IN BUFFERDATA-OUT BUFFEROEDQ1.DQ4.COLUMN DECODER2048SENSE AMPLIFIERSI/O GATING2048x42048x2048x4MEMORY ARRAY2048R O W D E C O D E RVcc VssBlock DiagramA9A10TRUTH TABLENotes: 1. EARLY WRITE only.FUNCTIONRASCAS WE OE ADDRESSESDQ SNotesROW COL STANDBY H X X X X High-Z READL L H L ROW COL Data-Out WRITE: (EARLY WRITE )L L L X ROW COL Data-lnREAD WRITE L L ROW COL Data-Out,Data-ln EDO-PAGE-MODE READ1st Cycle L H L ROW COL Data-Out 2nd CycleL H L n/a COL Data-Out EDO-PAGE MODE WRITE1st CycleL L X ROW COL Data-In 2nd Cycle L L Xn/a COL Data-InEDO-PAGE-MODEREAD-WRITE 1st Cycle L ROW COL Data-Out, Data-In 2nd Cycle L n/a COL Data-Out, Data-In HIDDEN REFRESHREAD L H L ROW COL Data-Out WRITEL L X ROW COL Data-In 1RAS-ONLY REFRESH L H X X ROW n/a High-Z CBR REFRESHLHXXXHigh-ZH X →H L →L H →H L →H L →H L →H L →H L →H L →L H →H L →H L →L H→L H L →→L H L→→H L→Absolute Maximum RatingsRecommended DC Operating ConditionsCapacitanceTa = 25°C, V CC = 3.3V%, f = 1MHz Note: 1. Capacitance measured with effective capacitance measuring method. 2. RAS, CAS = V IH to disable Dout.ParameterSymbol Value Unit Voltage on any pin relative to Vss V T -0.5 to + 4.6V Supply voltage relative to Vss V CC -0.5 to + 4.6V Short circuit output current I OUT 50mA Power dissipation P D 1.0WOperating temperature T OPT 0 to + 70°C Storage temperatureT STG-55 to + 125°CParameter/Condition Symbol3.3 Volt VersionUnitMinTyp MaxSupply VoltageV CC 3.0 3.33.6V Input High Voltage, all inputs V IH 2.0-V CC + 0.3V Input Low Voltage, all inputsV IL-0.3-0.8VParameterSymbol Typ Max Unit Note Input capacitance (Address)C I1 -5pF 1Input capacitance (RAS, CAS, OE, WE)C I2-7pF 1Output capacitance(Data-in, Data-out)C I/O-7pF1, 210±DC Characteristics :(T a = 0 to 70°C, V CC = + 3.3V%, V SS = 0V)Parameter Symbol Test Conditions AD404M42V Unit Notes-5-6Min Max Min MaxOperating current I CC1RAS cyclingCAS, cyclingt RC = min-120-110mA1, 2Standby Current LowpowerS-versionI CC2LVTTL interfaceRAS, CAS = V IHDout = High-Z-0.5-0.5mACMOS interfaceRAS, -0.2VDout = High-Z-0.15-0.15mAStandardpowerversionLVTTL interfaceRAS, CAS = V IHDout = High-Z-2-2mACMOS interfaceRAS,-0.2VDout = High-Z-0.5-0.5mARAS- only refresh current I CC3RAS cycling, CAS = V IHt RC = min-120-110mA1, 2 EDO page mode current I CC4t PC = min-90-80mA1, 3CAS- before- RAS refresh current I CC5t RC = minRAS, CAS cycling-120-110mA1, 2Self- refresh current (S-Version)I CC8 - 550 - 55010±CAS V CC≥CAS V CC≥t RASS100µs≥µADC Characteristics :(T a = 0 to 70°C , V CC = +3.3V %, V SS = 0V)Notes:1. I CC is specified as an average current. It depends on output loading condition and cycle rate when the device is selected. I CC max is specified at the output open condition.2. Address can be changed once or less while RAS = V IL .3. For I CC4, address can be changed once or less within one EDO page mode cycle time.Parameter Symbol Test Conditions AD404M42VUnitNotes-5-6Min MaxMin MaxInput leakage current I LI + 0.3V -55-55Output leakage current I LO + 0.3V Dout = Disable -55-55Output high Voltage V OH I OH = -2mA 2.4- 2.4-V Output low voltage V OLI OL = +2mA-0.4-0.4V10±0V Vin V CC ≤≤µA 0V Vout V CC ≤≤µAAC Characteristics(T a = 0 to + 70°C , V cc = 3.3V %, V ss = 0V) *1, *2, *3, *4Test conditions• Output load: one TTL Load and 100pF (V CC = 3.3V %)• Input timing reference levels:V IH = 2.0V, V IL = 0.8V (V CC = 3.3V %)• Output timing reference levels:V OH = 2.0V, V OL = 0.8V10±10±10±Read, Write, Read- Modify- Write and Refresh Cycles (Common Parameters)ParameterSymbol AD404M42V UnitNotes-5-6Min MaxMin MaxRandom read or write cycle time t RC 84-104-ns RAS precharge timet RP 30-40-ns CAS precharge time in normal mode t CPN 10-10-ns RAS pulse width t RAS 50100006010000ns 5CAS pulse width t CAS 8100001010000ns 6Row address setup time t ASR 0-0-ns Row address hold time t RAH 8-10-ns Column address setup time t ASC 0-0-ns 7Column address hold time t CAH 8-10-ns RAS to CAS delay timet RCD 12371445ns 8RAS to column address delay time t RAD 10251230ns 9Column address to RAS lead time t RAL 25-30-ns RAS hold time t RSH 8-10-ns CAS hold timet CSH 38-40-ns CAS to RAS precharge time t CRP 5-5-ns 10OE to Din delay time t OED 12-15-ns Transition time (rise and fall)t T 150150ns 11Refresh periodt REF -32-32ms Refresh period (S- Version)t REF -128-128ms CAS to output in Low- Z t CLZ 0-0-ns CAS delay time from Din t DZC 0-0-ns OE delay time from Dint DZO-0-nsRead CycleWrite Cycle Parameter SymbolAD404M42V Unit Notes-5-6Min Max Min MaxAccess time from RAS t RAC-50-60ns12 Access time from CAS t CAC-14-15ns13, 14 Access time from column address t AA-25-30ns14, 15 Access time from OE t OEA-12-15nsRead command setup time t RCS0-0-ns7 Read command hold time to CAS t RCH0-0-ns10, 16 Read command hold time to RAS t RRH0-0-ns16 Output buffer turn-off time t OFF012015ns17 Output buffer turn-off time from OE t OEZ012015ns17Parameter SymbolAD404M42V Unit Notes -5-6Min Max Min MaxWrite command setup time t WCS0-0-ns7, 18 Write command hold time t WCH8-10-nsWrite command pulse width t WP8-10-nsWrite command to RAS lead time t RWL13-15-nsWrite command to CAS lead time t CWL8-10-nsData-in setup time t DS0-0-ns19 Data-in hold time t DH8-10-ns19 WE to Data-in delay t WED10-10-nsRead- Modify- Write CycleRefresh Cycle Parameter SymbolAD404M42V Unit Notes-5-6Min Max Min MaxRead-modify- write cycle time t RWC108-133-nsRAS to WE delay time t RWD64-77-ns18 CAS to WE dealy time t CWD26-32-ns18 Column address to WE delay time t AWD39-47-ns18 OE hold time from WE t OEH8-10-nsParameter SymbolAD404M42VUnit Notes -5-6Min Max Min MaxCAS setup time (CBR refresh) t CSR5-5-nsCAS hold time (CBR refresh)t CHR8-10-ns10 RAS precharge to CAS hold time t RPC5-5-ns7 RAS pulse width (self refresh)t RASS100-100-RAS precharge time (self refresh)t RPS90-110-nsCAS hold time (CBR self refresh)t CHS-50--50-nsWE setup time t WSR0-0-nsWE hold time t WHR10-10-nsµsEDO Page Mode CycleEDO Page Mode Read Modify Write CycleParameterSymbol AD404M42VUnit Notes-5-6Min MaxMin MaxEDO page mode cycle timet PC 20-25-ns EDO page mode CAS precharge time t CP 10-10-ns EDO page mode RAS pulse width t RASP 5010560105ns 20Access time from CAS precharge t CPA -30-35ns 10, 14RAS hold time from CAS precharge t CPRH 30-35-ns OE high hold time from CAS high t OEHC 5-5-ns OE high pulse widtht OEP 10-10-ns Data output hold time after CAS low t COH 5-5-ns Output disable delay from WEt WHZ 310310ns WE pulse width for output disable whenCAS hight WPZ7-7-nsParameterSymbol AD404M42V Unit Notes -5-6Min MaxMin MaxEDO page mode read- modify- write cycle CAS precharge to WE delay timet CPW 45-55-ns 10EDO page mode read- modify- write cycle timet PRWC56-68-nsNotes :1. AC measurements assume t T = 2ns.2. An initial pause of 100 is required after power up, and it followed by a minimum of eightinitialization cycles (RAS - only refresh cycle or CAS - before - RAS refresh cycle). If the internal refresh counter is used, a minimun of eight CAS - before - RAS refresh cycles are required.3. In delayed write or read-modify-write cycles, OE must disable output buffer prior to applying data to the device.4. All the V CC and V SS pins shall be supplied with the same voltages.5. t RAS (min) = t RWD (min)+t RWL (min)+t T in read-modify-write cycle.6. t CAS (min) = t CWD (min)+t CWL (min)+t T in read-modify-write cycle.7. t ASC (min), t RCS (min), t WCS (min), and t RPC are determined by the falling edge of CAS .8. t RCD (max) is specified as a reference point only, and t RAC (max) can be met with the t RCD (max) limit.Otherwise, t RAC is controlled exclusively by t CAC if t RCD is greater than the specified t RCD (max) limit. 9. t RAD (max) is specified as a reference point only, and t RAC (max) can be met with the t RAD (max) limit.Otherwise, t RAC is controlled exclusively by t AA if t RAD is greater than the specified t RAD (max) limit. 10. t CRP , t CHR , t RCH , t CPA and t CPW are determined by the rising edge of CAS .11. V IH (min) and V IL (max) are reference levels for measuring timing or input signals. Therefore, transitiontime is measured between V IH and V IL .12. Assumes that t RCD tRCD (max) and t RAD t RAD (max). If t RCD or t RAD is greater than the maximum recommended value shown in this table, t RAC exceeds the value shown. 13. Assumes that (max) and (max).14. Access time is determined by the maximum of t AA , t CAC , t CPA . 15. Assumes that (max) and (max). 16. Either t RCH or t RRH must be satisfied for a read cycle.17. t OFF (max) and t OEZ (max) define the time at which the output achieves the open circuit condition (highimpedance). t OFF is determined by the later rising edge of RAS or CAS.18. t WCS , t RWD , t CWD , and t AWD are not restrictive operating parameters. They are included in the datasheet as electrical characteristics only. If (min), the cycle is an early write cycle and the data out will remain open circuit (high impedance) throughout the entire cycle. If (min),(min), (min) and (min), the cycle is a read-modify-write and the data output will contain data read from the selected cell. If neither of the above sets of conditions is satisfied, the condition of the data output (at access time) is indeterminate.19. These parameters are referenced to CAS separately in an early write cycle and to WE edge in adelayed write or a read-modify-write cycle.20. t RASP defines RAS pulse width in EDO page mode cycles.µs ≤≤t RCD t RCD ≥t RADt RAD ≤t RCD t RCD ≤t RAD t RAD ≥t WCS t WCS ≥t RWD t RWD ≥t CWDt CWD ≥t AWD t AWD ≥t CPW t CPW≥Timing Waveforms• Read Cyclet RC t RASt RPtCRPtCPNtRRHtRCHt OEZ t OFF tOEA tCACt AAtRACt CLZD OUTtRCS t ASR tRAH tASC tCAH tRAD t RALtCAStRSH tRCDt TtCSHRASCASADDRESSWEDQ1~DQ4Note : = don’t care OEt OFFRowColumn= Invalid Dout•Early Write CycletRC t RASt RPt WCHt DSt DHt WCS t RALtCAStRSH tRCDt TtCSHRASCASWEDQ1~DQ4tCRPtASRtRAH tASCtCAH ADDRESSColumnRowtCPND INtRADt RAL• Delayed Write CycletRC t RASt RPt RWL t RCSt CAStRSH tRCDt TtCSHRASCAStASR tRAH tCAHADDRESSColumnRow tASC D INDQ1~DQ4WEtCRPtCPNt DHt DSt OEHt OEDOEt DSOPENt WPt CWL• Read - Modify - Write CycletRWC t RASt RPtRWDt WPtRADtRWL tCAStCWL tRCDt TtCPNRASCASWEtCRP t ASRtRAHtASCtCAHADDRESS Column RowDQ1~DQ4t DHt DSOEtRCStAWD tCWD D INt OEDt OEHt OEZt OEA t CAC t RACt AADQ1~DQ4D OUTOPENtDZCtDZO• EDO Page Mode Read CycletRASPtCPRHt RCStCAStRSH tRCDt OEAtCSHRASCAStASRtRAHtCAHADDRESStCASWEtCRPt CPOEDQ1~DQ4OPENtOEPD OUT 1t PCt CPtCAStCPNtCRPtRADtCAHtASCt ASCtCAHt ASCt RAL Row Column 1t OEAt OEHCtRRH tRCHt RACt AAt AAt AA t CPA t CPA t OEZt OFFt OFFt CACt OEZt CAC t CACt COHD OUT NWE OE Column 2Column N Rowt RPD OUT 2• EDO Page Mode Early Write CycletRASPtRPt WCSt CAStRSH tRCDRASCAStASRtRAHtCAHADDRESStCASWEt CPDQ1~DQ4t PCt CPt CAStCPNtCRP tCAH tASCtASC tCAH tASC Row Column 1t DS WE Column 2Column Nt WCH t WCS t WCH t WCS t WCHt DH t DS t DH t DS t DHD IN 1D IN 2D IN Nt TtCSH• EDO Page Mode Read-Early-Write Cyclet RASPtCPRHt RCStCAStRSH tRCDt OEAtCSHRASCAStASRtRAHtCAHADDRESStCASWEtCRPt CPOEDQ1~DQ4OPENtWEDt PCt CPtCAStCPNtCRPtRADtRAHtASCt ASCtCAHt ASCt RAL Row Column 1tWCStRCHt RACt AAt AAt CPA t DHt WHZt CACt CACt COHWE OE Column 2Column N Rowt RPt CAL tWCHDataDoutput 2Data Input NDataDoutput 1t DStCSH• EDO Page Mode Read-Modify-Write Cyclet RASPt CPRHt RCStCASt WP RASCASt ASRtRAHtCAHADDRESSt CASWEtRCDCPDQ1~DQ4tPRWCt CPtCAStCRPtRADtCAHtASCt ASCtCAH tASC Row Column 1tRWLtRCSt OEDt DZOt CAC WE OEt RPt RAL D OUT 2D OUT ND OUT 1tTt Column NColumn 2Column 1tRWD tAWD tCWDtCWLtRCStCWDtAWD tCPW tCWL tCPW tAWD tCWDtCWL t OEDt OEDt OEHt OEHt OEHt CAC t CAC t OEA t AAt RACt OEZt OEAt AA t CPAt OEZt OEAt AA t CPAt OEZ t DSt DHt WP t DSt DHt WP t DSt DHOPENOPENOPEN D IN 1D IN ND IN 2DQ1~DQ4t DZCt DZOt DZCt DZCt DZO• Read Cycle with WE Controlled Disablet WPZt RCStCAStRCDt TtCSHRASCASt ASRtRAHtCAHADDRESSColumnRow tASCD DQ1~DQ4WEt OEZt DSt WHZOEt RCH t OEA t CACt AAt RACt CLZOUTtRADRASADDRESSt RC t CRPt ASRt RAHt Tt RPCROWt OFFCAS t RASt RPOPENt CRPDQ1~DQ4RASt CSRt WSRt RPt T t RPCt OFFCAS t RASt RPOPENt CRPDQ1~DQ4t RPCt CHRt RASt RPt RCt RCt CHRt CSRt WHRt WSRt WHRWECAS-Before-RAS Refresh CycleRASWEt RPCt OFFt CSRt CHSt WSRCASt RASS t RPSOPENDQ1~DQ4t WHRHigh lmpedance• Hidden Refresh Cyclet RPt RASRASt RCDt CRPADDRESSWEt CHRt CASt RSHt RAHt ASRt ASCt CAHt RAL ROW t RCHt OEZCASDQ1~DQ4t Tt RCSD t RASt RASt RPt RPt RC t RCt RCt RADt RRHt OFF t OFFt OEA t CACt AAt RACCOlumnOUTOE(READ)(REFRESH)(REFRESH)Ordering informationAD404M42VSA-5• AD• Ascend Memory Product • 40 • Device Type• 4M4 • Density and Organization • 2• Refresh Rate, 2: 2K Refresh • V• T: 5V, V: 3.3V• S • Package Type (S : SOJ, T : TSOP II)• A• Version• 5• Speed (5: 50 ns, 6: 60 ns)Part Number Access time PackageAD404M42VSA-5AD404M42VSA-6AD404M42VTA-5AD404M42VTA-650 ns 60 ns 50 ns 60 ns300mil 26/24-Pin Plastic SOJTSOP IIPackaging information • 300 mil, 26/24-Pin Plastic SOJ• 300 mil, 26/24-Pin TSOP II。

AD420中文资料

AD420中文资料摘要:AD420是具有灵活串行数字接口的16住数模转换器,它带有SPI和Microwire总线接口,使用方便、性价比高。

介绍了AD420的引脚功能、电气特性,阐述了AD420与MSP430的接口技术,并给出了在MSP430控制下的实际应用电路及程序。

关键词:AD420;D/A转换;MSP430;电流环1 概述AD420是ADI公司生产的高精度、低功耗全数字电流环输出转换器。

AD420的输出信号可以是电流信号,也可以是电压信号。

其中电流信号的输出范围为4mA~20mA,0mA~20mA或0mA~24mA,具体可通过引脚RANGE SELECTl,RANGE SELECT2进行配置。

当需要输出电压信号时,它也能从一个隔离引脚提供电压输出,这时需外接一个缓冲放大器,可输出0V~5V,0V~10V,±5V 或±10V电压。

AD420具有灵活的串行数字接口(最大速率可达3.3 Mb/s),使用方便、性价比高、抑制干扰能力强,非常适合用于高精度远程控制系统。

AD420与单片机的接口方式有2种:3线制和异步制。

单片机系统通过AD420可实现连续的模拟量输出。

其主要特点如下:宽泛的电源电压范围为12 V~32 V,输出电压范围为0V~-2.5 V;带有3线模式的SPI或Microwire接口,可采集连续的模拟输入信号,采用异步模式时仅需少量的信号线;数据输出引脚可将多个AD420器件连接成菊链型;上电初始化时,其输出最小值为0 mA,4 mA或O V;具有异步清零引脚,可将输出复位至最小值(0mA、4 mA或0V);BOOST引脚可连接一个外部晶体管来吸收回路电流,降低功耗;只需外接少量的外部器件,就能达到较高的精度。

AD420采用24引脚SOIC和PDIP封装,表1是其引脚功能说明。

2 工作原理在AD420中,二阶调节器用于保持最小死区。

从调节器发出的单字节流控制开关电流源,两个连续的电阻电容装置进行过滤。

DAP401中文资料

1)Valid, if leads are kept at ambient temperature at a distance of 3 mm from caseGültig, wenn die Anschlußdrähte in 3 mm Abstand von Gehäuse auf Umgebungstemperatur gehalten werden 35828.02.2002Small Signal Diode ArraysDioden Sätze mit AllzweckdiodenNominal power dissipation 200 mW Nenn-VerlustleistungRepetitive peak reverse voltage 80 VPeriodische Spitzensperrspannung 5 Pin-Plastic case13 x 3.5 x 6.6 [mm]5 Pin-Kunststoffgehäuse Weight approx. – Gewicht ca.0.6 g Dimensions / Maße in mmStandard packaging: bulksee page 22Standard Lieferform: lose im Kartons. Seite 22"DAP": common anodes / gemeinsame Anoden "DAN": common cathodes / gemeinsame KathodenMaximum ratings GrenzwerteType Typ Repetitive peak reverse voltage Periodische SpitzensperrspannungV RRM [V]Surge peak reverse voltage StoßspitzensperrspannungV RSM [V]DAN 4018080DAP 4018080Max. average forward rectified current, R-load,T A = 25/Cfor one diode operation onlyI FAV 100 mA 1)per diode for simultaneous operation I FAV 50 mA 1)Dauergrenzstrom in Einwegschaltung mit R-Last,T U = 25/Cfür eine einzelne DiodeI FAV 100 mA 1)pro Diode bei gleichzeitigem Betrieb I FAV 50 mA 1)Peak forward surge current, 50 Hz half sine-wave T A = 25/CI FSM500 mAStoßstrom für eine 50 Hz Sinus-Halbwelle1)Valid, if leads are kept at ambient temperature at a distance of 3 mm from caseGültig, wenn die Anschlußdrähte in 3 mm Abstand von Gehäuse auf Umgebungstemperatur gehalten werden 35928.02.2002Operating junction temperature – Sperrschichttemperatur T j – 50…+150/C Storage temperature – LagerungstemperaturT S– 50…+150/CCharacteristics KennwerteForward voltage T j = 25/C I F = 10 mA V F < 1.0 V Durchlaßspannung Leakage current T j = 25/CV R = 20 VI R < 25 nA SperrstromReverse recovery time I F = 10 mA through/über t rr < 4 ns SperrverzugI R = 10 mA to/auf I R = 1 mAThermal resistance junction to ambient airR thA< 85 K/W 1)Wärmewiderstand Sperrschicht – umgebende Luft。

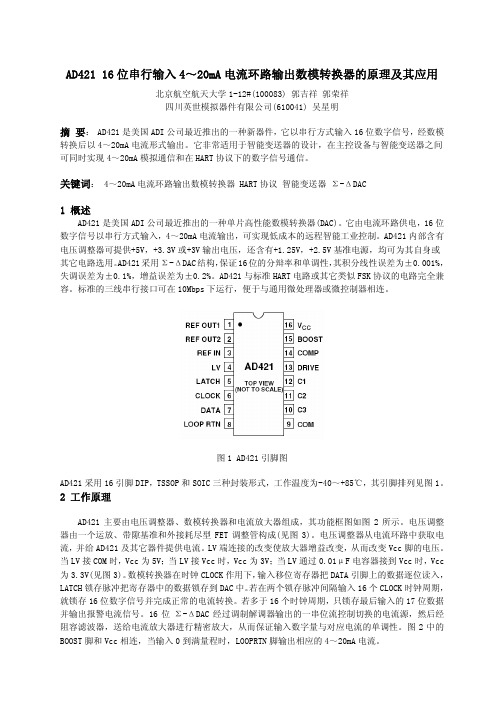

AD421原理及应用

AD421 16位串行输入4~20mA电流环路输出数模转换器的原理及其应用北京航空航天大学1-12#(100083) 郭吉祥 郭荣祥四川英世模拟器件有限公司(610041) 吴星明摘 要: AD421是美国ADI公司最近推出的一种新器件,它以串行方式输入16位数字信号,经数模转换后以4~20mA电流形式输出。

它非常适用于智能变送器的设计,在主控设备与智能变送器之间可同时实现4~20mA模拟通信和在HART协议下的数字信号通信。

关键词: 4~20mA电流环路输出数模转换器 HART协议 智能变送器 Σ-ΔDAC1 概述AD421是美国ADI公司最近推出的一种单片高性能数模转换器(DAC)。

它由电流环路供电,16位数字信号以串行方式输入,4~20mA电流输出,可实现低成本的远程智能工业控制。

AD421内部含有电压调整器可提供+5V,+3.3V或+3V输出电压,还含有+1.25V,+2.5V基准电源,均可为其自身或其它电路选用。

AD421采用Σ-ΔDAC结构,保证16位的分辩率和单调性,其积分线性误差为±0.001%,失调误差为±0.1%,增益误差为±0.2%。

AD421与标准HART电路或其它类似FSK协议的电路完全兼容。

标准的三线串行接口可在10Mbps下运行,便于与通用微处理器或微控制器相连。

图1 AD421引脚图AD421采用16引脚DIP,TSSOP和SOIC三种封装形式,工作温度为-40~+85℃,其引脚排列见图1。

2 工作原理AD421主要由电压调整器、数模转换器和电流放大器组成,其功能框图如图2所示。

电压调整器由一个运放、带隙基准和外接耗尽型FET调整管构成(见图3)。

电压调整器从电流环路中获取电流,并给AD421及其它器件提供电流。

LV端连接的改变使放大器增益改变,从而改变Vcc脚的电压。

当LV接COM时,Vcc为5V;当LV接Vcc时,Vcc为3V;当LV通过0.01μF电容器接到Vcc时,Vcc 为3.3V(见图3)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

ASCEND Semiconductor 4Mx4 EDO Data sheetDescriptionThe device CMOS Dynamic RAM organized as 4,194,304 words x 4 bits with extended data out access mode. It is fabricated with an advanced submicron CMOS technology and designed to operate from a single 3.3V oniy power supply. Low voltage operation is more suitable to be used on battery backup, portable elec-tronic application. lt is packaged in JEDEC standard 26/24-pin plastic SOJ or TSOP(II).Features• Single 3.3V(%) only power supply • High speed t RAC acess time: 50/60ns • Low power dissipation- Active mode : 432/396 mW (Mas) - Standby mode: 0.54 mW (Mas)• Extended - data - out(EDO) page mode access • I/O level: CMOS level (Vcc = 3.3V)• 2048 refresh cycle in 32 ms(Std.) or 128 ms(S-version)• 4 refresh modesh: - RAS only refresh- CAS - before - RAS refresh - Hidden refresh - Self-refresh(S-version)10±Pin Name FunctionA0-A10Address inputs- Row address - Column address - Refresh address DQ1~DQ4Data-in / data-out RAS Row address strobe CAS Column address strobe WE Write enable OE Output enable Vcc Power (+ 3.3V)VssGroundVCC 1DQ12DQ23DQ34DQ45VCC6891011 NC 12 WE 13A0 A117 A218 A319VSS RAS CAS OE A8A7A6A5A4VSSAD404M42VSPin Description Pin Configuration21222324 2526151416 A1026/24-PIN 300mil Plastic SOJA9VCC 1DQ12DQ23DQ34DQ45VCC6891011 NC 12 WE 13A0 A117 A218 A319VSS RAS CAS OE A8A7 A6A5 A4VSSAD404M42VT212223242526151416 A1026/24-PIN 300mil Plastic TSOP (ll)A9A0-A10A0-A10A0-A10WECASNO. 2 CLOCK GENERATORCOLUMN ADDRESS BUFFERS (11)REFRESH CONTROLLERREFRESH COUNTERBUFFERS (11)ADDRESS ROW NO. 1 CLOCK GENERATORA0RASA1A2A3A4A5A6A7A8CONTROLLOGICDATA-IN BUFFERDATA-OUT BUFFEROEDQ1.DQ4.COLUMN DECODER2048SENSE AMPLIFIERSI/O GATING2048x42048x2048x4MEMORY ARRAY2048R O W D E C O D E RVcc VssBlock DiagramA9A10TRUTH TABLENotes: 1. EARLY WRITE only.FUNCTIONRASCAS WE OE ADDRESSESDQ SNotesROW COL STANDBY H X X X X High-Z READL L H L ROW COL Data-Out WRITE: (EARLY WRITE )L L L X ROW COL Data-lnREAD WRITE L L ROW COL Data-Out,Data-ln EDO-PAGE-MODE READ1st Cycle L H L ROW COL Data-Out 2nd CycleL H L n/a COL Data-Out EDO-PAGE MODE WRITE1st CycleL L X ROW COL Data-In 2nd Cycle L L Xn/a COL Data-InEDO-PAGE-MODEREAD-WRITE 1st Cycle L ROW COL Data-Out, Data-In 2nd Cycle L n/a COL Data-Out, Data-In HIDDEN REFRESHREAD L H L ROW COL Data-Out WRITEL L X ROW COL Data-In 1RAS-ONLY REFRESH L H X X ROW n/a High-Z CBR REFRESHLHXXXHigh-ZH X →H L →L H →H L →H L →H L →H L →H L →H L →L H →H L →H L →L H→L H L →→L H L→→H L→Absolute Maximum RatingsRecommended DC Operating ConditionsCapacitanceTa = 25°C, V CC = 3.3V%, f = 1MHz Note: 1. Capacitance measured with effective capacitance measuring method. 2. RAS, CAS = V IH to disable Dout.ParameterSymbol Value Unit Voltage on any pin relative to Vss V T -0.5 to + 4.6V Supply voltage relative to Vss V CC -0.5 to + 4.6V Short circuit output current I OUT 50mA Power dissipation P D 1.0WOperating temperature T OPT 0 to + 70°C Storage temperatureT STG-55 to + 125°CParameter/Condition Symbol3.3 Volt VersionUnitMinTyp MaxSupply VoltageV CC 3.0 3.33.6V Input High Voltage, all inputs V IH 2.0-V CC + 0.3V Input Low Voltage, all inputsV IL-0.3-0.8VParameterSymbol Typ Max Unit Note Input capacitance (Address)C I1 -5pF 1Input capacitance (RAS, CAS, OE, WE)C I2-7pF 1Output capacitance(Data-in, Data-out)C I/O-7pF1, 210±DC Characteristics :(T a = 0 to 70°C, V CC = + 3.3V%, V SS = 0V)Parameter Symbol Test Conditions AD404M42V Unit Notes-5-6Min Max Min MaxOperating current I CC1RAS cyclingCAS, cyclingt RC = min-120-110mA1, 2Standby Current LowpowerS-versionI CC2LVTTL interfaceRAS, CAS = V IHDout = High-Z-0.5-0.5mACMOS interfaceRAS, -0.2VDout = High-Z-0.15-0.15mAStandardpowerversionLVTTL interfaceRAS, CAS = V IHDout = High-Z-2-2mACMOS interfaceRAS,-0.2VDout = High-Z-0.5-0.5mARAS- only refresh current I CC3RAS cycling, CAS = V IHt RC = min-120-110mA1, 2 EDO page mode current I CC4t PC = min-90-80mA1, 3CAS- before- RAS refresh current I CC5t RC = minRAS, CAS cycling-120-110mA1, 2Self- refresh current (S-Version)I CC8 - 550 - 55010±CAS V CC≥CAS V CC≥t RASS100µs≥µADC Characteristics :(T a = 0 to 70°C , V CC = +3.3V %, V SS = 0V)Notes:1. I CC is specified as an average current. It depends on output loading condition and cycle rate when the device is selected. I CC max is specified at the output open condition.2. Address can be changed once or less while RAS = V IL .3. For I CC4, address can be changed once or less within one EDO page mode cycle time.Parameter Symbol Test Conditions AD404M42VUnitNotes-5-6Min MaxMin MaxInput leakage current I LI + 0.3V -55-55Output leakage current I LO + 0.3V Dout = Disable -55-55Output high Voltage V OH I OH = -2mA 2.4- 2.4-V Output low voltage V OLI OL = +2mA-0.4-0.4V10±0V Vin V CC ≤≤µA 0V Vout V CC ≤≤µAAC Characteristics(T a = 0 to + 70°C , V cc = 3.3V %, V ss = 0V) *1, *2, *3, *4Test conditions• Output load: one TTL Load and 100pF (V CC = 3.3V %)• Input timing reference levels:V IH = 2.0V, V IL = 0.8V (V CC = 3.3V %)• Output timing reference levels:V OH = 2.0V, V OL = 0.8V10±10±10±Read, Write, Read- Modify- Write and Refresh Cycles (Common Parameters)ParameterSymbol AD404M42V UnitNotes-5-6Min MaxMin MaxRandom read or write cycle time t RC 84-104-ns RAS precharge timet RP 30-40-ns CAS precharge time in normal mode t CPN 10-10-ns RAS pulse width t RAS 50100006010000ns 5CAS pulse width t CAS 8100001010000ns 6Row address setup time t ASR 0-0-ns Row address hold time t RAH 8-10-ns Column address setup time t ASC 0-0-ns 7Column address hold time t CAH 8-10-ns RAS to CAS delay timet RCD 12371445ns 8RAS to column address delay time t RAD 10251230ns 9Column address to RAS lead time t RAL 25-30-ns RAS hold time t RSH 8-10-ns CAS hold timet CSH 38-40-ns CAS to RAS precharge time t CRP 5-5-ns 10OE to Din delay time t OED 12-15-ns Transition time (rise and fall)t T 150150ns 11Refresh periodt REF -32-32ms Refresh period (S- Version)t REF -128-128ms CAS to output in Low- Z t CLZ 0-0-ns CAS delay time from Din t DZC 0-0-ns OE delay time from Dint DZO-0-nsRead CycleWrite Cycle Parameter SymbolAD404M42V Unit Notes-5-6Min Max Min MaxAccess time from RAS t RAC-50-60ns12 Access time from CAS t CAC-14-15ns13, 14 Access time from column address t AA-25-30ns14, 15 Access time from OE t OEA-12-15nsRead command setup time t RCS0-0-ns7 Read command hold time to CAS t RCH0-0-ns10, 16 Read command hold time to RAS t RRH0-0-ns16 Output buffer turn-off time t OFF012015ns17 Output buffer turn-off time from OE t OEZ012015ns17Parameter SymbolAD404M42V Unit Notes -5-6Min Max Min MaxWrite command setup time t WCS0-0-ns7, 18 Write command hold time t WCH8-10-nsWrite command pulse width t WP8-10-nsWrite command to RAS lead time t RWL13-15-nsWrite command to CAS lead time t CWL8-10-nsData-in setup time t DS0-0-ns19 Data-in hold time t DH8-10-ns19 WE to Data-in delay t WED10-10-nsRead- Modify- Write CycleRefresh Cycle Parameter SymbolAD404M42V Unit Notes-5-6Min Max Min MaxRead-modify- write cycle time t RWC108-133-nsRAS to WE delay time t RWD64-77-ns18 CAS to WE dealy time t CWD26-32-ns18 Column address to WE delay time t AWD39-47-ns18 OE hold time from WE t OEH8-10-nsParameter SymbolAD404M42VUnit Notes -5-6Min Max Min MaxCAS setup time (CBR refresh) t CSR5-5-nsCAS hold time (CBR refresh)t CHR8-10-ns10 RAS precharge to CAS hold time t RPC5-5-ns7 RAS pulse width (self refresh)t RASS100-100-RAS precharge time (self refresh)t RPS90-110-nsCAS hold time (CBR self refresh)t CHS-50--50-nsWE setup time t WSR0-0-nsWE hold time t WHR10-10-nsµsEDO Page Mode CycleEDO Page Mode Read Modify Write CycleParameterSymbol AD404M42VUnit Notes-5-6Min MaxMin MaxEDO page mode cycle timet PC 20-25-ns EDO page mode CAS precharge time t CP 10-10-ns EDO page mode RAS pulse width t RASP 5010560105ns 20Access time from CAS precharge t CPA -30-35ns 10, 14RAS hold time from CAS precharge t CPRH 30-35-ns OE high hold time from CAS high t OEHC 5-5-ns OE high pulse widtht OEP 10-10-ns Data output hold time after CAS low t COH 5-5-ns Output disable delay from WEt WHZ 310310ns WE pulse width for output disable whenCAS hight WPZ7-7-nsParameterSymbol AD404M42V Unit Notes -5-6Min MaxMin MaxEDO page mode read- modify- write cycle CAS precharge to WE delay timet CPW 45-55-ns 10EDO page mode read- modify- write cycle timet PRWC56-68-nsNotes :1. AC measurements assume t T = 2ns.2. An initial pause of 100 is required after power up, and it followed by a minimum of eightinitialization cycles (RAS - only refresh cycle or CAS - before - RAS refresh cycle). If the internal refresh counter is used, a minimun of eight CAS - before - RAS refresh cycles are required.3. In delayed write or read-modify-write cycles, OE must disable output buffer prior to applying data to the device.4. All the V CC and V SS pins shall be supplied with the same voltages.5. t RAS (min) = t RWD (min)+t RWL (min)+t T in read-modify-write cycle.6. t CAS (min) = t CWD (min)+t CWL (min)+t T in read-modify-write cycle.7. t ASC (min), t RCS (min), t WCS (min), and t RPC are determined by the falling edge of CAS .8. t RCD (max) is specified as a reference point only, and t RAC (max) can be met with the t RCD (max) limit.Otherwise, t RAC is controlled exclusively by t CAC if t RCD is greater than the specified t RCD (max) limit. 9. t RAD (max) is specified as a reference point only, and t RAC (max) can be met with the t RAD (max) limit.Otherwise, t RAC is controlled exclusively by t AA if t RAD is greater than the specified t RAD (max) limit. 10. t CRP , t CHR , t RCH , t CPA and t CPW are determined by the rising edge of CAS .11. V IH (min) and V IL (max) are reference levels for measuring timing or input signals. Therefore, transitiontime is measured between V IH and V IL .12. Assumes that t RCD tRCD (max) and t RAD t RAD (max). If t RCD or t RAD is greater than the maximum recommended value shown in this table, t RAC exceeds the value shown. 13. Assumes that (max) and (max).14. Access time is determined by the maximum of t AA , t CAC , t CPA . 15. Assumes that (max) and (max). 16. Either t RCH or t RRH must be satisfied for a read cycle.17. t OFF (max) and t OEZ (max) define the time at which the output achieves the open circuit condition (highimpedance). t OFF is determined by the later rising edge of RAS or CAS.18. t WCS , t RWD , t CWD , and t AWD are not restrictive operating parameters. They are included in the datasheet as electrical characteristics only. If (min), the cycle is an early write cycle and the data out will remain open circuit (high impedance) throughout the entire cycle. If (min),(min), (min) and (min), the cycle is a read-modify-write and the data output will contain data read from the selected cell. If neither of the above sets of conditions is satisfied, the condition of the data output (at access time) is indeterminate.19. These parameters are referenced to CAS separately in an early write cycle and to WE edge in adelayed write or a read-modify-write cycle.20. t RASP defines RAS pulse width in EDO page mode cycles.µs ≤≤t RCD t RCD ≥t RADt RAD ≤t RCD t RCD ≤t RAD t RAD ≥t WCS t WCS ≥t RWD t RWD ≥t CWDt CWD ≥t AWD t AWD ≥t CPW t CPW≥Timing Waveforms• Read Cyclet RC t RASt RPtCRPtCPNtRRHtRCHt OEZ t OFF tOEA tCACt AAtRACt CLZD OUTtRCS t ASR tRAH tASC tCAH tRAD t RALtCAStRSH tRCDt TtCSHRASCASADDRESSWEDQ1~DQ4Note : = don’t care OEt OFFRowColumn= Invalid Dout•Early Write CycletRC t RASt RPt WCHt DSt DHt WCS t RALtCAStRSH tRCDt TtCSHRASCASWEDQ1~DQ4tCRPtASRtRAH tASCtCAH ADDRESSColumnRowtCPND INtRADt RAL• Delayed Write CycletRC t RASt RPt RWL t RCSt CAStRSH tRCDt TtCSHRASCAStASR tRAH tCAHADDRESSColumnRow tASC D INDQ1~DQ4WEtCRPtCPNt DHt DSt OEHt OEDOEt DSOPENt WPt CWL• Read - Modify - Write CycletRWC t RASt RPtRWDt WPtRADtRWL tCAStCWL tRCDt TtCPNRASCASWEtCRP t ASRtRAHtASCtCAHADDRESS Column RowDQ1~DQ4t DHt DSOEtRCStAWD tCWD D INt OEDt OEHt OEZt OEA t CAC t RACt AADQ1~DQ4D OUTOPENtDZCtDZO• EDO Page Mode Read CycletRASPtCPRHt RCStCAStRSH tRCDt OEAtCSHRASCAStASRtRAHtCAHADDRESStCASWEtCRPt CPOEDQ1~DQ4OPENtOEPD OUT 1t PCt CPtCAStCPNtCRPtRADtCAHtASCt ASCtCAHt ASCt RAL Row Column 1t OEAt OEHCtRRH tRCHt RACt AAt AAt AA t CPA t CPA t OEZt OFFt OFFt CACt OEZt CAC t CACt COHD OUT NWE OE Column 2Column N Rowt RPD OUT 2• EDO Page Mode Early Write CycletRASPtRPt WCSt CAStRSH tRCDRASCAStASRtRAHtCAHADDRESStCASWEt CPDQ1~DQ4t PCt CPt CAStCPNtCRP tCAH tASCtASC tCAH tASC Row Column 1t DS WE Column 2Column Nt WCH t WCS t WCH t WCS t WCHt DH t DS t DH t DS t DHD IN 1D IN 2D IN Nt TtCSH• EDO Page Mode Read-Early-Write Cyclet RASPtCPRHt RCStCAStRSH tRCDt OEAtCSHRASCAStASRtRAHtCAHADDRESStCASWEtCRPt CPOEDQ1~DQ4OPENtWEDt PCt CPtCAStCPNtCRPtRADtRAHtASCt ASCtCAHt ASCt RAL Row Column 1tWCStRCHt RACt AAt AAt CPA t DHt WHZt CACt CACt COHWE OE Column 2Column N Rowt RPt CAL tWCHDataDoutput 2Data Input NDataDoutput 1t DStCSH• EDO Page Mode Read-Modify-Write Cyclet RASPt CPRHt RCStCASt WP RASCASt ASRtRAHtCAHADDRESSt CASWEtRCDCPDQ1~DQ4tPRWCt CPtCAStCRPtRADtCAHtASCt ASCtCAH tASC Row Column 1tRWLtRCSt OEDt DZOt CAC WE OEt RPt RAL D OUT 2D OUT ND OUT 1tTt Column NColumn 2Column 1tRWD tAWD tCWDtCWLtRCStCWDtAWD tCPW tCWL tCPW tAWD tCWDtCWL t OEDt OEDt OEHt OEHt OEHt CAC t CAC t OEA t AAt RACt OEZt OEAt AA t CPAt OEZt OEAt AA t CPAt OEZ t DSt DHt WP t DSt DHt WP t DSt DHOPENOPENOPEN D IN 1D IN ND IN 2DQ1~DQ4t DZCt DZOt DZCt DZCt DZO• Read Cycle with WE Controlled Disablet WPZt RCStCAStRCDt TtCSHRASCASt ASRtRAHtCAHADDRESSColumnRow tASCD DQ1~DQ4WEt OEZt DSt WHZOEt RCH t OEA t CACt AAt RACt CLZOUTtRADRASADDRESSt RC t CRPt ASRt RAHt Tt RPCROWt OFFCAS t RASt RPOPENt CRPDQ1~DQ4RASt CSRt WSRt RPt T t RPCt OFFCAS t RASt RPOPENt CRPDQ1~DQ4t RPCt CHRt RASt RPt RCt RCt CHRt CSRt WHRt WSRt WHRWECAS-Before-RAS Refresh CycleRASWEt RPCt OFFt CSRt CHSt WSRCASt RASS t RPSOPENDQ1~DQ4t WHRHigh lmpedance• Hidden Refresh Cyclet RPt RASRASt RCDt CRPADDRESSWEt CHRt CASt RSHt RAHt ASRt ASCt CAHt RAL ROW t RCHt OEZCASDQ1~DQ4t Tt RCSD t RASt RASt RPt RPt RC t RCt RCt RADt RRHt OFF t OFFt OEA t CACt AAt RACCOlumnOUTOE(READ)(REFRESH)(REFRESH)Ordering informationAD404M42VSA-5• AD• Ascend Memory Product • 40 • Device Type• 4M4 • Density and Organization • 2• Refresh Rate, 2: 2K Refresh • V• T: 5V, V: 3.3V• S • Package Type (S : SOJ, T : TSOP II)• A• Version• 5• Speed (5: 50 ns, 6: 60 ns)Part Number Access time PackageAD404M42VSA-5AD404M42VSA-6AD404M42VTA-5AD404M42VTA-650 ns 60 ns 50 ns 60 ns300mil 26/24-Pin Plastic SOJTSOP IIPackaging information • 300 mil, 26/24-Pin Plastic SOJ• 300 mil, 26/24-Pin TSOP II。