RXV中文资料

CODEV中文使用手册1

CODEV 使用手册1CODEV是进行光学系统设计和分析的工具。

这一章向您介绍CODEV,帮助您学习和使用它,并且简单介绍用户使用界面和结构。

目录CODEV功能...简单介绍.......关于命令和宏............ CODEV的结构...............开始,退出,技术支持.............. CODEV功能光学系统设计和分析工具CODEV是为解决光学问题的一件有力和灵活的工具软件。

他的发展已经经历了30年,CODEV是不断随着光学和计算机技术的提高而改进。

他基于与一个可定制Windows用户界面,有广泛的帮助,和优秀的技术支持,便于通过手册CODEV学习和使用。

CODEV的典型应用CODEV有许多方面的应用。

下面一些典型的应用。

为了个新的光学设计而利用一个现有的设计进行评估和改善,可以减少制作花费。

塑料的,非球面,衍射光栅面,或现有的部件都可以如此进行设计。

基于一个新的产品要求要求而创造一个新设计。

对光学设计进行生产公差分析,产生制图甚至输出IGES (CAD)文件应用是什么主要有三个方面:成象系统,光电子或光通信信系统,照明和其他的系统过去,主要应用在图象系统中。

比如包括数码相机,变焦系统和增透镜,光盘系统,医学系统,望远镜,分光镜,复印机,投影机,扫描仪,缩微镜头系统,还包括许多太空应用,军用或者民间等。

尽管这些应用已经存在许多年,但是随着技术的进展,使一些新的工作产生如———照相机到数码相机,CD 到DVD,等等。

近年光电子的应用一直在成长,在照明和其他系统的应用显示了CODEV灵活适应性。

不需要从草稿开始现在说最后一项,CODEV已广泛使用多年。

它的一个优点是不必需从草稿开始进行光学设计。

从一个现有设计做修改是是它典型的应用,并且下面我们将教你怎么做,使用CODEV的New Lens Wizard。

利用专利首先,New Lens Wizard.允许你从CODEV 的一个透镜设计样品开始,从2,400个专利的数据库,或者从你的自己的收集的“favorites”或从一个空白的透镜开始。

VirtualBox中文技术手册

VirtualBox中文技术手册VirtualBox中文技术手册由于在2010年收购了Sun公司,甲骨文获得了VirtualBox平台。

虽然Oracle VirtualBox常用于桌面虚拟化部署,但也适合虚拟服务器环境。

在本期TT虚拟化技术手册中,我们将介绍VirtualBox快照、VirtualBox在虚拟化平台、P2V迁移设备方面提供的信息,还会介绍设置USB设备的过程。

快速认识VirtualBox当谈到基于主机的虚拟化,IT人士通常转向两个平台:VMware Workstation 7和Sun xVM VirtualBox。

关于VirtualBox vs. VMware Workstation的比较信息,请看我们TechTarget虚拟化专家的面对面讨论。

专家面对面:Sun xVM VirtualBox vs. VMware WorkstationVirtualBox功能集合VirtualBox有哪些主要的功能?比如Guest Additions有何作用?共享文件夹如何使用?VirtualBox快照又该如何使用?本部分将详细介绍这些功能。

Sun xVM VirtualBox Guest Additions功能解析Sun xVM VirtualBox之共享文件夹功能VirtualBox功能之VRDP部署Sun xVM VirtualBox快照功能简介VirtualBox网络桥接功能简介VirtualBox迁移功能这系列两部分文章详细介绍Sun公司VirtualBox hypervisor的P2V转换选项。

第一部分主要介绍如何为VirtualBox转换准备VMware虚拟机。

第二部分将介绍驱动安装、管理和其他的转换问题。

Sun VirtualBox P2V服务器转换过程实战轻松搞定VirtualBox P2V转换遇到的难题VirtualBox实用技巧用于Windows的Sun xVM VirtualBox提供了一种功能:将基于VMware的VMDK文件输入到虚拟机,这使得迁移和跨平台部署更为诱人。

XVR300显卡中文说明文档for solaris

新词术语强调 《书名》

含义

命令、文件和目录的名称;计算 机屏幕输出

用户键入的内容,与计算机屏幕 输出的显示不同

保留未译的新词或术语以及要强 调的词。 要使用实名或值替换的 命令行变量。 新词或术语以及要强调的词。 书名

示例

编辑 .login 文件。 使用 ls -a 列出所有文件。 % You have mail.

vii

viii Sun XVR-300 x8 图形加速器用户指南 • 2007 年 11 月

前言

本指南介绍如何在 Sun 系统中安装 Sun™ XVR-300 x8 图形加速器硬件及软件。

本书的结构

第 1 章概述了 Sun XVR-300 x8 图形加速器。 第 2 章介绍了硬件和软件的安装信息。 第 3 章描述了配置多个帧缓冲器的过程。 第 4 章介绍了相关功能信息,包括几种视频输出方法。 附录 A 描述了 DVI 和 HD15 (VGA) 型显示器视频端口的电缆连接。 附录 B 介度选项信息。

DMS-59 视频端口 图 1-1 全高型 Sun XVR-300 x8 图形加速器

2 Sun XVR-300 x8 图形加速器用户指南 • 2007 年 11 月

图 1-2 所示为窄板型 Sun XVR-300 x8 图形加速器。 Sun XVR-300 x8 图形加速器 : 窄板型

DMS-59 视频端口 图 1-2 窄板型 Sun XVR-300 x8 图形加速器 图 1-3 所示为全高型 I/O 支架上的 DMS-59 视频端口。

xii Sun XVR-300 x8 图形加速器用户指南 • 2007 年 11 月

第1章

Sun XVR-300 x8 图形加速器概述

雅马哈 RX-V385 HTR-3072收音扩音机 快速启动指南

T 收音扩音机RX-V385/HTR-3072快速启动指南注意事项 (2)准备工作 (8)播放 (16)RX-V385HTR-3072注意事项请在使用前,仔细阅读下述内容。

请务必按照这些指示操作。

下列注意事项能够防止给用户和其他事物造成伤害的风险以及防止财产损失,并为用户合理、安全地使用本产品提供帮助。

请务必按照这些指示操作。

阅读完本手册后,请将本手册放置在安全的位置以便您日后参考。

警告本内容表示“有重伤或死亡的风险”。

电源/电源线•请勿进行任何会伤害电源线的操作。

-请勿将电源线放置在取暖器附近。

-请勿将电源线过度弯曲或改变形状。

-请勿刮擦电源线。

-请勿将电源线放置在重物之下。

将电源线/适配器的芯线暴露在外使用,可能造成触电或火灾。

•当可能发生闪电时,请勿触摸电源插头或电线。

否则可能造成触电。

•使用电源电压印制其上的产品。

未连接适当AC插座可能造成火灾、触电或故障。

•定期检查电插头,擦除插头上积起来的脏物或灰尘。

否则可能造成火灾或触电。

•设置本产品时,请确认要使用的AC插座伸手可及。

如果发生问题或者故障,请立即断开电源开关并从AC插座中拔下插头。

即使电源已经关闭,只要电源线未从AC插座上拔除,本产品就不会从电源上真正断开。

•如果听到雷声或怀疑闪电接近,请快速关闭电源开关并将插头从AC插座上拔下。

否则可能造成火灾或故障。

•如果长时间不使用本产品,请务必将插头从AC插座上拔下。

否则可能造成火灾或故障。

请勿拆卸•请勿拆卸或改装本产品。

否则可能造成火灾、触电、受伤或故障。

如果您发现任何不恰当的操作,请务必向您购买本产品的经销商或具有资质的Yamaha 服务人员要求检测或维修。

防水警告•请勿让本产品淋雨或在水附近及潮湿环境中使用,或将盛有液体的容器(如花瓶、水瓶或玻璃杯)放在其上,否则可能会导致液体溅入任何开口或可能掉落水的位置。

液体,如水等进入本产品,可能造成火灾、触电或故障。

如果任何液体如水渗入本设备,请立即切断电源并从AC电源插座拔下电源线。

Gowin DVI TX RX IP 用户指南

Gowin DVI TX RX IP 用户指南IPUG938-2.2,2021-09-18版权所有© 2021广东高云半导体科技股份有限公司、、Gowin、GowinSynthesis以及高云均为广东高云半导体科技股份有限公司注册商标, 本手册中提到的其他任何商标,其所有权利属其拥有者所有。

未经本公司书面许可,任何单位和个人都不得擅自摘抄、复制、翻译本文档内容的部分或全部,并不得以任何形式传播。

免责声明本文档并未授予任何知识产权的许可,并未以明示或暗示,或以禁止发言或其它方式授予任何知识产权许可。

除高云半导体在其产品的销售条款和条件中声明的责任之外,高云半导体概不承担任何法律或非法律责任。

高云半导体对高云半导体产品的销售和/或使用不作任何明示或暗示的担保,包括对产品的特定用途适用性、适销性或对任何专利权、版权或其它知识产权的侵权责任等,均不作担保。

高云半导体对文档中包含的文字、图片及其它内容的准确性和完整性不承担任何法律或非法律责任,高云半导体保留修改文档中任何内容的权利,恕不另行通知。

高云半导体不承诺对这些文档进行适时的更新。

目录目录 (i)图目录 (iii)表目录 (iv)1关于本手册 (1)1.1 手册内容 (1)1.2 相关文档 (1)1.3 术语、缩略语 (2)1.4 技术支持与反馈 (2)2概述 (3)2.1 概述 (3)2.2 主要特征 (3)2.3 资源利用 (3)3功能描述 (5)3.1 系统框图 (5)3.2 实现框图 (5)3.2.1 DVI TX (6)3.2.2 DVI RX (7)3.3 端口列表 (8)3.3.1 DVI TX端口 (8)3.3.2 DVI RX端口 (9)3.4 参数配置 (10)3.4.1 DVI TX参数 (10)3.4.2 DVI RX参数 (11)3.5 时序说明 (12)4界面配置 (13)4.1 DVI TX IP配置 (13)4.2 DVI RX IP配置 (15)5参考设计 (19)5.1 设计实例一 (19)5.2 设计实例二 (20)6文件交付 (21)6.1 文档 (21)6.2 设计源代码(加密) (21)6.3 参考设计 (21)7附录 (23)7.1 DVI和HDMI兼容性 (23)7.2 DVI针脚分配 (23)7.3 HDMI针脚分配 (24)图目录图3-1系统框图 (5)图3-2实现框图 (5)图3-3 TMDS编码算法流程图 (6)图3-4 TMDS解码算法流程图 (7)图3-5 DVI TX IO端口示意图 (8)图3-6 DVI RX IO端口示意图 (9)图3-7 DVI视频接口时序示意图 (12)图3-8 TMDS接口时序图 (12)图4-1打开IP Core Generator (13)图4-2打开DVI TX IP核 (14)图4-3 DVI TX IP核接口示意图 (14)图4-94基本信息配置界面 (17)图4-50 Options选项卡 (18)图5-1参考设计实例一基本结构框图 (19)图5-2参考设计实例二基本结构框图 (20)图7-1 DVI-D连接器示意图 (23)图7-2 A类HDMI连接器示意图 (24)表目录表目录表1-1术语、缩略语 (2)表2-1 Gowin DVI TX RX IP (3)表2-2 DVI TX占用资源 (4)表2-3 DVI RX占用资源 (4)表3-1编码算法定义 (7)表3-2 Gowin DVI TX IP的端口列表 (8)表3-3 Gowin DVI RX IP的端口列表 (9)表3-4 DVI TX参数 (10)表3-5 DVI RX参数 (11)表6-1文档列表 (21)表6-2 DVI TX设计源代码列表 (21)表6-3 DVI RX设计源代码列表 (21)表6-4 Gowin DVI RX RefDesign文件夹内容列表 (21)表6-5 Gowin DVI TX RefDesign文件夹内容列表 (22)表7-1 DVI-D连接器针脚分配 (23)表7-2 A类HDMI连接器针脚分配 (24)1关于本手册 1.1手册内容1关于本手册1.1手册内容Gowin DVI TX RX IP用户指南主要内容包括产品概述、功能描述、配置调用、参考设计等,旨在帮助用户快速了解Gowin DVI TX RX IP的特性及使用方法。

雅马哈功放-使用说明书RX-V575_setup

2Zh参考下图在房间内设置音箱。

有关其他音箱系统的信息,请参见《使用说明书》。

1前置音箱(左)2前置音箱(右)3中置音箱4环绕声音箱(左)5环绕声音箱(右)6后置环绕声音箱(左)7后置环绕声音箱(右)9低音炮2放置音箱5.1 声道系统7.1 声道系统(仅限于 RX-V575)3连接音箱/低音炮Zh33将环绕声音箱 (4/5) 连接至4将低音炮 (9) 连接至 SUBWOOFER PRE 对于 7.1 声道系统(仅限于 RX-V575)4ZhZh54连接外部装置AV 1将外部装置连接至本机。

a 使用 HDMI 缆线将 BD/DVD 播放机连接至本机。

如果 BD/DVD 播放机当前通过 HDMI 缆线直接连接到电视,则应将此缆线从电视断开,然后将其连接到本机。

b 使用其他 HDMI 缆线将电视连接至本机。

c 使用数字光纤缆线将电视连接至本机。

在本机上播放电视视频时需要此连接。

如果电视支持 ARC (Audio Return Channel),则不需要此连接。

d 将电源线连接至交流墙壁电源插座。

•有关如何连接收音机天线或其他外部装置的信息,请参见《使用说明书》中的“准备工作”。

2打开本机、电视和 BD/DVD 播放机。

3使用电视遥控器将电视输入更改为来自本机的视频。

现在已经完成了连接。

请转到下一页,优化音箱设置。

•通过使用 HDMI 缆线将电视连接至本机,可使用电视上显示的菜单来配置本机的设置。

连接电源线之前(仅限通用型号)确保根据当地电压设置了 VOLTAGE SELECTOR 的开关位置。

电压为 AC 110-120/220-240 V ,50/60 Hz 。

6ZhYamaha Parametric room Acoustic Optimizer (YPAO) 功能将检测音箱连接,测量音箱与收听位置之间的距离,然后自动优化音箱设置(如音量平衡和音响参数)以适应您的房间。

5自动优化音箱设置 (YPAO)•测量过程中,测试音会以高音量输出。

电路图中常用的英文缩写的中文解释

AA 模拟A/DC模拟信号到数字信号的转换A/L音频/逻辑板AAFPCB音频电路板AB 地址总线ab 地址总线accessorier 配件ACCESSORRIER 配件ADC(A/O)模拟到数字的转换adc 模拟到数字的转换ADDRESS BUS地址总线AFC 自动频率控制afc 自动频率控制AFC自动频率控制AFMS 来音频信号afms 来自音频信号AFMS来音频信号AFPCB 音频电路板AF音频信号AGC 自动增益控制agc 自动增益控制AGC自动增益控制aged 模拟地AGND 模拟地AGND模拟地ALARM 告警alarm 告警ALC 自动电平控制ALEV 自动电平AM 调幅AMP 放大器AMP放大器AM调幅ANT 天线ANT/SW 天线开关ant 天线Anternna天线antsw 天线开关ANTSW天线切换开关ANT天线APC 自动功率控制APC/AOC自动功率控制ARFCH 绝对信道号ASIC 专用接口集成电路AST-DET 饱和度检测ATMS 到移动台音频信号atms 到移动台音频信号ATMS到移动台音频信号AUC 身份鉴定中心AUDIO 音频AUDIO音频AUTO自动AUX辅助AVCC音频处理芯片A模拟信号b+ 内电路工作电压BALUN平衡于一不平衡转换BAND-SEL频段选择/切换BAND频段Base band基带(信号)base 三极管基极batt+ 电池电压BDR接收数据信号Blick Diagram方框图BPF带通滤波器BUFFER缓冲放大器BUS通信总线buzz 蜂鸣器CCALL 呼叫CARD 卡Carrier载波调制CCONTCSX开机维持(NOKIA) CCONTINT关机请求信号CDMA 码分多址cdma 码分多址CEPT 欧洲邮电管理委员会CH 信道CHAGCER 充电器CHECK 检查CIRCCITY 整机Circuit Diagram电路原理图CLK 时钟CLK-OUT逻辑时钟输出CLK-SELECT时钟选择信号(Motorola 手机)COBBA音频IC(诺基亚系列常用)COL 列COLLECTOR 集电极CONTROL 控制control 控制CP 脉冲、泵CP-TX RXVCO控制输出接收锁相电平CP-TX TXVCO控制输出发射锁相电平CPU 中央处理器cpu 中央处理器CS 片选CTL-GSM频段控制信号d b 数据总线D/AC数字信号到模拟信号的转换d 数字dac 数字到模拟的转换dcin 外接直流电愿输入DCS-CS发射机控制信号:控制TXVCO 与I/Q调制器DDI数据接口电路DECIPHRIG解秘DEINTERLEARING去交织DET检测dfms 来数据信号dgnd 数字地Diplex双工滤波器Direct Coner Siorl Lionear Receicer直接变换的线性接收机dsp 数字信号处理器DSP数字信号处理器dtms 到数据信号DUPLEX / DIPLEX双工器Duplex Sapatation双工间隔EEarph 耳机EEPROM 电擦除可编程只读存储器EIR 设备号寄存器EL 发光EMITTER 发射极emitter 三极管发射极EMOD Demodu Laticon解调EN 使能EN 使能、允许、启动en 使能ENAB 使能EPROM 电编程只读存贮器ERASABLE 可擦的ETACS 增强的全接入通信系统etacs 增强的全接入通信系统EXT 外部EXT 外部ext 外部的FBUS处接通信接口信号线fdma 频分多址feed back 反馈fh 跳频FILFTER滤波器fl 滤波器fm 调频from 来自于gain 增益GAIN增益Gen Out信号发生器gnd 地GSM-PINDIODE功率放大器输出匹配电路切换控制信号GSM-SEL频段切换控制信号之一G-TX-VCO900MHZ发射VCO切换控制hook 外接免提状态II 同相支路I/O 输入/输出I/O输入/输出i/o输入输出i 同相支路IC 集成电路ICTRL 供电电流大小控制端ictrl 供电电流大小控制端IF 中频if 中频IFLO中频本振IF中频IMEI 国际移动设备识别码IN 输入INSERT CARD 插卡INT 中断int 中断Interface界面,电子电路基础知识2,接口ISDN 综合业务数字网I同相支路LayoutPCB元件分布图LCDCLK显示器时钟led 发光二极管LOCK锁定loop fliter 环路滤波器LO本振LPF低通滤波器lspctrl 扬声器控制MMAINVCO主振荡器(Motorola) MCC 移动国家码MCLK 主时钟mclk 主时钟MCLK主时钟MCLK主时钟MDM 调制解调MDM调制解调器(Motorola手机) MENU 菜单MF 陶瓷滤波器MIC 话筒mic 送话器MISO主机输入从机输出(Motorola) MIX 混合Mixed Second第二混频信号MIXER SECOND 第二混频信号MIX混频器MOD 调制信号mod 调制信号MODEM调制解调器MODFreq调制频率MODIN 调制I信号负modin 调制i信号负MODIN调制I信号负MODIP 调制I信号正MODIP调制I信号正MODQN 调制Q信号负MODQN调制Q信号负MODQP 调制Q信号正MODQP调制Q信号正MOD调制MOD调制信号MOEM调制解调器DMmopip 调制i信号正MOSI主机输出从机输入(Motorola) MS 移动台MSC 移动交换中心MSIN 移动台识别码MSK 最小移频键控MSRN 漫游MUTE 静音mute 静音NNAM 号码分配模块NC 空、不接NO NETWORK 无网络ofst 偏置on 开onsrq 免提开关控制PA 功率放大器PADRV功率放大器驱动PCB板图PCM脉冲编码调制PD/PH相位比较器pll 锁相环PLL锁相环PLL锁相环路powcontrol 功率控制POWCONTROL功率控制Power Supply电源系统powlev 功率级别POWLEV功放级别PURX复位信号(NOKIA)pwrsrc 供电选择QQ uadrature modulalion正交调制Q 正交支路Q 正交支路q 正交支路RRACH 随机接入信道RADIO射频本振RAM 随机存储器ram 随机储存器(暂存)RD 读Receiver收信机REF 参考、基准ref 参考RESET 复位reset 复位RF PCB 射频板RF 射频rf 射频RFADAT 射频频率合成器数据rfadat 射频频率合成数据RFADAT射频频率合成器数据RFAENB 射频频率合成器启动rfaenb 射频频率合成启动RFAENB射频频率合成器启动RFConnector射频接口RFI 射频接口RFIN/OFF高频输入/输出ROM 只读存储器ROW 行RSSI 场强RSSI 接收信号强度指示rssi 接收强度指示RSSI接收信号强度指示RX 接收rx 接收RX-ACQ接收机数据传输请求信号RXEN接收使能RXIFN 接收中频信号负rxifn 接收中频信号负RXIFN接收中频信号负RXIFP 接收中频信号正rxifp 接收中频信号正RXIFP接收中频信号正RXIN接收I信号负RXIN接收输出RXIP接收I信号正RXI接收基带信号(同相)RXON 接收开rxon 接收开RXON接收机启动/开关控制RXOUT接收输出RXQN接收Q信号负RXQP接收Q信号正RXQ接收基带信号(正交) RXVCO 收信压控振荡器RX接收sat-det 饱和度检测saw 声表面波滤波器SAW声表面波滤波器SF超级滤波器SHFVCO专用射频VCO(NOKIA) SLEEPCLK睡眠时钟SMOC数字信号处理器spi 串行外围接口spk 扬声器SUPLEX双工器作用相当于天线开关sw 开关swdc 末调整电压SW开关synclk 频率合成器时钟SYNCLK频率合成器时钟syndat 频率合成器数据SYNDAT频率合成器数据SYNEN频率合成器启动/使能synstr 频率合成器启动SYNSTR频率合成器启动SYNTCON频率合成器开/关synton 频率合成器开/关TTACS 全接入移动通信系统TCH 话音通道TDMA 时分多址tdma 时分多址TEMP 温度监测temp 温度监测TEST 测试TP 测试点tp 测试点tx 发送Transmitter发信机TRX 收发信机TX EN 发送使能tx en 发送使能TX 发送TX 发信TXC 发信控制TX-DEY-OUT发射时序控制输出TXENT发射供电TXEN发射使能TXEN发送使能TX-IF 发信中频TXIN发送I信号负TXIP发送I信号正TXI发射基带信号TXON 发送开txon 发送开TXON发送开TXOUT发射输出TXPWR发射功率TXQN发送Q信号负TXQP发送Q信号正TXQ发射基带信号TXRF发射射频TXVCO 发信压控振荡器txvco 发送压控振荡器频率控制UHFVCO超高频/射频VCO UHF超高频段UI用户接口BSIC专用集成电路UREGISTERED未注册vbatt 电池电压vcc 电愿VCO 压控振荡器vco 压控振荡VCTCXO温补压控振荡器vcxocont 基准振荡器频率控制VHFVCO甚高频/中频VCO vpp 峰峰值vppflash flash 编程控制vrpad 调整后电压vswitch 开关电压WWATCH DOG 看门狗WATCHDOG看门狗信号WCDMA 宽带码分多址WD-CP 看门狗脉冲WDG看门狗(维持信号电压) WDOG 看门狗WR 写逻辑音频电路射频电路电路图中常用的英文缩写的中文解释电子知识UHF超高频段UREGISTERED未注册SW开关UI用户接口BSIC专用集成电路BAND频段BAND-SEL频段选择/切换BUFFER缓冲放大器BUS通信总线DET检测Circuit Diagram电路原理图Blick Diagram方框图PCB板图LayoutPCB元件分布图Receiver收信机Transmitter发信机Interface界面,电子电路基础知识2,接口Power Supply电源系统射频电路A模拟信号AFC自动频率控制AGC自动增益控制APC/AOC自动功率控制AGND模拟地ANT天线ANTSW天线切换开关AM调幅BPF带通滤波器CP-TX RXVCO控制输出接收锁相电平CP-TX TXVCO控制输出发射锁相电平DUPLEX / DIPLEX双工器Duplex Sapatation双工间隔DCS-CS发射机控制信号:控制TXVCO 与I/Q调制器FILFTER滤波器Gen Out信号发生器GAIN增益GSM-PINDIODE功率放大器输出匹配电路切换控制信号GSM-SEL频段切换控制信号之一G-TX-VCO900MHZ发射VCO切换控制IF中频IFLO中频本振LO本振LOCK锁定MODFreq调制频率Mixed Second第二混频信号PA 功率放大器PLL锁相环路PADRV功率放大器驱动TXRF发射射频TXEN发射使能TXENT发射供电TXIN发送I信号负TXIP发送I信号正TXON发送开TXQN发送Q信号负TXQP发送Q信号正TXI发射基带信号TX-DEY-OUT发射时序控制输出TXQ发射基带信号UHFVCO超高频/射频VCO VHFVCO甚高频/中频VCO SHFVCO专用射频VCO(NOKIA) VCO 压控振荡器VCTCXO温补压控振荡器AMP放大器CTL-GSM频段控制信号Diplex双工滤波器SUPLEX双工器作用相当于天线开关LPF低通滤波器MAINVCO主振荡器(Motorola)MIX混频器Anternna天线RFConnector射频接口BALUN平衡于一不平衡转换Direct Coner Siorl Lionear Receicer直接变换的线性接收机Carrier载波调制POWCONTROL功率控制POWLEV功放级别RFIN/OFF高频输入/输出RADIO射频本振RFADAT射频频率合成器数据RFAENB射频频率合成器启动RSSI接收信号强度指示RX接收RXIN接收输出RXON接收机启动/开关控制RXOUT接收输出RXEN接收使能RXIFN接收中频信号负RXIFP接收中频信号正RXIN接收I信号负RXIP接收I信号正RXQN接收Q信号负RXQP接收Q信号正RX-ACQ接收机数据传输请求信号RXI接收基带信号(同相)RXQ接收基带信号(正交)SAW声表面波滤波器SF超级滤波器SYNCLK频率合成器时钟SYNDAT频率合成器数据SYNEN频率合成器启动/使能SYNSTR频率合成器启动SYNTCON频率合成器开/关TX 发送TXEN发送使能TXOUT发射输出TXPWR发射功率逻辑音频电路AFMS来音频信号AAFPCB音频电路板ATMS到移动台音频信号AUDIO音频AUX辅助AVCC音频处理芯片AUTO自动A/L音频/逻辑板COBBA音频IC(诺基亚系列常用) Base band基带(信号)BDR接收数据信号CLK-OUT逻辑时钟输出CLK-SELECT时钟选择信号(Motorola 手机)DEINTERLEARING去交织DECIPHRIG解秘I同相支路I/O输入/输出MODEM调制解调器MCLK主时钟MDM调制解调器(Motorola手机) MISO主机输入从机输出(Motorola) MOD调制信号MODIN调制I信号负MODIP调制I信号正MODQN调制Q信号负MODQP调制Q信号正MOSI主机输出从机输入(Motorola) PCM脉冲编码调制Q uadrature modulalion正交调制Q 正交支路SMOC数字信号处理器WATCHDOG看门狗信号WDG看门狗(维持信号电压)A/DC模拟信号到数字信号的转换AF音频信号CCONTCSX开机维持(NOKIA) CCONTINT关机请求信号D/AC数字信号到模拟信号的转换DDI数据接口电路EMOD Demodu Laticon解调DSP数字信号处理器FBUS处接通信接口信号线MCLK主时钟MOD调制MOEM调制解调器DMPD/PH相位比较器PLL锁相环PURX复位信号(NOKIA) SLEEPCLK睡眠时钟LCDCLK显示器时钟ab》地址总线accessorier》配件adc》模拟到数字的转换afc》自动频率控制agc》自动增益控制aged》模拟地afms》来自音频信号alarm》告警ant》天线antsw》天线开关atms》到移动台音频信号base》三极管基极batt+》电池电压b+》内电路工作电压buzz》蜂鸣器cdma》码分多址control》控制cpu》中央处理器d》数字dac》数字到模拟的转换d b》数据总线dcin》外接直流电愿输入dgnd》数字地dtms》到数据信号dfms》来数据信号dsp》数字信号处理器emitter》三极管发射极en》使能etacs》增强的全接入通信系统ext》外部的feed back》反馈fdma》频分多址fh》跳频fl》滤波器fm》调频from》来自于gain》增益gnd》地hook》外接免提状态i》同相支路if》中频int》中断i/o输入输出ictrl》供电电流大小控制端led》发光二极管loop fliter》环路滤波器lspctrl》扬声器控制mclk》主时钟mic》送话器mod》调制信号mopip》调制i信号正modin》调制i信号负mute》静音ofst》偏置on》开onsrq》免提开关控制powcontrol》功率控制powlev》功率级别pwrsrc》供电选择pll》锁相环q》正交支路ram》随机储存器(暂存)ref》参考reset》复位rf》射频rfadat》射频频率合成数据rfaenb》射频频率合成启动rssi》接收强度指示rx》接收rxon》接收开rxifp》接收中频信号正rxifn》接收中频信号负sat-det》饱和度检测saw》声表面波滤波器spk》扬声器spi》串行外围接口swdc》末调整电压synstr》频率合成器启动synclk》频率合成器时钟syndat》频率合成器数据synton》频率合成器开/关sw》开关tdma》时分多址temp》温度监测txvco》发送压控振荡器频率控制tp》测试点tx》发送tx en》发送使能txon》发送开vbatt》电池电压vrpad》调整后电压vpp》峰峰值vppflash flash》编程控制vcxocont》基准振荡器频率控制vswitch》开关电压vcc》电愿vco》压控振荡AA 模拟AB 地址总线ACCESSORRIER 配件ADC(A/O)模拟到数字的转换ADDRESS BUS地址总线AFC 自动频率控制AGC 自动增益控制AGND 模拟地AFMS 来音频信号ALARM 告警ALEV 自动电平ALC 自动电平控制AM 调幅AMP 放大器ANT 天线ANT/SW 天线开关APC 自动功率控制ARFCH 绝对信道号AFPCB 音频电路板ATMS 到移动台音频信号ASIC 专用接口集成电路AST-DET 饱和度检测AUC 身份鉴定中心AUDIO 音频CCDMA 码分多址CONTROL 控制CPU 中央处理器CIRCCITY 整机COLLECTOR 集电极CALL 呼叫CARD 卡CEPT 欧洲邮电管理委员会CH 信道CHAGCER 充电器CHECK 检查CLK 时钟COL 列CP 脉冲、泵CS 片选EEMITTER 发射极EN 使能ENAB 使能ETACS 增强的全接入通信系统EXT 外部EL 发光ERASABLE 可擦的Earph 耳机EEPROM 电擦除可编程只读存储器EPROM 电编程只读存贮器EIR 设备号寄存器EN 使能、允许、启动EXT 外部II 同相支路IF 中频INT 中断I/O 输入/输出ICTRL 供电电流大小控制端IC 集成电路IMEI 国际移动设备识别码IN 输入INSERT CARD 插卡ISDN 综合业务数字网MMCLK 主时钟MIC 话筒MOD 调制信号MODIP 调制I信号正MODIN 调制I信号负MODQP 调制Q信号正MODQN 调制Q信号负MUTE 静音MIXER SECOND 第二混频信号MF 陶瓷滤波器MCC 移动国家码MENU 菜单MDM 调制解调MIX 混合MS 移动台MSC 移动交换中心MSK 最小移频键控MSIN 移动台识别码MSRN 漫游NNAM 号码分配模块NC 空、不接NO NETWORK 无网络QQ 正交支路RRAM 随机存储器REF 参考、基准RESET 复位RF 射频RFADAT 射频频率合成器数据RFAENB 射频频率合成器启动RSSI 接收信号强度指示RX 接收RXON 接收开RXIFP 接收中频信号正RXIFN 接收中频信号负RF PCB 射频板RACH 随机接入信道RD 读RFI 射频接口ROM 只读存储器ROW 行RSSI 场强RXVCO 收信压控振荡器TTDMA 时分多址TEMP 温度监测TXVCO 发信压控振荡器TP 测试点TX 发信TX EN 发送使能TXON 发送开TACS 全接入移动通信系统TCH 话音通道TEST 测试TRX 收发信机TXC 发信控制TX-IF 发信中频WWATCH DOG 看门狗WCDMA 宽带码分多址WD-CP 看门狗脉冲WDOG 看门狗WR 写。

Voxler4.0中文教程北冥出品

北冥有鱼,其名为鲲。

鲲之大,不知其几千里也;化而为鸟,其名为鹏。

--庄子《逍遥游》 Voxler®4.0中文教程本译文为使用Voxler4.0过程中的的一个中间产物,主要是对Voxler4.0的英文帮助文档进行了一个粗糙的翻译,同时在翻译过程中对有些概念和功能进行了比较系统的梳理和理解。

现分享给大家,希望对大家有用。

Voxler4.0是Golden Software有限责任公司出品的一款卓越的商业三维可视化软件,希望大家在法律法规的框架内使用该软件,尊重软件著作权。

您可以自由传播此文档,可以进行修改、勘误,但建议仅限于学习与研究之用而勿利用此文档进行盈利性的活动,本文档用于纯粹的商业用户是禁止的。

受译者水平和时间限制,译文肯定存在很多很多很多问题,请大家在使用此文档时,自行进行甄别,给予勘误,万分感谢。

译者:目录VOXLER用户界面概览 (4)VOXLER用户界面 (5)改变视窗布局 (6)工作表文档 (6)工作表命令 (7)标签视图 (7)工作表文档 (7)工作表窗口 (8)教程介绍 (10)高级教程 (11)关于文档的一个备注 (11)使用演示版本的教程 (11)开始VOXLER–教程 (11)课程1-装载数据-教程 (12)课程2–创建图形输出模块-教程 (14)2.1-创建一个散射图-教程 (14)2.2–添加一个边界框-教程 (15)课程 3–更改属性-教程 (17)3.1–改变符号颜色-教程 (17)3.2–显示标签–教程 (19)3.3–改变边框盒属性-教程 (19)3.4–旋转图形-教程 (20)课程 4–编辑工作表中的连接数据 (22)课程 5–使用计算模块–教程 (24)5.1–网格化数据-教程 (24)5.2–创建一个等值面-教程 (25)5.3–更改等值面属性-教程 (26)5.4–关于透明度的一个标注-教程 (28)5.5–过滤数据–教程 (28)课程 6–连接多个模块-教程 (32)6.1–添加等值线-教程 (32)6.2–改变透明度-教程 (34)课程 7-保存信息-教程 (35)7.1–保存一个项目-教程 (35)7.2–保存数据–教程 (36)7.3–保存图形–教程 (36)7.4–拷贝一个快照-教程 (36)7.5–捕获视频-教程 (37)课程 8–导入井体数据 (38)8.1–导入井口位置数据 (38)8.2–导入轨迹数据 (39)8.3–井的显示 (40)8.4–导入测井L OG数据 (40)8.5–在井体上面显示测井数据 (41)高级教程导引 (42)高程场-高级建议 (42)方法1 (42)方法2 (43)数学模块–高级建议 (45)Voxler 用户界面概览Voxler 使用多线程来保持用户界面反应灵敏,甚至对计算量较大的后台任务也反应灵敏。

EXBVxxxx中文资料

5.08+0.20 –0.10

2.20 +0.20 –0.10

0.70 ±0.20

0.80 ±0.15

0.80 ±0.15

0.50 ±0.15

0.55 ±0.15

(3) Flat Terminal type

A1 A2 EXB18V G T G W P L B B

Type (inches) EXB18V (0201 4)

±0.10

B

W 0.60 ±0.10 1.00 ±0.10 1.00

±0.10

T 0.35 ±0.10 0.35 ±0.10 0.35

±0.10

A1 0.35 ±0.10 0.40 ±0.10 0.45

±0.10

A2 — — 0.35

±0.10

B 0.15 ±0.10 0.18 ±0.10 0.20

May. 2005

元器件交易网

Chip Resistor Array

■

Item Resistance Range Resistance Tolerance 14V,24V,V4V,34V Specifications 10 to 1 M :E24 series J: ±5 % 4 terminal Item 14V,18V (1) Limiting Element Voltage 2HV Max. Rated Continuous 24V,28V,N8V,38V,34V,V4V,V8V Working Voltage S8V Specifications 12.5 V 25 V 50 V 100 V 25 V 50 V 200 V ±200 10 -6/°C(ppm/°C)

Dimensions (mm) L 1.40 ±0.10 W 0.60 ±0.10 T 0.35 ±0.10 A1 0.20 ±0.10 A2 0.20 ±0.10 B 0.10 ±0.10 P (0.40) G 0.20 ±0.10

永不止步—— 东风本田全新XR-V

4 328、1 772、1 605 2 610

1 535/1 540 130

1 398

动力系统及车辆性能 发动机型式 发动机排量 L 最大功率 kW(r/min) 最大扭矩 N·m(r/min) 变速器型式 燃油标号 环保标准

L4,涡轮增压,直喷 1.498

130(6 000) 220(1 700~5 500)

我印象里,上一次开这辆车,还是 2017 年执行 一个女神节的选题,我们选了 5 辆不同价位,不同风 格,但是都很适合推荐给女性的车,XR-V 是其中一 辆。当时选择这辆车的理由很简单,就是因为它尺寸

49

50

TEST REPORT 试车报告

12

1. 内饰没有变化,配置有所提升

2. CVT 变速器一贯地省油

48

TEST REPORT 试车报告

永不止步

东风本田全新 XR-V

五年,对于一辆车来说,意味 着什么呢?自 2014 年 12 月份上市以来, XR-V 用五年的时间,从一张白纸成长为了合资品牌小型 SUV 的卖座王, 累计销量 65 万辆,三年保值率 67.55%,凭借出众的实力留下了一连串 美丽的数字。而现在,它又迎来了大改款,换装了1.5T 的涡轮增压发动机, 准备用一颗更强劲的心脏去面对纷繁复杂的小型 SUV 市场。

撰文 / 王现 摄影 / 吴启舟

东风本田全新 XR-V

上市时间 2019 年 7 月 价格 12.79 万 ~17.59 万元 强项 车身颜色亮眼、车内布局灵活 度高、动力充沛、燃油经济性佳。 弱项 静谧性有待提升。

假 如你问,1.5T 的发动机够快吗?答案当然是 肯定的,最大功率 130 kW,最大扭矩 220 N·m,参考 试驾全新缤智时,我们实测出的 9.1 s 的 0~100 km/h 加速时间,我觉得如果气候更凉爽一些,跑进 9 s 也 是有可能的。但是对于这辆家用的小型 SUV 来说, 我 更 把 动力看 做 是 银行里的存 款,它是 来自内心的 一种满足感,可能平时用不着,但是关键时刻绝对不 能没有。

电路中rx-概述说明以及解释

电路中rx-概述说明以及解释1.引言1.1 概述概述部分内容的编写:电路中的RX是指接收端,即接收信号的电路部分。

在现代电子通信中,许多设备和系统都需要进行信号的接收和解码,而接收端就扮演着重要的角色。

接收端主要用于接收来自发送端发送的信号,并进行解调、解码和恢复信号的过程。

无论是无线通信还是有线通信,接收端都是关键的组成部分。

在无线通信中,接收端的主要功能是接收无线信号,进行信号的放大、滤波和频率转换等操作。

通过这些处理,可以将原始信号转化为可被接收设备处理的信号。

接收端还可能涉及到解调和解码,以获取传输的信息内容。

在有线通信中,接收端的任务是接收传输线上的信号,并进行放大和恢复。

对于数字信号而言,接收端还可能需要进行解码和复原,以还原传输的数据。

尽管不同的通信系统和设备的接收端有所差异,但其基本原理和功能都是类似的。

通过接收端,我们可以从传输媒介中接收到信息并进行相应的处理,使得通信能够顺利进行。

因此,了解接收端的原理和功能对于理解电路设计和通信系统的工作原理都是非常重要的。

本文将主要介绍接收端的相关原理和基本功能,并对其在不同通信系统中的应用进行探讨。

1.2 文章结构文章结构部分是为了给读者展示文章的整体结构,并提供一个大纲,使读者能够更好地理解和组织文章内容。

在本文中,文章结构部分主要包括三个方面:引言、正文和结论。

引言部分将提供一个对整个文章的概述,说明文章的目的和主题,并介绍一些背景信息。

这将帮助读者了解为何编写这篇文章以及可以期待在接下来的内容中学到什么。

正文部分是文章的核心内容,包括主要的要点和论述。

这部分将进一步展开文章的主题,提供更多细节、证据和解释,以支持作者的观点。

在本文中,正文部分包括要点1和要点2,将进一步讨论关于电路中Rx的相关信息。

结论部分是对整篇文章的总结和回顾。

在这一部分中,作者将对前面的论述进行汇总,重申文章的核心内容和观点,并提供一些展望,指出可能的未来发展方向或进一步的研究方向。

VR虚拟现实-HDDMDVR说明书V30中文版 精品

车载HDD-MDVR使用说明书(电子版)文档起草JHIC/家槐目录1 注意事项 (4)2 产品规格 (4)3 前后板及录像机安装说明 (7)3.1 前面板说明 (7)3.2 后面板接口说明 (8)3.3 接线说明 (9)3.3.1 AV视音频输入线说明 (9)3.3.2 电源线说明 (9)3.3.3 I/O 报警输入输出说明 (10)3.4 录像机检查 (11)3.4.1 开箱及附件检查 (11)3.4.2 SD卡安装说明 (12)4 遥控器使用说明 (13)4.1 遥控器按键说明 (13)4.2 软键盘输入说明 (15)5 录像机使用操作说明 (16)5.1 用户登录 (17)5.2 直通预览界面 (18)5.3 录像检索 (19)5.3.1 详细文件及备份说明 (20)5.3.1 录像回放说明 (21)5.4 录像设置 (21)5.4.1 帧率动态配置等说明 (21)5.4.2 定时录像设置 (23)5.5 功能设置 (25)5.5.1 报警设置 (26)5.5.2 云台设置 (29)5.5.3 时间设置 (30)5.5.4 存储设备管理 (31)5.5.5 设备维护,系统升级说明 (31)5.5.6 网络设置 (33)5.6 系统信息 (36)5.7 车辆信息 (37)5.7.1 基本信息 (38)5.7.2 速度设置 (38)5.7.3 加速度设置 (39)5.7.4 温度设置 (39)5.7.5 开关机设置 (40)5.7.6 无线设置 (41)5.7.7 WIFI设置 (41)5.8 显示设置 (42)5.9 密码管理 (43)6 FAQ (45)1 注意事项安装和使用之前,请一定详细阅读使用说明书,以便您能正确使用和保护您的机器。

本说明书前面部分为注意事项和安装使用介绍,请先行阅读。

➢注意事项●为保障您的权益,在安装使用本产品前,请仔细阅读本手册内容。

●本产品为车内使用设备,为了防止短路或电击危险,请勿将本机放在雨中或潮湿的环境中。

XCS05XL-4VQ240C资料

© 2001 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at /legal.htm .All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.IntroductionThe Spartan ™ and the Spartan-XL families are a high-vol-ume production FPGA solution that delivers all the key requirements for ASIC replacement up to 40,000 gates.These requirements include high performance, on-chip RAM, core solutions and prices that, in high volume,approach and in many cases are equivalent to mask pro-grammed ASIC devices.The Spartan series is the result of more than 14 years of FPGA design experience and feedback from thousands of customers. By streamlining the Spartan series feature set,leveraging advanced process technologies and focusing on total cost management, the Spartan series delivers the key features required by ASIC and other high-volume logic users while avoiding the initial cost, long development cycles and inherent risk of conventional ASICs. The Spar-tan and Spartan-XL families in the Spartan series have ten members, as shown in T able 1.Spartan and Spartan-XL FeaturesNote: The Spartan series devices described in this data sheet include the 5V Spartan family and the 3.3V Spartan-XL family. See the separate data sheet for the 2.5V Spartan-II family.•First ASIC replacement FPGA for high-volume production with on-chip RAM•Density up to 1862 logic cells or 40,000 system gates •Streamlined feature set based on XC4000 architecture •System performance beyond 80MHz•Broad set of AllianceCORE ™ and LogiCORE ™ predefined solutions available •Unlimited reprogrammability •Low cost•System level features-Available in both 5V and 3.3V versions -On-chip SelectRAM ™ memory -Fully PCI compliant-Full readback capability for program verificationand internal node observability -Dedicated high-speed carry logic -Internal 3-state bus capability-Eight global low-skew clock or signal networks -IEEE 1149.1-compatible Boundary Scan logic -Low cost plastic packages available in all densities -Footprint compatibility in common packages•Fully supported by powerful Xilinx development system -Foundation Series: Integrated, shrink-wrapsoftware-Alliance Series: Dozens of PC and workstationthird party development systems supported-Fully automatic mapping, placement and routing Additional Spartan-XL Features• 3.3V supply for low power with 5V tolerant I/Os •Power down input •Higher performance •Faster carry logic•More flexible high-speed clock network•Latch capability in Configurable Logic Blocks •Input fast capture latch•Optional mux or 2-input function generator on outputs •12 mA or 24 mA output drive •5V and 3.3V PCI compliant •Enhanced Boundary Scan •Express Mode configuration •Chip scale packagingSpartan and Spartan-XL Families Field Programmable Gate ArraysDS060 (v1.6) September 19, 2001Product Specification T able 1: Spartan and Spartan-XL Field Programmable Gate Arrays1.Max values of Typical Gate Range include 20-30% of CLBs used as RAM.2DS060 (v1.6) September 19, 2001General OverviewSpartan series FPGAs are implemented with a regular, flex-ible, programmable architecture of Configurable Logic Blocks (CLBs), interconnected by a powerful hierarchy of versatile routing resources (routing channels), and sur-rounded by a perimeter of programmable Input/Output Blocks (IOBs), as seen in Figure 1. They have generous routing resources to accommodate the most complex inter-connect patterns.The devices are customized by loading configuration data into internal static memory cells. Re-programming is possi-ble an unlimited number of times. The values stored in thesememory cells determine the logic functions and intercon-nections implemented in the FPGA. The FPGA can either actively read its configuration data from an external serial PROM (Master Serial mode), or the configuration data can be written into the FPGA from an external device (Slave Serial mode).Spartan series FPGAs can be used where hardware must be adapted to different user applications. FPGAs are ideal for shortening design and development cycles, and also offer a cost-effective solution for production rates well beyond 50,000 systems per month.Figure 1: Basic FPGA Block DiagramSpartan series devices achieve high-performance, low-cost operation through the use of an advanced architecture and semiconductor technology. Spartan and Spartan-XL devices provide system clock rates exceeding 80MHz and internal performance in excess of150MHz. In contrast to other FPGA devices, the Spartan series offers the most cost-effective solution while maintaining leading-edge per-formance. In addition to the conventional benefit of high vol-ume programmable logic solutions, Spartan series FPGAs also offer on-chip edge-triggered single-port and dual-port RAM, clock enables on all flip-flops, fast carry logic, and many other features.The Spartan/XL families leverage the highly successful XC4000 architecture with many of that family’s features and benefits. T echnology advancements have been derived from the XC4000XLA process developments.Logic Functional DescriptionThe Spartan series uses a standard FPGA structure as shown in Figure1, page2. The FPGA consists of an array of configurable logic blocks (CLBs) placed in a matrix of routing channels. The input and output of signals is achieved through a set of input/output blocks (IOBs) forming a ring around the CLBs and routing channels.•CLBs provide the functional elements for implementing the user’s logic.•IOBs provide the interface between the package pins and internal signal lines.•Routing channels provide paths to interconnect the inputs and outputs of the CLBs and IOBs.The functionality of each circuit block is customized during configuration by programming internal static memory cells. The values stored in these memory cells determine the logic functions and interconnections implemented in the FPGA.Configurable Logic Blocks (CLBs)The CLBs are used to implement most of the logic in an FPGA. The principal CLB elements are shown in the simpli-fied block diagram in Figure2. There are three look-up tables (LUT) which are used as logic function generators, two flip-flops and two groups of signal steering multiplexers. There are also some more advanced features provided by the CLB which will be covered in the Advanced Features Description, page13.Function GeneratorsTwo 16x1 memory look-up tables (F-LUT and G-LUT) are used to implement 4-input function generators, each offer-ing unrestricted logic implementation of any Boolean func-tion of up to four independent input signals (F1 to F4 or G1 to G4). Using memory look-up tables the propagation delay is independent of the function implemented.A third 3-input function generator (H-LUT) can implement any Boolean function of its three inputs. Two of these inputs are controlled by programmable multiplexers (see box "A" of Figure2). These inputs can come from the F-LUT or G-LUT outputs or from CLB inputs. The third input always comes from a CLB input. The CLB can, therefore, implement cer-tain functions of up to nine inputs, like parity checking. The three LUTs in the CLB can also be combined to do any arbi-trarily defined Boolean function of five inputs.4DS060 (v1.6) September 19, 2001A CLB can implement any of the following functions:•Any function of up to four variables, plus any second function of up to four unrelated variables, plus any third function of up to three unrelated variablesNote: When three separate functions are generated, one of the function outputs must be captured in a flip-flop internal to the CLB. Only two unregistered function generator outputs are available from the CLB.•Any single function of five variables•Any function of four variables together with some functions of six variables•Some functions of up to nine variables.Implementing wide functions in a single block reduces both the number of blocks required and the delay in the signal path, achieving both increased capacity and speed. The versatility of the CLB function generators significantly improves system speed. In addition, the design-software tools can deal with each function generator independently.This flexibility improves cell usage.Flip-FlopsEach CLB contains two flip-flops that can be used to regis-ter (store) the function generator outputs. The flip-flops and function generators can also be used independently (see Figure 2). The CLB input DIN can be used as a direct input to either of the two flip-flops. H1 can also drive either flip-flop via the H-LUT with a slight additional delay.The two flip-flops have common clock (CK), clock enable (EC) and set/reset (SR) inputs. Internally both flip-flops are also controlled by a global initialization signal (GSR) which is described in detail in Global Signals: GSR and GTS ,page 20.Latches (Spartan-XL only)The Spartan-XL CLB storage elements can also be config-ured as latches. The two latches have common clock (K)and clock enable (EC) inputs. Functionality of the storage element is described in Table 2.Figure 2: Spartan/XL Simplified CLB Logic Diagram (some features not shown)Clock InputEach flip-flop can be triggered on either the rising or falling clock edge. The CLB clock line is shared by both flip-flops.However, the clock is individually invertible for each flip-flop (see CK path in Figure 3). Any inverter placed on the clock line in the design is automatically absorbed into the CLB. Clock EnableThe clock enable line (EC) is active High. The EC line is shared by both flip-flops in a CLB. If either one is left discon-nected, the clock enable for that flip-flop defaults to the active state. EC is not invertible within the CLB. The clock enable is synchronous to the clock and must satisfy the setup and hold timing specified for the device.Set/ResetThe set/reset line (SR) is an asynchronous active High con-trol of the flip-flop. SR can be configured as either set or reset at each flip-flop. This configuration option determines the state in which each flip-flop becomes operational after configuration. It also determines the effect of a GSR pulse during normal operation, and the effect of a pulse on the SR line of the CLB. The SR line is shared by both flip-flops. If SR is not specified for a flip-flop the set/reset for that flip-flop defaults to the inactive state. SR is not invertible within the CLB.CLB Signal Flow ControlIn addition to the H-LUT input control multiplexers (shown in box "A" of Figure 2, page 4) there are signal flow control multiplexers (shown in box "B" of Figure 2) which select the signals which drive the flip-flop inputs and the combinatorial CLB outputs (X and Y).Each flip-flop input is driven from a 4:1 multiplexer which selects among the three LUT outputs and DIN as the data source.Each combinatorial output is driven from a 2:1 multiplexer which selects between two of the LUT outputs. The X output can be driven from the F-LUT or H-LUT, the Y output from G-LUT or H-LUT .Control SignalsThere are four signal control multiplexers on the input of the CLB. These multiplexers allow the internal CLB control sig-nals (H1, DIN, SR, and EC in Figure 2 and Figure 4) to be driven from any of the four general control inputs (C1-C4 in Figure 4) into the CLB. Any of these inputs can drive any of the four internal control signals.T able 2: CLB Storage Element FunctionalityLegend:XDon ’t careRising edge (clock not inverted).SR Set or Reset value. Reset is default.0*Input is Low or unconnected (default value)1*Input is High or unconnected (default value)Figure 3: CLB Flip-Flop Functional Block Diagram6DS060 (v1.6) September 19, 2001The four internal control signals are:•EC: Enable Clock•SR: Asynchronous Set/Reset or H function generator Input 0•DIN: Direct In or H function generator Input 2•H1: H function generator Input 1.Input/Output Blocks (IOBs)User-configurable input/output blocks (IOBs) provide the interface between external package pins and the internal logic. Each IOB controls one package pin and can be con-figured for input, output, or bidirectional signals. Figure 6shows a simplified functional block diagram of the Spar-tan/XL IOB.IOB Input Signal PathThe input signal to the IOB can be configured to either go directly to the routing channels (via I1 and I2 in Figure 6) or to the input register. The input register can be programmed as either an edge-triggered flip-flop or a level-sensitive latch. The functionality of this register is shown in Table 3,and a simplified block diagram of the register can be seen in Figure 5.Figure 4: CLB Control Signal InterfaceFigure 5: IOB Flip-Flop/Latch Functional BlockDiagramTable 3: Input Register FunctionalityX Don ’t care.Rising edge (clock not inverted).SR Set or Reset value. Reset is default.0*Input is Low or unconnected (default value)1*Input is High or unconnected (default value)The register choice is made by placing the appropriate library symbol. For example, IFD is the basic input flip-flop (rising edge triggered), and ILD is the basic input latch (transparent-High). Variations with inverted clocks are also available. The clock signal inverter is also shown in Figure5 on the CK line.The Spartan IOB data input path has a one-tap delay ele-ment: either the delay is inserted (default), or it is not. The Spartan-XL IOB data input path has a two-tap delay ele-ment, with choices of a full delay, a partial delay, or no delay. The added delay guarantees a zero hold time with respect to clocks routed through the global clock buffers. (See Glo-bal Nets and Buffers, page12 for a description of the glo-bal clock buffers in the Spartan/XL families.) For a shorter input register setup time, with positive hold-time, attach a NODELAY attribute or property to the flip-flop.The output of the input register goes to the routing channels (via I1 and I2 in Figure6). The I1 and I2 signals that exit the IOB can each carry either the direct or registered input signal.The 5V Spartan input buffers can be globally configured for either TTL (1.2V) or CMOS (VCC/2) thresholds, using an option in the bitstream generation software. The Spartan output levels are also configurable; the two global adjust-ments of input threshold and output level are independent. The inputs of Spartan devices can be driven by the outputs of any 3.3V device, if the Spartan inputs are in TTL mode. Input and output thresholds are TTL on all configuration pins until the configuration has been loaded into the device and specifies how they are to be used. Spartan-XL inputs are TTL compatible and 3.3V CMOS compatible. Supported sources for Spartan/XL device inputs are shown in Table4.Spartan-XL I/Os are fully 5V tolerant even though the V CC is 3.3V. This allows 5V signals to directly connect to the Spar-tan-XL inputs without damage, as shown in Table4. In addi-tion, the 3.3V V CC can be applied before or after 5V signals are applied to the I/Os. This makes the Spartan-XL devices immune to power supply sequencing problems.Figure 6: Simplified Spartan/XL IOB Block Diagram8DS060 (v1.6) September 19, 2001Spartan-XL V CC ClampingSpartan-XL FPGAs have an optional clamping diode con-nected from each I/O to V CC . When enabled they clamp ringing transients back to the 3.3V supply rail. This clamping action is required in 3.3V PCI applications. V CC clamping is a global option affecting all I/O pins.Spartan-XL devices are fully 5V TTL I/O compatible if V CC clamping is not enabled. With V CC clamping enabled, the Spartan-XL devices will begin to clamp input voltages to one diode voltage drop above V CC . If enabled, TTL I/O com-patibility is maintained but full 5V I/O tolerance is sacrificed.The user may select either 5V tolerance (default) or 3.3V PCI compatibility. In both cases negative voltage is clamped to one diode voltage drop below ground.Spartan-XL devices are compatible with TTL, LVTTL, PCI 3V, PCI 5V and LVCMOS signalling. The various standards are illustrated in Table 5.Additional Fast Capture Input Latch (Spartan-XL only)The Spartan-XL IOB has an additional optional latch on the input. This latch is clocked by the clock used for the output flip-flop rather than the input clock. Therefore, two different clocks can be used to clock the two input storage elements.This additional latch allows the fast capture of input data,which is then synchronized to the internal clock by the IOB flip-flop or latch.T o place the Fast Capture latch in a design, use one of the special library symbols, ILFFX or ILFLX. ILFFX is a trans-parent-Low Fast Capture latch followed by an active High input flip-flop. ILFLX is a transparent Low Fast Capture latch followed by a transparent High input latch. Any of the clock inputs can be inverted before driving the library element,and the inverter is absorbed into the IOB.IOB Output Signal PathOutput signals can be optionally inverted within the IOB,and can pass directly to the output buffer or be stored in an edge-triggered flip-flop and then to the output buffer. The functionality of this flip-flop is shown in T able 6.T able 4: Supported Sources for Spartan/XL InputsT able 5: I/O Standards Supported by Spartan-XL FPGAsTable 6: Output Flip-Flop Functionality X Don ’t careRising edge (clock not inverted). SR Set or Reset value. Reset is default.0*Input is Low or unconnected (default value)1*Input is High or unconnected (default value)Z3-stateOutput Multiplexer/2-Input Function Generator (Spartan-XL only)The output path in the Spartan-XL IOB contains an addi-tional multiplexer not available in the Spartan IOB. The mul-tiplexer can also be configured as a 2-input function generator, implementing a pass gate, AND gate, OR gate, or XOR gate, with 0, 1, or 2 inverted inputs.When configured as a multiplexer, this feature allows two output signals to time-share the same output pad, effec-tively doubling the number of device outputs without requir-ing a larger, more expensive package. The select input is the pin used for the output flip-flop clock, OK.When the multiplexer is configured as a 2-input function generator, logic can be implemented within the IOB itself. Combined with a Global buffer, this arrangement allows very high-speed gating of a single signal. For example, a wide decoder can be implemented in CLBs, and its output gated with a Read or Write Strobe driven by a global buffer. The user can specify that the IOB function generator be used by placing special library symbols beginning with the letter "O." For example, a 2-input AND gate in the IOB func-tion generator is called OAND2. Use the symbol input pin labeled "F" for the signal on the critical path. This signal is placed on the OK pin — the IOB input with the shortest delay to the function generator. Two examples are shown in Figure7.Output BufferAn active High 3-state signal can be used to place the out-put buffer in a high-impedance state, implementing 3-state outputs or bidirectional I/O. Under configuration control, the output (O) and output 3-state (T) signals can be inverted. The polarity of these signals is independently configured for each IOB (see Figure6, page7). An output can be config-ured as open-drain (open-collector) by tying the 3-state pin (T) to the output signal, and the input pin (I) to Ground.By default, a 5V Spartan device output buffer pull-up struc-ture is configured as a TTL-like totem-pole. The High driver is an n-channel pull-up transistor, pulling to a voltage one transistor threshold below V CC. Alternatively, the outputs can be globally configured as CMOS drivers, with additional p-channel pull-up transistors pulling to V CC. This option, applied using the bitstream generation software, applies to all outputs on the device. It is not individually programma-ble.All Spartan-XL device outputs are configured as CMOS drivers, therefore driving rail-to-rail. The Spartan-XL outputs are individually programmable for 12mA or 24mA output drive.Any 5V Spartan device with its outputs configured in TTL mode can drive the inputs of any typical 3.3V device. Sup-ported destinations for Spartan/XL device outputs are shown in Table7.Three-State Register (Spartan-XL Only)Spartan-XL devices incorporate an optional register control-ling the three-state enable in the IOBs. The use of the three-state control register can significantly improve output enable and disable time.Output Slew RateThe slew rate of each output buffer is, by default, reduced, to minimize power bus transients when switching non-criti-cal signals. For critical signals, attach a FAST attribute or property to the output buffer or flip-flop.Spartan/XL devices have a feature called "Soft Start-up," designed to reduce ground bounce when all outputs are turned on simultaneously at the end of configuration. When the configuration process is finished and the device starts up, the first activation of the outputs is automatically slew-rate limited. Immediately following the initial activation of the I/O, the slew rate of the individual outputs is deter-mined by the individual configuration option for each IOB. Pull-up and Pull-down NetworkProgrammable pull-up and pull-down resistors are used fortying unused pins to V CC or Ground to minimize power con-sumption and reduce noise sensitivity. The configurablepull-up resistor is a p-channel transistor that pulls to V CC.The configurable pull-down resistor is an n-channel transis-tor that pulls to Ground. The value of these resistors is typi-cally 20KΩ − 100KΩ (See "Spartan DC Characteristics Figure 7: AND and MUX Symbols in Spartan-XL IOB10DS060 (v1.6) September 19, 2001Over Operating Conditions" on page 43.). This high value makes them unsuitable as wired-AND pull-up resistors.After configuration, voltage levels of unused pads, bonded or unbonded, must be valid logic levels, to reduce noise sensitivity and avoid excess current. Therefore, by default,unused pads are configured with the internal pull-up resistor active. Alternatively, they can be individually configured with the pull-down resistor, or as a driven output, or to be driven by an external source. To activate the internal pull-up, attach the PULLUP library component to the net attached to the pad. To activate the internal pull-down, attach the PULL-DOWN library component to the net attached to the pad.Set/ResetAs with the CLB registers, the GSR signal can be used to set or clear the input and output registers, depending on the value of the INIT attribute or property. The two flip-flops can be individually configured to set or clear on reset and after configuration. Other than the global GSR net, no user-con-trolled set/reset signal is available to the I/O flip-flops (Figure 5). The choice of set or reset applies to both the ini-tial state of the flip-flop and the response to the GSR pulse.Independent ClocksSeparate clock signals are provided for the input (IK) and output (OK) flip-flops. The clock can be independently inverted for each flip-flop within the IOB, generating eitherfalling-edge or rising-edge triggered flip-flops. The clock inputs for each IOB are mon Clock EnablesThe input and output flip-flops in each IOB have a common clock enable input (see EC signal in Figure 5), which through configuration, can be activated individually for the input or output flip-flop, or both. This clock enable operates exactly like the EC signal on the Spartan/XL CLB. It cannot be inverted within the IOB.Routing Channel DescriptionAll internal routing channels are composed of metal seg-ments with programmable switching points and switching matrices to implement the desired routing. A structured,hierarchical matrix of routing channels is provided to achieve efficient automated routing.This section describes the routing channels available in Spartan/XL devices. Figure 8 shows a general block dia-gram of the CLB routing channels. The implementation soft-ware automatically assigns the appropriate resources based on the density and timing requirements of the design.The following description of the routing channels is for infor-mation only and is simplified with some minor details omit-ted. For an exact interconnect description the designer should open a design in the FPGA Editor and review the actual connections in this tool.The routing channels will be discussed as follows;•CLB routing channels which run along each row and column of the CLB array.•IOB routing channels which form a ring (called a VersaRing) around the outside of the CLB array. It connects the I/O with the CLB routing channels.•Global routing consists of dedicated networks primarily designed to distribute clocks throughout the device with minimum delay and skew. Global routing can also be used for other high-fanout signals.CLB Routing ChannelsThe routing channels around the CLB are derived from three types of interconnects; single-length, double-length,and longlines. At the intersection of each vertical and hori-zontal routing channel is a signal steering matrix called a Programmable Switch Matrix (PSM). Figure 8 shows the basic routing channel configuration showing single-length lines, double-length lines and longlines as well as the CLBs and PSMs. The CLB to routing channel interface is shown as well as how the PSMs interface at the channel intersec-tions.T able 7: Supported Destinations for Spartan/XL OutputsNotes:1.Only if destination device has 5V tolerant inputs.CLB InterfaceA block diagram of the CLB interface signals is shown in Figure9. The input signals to the CLB are distributed evenly on all four sides providing maximum routing flexibility. In general, the entire architecture is symmetrical and regular. It is well suited to established placement and routing algo-rithms. Inputs, outputs, and function generators can freely swap positions within a CLB to avoid routing congestion during the placement and routing operation. The exceptions are the clock (K) input and CIN/COUT signals. The K input is routed to dedicated global vertical lines as well as four single-length lines and is on the left side of the CLB. The CIN/COUT signals are routed through dedicated intercon-nects which do not interfere with the general routing struc-ture. The output signals from the CLB are available to drive both vertical and horizontal channels.Programmable Switch MatricesThe horizontal and vertical single- and double-length lines intersect at a box called a programmable switch matrix (PSM). Each PSM consists of programmable pass transis-tors used to establish connections between the lines (see Figure10).For example, a single-length signal entering on the right side of the switch matrix can be routed to a single-length line on the top, left, or bottom sides, or any combination thereof, if multiple branches are required. Similarly, a dou-ble-length signal can be routed to a double-length line on any or all of the other three edges of the programmable switch matrix.Single-Length LinesSingle-length lines provide the greatest interconnect flexibil-ity and offer fast routing between adjacent blocks. There are eight vertical and eight horizontal single-length lines associ-ated with each CLB. These lines connect the switching matrices that are located in every row and column of CLBs. Single-length lines are connected by way of the program-mable switch matrices, as shown in Figure10. Routing con-nectivity is shown in Figure8.Single-length lines incur a delay whenever they go through a PSM. Therefore, they are not suitable for routing signals for long distances. They are normally used to conduct sig-nals within a localized area and to provide the branching for nets with fanout greater than one.Figure 8: Spartan/XL CLB Routing Channels and Interface Block DiagramFigure 9: CLB Interconnect Signals。

5962-8864405VXXA资料

Standard Products Data Sheet

UT63M1XX MIL-STD-1553A/B Bus Transceiver

Sept. 1999

FEATURES q Full conformance to MIL-STD-1553A and 1553B q Completely monolithic bipolar technology q Low power consumption q Fit and functionally compatible to industry standard 631XX series q Idle low encoding version q Flexible power supply voltages: V CC=+5V, V EE=-12V or 15V, and V CCA=+5V to +12V or +5V to +15V -

POWER AND GROUND NAME VCC (A) VCC (B) VCCA (A) VCCA (B) VEE (A) VEE (B) GND (A) GND (B) PACKAGE PIN SINGLE DUAL 20 33 N/A 13 N/A 19 N/A 3, 9, 18 N/A 24 28 19 32 23 3, 7, 31 12, 16, 22 TYPE PWR PWR PWR PWR PWR PWR GND GND Ground reference -12 or -15VDC power (± 5%) Recommended de-coupling capacitors 4.7µF and.1µF +5 to +12VDC power or +5 to +15VDC power (± 5%) +5VDC power (±10%) DESCRIPTION

code v参考手册中文版

CODE V 参考手册中文版

参考手册中文版

变更控制责任人

评审责任人

读者范围

作者:魏葰

页数:28

关键词:

未经 FLOMS 许可,不得擅自复制

CODE V 参考手册中文版

修订人 修订日期 状态

文档修订记录

版本 变更请求

文档作者 :魏葰 标识版本 :CODE V Manual/1.0 更新日期 :2008/06/11 文档状态 :概念

未经 FLOMS 许可,不得擅自复制 第 11 页 共 28 页

CODE V 参考手册中文版

文档作者 :魏葰 标识版本 :CODE V Manual/1.0 更新日期 :2008/06/11 文档状态 :概念

输出描述 技术要点 FMA—视场图 何时使用视场图功能选项 缺省操作 命令清单 定义物方空间网格设置 定义非均匀参考网格设置 定义全视场显示设置 定义波阵面拟合设置 定义视场描述设置 输入与计算讨论 输出描述 技术要点 FOV—双目视场绘图 何时使用双目视场绘图 缺省操作 命令清单 定义计算与绘图控制 定义图形控制 定义特定/多重模式投影控制 输入与计算讨论 输出描述 BEA—高斯光束追迹 何时使用高斯光束追迹功能选项 缺省操作 命令清单 定义输入光束设置

VPlayer 用户手册(Windows)-V2.5.2说明书

用户手册VPlayerV2.5.2 NS170000347西安诺瓦星云科技股份有限公司更新记录发布版本 发布日期 修订说明 V2.5.22019-05-31增加1个功能:软件语言支持日语、韩语、法语、西班牙语。

V2.5.1 2019-05-22 增加2个功能:● 视频音量开启和关闭。

●硬件加速开启和关闭。

资料更新3个内容:● 增加“配置项检查”和“FAQ ”章节。

● 更新封面并增加封底。

● 更新与VNNOX 相关的描述。

解决3个问题:● 图片切换视频时出现黑场。

● 插播的清单中媒体全部过期时,插播时间段内播放黑屏。

●流媒体切换其他媒体后,流媒体声音不消失。

西安诺瓦星云科技股份有限公司目录更新记录 (i)目录 ..................................................................................................................................................... ii 1 软件简介 .......................................................................................................................................... 1 2 软件安装 .......................................................................................................................................... 2 3 播放器绑定 ...................................................................................................................................... 3 4 配置项检查 .. (5)4.1 Windows 自动更新 ....................................................................................................................................... 5 4.2 防火墙 ......................................................................................................................................................... 6 4.3 关屏和睡眠 .................................................................................................................................................. 7 4.4 屏幕缩放率和多屏显示模式 ......................................................................................................................... 7 4.5 UAC ............................................................................................................................................................. 8 4.6 Antimalware Service Executable ................................................................................................................. 9 4.7 Superfetch (9)5 通用功能 (11)5.1 设置播放窗口 (11)5.2 锁定屏幕 ..................................................................................................................................................... 11 5.3 设置系统信息 (11)5.4 查看软件信息 (12)6 FAQ (13)6.1 如何处理视频无法正常播放的问题 ............................................................................................................ 13 6.2 如何设置防火墙入站规则 .. (13)西安诺瓦星云科技股份有限公司1软件简介VPlayer 是诺瓦科技推出的一款应用软件,作为终端播放器可应用于安装Windows 系统的设备。

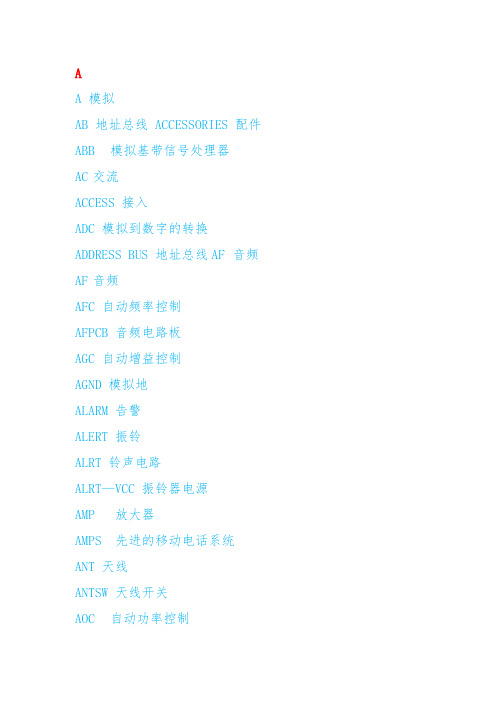

手机维修术语中英文对照表

AA 模拟AB 地址总线 ACCESSORIES 配件ABB 模拟基带信号处理器AC 交流ACCESS 接入ADC 模拟到数字的转换ADDRESS BUS 地址总线AF 音频AF 音频AFC 自动频率控制AFPCB 音频电路板AGC 自动增益控制AGND 模拟地ALARM 告警ALERT 振铃ALRT 铃声电路ALRT—VCC 振铃器电源AMP 放大器AMPS 先进的移动电话系统ANT 天线ANTSW 天线开关AOC 自动功率控制AOC-DRIVE 自动功率控制驱动APC 音频处理芯片ASIC 专用应用集成电路AUC 鉴权中心AUDIO 音频AUTO 自动AUX 辅助AVCC 音频供电A/D 模拟/数字转换A/L 音频/逻辑板APC 自动功率控制BBIT 比特BACKLIGHT 背光BURST 突发脉冲串BCCH 广播信道BW 带宽BUSY 忙BUS 总线BARRING 限制BCD 二/十进制码BPF 带通滤波器Block Digram 方框图Backlight 背光Base Band 基带(信号)BATT+ 电池BATTERY 电池BIC 总线接口芯片BS 基站BUZZ 振铃BDR 接收数据信号BDX 发送数据信号BKLT—EN 背景灯启/闭控制BALUN 平衡/不平衡转换BCH 广播信道BDR 接收数据信号BDX 发射数据信号BIAS 偏压CCARD 卡CLONE 复制CODE 代码CONNECTOR 连接器CONTACT SERVICER 联系服务商CONTROL 控制COUPLING 耦合CRYSTAL 晶体COVER 覆盖CP 表示鉴相器的输出端CP—RX RXVCO控制信号输出CP-TX 发射VCO控制输出端CPU 中央处理器CRYSTA 晶振CS 片选CS FLASH 闪存片选CS RAM 随机存储器片选CS ROM 只读存储器片选CAR 电压控制/音频/振铃模块CCH 控制信道CDMA 码分多址CONVERTER 变频器CPU 中央处理器CHARGE 充电CLK OUT 逻辑时钟输出CLK SELECT 时钟选择信号CODEC 编码CP-RX RXVCO 接收锁相压控振荡器CP-TX TXVCO 发射锁相压控振荡器CHARG 充电电源负端CHARG+ 充电正电源CHECK 检查DDB 数据总线DTMF 双音多频DTX 非连续发送DATA 数据DISABLE 禁用DISTORTION 失真DEINTERLEARING 去交织DECIPHERING 解密DBB 数字基带信号处理器DC 直流DCIN 外接电源输入DCON 直流接通DCS 数字通信系统DCSPA 功率放大器输出的DCS信号DCSRX DCS射频接收信号DCS-SEL DCS频段选择信号DEMOD 解调DET 检测DFMS 来数据信号DGND 数字地DIGITAL 数字DIODE 二极管DISPLAY 显示DM-CS 片选信号DP-EN 显示电路启动控制DSP 数字语音处理器DTMS 到数据信号D-TX-VCO DCS发射VCO切换控制DYNATRON 晶体管DUPLEX 双工Duplex Saparation 双工间隔DCS-LNA275 1800MHz低噪声放大器电压(2.75V)DCS—SEL 频段选择信号之一(1800MHz)DCS-VCO RXVCO频段切换控制信号之一(1800MHz)DEMODULATION 解调DM-CS 发射机控制信号,控制TXVCO和I/O调制器DP—EN 显示电路启动控制D-TX—VCO 1800MHz发射压控振荡器EEAR 听筒E-TACS 扩展的全接入通信系统ESN 电子串号E2PROM 可擦写可编程只读存储器EPR 有效辐射功率ENABLE 启用EQUALIZER 均衡器EAR 耳机EL 发光EN 使能ENAB 使能ERASABLE 可擦写EXC 外部EXT 外部的EXT-B+ 外接电源、充电电压输入FFDMA 频分多址FULL DUPLEX 全双工FACCH 快接入控制信道Freq。