串口通信vhdl程序

基于VHDL语言的同步串口设计

F GA T ec c iSt n eu nes l i scmpee nQur sI. h nefc i ut ycn g r g te P , h i ut migsq ec i a o i o l di at I T eit aec ci b o f ui r ’i mu t n t u r r i n h

1 NP l NM DI N

O T U P OU M T

D OU T T V 2AC 0 F L 3 0 I 1 S S L C K

M92 0 50 0

作者简 介;徐 奎 ( 8 一 ) 男,研 究 1 1 , 9 方向:数 字通信 。朱晓明 ( 9 l ) 1 6 一 ,男, 高工。研 究方向:数字通信 。

2 T V 2 A 0 0芯片工作原理 L 3 0 11

由图 1 可知, L 3 0 I 1 进行 串行通信时使 T V 2A C 0

用4 个管脚 :D N、D U 、F 、S L . I 和 I O T S C K 。D N

用两路模拟输入信号 中的一路进行模数转换 ,通过

D U O T传至 F G 同样通过 D 接受 F G P A; N I P A传来 的数据 ,进行数模转换以后 ,由模拟输出端输 出。

V L I K C

图 1 硬件连接 示意图

维普资讯

基 于 VD 语 言的同步 串口设计 HL

3 L30 l1 TV2AC0时序分析

T V 2A C 0 L 30 I 1 有两种工作模式 : 首通信、 次通 信 。其时序 图如图 2 所示 ,在首通信期间可以通过 在最低位发送逻辑 1 来请求次通信 , 可以利用次通 信对 T V 2A C 0的寄存器进行写或者读操作 , L 30 I 1 来初始化 T V 2 A C 0 L 30 I 1 和监测 T V 2A C 0的工 L 30 I 1

51单片机的串口通信程序(C语言)

51单片机的串口通信程序(C语言) 51单片机的串口通信程序(C语言)在嵌入式系统中,串口通信是一种常见的数据传输方式,也是单片机与外部设备进行通信的重要手段之一。

本文将介绍使用C语言编写51单片机的串口通信程序。

1. 硬件准备在开始编写串口通信程序之前,需要准备好相应的硬件设备。

首先,我们需要一块51单片机开发板,内置了串口通信功能。

另外,我们还需要连接一个与单片机通信的外部设备,例如计算机或其他单片机。

2. 引入头文件在C语言中,我们需要引入相应的头文件来使用串口通信相关的函数。

在51单片机中,我们需要引入reg51.h头文件,以便使用单片机的寄存器操作相关函数。

同时,我们还需要引入头文件来定义串口通信的相关寄存器。

3. 配置串口参数在使用串口通信之前,我们需要配置串口的参数,例如波特率、数据位、停止位等。

这些参数的配置需要根据实际需要进行调整。

在51单片机中,我们可以通过写入相应的寄存器来配置串口参数。

4. 初始化串口在配置完串口参数之后,我们需要初始化串口,以便开始进行数据的发送和接收。

初始化串口的过程包括打开串口、设置中断等。

5. 数据发送在串口通信中,数据的发送通常分为两种方式:阻塞发送和非阻塞发送。

阻塞发送是指程序在发送完数据之后才会继续执行下面的代码,而非阻塞发送是指程序在发送数据的同时可以继续执行其他代码。

6. 数据接收数据的接收与数据的发送类似,同样有阻塞接收和非阻塞接收两种方式。

在接收数据时,需要不断地检测是否有数据到达,并及时进行处理。

7. 中断处理在串口通信中,中断是一种常见的处理方式。

通过使用中断,可以及时地响应串口数据的到达或者发送完成等事件,提高程序的处理效率。

8. 串口通信实例下面是一个简单的串口通信实例,用于在51单片机与计算机之间进行数据的传输。

```c#include <reg51.h>#include <stdio.h>#define BAUDRATE 9600#define FOSC 11059200void UART_init(){TMOD = 0x20; // 设置定时器1为模式2SCON = 0x50; // 设置串口为模式1,允许接收TH1 = 256 - FOSC / 12 / 32 / BAUDRATE; // 计算波特率定时器重载值TR1 = 1; // 启动定时器1EA = 1; // 允许中断ES = 1; // 允许串口中断}void UART_send_byte(unsigned char byte){SBUF = byte;while (!TI); // 等待发送完成TI = 0; // 清除发送完成标志位}unsigned char UART_receive_byte(){while (!RI); // 等待接收完成RI = 0; // 清除接收完成标志位return SBUF;}void UART_send_string(char *s){while (*s){UART_send_byte(*s);s++;}}void main(){UART_init();UART_send_string("Hello, World!"); while (1){unsigned char data = UART_receive_byte();// 对接收到的数据进行处理}}```总结:通过以上步骤,我们可以编写出简单的51单片机串口通信程序。

基于VHDL的串行同步通信SPI设计

基于VHDL的串行同步通信SPI设计串行同步通信(SPI)是一种常用的通信协议,用于在集成电路中进行片内通信。

它是一种全双工的通信方式,通过四根信号线来传输数据:SCLK(时钟线),MOSI(主设备输出从设备输入线),MISO(主设备输入从设备输出线)和SS(片选线)。

SPI采用主从架构,其中主设备控制通信时序,并负责发起数据传输。

从设备在主设备的指令下进行相应操作并传输数据。

以下是一个基于VHDL的串行同步通信SPI的设计,包括主设备和从设备两部分。

主设备部分:```library ieee;use ieee.std_logic_1164.all;entity spi_master isportCLK: in std_logic; -- 时钟线MOSI: out std_logic; -- 主设备输出从设备输入线MISO: in std_logic; -- 主设备输入从设备输出线SS: out std_logic; -- 片选线data_out: out std_logic_vector(7 downto 0); -- 发送数据data_in: in std_logic_vector(7 downto 0); -- 接收数据valid: out std_logic -- 有效数据标志位end spi_master;architecture behavioral of spi_master istype state_type is (idle, send_data, receive_data); signal state: state_type;signal count: integer range 0 to 7;signal tx_data: std_logic_vector(7 downto 0);signal rx_data: std_logic_vector(7 downto 0);beginprocess (CLK)beginif rising_edge(CLK) thencase state iswhen idle =>if SS = '0' thenstate <= send_data;count <= 0;tx_data <= data_out;end if;when send_data =>MOSI <= tx_data(count); -- 发送数据位count <= count + 1;if count = 7 thenstate <= receive_data;end if;when receive_data =>rx_data(count) <= MISO; -- 接收数据位count <= count - 1;if count = 0 thenstate <= idle;valid <= '1';data_in <= rx_data;end if;end case;end if;end process;end behavioral;```从设备部分:```library ieee;use ieee.std_logic_1164.all;entity spi_slave isportCLK: in std_logic; -- 时钟线MOSI: in std_logic; -- 主设备输出从设备输入线MISO: out std_logic; -- 主设备输入从设备输出线SS: in std_logic; -- 片选线data_in: in std_logic_vector(7 downto 0); -- 接收数据data_out: out std_logic_vector(7 downto 0); -- 发送数据valid: in std_logic -- 有效数据标志位end spi_slave;architecture behavioral of spi_slave istype state_type is (idle, receive_data, send_data);signal state: state_type;signal count: integer range 0 to 7;signal tx_data: std_logic_vector(7 downto 0);signal rx_data: std_logic_vector(7 downto 0); beginprocess (CLK)beginif rising_edge(CLK) thencase state iswhen idle =>if SS = '0' thenstate <= receive_data;count <= 0;end if;when receive_data =>rx_data(count) <= MOSI; -- 接收数据位count <= count + 1;if count = 7 thenstate <= send_data;valid <= '1';data_in <= rx_data;end if;when send_data =>MISO <= tx_data(count); -- 发送数据位count <= count - 1;if count = 0 thenstate <= idle;tx_data <= data_out;end if;end case;end if;end process;end behavioral;```在主设备部分,设计了一个状态机来控制 SPI 的通信过程。

VHDL 实现UART(四)

17.

ponent receiver -- receiver元件

19.Port( bclkr : in STD_LOGIC; -- 分频后的时钟

20.resetr : in STD_LOGIC; -- RESET OF RECEIVER,<= '1' 有效

64.rxdr => rxd,

65.r_ready => irdy,

66.rbuf => ibuffer

67.);

68.

69.u3:

70.transfer port map(

71.bclkt => b,

72.resett => reset,

73.xmit_cmd_p => irdy,

21.rxdr : in STD_LOGIC; -- RXD IN RECEIVER COMPONENT

22.r_ready : out STD_LOGIC; -- RECEIVER 接受数据后给出的ready信号

23.rbuf : out STD_LOGIC_VECTOR (7 downto 0) -- 数据接受缓冲区

32.xmit_cmd_p : in STD_LOGIC; -- 传输命令信号,

33.txdbuf : in STD_LOGIC_VECTOR (7 downto 0); -- 发送数据缓冲区

34.txd : out STD_LOGIC; -- TXD IN TRANSFER

35.txd_done : out STD_LOGIC -- 数据发送完毕信号,也是标志位,没有控制作用,在停止位后变化. <= '1' 表示数据发送完毕

vhdl语言100例程序

vhdl语言100例程序以下是100个关于VHDL语言的程序示例:1. 用VHDL编写一个计数器模块2. 用VHDL编写一个SR-Latch模块3. 用VHDL编写一个JK-Flip Flop模块4. 用VHDL编写一个D-Flip Flop模块5. 用VHDL编写一个T-Flip Flop模块6. 用VHDL编写一个复位计数器模块7. 用VHDL编写一个移位寄存器模块8. 用VHDL编写一个状态机模块9. 用VHDL编写一个MUX模块10. 用VHDL编写一个DeMUX模块11. 用VHDL编写一个加法器模块12. 用VHDL编写一个减法器模块13. 用VHDL编写一个乘法器模块14. 用VHDL编写一个除法器模块15. 用VHDL编写一个比较器模块16. 用VHDL编写一个位逻辑模块17. 用VHDL编写一个字逻辑模块18. 用VHDL编写一个数据选择器模块19. 用VHDL编写一个FIFO队列模块20. 用VHDL编写一个LIFO栈模块21. 用VHDL编写一个流水线模块22. 用VHDL编写一个中断控制器模块23. 用VHDL编写一个时钟分频器模块24. 用VHDL编写一个IO控制器模块25. 用VHDL编写一个SPI通信控制器模块26. 用VHDL编写一个I2C通信控制器模块27. 用VHDL编写一个UART通信控制器模块28. 用VHDL编写一个哈希函数模块29. 用VHDL编写一个随机数产生器模块30. 用VHDL编写一个CRC校验器模块31. 用VHDL编写一个AES加密算法模块32. 用VHDL编写一个DES加密算法模块33. 用VHDL编写一个SHA加密算法模块34. 用VHDL编写一个MD5加密算法模块35. 用VHDL编写一个RSA加密算法模块36. 用VHDL编写一个卷积滤波器模块37. 用VHDL编写一个峰值检测器模块38. 用VHDL编写一个平滑滤波器模块39. 用VHDL编写一个中值滤波器模块40. 用VHDL编写一个微处理器模块41. 用VHDL编写一个信号发生器模块42. 用VHDL编写一个信号采集器模块43. 用VHDL编写一个频率计算器模块44. 用VHDL编写一个相位计算器模块45. 用VHDL编写一个时序分析器模块46. 用VHDL编写一个正弦波产生器模块47. 用VHDL编写一个余弦波产生器模块48. 用VHDL编写一个数字滤波器模块49. 用VHDL编写一个数字信号处理器模块50. 用VHDL编写一个数字识别模块51. 用VHDL编写一个自动售货机模块52. 用VHDL编写一个二进制加法器模块53. 用VHDL编写一个二进制减法器模块54. 用VHDL编写一个二进制乘法器模块55. 用VHDL编写一个二进制除法器模块56. 用VHDL编写一个自然对数模块57. 用VHDL编写一个指数函数模块58. 用VHDL编写一个三角函数模块59. 用VHDL编写一个高斯滤波器模块60. 用VHDL编写一个激光传感器模块61. 用VHDL编写一个超声波传感器模块62. 用VHDL编写一个光电传感器模块63. 用VHDL编写一个温度传感器模块64. 用VHDL编写一个气压传感器模块65. 用VHDL编写一个陀螺仪模块67. 用VHDL编写一个电流传感器模块68. 用VHDL编写一个电容传感器模块69. 用VHDL编写一个磁场传感器模块70. 用VHDL编写一个通信电缆模块71. 用VHDL编写一个电源控制器模块72. 用VHDL编写一个电机控制器模块73. 用VHDL编写一个汽车控制器模块74. 用VHDL编写一个飞机控制器模块75. 用VHDL编写一个摄像头模块76. 用VHDL编写一个音频控制器模块77. 用VHDL编写一个扬声器控制器模块78. 用VHDL编写一个拨号器模块79. 用VHDL编写一个振动控制器模块80. 用VHDL编写一个压力控制器模块81. 用VHDL编写一个过滤器模块82. 用VHDL编写一个微波发射模块84. 用VHDL编写一个智能电表模块85. 用VHDL编写一个闹钟模块86. 用VHDL编写一个计时器模块87. 用VHDL编写一个时间戳模块88. 用VHDL编写一个脉冲宽度模块89. 用VHDL编写一个电路仿真模块90. 用VHDL编写一个电路控制模块91. 用VHDL编写一个电路测试模块92. 用VHDL编写一个电路优化模块93. 用VHDL编写一个电路布局模块94. 用VHDL编写一个电路验证模块95. 用VHDL编写一个数字信号发生器模块96. 用VHDL编写一个数字信号反演器模块97. 用VHDL编写一个数字信号滤波器模块98. 用VHDL编写一个数字信号加速器模块99. 用VHDL编写一个数字信号降噪器模块100. 用VHDL编写一个数字信号解调器模块VHDL语言是一种硬件描述语言,它用于描述数字电路和系统。

串并转换VHDL

ready <= '1';

data_valid <= '0';

shift_start <= '0';

next_state <= shift;

when shift =>

reg_en <= '1';

ready : out std_logic; --low active,ready to recieve data

q : out std_logic

);

end p2s;

architecture Behavioral of p2s is

signal reg : std_logic_vector(7 downto 0);

-- Description: This module is designed to implement parallel to serial conversion

--------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity p2s is

port(

reset : in std_logic;

begin

counter: process(reset,clk,shift_start)

vhdl语言常用实例 -回复

vhdl语言常用实例-回复VHDL语言常用实例VHDL是一种硬件描述语言,广泛应用于数字系统的设计与验证中。

它提供了一种结构化的方式来描述电子系统的行为和结构。

在本篇文章中,将详细介绍VHDL语言的常用实例,并一步一步回答与之相关的内容。

1. VHDL的简介VHDL(VHSIC(Very High-Speed Integrated Circuit)Hardware Description Language)是一种用于描述和设计数字电路的硬件描述语言。

它是由美国国防部在20世纪80年代初提出并发展起来的,旨在解决高速集成电路设计的问题。

2. VHDL实例的编写步骤在编写VHDL实例之前,首先需要确定所要设计的电路的功能和结构。

接下来,可以根据电路的需求使用VHDL语言的各种特性来编写代码。

编写的过程可分为以下步骤:步骤一:定义实体在VHDL中,实体(Entity)用于描述电路的接口和输入输出信号的属性。

在定义实体时,需要指定实体的名称、输入输出端口以及信号类型。

步骤二:定义体(Architecture)定义体(Architecture)用于描述电路的功能和行为。

在定义体时,需要使用VHDL语言提供的语法和特性来描述所需的功能。

步骤三:模块化设计在VHDL中,可以使用模块化设计来实现复杂电路的描述和功能。

可以将电路划分为多个不同的模块,每个模块负责实现不同的功能。

通过将这些模块连接在一起,可以构建复杂的电路。

步骤四:仿真和验证在编写完VHDL代码后,可以使用仿真工具对代码进行验证。

通过仿真,可以模拟出电路的行为并检查其功能是否符合预期。

3. VHDL语言常用实例VHDL语言提供了丰富的语法和特性,可用于描述各种不同的电路和功能。

以下是几个常用的VHDL语言实例的示例:实例一:2-to-1多路选择器该实例描述了一个基本的2-to-1多路选择器电路。

此电路有两个输入信号A和B,一个选择信号S,一个输出信号Y。

CRC16校验码移位算法及VHDL实现4页word文档

CRC16校验码移位算法及VHDL实现在数据传输过程中,由于信道干扰,往往使得发送和接收的数据不一致。

为了降低误码率,保证传输数据的可靠性,通常会改进信道的传输质量或在传输的数据中加入校验信息。

在各种校验方法中,循环冗余校验CRC (CyclicRedundancy Check)是一种最常用的方法。

CRC校验技术是一种十分有效的数据传输错误检测技术,由于其编码和解码过程简单,检错和纠错能力强,广泛应用于通信领域用于实现差错控制。

串行通信普遍应用于工业通信控制领域,如何提高数据的传输可靠性尤为重要,现有的串口在数据传输过程中加入CRC校验可提高数据传输的可靠性。

普通串行口不自带CRC校验功能,大多数应用中都是通过软件编程计算CRC码后再附加在数据末尾传输的,由于软件执行耗费时间长,影响数据的传输速度。

现场可编程门阵列FPGA (Field-Programmable Gate Array)在数字系统设计中已被广泛使用。

用硬件描述语言(VHDL)实现CRC校验码的计算,然后下载到FPGA芯片中,硬件实现CRC校验,与软件实现相比,对数据的传输速度影响较小。

本文介绍一种CRC16校验码串行产生的方法,并给出了其VHDL实现及仿真分析。

1 CRC校验原理在发送方要发送的K位数据码后,以一定的规则产生一个r位用于校验的监督码,附加在原数据后面,构成的信息码为n=k+r位,因此,这种编码又叫(n,k)码。

接收方根据通信双方约定的规则进行校验,确定数据是否出错。

这个规则即“生成多项式”。

K位数据码表示为M(x),选择合适的CRC生成多项式G(x),G(x)的最高次幂为r。

把M(x)左移r位,即M(x)*xr对G(x)做不借位除法(即异或运算),所得余数为CRC校验码,即:其中R(x)为CRC校验码。

发送方以上述原理生成校验码附加在数据末尾发送出去,接收方接收到的数据也对同样的G(x)做除法,如果余数为0,则认为数据传送无误,否则按出错处理。

毕业设计55UART电路的VHDL设计与实现

本科生毕业论文(设计) 题目:UART电路的VHDL设计及实现院系计算机学院专业通信工程指导教师韩晓茹学生姓名姚芳学号0040622062004 年6 月9日UART电路的VHDL设计及实现作者:姚芳指导教师:韩晓茹摘要:UART是设备和设备间进行通信的关键,当一个设备需要和另一个连接的设备进行通信时,通常采用数字信号,这种源自并行的信号必须转换成串行信号才能通过有线或无线传输到另一台设备。

在接收端,串行信号又转换成并行信号进行处理,UART处理这种数据总线和串行口之间的串-并和并-串转换。

本文所要实现的就是就是这种串-并和并-串的转换,使之能够进行数据的传输。

本文介绍了用FPGA技术实现UART电路的一种方法,用VHDL进行编程,在Modelsim下进行编译及仿真等。

关键词:FPGA,VHDL,UART,接收,发送Abstract:UART is the key of communications between devices.When a device needs to communicate with a connected device,usually digital signals applied,which must be transformed into serialised signal to another device through wires or wireless space.When being received to process, the serialised signals must be transformed to parellised signals.UART processes this serial_data to parallel_data /parallel _data to serial_data transform between data bus and slave port. This paper is to implement this serial to parallel and parallel to serial transform and make the transferring between data properly.This paper introduces a method implemented by FPGA technique programmed by VHDL,simulated and compiled by Modelsim.Keyword:FPGA,VHDL ,UART,receive ,send目录第1章绪论 (1)1.1本文研究的意义 (1)1.2本文研究的内容 (1)第2章FPGA和VHDL语言简介 (2)2.1FPGA (2)2.2VHDL语言 (2)第3章串行通信的基本概念 (5)3.1串行通信的特点及通信方式 (5)3.2传输速率与传输距离 (11)3.3UART简介 (12)第4章UART结构 (13)4.1串行数据时钟 (13)4.2UART发送器 (14)4.3格式化 (14)4.4发送器状态 (14)4.5UART接收器 (15)4.6错误检测 (15)第5章UART的VHDL语言编写 (17)5.1UART的串行数据 (17)5.2UART整体结构 (18)5.3UART的接收部分 (19)5.4UART的发送部分 (21)5.5波特率发生部分 (23)5.6总线接口及中断 (25)第6章功能仿真 (26)6.1总体布线图 (26)6.2接收部分 (27)6.3发送部分 (30)第7章小结 (33)致谢: (34)参考文献: (35)第1章绪论1.1 本文研究的意义在1980至1990年代,提供FPGA数万逻辑门的FPGA器件主要被系统设计人员用作“连接逻辑”,将电路板上的不同元器件连接到一起,或用来修正ASIC不方便处理的问题。

VHDL语言入门教程

VHDL语言入门教程VHDL是一种硬件描述语言,主要用于设计数字电路和系统。

它是由美国国防部门于1980年代初开发的,目的是为了改进电子设计自动化(EDA)工具的开发效率和设计文档的可重复性。

VHDL广泛应用于数字信号处理(DSP)、嵌入式系统、通信系统和各种ASIC(专用集成电路)和FPGA(现场可编程门阵列)的设计。

本教程将介绍VHDL的基础知识,包括语法、数据类型和常见的建模技术。

一、VHDL的语法VHDL的语法由标识符、关键字、运算符和分隔符组成。

其中,标识符用于给变量、信号和实体命名,关键字用于定义语言特定的操作,运算符用于数学和逻辑运算,分隔符用于分隔语句。

VHDL中的代码以一个实体(entity)的声明开始,然后是体(architecture)的声明,最后是信号声明和进程(process)的描述。

以下是一个简单的例子:```vhdlentity AND_gate isportA, B: in std_logic;C: out std_logicend entity AND_gate;architecture Behavior of AND_gate isbeginC <= A and B;end architecture Behavior;```在这个例子中,我们声明了一个名为AND_gate的实体,它有两个输入信号A和B,一个输出信号C。

然后我们定义了一个名为Behavior的体,它描述了AND门的行为:C等于A与B的逻辑与运算结果。

二、VHDL的数据类型VHDL支持许多数据类型,包括标量类型、数据类型、自定义类型和引用类型。

标量类型包括bit、bit_vector、integer、real、std_logic和std_ulogic等。

其中,bit_vector是一组连续的位,std_logic和std_ulogic用于表示单个信号。

数据类型是由标量类型和数组类型组成的。

数组类型可以是一维、二维或更高维的,用于存储多个数据。

c语言怎么写串口通信编程

c语言怎么写串口通信编程串口通信是一种广泛应用于嵌入式系统和电子设备之间的通信方式。

无论是嵌入式开发还是电子设备控制,串口通信都是常见的需求。

在C语言中,实现串口通信需要通过操作串口的硬件寄存器和使用相应的通信协议来实现数据的发送和接收。

本文将一步一步介绍如何使用C语言编写串口通信程序。

第一步:打开串口要开始串口通信,首先需要打开串口。

在C语言中,可以使用文件操作函数来打开串口设备。

通常,串口设备被命名为/dev/ttyS0,/dev/ttyS1等,具体名称取决于系统。

下面是一个打开串口设备的示例代码:cinclude <stdio.h>include <fcntl.h>include <termios.h>int open_serial_port(const char *port) {int fd = open(port, O_RDWR O_NOCTTYO_NDELAY);if (fd == -1) {perror("open_serial_port");return -1;}设置串口属性struct termios options;tcgetattr(fd, &options);cfmakeraw(&options);cfsetspeed(&options, B9600);tcsetattr(fd, TCSANOW, &options);return fd;}int main() {const char *port = "/dev/ttyS0";int fd = open_serial_port(port);if (fd == -1) {打开串口失败,处理错误return -1;}串口已打开,可以进行数据的读写操作return 0;}在上面的代码中,open_serial_port函数用于打开指定的串口设备并进行一些必要的设置。

VHDL的串口程序

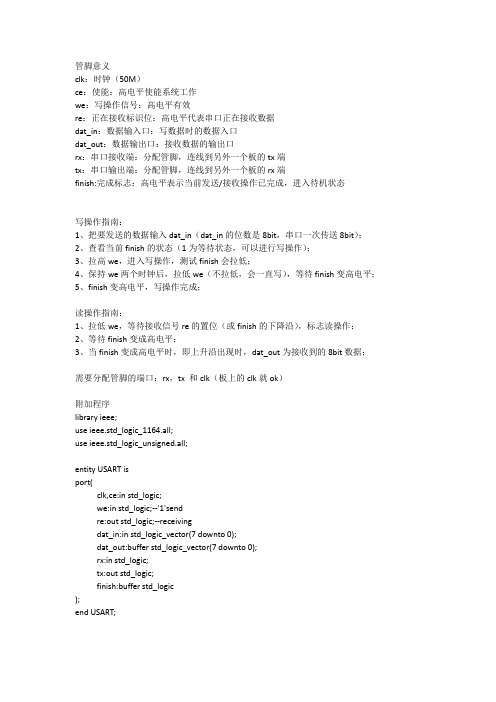

管脚意义clk:时钟(50M)ce:使能:高电平使能系统工作we:写操作信号:高电平有效re:正在接收标识位:高电平代表串口正在接收数据dat_in:数据输入口:写数据时的数据入口dat_out:数据输出口:接收数据的输出口rx:串口接收端:分配管脚,连线到另外一个板的tx端tx:串口输出端:分配管脚,连线到另外一个板的rx端finish:完成标志:高电平表示当前发送/接收操作已完成,进入待机状态写操作指南:1、把要发送的数据输入dat_in(dat_in的位数是8bit,串口一次传送8bit);2、查看当前finish的状态(1为等待状态,可以进行写操作);3、拉高we,进入写操作,测试finish会拉低;4、保持we两个时钟后,拉低we(不拉低,会一直写),等待finish变高电平;5、finish变高电平,写操作完成;读操作指南:1、拉低we,等待接收信号re的置位(或finish的下降沿),标志读操作;2、等待finish变成高电平;3、当finish变成高电平时,即上升沿出现时,dat_out为接收到的8bit数据;需要分配管脚的端口:rx,tx 和clk(板上的clk就ok)附加程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity USART isport(clk,ce:in std_logic;we:in std_logic;--'1'sendre:out std_logic;--receivingdat_in:in std_logic_vector(7 downto 0);dat_out:buffer std_logic_vector(7 downto 0);rx:in std_logic;tx:out std_logic;finish:buffer std_logic);end USART;architecture behave of USART istype state is (s0,s1,s2,s3);type modetype is (waiting,send,receive); signal pre_s,nx_s:state:=s0;signal clock,clk_out:std_logic;signal start,timed:std_logic;signal start2,timed2:std_logic;signal mode:modetype;signal en:std_logic:='0';signal dat:std_logic_vector(8 downto 0); signal dat_o:std_logic_vector(8 downto 0); signal t,s:std_logic;begindat_out<=dat_o(8 downto 1);s<=dat_o(0);tx<=not clk_out when mode=receive else t when mode=send else'0' ;cdiv:process(clk,en)--1usvariable cnt:integer range 0 to 25;beginif(en='0')thenclk_out<='1';cnt:=0;elsif(clk'event and clk='1')thencnt:=cnt+1;if(cnt=25)thencnt:=0;clk_out<=not clk_out;end if;end if;end process cdiv;--com:process(clock)--begin--if(clock'event and clock='1')then--pre_s<=nx_s;--end if;--end process com;con:process(clk,ce)beginif(ce='0')thennx_s<= s0;elsif(clk'event and clk='1')thencase nx_s iswhen s0=> --waitfinish<='1';mode<=waiting;start<='0';start2<='0';en<='0';if(rx='1')thenfinish<='0';mode<=receive;start<='1';en<='1';nx_s<=s1;--receiveelsif(we='1')thenfinish<='0';mode<=send;start2<='1';en<='0';nx_s<=s2;--sendelsestart<='0';start2<='0';mode<=waiting;finish<='1';en<='0';nx_s<=s0;--waitend if;when s1=> --receivestart<='1';re<='1';finish<='0';mode<=receive;en<='1';if(timed='1')thenstart<='0';finish<='1';mode<=waiting;re<='0';en<='0';nx_s<=s0;elsestart<='1';finish<='0';mode<=receive;re<='1';en<='1';nx_s<=s1;end if;when s2=> --sendstart2<='1';finish<='0';en<='0';mode<=send;if(timed2='1')thenstart2<='0';finish<='1';en<='0';mode<=waiting;nx_s<=s3;elsestart<='1';finish<='0';en<='0';mode<=send;nx_s<=s2;end if;when s3=>if(rx='0')thennx_s<=s0;elsenx_s<=s3;end if;when others=>nx_s<=s0;end case;end if;end process con;rec:process(clk_out,start) --receive variable count:integer range 0 to 9; beginif(start='0')thencount:=0;timed<='0';elsif(clk_out'event and clk_out='1')thendat_o<=dat_o(7 downto 0)& rx;count:=count+1;if(count=9)thencount:=0;timed<='1';end if;end if;end process rec;sen:process(rx,start2,dat_in) --send variable count:integer range 0 to 10; beginif(start2='0')thencount:=0;timed2<='0';t<='1';dat<=dat_in&'0';elsif(rx'event and rx='1')thent<=dat(8);dat<=dat(7 downto 0)& '0';count:=count+1;if(count=9)thencount:=0;timed2<='1';end if;end if;end process sen;end behave;。

基于VHDL的串行同步通信电路设计

r c i i gcr ut n i es q e c i lto e ev n ic i a d t e u n esmu ain. m

Ke wo d : y r s VHDL; n h o o sc mm u i a i n Ti e s q e e smu a i n Sy c r n u o n c t ; m e u nc i l to o

Abt c:T e crut ein f sr ls n ho o s o sat h i i r c d s o ei y c rn u c mmu iain ae o VHD n ld s e in f eil g a nc t b sd n o L icu e d sg o sr a

发 送 电路及 时序 仿真 的设 计 ,后 者 则 由波特 率 发生 器和 采 样 时钟 的设 计 、接 收 电路 的设 计及 时序仿 真 组 戍 关键 词 :V HDL 同步 通信 ; 时序仿 真 ;

中图分 类号 :T 3 30 P 9 .3 文献 标 识码 :A

Cic i De i n o e i l y c r n u mm u i a i n Ba e n VHDL r u t sg fS ra n h o o sCo S n c t s do o

一

致 。位 同步 是 实现 收 发 双 方 的码 元 同 步 , 由数 据

从抽象到具体级别硬件 的工业标准语言 ,它支持硬 件 的设计 、验证 、综 合和 测试 ,以及硬件 设计数据 的交 换 、维 护 、修 改和 硬 件 的 实 现 。具 有 捕述 能 力 强 、生 命 周 期 长 、支 持 大 规 模 设 计 的分 解 和 已有 设

O. . t ma i n I Au o t o 2 0 , o . 5 No 2 0 6 V 12 , .

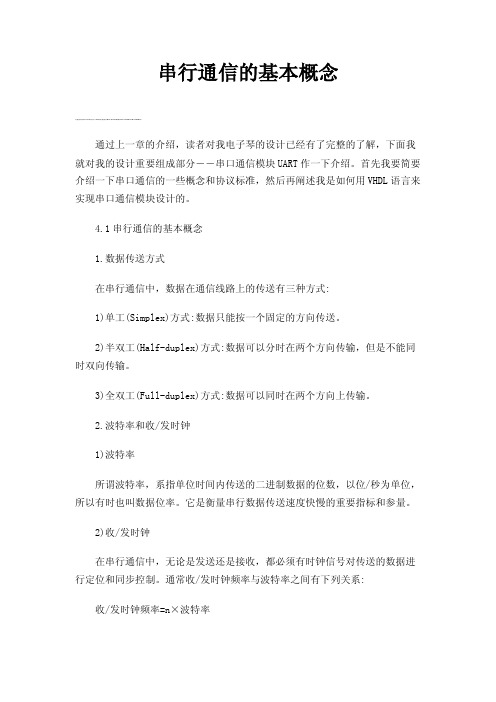

串行通信的基本概念

串行通信的基本概念000通过上一章的介绍,读者对我电子琴的设计已经有了完整的了解,下面我就对我的设计重要组成部分――串口通信模块UART作一下介绍。

首先我要简要介绍一下串口通信的一些概念和协议标准,然后再阐述我是如何用VHDL语言来实现串口通信模块设计的。

4.1串行通信的基本概念1.数据传送方式在串行通信中,数据在通信线路上的传送有三种方式:1)单工(Simplex)方式:数据只能按一个固定的方向传送。

2)半双工(Half-duplex)方式:数据可以分时在两个方向传输,但是不能同时双向传输。

3)全双工(Full-duplex)方式:数据可以同时在两个方向上传输。

2.波特率和收/发时钟1)波特率所谓波特率,系指单位时间内传送的二进制数据的位数,以位/秒为单位,所以有时也叫数据位率。

它是衡量串行数据传送速度快慢的重要指标和参量。

2)收/发时钟在串行通信中,无论是发送还是接收,都必须有时钟信号对传送的数据进行定位和同步控制。

通常收/发时钟频率与波特率之间有下列关系:收/发时钟频率=n×波特率一般n取1,16,32,64等。

对于异步通信,常采用n=16;对于同步通信,则必须取n=1。

3.误码率和串行通信中的差错控制1)误码率所谓误码率,是指数据经过传输后发生错误的位数(码元数)与总传输位数(总码元数)之比,其与通信线路质量、干扰大小及波特率等因素有关,一般要求误码率达到10-6数量级。

2)差错控制为了减小误码率,一方面要从硬件和软件两个面对通信系统进行可靠性设计,以达到尽量少出错的目的;另一方面就是对传输的信息采用一定的检错、纠错编码技术,以便发现和纠正传输过程中可能出现的差错。

常用的编码技术有:奇偶校验、循环冗余码校验、海明码校验、交叉奇偶校验等。

4.串行通信的基本方式串行通信的基本方式可分为两种:1)异步串行方式:通信的数据流中,字符间异步,字符内部各位间同步。

2)同步串行方式:通信的数据流中,字符间以及字符内部各位间都同步。

单片机串口通信程序

引言:单片机串口通信程序是一种用于实现单片机与外部设备进行数据传输的通信方式。

它通过串口接口将数据以串行的形式传输,实现了高效、可靠的数据交互。

本文将详细介绍单片机串口通信程序的实现原理、步骤和注意事项。

概述:单片机串口通信程序主要包括串口初始化、发送数据、接收数据和中断处理等部分。

其中,串口初始化是设置串口通信的参数,发送数据和接收数据是具体的数据传输操作,中断处理则是处理串口中断事件的相关操作。

正文:一、串口初始化1.确定串口通信的波特率:波特率是指单位时间内传输的比特数,需要根据通信双方的需求确定合适的波特率。

2.设置数据位、停止位和校验位:数据位决定了每个字节中实际有效数据的位数,通常为8位;停止位用于判断一个字节的结束,通常为1位;校验位用于检测和纠正数据传输过程中的错误。

3.打开串口:通过使能相应的寄存器位,开启串口功能。

二、发送数据1.准备要发送的数据:将要发送的数据存储在缓冲区中,可以是一个字节、多个字节或一个字符串。

2.判断发送缓冲区是否为空:检查发送缓冲区是否已被发送完毕,如果为空则可以开始发送新的数据。

3.将数据发送到串口寄存器:将准备好的数据写入串口寄存器,启动数据传输。

4.等待数据发送完毕:通过检查发送完成标志位,判断数据是否已经成功发送完毕。

三、接收数据1.等待接收缓冲区非空:通过检查接收缓冲区是否有新的数据接收到,判断是否可以开始接收数据。

2.读取接收缓冲区的数据:通过读取串口寄存器中的数据,获取已接收到的数据。

3.处理接收到的数据:对接收到的数据进行相应的处理操作,可以是存储、显示或其他操作。

四、中断处理1.使能串口中断:通过设置相应的中断使能标志位,允许串口中断事件的发生。

2.处理接收中断:当接收缓冲区有新的数据到达时,触发串口接收中断,通过中断服务程序对接收到的数据进行处理。

3.处理发送中断:当发送缓冲区为空时,触发串口发送中断,通过中断服务程序发送新的数据。

VHDL详细语法教程

VHDL详细语法教程VHDL(Very High Speed Integrated Circuit HardwareDescription Language)是一种硬件描述语言,用于对数字电路进行描述、建模和仿真。

它是一种用于描述数字系统结构和行为的语言,广泛用于FPGA(Field Programmable Gate Array)和ASIC(ApplicationSpecific Integrated Circuit)设计中。

VHDL语言具有丰富的语法结构,可以描述数字系统的结构和行为,并可以进行仿真和综合。

下面是VHDL语言的详细语法教程:1. 实体声明(Entity Declaration):VHDL代码的第一部分是实体声明,用于定义设计的接口和名称。

实体声明是设计的顶级结构,它包含输入输出端口的定义。

语法格式如下:```vhdlentity entity_name isportport_name : in/out type;port_name : in/out type;...end entity_name;```其中,entity_name为实体名称,port_name为端口名称,type为端口类型,in表示输入端口,out表示输出端口。

2. 结构体声明(Architecture declaration):在实体声明后,需要定义该实体的结构和行为。

这一部分被称为结构体声明。

语法格式如下:```vhdlarchitecture architecture_name of entity_name issignal signal_name : type;...begin...end architecture_name;```3. 信号声明(Signal declaration):信号用于在VHDL代码中传输数据。

通过信号声明,可以定义存储或传输数据的变量。

信号声明需要在结构体声明的前面进行。

语法格式如下:```vhdlsignal signal_name : type;```其中,signal_name为信号名称,type为信号类型。

VHDL串口程序

rx_int: in std_logic --接收数据中断信号,接收数据期间时钟为高电平,传送给串口发送

bps_start:out std_logic; --接收到数据后,波特率时钟启动置位

rx_data: out std_logic_vector(7 downto 0); --接收数据寄存器,保存直至下一个数据来到

rx_int: out std_logic --接收数据中断信号,接收数据期间时钟为高电平,传送给串口发送

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity uart_rx is

port(clk : in std_logic; --系统时钟

rst_n=>rst_n, --复位信号

rs232_tx=>rs232_tx, --RS232发送数据信号

clk_bps=>clk_bps_2, --此时clk_bps的高电平为发送数据的采样点

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity uart is

port(clk : in std_logic; --系统时钟

rst_n: in std_logic; --复位信号

clk_bps=>clk_bps_2,

bps_start=>bps_start_2

);

VHDL串口通信

4 .UART 模块设计UART 异步通信串口协议的VHDL实现包括3个基本模块:时钟分频、接收模块和发送模块,下面逐一介绍其实现方法。

4.2.1 时钟分频模块由于UART是异步传输,没有传输同步时钟。

为了能保证数据传输的正确性,UART采用16倍数据波特率的时钟进行采样。

每个数据有16个时钟采样,取中间的采样值,以保证采样不会滑码或误码。

一般UART一帧的数据位数为8,这样即使每个数据有一个时钟的误差,接收端也能正确地采样到数据。

这里采用常用的数据波特率为9600bps,则所需时钟的频率为16*9600。

系统时钟为50MHz,则分频系数为50000000/(16*9600) =325.52,取整为325。

分频器实现相对简单,这里对其设计流程图不做详细介绍。

只是将设计过程和结果简述如下:首先用VHDL语言进行设计输入,并生成模块文件如图4.3所示,其中clk 为50M系统时钟输入,clkout为325分频后时钟输出。

图4.3 分频模块然后建立波形文件,对以上模块进行时序仿真,仿真结果如图4.4所示,方正结果说明,分频输出实现了对输入的325分频,分频模块设计正确。

图4.4 分频模块仿真结果4.2.2 UART发送模块发送过程:空闲状态,线路处于高电平;当受到发送数据指令后,拉低线路一个数据位的时间T,接着数据按地位到高位依次发送,数据发送完毕后,接着发送停止位(停止位为高电平),一帧数据发送结束。

(1)模块流程图根据以上发送过程,发送模块算法示意图设计如图4.5所示。

图4.5 UART发送数据算法示意图(2)生成模块文件新建一原理图文件,将VHDL 源文件生成对应的模块文件如图4.6所示,其中clk为时钟输入,datain为需要发送的数据输入,wrsig为发送命令输入,idle 为忙闲信号输出,tx为串行数据输出端。

图4.6 UART发送模块(3)波形仿真要对发送模块进行时序仿真必须设计一测试模块,即在每一个clk来时产生一个八位的数据。

VHDL语言程序及其详细注释

Y <=A after TDP when sel = ‘1’ else B after TDP; 延时 赋值 end;实体说明结束

if CLK = ‘1’ then Qi <=‘0’ after TRQ 条件 延时 赋值 elsif CLK’EVENT and CLK= ‘1’ 当时钟信号clk发生改变并且clk=1

then Qi <= D after TCQ; end if; end process;进程结束 end;结构体结束

end;实体说明结束 architecture Behave of DFFClr is实体的结构体名称及其所属关系 signal Qi : BIT;定义信号 begin QB <= not Qi ; Q <= Qi 结构体开始 信号赋值 process (CLR, CLK) begin 定义进程并且开始进程

stages: for i in 7 downto 0 generate 整体布局描述

LowBit: if i = 0 generate 局部布局描述

FA:Full_Adder port map (A(0),B(0),Cin,C(0),Sum(0));

end generate;

otherBits : if i /= 0 generate

STAGES: for i in 7 downto 0 generate 整体布局描述 FF:DFFClr port map (Clr,Clk,D(i),Q(i),open); 局部布局描述

end generate; 循环描述结束 end;结构体结束

VHDL并串转换

VHDL并串转换并串转换⼀、电路功能:本电路能实现FPGA与单⽚机的部分接⼝功能,使单⽚机与FPGA 能进⾏简单通信的功能,即单⽚机通过ale、wr、P0、P2管脚与FPGA 相连接,通过这⼏个控制引脚,指导FPGA进⾏并串转换。

同时,在FPGA上⾃带有clr与clk,实现对系统的清零复位,保证串⾏输出有条进⾏。

⼆、电路设计思路:(1)单⽚机是⼀个拥有多扩展模块的芯⽚,所以,⾸先我们要设计地址总线。

本题中设地址为FAH,当ale来⼀个上升沿时,我们要锁存当前P0⼝的地址,然后再将此地址与FAH⽐较。

若⽐较结果相等,则写有效(把wr赋给FPGA的内部信号wr_en)否则写⽆效(把1赋给wr_en),其中wr_en为0有效。

(2)设计数据总线当选择该芯⽚时,若单⽚机发⼀个写有效来,则将P2和P0⼝的数据读⼊FPGA内部数据锁存器.当数据读⼊后,同时,内部应该产⽣⼀个读⼊完成型号a,以便通知FPGA进⾏并串转换。

(3)并串转换当a有效时,开始进⾏并串转换,并输出串⼝按时钟clk将数据⼀个⼀个输出,当并串转换结束后,应当产⽣⼀个结束控制标志(本电路中将ld反馈回电路做结束标志),使a⽆效,停⽌停⽌并串转换。

三、电路原理框图如下:四、具体程序与原理图:(1)地址锁存器library ieee;use ieee.std_logic_1164.all;entity latch_add isport ( ale,clr:in std_logic;P0:in std_logic_vector(7 downto 0);add:out std_logic_vector(7 downto 0));end latch_add;architecture art of latch_add isbeginprocess(clr,ale)beginif(clr='1') thenadd<="00000000";elsif(ale'event and ale='1') then --锁存地址add<=P0;end if;end process;end art;(2)⽐较器library ieee;use ieee.std_logic_1164.all;entity en isport( wr,clr:in std_logic;add:in std_logic_vector(7 downto 0);wr_en:out std_logic);end en;architecture art of en isbeginprocess(add,wr,clr)beginif (clr='1') thenwr_en<='1';elsif(add="11111010") thenwr_en<=wr; --写允许elsewr_en<='1'; --写禁⽌end if;end process;end art;(3)数据锁存library ieee;use ieee.std_logic_1164.all;entity latch_data isport( wr_en,b,clr:in std_logic;P1,P2:in std_logic_vector(7 downto 0);datain:out std_logic_vector(15 downto 0);a:out std_logic); --a是允许并串转换end latch_data;architecture art of latch_data isbeginprocess(wr_en,clr)beginif(clr='1') thena<='0';elsif(wr_en'event and wr_en='0') then --数据读⼊FPGA datain<=P2&P1; a<='1'; --a为1,开始并串转换end if; if(b='1') then --将ld接⼊b端⼝,为并串结束标志a<='0'; --a为0,结束并串转换end if;end process;end art;(4)并串转换library ieee;use ieee.std_logic_1164.all;entity bing_chuan isport( a,clk,clr: in std_logic;datain1:in std_logic_vector(15 downto 0);ld,s_clk,s_data: out std_logic);end bing_chuan;architecture art of bing_chuan issignal b:std_logic; -- b为产⽣输出同步时钟s_clk的控制信号begin process(a,clk)variable I: integer;beginif(clr='1') thenI:=16;ld<='0';elsif( clk'event and clk='1') thenb<=a;if(a='1') thenif(I=0) thenI:=16; ld<='1';s_data<='0';b<='0';elses_data<=datain1(I-1);I:=I-1;end if;else ld<='0';end if;end if;end process ;s_clk<=clk when b='1' else --b为1,产⽣输出同步时钟'0';end art;五、并串转换原理图:仿真结果:六、结果分析仿真如上图,我们可以看出,当ale来上升沿时,FPGA读⼊P0⼝的地址11111010,此地址与设置地址FAH相同,所以写有效(wr_en<=wr)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

:本模块的功能是验证实现和PC机进行基本的串口通信的功能。需要在PC机上安装一个串口调试工具来验证程序的功能。程序实现了一个收发一帧10个bit(即无奇偶校验位)的串口控制器,10个bit是1位起始位,8个数据位,1个结束位。串口的波特律由程序中定义的div_par参数决定,更改该参数可以实现相应的波特率。程序当前设定的div_par 的值是0x104,对应的波特率是9600。用一个8倍波特率的时钟将发送或接受每一位bit的周期时间划分为8个时隙以使通信同步.程序的工作过程是:串口处于全双工工作状态,按动key2,CPLD向PC发送皐elcome"字符串(串口调试工具设成按ASCII码接受方式);PC可随时向CPLD发送0-F的十六进制数据,CPLD接受后显示在7段数码管上。

SIGNAL state_tras : std_logic_vector(3 DOWNTO 0); 发送状态寄存器

SIGNAL state_rec : std_logic_vector(3 DOWNTO 0); 接受状态寄存器

SIGNAL div8_tras_reg : std_logic_vector(2 DOWNTO 0);该寄存器的计数值对应发送时当前位于的时隙数

SIGNAL div8_rec_reg : std_logic_vector(2 DOWNTO 0); 寄存器的计数值对应接收时当前位于的时隙数

//////////////////////////////////////////////

CONSTANT div_par : std_logic_vector(15 DOWNTO 0) := "0000000100000100";

分频参数,其值由对应的波特率计算而得,按此参数分频的时钟频率是波倍特率的8倍,此处值对应9600的波特率,即分频出的时钟频率是9600*8

ELSE

cnt_delay <= "00000000000000000000";

start_delaycnt <= ’0’;

END IF;

ELSE

IF ((NOT key_input=’1’) AND (cnt_delay = "00000000000000000000")) THEN

div8_rec_reg <= "000";

ELSE IF(clkbaud8x’EVENT AND clkbaud8x = ’1’) THEN

IF (recstart = ’1’) THEN 接收开始标志

div8_rec_reg <= div8_rec_reg + "001";接收开始后,时隙数在8倍波特率的时钟下加1循环

start_delaycnt <= ’1’;

END IF;

END IF;

END IF;

END PROCESS;

PROCESS(clk,rst)

BEGIN

IF (NOT rst = ’1’) THEN

END IF;

END IF;

END IF;

END PROCESS;

PROCESS(clk,rst)

BEGIN

IF (NOT rst = ’1’) THEN

div_reg <= "0000000000000000";

IF (start_delaycnt = ’1’) THEN

IF (cnt_delay /= "11000011010100000000") THEN

cnt_delay <= cnt_delay + "00000000000000000001";

IF (cnt_delay = "11000011010100000000") THEN

IF (NOT key_input = ’1’) THEN

key_entry1 <= ’1’;

END IF;

BEGIN

IF (NOT rst = ’1’) THEN

cnt_delay <= "00000000000000000000";

start_delaycnt <= ’0’;

ELSIF(clk’EVENT AND clk=’1’)THEN

clkbaud8x <= NOT clkbaud8x;

END IF;

END IF;

END PROCESS;

PROCESS(clkbaud8x,rst)

BEGIN

IF (NOT rst = ’1’) THEN

key_entry1 <= ’0’;

ELSIF(clk’EVENT AND clk=’1’)THEN

IF (key_entry2 = ’1’) THEN

key_entry1 <= ’0’;

ELSE

SIGNAL start_delaycnt : std_logic; 开始延时计数标志

SIGNAL key_entry1 : std_logic; 确定有键按下曛?

SIGNAL key_entry2 : std_logic; 确定有键按下标志

SIGNAL send_state : std_logic_vector(2 DOWNTO 0);每次按键给PC发送"Welcome"字符串,这是发送状态寄存器

SIGNAL cnt_delay : std_logic_vector(19 DOWNTO 0);延时去抖计数器

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY UART IS

PORT (

clk : IN std_logic;

SIGNAL txd_xhdl3 : std_logic;

BEGIN

en <="01010101" ;7段数码管使能信号赋值

txd <= txd_xhdl3;

txd_xhdl3 <= txd_reg ;

PROCESS(clk,rst)

rst : IN std_logic;

rxd : IN std_logic; 串行数据接收端

txd : OUT std_logic; 串行数据发送端

SIGNAL rxd_buf : std_logic_vector(7 DOWNTO 0);接受数据缓存

SIGNAL txd_buf : std_logic_vector(7 DOWNTO 0);发送数据缓存

en : OUT std_logic_vector(7 downto 0); 数码管使能

seg_data : OUT std_logic_vector(7 DOWNTO 0); 数码管数据

key_input : IN std_logic 按键输入

SIGNAL rxd_reg1 : std_logic; 接收寄存器1

SIGNAL rxd_reg2 : std_logic; 接收寄存器2,因为接收数据为异步信号,故用两级缓存

SIGNAL txd_reg : std_logic; 发送寄存器

SIGNAL clkbaud_tras : std_logic; 以波特率为频率的发送使能信号

SIGNAL clkbaud_rec : std_logic; 以波特率为频率的接受使能信号

SIGNAL clkbaud8x : std_logic; 以8倍波特率为频率的时钟,它的作用是将发送或接受一个bit的时钟周期分为8个时隙

IF (NOT rst = ’1’) THEN

clkbaud8x <= ’0’;

ELSIF(clk’EVENT AND clk=’1’)THEN

IF (div_reg = div_par - "0000000000000001") THEN

div_reg <= div_reg + "000000000000000

END PROCESS;

PROCESS(clk,rst) 分频得到8倍波特率的时钟

BEGIN

ELSIF(clk’EVENT AND clk=’1’)THEN

IF (div_reg = div_par - "0000000000000001") THEN

div_reg <= "0000000000000000";

ELSE

SIGNAL recstart : std_logic; 开始发送标志

SIGNAL recstart_tmp : std_logic; 开始接受标志

SIGNAL trasstart : std_logic;

);

END UART;

ARCHITECTURE arch OF UART IS

//////////////////inner reg////////////////////

SIGNAL div_reg : std_logic_vector(15 DOWNTO 0);分频计数器,分频值由波特率决定。分频后得到频率8倍波特率的时钟