[CH03]存储器及其组成设计

南邮 微机接口-[CH03]存储器及其组成设计(打印版)

![南邮 微机接口-[CH03]存储器及其组成设计(打印版)](https://img.taocdn.com/s3/m/5553ae05f18583d04964597d.png)

6

微型计算机原理与接口技术

第3章 存储器及其组成设计

3.2 微型计算机系统中的存 储器组织

现代计算机中的存储器处于全机中心地位 对存储器的要求是: 容量大,速度快,成本低 为解决三者之间的矛盾,目前通常采用多级存储器结构,即 使用高速缓冲存储器、主存储器和外存储器。

2012/2/18

25

微型计算机原理与接口技术

3、ROM / EPROM在微机系统中的应用 存放“基本输入/输出系统程序”(简称BIOS) BIOS是计算机最底层的系统管理程序,操作系统和用户程 序均可调用。 4、高速缓冲存储器Cache Cache位于CPU与主存储器之间,由高速静态RAM组成。容 量较小,为提高整机的运行速度而设置,应用程序不能访问 Cache,CPU内部也有Cache。

2012/2/18 13

微型计算机原理与接口技术 三、存储器(芯片)结构与存储原理

1、存储体 一个基本存储电路只能存储一个二进制位。 将基本的存储电路有规则地组织起来,就是存储体。 存储体又有不同的组织形式: 将各个字的同一位组织在一个芯片中,如:8118 16K*1 (DRAM); 将各个字的 4位 组织在一个芯片中,如:2114 1K*4 (SRAM); 将各个字的 8位 组织在一个芯片中, 如:6116 2K*8 (SRAM)。

微型计算机原理与接口技术

第3章 存储器及其组成设计

3.1 概述

存储器处于现代计算机的中心地位

2012/2/18

1

2012/2/18

2

微型计算机原理与接口技术 复习:存储器各个概念之间的关系

微型计算机原理与接口技术 一、计算机系统存储器的主要性能指标

1、存储容量(Memory Capacity) 存储器由若干“存储单元” 组成,每一单元存放一个“ 字节” 的信息 1字节(BYTE)即为8位二进制数; 2字节即为1个“字”(WORD); 4字节即为1个“双字”(DWORD)。 存储容量以K为单位,1K容量为1024个单元 1M = 1024K = 1024×1024单元 1G = 1024M 1T = 1024G

课程设计存储器设计

课程设计存储器设计一、教学目标本课程的学习目标包括:知识目标:学生需要掌握存储器的基本原理、不同类型的存储器及其特点,以及存储器的设计方法和步骤。

技能目标:学生能够运用所学的知识,分析和设计简单的存储器电路,并能够使用相关工具进行仿真和测试。

情感态度价值观目标:通过学习存储器设计,培养学生的创新意识和团队合作精神,提高他们对电子技术的兴趣和热情。

二、教学内容本课程的教学内容主要包括:1.存储器的基本原理:介绍存储器的工作原理、存储单元的结构和存储器的主要性能指标。

2.不同类型的存储器及其特点:讲解随机存储器(RAM)、只读存储器(ROM)、闪存等不同类型存储器的原理和应用。

3.存储器的设计方法和步骤:介绍存储器的设计流程,包括需求分析、逻辑设计、物理设计等步骤。

4.存储器电路的仿真和测试:使用相关工具进行存储器电路的仿真和测试,验证设计的正确性和性能。

三、教学方法本课程的教学方法包括:1.讲授法:通过讲解存储器的基本原理、不同类型的存储器及其特点,以及存储器的设计方法和步骤,传授给学生相关的知识。

2.讨论法:通过小组讨论,引导学生思考和探索存储器设计的难点和问题,培养他们的创新思维和解决问题的能力。

3.案例分析法:通过分析具体的存储器设计案例,让学生了解和掌握存储器设计的实际应用。

4.实验法:通过实验室的实践操作,让学生亲手设计和测试存储器电路,提高他们的实际操作能力和实践能力。

四、教学资源本课程的教学资源包括:1.教材:选用合适的教材,提供全面、系统的存储器设计知识。

2.参考书:提供相关的参考书籍,供学生深入学习和参考。

3.多媒体资料:制作课件、演示文稿等多媒体资料,生动形象地展示存储器的设计原理和过程。

4.实验设备:提供实验室设备和工具,供学生进行存储器电路的设计和测试。

五、教学评估本课程的评估方式包括:1.平时表现:通过课堂参与、提问、小组讨论等环节,评估学生的学习态度和积极性。

2.作业:布置相关的作业,评估学生的理解和应用能力,包括设计存储器电路的练习和报告。

CH03 元件功能说明39-63_简

数值显示此组件会读取所设定地址的值,依照使用者所设定的格式,实时显示出来。

图3-7-1数值显示属性画面此组件会读取所设定地址的值,转换成字符的型式显示出来,因此所读取的值必须是ASCII的显示格式,否则使用者将无法看到所显示的字符。

(字符串长度最长28个字)图3-7-2文数值显示属性画面⏹日期显示此组件会于人机端,显示人机端内部所设定的日期。

亦可选择显示的格式。

图3-7-3日期显示属性画面此组件会于人机端,显示人机端内部所设定的时间。

亦可选择时间显示的格式。

图3-7-4时间显示属性画面⏹星期显示依照所设定的状态,显示星期日到星期一的其中一天。

图3-7-5星期显示属性画面⏹一般型讯息显示设定状态的总数以及各种状态的文字,如此依照所选定地址的值改变,来改变显示其对应的文字。

图3-7-6一般型讯息显示属性画面⏹走马灯讯息显示文字显示会有如走马灯一样的移动跟循环出现,此外还可以设定每次移动点数以及间隔时间,来决定走马灯的显示方式。

图3-7-7走马灯讯息显示属性画面3-8 图形显示状态图显示在人机与PLC 联机使用时,如果您希望由PLC 控制复数个图形显示在人机屏幕的固定位置,并可控制它的状态而能显示不同的图形文件。

图3-8-1状态图显示属性画面以下将对状态图显示功能中所使用之属性加以说明:选择联机中内部存储器或已联机的内存地址,由指定内存地址读取内容。

使用者可依图形库所支持之图形选择丰富画面编辑方法请参考第二章。

使用者依PLC 所提供之数值格式与单位选择如下图。

设定状态图显示之状态总数。

如果数值单位为word,则可以设定1-256个状态;LSB就可以设定16个状态;Bit只能设定2个状态。

设定各状态自动变换模式与变换速度,自动换图选择如下图。

指定内存读地址=Dn,自动变换图形为Variation 时,则自动变换图形控制缓存器Dn+1;当Dn+1 = 0时自动换图= No,Dn+1 > 0时自动换图= Yes。

计算机中存储单元的硬件结构

计算机中存储单元的硬件结构

计算机中存储单元的硬件结构通常由存储器模块、存储器控制器和存储器总线组成。

1. 存储器模块:存储器模块是存储数据的物理部分,包括主存储器(RAM)和辅助存储器(硬盘、SSD等)。

主存储器用

于临时存储正在执行的程序和数据,而辅助存储器则用于永久存储数据和程序,以便在断电后不丢失。

2. 存储器控制器:存储器控制器是负责管理存储器模块的硬件组件,将CPU发送的读写指令转化为存储器操作。

它负责选

择特定的存储单元,并控制存储器进行数据的读取和写入操作。

3. 存储器总线:存储器总线是连接存储器模块和存储器控制器的物理通道,用于传输控制信号和数据。

存储器总线的宽度决定了一次能读写的位数,通常以字节为单位。

总之,存储单元的硬件结构包括存储器模块、存储器控制器和存储器总线,它们协同工作来实现计算机对数据的存储和读写操作。

CH03 元件功能说明1-17_简

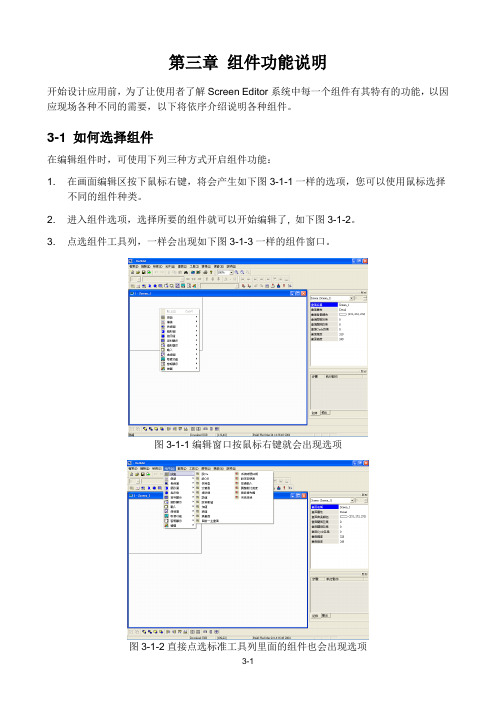

第三章组件功能说明开始设计应用前,为了让使用者了解Screen Editor系统中每一个组件有其特有的功能,以因应现场各种不同的需要,以下将依序介绍说明各种组件。

3-1 如何选择组件在编辑组件时,可使用下列三种方式开启组件功能:1. 在画面编辑区按下鼠标右键,将会产生如下图3-1-1一样的选项,您可以使用鼠标选择不同的组件种类。

2. 进入组件选项,选择所要的组件就可以开始编辑了, 如下图3-1-2。

3. 点选组件工具列,一样会出现如下图3-1-3一样的组件窗口。

图3-1-1编辑窗口按鼠标右键就会出现选项图3-1-2直接点选标准工具列里面的组件也会出现选项图3-1-3直接点选组件工具列使用鼠标左键选择欲使用之组件种类后,再使用鼠标按住左键,拖曳出组件范围即能建立一新组件如下图3-1-4所示。

图3-1-4选好后按住鼠标左键拖曳出范围放开后即可组件建立3-2 按钮组件图3-2-1一般按钮组件功能选项表格3-2-1一般按钮功能触摸此按钮,人机马上送出信号给PLC 相对应之接点ON 或OFF 。

按钮共有四类可选择:一、设ON 按钮;二、设OFF 按钮;三、交替型按钮;四、保持型按钮。

图3-2-2按钮功能组件属性以下将对按钮组件中所使用之属性加以说明:选择联机中内部存储器或已联机的内存地址,将内容写入或读取指定内存地址。

使用者可依软件所提供之组件型式与组件使用前景颜色作选择如下图(Invisible :隐藏式按钮)。

按钮组件型式编辑 ON 、OFF 宏,编辑方法请参考 第四章。

使用者可依Windows 所提供之文字大小、字型与颜色功能,设定该组件文字显示型态。

选择此组件状态是否闪烁,闪烁间隔时间可在设定模块参数的其它选项中设定(闪烁颜色为前景色直接反向)。

使用者可依图形库所支持之图形选择丰富画面,编辑方法请参考第二章。

利用本属性可直接修改组件特性,而不必重新建立组件如下图。

按钮组件特性设ON按钮:按一次该接点设为ON,手放开或再按仍为ON。

集成电路设计基础Ch03

15

华•侨•大•学

• 专用集成电路系统实验室

2. 图案发生器方法

(PG: Pattern Generator)

在PG法中, 规定layout 的基本图形为矩形. 任 何版图都将分解成一 系列各种大小、不同 位置和方向的矩形条 的组合. 每个矩形条用 5个参数进行描述:

(X, Y, A, W, H)

2020/3/30

18

华•侨•大•学

• 专用集成电路系统实验室

4. 电子束扫描法(E-Beam Scanning)

采用电子束对抗蚀剂进行曝光,由 于高速的电子具有较小的波长。分 辨率极高。先进的电子束扫描装置 精度50nm,这意味着电子束的步进 距 离 为 5 0 nm, 轰 击 点 的 大 小 也 为 50nm

三、显影: 晶圆用真空吸盘吸牢,高速旋转, 将显影液喷射到晶圆上。显影后,用清 洁液喷洗。

四、烘干: 将显影液和清洁液全部蒸发掉。

2020/3/30

27

华•侨•大•学

• 专用集成电路系统实验室

3.3.2 曝光方式

1. 接触式曝光方式中,把掩膜以0.05 0.3ATM 的压力压在涂光刻胶的晶圆上, 曝光光源的波长在0.4m左右。

常用OMR83,负片型。

光刻胶对大部分可见光灵敏,对黄光不灵敏,可在黄光下 操作。

再烘晶圆再烘,将溶剂蒸发掉,准备曝光

2020/3/30

24

华•侨•大•学

• 专用集成电路系统实验室Leabharlann 正性胶与负性胶光刻图形的形成

2020/3/30

25

华•侨•大•学

• 专用集成电路系统实验室

涂光刻胶的方法(见下图):

2020/3/30

19

第15讲存储器组成存储器工作原理

第15讲存储器组成存储器工作原理存储器是计算机的重要组成部分,可用于存储数据和程序,并在需要时提供快速的访问和读写。

存储器通常由许多存储单元组成,每个存储单元都能存储一定数量的数据。

本文将介绍存储器的组成以及其工作原理。

存储器通常由两个主要部分组成:存储单元和存储器控制器。

存储单元是存储数据和指令的物理位置,每个存储单元都有一个唯一的地址,用于访问和读写数据。

存储器控制器负责管理存储器的操作,包括读取、写入和复位等。

存储器单元可以分为两种类型:主存储器和辅助存储器。

主存储器是计算机中最快的存储器,通常使用动态随机存储器(DRAM)或静态随机存储器(SRAM)来实现。

主存储器的作用是存储当前正在执行的程序和数据。

辅助存储器则用于长期存储大量的数据和程序,通常使用硬盘驱动器或固态硬盘来实现。

存储器的工作原理基于存储单元的读写操作。

当计算机需要读取存储器中的数据时,存储器控制器根据给定的地址,将存储单元中的数据传输到计算机的寄存器或缓存中。

当计算机需要向存储器写入数据时,存储器控制器将数据从计算机的寄存器或缓存传输到指定的存储单元中。

存储器的读写速度取决于存储器的访问时间,即从发出读写指令到数据可读或可写的时间。

存储器还具有存储器层次结构,用于优化计算机的性能。

存储器层次结构包括寄存器、缓存、主存储器和辅助存储器等多个层次。

寄存器是位于CPU内部的最快的存储器,用于存储当前执行的指令和数据。

缓存是位于CPU和主存储器之间的存储器,用于存储最常访问的数据和指令,以提高访问速度。

主存储器是离CPU最近的存储器,用于存储当前正在执行的程序和数据。

辅助存储器是离CPU最远的存储器,用于长期存储大量的数据和程序。

存储器的访问速度和容量是计算机性能的重要指标。

存储器的访问速度取决于其访问时间,较快的存储器通常具有较短的访问时间。

存储器的容量取决于存储单元的数量和每个存储单元能存储的数据量,较大容量的存储器可以存储更多的数据和程序。

存储器设计课程设计

存储器设计课程设计一、教学目标本课程的教学目标是让学生掌握存储器设计的基本原理和方法,包括存储器的分类、工作原理、性能评价和设计流程。

学生应能够理解并分析不同类型的存储器,如RAM、ROM、Cache等,并掌握存储器层次结构的设计和优化方法。

此外,学生还应具备一定的实验技能,能够进行存储器设计的仿真和测试。

通过本课程的学习,学生应能够将所学的知识和技能应用于实际的存储器设计项目中,提高解决实际问题的能力。

二、教学内容本课程的教学内容主要包括存储器的基本概念、存储器层次结构、存储器设计方法和实验技能。

具体包括:1.存储器的基本概念:介绍存储器的定义、分类和性能指标,如容量、速度、功耗等。

2.存储器层次结构:讲解存储器层次结构的原理和设计方法,包括单级存储器、多级存储器和虚拟存储器。

3.存储器设计方法:详细介绍存储器的设计流程,包括存储单元设计、存储器阵列设计和读写电路设计。

4.实验技能:通过实际操作,使学生掌握存储器设计的仿真和测试方法,提高实验技能。

三、教学方法为了提高学生的学习兴趣和主动性,本课程将采用多种教学方法,如讲授法、讨论法、案例分析法和实验法等。

具体方法如下:1.讲授法:通过教师的讲解,使学生掌握存储器设计的基本原理和方法。

2.讨论法:学生进行小组讨论,引导学生主动思考和探索存储器设计的问题。

3.案例分析法:通过分析实际案例,使学生了解存储器设计的应用场景和挑战。

4.实验法:让学生亲自动手进行存储器设计的仿真和测试,提高实验技能和实际问题解决能力。

四、教学资源为了支持教学内容和教学方法的实施,本课程将准备以下教学资源:1.教材:选用合适的教材,如《存储器设计》等,为学生提供系统的学习材料。

2.参考书:提供相关的参考书籍,如《计算机组成与设计》等,供学生深入学习和参考。

3.多媒体资料:制作课件、视频等多媒体资料,丰富学生的学习体验。

4.实验设备:准备存储器设计的实验设备,如FPGA开发板、仿真器等,为学生提供实际操作的机会。

知识点归纳 计算机硬件中的计算机组成与存储器设计

知识点归纳计算机硬件中的计算机组成与存储器设计计算机硬件中的计算机组成与存储器设计计算机硬件是指构成计算机的物理部分,其中计算机组成和存储器设计是计算机硬件中的两个重要方面。

本文将对计算机组成和存储器设计进行归纳和总结。

一、计算机组成计算机组成指计算机内部各个部件的组织方式以及它们之间的互联关系。

计算机组成主要包括中央处理器(CPU)、主存储器、输入输出设备和总线。

1. 中央处理器(CPU)中央处理器是计算机的核心部件,负责执行指令、控制计算机的操作和处理数据。

CPU由控制器和运算器组成,控制器负责解析和执行指令,运算器负责进行算数和逻辑运算。

2. 主存储器主存储器是计算机中用于存储数据和指令的地方,也叫做内存。

主存储器的容量越大,计算机的性能越好。

主存储器分为随机存取存储器(RAM)和只读存储器(ROM),其中RAM可读可写,ROM只读不可写。

3. 输入输出设备输入输出设备用于与计算机进行信息的输入和输出。

常见的输入设备有键盘、鼠标和扫描仪,输出设备包括显示器、打印机和音响等。

4. 总线总线是计算机内部各个部件之间传输数据和信号的通道。

总线分为地址总线、数据总线和控制总线,地址总线用于传输地址信息,数据总线用于传输数据信息,控制总线用于传输控制信号。

二、存储器设计存储器是计算机中用于存储数据和指令的设备,存储器设计主要包括存储器层次结构和存储器技术。

1. 存储器层次结构存储器层次结构是指计算机中各个级别的存储器按照速度和容量进行划分和组织。

存储器层次结构分为高速缓存、主存储器和辅助存储器三个层次。

高速缓存位于CPU内部,速度最快但容量较小;主存储器是指RAM,速度较快但容量有限;辅助存储器如硬盘和光盘,速度较慢但容量较大。

2. 存储器技术存储器技术指的是用于实现不同层次存储器的具体技术和方法。

常见的存储器技术有随机存取存储器(RAM)、只读存储器(ROM)、动态随机存取存储器(DRAM)和快速动态存取存储器(SDRAM)等。

存储器及其组成设计46页PPT

16、业余生活要有意义,不要越轨。——华盛顿 17、一个人即使已登上顶峰,也仍要自强不息。——罗素·贝克 18、最大的挑战和突破在于用人,而用人最大的突破在于信任人。——马云 19、自己活着,就是为了使别人过得更美好。——雷锋 20、要掌握书,莫被书掌握;要为生而读,莫为读而生。——布尔沃

存储器及其组成设计

41、实际上,我们想要的不是针对犯 罪的法 律,而 是针对 疯狂的 法律。 ——马 克·吐温 42、法律的力量应当跟随着公民,就 像影子 跟随着 身体一 样。— —贝卡 利亚 43、法律和制度必须跟上人类思想进 步。— —杰弗 逊 44、人类受制于法律,法律受制于情 理。— —托·富 勒

ቤተ መጻሕፍቲ ባይዱEND

组成原理课件 - 存储器分析共37页文档

2、要冒一次险!整个生命就是一场冒险。走得最远的人,常是愿意 去做,并愿意去冒险的人。“稳妥”之船,从未能从岸边走远。-戴尔.卡耐基。

梦 境

3、人生就像一杯没有加糖的咖啡,喝起来是苦涩的,回味起来却有 久久不会退去的余香。

组成原理课件 - 存储器分析 4、守业的最好办法就是不断的发展。 5、当爱不能完美,我宁愿选择无悔,不管来生多么美丽,我不愿失 去今生对你的记忆,我不求天长地久的美景,我只要生生世世的轮 回里有你。

谢谢

11、越是没有本领的就越加自命不凡。——邓拓 12、越是无能的人,越喜欢挑剔别人的错儿。——爱尔兰 13、知人者智,自知者明。胜人者有力,自胜者强。——老子 14、意志坚强的人能把世界放在手中像泥块一样任意揉捏。——歌德 15、最具挑战性的挑战莫过于提升自我。——迈克尔·F·斯特利

存储器和阵列结构设计课件

12.2.2 非易失性读写存储器

浮栅晶体管

• 多了一个额外的多晶硅条插在栅和沟道之间,因 而称为浮栅

Floating gate Source

tox tox

Gate Drain

D G

n+

p Substrate

器件截面图

n+_

S

电路符号

存储器和阵列结构设计. 25

• 它的阈值电压是可编程的

[Hirose90]

存储器和阵列结构设计. 8

• 支持3种工作模式:读、写和匹配

I/O Buffers

CAM存储器

Data (64 bits)

Commands

Comparand

Mask

Address Decoder

Control Logic R/W Address (9 bits)

CAM Array 2 words 3 64 bits

• 存储单元和上拉晶体管尺寸的问题 Metal1 • 噪声容限换取性能 Diffusion Metal1 on Diffusion • ACTIVE和CONTACT编程方式的比较

Cell

ROM存储器编程 Polysilicon

注意在布线GND信号时采用了扩散区

存储器和阵列结构设计. 15

• 单元的大部分面积用于位线接触和接地连接 • 解决方案:采用不同的存储器结构

2. 关于位线延时,最坏情况发生在当整个一列除一个单元以外都存放0 并且最下面的晶体管导通时。(忽略上拉晶体管的影响)

tHL = 0.388.7kΩ0.85fF5112=0.73s

tLH = 0.69(31kΩ/0.0077)(5110.85fF) = 1.2s

存储器设计PPT课件

D0~D7

加载地址 信号

tRC

加载片选 信号

OE低电平有 效,WE为高电平

7

第7页/共68页

SRAM 写入时序

A0~A12 CS1 CS2 WE

D0~D7

加载地址 信号 tWC

片选信号 有效

数据加载到总线, WE为低电平

8

第8页/共68页

SRAM的VHDL程序实现

• 端口定义

PORT(address : IN STD_LOGIC_VECTOR(3 DOWNTO 0); cs , oe , we: IN STD_LOGIC; data : INOUT STD_LOGIC_VECTOR(7 DOWNTO 0));

第42页/共68页

存储器设计总结

• 存储单元初始化(外部文件读取) ➢自定义数据格式文件 ➢.COE文件

第43页/共68页

自定义数据格式文件

• VHDL文本输入输出包集合(TEXTIO) • VHDL语言对文件格式不作任何限制。 • TEXTIO按行进行处理,一行为一个字符串,以回车、换行符作

为行结束符。

的整数序列,相加得到 校验码。

第51页/共68页

CRC原理

将待发送的位串看成系数为 0 或 1 的多项式;

收发双方约定一个生成多项式 G(x)(其最高阶 和最低阶系数必须为1)。 发送方用位串及 G(x)进行某种运算得到校验和, 并在帧的末尾加上校验和,使带校验和的帧的多 项式能被 G(x) 整除。 接收方收到后,用 G(x) 除多项式,若有余数, 则传输有错。

第15页/共68页

通用ROM的VHDL设计

• 设计一个容量为256*8bit的ROM • 8位地址线Addr[7..0] • 8位数据输出线Dout[7…0] • 使能信号线OE

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

微型计算机原理与接口技术

地址空间分配表

地址 片号 1 2 3 4 选片 A15 A14 00 00 01 01 10 10 11 11 片内 A13 A12 ……..A1 A0 00,0000,0000,0000 11,1111,1111,1111 00,0000,0000,0000 11,1111,1111,1111 00,0000,0000,0000 11,1111,1111,1111 00,0000,0000,0000 11,1111,1111,1111 总地址 0000 3FFF 4000 7FFF 8000 BFFF C000 FFFF 说明 最低地址 最高地址 最低地址 最高地址 最低地址 最高地址 最低地址 最高地址

2012/10/7

19

2012/10/7

20

5

微型计算机原理与接口技术 四、存储器的读写操作

系统为每个存储单元安排一个地址。地址为二进制数,习 惯上写成16进制的形式,由CPU通过地址总线送到存储器地址 译码器的输入。 1、存储器容量由地址线“宽度”决定 1M容量的存储器 地址范围:00000H~FFFFFH,地址线为20根; 16M容量的存储器 地址范围:000000H~FFFFFFH,地址线为24根; 4G容量的存储器 地址范围:0000,0000H~FFFF,FFFFH,地址线为32根。

2012/10/7

25

2012/10/7

26

微型计算机原理与接口技术

存储器的用途和特点 名称 高速缓冲存 储器 主存储器 外存储器 特点 存储速度快,但 Cache 高速存取指令和数据 存储容量小 存放计算机运行期间 存取速度较快, 主存 大量的程序和数据 存储容量较大 存放系统程序及各种 容量大,单位成 外存 应用程序、数据 本低,速度慢 简称 用途

微型计算机原理与接口技术

位扩展法

南京邮电大学计算机学院 倪晓军

2012/10/7

29

2012/10/7

30

微型计算机原理与接口技术

字扩展法 例如:用16K8位的芯片组成64K8位的存储器需4个芯片 地址线 —— 共需16根 片内:14根(214 = 16384),选片:2根 数据线 —— 8根 控制线 —— CPU和存储器的读写线同名对接

24

6

微型计算机原理与接口技术

第3章 存储器及其组成设计

现代计算机中的存储器处于全机中心地位 对存储器的要求是: 容量大,速度快,成本低 为解决三者之间的矛盾,目前通常采用多级存储器结构,即 使用高速缓冲存储器、主存储器和外存储器。

3.2 微型计算机系统中的存 储器组织

南京邮电大学计算机学院 倪晓军

2012/10/7 13

微型计算机原理与接口技术 三、存储器(芯片)结构与存储原理

1、存储体 一个基本存储电路只能存储一个二进制位。 将基本的存储电路有规则地组织起来,就是存储体。 存储体又有不同的组织形式: 将各个字的同一位组织在一个芯片中,如:8118 16K*1 (DRAM); 将各个字的 4位 组织在一个芯片中,如:2114 1K*4 (SRAM); 将各个字的 8位 组织在一个芯片中, 如:6116 2K*8 (SRAM)。

存储元 存储单元

2012/10/7

3

2012/10/7

4

1

微型计算机原理与接口技术

2、存取时间(Memory Access Time); 3、存储周期(Memory Cycle Time); 4、可靠性(Reliability); 5、功耗与集成度(Power Loss and Integration Level); 6、性能价格比(Cost Performance); 7、存取宽度(Access Width)。

2012/10/7 17 2012/10/7 18

微型计算机原理与接口技术

微型计算机原理与接口技术

(4) 片选 只有当存储器芯片的片选信号有效时,才表示此时地址线 上的地址对本芯片是有效的。

(5) 输出驱动电路 为了扩展存储器的容量,常需要将几个芯片的数据线并联 使用;另外存储器的读出数据或写入数据都放在双向的数据 总线上。这就用到三态输出缓冲器。

2012/10/7

31

2012/10/7

32

8

微型计算机原理与接口技术

微型计算机原理与接口技术

字位同时扩展法 用1k 4 的存储器芯片 2114 组成 2k 8 的存储器

南京邮电大学计算机学院 倪晓军

2012/10/7

33

2012/10/7

34

微型计算机原理与接口技术

例: 有若干片1K×8位的SRAM芯片,采用字扩展方法构成 4KB存储器,问: (1) 需要多少片RAM芯片? (2) 该存储器需要多少地址位? (3) 画出该存储器与CPU连接的结构图,设CPU的接口信号有 地址信号、数据信号、控制信号MREQ和R/W#。 (4) 给出地址译码器的逻辑表达式。

微型计算机原理与接口技术

解:(1) 需要4K/1K = 4片SRAM芯片; (2) 存储器容量4KB,需要12条地址线; (3) 译码器的输出信号逻辑表达式为:

微型计算机原理与接口技术

3、ROM / EPROM在微机系统中的应用 存放“基本输入/输出系统程序”(简称BIOS) BIOS是计算机最底层的系统管理程序,操作系统和用户程 序均可调用。 4、高速缓冲存储器Cache Cache位于CPU与主存储器之间,由高速静态RAM组成。容 量较小,为提高整机的运行速度而设置,应用程序不能访问 Cache,CPU内部也有Cache。

微型计算机原理与接口技术

1、存储器的基本组织:由多个存储器芯片组成一个实际存储器,并与CPU连接 (1) 与CPU的连接 主要是 地址线、控制线、数据线 的连接。 (2) 多个芯片连接 设计的存储器容量与实际提供的存储器多有不符。实际使 用时,需进行字和位扩展(多个芯片连接),组成所需要的实 际的存储器容量:

微型计算机原理与接口技术

闪速存储器的工作原理 电擦除和重新编程能力 闪速存储器是在EPROM功能基础上增加了电路的电擦除 和重新编程能力。28F256A引入一个指令寄存器来实现这种功 能。其作用是: (1) 保证TTL电平的控制信号输入; (2) 在擦除和编程过程中稳定供电; (3) 最大限度的与EPROM兼容。

2012/10/7 21

微型计算机原理与接口技术

2、存储器读写示意 例:容量为8KB(213B)的存储器地址范围:0000H~1FFFH, 地址线为13根。

南京邮电大学计算机学院 倪晓军

2012/10/7

22

微型计算机原理与接口技术

读存储器过程 ① ② ④

微型计算机原理与接口技术

写存储器过程 ① ② ④ ①

2012/10/7

11

2012/10/7

12

3

微型计算机原理与接口技术

6、高速存储器 由于CPU和主存储器在速度上不匹配,限制了高速计算。 为了使CPU不至因为等待存储器读写操作的完成而空转,可 以采取一些加速CPU和存储器之间有效传输的特殊措施。 (1) 芯片技术 研究开发高性能芯片技术,如: DRAMFPMDEDO EDRAMCDRAMSDRAMRambusDRAM。 (2) 结构技术 采用并行操作方式 双端口存储器 采用并行主存储器,提高读出并行性 多模块交叉存储器 主存储器采用更高速的技术来缩短存储器的读出时间 相联存储

南京邮电大学计算机学院 倪晓军

2012/10/7

9

2012/10/7

10

微型计算机原理与接口技术

5、闪速存储器 什么是闪速存储器? Flash Memory 闪速存储器是一种高密度、非易失性的读/写半导体存储 器,它突破了传统的存储器体系,改善了现有存储器的特性。 特点: (1) 固有的非易失性; (2) 廉价的高密度; (3) 可直接执行; (4) 固态性能。

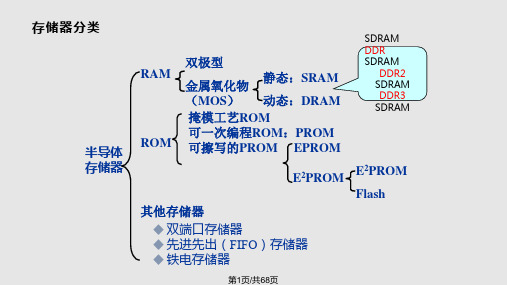

微型计算机原理与接口技术 二、存储器分类:

1、 按存储介质分 半导体存储器:用半导体器件组成的存储器; 磁表面存储器:用磁性材料做成的存储器; 2、 按存储器的读写功能分 只读存储器(ROM):存储的内容是固定不变的、只能读 出而不能写入的半导体存储器; 随机读写存储器(RAM):既能读出又能写入的半导体存 储器; 3、 按在计算机系统中的作用分 根据存储器在计算机系统中所起的作用,可分为: 主存、辅存、高速缓冲存储器、 控制存储器等。

(1) 地址译码 单译码方式——适用于小容量存储器中,只有一个地址译码器

2012/10/7

15

2012/10/7

16

4

微型计算机原理与接口技术

双译码方式——地址译码器分成两个,可减少选择线的数目 例:1024 * 1 的存储器

微型计算机原理与接口技术

南京邮电大学计算机学院 倪晓军

(2) 驱动器 双译码结构中,在译码器输出后加驱动器,驱动挂在各 条X方向选择线上的所有存储元电路; (3) I/O电路 处于数据总线和被选用的单元之间, 控制被选中的单元 读出或写入,放大信息。

微型计算机原理与接口技术

第3章 存储器及其组成设计

存储器处于现代计算机的中心地位

3.1 概述

南京邮电大学计算机学院 倪晓军

2012/10/7

1

2012/10/7

2

微型计算机原理与接口技术 复习:存储器各个概念之间的关系

微型计算机原理与接口技术 一、计算机系统存储器的主要性能指标

1、存储容量(Memory Capacity) 存储器由若干“存储单元”组成,每一单元存放一个“字 节”的信息 1字节(BYTE)即为8位二进制数; 2字节即为1个“字”(WORD); 4字节即为1个“双字”(DWORD)。 存储容量以K为单位,1K容量为1024个单元 1M = 1024K = 1024×1024单元 1G = 1024M 1T = 1024G