一种VLSI高层综合低功耗设计方案及实现

集成电路设计基础第11章数字集成vlsi系统设计基础

通过对时序逻辑电路的输入、输出及状态进行分析,了解其工作原理和特性。

时序逻辑电路设计

根据实际需求,选用合适的触发器和组合逻辑电路,设计出满足特定功能的时序逻辑电路。同时 需要考虑时序问题,确保电路的正确性和稳定性。

03

数字集成VLSI系统关键技术

高性能计算技术

并行处理技术

通过多核处理器、GPU加速等技术提高计算能力。

逻辑综合

将HDL代码转换为门级网表,优化电路性能并降低功 耗。

布局布线

根据电路需求和工艺要求,将门级网映射到具体的 芯片上,实现电路的物理实现。

时序分析

对布局布线后的电路进行时序分析,确保电路时序的 正确性和性能。

仿真验证与测试方法

前仿真

在电路设计阶段进行仿真验证, 检查电路功能和性能是否符合设 计要求。

THANKS

感谢观看

集成电路设计基础第11章数 字集成vlsi系统设计基础

• 数字集成VLSI系统概述 • 数字集成VLSI系统基本原理 • 数字集成VLSI系统关键技术 • 数字集成VLSI系统实现方法

• 数字集成VLSI系统应用实例 • 数字集成VLSI系统前沿研究动态

01

数字集成VLSI系统概述

定义与发展历程

柔性电子在数字集成VLSI中潜在价值

柔性电子器件

利用柔性基底和可弯曲的电 子材料制造柔性电子器件, 实现可穿戴、可折叠的数字

集成VLSI系统。

生物兼容性

柔性电子具有良好的生物兼 容性,可用于生物医学应用 中与人体紧密接触的电子设

备。

轻量化与便携性

柔性电子器件具有轻量化、 薄型化和可弯曲的特点,便 于携带和集成到各种移动设 备中。

应用领域及市场需求

VLSI技术的基本原理与设计方法

VLSI技术的基本原理与设计方法随着科技的迅猛发展,各种电子产品在我们生活中占据着越来越重要的地位。

而所有这些电子产品都离不开一个重要的技术:VLSI技术。

VLSI指的是非常大规模集成电路技术,是目前集成电路技术的一种基本形式。

本文将对VLSI技术的基本原理和设计方法做一个简要的介绍。

一、VLSI技术的基本原理VLSI技术是基于微电子技术的一种重要形式。

它主要是将各种电子元器件(芯片、集成电路、电阻、传感器等)集成在一个小小的芯片上。

具体实现中,VLSI技术主要遵循以下三个原理:1. MOSFET(金属氧化物半导体场效应晶体管)原理当VLSI集成电路中的MOSFET晶体管导通时,电子会在它们的通道中游走。

而当晶体管截止时,电子在通道中的移动会停止。

MOSFET晶体管是VLSI集成电路的核心,它能够完成各种逻辑功能,包括与门、或门、非门等。

2. CMOS(互补金属氧化物半导体)原理CMOS原理是一种优秀的低功耗技术,其基本思想是利用PMOS(钨氧化物半导体)和NMOS(有机金属半导体)晶体管的互补特性来实现电路的全量化。

VLSI集成电路中使用CMOS电路可以实现高效和低功耗的目的。

3. 精细化工艺原理精细化工艺是指通过提高制造VLSI集成电路的工艺过程的精度和准确性,从而实现制造更加复杂的电路。

当VLSI集成电路的工艺精度和准确性越高时,芯片上的电子元器件数量就越多,电路的密度和速度也能够得到更大的提升。

二、VLSI技术的设计方法VLSI技术的设计方法是制造VLSI集成电路的重要步骤之一。

它主要包括以下几个方面:1. 电路设计VLSI集成电路的电路设计是指从电路原理图开始设计电路与芯片。

其中,电路的设计需要考虑到电路特性、电路定位、功能需求和功耗等。

当电路设计完成后,可以使用电磁仿真软件对其进行仿真,以确保电路的正常运转。

2. 物理设计物理设计是指将电路转化为动态的、几何的物理结构,这能够确保电路的顺利布局。

基于数据可重用的运动估计低功耗VLSI实现

A src: l k ae lsac l kma h(S M i te et oi s m t nagrh , u t uecm ua o bta t Bo sdf l erhbo t F B )s h s m t net a o l i m b th hg o p tt n cb u c c b o i i ot e i

的 视 频 压 缩 标 准 MP G V 第 l E 4A C 0部 分 以 及 H. 2 4H.6 6 / 2 L在 内 块 匹 配 运 动 估 计 算 法 一 直 是 视

收 稿 日期 :0 5 O — 5 2 o 一 4 1

算 量 , 们 提 出 了许 多 快 速 搜 索 算 法 , 括 三 步 人 包 法 f 新 三 步 法1、 】 1 、 2 四步 法 【 l 3 J 是 这些 算 法 都 是 通 。但 过 减 少 搜 索 的 向量 数 目来 实 现 对 计 算 量 的减 少 。

p we o s mp i n C nr n e t h sc n i o , u h rb n sfr a d a d a c d sr c u e S me n w a g rt msa e o rc n u t . o f td wi t i o d t n a t o r g o w r n a v n e t t r . o e o h r o o h i i u l i a o td i cu e hg aa r u e a d lw p w rtc n lg . S h e r h t cu e a he e 0 p w ro n 0 d pe n l d ih d t e s n o o e e h oo y o t e n w ac i t r c iv s 5 % o e f a d 1 % e 0 o hp r s u c s g a wh l s u e o e ur d I u e n moy n c i e o re u a e me n i a s r s lw r q i / n mb ra d me r . e e O

低功耗电路设计中的VLSI技术及应用

低功耗电路设计中的VLSI技术及应用随着科技的不断进步,电子设备越来越普及,而低功耗设计就越发成为电路设计中的热点话题。

在众多低功耗电路设计中,VLSI技术具有其独特的优势,也成为低功耗电路设计的重点研究方向。

一、 VLSI技术简介VLSI即Very Large Scale Integration(超大规模集成电路)技术,它是指在单片半导体芯片上集成数亿个(至少包括几十万个至上百万个)晶体管和其它电子元器件,用来实现各种功能的技术。

VLSI技术在现代电路设计中扮演着至关重要的角色,它的应用不仅能够大大提高电路性能,还能减少芯片的功率消耗,进而实现低功耗电路的设计。

二、低功耗设计的重要性低功耗设计是现代电路设计中不可或缺的一部分。

随着移动设备,可穿戴设备等电子产品的不断涌现,低功耗电路将更加重要。

低功耗电路设计对于电子设备的使用寿命、效率、成本等方面都有极大的影响。

当电子设备在待机状态下,电路应能够在最小功耗的前提下,仍然能够快速唤醒;当处于工作状态时,芯片也应尽量保持低功耗状态。

而VLSI技术正是为实现低功耗电路提供了可靠的技术支持。

三、VLSI技术在低功耗电路设计中的应用1. 通用体积缩小技术在现代电路设计中,体积缩小已成为一种大势所趋。

VLSI技术可以通过缩小器件等方式,实现芯片体积的缩小。

这样做可以带来许多好处,如更加轻便的设备,更方便的携带与使用等。

缩小器件的工艺流程,可以进一步改善芯片材料及结构,使得芯片的功耗降低。

2. 针对特殊应用的设计设计专门针对特定应用领域的芯片也是VLSI技术的一个优势。

例如,深度学习等领域需要大量的计算资源。

针对这种需求,VLSI芯片可以在保证计算能力的前提下,使芯片功耗降低,达到低功耗的效果。

3. 低功耗模式的设计在电子产品使用过程中,待机状态下芯片应能够在最小功耗的前提下,仍然能够快速唤醒。

同时,当处于工作状态时,芯片也应尽量保持低功耗状态。

这就需要在设计电路时,针对特定功能需求,实现低功耗模式的设计。

微电子技术中的超大规模集成电路设计方法

微电子技术中的超大规模集成电路设计方法超大规模集成电路(VLSI)是指具有上百万个晶体管的集成电路。

在微电子技术领域,VLSI设计方法是实现高集成度和高性能的关键因素之一。

本文将介绍一些常用的VLSI设计方法,包括物理设计和逻辑设计。

VLSI的物理设计是将电路设计转化为实际器件的布局和布线。

其中,关键路径优化是物理设计的关键问题之一。

通常,对于高速电路,关键路径上的时延应该尽可能小。

为了达到这个目标,设计工程师可以采用多种技术。

例如,层次布局和多管道化布局可以减少布局中的电气延迟。

另外,时钟树设计也是关键路径优化的一部分。

通过合理的时钟树设计,可以减少时钟信号的延迟和抖动,从而提高电路的工作频率。

此外,VLSI的物理设计还需要考虑功耗优化。

通过采用低功耗器件和电源网络优化技术,可以降低功耗,延长电池寿命。

逻辑设计是将电路功能转化为逻辑元件和电路连接的过程。

在逻辑设计中,设计工程师需要使用硬件描述语言(HDL)来描述电路功能。

常用的HDL包括VHDL和Verilog。

使用HDL,设计工程师可以将电路设计分解为更小的逻辑电路模块,然后将这些模块通过逻辑门、寄存器和触发器等元件进行连接。

在逻辑设计中,设计工程师还需要考虑电路的延迟、功耗和面积等指标。

因此,设计工程师常常需要权衡不同的电路结构和技术参数来优化整个电路的性能。

在VLSI设计过程中,验证是一个非常重要的步骤。

验证是通过仿真、验证和测试来验证电路设计的正确性和可行性。

在仿真过程中,设计工程师可以使用电路仿真工具来验证电路功能的正确性。

通过检查电路输出是否与预期输出一致,设计工程师可以发现并修复电路设计中的错误。

此外,验证还包括对电路的可靠性和容错性进行测试。

通过使用电路测试设备和技术,设计工程师可以检测电路的性能和可靠性,并确保电路在不同工作条件下都能正常工作。

除了物理设计、逻辑设计和验证,VLSI设计还涉及到一些其他的问题。

例如,VLSI设计中的数据通信和互连问题是一个关键的挑战。

VLSI论文:大规模集成电路设计中的低功耗高层次综合算法研究

VLSI论文:大规模集成电路设计中的低功耗高层次综合算法研究【中文摘要】大规模集成电路(Very Large Scale Integrated circuit, VLSI)是计算机科学和电子科学的基础和载体。

当前,大规模集成电路的半导体制程已经进入32nm工艺,芯片内部集成的运算单元数目在不断增长。

随着大规模集成电路的工艺进步及功能、结构的日趋复杂,对于集成电路计算机辅助设计(Computer Aided Design)的要求也越来越高。

而电路CAD技术的核心在于各种自动综合和规划布线算法。

高层次综合是进行电路功能模块设计和行为描述的重要步骤,是进行芯片进行物理设计的第一步。

高层次综合的主要在于为电路中的各种操作分配硬件功能单元,实现各种操作的时间调度、功能单元共享和绑定。

高层次综合接受系统行为描述,通过一定的算法,将其转换成由功能单元、存储单元、选择器件等组成电路结构。

再经过寄存器转移级别转换、区域划分、布图、布线等步骤得到整个电路的完整物理版图。

当前工业界高层次综合算法大都是基于元件库里相对于每一种操作只有一种功能单元来实现的情况,并在此基础上为所有需要执行的操作分配功能单元,实现调度和互连。

考虑到每种功能单元在晶体管电路级别上可以有多种不同的实现方式,而...【英文摘要】Very Large Scale Integrated circuit (VLSI) design is very important to modern industry. Currently, the manufacture standard of semiconductor device has move into 32nmera. As the advance of circuit technology, the requirement for Electronic Design Automation (EDA) tools is increasing too. The core part of any EDA tool lies in the algorithm.High Level Synthesis (HLS) is a critical procedure following the behavior description of the circuit function. It is the first step of doing physical design of a chip...【关键词】VLSI 高层次综合调度退火算法力导向算法【英文关键词】VLSI High Level Synthesis Scheduling Simulated Annealing Force Directed Scheduling【目录】大规模集成电路设计中的低功耗高层次综合算法研究摘要4-5Abstract5第1章绪论8-19 1.1 论文的研究背景8-15 1.1.1 大规模集成电路(VLSI)和计算机辅助设计(CAD)8-13 1.1.2 大规模集成电路设计中的高层次综合13-15 1.2 国内外研究现状15-18 1.3 论文工作的主要目的和意义18 1.4 论文的主要工作内容18-19第2章大规模集成电路设计中的低功耗高层次综合问题19-29 2.1 VLSI设计中高层次综合的基础算法19-24 2.1.1 ASAP算法和ALAP算法20-22 2.1.2 力导向算法22 2.1.3 随机算法22-23 2.1.4 其他算法23-24 2.2 VLSI设计中低功耗高层次综合问题24-28 2.2.1 VLSI的功耗分析24-25 2.2.2 VLSI设计中的低功耗高层次综合问题25-28 2.3 本章小结28-29第3章大规模集成电路设计中的单一功能单元高层次综合退火算法29-42 3.1 VLSI设计中单一功能单元高层次综合退火算法的基础29-31 3.2 VLSI设计中的单一功能单元高层次综合退火算法31-37 3.2.1 初始状态选择31-34 3.2.2 状态转移函数34 3.2.3 成本估计函数34-35 3.2.4 降温函数的选择35 3.2.5 功能单元参数设定35-37 3.3 VLSI设计中单一功能单元高层次综合退火算法实现与对比37-40 3.3.1 单一功能单元低功耗高层次综合退火算法的实现37-39 3.3.2 单一功能单元低功耗高层次综合退火算法的对比39-40 3.4 本章小结40-42第4章大规模集成电路设计中的多功能单元高层次综合退火算法42-51 4.1 面向VLSI设计中低功耗高层次综合的模拟退火算法改进42-44 4.2 VLSI设计中低功耗高层次综合的超前预估44-45 4.3 VLSI设计中低功耗高层次综合的功能单元参数设定45-50 4.4 本章小结50-51第5章大规模集成电路设计中的低功耗高层次综合的力导向算法51-57 5.1 VLSI设计中高层次综合的基本力导向算法51-54 5.2 VLSI设计中的低功耗高层次综合的力导向算法54-55 5.3 本章小结55-57第6章大规模集成电路设计中的低功耗高层次综合算法的对比57-65 6.1 单一功能退火算法与多功能单元退火算法的对比57-61 6.2 多功能单元退火算法结果与力导向算法的对比61-64 6.3 本章小结64-65第7章全文总结与展望65-66致谢66-67参考文献67-71攻读硕士学位其间所发表的论文71。

VLSI论文:温度驱动的三维芯片低功耗设计方法研究

VLSI论文:温度驱动的三维芯片低功耗设计方法研究【中文摘要】日益增长的便携式电子产品对低功耗有着迫切需求,同时国家节能减排政策的提出以及低碳环保观念的深入人心,使得超大规模集成电路(VLSI)低功耗设计变得越来越重要。

功耗问题已经成为VLSI设计所必须考虑的一个关键问题。

为了进一步降低互连延迟,提高芯片性能,在芯片设计与制造工艺中,出现了“三维芯片”。

三维芯片能够明显的提高芯片的性能,三维芯片结构面临的最大的问题是散热问题。

本文在研究VLSI设计流程及各个阶段的低功耗技术的基础上提出了一种适用于三维芯片的低功耗技术。

首先,本文分析了芯片的功耗来源,并介绍VLSI设计中在不同层次使用的低功耗技术,然后对不同的低功耗技术的效果进行对比。

其次,介绍了Synopsys的Liberty库及从Liberty中提取功耗数据。

然后介绍三维芯片的热阻抗模型,并使用这种模型来计算三维芯片各个模块的温度。

实验结果表明,随着三维芯片层数的增加,三维芯片的温度急剧增加,可以增加到几千度,远远超出芯片可以承受的温度。

最后,提出了适用于三维芯片的电压岛低功耗技术。

我们使用ILP算法生成电压岛,并在生成电压岛时考虑芯片的温度。

实验结果表明我们的算法能够明显降低三维芯片...【英文摘要】The increasing market of mobile product has urgent requirement in low power. The proposing energy saving and environmentally friendly national policy and low carbonconcept deeply rooting among peoples, the VLSI low power design is becoming increasingly important. Minimization of power consumption is the key technique in modern VLSI design. In order to further reduce the interconnect delay and improve the performance, in the design and manufacturing process chip, Three-dimensional Integrated Circuits(3D IC...【关键词】VLSI 低功耗三维芯片多电压电压岛【英文关键词】VLSI Low Power Three-dimensional Integrated Circuits (3D ICs) MSV Voltage Islands【目录】温度驱动的三维芯片低功耗设计方法研究摘要4-5Abstract5第1章绪论8-15 1.1 VLSI技术的发展8-9 1.2 VLSI设计的流程9-11 1.3 研究背景以及问题的提出11-14 1.4 本文主要工作与组织结构14-15第2章三维芯片与低功耗技术概述15-23 2.1 三维芯片简介15-16 2.2 低功耗技术简介16-21 2.2.1 功耗的组成16-17 2.2.2 低功耗技术17-21 2.3 热问题的解决方案21-23 2.3.1 热通孔21 2.3.2 电压岛21-22 2.3.3 动态热量管理22-23第3章温度模型23-37 3.1 从Synopsys CCS Power模型中提取功耗23-31 3.1.1 Synopsys CCS Liberty简介23-25 3.1.2 从Liberty库中提取数据25-27 3.1.3 Synopsys CCS Power简介27-28 3.1.4 CCS库模型28-31 3.2 温度模型31-34 3.2.1 热传导方程31-32 3.2.2 有限差分方法(Finite Difference Method,FDM)32 3.2.3 有限元分析(Finite Element Analysis,FEA)32 3.2.4 热阻抗模型(Resistive Thermal Model)32-34 3.3 结果分析34-37 3.3.1 从Liberty中提取数据34-35 3.3.2 温度模型35-37第4章温度驱动的三维芯片电压岛ILP算法37-49 4.1 研究背景37-40 4.1.1 多电压技术37-38 4.1.2 电压岛38-40 4.2 线性规划问题及求解40-41 4.2.1 线性规划40 4.2.2 线性规划求解工具GLPK40-41 4.3 温度驱动的三维芯片电压岛ILP算法41-47 4.3.1 问题描述41-46 4.3.2 基于ILP算法的功耗模型46-47 4.3.3 基于ILP算法的温度模型47 4.4 实验结果47-49第5章总结与展望49-50参考文献50-52致谢52-53攻读硕士学位期间发表的论文与参与的项目53。

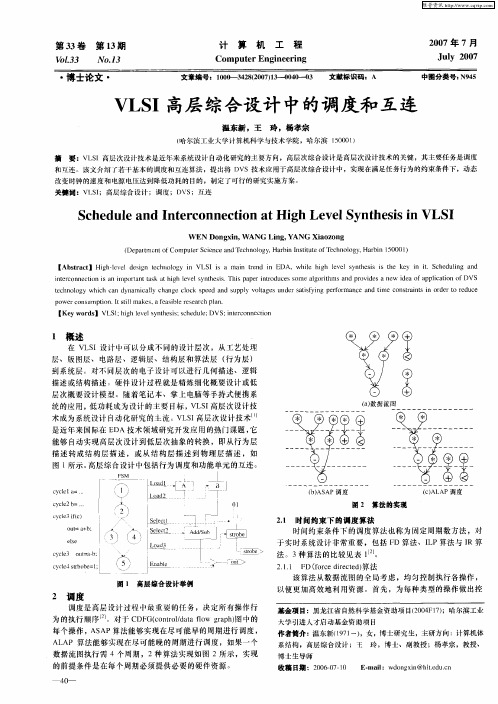

VLSI高层综合设计中的调度和互连

[ src] Hihlv ld s n t h oo y i S sa man t n n E A,whl hg ee snh s ste ky i i ce uig a d Abta t g — e ei e n lg n VL Ii i r d i D e g c e i ih l l y tei i h e n t h d l n e v s S n

[ yw r s Ke o d ]VL 1hg v ly tei;ce ue D ;nec n et n S; ihl e snh s sh d l; VS itro nci e s o

1 概述

在 V S L I设计 中可 以分成不同的设计层次 ,从工艺处理 层 、 版 图 层 、 电路 层 、 逻 辑 层 、 结 构 层 和 算 法 层 ( 为 层 ) 行 到系统层 。对不同层次的电子 没计可 以进行几何描述、逻辑 描述 或结构描述。硬件设计过程就是精炼细化概要设计或低 层次概要设计模型。随着 笔记 本、掌上 电脑等手持式便携 系 统 的应用 , 低功耗成为设计 的主要 目标 , L I V S 高层次设计技 术成为系统设计 自动化研究 的主流。V S 高层次设 计技术… LI

是近 年 来 国际 在 E DA技 术 领 域 研 究 开 发应 用 的热 门课 题 , 它

f) a 数据 流图

詈

善

能够 自动实现高层次没 计到低层 次抽象 的转换 ,即从行为层

低功耗设计方法范文

低功耗设计方法范文低功耗设计方法是指在电子产品设计过程中,通过合理的电路设计和软件优化,实现产品在正常工作状态下的电力消耗最小化。

低功耗设计方法对于节省能源、延长电池寿命、减少产品发热和环境保护等方面都具有重要意义。

以下是几种低功耗设计方法:1.选择低功耗组件:在电子产品设计中,选择低功耗的关键元件是降低功耗的一个有效方法。

例如,选择低功耗的微处理器、传感器和发射接收模块等元件,可以降低整个系统的功耗。

2.优化电源管理电路:电源管理电路对于整个系统的功耗非常重要。

通过采用高效的降压电源方案,可以减少能量损耗;通过设计适合产品需要的睡眠模式和待机模式,可以降低系统在闲置状态下的功耗。

3.优化电路布局和走线:合理的电路布局和走线可以减少电路的阻抗,降低功耗。

例如,减少电路的长度和厚度,降低走线的阻抗和电流损耗。

此外,通过使用最短路径和最小电容的连接方式,可以进一步降低功耗。

4.优化软件算法:软件优化是低功耗设计的关键。

通过优化算法,减少不必要的运算和数据存储,可以降低CPU的功耗。

此外,合理使用休眠和唤醒机制,以及调整任务优先级,都可以有效地降低系统功耗。

5.采用功耗管理策略:在设计时加入功耗管理功能,如动态频率调整、智能功耗调整等策略,可以根据系统负载和需求实时调整系统电压和频率,以达到最佳功耗效果。

6.使用节能模式:在电子产品设计中,引入特定的节能模式可以降低系统功耗。

例如,通过调整显示屏的亮度和背光强度,关闭不必要的外部设备,调整无线信号强度等方式,可以大幅度降低整个系统的功耗。

7.合理使用定时器和中断:定时器和中断是控制系统状态和响应外部事件的重要组成部分。

通过合理设置定时器和中断的参数,可以在必要时唤醒系统,以及在系统闲置时进入睡眠模式,从而降低功耗。

总之,通过以上低功耗设计方法,可以在满足产品功能和性能要求的前提下,降低整个系统的功耗,延长电池寿命,达到节能环保的目的。

在电子产品设计中,低功耗设计是一个非常重要的趋势,也是未来产品发展的方向之一。

VLSI课程论文低功耗设计方法的总结、低功耗设计的实践与未来展望

一、低功耗设计方法的总结近几年,集成电路的供电电压有所下降,功耗却增长了近两倍;由于芯片的面积不断减小,功率密度增加,带来了散热设计的难度和封装的成本不断增高。

而在现在智能手机在追求其高性能,从而导致其高消耗,基本上每天都需给手机充电,甚至得带个充电宝才能满足其电量。

随着时间的发展集成电路性能的提高和功耗越发矛盾,未来的发展方向是可佩带设备,比如说现在的谷歌眼镜,谷歌眼镜在拍摄状态下30分钟电量就会用完,在轻便的同时电量不足以提供长时间使用,低功耗是一个不错的选择。

可佩带设备是现在全球的的发展趋势,索尼和三星在研发智能的手表,可以实现接听电话,查看短信邮件和一些互联网社交上的有一些功能。

带系统了,功能多了,必然会非常耗电。

如果集成电路在未来发展上即可把性能提高,又把耗能降低,在未来的集成电路会带动新的数码世界的高度。

以下讨论功耗是如何产生的以及低功耗的设计方法。

1、功耗的产生CMOS 电路的功耗可分为静态功耗和动态功耗两大类,而动态功耗中可分为开 关功耗和内部功耗。

1)静态功耗。

静态功耗是当逻辑门没有开关时所消耗的能量,是亚阈值漏电流所致,总漏电流功耗为设计各单元功耗之和2)开关功耗。

是驱动输出单元的输出端的负债电容冲放电的功耗∑∀⨯=)()(i i L oadiDD f CV nets 2c )(P (公式1)显然通过(公式1),在设计电路的时候通过减小供电电压可以明显的减小开关功耗。

近几年Intel 公司他们提出的超级本就用的比正常电压的低的CPU ,也是降低其功耗。

3)内部功耗。

内部功耗是边缘边界以内的功耗,是由于开关过程中,一个电路通过单元内部的电容冲放电消耗的能量。

合理的结构设计和先进的技术工艺能很大的程度降低系统的功耗。

设计流程由三类功耗分析技术分别是RTL 级功耗分析、布局布线前门级功耗分析和布局布线后门级功耗分析。

分别基于RTL 级分析、布局布线前门级仿真和布局布线后门级仿真。

主要进行时序和面积的优化,以功耗优化为主。

低功耗并行LTE—Turbo译码器的VLSI结构设计及实现

( yL b r tr f R d rsg a r c s n Ke a o a o y o a a i n l o e s g,Xi i nU ie st p i d a n v ri y,xi n 7 0 7 ) ’ 1 0 1 a 。 ( t t Ke a o a o y o ne r td S r i t o k , d a n v ri ’ S a e y L b r t r f I tg a e e vc New r s Xi in U ie s y,xi n 7 0 7 ) e t 1 0 1 r a

b oc l k. An e u sve a go ih i d v l e o ac a e he e wo d e s s n pa a ll c d r, r c r i l rt m s e eop d t c lult t s t a dr s e i a r le de o e whih la o t e p r lei m a e a a u c e ds t h a a lls c n b ny v l e,br a ng t i t ton o he po ro e ki he lmia i ft we f2.Reyi n l ng o t veop d a go ih a r e r i e VLS r h t c u e i e e t d,whih sg fc nty sm p iis t he de l e l rt m e u sv I a c ie t r s pr s n e c i nii a l i lfe he e t i i n or ton i t r on c i t r nd a o ds t e us g fi e l a e t r ge m e o y i x rnsc i f ma i n e c ne tng ne wo ks a v i h a e o nt re v r s o a m r n

VLSI电路设计优化技术研究

VLSI电路设计优化技术研究在现代信息时代,电子产品得到了广泛的应用,如手机、电视、电脑等等。

这些电子产品搭载了大量的电路芯片。

在这样的背景下,VLSI电路设计优化技术成为了电子设备领域中最为关键的技术之一。

VLSI是Very Large Scale Integration的缩写,即超大规模集成技术。

VLSI电路设计优化技术的主要目的是在尽可能少的芯片面积(通常以门数为单位),消耗尽可能少的功耗,并满足尽可能多的需求与功能的前提下,设计出满足制约约束的电路。

要做到这些,需要通过优化几个方面来实现:第一个方面是算法优化。

在设计电路时,通常需要使用一些算法。

这些算法的效率和准确性会影响电路的性能和质量。

因此,对算法进行优化至关重要。

第二个方面是器件技术的优化。

当现代电路中使用的器件数量增加时,芯片面积和功耗会增加。

为了减小芯片面积和功耗,必须使用更小、更快和更有效率的器件。

这就需要对器件技术进行优化,以达到更高的性能和效率要求。

第三个方面是物理布局的优化。

物理布局是将电路中的各个部分安排在芯片表面的过程。

正确的物理布局既可以更方便地调试电路,又可以让电路尽可能地紧凑并满足设计要求。

因此,对物理布局进行优化是至关重要的。

第四个方面是电路级优化。

电路级优化指对电路中的逻辑和结构进行调整,以保证电路满足设计要求,同时降低功耗和芯片面积。

这需要精确的电路设计和优化方法。

除了这些方面,还有很多技术和方法可以用来优化VLSI电路设计。

例如,通过选择更优化的电路拓扑结构或布线方式,可以进一步提升电路的性能。

总之,VLSI电路设计优化技术是现代电子设备中不可或缺的一部分。

只有掌握了这些技术和方法,我们才能更好地满足电子设备的需要,并推动电子产业的发展。

超大规模集成电路设计与优化技术

超大规模集成电路设计与优化技术超大规模集成电路(VLSI)是电子科技领域的重要分支之一,它是将数百万个电子元件集成到一个芯片上的技术,被广泛应用于计算机、通信、医疗和工业控制等各个领域。

而VLSI的设计与优化则是VLSI技术的核心,下面介绍一些相关的技术。

一、逻辑综合逻辑综合是指将高级语言或者RTL级的电路描述转化为门级电路的过程。

逻辑综合一般包括两个主要步骤:综合和优化。

综合是将电路描述转换成查找表(LUT)、触发器等基本电路的过程;而优化则是对综合结果进行优化,使得电路具备更好的性能和效率。

逻辑综合是进行VLSI设计的基础过程,能够高度提高芯片设计效率和减少功耗。

二、物理综合物理综合是指在逻辑综合的基础上,将门级电路转化为布局,并完成布线的过程。

其过程中主要涉及到电路面积、功耗、速度等方面的优化。

物理综合是VLSI设计过程中非常关键的步骤,能够大大缩减芯片设计周期和提高设计时效性。

三、功耗优化超大规模集成电路的功耗一直是设计过程中需要重点考虑的问题。

功耗优化可以采用多种不同的方法,例如电源管理、结构设计、时序优化等。

有效的功耗优化方法能够大大增加芯片的电池寿命、降低成本和提高性能。

四、时序约束时序约束是指将时序目标约束到VLSI电路上。

时序约束将电路的输入和输出之间的时间联系起来,并将时序参数与设计重要性联系起来。

时序约束在VLSI设计过程中扮演了非常重要的角色,能够准确控制电路的时序特性,确保芯片的性能和可靠性。

五、高可靠性设计高可靠性设计是指在高温、高压等严苛的环境下,芯片依然能够准确运行的设计方式。

高可靠性设计是一种重要的VLSI设计技术,具备抗大气环境的能力,是航空航天和军事等领域的重要技术。

六、芯片测试芯片测试是指对芯片在生产过程中的各个阶段进行测试,确保芯片满足规定的规格要求与性能指标。

芯片测试是实现芯片可靠性的重要手段,能够确保芯片成功投入市场并满足客户需求。

总之,在VLSI技术中,设计与优化是非常重要的环节,是实现芯片功能、性能和可靠性的关键决定因素。

低功耗的VLSI电路设计技术研究

低功耗的VLSI电路设计技术研究一、引言微观电子学的发展已经使得超大规模集成电路(VLSI)成为电子领域的主要发展方向之一。

VLSI电路的出现使得电子设备在体积小的情况下集成更多的模块,功能块数目更多、整体性能更好,也对电子产品的设计带来了更多的灵活性。

二、低功耗设计需求的提出大体积、大功率的可编程逻辑器件已经不符合当今电子设备低功耗、小体积的要求,因此设计中提出了三个目标:通用性、低功耗、高性能,这三者共同促进了设计中各个方面的发展。

三、低功耗技术的分类3.1 电源管理技术在电路设计中,电源管理技术通常被用来解决功耗过高的问题。

在整体电路设计中,电源线的布局非常关键。

一个好的设计不仅能够保证正确供电,更能够有效地降低功耗。

采用降压和电压调整技术等措施有效降低驱动功率。

3.2时钟管理技术时钟设计是电路设计中最重要的环节之一。

时钟频率在一定程度上决定了电路功率,采用一些可调的、自适应的时钟技术,可以实现功耗自动调节,降低了关键电路的功率而不会降低整体性能。

3.3设计和算法优化为了在电路设计中降低功率,很重要的一点是选择合适的设计技术和算法,优化电路的总功率。

例如,手动或自动地继电器树优化,以及双接收器、回填译码器等优化方法都可以在某些情况下显著地改进电路的性能。

3.4低静音电压升(LDO)技术在VLSI电路中,为了降低功耗,低静音电压升(LDO)可以将电压升高到所需电平,但是在恒流模式下,LDO基本上有0V 的误差电压。

四、低功耗技术的应用4.1集成电路的最优化设计在VLSI电路的最优化设计中,必须将整个电路功耗视为一个主要约束,同时对其他约束项进行考虑。

在实际电路设计中,缩短信号路径、降低时钟频率、采用高效算法可以降低电路功耗,从而减少电路的功耗。

4.2应用于微处理器的设计微处理器是计算机芯片的核心部分。

在微处理器设计中,优化体系结构、增加片上存储器、采用可调芯片电源管理技术等措施可以有效地降低线路功耗。

超大规模集成电路(VLSI)技术在电脑芯片制造中的应用分析

超大规模集成电路(VLSI)技术在电脑芯片制造中的应用分析超大规模集成电路(VLSI)技术是现代电子工艺领域的重要组成部分,也是电脑芯片制造中的关键技术之一。

本文将分析VLSI技术在电脑芯片制造中的应用,并探讨其对电脑性能提升的重要作用。

一、VLSI技术概述VLSI技术是指将数百万个晶体管和其他电子组件集成到一个微小的硅芯片上的技术。

它通过减小电路尺寸,提高集成度和密度,实现了电子元器件的高度集成,大大提高了电路的性能和功能。

二、电脑芯片中的VLSI技术应用1. 微处理器微处理器是电脑芯片的核心组成部分,也是VLSI技术应用最广泛的领域之一。

通过VLSI技术,我们可以将多个功能模块集成到一个芯片上,实现了多核处理、流水线等高级技术,大大提升了电脑的运算能力和响应速度。

2. 存储器电脑的存储器也是VLSI技术应用的重要领域。

通过微小的硅芯片,VLSI技术实现了DRAM和SRAM等高速存储器的集成,提供了大容量、高速度和低功耗的特性,满足了电脑对存储容量和读写速度的要求。

3. 图形处理器随着图形处理需求的不断增加,VLSI技术在图形处理器中的应用也日益重要。

通过VLSI技术,图形处理器实现了高度并行计算和复杂的图形渲染,为电脑游戏、多媒体应用等提供了强大的图形处理能力。

4. 通信模块现代电脑中的通信模块,如网卡和蓝牙模块,也广泛应用了VLSI技术。

通过集成电路的高度集成,VLSI技术实现了小尺寸、低功耗、高速度的通信模块,为电脑提供了高效的通信能力。

三、VLSI技术对电脑性能提升的重要作用1. 性能提升VLSI技术实现了电路尺寸的缩小和集成度的提高,使得电脑芯片在相同面积内集成更多的晶体管和功能模块。

这使得电脑的运算能力、存储容量和通信速度得到了大幅提升。

2. 功耗降低电脑的功耗一直是制约电脑发展的一个关键问题。

通过VLSI技术,电路尺寸的缩小和新材料的应用使电脑芯片功耗得到了有效控制。

高度集成的电路不仅提高了电脑的性能,还降低了功耗。

VLSI低功耗设计方法综述

VLSI低功耗设计方法综述孙强【摘要】分析了VLSI电路功耗的来源,阐述了VLSI电路物理层、逻辑层、结构层等不同设计层次的低功耗设计方法和VLSI高层次低功耗设计技术方法.【期刊名称】《牡丹江师范学院学报(自然科学版)》【年(卷),期】2011(000)003【总页数】2页(P6-7)【关键词】VLSI;低功耗;高层次综合【作者】孙强【作者单位】牡丹江师范学院计算机科学与技术系,黑龙江牡丹江157011【正文语种】中文【中图分类】TP391.7随着VLSI集成度和时钟频率的不断提高,电路的功耗问题显得越来越突出.有时可能因为电路某些部分功耗过大引起温度过高而导致系统工作不稳定或失效.功耗过大也会对封装带来很大的困难.因此,功耗已经逐渐成为VLSI设计时首要考虑的因素[1].为此,本文分析了CMOS电路功耗的来源,阐述了VLSI不同设计层次的低功耗设计方法和VLSI高层次低功耗设计方法.CMOS电路中有两种主要的功耗来源:动态功耗和静态功耗.动态功耗包括负载电容的功耗(称为开关功耗)和短路电流引起的功耗(称为短路功耗);静态功耗主要是由漏电流引起的漏电功耗.开关功耗当反相器的输入为理想阶跃波时,对纯电容负载Ceff充放电所消耗的功耗为开关功耗.其公式为其中,f为时钟频率,Ceff为有效开关电容,它不仅依靠电路结构,而且依靠系统的输入类型,V dd为供应电压,也是CMOS电路的逻辑摆幅.短路功耗当反相器输入为非理想阶跃波时,在输入波上升沿或者下降沿瞬间,存在PMOS器件和NMOS器件同时导通的区域,由此引起的功耗称为短路功耗.其公式为其中,V dd为供应电压,Istztic为短路电流.静态功耗从理论上讲,CMOS电路在稳定状态下没有从电源到地的直接路径,所以没有静态功耗.然而,在实际情况下,扩散器和衬底之间的PN结上总存在反向漏电流,该漏电流与扩散结点浓度和面积有关,从而造成一定的漏电功耗,也就是静态功耗.其公式为其中,V dd为供应电压,Ileakage为漏电流.由公式(1),(2),(3)可得出CMOS电路的总功耗为在公式(4)中,占主要地位的是PD,它大概占到整个CMOS电路总功耗的75%~80%.短路功耗和静态功耗与工艺有密切的关系,在系统设计时较难控制.因此,CMOS电路的低功耗设计主要考虑开关功耗[2].CMOS电路中能耗和延迟公式可以通过公式(5)和公式(6)表示.CMOS电路中每个操作的能耗公式为其中,Ceff为有效开关电容,V dd为供应电压.CMOS电路中每个操作的延迟公式为其中,V T为阈值电压,k是常数,α为技术依赖因子,V dd为供应电压.VLSI低功耗设计技术覆盖面广,设计灵活多变,既有系统的整体规划,又有物理的局部考虑.VLSI低功耗的设计方法[3]自下而上可以分为:物理层、逻辑层、结构层、算法(行为)层和系统层.物理层功耗优化技术物理层功耗优化技术主要以晶体管为基本器件来估算电路的功耗.在物理层由于节点的电平翻转行为已经确定,所以只有通过调整节点的电容来改善功耗.具体说,可以通过合理安排晶体管的次序来优化功耗.主要有绝缘体上硅设计技术和布局布线优化技术.逻辑层功耗优化技术逻辑层功耗优化技术主要以逻辑门为基本器件来估算电路的功耗,所以它没有晶体管级功耗的分析工具精确,但它所表示的电路更易懂.目前逻辑层功耗优化技术有逻辑优化设计、预计算技术和多阈值电压等技术.结构层功耗优化技术结构层功耗优化技术是在确定电路实现方案时考虑电路的功耗问题,在电路的面积、速度、功耗和可测性方面做出权衡.因此,设计会在面积、速度和可测性方面有所牺牲,但是电路的功耗往往会有一个数量级的下降.目前主要采用并行结构和流水线两种方法.行为(算法)层和系统层功耗优化技术行为层设计是首先翻译和分析硬件描述语言,并在给定的性能、面积和功耗的条件下,确定需要哪些硬件资源,如功能单元、存储器、互连单元和控制器等.由于实现设计的功能可能有多种硬件结构,因而行为层低功耗设计主要是在满足目标和约束条件的前提下,找到一个代价最小的硬件结构,使功耗最小.目前的功耗优化技术有动态电压缩放技术、多电压技术和并行流水线设计技术等.系统层的低功耗需要从软件编制、编译器设计和功耗管理等方面对系统进行优化,如动态功耗管理技术.高层次低功耗综合是一项新的高层次综合技术.随着设计层次的不同,VLSI低功耗设计方法的功耗优化概率也有很大的差别.不同设计层次的功耗优化概率,层次越高低功耗设计效果越明显[4].高层次设计能够最大程度地实现功耗优化,这是因为高层次设计对具体实现的依赖性很小,对算法和架构的选择自由度高,而算法和架构对最终硬件实现的可测性和功耗影响显著.随着电路集成度和运算速度的提高,对于需要减小功耗的设计,逻辑层或物理层的功耗优化已经无法满足要求,需要高层次设计优化来完成.高层次低功耗综合方法有很多种.因为VLSI中总的功耗主要是由动态功耗来决定的,并且电源的供应电压和动态功耗成二次平方关系,所以降低供应电压是最有效的降低功耗方法,于是很多研究通过降低电压的方法来减少功耗.然而,减小供应电压会导致电路延迟的增加和吞吐率的降低.为了解决供应电压和电路延迟之间的制约问题,一部分研究者[5]在使用降低供应电压实现功耗优化的同时采用并行和流水线结构的方法来提高吞吐率.另一部分研究者[6]通过在电路上设置多个大小不同的供应电压来达到上述目的,即在电路关键路径上为操作分配较高的供应电压来提高系统速度,而在非关键路径上为操作分配较低供应电压来降低系统功耗.采用此方法,既降低了功耗,又不会使电路的延迟增加和吞吐率降低.因此,多电压技术在高层次低功耗综合技术中起到了举足轻重的作用.近几年来,采用多电压方法减小功耗已成为一种趋势,大多数的高层次多电压设计方法有着相近的流程,该流程重点在调度上,因为它决定了VLSI设计中速度与硬件费用之间的折衷.高层次多电压调度主要目的是在保证电路性能的前提下,将不同的电源供应电压分配给相应操作来降低功耗.目前,国内外对基于多电压的高层次低功耗综合设计的研究已经比较深入.基于多电压调度算法的研究大致可分为基于时间约束、基于资源约束和基于时间与资源约束三种.通常,在VLSI高层次低功耗设计中主要考虑的调度方法是基于多电压的单时钟频率调度方法,而近几年来基于多电压的动态时钟频率调度方法也开始得到了研究,这是因为通过改变供应电压和时钟频率,不仅能够使系统的功耗和能耗降低,而且能够获得较高的性能.为了适应VLSI集成度和时钟频率的不断提高的需要,必须很好地解决电路的功耗问题对VLSI发展的影响.本文讨论了电路的功耗来源和不同设计层次的低功耗设计技术特点.分析了高层次低功耗设计技术在VLSI低功耗设计中的重要性,并提出了相关的VLSI高层次低功耗设计方法.【相关文献】[1]边计年,薛宏熙,苏明,等.数字系统设计自动化[M].北京:清华大学出版社,2005:270-276.[2]刘志鹏,边计年,周强.高层次综合中面向功耗优化的方法与技术[J].计算机辅助设计与图形学学报,2007,19(11):1374-1379.[3]温东新,杨孝宗,王玲.一种VLSI高层次综合低功耗设计方案及实现[J].计算机研究与发展,2007,44(7):1259-1264.[4]Han L,Chen J,Chen X D.Power optimization for the datapath of a 32-bit reconfigurable pipelined DSP processo r[J].Chinese Journal of Electronics,2005,22(6):650-657.[5]Rafael R S,María CM,JoséM M,Román H.Behavioural Transformation to Imp rove Circuit Performance in High-Level Synthesis.Proceedings of the 2005 Design,Automation and Test in Europe,M unich,Germany,2005,2:1252-1257.[6]Mohanty S P,Ranganathan N.Energy Efficient Datapath Scheduling using Multiple Voltages and Dynamic Clocking[J].ACM Transactions on Design Automation of Electronic Systems,2005,10(2):330-353.。

vlsi数字集成电路一般设计流程

vlsi数字集成电路一般设计流程VLSI数字集成电路一般设计流程VLSI(Very Large Scale Integration)数字集成电路设计是现代电子技术的重要组成部分,它涉及到了从设计到制造的整个过程。

在设计流程中,设计工程师需要遵循一系列的步骤和方法,以确保最终设计的数字集成电路能够满足要求并正常运行。

一般而言,VLSI数字集成电路的设计流程包括以下几个主要步骤:1. 系统规划与需求分析在这一阶段,设计工程师需要与客户或项目组进行充分的沟通,了解电路设计的具体需求和技术要求。

同时,还需要进行一些必要的市场调研和技术研究,以确定设计的方向和目标。

2. 电路架构设计在完成需求分析后,设计工程师需要对电路进行整体架构设计。

这一步骤主要包括确定电路的功能模块、模块之间的连接方式以及电路的整体性能指标等。

通过合理的架构设计,可以使电路的功能和性能得到最佳的实现。

3. 逻辑设计逻辑设计是VLSI数字集成电路设计的核心环节。

在这个阶段,设计工程师需要将电路的功能划分为若干个逻辑模块,并进行逻辑电路的设计和优化。

常用的逻辑设计工具有VHDL(VHSIC Hardware Description Language)和Verilog等。

4. 电路级设计在逻辑设计完成后,设计工程师需要进行电路级设计。

这一步骤主要包括选择合适的元器件、设计电路的结构和拓扑、进行电路参数的计算和仿真等。

通过电路级设计,可以确保电路在实际运行时能够满足性能和稳定性的要求。

5. 物理布局设计物理布局设计是将电路的逻辑和电路级设计转化为实际的物理结构和布局。

在这个阶段,设计工程师需要考虑电路的面积、功耗、时序等因素,进行电路的布局和布线。

常用的物理布局设计工具有Cadence等。

6. 验证和仿真在完成物理布局设计后,设计工程师需要对设计的电路进行验证和仿真。

这一步骤主要包括功能验证、时序验证和功耗验证等。

通过验证和仿真,可以确保设计的电路能够按照预期工作,并满足设计要求。

低功耗VLSI芯片的设计方法

低功耗VLSI芯片的设计方法

郝冬艳;张明;郑伟

【期刊名称】《微电子学与计算机》

【年(卷),期】2007(24)6

【摘要】对便携式电子器件的日益需求已经导致了功耗在IC设计产业的重要性。

根据VLSI的设计流程,结合微处理器的工作机制,在系统、行为、结构、逻辑和物理5个层面上对低功耗的设计方法做了全面地分析。

【总页数】4页(P137-139)

【关键词】低功耗;VLSI;IC

【作者】郝冬艳;张明;郑伟

【作者单位】浙江大学信息电子工程系

【正文语种】中文

【中图分类】TP332

【相关文献】

1.基于天通卫星移动通信系统的基带处理芯片低功耗设计方法 [J], 李恒

2.VLSI低功耗设计方法的研究 [J], 樊持杰;司巧梅;张丹

3.VLSI低功耗设计方法综述 [J], 孙强

4.一种低功耗MCU芯片的设计方法 [J], 王欣宇

5.低功耗方法在SoC芯片设计中的应用 [J], 马芝

因版权原因,仅展示原文概要,查看原文内容请购买。

超低功耗电子设备设计与实现

超低功耗电子设备设计与实现在当今高科技时代,超低功耗电子设备的设计与实现已经成为重要的研究课题。

随着移动设备、物联网、智能家居等领域的快速发展,对于电子设备在续航时间和功耗方面的要求也越来越高。

因此,如何设计和实现超低功耗电子设备成为了电子工程领域的一个重要挑战。

首先,超低功耗电子设备的设计需要考虑到多个方面。

首先是硬件设计方面,需要选择低功耗的处理器和组件,设计低功耗电路以降低设备整体功耗。

其次是软件设计方面,需要优化系统架构和算法,避免不必要的能耗;同时,采用功耗管理技术,根据应用需求动态调整设备功耗,实现节能的同时保证性能。

在实际实现超低功耗电子设备时,可以采取以下一些策略:1. 选择低功耗的处理器和组件:在设计电子设备时,选择低功耗的处理器和其他组件是至关重要的。

比如,选择基于ARM Cortex-M 系列处理器的芯片,通常具有低功耗和高性能的特点,适合用于低功耗电子设备的设计。

2. 优化系统架构和算法:通过优化系统架构和算法,可以实现在保证性能的前提下降低功耗。

比如,采用异步工作模式、睡眠模式等技术,减少设备在空闲状态下的功耗消耗。

3. 采用功耗管理技术:通过采用功耗管理技术,可以根据系统需求动态调整设备功耗。

比如,自适应调节电压和频率,选择合适的工作模式,延长设备续航时间。

4. 采用低功耗通信技术:在通信模块设计中选择低功耗的通信技术,如Bluetooth Low Energy(BLE)、Zigbee等,可以降低通信模块的功耗,延长设备电池续航时间。

总的来说,超低功耗电子设备的设计与实现需要综合考虑硬件设计、软件设计、功耗管理等多个方面的因素。

只有在不影响设备性能的前提下最大程度降低功耗,才能实现超低功耗电子设备的设计与实现。

希望未来能有更多的技术突破,为超低功耗电子设备的发展提供更多可能。

VLSI电路设计与集成电路优化

VLSI电路设计与集成电路优化摘要:在现代电子设备的发展中,集成电路扮演着至关重要的角色。

从微处理器到移动设备,从通信系统到嵌入式系统,都需要高度复杂且性能卓越的VLSI电路来实现各种功能。

因此,VLSI电路设计与集成电路优化成为了确保电子产品性能和功能的关键。

VLSI电路设计的核心任务包括将高级逻辑功能描述转化为门级电路,并在考虑时序、功耗和面积等因素的情况下进行优化。

这需要采用各种工具和技术,如逻辑综合、布局设计和布线设计。

同时,电路的时序特性需要特别关注,以确保电路在指定的时钟频率下正常工作。

电路的功耗也是一个重要的考虑因素。

随着移动设备的普及,低功耗设计成为了迫切需求。

通过电源管理、电压频率调整和逻辑优化等技术,工程师可以降低电路的功耗,延长电池寿命。

此外,电路的面积也需要最小化,以降低制造成本。

面积优化方法包括逻辑重用、共享逻辑资源和多核设计,以确保芯片的物理布局紧凑而高效。

最后,电路设计还需要考虑制造工艺的可行性和电路的可靠性。

制造工艺的不完美性和变化会影响电路的性能,因此需要进行适当的工艺控制和优化。

同时,电路设计也应考虑到故障容忍性,以确保电路在面对不可避免的故障情况时仍能正常运行。

关键词:VLSI;集成电路;电路设计;电路优化;半导体工艺引言VLSI(Very Large Scale Integration)电路设计与集成电路优化是当今电子工程领域的关键领域之一。

随着半导体技术的不断进步,芯片上的晶体管数量迅速增加,使得能够在小型芯片上实现更复杂的功能。

然而,这也带来了一系列的挑战,如电路设计的复杂性、功耗优化、故障容忍性和制造过程的可行性等。

本文将深入研究VLSI电路设计与集成电路优化的关键方面,以帮助读者更好地理解这一领域的核心概念和方法。

将从半导体工艺开始,介绍芯片制造的基础知识,包括制造工艺、工艺参数和工艺变化对电路性能的影响。

然后,将关注逻辑设计,讨论数字电路的建模、优化和验证方法。