GD32F107数据手册

STM32F105xx 107xx 数据手册

参照2011年8月 STM32F105xx 107xx数据手册 英文第6版 (本译文仅供参考,如有翻译错误,请以英文原稿为准)

STM32F105xx 107xx数据手册

目录

1 2 介绍 ............................................................................................................................................................ 4 规格说明 ..................................................................................................................................................... 5 2.1 2.2 2.3 器件一览 ......................................................................................................................................... 5 系列之间的全兼容性 ....................................................................................................................... 6 概述 .............................................................................................

机车车辆称重系统_使用说明书

103·符合国家《电子信息产品污染控制管理办法》的要求。

15

秤体的堆放和贮

用户在堆放秤体时需注意:

104·秤体应水平放置。

注意

严禁带电插拔

请先切断电源,再进行电气设备连接,检修

METTLER TOLEDO保留修改本说明书的权利

目 次

11

GCS系列静态电子轨道衡机车车辆称重系统,是我公司开发的最新产品。秤台采用模块化设计。结构设计合理、技术先进,适于大规模生产,质量稳定可靠。称重轨道衡由多个(2个及2个以上的双数)相互独立的单称量台组合而成,可分别提供独立称量台的称重数据和组合后的称量数据,从而满足用户的各种称重管理。

本手册归梅特勒-托利多()称重设备系统XX所有,未经许可不得翻印、修改或引用!

METTLER TOLEDO为梅特勒-托利多公司的注册商标!

警告

车辆必须直线上下轨道衡秤台,禁止车辆在秤台上转弯

警告

请专业人员调试、检测和维修系统

请保持本设备良好接地

注意

在进行仪表的电气连接时,请预先将电源切断.在给仪表上电前请等待30秒钟再给仪表接通电源

97·接收缓冲区:128K; 色带寿命:1000万字符; 打印头寿命: 4亿次/针

98·接口:并行接口、USB接口

99·工作温度X围:0C~45C, 湿 度:10~90%RH

100·电源:220V10%,50Hz/60Hz±1Hz;额定功率:81W

101·数据格式:通常、特殊命令和TOLEDO连续格式

79·串口输入:ASCⅡ指令CPTZ(清皮,去皮,打印,清零),SICS(提供0级和1级指令)

stm32f107 usbh主模式库解析

简介STM32F105/7 USB主模式库的目的是为USB主模式应用程序开发提供一个框架。

库代表了在STM32F105/7之上的USB OTG周边底层驱动。

它实现必要的软件块,目的是便于USB的主模式应用程序开发。

STM32F105/7USB主模式协议栈的库支持以下两个USB标准应用类:■大批量存储类(MSC)用于访问USB闪存pendrives■人机接口设备类(HID)用于键盘和鼠标设备目录1 USB的主模式包文件夹结构。

(6)2 USB主模式的库结构 (8)2.1库的结构框图 (8)2.2库内核的描述。

(9)2.2.1内核状态机。

(9)2.2.2设备枚举。

(10)2.2.3控制传输状态机。

(11)2.2.4 USB的I / O请求模块。

(11)2.2.5主模式通道控制模块。

(12)2.3类驱动程序。

(13)2.3.1 USB大批量存储类(MSC)驱动程序。

(13)2.3.2 USB人机接口设备类(HID)鼠标键盘设备驱动。

(17)3库用户API和回调函数。

(20)3.1库用户API。

(20)3.2用户的回调函数。

(20)3.2.1类的回调函数。

(20)3.2.2独立类的回调函数。

(22)4演示固件。

……. . 254.1大容量存储类演示。

…。

254.1.1软件初始化。

254.1.2大容量存储设备枚举。

254.1.3访问大容量存储器内容。

264.1.4 Flash pendrive测试。

264.2HID鼠标和键盘演示。

274.2.1初始化准备。

274.2.2鼠标或键盘设备枚举。

274.2.3 .鼠标演示。

284.2.4键盘演示。

284.3演示脚本。

285已知的限制。

(29)6修订历史。

(30)list of表表1 内核文件 (7)表2 class文件 (7)表3 枚举请求 (11)表4 USB的I / O请求模块 (12)表5 主模式通道控制模块 (12)表6 大容量存储类模块 (13)表7 MSC的内核模块 (15)表8 MSC BOT模块 (15)表9 MSC SCSI命令 (16)表10 MSC文件系统接口功能 (16)表11 efsl 主API (17)表12 HID类模块 (17)表13 MSC内核模块的功能 (18)表14 鼠标和键盘初始化和HID Report解码功能 (19)表15 测试U盘 (27)表16 演示的足迹 (28)表17文件修订历史 (30)数字表图1。

APM32F072x8xB 32位微控制器数据手册说明书

数据手册DatasheetAPM32F072x8xB基于Arm® Cortex®-M0+内核的32位微控制器版本:V1.5产品特性⏹内核32位Arm®w Cortex®-M0+内核最高48MHz工作频率⏹片上存储器Flash:64~128KBSRAM:16KB⏹时钟4~32MHz晶体振荡器带校准的32.768KHzw晶体/陶瓷振荡器内部8MHzwRC振荡器内部48MHz自动校正RC振荡器内部40KHzwRC振荡器PLL支持2~16倍频⏹复位、电源管理上电/掉电复位(POR/PDR)可编程电压调节器数字供电电压:V DD=2.0~3.6V模拟供电电压:V DDA=V DD~3.6V部分I/O供电电压:V DDIO2=1.65~3.6V支持外部电池V BAT为RTC供电:V BAT=1.65~3.6V⏹低功耗模式睡眠、停机、待机模式⏹串行线调试(SWD)⏹I/O最多87个I/Os所有I/O可映射到外部中断向量最多68个容忍5V输入的I/O,19个I/O由V DDIO2供电⏹通信接口2个I2C接口(1Mbit/s),全部支持SMBus/PMBus和唤醒。

4个USART接口,全部支持主同步SPI和调制解调控制,其中2个支持ISO7816、LIN、IrDA接口、自动波特率检测和唤醒。

2个SPI接口(18Mbit/s),全部支持I2S接口复用1个CAN接口1个全速USBD2.0接口,无需外挂晶振,支持BCD和LPMHDMIwCEC⏹模拟外设1个12位ADC,最多支持16个外部通道,转换范围0~3.6V,独立模拟电源输入:2.4~3.6V1个双通道、12位DAC2个可编程模拟比较器最多24个电容传感通道,可用于接近、触键、线性或旋转传感器⏹定时器1个可提供最多7通道PWM输出的16位的高级控制定时器,支持死区生成和刹车输入功能1个32位和5个16位通用定时器,每个定时器最多有4个独立通道用于输入捕获/输出比较。

智嵌STM32F107网络互联开发板V3.0实验例程操作手册

北京智嵌物联网电子技术ISTM32F107网络互联开发板3.0实验例程操作手册版本号:A拟制人:赵工时间:2013年7月1日目录1本文档编写目的 (1)2实验例程操作说明 (1)2.1LED闪烁实验 (1)2.2KEY_LED实验 (1)2.3RS232通讯实验 (1)2.4RS485通讯实验 (2)2.5CAN1通讯实验 (2)2.6CAN1与CAN2通讯实验 (3)2.7I2C实验—读写24c04 (4)2.8SPI通讯实验--读写SST2508B (5)2.9TCP服务器收发数据实验 (5)2.10动态IP实验 (7)2.11HTTP网页服务器实验 (7)2.12USB数据存储实验1(读写STM32F107片内flash) (9)2.13USB数据存储实验2(读写板载SST25F08B) (9)2.14U盘读写实验 (9)2.15USB鼠标实验 (11)2.16USB_JoyStickMouse实验 (11)2.17 2.4G无线模块NRF24l01通信实验 (12)2.18基于NRF24L01的无线RS232通讯实验 (12)2.19DS18B20温度试验 (13)2.20UDP客户端发送数据实验 (14)2.21UDP服务器收发数据实验 (15)2.22TCP客户端收发数据实验 (18)2.2316通道ADC采集实验 (21)2.24UDP与RS232RS485双向数据透明传输例程---开发板做服务器 (23)2.25TCP与RS232RS485双向数据透明传输实验 (23)2.26TCP与CAN双向数据透明传输实验 (23)1本文档编写目的本手册是针对STM32F107网络互联开发板V2.2的例程而编写的,包括每个实验例程的实验原理、实验步骤、注意事项等。

2实验例程操作说明2.1LED闪烁实验实验原理:通过控制PE2/PE3/PE4/PE5的电平变化实现LED灯的亮灭。

实验步骤:(1)用Keil uVision4打开LED灯闪烁实验工程,并编译。

STM32F107VCT6 微控制器用户手册说明书

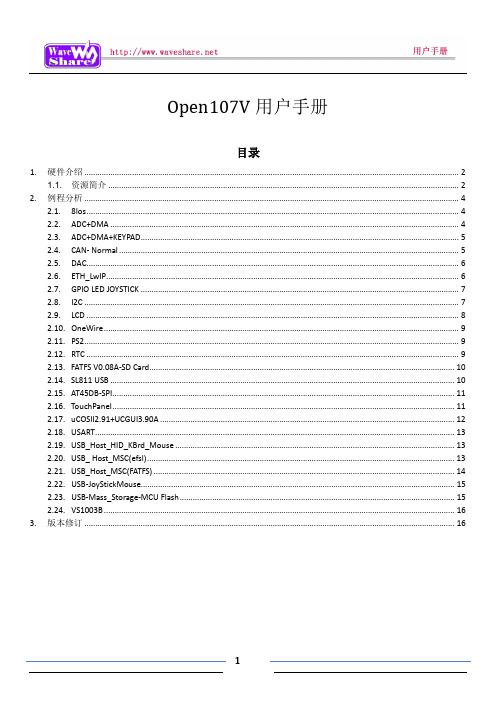

Open107V用户手册目录1. 硬件介绍 (2)1.1.资源简介 (2)2. 例程分析 (4)2.1. 8Ios (4)2.2. ADC+DMA (4)2.3. ADC+DMA+KEYPAD (5)2.4. CAN- Normal (5)2.5. DAC (6)2.6. ETH_LwIP (6)2.7. GPIO LED JOYSTICK (7)2.8. I2C (7)2.9. LCD (8)2.10. OneWire (9)2.11. PS2 (9)2.12. RTC (9)2.13. FATFS V0.08A-SD Card (10)2.14. SL811 USB (10)2.15. AT45DB-SPI (11)2.16. TouchPanel (11)2.17. uCOSII2.91+UCGUI3.90A (12)2.18. USART (13)2.19. USB_Host_HID_KBrd_Mouse (13)2.20. USB_ Host_MSC(efsl) (13)2.21. USB_Host_MSC(FATFS) (14)2.22. USB-JoyStickMouse (15)2.23. USB-Mass_Storage-MCU Flash (15)2.24. VS1003B (16)3. 版本修订 (16)1.硬件介绍1.1. 资源简介[ 芯片简介 ]1.STM32F107VCT6STM32功能强大,下面仅列出STM32F107VCT6的核心资源参数:内核:Cortex-M3 32-bit RISC;工作频率:72MHz,1.25 DMIPS/MHz;工作电压:2-3.6V;封装:LQFP100;I/O口:80;存储资源:256kB Flash,64kB RAM;接口资源:3 x SPI,3 x USART,2 x UART,2 x I2S,2 x I2C;1 x Ethernet MAC,1 x USB OTG,2 x CAN;模数转换:2 x AD(12位,1us,分时16通道),[ 其它器件简介 ]3."5V DC"或"USB"供电选择开关切换到上面,选择5V DC供电;切换到下面,选择USB供电。

KF8F204数据手册V1.0

17

I/O

T0CK

INT0

P0.1

AN1

18

I/O

ADVRIN

SPCLK

P0.0

19

I/O AN0

SPDAT

20

P VSS

KF8F204 数据手册 V1.0

双向输入输出端口 ADC 输入通道 8 双向输入输出端口 ADC 输入通道 6 外部中断 1 输入 双向输入输出端口 ADC 输入通道 5 双向输入输出端口 ADC 输入通道 4 PWM1 输出 带上拉和电平变化中断功能的双向输入输出端口 ADC 输入通道 2 T0 时钟输入 外部中断 0 输入 带上拉和电平变化中断功能的双向输入输出端口 ADC 输入通道 1 AD 外部参考电压输入 在线编程时钟输入 带上拉和电平变化中断功能的双向输入输出端口 ADC 输入通道 0 在线编程数据输入 地,0V 参考点

2.2.2 P1 口原理功能框图 .....................................................26 2.3 P2 口 .....................................................................27

2 I/O端口介绍 ............................................................... 17

2.1 P0 口 .....................................................................18 2.1.1 P0 口相关的寄存器 .....................................................19

STM32F105xx 107xx 数据手册

STM32F107xx

参照2011年8月 STM32F105xx 107xx数据手册 英文第6版 (本译文仅供参考,如有翻译错误,请以英文原稿为准)

STM32F105xx 107xx数据手册

目录

1 2 介绍 ............................................................................................................................................................ 4 规格说明 ..................................................................................................................................................... 5 2.1 2.2 2.3 器件一览 ......................................................................................................................................... 5 系列之间的全兼容性 ...........................................................

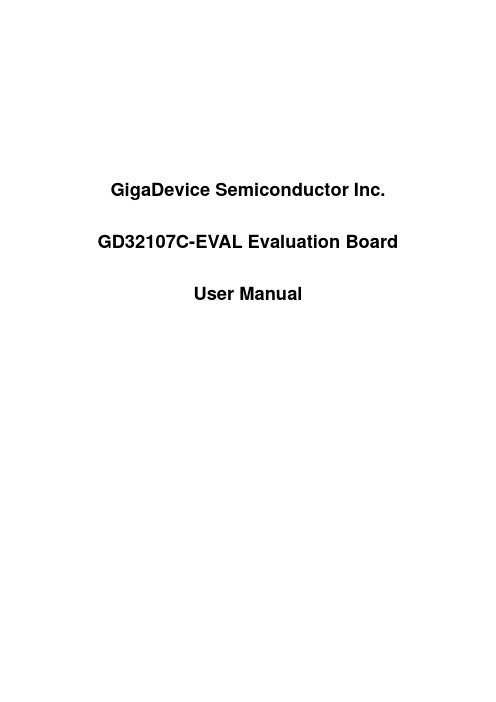

GD32107C-EVAL User-Manual

GigaDevice Semiconductor Inc. GD32107C-EVAL Evaluation BoardUser ManualTable of ContentsList of Figures (2)1 Introduction (3)2 Function pin assignment (3)3 Getting started (5)4 Hardware layout overview (5)4.1 Power supply (5)4.2 Boot option (5)4.3 LED (6)4.4 Key (6)4.5 USART1/USART2 (7)4.6 ADC/DAC (7)4.7 I2S (8)4.8 I2C (8)4.9 SPI-Serial Flash (9)4.10 USB (9)4.11 CAN (10)4.12 RTC (10)4.13 EXMC-LCD (11)4.14 EXMC-NAND Flash (12)4.15 Ethernet (12)4.16 Extension (13)5 Revision history (14)List of FiguresFigure 1 Schematic diagram of power supply (5)Figure 2. Schematic diagram of boot option (5)Figure 3. Schematic diagram of LED function (6)Figure 4. Schematic diagram of Key function (6)Figure 5. Schematic diagram of USART1/USART2 function (7)Figure 6. Schematic diagram of ADC/DAC function (7)Figure 7. Schematic diagram of I2S function (8)Figure 8. Schematic diagram of I2C function (8)Figure 9. Schematic diagram of SPI-Serial Flash function (9)Figure 10.Schematic diagram of USB function (9)Figure 11. Schematic diagram of CAN function (10)Figure 12. Schematic diagram of RTC function (10)Figure 13. Schematic diagram of EXMC-LCD function (11)Figure 14. Schematic diagram of EXMC-NAND Flash function (12)Figure 15. Schematic diagram of Ethernet (12)Figure 16. Schematic diagram of Extension Pin (13)1 IntroductionGD32107C-EVAL evaluation board uses GD32F107VCT6 as the main controller. As acomplete development platform of GD32F107xx connectivity line powered by ARM®Cortex™-M3 core, the board supports full range of peripherals. It uses Mini USB interface orAC/DC adapter as 5V power supply. JTAG, Reset, Boot, User button key, LED, CAN, I2C,I2S, USART, RTC, EXMC, SPI, USB_OTG, ADC, DAC, Ethernet and Extension Pin are alsoincluded. This document details its hardware schematic and the relevant applications.2 Function pin assignment3 Getting startedThe EVAL Board uses Mini USB connecter to get power, the hardware system power is+3.3V. A Mini USB cable and a J-Link tool are necessary to down programs. Select thecorrect boot mode and then power on, the LED1 will turn on, which indicates the powersupply is ready.4 Hardware layout overview4.1 Power supply4.2 Boot option4.3 LED4.4 Key4.5 USART1/USART24.6 ADC/DAC4.7 I2S4.8 I2C4.9 SPI-Serial Flash4.10 USB4.11 CAN4.12 RTC4.13 EXMC-LCDThe EVAL Board supports EXMC function and uses a short jumper to extend EXMC_NE1.But only one extended NE1 (LCD_CS, Nand_CS) can be used at any time.4.14 EXMC-NAND Flash4.15 Ethernet4.16 Extension5 Revision history。

fr107中文资料_数据手册_参数

金龙107开发板用户手册(User Manual)

深圳市旺宝电子科技有限公司

11

论坛:

深圳市旺宝电子科技有限公司

论坛:

这里 download from file 选择要下载的文件,并且选择全片擦除,或擦除需要 的块,其他可默认,然后 next 下载 成功后

深圳市旺宝电子科技有限公司 14 论坛:

深圳市旺宝电子科技有限公司

论坛:

0x08003000,因为程序定义的地址是这个,更改地址时需要注意向量表等等的设 置,选择我们编译好的.hex 文件, 点击产生,将生产我们需要的 dfu 文件,可退出软了, .hex 文件生产可用以下方法

开发板没设置正确, 当出现以下界面,则完成

深圳市旺宝电子科技有限公司

10

论坛:

深圳市旺宝电子科技有限公司

论坛:

如果出不来,此时只能用串口 2 下载了,设置跳线 JP3 为 2-3,然后插上 usb 线到 USB-1,然后关闭软件,并重新打开,然后按复 位键(必须的)按软件的 next,将会出现上面的界面,然后点 next 下一步,一 直下一步到如下界面

深圳市旺宝电子科技有限公司

13

论坛:bbs.opΒιβλιοθήκη

深圳市旺宝电子科技有限公司

论坛:

设备管理器出现了 stm device in dfu mode,证明安装成功 (我们是默认进入 DFU 模式的,可查看)

深圳市旺宝电子科技有限公司

论坛:

旺宝-金龙 107 开发板 用户手册

深圳市旺宝电子科技有限公司

1

论坛:

深圳市旺宝电子科技有限公司

论坛:

1.2.开发板板载资源

STM32F107VCT6,ARM Cortex-M3 内核,主频 72MHz,内部含有 256K 字 节的 FLASH 和 64K 字节的 SRAM 1 个 10M/100M 以太网接口,标准 RJ45 接口,支持平行交叉网线自适应 1 个 USB 2.0 OTG 全速接口, 可以作为 USB SLAVE, 也可以作为 USB HOST 1 个标准的 3.2/4.3/5/7 寸 TFT LCD 接口,带触摸功能 1 个 I2S 音频解码芯片 WM8978,支持 MP3 软解,高品质音乐播放 1 个 FM 收音机芯片 TEA5767 2 个耳机接口 1 个 SD 卡接口 1 个 2.4G 无线通信模块接口 1 个红外接收头 1 个摄像头接口,选配 OV7670 模块 1 个温度传感器接口,选配 DS18B20 2 个 CAN 总线接口 1 个 RS485 接口 1 个 RS232 串口,DB9 母头 1 个 USB 转串口芯片 PL2303,笔记本使用更加方便 1 个 SPI FLASH 芯片,W25Q16,存储字库更加方便 1 个 IIC 接口的 EEPROM 芯片,24C02,容量 2K 1 个小喇叭 1 个复位按钮,控制整板硬件复位 4 个功能按钮,其中包括 WAKEUP 唤醒功能和 TEMPER 入侵功能 1 个五向按键 1 个电源指示灯,LD2,红色 4 个用户状态指示灯,LD1,LD3,LD4,LD5 红色 2 个启动模式选择配置端口 1 个 RTC 实时时钟后备电池座

lc32f107芯片手册

lc32f107芯片手册

LC32F107 是一款由 Linear Technology 公司制造的 32 位低

功耗微控制器。

以下是 LC32F107 芯片手册的简要概述:

1. 硬件特性:

- 32 位处理器,采用 ARM Cortex-M3 内核,最高可达 200 MHz - 低功耗模式:有多种睡眠和休眠模式可选,可实现极低的功耗 - 实时时钟 (RTC):支持实时时钟功能,可进行日历和闰年自动校正

- 两个16位定时器/计数器:具有预分频器和比较器功能

- 多个中断源:支持多个中断请求

- 外设接口:支持多个 GPIO 口、一个串口、一个 SPI 接口、一个 I2C 接口等

2. 软件特性:

- 可编程 Flash 存储器:支持擦写和编程功能

- 可编程只读存储器 (ROM):支持读取和编程功能

- 外设驱动软件库:提供多种外设驱动软件库,方便开发者开发外设应用程序

- 汇编语言和 C 语言编译器:支持汇编语言和 C 语言编译器,支持多种开发环境

3. 外围模块:

- 串口模块:支持高速数据传输和低速数据传输模式

- SPI 接口模块:支持高速数据传输和低速数据传输模式

- I2C 接口模块:支持高速数据传输模式

- RTC 模块:支持实时时钟功能

- 模拟输入模块:支持多个模拟输入通道

- 时钟和电源管理模块:支持时钟和电源管理功能

LC32F107 芯片手册可以在 Linear Technology 公司的官方网站上免费下载。

gd32f307 基本项目工程模板

1. 项目背景介绍gd32f307 是一款基于ARM Cortex-M4内核的高性能微控制器,具有丰富的外设和强大的处理能力。

在开发基于gd32f307的项目时,一个好的项目工程模板是非常重要的。

它可以提高开发效率,规范项目结构,减少重复工作,帮助开发人员更好地管理项目。

2. 项目工程模板概述一个优秀的gd32f307项目工程模板应该包括以下内容:- 项目结构:合理的文件夹组织结构,包括源文件、头文件、外设驱动、中间件等目录。

- 主函数:包括系统初始化、外设初始化等基本内容。

- HAL库的使用:使用官方提供的HAL库对外设进行操作,简化开发过程。

- FreeRTOS集成:如果项目需要多任务处理,可以集成FreeRTOS 实现任务管理。

- 调试配置:配置好调试选项,方便开发人员调试程序。

- 编译信息脚本:包括Makefile或者CMakeLists.txt等,用于编译信息整个工程。

- 版本管理:建议使用Git等版本管理工具进行代码管理。

3. 项目工程模板深度解析3.1 项目结构:合理的项目结构可以提高代码的可维护性和可读性。

比如将外设驱动、中间件等模块化组织,方便复用和维护。

3.2 主函数:主函数应该包括系统时钟初始化、外设初始化、中断优先级配置等内容,确保系统能够正常运行。

3.3 HAL库的使用:HAL库是官方提供的外设操作库,可以大大简化外设操作的流程,提高开发效率。

3.4 FreeRTOS集成:如果项目需要多任务处理,集成FreeRTOS 可以帮助开发人员更好地管理任务,提高系统的稳定性。

3.5 调试配置:良好的调试配置可以帮助开发人员快速定位问题,提高开发效率。

3.6 编译信息脚本:合理的编译信息脚本可以简化编译信息过程,减少错误发生的概率。

3.7 版本管理:使用版本管理工具可以帮助团队协作开发,更好地管理代码变更。

4. 项目工程模板总结一个优秀的gd32f307项目工程模板应该具备良好的项目结构、合理的主函数内容、HAL库的使用、FreeRTOS集成、调试配置、编译信息脚本和版本管理。

金龙107基础例程文档

在此首先说明,限于本人水平有限,以下说明可能会有错误,如果发现错误的地方,请及时向我反映,本人邮箱772113229@,本人经过校对确认之后,会及时的作出修改。

本文档只作参考使用,具体的实验现象与实际条件有关,所以难免会有所出入。

本实验说明是在实验者对keil设置和对STM32的库有一定的了解的基础上所作的说明,如果对keil的设置和STM32的库文件一点都不了解,请先学习用keil建立一个工程以及对外设固件库使用说明。

第一章金龙107——LED实验实验目的:1、熟悉金龙107的LED硬件设计,2、熟悉STM32的IO使用实验器材:金龙107开发板V1.0一块,J-linkV8,keil4.23,STM3.2库文件V3.5.0,USB数据线一根实验说明:在本实验中,主要使用到开发板上的LED灯,实现跑马灯,主要跳线帽:JP4和JP7都接在2-3上硬件说明:端口输出高电平,LED灯亮,端口输出低电平,LED灯灭。

程序说明:首先说明一点,STM32的启动过程,并不是从main开始的,而是从启动文件里面开始,然后又跳转到main(详细说明可以参见STM32启动文件说明),并且在启动文件中,跳转到main之前,已经调用了SystemInit();,实现对STM32的时钟配置。

然后从main函数开始说明,第一步SystemInit();这个函数官方已经写好,其主要配置了STM32的时钟,该函数,在启动文件中已经被调用了(详见STM32启动文件的说明),所以这里可以去掉。

接下来是对LED的初始化,其中该函数在hw_config.h中,首先是对端口的初始化,对端口的初始化,要注意的是首先要声明定义结构体,然后开启对应端口的时钟,然后对端口的结构体进行配置(配置说明详见固件库说明)。

下面就是对四个LED灯的初始化,在本例程中我们采用了宏定义,如下图,详见hw_config.h。

在while循环中,实现LED灯的循环亮灭。

GD32固件库使用手册+(LCD+RTC+RCC)

GD32 MCU外设固件库使用手册——基于《GD32F10x_Firmware_Library_V1.0.0》固件库目录目录 1一、LCD模块 (1)6.1 LCD模块寄存器 (1)6.2 LCD模块初始化结构体LCD_InitPara (1)6.3 LCD模块库函数 (3)6.4 应用实例 (4)二、RTC模块 (6)7.1 RTC模块寄存器 (6)7.2 RTC模块库函数 (7)7.3 应用实例 (8)三、RCC模块 (10)8.1 RCC模块寄存器 (10)8.2 RCC模块库函数 (12)8.3 应用实例 (13)一、LCD模块备注:LCD模块针对GD32F170和GD32F190的芯片。

LCD模块的固件库文件为gd32f1x0_lcd.c和gd32f1x0_lcd.h。

6.1 LCD模块寄存器LCD模块寄存器的定义如代码清单6.1.1所示。

代码清单6.1.1 LCD模块寄存器定义6.2 LCD模块初始化结构体LCD_InitParaLCD初始化结构体为LCD_InitPara,其定义如代码清单6.2.1所示。

代码清单6.2.1 LCD_InitPara初始化结构体定义代码该初始化结构体包含五个成员变量,具体说明如表6.2.1所示。

LCDCLK先经过预分频器进行分频,之后再经过分频器进行分频,具体可参考图6.2.1所示。

图6.2.1 LCD时钟信号示意图具体定义如代码清单6.2.2所示。

代码清单6.2.2 LCD_Duty所标识的宏定义清单码表和一些LCD显示的接口,数字段码表代码如代码清单6.3.1所示。

代码清单6.3.1 数字断码表代码清单6.4.2 系统时钟配置代码表7.2.1 RTC模块库函数列表1、等待RTC_CTLR寄存器中LWOFF控制位变为1,即上次对RTC的操作完成,具体寄存器操作语句如下:while(RTC->CTLR2 && RTC_FLAG_LWOFF == 0){}。

SIM32F107VCT6平台的bxCAN标识符过滤技术与应用

SIM32F107VCT6平台的bxCAN标识符过滤技术与应用以STM32F107VCT6芯片的bxCAN控制器为例,介绍了与标识符过滤相关的寄存器构成,并详细分析了标识符过滤参数的配置方法和过滤规则。

最后,为方便移植和使用,给出了该控制器标识符过滤的C语言程序。

引言在CAN协议里,报文的标识符不代表节点的地址,而是与报文的内容相关。

在通信过程中,发送方将数据附上特定的标识符以广播的形式发送到总线上。

由于CAN总线的局域网性质,总线上的其他节点会同时检测到此报文,接收节点会根据标识符的值来决定软件是否需要该报文。

如果需要,就拷贝到SRAM里;如果不需要,则报文被丢弃,且无需软件的干预。

采用这种硬件过滤的方式可以大大节省CPU的开销。

目前应用比较广泛的STM32F10x系列嵌入式芯片内置有bxCAN控制器,该控制器是一种在标准CAN总线基础上扩展的总线接口,支持CAN总线协议2.0A和2.0B。

它的设计目标是以最小的CPU 负荷来高效处理收到的大量报文。

它也支持报文发送的优先级要求(优先级特性可软件配置)。

为了满足CAN总线协议中的标识符硬件过滤需求,bxCAN控制器提供了位宽可变的、可配置的过滤器组,用来完成只接收软件需要的报文功能。

本文主要以STM32F107VCT6平台下的bxCAN控制器为研究对象,系统分析了该控制器的标识符过滤使用方法,并给出了C语言程序,从而方便移植和使用。

1 标识符过滤相关寄存器简介bxCAN控制器要实现标识符的硬件过滤,需要由一组相应的寄存器进行控制。

这些寄存器主要包括CAN过滤器位宽寄存器、CAN 过滤器主控寄存器、CAN过滤器组寄存器等。

上述寄存器可以分别控制过滤器的位宽、过滤模式以及过滤ID。

下面对这些寄存器进行介绍。

(1)CAN过滤器位宽寄存器bxCAN控制器过滤器位宽可变指的是每个过滤器组的位宽都可以独立配置,以满足应用程序的不同需求。

根据位宽的不同,每个过滤器组可提供1个32位过滤器或2个16位过滤器。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

GigaDevice Semiconductor Inc.GD32F107xxARM® Cortex™-M3 32-bit MCUDatasheetTable of ContentsList of Figures (3)List of Tables (4)1 General description (5)2 Device overview (6)2.1 Device information (6)2.2 Block diagram (8)2.3 Pinouts and pin assignment (9)2.4 Memory map (12)2.5 Clock tree (13)2.6 Pin definitions (14)3 Functional description (22)3.1 ARM® Cortex™-M3 core (22)3.2 On-chip memory (22)3.3 Clock, reset and supply management (23)3.4 Boot modes (23)3.5 Power saving modes (24)3.6 Analog to digital converter (ADC) (24)3.7 Digital to analog converter (DAC) (25)3.8 DMA (25)3.9 General-purpose inputs/outputs (GPIOs) (25)3.10 Timers and PWM generation (26)3.11 Real time clock (RTC) (27)3.12 Inter-integrated circuit (I2C) (27)3.13 Serial peripheral interface (SPI) (28)3.14 Universal synchronous asynchronous receiver transmitter (USART) (28)3.15 Inter-IC sound (I2S) (28)3.16 Universal serial bus on-the-go full-speed (USB OTG FS) (29)3.17 Controller area network (CAN) (29)3.18 Ethernet MAC interface (29)3.19 External memory controller (EXMC) (30)3.20 Debug mode (30)3.21 Package and operation temperature (30)4 Electrical characteristics (31)4.1 Absolute maximum ratings (31)4.2 Recommended DC characteristics (31)4.3 Power consumption (32)4.4 EMC characteristics (33)4.5 Power supply supervisor characteristics (33)4.6 Electrical sensitivity (34)4.7 External clock characteristics (34)4.8 Internal clock characteristics (35)4.9 PLL characteristics (36)4.10Memory characteristics (36)4.11 GPIO characteristics (36)4.12 ADC characteristics (37)4.13 DAC characteristics (37)4.14 I2C characteristics (37)4.15SPI characteristics (38)5 Package information (39)6 Ordering Information (41)7 Revision History (42)List of FiguresFigure 1. GD32F107xx block diagram (8)Figure 2. GD32F107Zx LQFP144 pinouts (9)Figure 3. GD32F107Vx LQFP100 pinouts (10)Figure 4. GD32F107Rx LQFP64 pinouts (11)Figure 6. GD32F107xx memory map (12)Figure 7. GD32F107xx clock tree (13)Figure 8. LQFP package outline (39)List of TablesTable 1. GD32F107xx devices features and peripheral list (6)Table 2. GD32F107xx pin definitions (14)Table 3. Absolute maximum ratings (31)Table 4. DC operating conditions (31)Table 5. Power consumption characteristics (32)Table 6. EMS characteristics (33)Table 7. EMI characteristics (33)Table 8.Power supply supervisor characteristics (33)Table 9. ESD characteristics (34)Table 10. Static latch-up characteristics (34)Table 11. High speed external clock (HSE) generated from a crystal/ceramic characteristics (34)Table 12. Low speed external clock (LSE) generated from a crystal/ceramic characteristics (35)Table 13. High speed internal clock (HSI) characteristics (35)Table 14. Low speed internal clock (LSI) characteristics (35)Table 15. PLL characteristics (36)Table 16. Flash memory characteristics (36)Table 17. I/O port characteristics (36)Table 18. ADC characteristics (37)Table 19. DAC characteristics (37)Table 20. I2C characteristics (37)Table 21. SPI characteristics (38)Table 22. LQFP package dimensions (40)Table 23. Part ordering code for GD32F107xx devices (41)Table 24. Revision history (42)1 General descriptionThe GD32F107xx device belongs to the connectivity line of GD32 MCU Family. It is a 32-bitgeneral-purpose microcontroller based on the ARM® Cortex™-M3 RISC core with enhancedconnectivity performance and best ratio in terms of processing power, reduced powerconsumption and peripheral set. The Cortex™-M3 is a next generation processor core whichis tightly coupled with a Nested Vectored Interrupt Controller (NVIC), SysTick timer andadvanced debug support.The GD32F107xx device incorporates the ARM®Cortex™-M3 32-bit processor coreoperating at 108 MHz frequency with Flash accesses zero wait states to obtain maximumefficiency. It provides up to 1 MB on-chip Flash memory and 96 KB SRAM memory. Anextensive range of enhanced I/Os and peripherals connected to two APB buses. Thedevices offer up to three 12-bit ADCs, up to two 12-bit DACs, up to ten general-purpose16-bit timers, two basic timers plus two PWM advanced-control timer, as well as standardand advanced communication interfaces: up to three SPIs, two I2Cs, three USARTs, twoUARTs, two I2Ss, two CANs, an USB OTG FS and an Ethernet MAC.The device operates from a 2.6 to 3.6 V power supply and available in –40 to +85 °Ctemperature range. Several power saving modes provide the flexibility for maximumoptimization between wakeup latency and power consumption, an especially importantconsideration in low power applications.The above features make the GD32F107xx devices suitable for a wide range ofinterconnection applications, especially in areas such as industrial control, motor drives,power monitor and alarm systems, consumer and handheld equipment, POS, vehicle GPS,LED display and so on.2 Device overview 2.1 Device information2.2 Block diagramFigure 1. GD32F107xx block diagram2.3 Pinouts and pin assignmentFigure 2. GD32F107Zx LQFP144 pinoutsPF2PF3PF7PC6PG8PG7PG6PG5PG4PG3PD15PD14PA3V SS_4V DD_4PA4PA5PA6PA7PC4PC5V DD_3V SS_3PE1PE0PB9PB8BOOT0PB7PB6PB5PB4PB3PF13PE7V DD_2V SS_2NC PA13PA12PA11PA10PA9PA8PC9PC8PC7PG14PG13PG12PG10PG9PD7PD6V BATPC14-OSC32_IN PC15-OSC32_OUTPF4PF0PF1OSC_IN V SS_10PF5V V PF6PG15V SSA V V V PD13PD12PD11PD10PD9PD8PB15PB14PB13PB12PD5PD4PD3PD2PD1PD0PC12PC10PA15PA14PF8PF9PF10V SS_6V DD_6PE8V SS_7V DD_7V SS_1V DD_1V DD_8V SS_8PG2V DD_9V SS_9V DD_10V SS_11V DD_11Figure 3. GD32F107Vx LQFP100 pinoutsOSC_IN OSC_OUTV SSA V REF-PA1PC6PD15PD14PD13PD12PD11PD10PD9PD8PB15PB14PB13PA3SS_4V DD_4PA4PA5PA6PA7PC4PC5PB0PB1PB2V DD_3V SS_3PE1PE0PB9PB8BOOT0PB7PB6PB5PB4PB3PE7PE8PE9PE10PE11PB11V SS_1V DD_2V SS_2NC PA13PA12PA11PA10PA9PA8PC9PC8PC7PD5PD4PD3PD2PD1PD0V BATPC13-TAMPER-RTCPC14-OSC32_IN PC15-OSC32_OUTNRST V SS_5V DD_5PA0-WKUPPE2PA2PB12V DD_1PE3PE4PE5PE6PC0PC1PC2PC3V V DDAPD6PD7Figure 4. GD32F107Rx LQFP64 pinoutsV SSA PA1PA12PA11PA10PA9PA8PC9PC8PC7PC6PB15PB14PB13PA3V SS_4V DD_4PA4PA5PA6PA7PC4PC5PB0PB1PB2V DD_3V SS_3PB8PB9PB7PB6BOOT0PB5PB4PB3PD2PC12PB10PB11V SS_1V DD_2V SS_2PA13PA15PA14V BATPC13-TAMPER-RTCPC14-OSC32_IN PC15-OSC32_OUTNRST PA0-WKUPPA2PB12V DD_1PC0PC1PC2PC3V DDAPC10PC11PD1 OSC_OUTPD0-OSC_IN2.4 Memory mapFigure 5. GD32F107xx memory map76543210x 4000 00000x 4000 04000x 4000 08000x 4000 0C000x 4000 10000x 4000 14000x 4000 18000x 4000 1C000x 4000 20000x 4000 24000x 4000 28000x 4000 2C000x 4000 30000x 4000 34000x 4000 38000x 4000 3C000x 4000 40000x 4000 44000x 4000 48000x 4000 4C000x 4000 50000x 4000 54000x 4000 58000x 4000 5C000x 4000 64000x 4000 68000x 4000 6C000x 4000 70000x 4000 74000x 4000 78000x 4001 00000x 4001 04000x 4001 08000x 4001 0C000x 4001 10000x 4001 14000x 4001 18000x 4001 1C000x 4001 20000x 4001 24000x 4001 28000x 4001 2C000x 4001 30000x 4001 34000x 4001 38000x 4001 3C000x 4001 40000x 4001 4C000x 4001 50000x 4001 54000x 4001 58000x 4002 00000x 4002 04000x 4002 08000x 4002 10000x 4002 14000x 4002 20000x 4002 24000x 4002 30000x 4002 34000x 4002 80000x 5000 04002.5 Clock treeFigure 6. GD32F107xx clock treeLegend:HSE = High speed external clockHSI = High speed internal clockLSE = Low speed external clockLSI = Low speed internal clock2.6 Pin definitionsNotes:1. Type: I = input, O = output, P = power.2. I/O Level: 5VT = 5 V tolerant.3. Functions are available in GD32F107xC, GD32F107xD, GD32F107xE, GD32F107xF, GD32F107xGdevices.4. Functions are available in GD32F107xF, GD32F107xG devices.3 Functional description3.1 ARM® Cortex™-M3 coreThe Cortex™-M3 processor is the latest generation of ARM®processors for embeddedsystems. It has been developed to provide a low-cost platform that meets the needs of MCUimplementation, with a reduced pin count and low-power consumption, while deliveringoutstanding computational performance and an advanced system response to interrupts.⏹32-bit ARM® Cortex™-M3 processor core⏹Up to 108 MHz operation frequency⏹Single-cycle multiplication and hardware divider⏹Integrated Nested Vectored Interrupt Controller (NVIC)⏹24-bit SysTick timerThe Cortex™-M3 processor is based on the ARMv7 architecture and supports both Thumband Thumb-2 instruction sets. Some system peripherals listed below are also provided byCortex™-M3:⏹Internal Bus Matrix connected with ICode bus, DCode bus, system bus, PrivatePeripheral Bus (PPB) and debug accesses (AHB-AP)⏹Nested Vectored Interrupt Controller (NVIC)⏹Flash Patch and Breakpoint (FPB)⏹Data Watchpoint and Trace (DWT)⏹Instrument Trace Macrocell (ITM)⏹Memory Protection Unit (MPU)⏹Serial Wire JTAG Debug Port (SWJ-DP)⏹Trace Port Interface Unit (TPIU)3.2 On-chip memory⏹Up to 1024 Kbytes of Flash memory⏹96 Kbytes of SRAMThe ARM®Cortex™-M3 processor is structured in Harvard architecture which can useseparate buses to fetch instructions and load/store data. 1024 Kbytes of inner Flash at mostand 96 Kbytes of inner SRAM is available for storing programs and data, both accessed(R/W) at CPU clock speed with zero wait states.The Figure 6. GD32F107xx memory mapshows the memory map of the GD32F107xx series of devices, including code, SRAM,peripheral, and other pre-defined regions.3.3 Clock, reset and supply management⏹Internal 8 MHz factory-trimmed RC and external 4 to 16 MHz crystal oscillator⏹Internal 40 KHz RC calibrated oscillator and external 32.768 KHz crystal oscillator⏹Integrated system clock PLL⏹ 2.6 to 3.6 V application supply and I/Os⏹Supply Supervisor: POR (Power On Reset), PDR (Power Down Reset), and low voltagedetector (LVD)The Clock Control Unit (CCU) provides a range of oscillator and clock functions. Theseinclude speed internal RC oscillator and external crystal oscillator, high speed and low speedtwo types.Several prescalers allow the configuration of the AHB frequency, the high-speedAPB (APB2) and the low-speed APB (APB1) domains. The maximum frequency of the AHBand the high-speed APB domains is 108 MHz. The maximum allowed frequency of thelow-speed APB domain is 54 MHz. See Figure 7 for details on the clock tree.The Reset Control Unit (RCU) controls three kinds of reset: system reset resets theprocessor core and peripheral IP components. Power-on reset (POR) and power-down reset(PDR) are always active, and ensures proper operation starting from/down to 2.6 V. Thedevice remains in reset mode when V DD is below a specified threshold. The embedded lowvoltage detector (LVD) monitors the power supply, compares it to the voltage threshold andgenerates an interrupt as a warning message for leading the MCU into security.Power supply schemes:⏹V DD range: 2.6 to 3.6 V, external power supply for I/Os and the internal regulator.Provided externally through V DD pins.⏹V SSA, V DDA range: 2.6 to 3.6 V, external analog power supplies for ADC, reset blocks,RCs and PLL. V DDA and V SSA must be connected to V DD and V SS, respectively.⏹V BAT range: 1.8 to 3.6 V, power supply for RTC, external clock 32 kHz oscillator andbackup registers (through power switch) when V DD is not present.3.4 Boot modesAt startup, boot pins are used to select one of three boot options:⏹Boot from main flash memory (default)⏹Boot from system memory⏹Boot from on-chip SRAMThe boot loader is located in the internal boot ROM memory (system memory). It is used toreprogram the Flash memory by using USART1, USART2, CAN2, USB OTG FS in devicemode. It also can be used to transfer and update the Flash memory code, the data and thevector table sections. In default condition, boot from bank 1 of Flash memory is selected. Italso supports to boot from bank 2 of Flash memory by setting a bit in option bytes.3.5 Power saving modesThe MCU supports three kinds of power saving modes to achieve even lower powerconsumption. They are Sleep mode, Deep-sleep mode, and Standby mode.These operatingmodes reduce the power consumption and allow the application to achieve the best balancebetween the CPU operating time, speed and power consumption.⏹Sleep modeIn sleep mode, only the clock of CPU core is off. All peripherals continue to operate andany interrupt/event can wake up the system.⏹Deep-sleep modeIn Deep-sleep mode, all clocks in the 1.2V domain are off, and all of the high speedcrystal oscillator (HSI, HSE) and PLL are disabled. Only the contents of SRAM andregisters are retained. Any interrupt or wakeup event from EXTI lines can wake up thesystem from the Deep-sleep mode including the 16 external lines, the RTC alarm, theLVD output, and USB wakeup. When exiting the Deep-sleep mode, the HSI is selectedas the system clock.⏹Standby modeIn Standby mode, the whole 1.2V domain is power off, the LDO is shut down, and all ofHSI, HSE and PLL are disabled.The contents of SRAM and registers (except BackupRegisters) are lost. There are four wakeup sources for the Standby mode, including theexternal reset from NRST pin, the RTC alarm, the IWDG reset, and the rising edge onWKUP pin.3.6 Analog to digital converter (ADC)⏹12-bit SAR ADC engine⏹Up to 1 MSPS conversion rate⏹Conversion range: V SSA to V DDA (2.6 to 3.6 V)⏹Temperature sensorUp to three 12-bit 1 μs multi-channel ADCs are integrated in the device. Each is a total of upto 21 multiplexed external channels. An analog watchdog block can be used to detect thechannels, which are required to remain within a specific threshold window. A configurablechannel management block of analog inputs also can be used to perform conversions insingle, continuous, scan or discontinuous mode to support more advanced usages.The ADCs can be triggered from the events generated by the general-purpose timers (TMx)and the advanced-control timers (TM1 and TM8) with internal connection. The temperaturesensor has to generate a voltage that varies linearly with temperature. The conversion rangeis between 2.6 V < V DDA< 3.6 V. The temperature sensor is internally connected to theADC_IN16 input channel which is used to convert the sensor output voltage into a digitalvalue.3.7 Digital to analog converter (DAC)⏹Two 12-bit DAC converters of independent output channel⏹8-bit or 12-bit mode in conjunction with the DMA controllerThe two 12-bit buffered DAC channels are used to generate variable analog outputs. TheDACs are designed with integrated resistor strings structure. The DAC channels can betriggered by the timer update outputs or EXTI with DMA support.In dual DAC channeloperation, conversions could be done independently or simultaneously. The maximumoutput value of the DAC is V REF+.3.8 DMA⏹7 channel DMA 1 controller and 5 channel DMA 2 controller⏹Peripherals supported: Timers, ADC, SPIs, I2Cs, USARTs, DAC, I2S⏹Dedicated DMA controller with the Ethernet applicationThe flexible general-purpose DMA controllers provide a hardware method of transferringdata between peripherals and/or memory without intervention from the CPU, thereby freeingup bandwidth for other system functions. Four types of access method are supported:peripheral to peripheral, peripheral to memory, memory to peripheral, memory to memoryEach channel is connected to fixed hardware DMA requests. The priorities of DMA channelrequests are determined by software configuration and hardware channel number.Transfersize of source and destination are independent and configurable.3.9 General-purpose inputs/outputs (GPIOs)⏹Up to 112 fast GPIOs, all mappable on 16 external interrupt vectors (EXTI)⏹Analog input/output configurable⏹Alternate function input/output configurableThere are up to 112 general purpose I/O pins (GPIO) in GD32F107xx, named PA0 ~ PA15and PB0 ~ PB15, PC0 ~ PC15, PD0 ~ PD15, PE0 ~ PE15, PF0-PF15, PG0-PG15 toimplement logic input/output functions. Each of the GPIO ports has related control andconfiguration registers to satisfy the requirements of specific applications. The externalinterrupts on the GPIO pins of the device have related control and configuration registers inthe External Interrupt Control Unit (EXTI). The GPIO ports are pin-shared with otheralternative functions (AFs) to obtain maximum flexibility on the package pins. Each of theGPIO pins can be configured by software as output (push-pull or open-drain), as input (withor without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins areshared with digital or analog alternate functions. All GPIOs are high-current capable exceptfor analog inputs.3.10 Timers and PWM generation⏹Up to two 16-bit advanced-control timer (TM1 & TM8), ten 16-bit general-purpose timers(GPTM), and two 16-bit basic timer (TM6 & TM7)⏹Up to 4 independent channels of PWM, output compare or input capture for each GPTMand external trigger input⏹16-bit, motor control PWM advanced-control timer with programmable dead-timegeneration for output match⏹Encoder interface controller with two inputs using quadrature decoder⏹24-bit SysTick timer down counter⏹ 2 watchdog timers (Independent watchdog and window watchdog)The advanced-control timer (TM1 & TM8) can be seen as a three-phase PWM multiplexedon 6 channels. It has complementary PWM outputs with programmable dead-timegeneration. It can also be used as a complete general-purpose timer. The 4 independentchannels can be used for⏹Input capture⏹Output compare⏹PWM generation (edge- or center-aligned counting modes)⏹Single pulse mode outputIf configured as a general-purpose 16-bit timer, it has the same functions as the TMx timer.Itcan be synchronized with external signals or to interconnect with other GPTMs togetherwhich have the same architecture and features.The general-purpose timer (GPTM), known as TM2 ~ TM5, TM9 ~ TM11, TM12 ~ TM14 canbe used for a variety of purposes including general time, input signal pulse widthmeasurement or output waveform generation such as a single pulse generation or PWMoutput, up to 4 independent channels for input capture/output compare. The GPTM alsosupports an encoder interface with two inputs using quadrature decoder.The basic timer, known as TM6 and TM7 are mainly used for DAC trigger generation. Theycan also be used as a simple 16-bit time base.The GD32F107xx have two watchdog peripherals, Independent watchdog and windowwatchdog. They offer a combination of high safety level, flexibility of use and timing accuracy.The independent watchdog timer includes a 12-bit down-counting counter and a 8-bitprescaler, It is clocked from an independent 40 kHz internal RC and as it operatesindependently of the main clock, it can operate in stop and standby modes.It can be usedeither as a watchdog to reset the device when a problem occurs, or as a free-running timerfor application timeout management.The window watchdog is based on a 7-bit down counter that can be set as free-running. Itcan be used as a watchdog to reset the device when a problem occurs. It is clocked from themain clock. It has an early warning interrupt capability and the counter can be frozen indebug mode.The SysTick timer is dedicated for OS, but could also be used as a standard down counter. Itfeatures:⏹ A 24-bit down counter⏹Auto reload capability⏹Maskable system interrupt generation when the counter reaches 0⏹Programmable clock source3.11 Real time clock (RTC)⏹32-bit up-counter with a programmable 20-bit prescaler⏹Alarm function⏹Interrupt and wake-up eventThe real time clock is an independent timer which provides a set of continuously runningcounters which can be used with suitable software to provide a clock calendar function, andprovides an alarm interrupt and an expected interrupt. The RTC features a 32-bitprogrammable counter for long-term measurement using the compare register to generatean alarm. A 20-bit prescaler is used for the time base clock and is by default configured togenerate a time base of 1 second from a clock at 32.768 kHz from external crystal oscillator.3.12 Inter-integrated circuit (I2C)⏹Up to two I2C bus interfaces can support both master and slave mode with a frequencyup to 400 kHz⏹Provide arbitration function, optional PEC (packet error checking) generation andchecking⏹Supports 7-bit and 10-bit addressing mode and general call addressing modeThe I2C interface is an internal circuit allowing communication with an external I2C interfacewhich is an industry standard two line serial interface used for connection to externalhardware. These two serial lines are known as a serial data line (SDA) and a serial clock line(SCL). The I2C module provides two data transfer rates: 100 kHz of standard mode or 400kHz of the fast mode. The I2C module also has an arbitration detect function to prevent thesituation where more than one master attempts to transmit data to the I2C bus at the sametime. A CRC-8 calculator is also provided in I2C interface to perform packet error checkingfor I2C data.3.13 Serial peripheral interface (SPI)⏹Up to two SPI interfaces with a frequency of up to 18 MHz⏹Support both master and slave mode⏹Hardware CRC calculation and transmit automatic CRC error checkingThe SPI interface uses 4 pins, among which are the serial data input and output lines (MISO& MOSI), the clock line (SCK) and the slave select line (NSS). Both SPIs can be served bythe DMA controller.The SPI interface may be used for a variety of purposes, includingsimplex synchronous transfers on two lines with a possible bidirectional data line or reliablecommunication using CRC checking.3.14 Universal synchronous asynchronous receiver transmitter(USART)⏹Up to three USARTs with operating frequency up to 4.5 MHz⏹Supports both asynchronous and clocked synchronous serial communication modes⏹IrDA SIR encoder and decoder support⏹LIN break generation and detection⏹USARTs support ISO 7816-3 compliant smart card interfaceThe USART (USART1, USART2 and USART3) are used to translate data between paralleland serial interfaces, provides a flexible full duplex data exchange using synchronous orasynchronous transfer. It is also commonly used for RS-232 standard communication. TheUSART includes a programmable baud rate generator which is capable of dividing thesystem clock to produce a dedicated clock for the USART transmitter and receiver.TheUSART also supports DMA function for high speed data communication except UART5.3.15 Inter-IC sound (I2S)⏹Two I2S bus Interfaces with sampling frequency from 8 kHz to 192 kHz⏹Support either master or slave modeThe Inter-IC sound (I2S) bus provides a standard communication interface for digital audioapplications by 3-wire serial lines. GD32F107xx contain two I2S-bus interfaces that can beoperated with 16/32 bit resolution in master or slave mode, pin multiplexed with SPI2 andSPI3. The audio sampling frequency from 8 kHz to 192 kHz is supported with less than 0.5%accuracy error.3.16 Universal serial bus on-the-go full-speed (USB OTG FS)⏹One USB device/host/OTG full-speed Interface with frequency up to 12 Mbit/s⏹Internal main PLL for USB CLK compliantlyThe Universal Serial Bus (USB) is a 4-wire bus with 4 bidirectional endpoints. The devicecontroller enables 12 Mbit/s data exchange with integrated transceivers in device/host/OTGmode. Full-speed peripheral is compliant with the USB 2.0 specification. Transactionformatting is performed by the hardware, including CRC generation and checking. The statusof a completed USB transfer or error condition is indicated by status registers. An interrupt isalso generated if enabled. The dedicated 48 MHz clock is generated from the internal mainPLL (the clock source must use a HSE crystal oscillator) and the operating frequency dividedfrom APB1 should be 12 MHz above.3.17 Controller area network (CAN)⏹Two CAN2.0B interface with communication frequency up to 1 Mbit/s⏹Internal main PLL for USB CLK compliantlyController area network (CAN) is a method for enabling serial communication in field bus.The CAN protocol has been used extensively in industrial automation and automotiveapplications. It can receive and transmit standard frames with 11-bit identifiers as well asextended frames with 29-bit identifiers. Each CAN has three mailboxes for transmission andtwo FIFOs of three message deep for reception.It also provides 14 scalable/configurableidentifier filter banks for selecting the incoming messages needed and discarding the others.3.18 Ethernet MAC interface⏹IEEE 802.3 compliant media access controller (MAC) for Ethernet LAN⏹10/100 Mbit/s rates with dedicated DMA controller and SRAM⏹Support hardware precision time protocol (PTP) with conformity to IEEE 1588The Ethernet media access controller (MAC) conforms to IEEE 802.3 specifications and fullysupports IEEE 1588 standards. The embedded MAC provides the interface to the requiredexternal network physical interface (PHY) for LAN bus connection via an internal mediaindependent interface (MII) or a reduced media independent interface (RMII). The number ofMII signals provided up to 17 with 25 MHz output and RMII up to 9 with 50 MHz output. Thefunction of 32-bit CRC checking is also available.3.19 External memory controller (EXMC)⏹Supported external memory: SRAM, PSRAM, ROM and NOR-Flash, NAND Flash andCF card⏹Up to 16-bit data bus⏹Support to interface with Motorola 6800 and Intel 8080 type LCD directlyExternal memory controller (EXMC) is an abbreviation of external memory controller. It isdivided in to several sub-banks for external device support, each sub-bank has its own chipselection signal but at one time, only one bank can be accessed. The EXMC support codeexecution from external memory except NAND Flash and CF card. The EXMC also can beconfigured to interface with the most common LCD module of Motorola 6800 and Intel 8080series and reduce the system cost and complexity.3.20 Debug mode⏹Serial wire JTAG debug port (SWJ-DP)The ARM® SWJ-DP Interface is embedded and is a combined JTAG and serial wire debugport that enables either a serial wire debug or a JTAG probe to be connected to the target.3.21 Package and operation temperature⏹LQFP144 (GD32F107Zx), LQFP100 (GD32F107Vx), LQFP64 (GD32F107Rx)⏹Operation temperature range: -40°C to +85°C (industrial level)。