74LVC3G34DC中文资料

7413中文资料

100

VDS VGS RG

RD D.U.T.

10V

Pulse Width ≤ 1 µs Duty Factor ≤ 0.1 %

+-VDD

Fig 10a. Switching Time Test Circuit

VDS 90%

10% VGS

td(on) tr

td(off) tf

Fig 10b. Switching Time Waveforms

tr td(off) tf Ciss

Rise Time Turn-Off Delay Time Fall Time Input Capacitance

––– 8.0 ––– ns ID = 7.2A

––– 35 –––

RG = 6.2Ω

––– 14 –––

VGS = 10V

––– 1670 –––

Benefits

l Low Gate to Drain Charge to Reduce

S

1

Switching Losses

l Fully Characterized Capacitance Including S 2

AA

8

D

7

D

Effective COSS to Simplify Design, (See

Max. 12 9.6 96 2.5 0.02 ± 20 1.0

-55 to + 150

300 (1.6mm from case )

Units

A

W W/°C

V V/ns

°C

Thermal Resistance

Symbol RθJL RθJA

Parameter Junction-to-Drain Lead Junction-to-Ambient

HD74ALVC2G240US资料

Item Propagation delay time Enable time Disable time

•

VCC = 1.5±0.1 V

Symbol tPLH tPHL tZH tZL tHZ tLZ Min 2.0 2.0 2.0 Typ Max 7.0 7.0 7.0 Unit ns ns ns Test conditions CL = 15 pF CL = 15 pF CL = 15 pF FROM (Input) A OE OE TO (Output) Y Y Y

Rev.1, Jan. 2002, page 5 of 13

HD74ALVC2G240

Switching Characteristics

(Ta = −40 to 85°C) • VCC = 1.2 V

Symbol tPLH tPHL tZH tZL tHZ tLZ Min Typ 5.5 6.5 4.5 Max Unit ns ns ns Test conditions CL = 15 pF CL = 15 pF CL = 15 pF FROM (Input) A OE OE TO (Output) Y Y Y

mA mA mA mA mW °C

VI < 0 VO < 0 or VO > VCC VO = 0 to VCC

The absolute maximum ratings are values which must not individually be exceeded, and furthermore, no two of which may be realized at the same time. 1. The input and output voltage ratings may be exceeded if the input and output clamp-current ratings are observed. 2. This value is limited to 4.6 V maximum. 3. The maximum package power dissipation was calculated using a junction temperature of 150°C.

74LVC1G32GF中文资料

For XSON6 packages: above 45 °C the value of Ptot derates linearly with 2.4 mW/K.

9. Recommended operating conditions

Table 6. Symbol VCC VI VO

Tamb ∆t/∆V

SOT353-1

SOT753 SOT886

SOT891

Table 2. Marking Type number 74LVC1G32GW 74LVC1G32GV 74LVC1G32GM 74LVC1G32GF

5. Functional diagram

Marking code VG V32 VG VG

1B 2A

元器件交易网

74LVC1G32

Single 2-input OR gate

Rev. 06 — 2 August 2007

Product data sheet

1. General description

The 74LVC1G32 provides one 2-input OR function.

plastic surface-mounted package; 5 leads

plastic extremely thin small outline package; no leads; 6 terminals; body 1 × 1.45 × 0.5 mm

74LVC3G34三路缓冲器产品数据手册说明书

74LVC3G34Triple bufferRev. 13 — 26 October 2018Product data sheet1. General descriptionThe 74LVC3G34 provides three buffers.The inputs can be driven from either 3.3 V or 5 V devices. This feature allows the use of the74LVC3G34 as a translator in a mixed 3.3 V and 5 V environment.This device is fully specified for partial power-down applications using I OFF. The I OFF circuitrydisables the output, preventing a damaging backflow current through the device when it is powereddown.2. Features and benefits•Wide supply voltage range from 1.65 V to 5.5 V• 5 V tolerant input/output for interfacing with 5 V logic•High noise immunity•Complies with JEDEC standard:•JESD8-7 (1.65 V to 1.95 V)•JESD8-5 (2.3 V to 2.7 V)•JESD8B/JESD36 (2.7 V to 3.6 V)•ESD protection:•HBM JESD22-A114F exceeds 2000 V•MM JESD22-A115-A exceeds 200 V•±24 mA output drive (V CC = 3.0 V)•CMOS low power consumption•Latch-up performance exceeds 250 mA•Direct interface with TTL levels•Multiple package options•Specified from -40 °C to +85 °C and -40 °C to +125 °C3. Ordering information4. Marking[1]The pin 1 indicator is located on the lower left corner of the device, below the marking code.5. Functional diagram001aah8421A 1Y3Y 3A 2A2YFig. 1.Logic symbol 11001aah8431Fig. 2.IEC logic symbol 001aac536YA Fig. 3.Logic diagram (one gate)6. Pinning information6.1. Pinning74LVC3G341A V CC 3Y 1Y 2A 3A GND2Y001aaa60912346587Fig. 4.Pin configuration SOT505-2 (TSSOP8) and SOT765-1 (VSSOP8)74LVC3G343A1YV CC2Y2A3Y1A GND 001aac02436271845T ransparent top viewFig. 5.Pin configuration SOT833-1, SOT1089,SOT1116 and SOT1203 (XSON8)001aag0833Y3A1AV C C2A1YG N D 2Y Transparent top view36415872terminal 1 index area74LVC3G34Fig. 6.Pin configuration SOT902-2 (XQFN8)6.2. Pin description7. Functional descriptionTable 4. Function tableH = HIGH voltage level; L = LOW voltage level.8. Limiting valuesTable 5. Limiting valuesIn accordance with the Absolute Maximum Rating System (IEC 60134). Voltages are referenced to GND (ground = 0 V).[1]The minimum input and output voltage ratings may be exceeded if the input and output current ratings are observed.[2]For TSSOP8 package: above 55 °C the value of P tot derates linearly with 2.5 mW/K.For VSSOP8 package: above 110 °C the value of P tot derates linearly with 8 mW/K.For XSON8, XQFN8 packages: above 118 °C the value of P tot derates linearly with 7.8 mW/K.9. Recommended operating conditions10. Static characteristicsTable 7. Static characteristicsAt recommended operating conditions; voltages are referenced to GND (ground = 0 V).[1]All typical values are measured at V CC = 3.3 V and T amb = 25 °C.11. Dynamic characteristicsTable 8. Dynamic characteristicsVoltages are referenced to GND (ground = 0 V); for test circuit see Fig. 8.[1]Typical values are measured at T amb = 25 °C and V CC = 1.8 V, 2.5 V, 2.7 V, 3.3 V and 5.0 V respectively.[2]t pd is the same as t PLH and t PHL.[3]C PD is used to determine the dynamic power dissipation (P D in μW).P D = C PD × V CC2 × f i × N + Σ(C L × V CC2 × f o) where:f i = input frequency in MHz;f o = output frequency in MHz;C L = output load capacitance in pF;V CC = supply voltage in V;N = number of inputs switching;Σ(C L × V CC2 × f o) = sum of outputs.11.1. Waveforms and test circuit12. Package outlineTSSOP8: plastic thin shrink small outline package; 8 leads; body width 3 mm; lead length 0.5 mm SOT505-2Fig. 9.Package outline SOT505-2 (TSSOP8)Fig. 10.Package outline SOT765-1 (VSSOP8)Fig. 11.Package outline SOT833-1 (XSON8)XSON8: extremely thin small outline package; no leads;Fig. 12.Package outline SOT1089 (XSON8)XQFN8: plastic, extremely thin quad flat package; no leads;Fig. 13.Package outline SOT902-2 (XQFN8)XSON8: extremely thin small outline package; no leads;Fig. 14.Package outline SOT1116 (XSON8)XSON8: extremely thin small outline package; no leads;Fig. 15.Package outline SOT1203 (XSON8)13. Abbreviations14. Revision history15. Legal informationData sheet status[1]Please consult the most recently issued document before initiating orcompleting a design.[2]The term 'short data sheet' is explained in section "Definitions".[3]The product status of device(s) described in this document may havechanged since this document was published and may differ in case ofmultiple devices. The latest product status information is available onthe internet at https://.DefinitionsDraft — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. Nexperia does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information. Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local Nexperia sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.Product specification — The information and data provided in a Product data sheet shall define the specification of the product as agreed between Nexperia and its customer, unless Nexperia and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the Nexperia product is deemed to offer functions and qualities beyond those described in the Product data sheet.DisclaimersLimited warranty and liability — Information in this document is believedto be accurate and reliable. However, Nexperia does not give any representations or warranties, expressed or implied, as to the accuracyor completeness of such information and shall have no liability for the consequences of use of such information. Nexperia takes no responsibility for the content in this document if provided by an information source outside of Nexperia.In no event shall Nexperia be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removalor replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.Notwithstanding any damages that customer might incur for any reason whatsoever, Nexperia’s aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of Nexperia.Right to make changes — Nexperia reserves the right to make changesto information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.Suitability for use — Nexperia products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunctionof an Nexperia product can reasonably be expected to result in personal injury, death or severe property or environmental damage. Nexperia and its suppliers accept no liability for inclusion and/or use of Nexperia products in such equipment or applications and therefore such inclusion and/or use is at the customer’s own risk.Quick reference data — The Quick reference data is an extract of the product data given in the Limiting values and Characteristics sections of this document, and as such is not complete, exhaustive or legally binding. Applications — Applications that are described herein for any of these products are for illustrative purposes only. Nexperia makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.Customers are responsible for the design and operation of their applications and products using Nexperia products, and Nexperia accepts no liability for any assistance with applications or customer product design. It is customer’s sole responsibility to determine whether the Nexperia product is suitableand fit for the customer’s applications and products planned, as well asfor the planned application and use of customer’s third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products. Nexperia does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer’s applications or products, or the application or use by customer’s third party customer(s). Customer is responsible for doing all necessary testing for the customer’s applications and products using Nexperia products in order to avoid a default of the applications and the products or of the application or use by customer’s third party customer(s). Nexperia does not accept any liability in this respect.Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above thosegiven in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.Terms and conditions of commercial sale — Nexperia products aresold subject to the general terms and conditions of commercial sale, as published at /profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. Nexperia hereby expressly objects to applying the customer’s general terms and conditions with regard to the purchase of Nexperia products by customer.No offer to sell or license — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.Export control — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.Non-automotive qualified products — Unless this data sheet expressly states that this specific Nexperia product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. Nexperia accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without Nexperia’s warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond Nexperia’s specifications such use shall be solely at customer’s own risk, and (c) customer fully indemnifies Nexperia for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond Nexperia’s standard warranty and Nexperia’s product specifications.Translations — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.TrademarksNotice: All referenced brands, product names, service names and trademarks are the property of their respective owners.Contents1. General description (1)2. Features and benefits (1)3. Ordering information (2)4. Marking (2)5. Functional diagram (2)6. Pinning information (3)6.1. Pinning (3)6.2. Pin description (3)7. Functional description (3)8. Limiting values (4)9. Recommended operating conditions (4)10. Static characteristics (5)11. Dynamic characteristics (6)11.1. Waveforms and test circuit (7)12. Package outline (8)13. Abbreviations (15)14. Revision history (15)15. Legal information (16)© Nexperia B.V. 2018. All rights reservedFor more information, please visit: Forsalesofficeaddresses,pleasesendanemailto:*************************** Date of release: 26 October 2018Mouser ElectronicsAuthorized DistributorClick to View Pricing, Inventory, Delivery & Lifecycle Information:N experia:74LVC3G34GD,12574LVC3G34GN,11574LVC3G34GS,11574LVC3G34DC,12574LVC3G34DP,125 74LVC3G34GM,12574LVC3G34GT,11574LVC3G34GF,115。

74ls74中文资料

74ls74中文资料74LS74内含两个独立的D上升沿双d触发器,每个触发器有数据输入(D)、置位输入()复位输入()、时钟输入(CP)和数据输出(Q、)。

、的低电平使输出预置或清除,而与其它输入端的电平无关。

当、均无效(高电平式)时,符合建立时间要求的D数据在CP上升沿作用下传送到输出端。

74ls74功能表:输入输出S D R D CP D Qn+1 Qn+10 1 ×× 1 01 0 ××0 10 0 ××φ φ1 1 ↑ 1 1 01 1 ↑0 0 11 1 ↓×Qn Qn图1 74ls74引脚图实验:用74LS74构成4位寄存器一个D触发器可实现一位二进数的存储,因此应采用4个D触发器实现4位寄存器。

由于要实现移位寄存,4个D触发器之间应相互联接。

(1)首先在图2中完成相应的联线,构成可实现并入并出、串入串出、并入串出、串入并出的多功能移位寄存。

按图接好电路。

(2) D3 D2 D1 D0分别接逻辑开关,Q3 Q2 Q1 Q0接发光二极管;(3) 先清零;(4) 按下列要求,实现相应功能,观察结果,并描述工作过程。

并入并出:使数据输入端D3D2D1D0=1011,给CP端输入一个正单脉冲,观察Q3Q2Q1Q0发光二极管的状态,、将结果填入表中。

并入串出:使数据输入端D3D2D1D0=1011,给CP端输入4个正单脉冲,观察Q3端发光二极管的状态,将结果填入表6中。

串入并出:使数据输入端D0分别为1011,同时通过给CP端输入正单脉冲将D0端的4 个数据送入寄存器。

观察Q3Q2Q1Q0端发光二极管的状态,将结果填入表中。

串入串出:使数据输入端D0分别为1011,同时通过给CP端输入正单脉冲,将D0端的4 个数据送入寄存器。

在CP端输完8个脉冲后,观察Q3端发光二极管的状态,将结果填入表2中。

并入并出:D3D2D1D0=10111个CP脉冲Q3Q2Q1Q0=结论:并入串出D3D2D1D0=10114个CP脉冲Q3=结论串入并出D3=10114个CP脉冲Q3Q2Q1Q0=结论串入串出D3=10118个CP脉冲Q3=结论图274ls153芯片管脚图引脚逻辑功能以及封装2007年12月17日 23:53 本站原创作者:本站用户评论()关键字:74ls153管脚图逻辑功能图封装:74LS163引脚功能表及管脚定义图(带时序波形图)发布:2011-08-30 | 作者: | 来源: huangjiapeng| 查看:2620次 | 用户关注:定时器由与系统秒脉冲(由时钟脉冲产生器提供)同步的计数器构成,要求计数器在状态信号ST作用下,首先清零,然后在时钟脉冲上升沿作用下,计数器从零开始进行增1计数,向控制器提供模5的定时信号TY和模25的定时信号TL。

74系列芯片标准数字电路资料

74系列芯片标准数字电路资料-功能大全一.74系列芯片标准数字电路资料-功能大全二。

74系列芯片资料三.74HC/LS/HCT/F系列芯片的区别四.逻辑电平介绍TTL,CMOS五.74HC244与245作用与区别六.74芯片分类总汇一.74系列芯片标准数字电路资料-功能大全7400 TTL 2输入端四与非门7401 TTL 集电极开路2输入端四与非门7402 TTL 2输入端四或非门7403 TTL 集电极开路2输入端四与非门7404 TTL 六反相器7405 TTL 集电极开路六反相器7406 TTL 集电极开路六反相高压驱动器7407 TTL 集电极开路六正相高压驱动器7408 TTL 2输入端四与门7409 TTL 集电极开路2输入端四与门7410 TTL 3输入端3与非门74107 TTL 带清除主从双J-K触发器74109 TTL 带预置清除正触发双J-K触发器7411 TTL 3输入端3与门74112 TTL 带预置清除负触发双J-K触发器7412 TTL 开路输出3输入端三与非门74121 TTL 单稳态多谐振荡器74122 TTL 可再触发单稳态多谐振荡器74123 TTL 双可再触发单稳态多谐振荡器74125 TTL 三态输出高有效四总线缓冲门74126 TTL 三态输出低有效四总线缓冲门7413 TTL 4输入端双与非施密特触发器74132 TTL 2输入端四与非施密特触发器74133 TTL 13输入端与非门74136 TTL 四异或门74138 TTL 3-8线译码器/复工器74139 TTL 双2-4线译码器/复工器7414 TTL 六反相施密特触发器74145 TTL BCD—十进制译码/驱动器7415 TTL 开路输出3输入端三与门74150 TTL 16选1数据选择/多路开关74151 TTL 8选1数据选择器74153 TTL 双4选1数据选择器74154 TTL 4线—16线译码器74155 TTL 图腾柱输出译码器/分配器74156 TTL 开路输出译码器/分配器74157 TTL 同相输出四2选1数据选择器74158 TTL 反相输出四2选1数据选择器7416 TTL 开路输出六反相缓冲/驱动器74160 TTL 可预置BCD异步清除计数器74161 TTL 可予制四位二进制异步清除计数器74162 TTL 可预置BCD同步清除计数器74163 TTL 可予制四位二进制同步清除计数器74164 TTL 八位串行入/并行输出移位寄存器74165 TTL 八位并行入/串行输出移位寄存器74166 TTL 八位并入/串出移位寄存器74169 TTL 二进制四位加/减同步计数器7417 TTL 开路输出六同相缓冲/驱动器74170 TTL 开路输出4×4寄存器堆74173 TTL 三态输出四位D型寄存器74174 TTL 带公共时钟和复位六D触发器74175 TTL 带公共时钟和复位四D触发器74180 TTL 9位奇数/偶数发生器/校验器74181 TTL 算术逻辑单元/函数发生器74185 TTL 二进制—BCD代码转换器74190 TTL BCD同步加/减计数器74191 TTL 二进制同步可逆计数器74192 TTL 可预置BCD双时钟可逆计数器74193 TTL 可预置四位二进制双时钟可逆计数器74194 TTL 四位双向通用移位寄存器74195 TTL 四位并行通道移位寄存器74196 TTL 十进制/二-十进制可预置计数锁存器74197 TTL 二进制可预置锁存器/计数器7420 TTL 4输入端双与非门7421 TTL 4输入端双与门7422 TTL 开路输出4输入端双与非门74221 TTL 双/单稳态多谐振荡器74240 TTL 八反相三态缓冲器/线驱动器74241 TTL 八同相三态缓冲器/线驱动器74243 TTL 四同相三态总线收发器74244 TTL 八同相三态缓冲器/线驱动器74245 TTL 八同相三态总线收发器74247 TTL BCD—7段15V输出译码/驱动器74248 TTL BCD—7段译码/升压输出驱动器74249 TTL BCD—7段译码/开路输出驱动器74251 TTL 三态输出8选1数据选择器/复工器74253 TTL 三态输出双4选1数据选择器/复工器74256 TTL 双四位可寻址锁存器74257 TTL 三态原码四2选1数据选择器/复工器74258 TTL 三态反码四2选1数据选择器/复工器74259 TTL 八位可寻址锁存器/3-8线译码器7426 TTL 2输入端高压接口四与非门74260 TTL 5输入端双或非门74266 TTL 2输入端四异或非门7427 TTL 3输入端三或非门74273 TTL 带公共时钟复位八D触发器74279 TTL 四图腾柱输出S-R锁存器7428 TTL 2输入端四或非门缓冲器74283 TTL 4位二进制全加器74290 TTL 二/五分频十进制计数器74293 TTL 二/八分频四位二进制计数器74295 TTL 四位双向通用移位寄存器74298 TTL 四2输入多路带存贮开关74299 TTL 三态输出八位通用移位寄存器7430 TTL 8输入端与非门7432 TTL 2输入端四或门74322 TTL 带符号扩展端八位移位寄存器74323 TTL 三态输出八位双向移位/存贮寄存器7433 TTL 开路输出2输入端四或非缓冲器74347 TTL BCD—7段译码器/驱动器74352 TTL 双4选1数据选择器/复工器74353 TTL 三态输出双4选1数据选择器/复工器74365 TTL 门使能输入三态输出六同相线驱动器74365 TTL 门使能输入三态输出六同相线驱动器74366 TTL 门使能输入三态输出六反相线驱动器74367 TTL 4/2线使能输入三态六同相线驱动器74368 TTL 4/2线使能输入三态六反相线驱动器7437 TTL 开路输出2输入端四与非缓冲器74373 TTL 三态同相八D锁存器74374 TTL 三态反相八D锁存器74375 TTL 4位双稳态锁存器74377 TTL 单边输出公共使能八D锁存器74378 TTL 单边输出公共使能六D锁存器74379 TTL 双边输出公共使能四D锁存器7438 TTL 开路输出2输入端四与非缓冲器74380 TTL 多功能八进制寄存器7439 TTL 开路输出2输入端四与非缓冲器74390 TTL 双十进制计数器74393 TTL 双四位二进制计数器7440 TTL 4输入端双与非缓冲器7442 TTL BCD—十进制代码转换器74352 TTL 双4选1数据选择器/复工器74353 TTL 三态输出双4选1数据选择器/复工器74365 TTL 门使能输入三态输出六同相线驱动器74366 TTL 门使能输入三态输出六反相线驱动器74367 TTL 4/2线使能输入三态六同相线驱动器74368 TTL 4/2线使能输入三态六反相线驱动器7437 TTL 开路输出2输入端四与非缓冲器74373 TTL 三态同相八D锁存器74374 TTL 三态反相八D锁存器74375 TTL 4位双稳态锁存器74377 TTL 单边输出公共使能八D锁存器74378 TTL 单边输出公共使能六D锁存器74379 TTL 双边输出公共使能四D锁存器7438 TTL 开路输出2输入端四与非缓冲器74380 TTL 多功能八进制寄存器7439 TTL 开路输出2输入端四与非缓冲器74390 TTL 双十进制计数器74393 TTL 双四位二进制计数器7440 TTL 4输入端双与非缓冲器7442 TTL BCD—十进制代码转换器74447 TTL BCD—7段译码器/驱动器7445 TTL BCD—十进制代码转换/驱动器74450 TTL 16:1多路转接复用器多工器74451 TTL 双8:1多路转接复用器多工器74453 TTL 四4:1多路转接复用器多工器7446 TTL BCD—7段低有效译码/驱动器74460 TTL 十位比较器74461 TTL 八进制计数器74465 TTL 三态同相2与使能端八总线缓冲器74466 TTL 三态反相2与使能八总线缓冲器74467 TTL 三态同相2使能端八总线缓冲器74468 TTL 三态反相2使能端八总线缓冲器74469 TTL 八位双向计数器7447 TTL BCD—7段高有效译码/驱动器7448 TTL BCD—7段译码器/内部上拉输出驱动74490 TTL 双十进制计数器74491 TTL 十位计数器74498 TTL 八进制移位寄存器7450 TTL 2-3/2-2输入端双与或非门74502 TTL 八位逐次逼近寄存器74503 TTL 八位逐次逼近寄存器7451 TTL 2-3/2-2输入端双与或非门74533 TTL 三态反相八D锁存器74534 TTL 三态反相八D锁存器7454 TTL 四路输入与或非门74540 TTL 八位三态反相输出总线缓冲器7455 TTL 4输入端二路输入与或非门74563 TTL 八位三态反相输出触发器74564 TTL 八位三态反相输出D触发器74573 TTL 八位三态输出触发器74574 TTL 八位三态输出D触发器74645 TTL 三态输出八同相总线传送接收器74670 TTL 三态输出4×4寄存器堆7473 TTL 带清除负触发双J-K触发器7474 TTL 带置位复位正触发双D触发器7476 TTL 带预置清除双J-K触发器7483 TTL 四位二进制快速进位全加器7485 TTL 四位数字比较器7486 TTL 2输入端四异或门7490 TTL 可二/五分频十进制计数器7493 TTL 可二/八分频二进制计数器7495 TTL 四位并行输入\\输出移位寄存器7497 TTL 6位同步二进制乘法器二。

74系列中文资料(非常全)

74系列芯片资料反相器驱动器LS04 LS05 LS06 LS07 LS125 LS240 LS244 LS245与门与非门LS00 LS08 LS10 LS11 LS20 LS21 LS27 LS30 LS38或门或非门与或非门LS02 LS32 LS51 LS64 LS65异或门比较器LS86译码器LS138 LS139寄存器LS74 LS175 LS373反相器:Vcc 6A 6Y 5A 5Y 4A 4Y 六非门74LS04┌┴─┴─┴─┴─┴─┴─┴┐六非门(OC门) 74LS05 _ │14 13 12 11 10 9 8│六非门(OC高压输出) 74LS06 Y = A )││1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1Y 2A 2Y 3A 3Y GND驱动器:Vcc 6A 6Y 5A 5Y 4A 4Y┌┴─┴─┴─┴─┴─┴─┴┐│14 13 12 11 10 9 8│Y = A )│六驱动器(OC高压输出) 74LS07 │1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1Y 2A 2Y 3A 3Y GNDVcc -4C 4A 4Y -3C 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐_ │14 13 12 11 10 9 8│Y =A+C )│四总线三态门74LS125 │1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘-1C 1A 1Y -2C 2A 2Y GNDVcc -G B1 B2 B3 B4 B8 B6 B7 B8┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐8位总线驱动器74LS245 │20 19 18 17 16 15 14 13 12 11│)│DIR=1 A=>B│1 2 3 4 5 6 7 8 9 10│DIR=0 B=>A└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘DIR A1 A2 A3 A4 A5 A6 A7 A8 GND正逻辑与门,与非门:Vcc 4B 4A 4Y 3B 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐│14 13 12 11 10 9 8│Y = AB )│2输入四正与门74LS08 │1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1B 1Y 2A 2B 2Y GNDVcc 4B 4A 4Y 3B 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐__ │14 13 12 11 10 9 8│Y = AB )│2输入四正与非门74LS00 │1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1B 1Y 2A 2B 2Y GNDVcc 1C 1Y 3C 3B 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐___ │14 13 12 11 10 9 8│Y = ABC )│3输入三正与非门74LS10 │1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1B 2A 2B 2C 2Y GNDVcc H G Y┌┴─┴─┴─┴─┴─┴─┴┐│14 13 12 11 10 9 8│)│8输入与非门74LS30│1 2 3 4 5 6 7│________└┬─┬─┬─┬─┬─┬─┬┘Y = ABCDEFGHA B C D E F GND正逻辑或门,或非门:Vcc 4B 4A 4Y 3B 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐2输入四或门74LS32│14 13 12 11 10 9 8│)│Y = A+B│1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1B 1Y 2A 2B 2Y GNDVcc 4Y 4B 4A 3Y 3B 3A┌┴─┴─┴─┴─┴─┴─┴┐2输入四或非门74LS02│14 13 12 11 10 9 8│___)│Y = A+B│1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1Y 1A 1B 2Y 2A 2B GNDVcc 2Y 2B 2A 2D 2E 1F┌┴─┴─┴─┴─┴─┴─┴┐双与或非门74S51│14 13 12 11 10 9 8│_____)│2Y = AB+DE│1 2 3 4 5 6 7│_______└┬─┬─┬─┬─┬─┬─┬┘1Y = ABC+DEF1Y 1A 1B 1C 1D 1E GNDVcc D C B K J Y┌┴─┴─┴─┴─┴─┴─┴┐4-2-3-2与或非门74S64 74S65(OC门) │14 13 12 11 10 9 8│______________)│Y = ABCD+EF+GHI+JK│1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘A E F G H I GND页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器2输入四异或门74LS86Vcc 4B 4A 4Y 3Y 3B 3A┌┴─┴─┴─┴─┴─┴─┴┐│14 13 12 11 10 9 8│)│_ _│1 2 3 4 5 6 7│Y=AB+AB└┬─┬─┬─┬─┬─┬─┬┘1A 1B 1Y 2Y 2A 2B GND8*2输入比较器74LS688_Vcc Y B8 A8 B7 A7 B6 A6 B5 A5┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐8*2输入比较器74LS688│20 19 18 17 16 15 14 13 12 11│)││1 2 3 4 5 6 7 8 9 10│└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘CE A1 B1 A2 B2 A3 B3 A4 B4 GND_Y=A1⊙B1+A2⊙B2+A3⊙B3+A4⊙B4+A5⊙B5+A6⊙B6+A7⊙B7+A8⊙B83-8译码器74LS138Vcc -Y0 -Y1 -Y2 -Y3 -Y4 -Y5 -Y6 __ _ _ _ __ _ _ __ _ _ __ _┌┴─┴─┴─┴─┴─┴─┴─┴┐Y0=A B C Y1=A B C Y2=A B C Y3=A B C│16 15 14 13 12 11 10 9 │)│__ _ _ __ _ __ _ __│1 2 3 4 5 6 7 8│Y4=A B C Y5=A B C Y6=A B C Y7=A B C└┬─┬─┬─┬─┬─┬─┬─┬┘A B C -CS0 -CS1 CS2 -Y7 GND双2-4译码器74LS139Vcc -2G 2A 2B -Y0 -Y1 -Y2 -Y3 __ __ __ __ __ __ __ __┌┴─┴─┴─┴─┴─┴─┴─┴┐Y0=2A 2B Y1=2A 2B Y2=2A 2B Y3=2A 2B│16 15 14 13 12 11 10 9 │)│__ __ __ __ __ __ __ __│ 1 2 3 4 5 6 7 8│Y0=1A 1B Y1=1A 1B Y2=1A 1B Y3=1A 1B└┬─┬─┬─┬─┬─┬─┬─┬┘-1G 1A 1B -Y0 -Y1 -Y2 -Y3 GND8*2输入比较器74LS688_Vcc Y B8 A8 B7 A7 B6 A6 B5 A5┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐8*2输入比较器74LS688 │20 19 18 17 16 15 14 13 12 11│)││1 2 3 4 5 6 7 8 9 10│└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘CE A1 B1 A2 B2 A3 B3 A4 B4 GND_Y=A1⊙B1+A2⊙B2+A3⊙B3+A4⊙B4+A5⊙B5+A6⊙B6+A7⊙B7+A8⊙B8寄存器:Vcc 2CR 2D 2Ck 2St 2Q -2Q┌┴─┴─┴─┴─┴─┴─┴┐双D触发器74LS74│14 13 12 11 10 9 8 │)││1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1Cr 1D 1Ck 1St 1Q -1Q GNDVcc 8Q 8D 7D 7Q 6Q 6D 5D 5Q ALE┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐8位锁存器74LS373│20 19 18 17 16 15 14 13 12 11│)││1 2 3 4 5 6 7 8 9 10│└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘-OE 1Q 1D 2D 2Q 3Q 3D 4D 4Q GND--------------------------------------------------------------------------------常见数字逻辑器件中文注解74系列:74LS00 TTL 2输入端四与非门74LS01 TTL 集电极开路2输入端四与非门74LS02 TTL 2输入端四或非门74LS03 TTL 集电极开路2输入端四与非门74LS04 TTL 六反相器74LS05 TTL 集电极开路六反相器74LS06 TTL 集电极开路六反相高压驱动器74LS07 TTL 集电极开路六正相高压驱动器74LS08 TTL 2输入端四与门74LS09 TTL 集电极开路2输入端四与门74LS10 TTL 3输入端3与非门74LS107 TTL 带清除主从双J-K触发器74LS109 TTL 带预置清除正触发双J-K触发器74LS11 TTL 3输入端3与门74LS112 TTL 带预置清除负触发双J-K触发器74LS12 TTL 开路输出3输入端三与非门74LS121 TTL 单稳态多谐振荡器74LS122 TTL 可再触发单稳态多谐振荡器74LS123 TTL 双可再触发单稳态多谐振荡器74LS125 TTL 三态输出高有效四总线缓冲门74LS126 TTL 三态输出低有效四总线缓冲门74LS13 TTL 4输入端双与非施密特触发器74LS132 TTL 2输入端四与非施密特触发器74LS133 TTL 13输入端与非门74LS136 TTL 四异或门74LS138 TTL 3-8线译码器/复工器74LS139 TTL 双2-4线译码器/复工器74LS14 TTL 六反相施密特触发器74LS145 TTL BCD—十进制译码/驱动器74LS15 TTL 开路输出3输入端三与门74LS150 TTL 16选1数据选择/多路开关74LS151 TTL 8选1数据选择器74LS153 TTL 双4选1数据选择器74LS154 TTL 4线—16线译码器74LS155 TTL 图腾柱输出译码器/分配器74LS156 TTL 开路输出译码器/分配器74LS157 TTL 同相输出四2选1数据选择器74LS158 TTL 反相输出四2选1数据选择器74LS16 TTL 开路输出六反相缓冲/驱动器74LS160 TTL 可预置BCD异步清除计数器74LS161 TTL 可予制四位二进制异步清除计数器74LS162 TTL 可预置BCD同步清除计数器74LS163 TTL 可予制四位二进制同步清除计数器74LS164 TTL 八位串行入/并行输出移位寄存器74LS165 TTL 八位并行入/串行输出移位寄存器74LS166 TTL 八位并入/串出移位寄存器74LS169 TTL 二进制四位加/减同步计数器74LS17 TTL 开路输出六同相缓冲/驱动器74LS170 TTL 开路输出4×4寄存器堆74LS173 TTL 三态输出四位D型寄存器74LS174 TTL 带公共时钟和复位六D触发器74LS175 TTL 带公共时钟和复位四D触发器74LS180 TTL 9位奇数/偶数发生器/校验器74LS181 TTL 算术逻辑单元/函数发生器74LS185 TTL 二进制—BCD代码转换器74LS190 TTL BCD同步加/减计数器74LS191 TTL 二进制同步可逆计数器74LS192 TTL 可预置BCD双时钟可逆计数器74LS193 TTL 可预置四位二进制双时钟可逆计数器74LS194 TTL 四位双向通用移位寄存器74LS195 TTL 四位并行通道移位寄存器74LS196 TTL 十进制/二-十进制可预置计数锁存器74LS197 TTL 二进制可预置锁存器/计数器74LS20 TTL 4输入端双与非门74LS21 TTL 4输入端双与门74LS22 TTL 开路输出4输入端双与非门74LS221 TTL 双/单稳态多谐振荡器74LS240 TTL 八反相三态缓冲器/线驱动器74LS241 TTL 八同相三态缓冲器/线驱动器74LS243 TTL 四同相三态总线收发器74LS244 TTL 八同相三态缓冲器/线驱动器74LS245 TTL 八同相三态总线收发器74LS247 TTL BCD—7段15V输出译码/驱动器74LS248 TTL BCD—7段译码/升压输出驱动器74LS249 TTL BCD—7段译码/开路输出驱动器74LS251 TTL 三态输出8选1数据选择器/复工器74LS253 TTL 三态输出双4选1数据选择器/复工器74LS256 TTL 双四位可寻址锁存器74LS257 TTL 三态原码四2选1数据选择器/复工器74LS258 TTL 三态反码四2选1数据选择器/复工器74LS259 TTL 八位可寻址锁存器/3-8线译码器74LS26 TTL 2输入端高压接口四与非门74LS260 TTL 5输入端双或非门74LS266 TTL 2输入端四异或非门74LS27 TTL 3输入端三或非门74LS273 TTL 带公共时钟复位八D触发器74LS279 TTL 四图腾柱输出S-R锁存器74LS28 TTL 2输入端四或非门缓冲器74LS283 TTL 4位二进制全加器74LS290 TTL 二/五分频十进制计数器74LS293 TTL 二/八分频四位二进制计数器74LS295 TTL 四位双向通用移位寄存器74LS298 TTL 四2输入多路带存贮开关74LS299 TTL 三态输出八位通用移位寄存器74LS30 TTL 8输入端与非门74LS32 TTL 2输入端四或门74LS322 TTL 带符号扩展端八位移位寄存器74LS323 TTL 三态输出八位双向移位/存贮寄存器74LS33 TTL 开路输出2输入端四或非缓冲器74LS347 TTL BCD—7段译码器/驱动器74LS352 TTL 双4选1数据选择器/复工器74LS353 TTL 三态输出双4选1数据选择器/复工器74LS365 TTL 门使能输入三态输出六同相线驱动器74LS365 TTL 门使能输入三态输出六同相线驱动器74LS366 TTL 门使能输入三态输出六反相线驱动器74LS367 TTL 4/2线使能输入三态六同相线驱动器74LS368 TTL 4/2线使能输入三态六反相线驱动器74LS37 TTL 开路输出2输入端四与非缓冲器74LS373 TTL 三态同相八D锁存器74LS374 TTL 三态反相八D锁存器74LS375 TTL 4位双稳态锁存器74LS377 TTL 单边输出公共使能八D锁存器74LS378 TTL 单边输出公共使能六D锁存器74LS379 TTL 双边输出公共使能四D锁存器74LS38 TTL 开路输出2输入端四与非缓冲器74LS380 TTL 多功能八进制寄存器74LS39 TTL 开路输出2输入端四与非缓冲器74LS390 TTL 双十进制计数器74LS393 TTL 双四位二进制计数器74LS40 TTL 4输入端双与非缓冲器74LS42 TTL BCD—十进制代码转换器74LS352 TTL 双4选1数据选择器/复工器74LS353 TTL 三态输出双4选1数据选择器/复工器74LS365 TTL 门使能输入三态输出六同相线驱动器74LS366 TTL 门使能输入三态输出六反相线驱动器74LS367 TTL 4/2线使能输入三态六同相线驱动器74LS368 TTL 4/2线使能输入三态六反相线驱动器74LS37 TTL 开路输出2输入端四与非缓冲器74LS373 TTL 三态同相八D锁存器74LS374 TTL 三态反相八D锁存器74LS375 TTL 4位双稳态锁存器74LS377 TTL 单边输出公共使能八D锁存器74LS378 TTL 单边输出公共使能六D锁存器74LS379 TTL 双边输出公共使能四D锁存器74LS38 TTL 开路输出2输入端四与非缓冲器74LS380 TTL 多功能八进制寄存器74LS39 TTL 开路输出2输入端四与非缓冲器74LS390 TTL 双十进制计数器74LS393 TTL 双四位二进制计数器74LS40 TTL 4输入端双与非缓冲器74LS42 TTL BCD—十进制代码转换器74LS447 TTL BCD—7段译码器/驱动器74LS45 TTL BCD—十进制代码转换/驱动器74LS450 TTL 16:1多路转接复用器多工器74LS451 TTL 双8:1多路转接复用器多工器74LS453 TTL 四4:1多路转接复用器多工器74LS46 TTL BCD—7段低有效译码/驱动器74LS460 TTL 十位比较器74LS461 TTL 八进制计数器74LS465 TTL 三态同相2与使能端八总线缓冲器74LS466 TTL 三态反相2与使能八总线缓冲器74LS467 TTL 三态同相2使能端八总线缓冲器74LS468 TTL 三态反相2使能端八总线缓冲器74LS469 TTL 八位双向计数器74LS47 TTL BCD—7段高有效译码/驱动器74LS48 TTL BCD—7段译码器/内部上拉输出驱动74LS490 TTL 双十进制计数器74LS491 TTL 十位计数器74LS498 TTL 八进制移位寄存器74LS50 TTL 2-3/2-2输入端双与或非门74LS502 TTL 八位逐次逼近寄存器74LS503 TTL 八位逐次逼近寄存器74LS51 TTL 2-3/2-2输入端双与或非门74LS533 TTL 三态反相八D锁存器74LS534 TTL 三态反相八D锁存器74LS54 TTL 四路输入与或非门74LS540 TTL 八位三态反相输出总线缓冲器74LS55 TTL 4输入端二路输入与或非门74LS563 TTL 八位三态反相输出触发器74LS564 TTL 八位三态反相输出D触发器74LS573 TTL 八位三态输出触发器74LS574 TTL 八位三态输出D触发器74LS645 TTL 三态输出八同相总线传送接收器74LS670 TTL 三态输出4×4寄存器堆74LS73 TTL 带清除负触发双J-K触发器74LS74 TTL 带置位复位正触发双D触发器74LS76 TTL 带预置清除双J-K触发器74LS83 TTL 四位二进制快速进位全加器74LS85 TTL 四位数字比较器74LS86 TTL 2输入端四异或门74LS90 TTL 可二/五分频十进制计数器74LS93 TTL 可二/八分频二进制计数器74LS95 TTL 四位并行输入\\输出移位寄存器74LS97 TTL 6位同步二进制乘法器CD系列:CD4000 双3输入端或非门+单非门TICD4001 四2输入端或非门HIT/NSC/TI/GOLCD4002 双4输入端或非门NSCCD4006 18位串入/串出移位寄存器NSCCD4007 双互补对加反相器NSCCD4008 4位超前进位全加器NSCCD4009 六反相缓冲/变换器NSCCD4010 六同相缓冲/变换器NSCCD4011 四2输入端与非门HIT/TICD4012 双4输入端与非门NSCCD4013 双主-从D型触发器FSC/NSC/TOSCD4014 8位串入/并入-串出移位寄存器NSCCD4015 双4位串入/并出移位寄存器TICD4016 四传输门FSC/TICD4017 十进制计数/分配器FSC/TI/MOTCD4018 可预制1/N计数器NSC/MOTCD4019 四与或选择器PHICD4020 14级串行二进制计数/分频器FSCCD4021 08位串入/并入-串出移位寄存器PHI/NSCCD4022 八进制计数/分配器NSC/MOTCD4023 三3输入端与非门NSC/MOT/TICD4024 7级二进制串行计数/分频器NSC/MOT/TICD4025 三3输入端或非门NSC/MOT/TICD4026 十进制计数/7段译码器NSC/MOT/TICD4027 双J-K触发器NSC/MOT/TICD4028 BCD码十进制译码器NSC/MOT/TICD4029 可预置可逆计数器NSC/MOT/TICD4030 四异或门NSC/MOT/TI/GOLCD4031 64位串入/串出移位存储器NSC/MOT/TICD4032 三串行加法器NSC/TICD4033 十进制计数/7段译码器NSC/TICD4034 8位通用总线寄存器NSC/MOT/TICD4035 4位并入/串入-并出/串出移位寄存NSC/MOT/TI CD4038 三串行加法器NSC/TICD4040 12级二进制串行计数/分频器NSC/MOT/TICD4041 四同相/反相缓冲器NSC/MOT/TICD4042 四锁存D型触发器NSC/MOT/TICD4043 4三态R-S锁存触发器("1"触发) NSC/MOT/TI CD4044 四三态R-S锁存触发器("0"触发) NSC/MOT/TI CD4046 锁相环NSC/MOT/TI/PHICD4047 无稳态/单稳态多谐振荡器NSC/MOT/TICD4048 4输入端可扩展多功能门NSC/HIT/TICD4049 六反相缓冲/变换器NSC/HIT/TICD4050 六同相缓冲/变换器NSC/MOT/TICD4051 八选一模拟开关NSC/MOT/TICD4052 双4选1模拟开关NSC/MOT/TICD4053 三组二路模拟开关NSC/MOT/TICD4054 液晶显示驱动器NSC/HIT/TICD4055 BCD-7段译码/液晶驱动器NSC/HIT/TI CD4056 液晶显示驱动器NSC/HIT/TICD4059 “N”分频计数器NSC/TICD4060 14级二进制串行计数/分频器NSC/TI/MOT CD4063 四位数字比较器NSC/HIT/TICD4066 四传输门NSC/TI/MOTCD4067 16选1模拟开关NSC/TICD4068 八输入端与非门/与门NSC/HIT/TICD4069 六反相器NSC/HIT/TICD4070 四异或门NSC/HIT/TICD4071 四2输入端或门NSC/TICD4072 双4输入端或门NSC/TICD4073 三3输入端与门NSC/TICD4075 三3输入端或门NSC/TICD4076 四D寄存器CD4077 四2输入端异或非门HITCD4078 8输入端或非门/或门CD4081 四2输入端与门NSC/HIT/TICD4082 双4输入端与门NSC/HIT/TICD4085 双2路2输入端与或非门CD4086 四2输入端可扩展与或非门CD4089 二进制比例乘法器CD4093 四2输入端施密特触发器NSC/MOT/ST CD4094 8位移位存储总线寄存器NSC/TI/PHICD4095 3输入端J-K触发器CD4096 3输入端J-K触发器CD4097 双路八选一模拟开关CD4098 双单稳态触发器NSC/MOT/TICD4099 8位可寻址锁存器NSC/MOT/STCD40100 32位左/右移位寄存器CD40101 9位奇偶较验器CD40102 8位可预置同步BCD减法计数器CD40103 8位可预置同步二进制减法计数器CD40104 4位双向移位寄存器CD40105 先入先出FI-FD寄存器CD40106 六施密特触发器NSC\\TICD40107 双2输入端与非缓冲/驱动器HAR\\TI CD40108 4字×4位多通道寄存器CD40109 四低-高电平位移器CD40110 十进制加/减,计数,锁存,译码驱动STCD40147 10-4线编码器NSC\\MOTCD40160 可预置BCD加计数器NSC\\MOTCD40161 可预置4位二进制加计数器NSC\\MOTCD40162 BCD加法计数器NSC\\MOTCD40163 4位二进制同步计数器NSC\\MOTCD40174 六锁存D型触发器NSC\\TI\\MOTCD40175 四D型触发器NSC\\TI\\MOTCD40181 4位算术逻辑单元/函数发生器CD40182 超前位发生器CD40192 可预置BCD加/减计数器(双时钟) NSC\\TICD40193 可预置4位二进制加/减计数器NSC\\TICD40194 4位并入/串入-并出/串出移位寄存NSC\\MOTCD40195 4位并入/串入-并出/串出移位寄存NSC\\MOTCD40208 4×4多端口寄存器CD4501 4输入端双与门及2输入端或非门CD4502 可选通三态输出六反相/缓冲器CD4503 六同相三态缓冲器CD4504 六电压转换器CD4506 双二组2输入可扩展或非门CD4508 双4位锁存D型触发器CD4510 可预置BCD码加/减计数器CD4511 BCD锁存,7段译码,驱动器CD4512 八路数据选择器CD4513 BCD锁存,7段译码,驱动器(消隐)CD4514 4位锁存,4线-16线译码器CD4515 4位锁存,4线-16线译码器CD4516 可预置4位二进制加/减计数器CD4517 双64位静态移位寄存器CD4518 双BCD同步加计数器CD4519 四位与或选择器CD4520 双4位二进制同步加计数器CD4521 24级分频器CD4522 可预置BCD同步1/N计数器CD4526 可预置4位二进制同步1/N计数器CD4527 BCD比例乘法器CD4528 双单稳态触发器CD4529 双四路/单八路模拟开关CD4530 双5输入端优势逻辑门CD4531 12位奇偶校验器CD4532 8位优先编码器CD4536 可编程定时器CD4538 精密双单稳CD4539 双四路数据选择器CD4541 可编程序振荡/计时器CD4543 BCD七段锁存译码,驱动器CD4544 BCD七段锁存译码,驱动器CD4547 BCD七段译码/大电流驱动器CD4549 函数近似寄存器CD4551 四2通道模拟开关CD4553 三位BCD计数器CD4555 双二进制四选一译码器/分离器CD4556 双二进制四选一译码器/分离器CD4558 BCD八段译码器CD4560 "N"BCD加法器CD4561 "9"求补器CD4573 四可编程运算放大器CD4574 四可编程电压比较器CD4575 双可编程运放/比较器CD4583 双施密特触发器CD4584 六施密特触发器CD4585 4位数值比较器CD4599 8位可寻址锁存器。

SN74LVC32244ZKER中文资料

PACKAGING INFORMATIONOrderable Device Status (1)Package Type Package Drawing Pins Package Qty Eco Plan (2)Lead/Ball FinishMSL Peak Temp (3)SN74LVC32244GKER ACTIVE LFBGA GKE 961000NoneSNPB Level-3-220C-168HR SN74LVC32244ZKERACTIVELFBGAZKE961000Green (RoHS &no Sb/Br)SNAGCULevel-3-250C-168HR(1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan -May not be currently available -please check /productcontent for the latest availability information and additional product content details.None:Not yet available Lead (Pb-Free).Pb-Free (RoHS):TI's terms "Lead-Free"or "Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all 6substances,including the requirement that lead not exceed 0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Green (RoHS &no Sb/Br):TI defines "Green"to mean "Pb-Free"and in addition,uses package materials that do not contain halogens,including bromine (Br)or antimony (Sb)above 0.1%of total product weight.(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDECindustry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducteddestructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.PACKAGE OPTION ADDENDUM25-Feb-2005IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. T esting and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. T o minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements. Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotiveDSP Broadband /broadbandInterface Digital Control /digitalcontrolLogic Military /militaryPower Mgmt Optical Networking /opticalnetwork Microcontrollers Security /securityTelephony /telephonyVideo & Imaging /videoWireless /wirelessMailing Address:Texas InstrumentsPost Office Box 655303 Dallas, Texas 75265Copyright 2005, Texas Instruments Incorporated。

74系列各个芯片详细介绍

74系列芯片资料程序匠人发表于 2005-10-29 19:20:00 阅读全文(2477) | 回复(0) | 引用通告(0) | 编辑74系列芯片资料反相器驱动器 LS04 LS05 LS06 LS07 LS125 LS240 LS244 LS245与门与非门 LS00 LS08 LS10 LS11 LS20 LS21 LS27 LS30 LS38或门或非门与或非门 LS02 LS32 LS51 LS64 LS65异或门比较器 LS86译码器 LS138 LS139寄存器 LS74 LS175 LS373反相器:Vcc 6A 6Y 5A 5Y 4A 4Y 六非门 74LS04┌┴─┴─┴─┴─┴─┴─┴┐六非门(OC门) 74LS05_ │14 13 12 11 10 9 8│六非门(OC高压输出) 74LS06Y = A )││ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1Y 2A 2Y 3A 3Y GND驱动器:Vcc 6A 6Y 5A 5Y 4A 4Y┌┴─┴─┴─┴─┴─┴─┴┐│14 13 12 11 10 9 8│Y = A )│六驱动器(OC高压输出) 74LS07│ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1Y 2A 2Y 3A 3Y GNDVcc -4C 4A 4Y -3C 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐_ │14 13 12 11 10 9 8│Y =A+C )│四总线三态门 74LS125│ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘-1C 1A 1Y -2C 2A 2Y GNDVcc -G B1 B2 B3 B4 B8 B6 B7 B8┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐ 8位总线驱动器 74LS245 │20 19 18 17 16 15 14 13 12 11│)│ DIR=1 A=>B│ 1 2 3 4 5 6 7 8 9 10│ DIR=0 B=>A└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘DIR A1 A2 A3 A4 A5 A6 A7 A8 GND页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器正逻辑与门,与非门:Vcc 4B 4A 4Y 3B 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐│14 13 12 11 10 9 8│Y = AB )│ 2输入四正与门 74LS08 │ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1B 1Y 2A 2B 2Y GNDVcc 4B 4A 4Y 3B 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐__ │14 13 12 11 10 9 8│Y = AB )│ 2输入四正与非门 74LS00 │ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1B 1Y 2A 2B 2Y GNDVcc 1C 1Y 3C 3B 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐___ │14 13 12 11 10 9 8│Y = ABC )│ 3输入三正与非门 74LS10 │ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1B 2A 2B 2C 2Y GNDVcc H G Y┌┴─┴─┴─┴─┴─┴─┴┐│14 13 12 11 10 9 8│)│ 8输入与非门 74LS30│ 1 2 3 4 5 6 7│ ________└┬─┬─┬─┬─┬─┬─┬┘ Y = ABCDEFGHA B C D E F GND页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器正逻辑或门,或非门:Vcc 4B 4A 4Y 3B 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐ 2输入四或门 74LS32│14 13 12 11 10 9 8│)│ Y = A+B│ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1B 1Y 2A 2B 2Y GNDVcc 4Y 4B 4A 3Y 3B 3A┌┴─┴─┴─┴─┴─┴─┴┐ 2输入四或非门 74LS02│14 13 12 11 10 9 8│ ___)│ Y = A+B│ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1Y 1A 1B 2Y 2A 2B GNDVcc 2Y 2B 2A 2D 2E 1F┌┴─┴─┴─┴─┴─┴─┴┐双与或非门 74S51│14 13 12 11 10 9 8│ _____)│ 2Y = AB+DE│ 1 2 3 4 5 6 7│ _______└┬─┬─┬─┬─┬─┬─┬┘ 1Y = ABC+DEF1Y 1A 1B 1C 1D 1E GNDVcc D C B K J Y┌┴─┴─┴─┴─┴─┴─┴┐ 4-2-3-2与或非门 74S64 74S65(OC门) │14 13 12 11 10 9 8│ ______________)│ Y = ABCD+EF+GHI+JK│ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘A E F G H I GND页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器2输入四异或门 74LS86Vcc 4B 4A 4Y 3Y 3B 3A┌┴─┴─┴─┴─┴─┴─┴┐│14 13 12 11 10 9 8│)│ _ _│ 1 2 3 4 5 6 7│ Y=AB+AB└┬─┬─┬─┬─┬─┬─┬┘1A 1B 1Y 2Y 2A 2B GND8*2输入比较器 74LS688_Vcc Y B8 A8 B7 A7 B6 A6 B5 A5┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐ 8*2输入比较器 74LS688│20 19 18 17 16 15 14 13 12 11│)││ 1 2 3 4 5 6 7 8 9 10│└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘CE A1 B1 A2 B2 A3 B3 A4 B4 GND_Y=A1⊙B1+A2⊙B2+A3⊙B3+A4⊙B4+A5⊙B5+A6⊙B6+A7⊙B7+A8⊙B8页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器3-8译码器 74LS138Vcc -Y0 -Y1 -Y2 -Y3 -Y4 -Y5 -Y6 __ _ _ _ __ _ _ __ _ _ __ _ ┌┴─┴─┴─┴─┴─┴─┴─┴┐ Y0=A B C Y1=A B B Y2=A B C Y3=A B C │16 15 14 13 12 11 10 9 │)│ __ _ _ __ _ __ _ __│ 1 2 3 4 5 6 7 8│ Y4=A B C Y5=A B C Y6=A B C Y7=A B C └┬─┬─┬─┬─┬─┬─┬─┬┘A B C -CS0 -CS1 CS2 -Y7 GND双2-4译码器 74LS139Vcc -2G 2A 2B -Y0 -Y1 -Y2 -Y3 __ __ __ __ __ __ __ __┌┴─┴─┴─┴─┴─┴─┴─┴┐ Y0=2A 2B Y1=2A 2B Y2=2A 2B Y3=2A 2B │16 15 14 13 12 11 10 9 │)│ __ __ __ __ __ __ __ __│ 1 2 3 4 5 6 7 8│ Y0=1A 1B Y1=1A 1B Y2=1A 1B Y3=1A 1B └┬─┬─┬─┬─┬─┬─┬─┬┘-1G 1A 1B -Y0 -Y1 -Y2 -Y3 GND8*2输入比较器 74LS688_Vcc Y B8 A8 B7 A7 B6 A6 B5 A5┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐ 8*2输入比较器 74LS688│20 19 18 17 16 15 14 13 12 11│)││ 1 2 3 4 5 6 7 8 9 10│└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘CE A1 B1 A2 B2 A3 B3 A4 B4 GND_Y=A1⊙B1+A2⊙B2+A3⊙B3+A4⊙B4+A5⊙B5+A6⊙B6+A7⊙B7+A8⊙B8寄存器:Vcc 2CR 2D 2Ck 2St 2Q -2Q┌┴─┴─┴─┴─┴─┴─┴┐双D触发器 74LS74│14 13 12 11 10 9 8 │)││ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1Cr 1D 1Ck 1St 1Q -1Q GNDVcc 8Q 8D 7D 7Q 6Q 6D 5D 5Q ALE┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐ 8位锁存器 74LS373│20 19 18 17 16 15 14 13 12 11│)││ 1 2 3 4 5 6 7 8 9 10│└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘-OE 1Q 1D 2D 2Q 3Q 3D 4D 4Q GND型号器件名称厂牌[数据表]SN7400四2输入端与非门 TI[DATA]SN7401四2输入端与非门(OC) SN7402四2输入端或非门 TI[DATA]SN7403四2输入端与非门(OC)TI[DATA]SN7404六反相器 TI[DATA]SN7405六反相器(OC)TI[DATA]SN7406六高压输出反相器 (OC,30V)TI[DATA]SN7407六高压输出缓冲,驱动器(OC,30V)TI[DATA]SN7408四2输入端与门 TI[DATA]SN7409四2输入端与门(OC)TI[DATA]SN7410三3输入端与非门 TI[DATA]SN7412三3输入端与非门(OC)TI[DATA]SN7413双4输入端与非门 TI[DATA]SN7414六反相器TI[DATA]SN7416六高压输出反相缓冲/驱动器 I[DATA]SN7417六高压输出缓冲/驱动器(OC,15V)TI[DATA]SN7420双4输入端与非门 TI[DATA]SN7422双4输入端与非门(OC)TI[DATA]SN7423可扩展双4输入端或非门 TI[DATA]SN7425双4输入端或非门TI[DATA]SN7426四2输入端高压输出与非缓冲器 [DATA]SN7427三3输入端或非门TI[DATA]SN7428四2输入端或非缓冲器 I[DATA]SN74308输入端与非门TI[DATA]SN7432四2输入端或门。

74LVC1G53资料

74LVC1G53

2-channel analog multiplexer/demultiplexer

Rev. 03 — 29 August 2007

Product data sheet

1. General description

The 74LVC1G53 is a low-power, low-voltage, high-speed, Si-gate CMOS device.

Rev. 03 — 29 August 2007

© NXP B.V. 2007. All rights reserved.

2 of 22

元器件交易网

NXP Semiconductors

6. Pinning information

6.1 Pinning

74LVC1G53

Z1 E2 GND 3 GND 4

The 74LVC1G53 provides one analog multiplexer/demultiplexer with a digital select input (S), two independent inputs/outputs (Y0 and Y1), a common input/output (Z) and an active LOW enable input (E). When pin E is HIGH, the switch is turned off.

For XSON8 and XQFN8 packages: above 45 °C the value of Ptot derates linearly with 2.4 mW/K.

74LVC1G53_3

Product data sheet

74LVC16373ADGG,118,74LVC16373ADGG,518,74LVC16373ADGG,118,74LVC16373ADGG,118,规格书,Datasheet 资料

74LVC16373A; 74LVCH16373A

DESCRIPTION data input data input latch enable input (active HIGH)

4, 10, 15, 21, 28, ground (0 V) 34, 39, 45 5 6 7, 18, 31, 42 8 9 11 12 13 14 16 17 19 20 22 23 24 25 26 27 29 30 32 33 35 36 37 38 40 41 43 44 data output data output supply voltage data output data output data output data output data output data output data output data output data output data output data output data output output enable input (active LOW) latch enable input (active HIGH) data input data input data input data input data input data input data input data input data input data input data input data input data input data input Fig.1 Pin configuration SSOP48 and TSSOP48.

2003 Dec 08

2

芯天下--/

Philips Semiconductors

Product specification

16-bit D-type transparent latch with 5 V tolerant inputs/outputs; 3-state

SN74LVC1G00中文资料

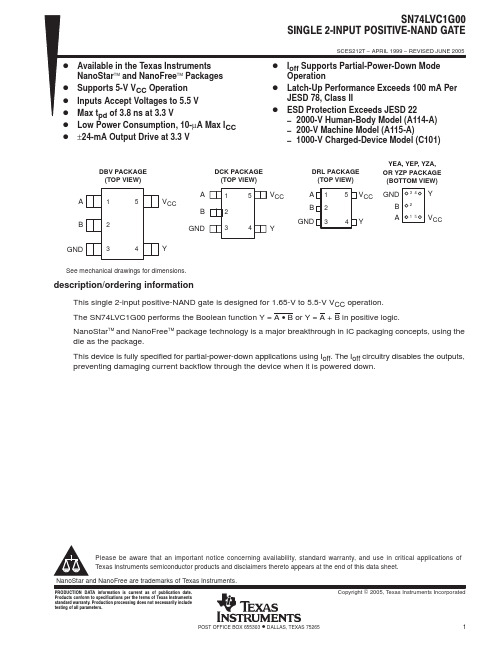

SN74LVC1G00 SINGLE 2ĆINPUT POSITIVEĆNAND GATE

SCES212T − APRIL 1999 − REVISED JUNE 2005

D Available in the Texas Instruments D D D D D

GND B A

3 4 2 1 5

Y VCC

2

4

GND

4

4

Y

3

Y

See mechanical drawings for dimensions.

description/ordering information

This single 2-input positive-NAND gate is designed for 1.65-V to 5.5-V VCC operation. The SN74LVC1G00 performs the Boolean function Y = A • B or Y = A + B in positive logic. NanoStar and NanoFree package technology is a major breakthrough in IC packaging concepts, using the die as the package. This device is fully specified for partial-power-down applications using Ioff. The Ioff circuitry disables the outputs, preventing damaging current backflow through the device when it is powered down.

74LVC1G74DC-G中文资料

2 of 20

NXP Semiconductors

74LVC1G74

Single D-type flip-flop with set and reset; positive edge trigger

C

C C

D

C RD

SD

CP

C

C

Fig 3. Logic diagram

6. Pinning information

plastic extremely thin small outline package; no leads; SOT996-2 8 terminals; UTLP based; body 3 × 2 × 0.5 mm

plastic extremely thin quad flat package; no leads; 8 terminals; UTLP based; body 1.6 × 1.6 × 0.5 mm

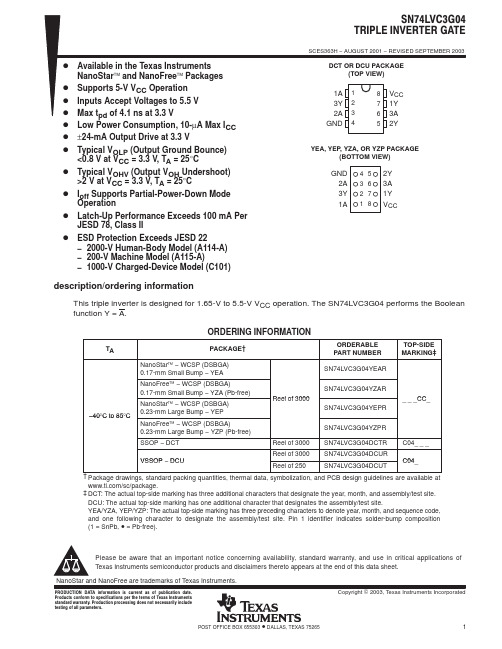

SN74LVC3G04DCTR中文资料

Copyright 2003, Texas Instruments Incorporated

POST OFFICE BOX 655303

• DALLAS, TEXAS 75265

1

元器件交易网

SN74LVC3G04 TRIPLE INVERTER GATE

description/ordering information (continued)

† Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at /sc/package. ‡ DCT: The actual top-side marking has three additional characters that designate the year, month, and assembly/test site. DCU: The actual top-side marking has one additional character that designates the assembly/test site. YEA/YZA, YEP/YZP: The actual top-side marking has three preceding characters to denote year, month, and sequence code, and one following character to designate the assembly/test site. Pin 1 identifier indicates solder-bump composition (1 = SnPb, • = Pb-free).

74LVC2G74DC,125,74LVC2G74GD,125,74LVC2G74GT,115,74LVC2G74GM,125, 规格书,Datasheet 资料

© NXP B.V. 2012. All rights reserved.

Product data sheet

Rev. 9 — 22 May 2012

2 of 25

芯天下--/

NXP Semiconductors

74LVC2G74

Single D-type flip-flop with set and reset; positive edge trigger

2. Features and benefits

Wide supply voltage range from 1.65 V to 5.5 V 5 V tolerant inputs for interfacing with 5 V logic High noise immunity Complies with JEDEC standard: JESD8-7 (1.65 V to 1.95 V) JESD8-5 (2.3 V to 2.7 V) JESD8-B/JESD36 (2.7 V to 3.6 V) 24 mA output drive (VCC = 3.0 V) ESD protection: HBM JESD22-A114F exceeds 2000 V MM JESD22-A115-A exceeds 200 V CMOS low power consumption Latch-up performance exceeds 250 mA Direct interface with TTL levels Inputs accept voltages up to 5 V Multiple package options Specified from 40 C to +85 C and 40 C to +125 C

SN74LVC1G374DCKR,SN74LVC1G374DCKR,SN74LVC1G374DCKR,SN74LVC1G374YZPR, 规格书,Datasheet 资料

FEATURESSee mechanical drawings for dimensions.DBV PACKAGE(TOP VIEW)DGNDCLKDCK PACKAGE(TOP VIEW)OEDGNDQCLKVCCYEP OR YZP PACKAGE(BOTTOM VIEW)OEGND VCCCLKD Q DESCRIPTION/ORDERING INFORMATIONSN74LVC1G374SINGLE D-TYPE FLIP-FLOP WITH3-STATE OUTPUTSCES520B–DECEMBER2003–REVISED SEPTEMBER2006•Available in the Texas Instruments•Latch-Up Performance Exceeds100mA Per NanoStar™and NanoFree™Packages JESD78,Class II•Supports5-V V CC Operation•ESD Protection Exceeds JESD22•Inputs Accept Voltages to5.5V–2000-V Human-Body Model(A114-A)•Max t pd of4ns at3.3V–200-V Machine Model(A115-A)•Low Power Consumption,10-µA Max I CC–1000-V Charged-Device Model(C101)•±24-mA Output Drive at3.3V•I off Supports Partial-Power-Down ModeOperationThis single D-type latch is designed for1.65-V to5.5-V V CC operation.The SN74LVC1G374features a3-state output designed specifically for driving highly capacitive or relatively low-impedance loads.This device is particularly suitable for implementing buffer registers,input/output(I/O) ports,bidirectional bus drivers,and working registers.NanoStar™and NanoFree™package technology is a major breakthrough in IC packaging concepts,using the die as the package.On the positive transition of the clock(CLK)input,the Q output is set to the logic level set up at the data(D) input.ORDERING INFORMATIONT A PACKAGE(1)ORDERING PART NUMBER TOP-SIDE MARKING(2)NanoStar–WCSP(DSBGA)SN74LVC1G374YEPR0.23-mm Large Bump–YEPReel of3000___D4_NanoFree–WCSP(DSBGA)SN74LVC1G374YZPR0.23-mm Large Bump–YZP(Pb-free)–40°C to85°C Reel of3000SN74LVC1G374DBVRSOT(SOT-23)–DBV CA4___Reel of250SN74LVC1G374DBVTReel of3000SN74LVC1G374DCKRSOT(SC-70)–DCK D4_Reel of250SN74LVC1G374DCKT(1)Package drawings,standard packing quantities,thermal data,symbolization,and PCB design guidelines are available at/sc/package.(2)DBV/DCK:The actual top-side marking has one additional character that designates the assembly/test site.YEP/YZP:The actual top-side marking has three preceding characters to denote year,month,and sequence code,and one following character to designate the assembly/test site.Pin1identifier indicates solder-bump composition(1=SnPb,•=Pb-free).Please be aware that an important notice concerning availability,standard warranty,and use in critical applications of TexasInstruments semiconductor products and disclaimers thereto appears at the end of this data sheet.NanoStar,NanoFree are trademarks of Texas Instruments.PRODUCTION DATA information is current as of publication date.Copyright©2003–2006,Texas Instruments Incorporated Products conform to specifications per the terms of the TexasInstruments standard warranty.Production processing does notnecessarily include testing of all parameters. DESCRIPTION/ORDERING INFORMATION(CONTINUED)OECLKD QSN74LVC1G374SINGLE D-TYPE FLIP-FLOP WITH3-STATE OUTPUTSCES520B–DECEMBER2003–REVISED SEPTEMBER2006A buffered output-enable(OE)input can be used to place the output in either a normal logic state(high or low logic levels)or the high-impedance state.In the high-impedance state,the output neither loads nor drives the bus lines significantly.The high-impedance state and increased drive provide the capability to drive bus lines without interface or pullup components.OE does not affect the internal operations of the flip-flop.Old data can be retained or new data can be entered while the outputs are in the high-impedance state.To ensure the high-impedance state during power up or power down,OE should be tied to V CC through a pullup resistor;the minimum value of the resistor is determined by the current-sinking capability of the driver.This device is fully specified for partial-power-down applications using I off.The I off circuitry disables the outputs, preventing damaging current backflow through the device when it is powered down.FUNCTION TABLEINPUTS OUTPUTOE CLK D QL↑L LL↑H HL H or L X QH X X ZLOGIC DIAGRAM(POSITIVE LOGIC)2Submit Documentation FeedbackAbsolute Maximum Ratings(1)SN74LVC1G374 SINGLE D-TYPE FLIP-FLOP WITH3-STATE OUTPUTSCES520B–DECEMBER2003–REVISED SEPTEMBER2006over operating free-air temperature range(unless otherwise noted)MIN MAX UNITV CC Supply voltage range–0.5 6.5VV I Input voltage range(2)–0.5 6.5VV O Voltage range applied to any output in the high-impedance or power-off state(2)–0.5 6.5VV O Voltage range applied to any output in the high or low state(2)(3)–0.5V CC+0.5VI IK Input clamp current V I<0–50mAI OK Output clamp current V O<0–50mAI O Continuous output current±50mAContinuous current through V CC or GND±100mADBV package165θJA Package thermal impedance(4)DCK package259°C/WYEP/YZP package123T stg Storage temperature range–65150°C (1)Stresses beyond those listed under"absolute maximum ratings"may cause permanent damage to the device.These are stress ratingsonly,and functional operation of the device at these or any other conditions beyond those indicated under"recommended operating conditions"is not implied.Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.(2)The input and output negative-voltage ratings may be exceeded if the input and output current ratings are observed.(3)The value of V CC is provided in the recommended operating conditions table.(4)The package thermal impedance is calculated in accordance with JESD51-7.3Submit Documentation FeedbackRecommended Operating Conditions (1)SN74LVC1G374SINGLE D-TYPE FLIP-FLOP WITH 3-STATE OUTPUTSCES520B–DECEMBER 2003–REVISED SEPTEMBER 2006MINMAX UNIT Operating1.65 5.5V CCSupply voltageVData retention only 1.5V CC =1.65V to 1.95V0.65×V CCV CC =2.3V to 2.7V 1.7V IHHigh-level input voltageVV CC =3V to 3.6V 2V CC =4.5V to 5.5V 0.7×V CCV CC =1.65V to 1.95V0.35×V CCV CC =2.3V to 2.7V 0.7V ILLow-level input voltageV V CC =3V to 3.6V 0.8V CC =4.5V to 5.5V0.3×V CCV I Input voltage 0 5.5V V OOutput voltage0V CC V V CC =1.65V –4V CC =2.3V–8I OHHigh-level output current–16mA V CC =3V –24V CC =4.5V –32V CC =1.65V 4V CC =2.3V8I OLLow-level output current16mA V CC =3V 24V CC =4.5V32V CC =1.8V ±0.15V,2.5V ±0.2V20∆t/∆v Input transition rise or fall rate V CC =3.3V ±0.3V 10ns/V V CC =5V ±0.5V5T A Operating free-air temperature–4085°C (1)All unused inputs of the device must be held at V CC or GND to ensure proper device operation.Refer to the TI application report,Implications of Slow or Floating CMOS Inputs ,literature number SCBA004.4Submit Documentation FeedbackElectrical CharacteristicsTiming Requirements Switching CharacteristicsSN74LVC1G374 SINGLE D-TYPE FLIP-FLOP WITH3-STATE OUTPUTSCES520B–DECEMBER2003–REVISED SEPTEMBER2006over recommended operating free-air temperature range(unless otherwise noted)PARAMETER TEST CONDITIONS V CC MIN TYP(1)MAX UNITI OH=–100µA 1.65V to5.5V V CC–0.1I OH=–4mA 1.65V 1.2I OH=–8mA 2.3V 1.9V OH VI OH=–16mA 2.43VI OH=–24mA 2.3I OH=–32mA 4.5V 3.8I OL=100µA 1.65V to5.5V0.1I OL=4mA 1.65V0.45I OL=8mA 2.3V0.3V OL VI OL=16mA0.43VI OL=24mA0.55I OL=32mA 4.5V0.55I I V I=5.5V or GND0to5.5V±1µAI OZ V O=0to5.5V±5µAI off V I or V O=5.5V0±10µAI CC V I=5.5V or GND,I O=0 1.65V to5.5V10µA∆I CC One input at V CC–0.6V,Other inputs at V CC or GND3V to5.5V500µAC i V I=V CC or GND 3.3V3pFC o V O=V CC or GND 3.3V6pF(1)All typical values are at V CC=3.3V,T A=25°C.over recommended operating free-air temperature range(unless otherwise noted)(see Figure1)V CC=1.8V V CC=2.5V V CC=3.3V V CC=5V±0.15V±0.2V±0.3V±0.5V UNITMIN MAX MIN MAX MIN MAX MIN MAXf clock Clock frequency100125150175MHzt w Pulse duration,CLK high or low 3.33 2.8 2.5nst su Setup time,data before CLK↑ 3.5 2.52 1.5nst h Hold time,data after CLK↑ 3.4 1.6 1.5 1.5nsover recommended operating free-air temperature range,CL=15pF(unless otherwise noted)(see Figure1)V CC=1.8V V CC=2.5V V CC=3.3V V CC=5VFROM TO±0.15V±0.2V±0.3V±0.5V PARAMETER UNIT INPUT(OUTPUT)MIN MAX MIN MAX MIN MAX MIN MAXf max100125150175MHzt pd CLK Q 2.51526 1.4413ns t en OE Q 2.2122 4.8 1.3 3.8 1.1 2.5ns t dis OE Q 2.2112 4.8 1.6 4.5 1.2 3.1ns5Submit Documentation FeedbackSwitching CharacteristicsOperating CharacteristicsSN74LVC1G374SINGLE D-TYPE FLIP-FLOP WITH 3-STATE OUTPUTSCES520B–DECEMBER 2003–REVISED SEPTEMBER 2006over recommended operating free-air temperature range,C L =30pF or 50pF (unless otherwise noted)(see Figure 2)V CC =1.8V V CC =2.5V V CC =3.3V V CC =5V FROM TO ±0.15V ±0.2V ±0.3V ±0.5V PARAMETERUNITINPUT(OUTPUT)MIN MAXMIN MAXMIN MAXMIN MAXf max 100125150175MHz t pd CLK Q 2.718.3 1.88.2 1.6614ns t en OE Q 213 1.5 6.30.950.7 3.5ns t disOEQ214 1.15.3 1.44.50.83.1ns T A =25°CV CC =1.8VV CC =2.5VV CC =3.3VV CC =5V TEST PARAMETERUNIT CONDITIONS TYP TYP TYP TYP Outputs enabled 24242527Power dissipation C pdf =10MHzpFcapacitanceOutputs disabled889116Submit Documentation FeedbackPARAMETER MEASUREMENT INFORMATIONFrom OutputUnder Test(see NoteLOAD CIRCUITOpenData InputTiming Input0 V0 V0 VInput0 VInputOutputWaveform 1S1 at V(see Note B)LOADOutputWaveform 2S1 at GND(see Note B)VOLVOH0 V»0 V OutputOutputt/tPLH PHLOpenTEST S1OutputControl1.8 V0.15 V±2.5 V0.2 V±3.3 V0.3 V±5 V0.5 V±1 M W1 M W1 M W1 M WVCCRL2 ×VCC2 ×VCC6 V2 ×VCCVLOADCL15 pF15 pF15 pF15 pF0.15 V0.15 V0.3 V0.3 VVD3 VVIVCC/2VCC/21.5 VVCC/2VM£2 ns£2 ns£2.5 ns£2.5 nsINPUTSt/tr fVCCVCCVCCVLOADt/tPLZ PZLGNDt/tPHZ PZHVOLTAGE WAVEFORMSENABLE AND DISABLE TIMESLOW-AND HIGH-LEVEL ENABLING VOLTAGE WAVEFORMSPROPAGATION DELAY TIMESINVERTING AND NONINVERTING OUTPUTSNOTES: A.C includes probe and jig capacitance.B.Waveform 1 is for an output with internal conditions such that the output is low, except when disabled by the output control.Waveform 2 is for an output with internal conditions such that the output is high, except when disabled by the output control.C.All input pulses are supplied by generators having the following characteristics: PRR10 MHz, Z= 50.D.The outputs are measured one at a time, with one transition per measurement.E.t and t are the same as t.F.t and t are the same as t.G.t and t are the same as t.H.All parameters and waveforms are not applicable to all devices.LOPLZ PHZ disPZL PZH enPLH PHL pd£WVOLTAGE WAVEFORMSPULSE DURATIONVOLTAGE WAVEFORMSSETUP AND HOLD TIMESVIVIVIV/2LOADVOLVOHVIVIVOHVOLSN74LVC1G374SINGLE D-TYPE FLIP-FLOP WITH3-STATE OUTPUTSCES520B–DECEMBER2003–REVISED SEPTEMBER2006Figure1.Load Circuit and Voltage Waveforms7Submit Documentation FeedbackFrom OutputUnder Test(see NoteLOAD CIRCUITOpenData InputTiming Input0 V0 V0 VInput0 VInputOutputWaveform 1S1 at V(see Note B)LOADOutputWaveform 2S1 at GND(see Note B)VOLVOH0 V»0 V OutputOutputTEST S1t/tPLH PHLOpenOutputControl1.8 V0.15 V±2.5 V0.2 V±3.3 V0.3 V±5 V0.5 V±1 k W500W500W500WVCCRL2 ×VCC2 ×VCC6 V2 ×VCCVLOADCL30 pF30 pF50 pF50 pF0.15 V0.15 V0.3 V0.3 VVD3 VVIVCC/2VCC/21.5 VVCC/2VM£2 ns£2 ns£2.5 ns£2.5 nsINPUTSt/tr fVCCVCCVCCVLOADt/tPLZ PZLGNDt/tPHZ PZHVOLTAGE WAVEFORMSENABLE AND DISABLE TIMESLOW-AND HIGH-LEVEL ENABLING VOLTAGE WAVEFORMSPROPAGATION DELAY TIMESINVERTING AND NONINVERTING OUTPUTSNOTES: A.C includes probe and jig capacitance.B.Waveform 1 is for an output with internal conditions such that the output is low, except when disabled by the output control.Waveform 2 is for an output with internal conditions such that the output is high, except when disabled by the output control.C.All input pulses are supplied by generators having the following characteristics: PRR10 MHz, Z= 50.D.The outputs are measured one at a time, with one transition per measurement.E.t and t are the same as t.F.t and t are the same as t.G.t and t are the same as t.H.All parameters and waveforms are not applicable to all devices.LOPLZ PHZ disPZL PZH enPLH PHL pd£WVOLTAGE WAVEFORMSPULSE DURATIONVOLTAGE WAVEFORMSSETUP AND HOLD TIMESVIVIVIV/2LOADVOLVOHVIVIVOHVOLSN74LVC1G374SINGLE D-TYPE FLIP-FLOP WITH3-STATE OUTPUTSCES520B–DECEMBER2003–REVISED SEPTEMBER2006PARAMETER MEASUREMENT INFORMATION(continued)Figure2.Load Circuit and Voltage Waveforms8Submit Documentation FeedbackPACKAGING INFORMATIONOrderable Device Status (1)Package Type Package Drawing Pins Package Qty Eco Plan (2)Lead/Ball Finish MSL Peak Temp (3)74LVC1G374DBVRE4ACTIVE SOT-23DBV 63000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM 74LVC1G374DBVRG4ACTIVE SOT-23DBV 63000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM 74LVC1G374DCKRE4ACTIVE SC70DCK 63000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM 74LVC1G374DCKRG4ACTIVE SC70DCK 63000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LVC1G374DBVR ACTIVE SOT-23DBV 63000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LVC1G374DCKR ACTIVE SC70DCK 63000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LVC1G374YZPRACTIVEDSBGAYZP63000Green (RoHS &no Sb/Br)SNAGCULevel-1-260C-UNLIM(1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan -The planned eco-friendly classification:Pb-Free (RoHS),Pb-Free (RoHS Exempt),or Green (RoHS &no Sb/Br)-please check /productcontent for the latest availability information and additional product content details.TBD:The Pb-Free/Green conversion plan has not been defined.Pb-Free (RoHS):TI's terms "Lead-Free"or "Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all 6substances,including the requirement that lead not exceed 0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Pb-Free (RoHS Exempt):This component has a RoHS exemption for either 1)lead-based flip-chip solder bumps used between the die and package,or 2)lead-based die adhesive used between the die and leadframe.The component is otherwise considered Pb-Free (RoHS compatible)as defined above.Green (RoHS &no Sb/Br):TI defines "Green"to mean Pb-Free (RoHS compatible),and free of Bromine (Br)and Antimony (Sb)based flame retardants (Br or Sb do not exceed 0.1%by weight in homogeneous material)(3)MSL,Peak Temp.--TheMoisture Sensitivity Level rating according to the JEDEC industry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.OTHER QUALIFIED VERSIONS OF SN74LVC1G374:•Automotive:SN74LVC1G374-Q1NOTE:Qualified Version Definitions:•Automotive -Q100devices qualified for high-reliability automotive applications targeting zero defectsPACKAGE OPTION ADDENDUM5-Dec-2008TAPE AND REELINFORMATION*Alldimensions are nominalDevicePackage Type Package Drawing Pins SPQReel Diameter (mm)Reel Width W1(mm)A0(mm)B0(mm)K0(mm)P1(mm)W (mm)Pin1Quadrant SN74LVC1G374DBVR SOT-23DBV 63000180.08.4 3.23 3.17 1.37 4.08.0Q3SN74LVC1G374DBVR SOT-23DBV 63000178.09.2 3.3 3.2 1.55 4.08.0Q3SN74LVC1G374DCKR SC70DCK 63000178.09.2 2.4 2.4 1.22 4.08.0Q3SN74LVC1G374YZPRDSBGAYZP63000180.08.41.021.520.634.08.0Q1PACKAGE MATERIALS INFORMATION11-Aug-2012*All dimensionsare nominalDevicePackage TypePackage DrawingPins SPQ Length (mm)Width (mm)Height (mm)SN74LVC1G374DBVR SOT-23DBV 63000202.0201.028.0SN74LVC1G374DBVR SOT-23DBV 63000180.0180.018.0SN74LVC1G374DCKR SC70DCK 63000180.0180.018.0SN74LVC1G374YZPRDSBGAYZP63000220.0220.034.0PACKAGE MATERIALS INFORMATION11-Aug-2012Pack Materials-Page 2IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,enhancements,improvements and other changes to its semiconductor products and services per JESD46C and to discontinue any product or service per JESD48B.Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All semiconductor products(also referred to herein as“components”)are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its components to the specifications applicable at the time of sale,in accordance with the warranty in TI’s terms and conditions of sale of semiconductor products.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by applicable law,testing of all parameters of each component is not necessarily performed.TI assumes no liability for applications assistance or the design of Buyers’products.Buyers are responsible for their products and applications using TI components.To minimize the risks associated with Buyers’products and applications,Buyers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any patent right,copyright,mask work right,or other intellectual property right relating to any combination,machine,or process in which TI components or services are rmation published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.Buyer acknowledges and agrees that it is solely responsible for compliance with all legal,regulatory and safety-related requirements concerning its products,and any use of TI components in its applications,notwithstanding any applications-related information or support that may be provided by TI.Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures,monitor failures and their consequences,lessen the likelihood of failures that might cause harm and take appropriate remedial actions.Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.In some cases,TI components may be promoted specifically to facilitate safety-related applications.With such components,TI’s goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements.Nonetheless,such components are subject to these terms.No TI components are authorized for use in FDA Class III(or similar life-critical medical equipment)unless authorized officers of the parties have executed a special agreement specifically governing such use.Only those TI components which TI has specifically designated as military grade or“enhanced plastic”are designed and intended for use in military/aerospace applications or environments.Buyer acknowledges and agrees that any military or aerospace use of TI components which have not been so designated is solely at the Buyer's risk,and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.TI has specifically designated certain components which meet ISO/TS16949requirements,mainly for automotive ponents which have not been so designated are neither designed nor intended for automotive use;and TI will not be responsible for any failure of such components to meet such requirements.Products ApplicationsAudio /audio Automotive and Transportation /automotiveAmplifiers Communications and Telecom /communicationsData Converters Computers and Peripherals /computersDLP®Products Consumer Electronics /consumer-appsDSP Energy and Lighting /energyClocks and Timers /clocks Industrial /industrialInterface Medical /medicalLogic Security /securityPower Mgmt Space,Avionics and Defense /space-avionics-defense Microcontrollers Video and Imaging /videoRFID OMAP Mobile Processors /omap TI E2E Community Wireless Connectivity /wirelessconnectivityMailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2012,Texas Instruments Incorporated。

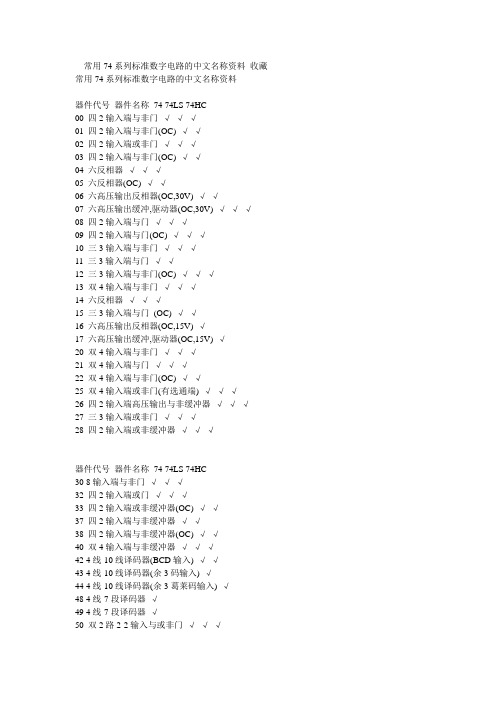

常用74系列标准数字电路的中文名称资料

常用74系列标准数字电路的中文名称资料收藏常用74系列标准数字电路的中文名称资料器件代号器件名称74 74LS 74HC00 四2输入端与非门√√√01 四2输入端与非门(OC) √√02 四2输入端或非门√√√03 四2输入端与非门(OC) √√04 六反相器√√√05 六反相器(OC) √√06 六高压输出反相器(OC,30V) √√07 六高压输出缓冲,驱动器(OC,30V) √√√08 四2输入端与门√√√09 四2输入端与门(OC) √√√10 三3输入端与非门√√√11 三3输入端与门√√12 三3输入端与非门(OC) √√√13 双4输入端与非门√√√14 六反相器√√√15 三3输入端与门(OC) √√16 六高压输出反相器(OC,15V) √17 六高压输出缓冲,驱动器(OC,15V) √20 双4输入端与非门√√√21 双4输入端与门√√√22 双4输入端与非门(OC) √√25 双4输入端或非门(有选通端) √√√26 四2输入端高压输出与非缓冲器√√√27 三3输入端或非门√√√28 四2输入端或非缓冲器√√√器件代号器件名称74 74LS 74HC30 8输入端与非门√√√32 四2输入端或门√√√33 四2输入端或非缓冲器(OC) √√37 四2输入端与非缓冲器√√38 四2输入端与非缓冲器(OC) √√40 双4输入端与非缓冲器√√√42 4线-10线译码器(BCD输入) √√43 4线-10线译码器(余3码输入) √44 4线-10线译码器(余3葛莱码输入) √48 4线-7段译码器√49 4线-7段译码器√50 双2路2-2输入与或非门√√√51 2路3-3输入,2路2-2输入与或非门√√√52 4路2-3-2-2输入与或门√53 4路2-2-2-2输入与或非门√54 4路2-3-3-2输入与或非门√√55 2路4-4输入与或非门√60 双4输入与扩展器√√61 三3输入与扩展器√62 4路2-3-3-2输入与或扩展器√64 4路4-2-3-2输入与或非门√65 4路4-2-3-2输入与或非门(OC) √70 与门输入J-K触发器√71 与或门输入J-K触发器√72 与门输入J-K触发器√器件代号器件名称74 74LS 74HC74 双上升沿D型触发器√√78 双D型触发器√√85 四位数值比较器√86 四2输入端异或门√√√87 4位二进制原码/反码√95 4位移位寄存器√101 与或门输入J-K触发器√102 与门输入J-K触发器√107 双主-从J-K触发器√108 双主-从J-K触发器√74F74是高速的TTL芯片和74HC一样就是速度高109 双主-从J-K触发器√110 与门输入J-K触发器√111 双主-从J-K触发器√√112 双下降沿J-K触发器√113 双下降沿J-K触发器√114 双下降沿J-K触发器√116 双4位锁存器√120 双脉冲同步驱动器√121 单稳态触发器√√√122 可重触发单稳态触发器√√√123 可重触发双稳态触发器√√√125 四总线缓冲器√√√126 四总线缓冲器√√√128 四2输入端或非线驱动器√√√132 四2输入端与非门√√√d触发器芯片有:74HC74 74LS90 双D触发器74LS7474LS364八D触发器(三态)7474、74 H74、74F74、74ALS74、74L74、74LS74A、74S74、74HC73、74C74双D型正沿触发器(带预置和清除端)74174、74LS174、74F174、74ALS174、74S174、74HC174、74C174六D型触发器(带清除端)74175、74LS175、74F175、74ALS175、74S175、74HC175、74C175 四D型触发器(带清除端)74273、74LS273、74S273、74F273、74ALS273、74HC273 八D型触发器(带清除端)74LS364八D触发器(三态)74LS377、74F377、74S3777八D 触发器74LS378、74F378、74S378、74HC378六D 触发器74LS379、74F379、74S379、74HC379八D 触发器。

SN74LVC1G32DCKTG4中文资料

FUNCTION TABLE

INPUTS

A

B

H

X

X

H

L

L

OUTPUT Y

H H L

LOGIC DIAGRAM (POSITIVE LOGIC)

2

Submit Documentation Feedback

元器件交易网

பைடு நூலகம்

SN74LVC1G32 SINGLE 2-INPUT POSITIVE-OR GATE

Copyright © 1999–2007, Texas Instruments Incorporated

元器件交易网

SN74LVC1G32 SINGLE 2-INPUT POSITIVE-OR GATE

SCES219O – APRIL 1999 – REVISED FEBRUARY 2007

Reel of 4000

SN74LVC1G32DRLR SN74LVC1G32DRLRG4

CG_

(1) Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at /sc/package.

元器件交易网

FEATURES

• Available in the Texas Instruments NanoStar™ and NanoFree™ Packages

• Supports 5-V VCC Operation • Inputs Accept Voltages to 5.5 V • Max tpd of 3.6 ns at 3.3 V • Low Power Consumption, 10-µA Max ICC • ± 24-mA Output Drive at 3.3 V

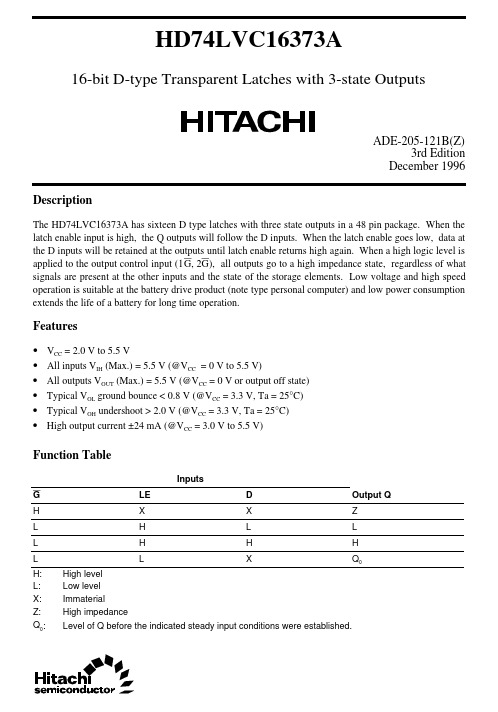

HD74LVC16373A中文资料

HD74LVC16373A16-bit D-type Transparent Latches with 3-state OutputsADE-205-121B(Z)3rd EditionDecember 1996 DescriptionThe HD74LVC16373A has sixteen D type latches with three state outputs in a 48 pin package. When the latch enable input is high, the Q outputs will follow the D inputs. When the latch enable goes low, data at the D inputs will be retained at the outputs until latch enable returns high again. When a high logic level is applied to the output control input (1G, 2G), all outputs go to a high impedance state, regardless of what signals are present at the other inputs and the state of the storage elements. Low voltage and high speed operation is suitable at the battery drive product (note type personal computer) and low power consumption extends the life of a battery for long time operation.Features• V CC = 2.0 V to 5.5 V• All inputs V IH (Max.) = 5.5 V (@V CC = 0 V to 5.5 V)• All outputs V OUT (Max.) = 5.5 V (@V CC = 0 V or output off state)• Typical V OL ground bounce < 0.8 V (@V CC = 3.3 V, Ta = 25°C)• Typical V OH undershoot > 2.0 V (@V CC = 3.3 V, Ta = 25°C)• High output current ±24 mA (@V CC = 3.0 V to 5.5 V)Function TableInputsG LE D Output QH X X ZL H L LL H H HL L X QlevelH: HighL:Low levelX:ImmaterialZ:High impedanceQ:Level of Q before the indicated steady input conditions were established.HD74LVC16373A Pin Arrangement2HD74LVC16373A3Absolute Maximum RatingsItemSymbol Ratings Unit ConditionsSupply voltage V CC –0.5 to 6.0V Input diode current I IK –50mA V I = –0.5 V Input voltage V I –0.5 to 6.0V Output diode current I OK –50mA V O = –0.5 V 50mA V O = V CC +0.5 V Output voltage V O –0.5 to V CC +0.5V Output "H" or "L"–0.5 to 6.0V Output "Z" or V CC :OFF Output current I O±50mA V CC , GND current / pin I CC or I GND 100mA Storage temperatureTstg–65 to +150°CNote:The absolute maximum ratings are values which must not individually be exceeded, and furthermore,no two of which may be realized at the same time.Recommended Operating ConditonsItemSymbol Ratings Unit Conditions Supply voltage V CC 1.5 to 5.5V Data hold 2.0 to 5.5V At operation Input / output voltageV I 0 to 5.5V G , LE, D V O0 to V CC V Output "H" or "L"0 to 5.5V Output "Z" or V CC :OFFOperating temperature Ta –40 to 85°C Output currentI OH –12mA V CC = 2.7 V –24*2mA V CC = 3.0 V to 5.5 V I OL12mA V CC = 2.7 V 24*2mA V CC = 3.0 V to 5.5 V Input rise / fall time *1t r , t f10ns/VNotes: 1.This item guarantees maximum limit when one input switches.Waveform : Refer to test circuit of switching characteristics.2.duty cycle ≤ 50%HD74LVC16373A4Electrical CharacteristicsTa = –40 to 85°CItem Symbol V CC (V)Min Max Unit Test Conditions Input voltageV IH 2.7 to 3.6 2.0—V 4.5 to 5.5V CC ×0.7—V V IL2.7 to3.6—0.8V4.5 to5.5—V CC ×0.3V Output voltageV OH2.7 to 5.5V CC –0.2—V I OH = –100 µA 2.7 2.2—V I OH = –12 mA3.0 2.4—V 3.0 2.2—V I OH = –24 mA4.53.8—V V OL2.7 to 5.5—0.2V I OL = 100 µA 2.7—0.4V I OL = 12 mA3.0—0.55V I OL = 24 mA4.5—0.55V Input currentI IN 0 to 5.5—±5.0µA V IN = 5.5 V or GND Off state output current I OZ 2.7 to 5.5—±5.0µA V IN = V CC , GNDV OUT = 5.5 V or GND Output leak currentI OFF0—20µA V IN / V OUT = 5.5 V Quiescent supply current I CC2.7 to3.6—±20µA V IN / V OUT = 3.6 to 5.5 V 2.7 to 5.5—20µA V IN = V CC or GND∆I CC3.0 to 3.6—500µAV IN = one input at(V CC –0.6)V,other inputs at V CC or GNDHD74LVC16373A5Switching CharacteristicsTa = –40 to 85°CItemSymbol V CC (V)Min Typ Max Unit From (Input)To (Output)Propagation delay timet PLH 2.7——7.7ns DQt PHL 3.3±0.3 1.5—7.0ns 5.0±0.5—— 5.5ns t PLH 2.7——8.0ns LEQt PHL3.3±0.3 2.0—7.0ns 5.0±0.5—— 5.5ns Output enable timet ZH 2.7——8.0ns GQt ZL3.3±0.3 1.5—7.0ns 5.0±0.5—— 6.0ns Output disable timet HZ 2.7——8.0ns GQt LZ3.3±0.3 1.5—7.0ns 5.0±0.5—— 6.0ns Setup timet su2.7 2.0——ns3.3±0.3 2.0——ns 5.0±0.52.0——ns Hold timet h2.7 1.5——ns3.3±0.3 1.5——ns 5.0±0.51.5——ns Pulse widtht w2.73.0——ns 3.3±0.3 3.0——ns 5.0±0.53.0——ns Between output pins skew *1t OSLH 2.7———ns t OSHL3.3±0.3—— 1.0ns 5.0±0.5—— 1.0ns Input capacitance C IN 2.7— 3.0—pF Output capacitance C O2.7—15.0—pFNote:1.This parameter is characterized but not tested.tos LH = | t PLHm – t PLHn |, tos HL = | t PHLm – t PHLn |HD74LVC16373A Test CircuitWaveforms – 16HD74LVC16373A Waveforms – 2Waveforms – 37HD74LVC16373A Waveforms – 48Hitachi CodeJEDECEIAJWeight (reference value)TTP-48DB——0.20 gUnit: mm*Dimension including the plating thickness Base material dimensionCautions1.Hitachi neither warrants nor grants licenses of any rights of Hitachi’s or any third party’s patent,copyright, trademark, or other intellectual property rights for information contained in this document.Hitachi bears no responsibility for problems that may arise with third party’s rights, includingintellectual property rights, in connection with use of the information contained in this document.2.Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.3.Hitachi makes every attempt to ensure that its products are of high quality and reliability. However,contact Hitachi’s sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation,traffic, safety equipment or medical equipment for life support.4.Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installationconditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.5.This product is not designed to be radiation resistant.6.No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.7.Contact Hitachi’s sales office for any questions regarding this document or Hitachi semiconductor products.Hitachi, Ltd.Semiconductor & Integrated Circuits.Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan Tel: Tokyo (03) 3270-2111 Fax: (03) 3270-5109Copyright ' Hitachi, Ltd., 1999. All rights reserved. Printed in Japan.Hitachi Asia Pte. Ltd.16 Collyer Quay #20-00Hitachi TowerSingapore 049318Tel: 535-2100Fax: 535-1533URLNorthAmerica : http:/Europe : /hel/ecg Asia (Singapore): .sg/grp3/sicd/index.htm Asia (Taiwan): /E/Product/SICD_Frame.htm Asia (HongKong): /eng/bo/grp3/index.htm Japan : http://www.hitachi.co.jp/Sicd/indx.htmHitachi Asia Ltd.Taipei Branch Office3F, Hung Kuo Building. No.167, Tun-Hwa North Road, Taipei (105)Tel: <886> (2) 2718-3666Fax: <886> (2) 2718-8180Hitachi Asia (Hong Kong) Ltd.Group III (Electronic Components)7/F., North Tower, World Finance Centre,Harbour City, Canton Road, Tsim Sha Tsui,Kowloon, Hong Kong Tel: <852> (2) 735 9218Fax: <852> (2) 730 0281 Telex: 40815 HITEC HXHitachi Europe Ltd.Electronic Components Group.Whitebrook ParkLower Cookham Road MaidenheadBerkshire SL6 8YA, United Kingdom Tel: <44> (1628) 585000Fax: <44> (1628) 778322Hitachi Europe GmbHElectronic components Group Dornacher Stra§e 3D-85622 Feldkirchen, Munich GermanyTel: <49> (89) 9 9180-0Fax: <49> (89) 9 29 30 00Hitachi Semiconductor (America) Inc.179 East Tasman Drive,San Jose,CA 95134 Tel: <1> (408) 433-1990Fax: <1>(408) 433-0223For further information write to:。

74HC3G34DC资料

− 500 −

ns ns ns