EM4-DINAV13DDR中文资料

维金Lite方向控制阀门值,G1 8,G1 4和G3 8说明书

3

Strategic Rationale

• To penetrate the global in-line valve market

• $100m addressable market

• Highly competitive product to address the in-line valve market in all regions of the world

• Overview • Specification • Design features • Options & accessories • Viking Lite & Xtreme – product differences

• Price & product positioning • Launch date • Summary

Viking Lite

Directional Control Valves

G1/8, G1/4 & G3/8 Body Ported

08 November 2019

Viking Lite

Table of contents

• Strategic rationale • Product information

Accessories

• Manifold bar - Anodised aluminium • Pressure bar - Anodised aluminium

10

Viking Lite

Table of contents

• Strategic rationale • Product information

EM4150A5WW11中文资料(EM Microelectronic)中文数据手册「EasyDatasheet - 矽搜」

EM微电子

- MARIN SA

EM4150 EM4350

1千比特读/写

非接触式识别装置

描述 该EM4150 / EM4350(以前称为P4150 / P4350) 是CMOS集成电路打算用于电子 读/写射频转发器.该芯片包含1千位 EEPROM,可以由用户来配置,允许写入禁止区,读出防 护护区,和一个连续地读区域输出功率上.存储器可以 通过使用所有写入和读防护护操作32位密码被固定. 密码可以被更新,但从来不看.固定代码序列号和设备标 识是激光编程尽一切芯片独一无二.

Control Word 0 - 7 First Word Read

8 - 15 Last Word Read 16 Password Check On/Off 17 Read After Write On/Off

18 - 31 User available

On means bit set to logic '1' Off means bit set to logic '0'

Device Identification Word & Serial Number Word Laser Programmed - Read Only

图. 6

4

芯片中文手册,看全文,戳

标准读模式

经过上电复位和一个完成时

命令,芯片将执行标准读

模式,将在其中通过连续发送数据,字

从第一之间限定存储器部分字

□ 场频位周期= 64或32学时 □ 170 pF±2%片上谐振电容 □ -40至+ 85°C温度范围 □ 100至150 kHz场频范围 □ 片上整流器和电压限制器 □ 由于无需外部电源缓冲电容

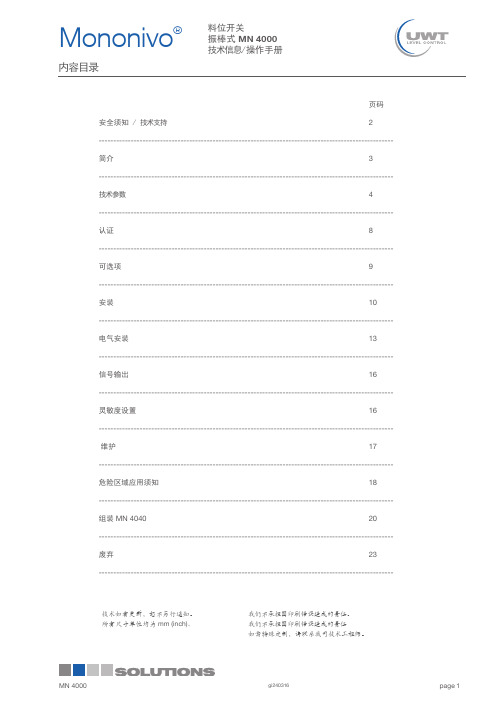

施耐德电气 MN4000 料位开关 振棒式 操作手册说明书

page 内容目录页码安全须知 / 技术支持2-----------------------------------------------------------------------------------------------------简介3-----------------------------------------------------------------------------------------------------技术参数4-----------------------------------------------------------------------------------------------------认证8-----------------------------------------------------------------------------------------------------可选项9-----------------------------------------------------------------------------------------------------安装10-----------------------------------------------------------------------------------------------------电气安装13-----------------------------------------------------------------------------------------------------信号输出16-----------------------------------------------------------------------------------------------------灵敏度设置16----------------------------------------------------------------------------------------------------- 维护17-----------------------------------------------------------------------------------------------------危险区域应用须知18-----------------------------------------------------------------------------------------------------组装 MN 404020-----------------------------------------------------------------------------------------------------废弃23-----------------------------------------------------------------------------------------------------技术如有更新,恕不另行通知。

EEV driver 4 EVD4 circuit diagram说明书

CVSTDUM0R0+050004150 - rel. 1.7 - 09.01.2013Tabella codici / Table of product codesEVD evolutioncode descriptionEVD0000E00EVD Evolution universal (tLAN)EVD0000E01EVD Evolution universal (tLAN),10 pz* (pcs)EVD0000E10EVD Evolution universal (pLAN)EVD0000E11EVD Evolution universal (pLAN),10 pz* (pcs)EVD0000E20EVD Evolution universal (RS485/Modbus®)EVD0000E21EVD Evolution universal (RS485/Modbus®), 10 pz* (pcs)EVD0000E30EVD Evolution for CAREL valves(tLAN)EVD0000E31EVD Evolution for CAREL valves(tLAN), 10 pz* (pcs)EVD0000E40EVD Evolution for CAREL valves(pLAN)EVD0000E41EVD Evolution for CAREL valves(pLAN), 10 pz* (pcs)EVD0000E50EVD Evolution for CAREL valves(RS485/Modbus®)EVD0000E51EVD Evolution for CAREL valves(RS485/Modbus®), 10 pz* (pcs)EVD0002E10EVD Evolution universaloptoisolated (pLAN)EVD0002E20EVD Evolution universaloptoisolated (RS485/Modbus®)(*) La confezione con imballo multiplo non è fornita di connettori / Th e multiple packages are not supplied with connectorsTabella compatibilità valvole / Table of valve compatibilityModel CAREL E*V****ALCOEX4; EX5; EX6; EX7; EX8 330 Hz (consigliato da CAREL/supported by CAREL ); EX8 500 Hz (da specifi che ALCO/from ALCO specifi cations )SPORLAN SEI 0.5-11; SER 1.5-20; SEI 30; SEI 50; SEH 100; SEH175Danfoss ETS 12.5-25B; ETS 50B; ETS 100B; ETS 250; ETS 400; CCM 10-20-30; CCM 40CAREL Due EXV CAREL collegate insieme / Two CAREL ExV connected together SPORLAN SER(I) G, J, K Montaggio scheda display D isplay board mountingC ompatibilità refrigeranti R efrigerant compatibilityR22; R134a; R404A; R407C; R410A; R507A; R290; R600; R600a; R717; R744; R728; R1270; R417A; R422D; R413A; R422A; R423A; R407A; R427A; R245Fa; R407F; R32; HTR01; HTR02For further information, see the “EEV system guide” (code +030220810) and the user manual (code +0300005EN) available at , under the“Literature” section.to be executed.Modalità di connessioni e alimentazione tL AN , pL AN e RS 485tL AN , pL AN and RS 485 connections and power supplyS chema elettrico per il controllo del surriscaldamento / W iring diagram for superheat controlCaso 1: applicazione di più driver collegati in rete, all’interno dello stesso quadro elettrico, alimentati dallo stesso trasformatore Case 1: a series of drivers is connected in a network, installed in the same electrical panel, powered by the same transformerCaso 2: applicazione di più driver collegati in rete, all’interno di quadri elettrici diversi, alimentati da trasformatori diversi (G0 non connesso a terra).Case 2: a series of drivers is connected in a network, installed in electrical diff erent panels, powered by diff erent transformers (G0 not connected to earth).punto di messa a terra.Case 3: a series of drivers is connected in a network, installed in electrical diff erent panels, powered by diff erent transformers with just one earth point.Per ulteriori informazioni, consultare la “Guida al sistema EEV” (codice +030220810) e il manuale d’uso (codice +03000005IT) disponibili sul sito, alla sezione “Documentazione”.procedura di prima messa in servizio.sovraccarico / Use a class 2 safety transformer, suitably protected against short-circuits and voltage surgesCASO 1/ CASE 1:alimentazione 230 Vac con modulo di emergenza/230 Vac power supply with emergency module CASO 3/ CASE 3:alimentazione 24 Vdc/ 24 Vdc power supplydisplay (accessorio/accessory)codedescriptionEVDIS00CN0Display (Chinese)EVDIS00CZ0Display (Czech)EVDIS00DE0Display (German)EVDIS00EN0Display (English)EVDIS00ES0Display (Spanish)EVDIS00FR0Display (French)EVDIS00IT0Display (Italian)EVDIS00JP0Display (Japanese)EVDIS00PL0Display (Polish)EVDIS00PT0Display (Portuguese)EVDIS00RU0Display (Russian)EVDIS00SE0Display (Swedish)altri accessori/other accessoriesEVDCON0021Kit connettori 10 pz*(connector kit 10 pcs)EVDCNV00E0Convertitore USB/tLAN(USB/tLAN converter)TRADRFE240trasformatore 35VA(35VA transformer)EVD0000UC0Modulo Ultracap(Ultracap module)C AREL INDUSTRIES HQsVia dell’Industria, 11 - 35020 Brugine - Padova (Italy)Tel.(+39)0499716611–Fax(+39)0499716600––e-mail:***************+050004150 - rel. 1.7 - 09.01.2013 CAREL si riserva la possibilità di apportare modifi che o cambiamenti ai propri prodotti senza alcun preavviso. / CAREL reserves the right to modify the features of its products without prior notice.。

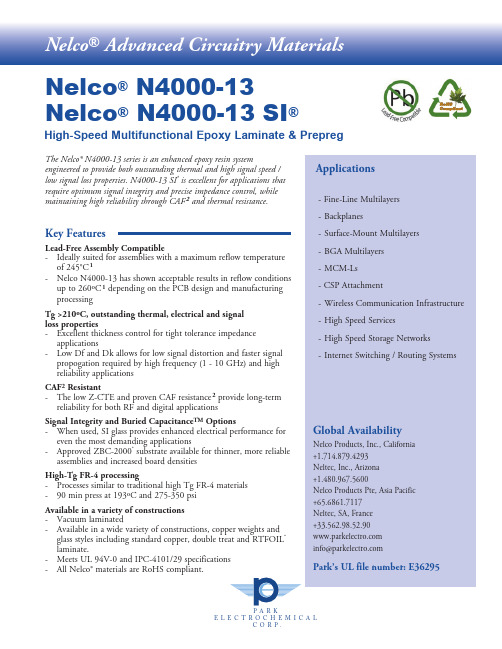

n4000-13(SI)

- Fine-Line Multilayers - B ackplanes- S urface-Mount Multilayers - B GA Multilayers - M CM-Ls - CSP Attachment- W ireless Communication Infrastructure - H igh Speed Services - H igh Speed Storage Networks - I nternet Switching / Routing SystemsThe Nelco® N4000-13 series is an enhanced epoxy resin systemengineered to provide both outstanding thermal and high signal speed / low signal loss properties. N4000-13 SI ® is excellent for applications that require optimum signal integrity and precise impedance control, while maintaining high reliability through CAF2 and thermal resistance.Lead-Free Assembly Compatible- Ideally suited for assemblies with a maximum reflow temperature of 245°C1- Nelco N4000-13 has shown acceptable results in reflow conditions up to 260ºC1 depending on the PCB design and manufacturing processingTg >210ºC, outstanding thermal, electrical and signalloss properties- Excellent thickness control for tight tolerance impedance applications- Low Df and Dk allows for low signal distortion and faster signal propogation required by high frequency (1 - 10 GHz) and high reliability applications CAF 2 Resistant- The low Z-CTE and proven CAF resistance2 provide long-term reliability for both RF and digital applicationsSignal Integrity and Buried Capacitance TM Options- When used, SI glass provides enhanced electrical performance for even the most demanding applications - Approved ZBC-2000® substrate available for thinner, more reliable assemblies and increased board densities High-Tg FR-4 processing- Processes similar to traditional high Tg FR-4 materials - 90 min press at 193ºC and 275-350 psiAvailable in a variety of constructions - Vacuum laminated- Available in a wide variety of constructions, copper weights and glass styles including standard copper, double treat and RTFOIL ® laminate.- Meets UL 94V-0 and IPC-4101/29 specifications - All Nelco® materials are RoHS compliant.Global AvailabilityHigh-Speed Multifunctional Epoxy Laminate & PrepregNelco ® N4000-13Nelco ® N4000-13 SI ®Park’s UL file number: E36295ApplicationsNelco Products, Inc., California+1.714.879.4293Neltec, Inc., Arizona +1.480.967.5600Nelco Products Pte, Asia Pacific +65.6861.7117Neltec, SA, France + info@P A R KE L E C T R O C H E M I C A LC O R P .Rev 4-10Mechanical PropertiesN4000-13-13 SIU.S. Units N4000-13-13 SI MetricTest MethodPeel Strength - 1 oz. (35 micron) Cu After Solder Float7.57.5 lb / inch 1.31 1.31 N / mm IPC-TM-650.2.4.8 At Elevated Temperature8.1 8.1 lb / inch 1.42 1.42 N / mm IPC-TM-650.2.4.8.2a After Exposure to Process Solutions 9.0 9.0 lb / inch 1.58 1.58 N / mm IPC-TM-650.2.4.8X / Y CTE [-40°C to +125°C] 10 - 14 9 - 13 ppm / °C 10 - 14 9 - 13 ppm / °C IPC-TM-650.2.4.41Z Axis CTE Alpha 1 [50°C to Tg] 70 70 ppm / °C 70 70 ppm / °C IPC-TM-650.2.4.41Z Axis CTE Alpha 2 [Tg to 260°C] 280 280 ppm / °C 280 280 ppm / °C IPC-TM-650.2.4.41Z Axis Expansion [50°C to 260°C] 3.5 3.5 %3.5 3.5 %IPC-TM-650.2.4.41Young’s Modulus (X / Y) 4.2 / 3.3 2.4 / 2.3 psi x 106 28.5 / 22.4 16.5 / 15.9 GN / m 2 ASTM D3039Poisson’s Ratios (X / Y) 0.13 / 0.11 0.18 / 0.170.13 / 0.11 0.18 / 0.17ASTM D3039Thermal Conductivity 0.350 0.294 W / mK 0.350 0.294 W / mK ASTM E1461Specific Heat1.201.30J / gK1.20 1.30J / gKASTM E1461Electrical PropertiesDielectric Constant (50% resin content)@ 1 GHz (RF Impedance) 3.73.4 3.7 3.4 IPC-TM-650.2.5.5.9 @ 2.5 GHz (Split Post Cavity) 3.7 3.2 3.7 3.2 @ 10 GHz (Stripline)3.6 3.2 3.6 3.2IPC-TM-650.2.5.5.5@ 10 GHz (Split Post Cavity) 3.7 3.3 3.7 3.3Dissipation Factor (50% resin content) @ 2.5 GHz (Split Post Cavity) 0.009 0.008 0.009 0.008 @ 10 GHz (Stripline)0.009 0.008 0.009 0.008 IPC-TM-650.2.5.5.5@ 10 GHz (Split Post Cavity) 0.0080.0070.0080.007Volume Resistivity C - 96 / 35 / 90 108 108 M Ω - cm 108 108M Ω - cm IPC-TM-650.2.5.17.1 E - 24 / 125 107 108 M Ω - cm107 108 M Ω - cm IPC-TM-650.2.5.17.1Surface Resistivity C - 96 / 35 / 90 107 107 M Ω 107 107 M Ω IPC-TM-650.2.5.17.1E - 24 / 125 107 107 M Ω 107 107 M Ω IPC-TM-650.2.5.17.1Electric Strength 1200 1000 V / mil 4.7x104 3.9x104 V / mm IPC-TM-650.2.5.6.2Dielectric Breakdown >50 >50 kV >50 >50 kV IPC-TM-650.2.5.6Arc Resistance123 123seconds 123 123 seconds IPC-TM-650.2.5.1Thermal PropertiesGlass Transition Temperature (Tg) DSC (°C) 210 210 °C 210 210 °C IPC-TM-650.2.4.25c TMA (°C) 200 200 °C 200 200 °C IPC-TM-650.2.4.24c DMA (°C) (Tan d Peak)240 240 °C 240 240 °C IPC-TM-650.2.4.24.3Degradation Temp (TGA) (5% wt. loss) 350 350 °C 350 350 °C IPC-TM-650.2.4.24.6Pressure Cooker-60 min then solder dip IPC-TM-650.2.6.16 @288°C until failure (max 10 min.) Pass Pass Pass Pass (modified)T260 30+ 30+ minutes 30+ 30+ minutes IPC-TM-650.2.4.24.1T28810+ 10+ minutes 10+ 10+ minutes IPC-TM-650.2.4.24.1Chemical / Physical PropertiesMoisture Absorption 0.10.1 wt. % 0.10.1 wt. % IPC-TM-650.2.6.2.1Methylene Chloride Resistance 0.7 0.7 % wt. chg. 0.7 0.7 % wt. chg. IPC-TM-650.2.3.4.3Density [50% resin content]1.911.79g / cm 31.911.79g / cm 3 Internal MethodNelco N4000-13 and N4000-13 SI ®High-Speed Multifunctional Epoxy Laminate & PrepregP A R KE L E C T R O C H E M I C A LC O R P .Park Electrochemical Corp. is a global advanced materials company which develops and manufactures high-technology digital and RF/microwave printed circuit materials and advanced composite materials. The company operates under the Nelco ®, Nelcote ® and Nova™ names. All test data provided are typical values and not intended to be specification values. For review of critical specification tolerances, please contact a Nelco representative directly. Nelco reserves the right to change these typical values as a natural process of refining our testing equipment and techniques. Nelco reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Nelco does not assume any liability arising out of the application or use of any product described herein; neither does it convey any license under its patent rights nor the rights of others. This disclaimer of warranty is in lieu of all warranties whether expressed, implied or statutory, including implied warranties of merchantability or fitness for a particular purpose.Nelco ®, Neltec ®, Nelcote ®, Nova™, RTFoil ®, SI ® , LD ® and EF ® are trademarks of Park Electrochemical Corp. BC ®, ZBC-2000® and Buried Capacitance™ are Trademarks of the Sanmina-SCI Corporation.1Refer to the N4000-13 Best Practices document and Contract Manufacturing Q&A for PCB processing recommendations. Visit for more information.2CAF resistance has been established to greater than 500 hours using a specific OEM coupon design and test procedure. Visit for more information.。

MEMORY存储芯片N25Q064A13ESE40F中文规格书

DDR3L SDRAMMT41K2G4 – 256 Meg x 4 x 8 banksMT41K1G8 – 128 Meg x 8 x 8 banksMT41K512M16 – 64 Meg x 16 x 8 banksDescriptionDDR3L (1.35V) SDRAM is a low voltage version of the DDR3 (1.5V) SDRAM. Refer to a DDR3 (1.5V) SDRAM data sheet specifications when running in 1.5V com-patible mode.Features•V DD = V DDQ = 1.35V (1.283–1.45V)•Backward compatible to V DD = V DDQ = 1.5V ±0.075V –Supports DDR3L devices to be backward com-patible in 1.5V applications•Differential bidirectional data strobe•8n-bit prefetch architecture•Differential clock inputs (CK, CK#)•8 internal banks•Nominal and dynamic on-die termination (ODT) for data, strobe, and mask signals •Programmable CAS (READ) latency (CL)•Programmable posted CAS additive latency (AL)•Programmable CAS (WRITE) latency (CWL)•Fixed burst length (BL) of 8 and burst chop (BC) of 4 (via the mode register set [MRS])•Selectable BC4 or BL8 on-the-fly (OTF)•Self refresh mode •T C of 0°C to +95°C–64ms, 8192-cycle refresh at 0°C to +85°C–32ms at +85°C to +95°C•Self refresh temperature (SRT)•Automatic self refresh (ASR)•Write leveling•Multipurpose register•Output driver calibrationOptions Marking •Configuration– 2 Gig x 42G4– 1 Gig x 81G8–512 Meg x 16512M16•FBGA package (Pb-free) – x4, x8–78-ball (9mm x 13.2mm)SN •FBGA package (Pb-free) – x16–96-ball (9mm x 14mm)HA •Timing – cycle time– 1.25ns @ CL = 11 (DDR3-1600)-125– 1.07ns @ CL = 13 (DDR3-1866)-107•Operating temperature–Commercial (0°C ≤ T C≤ +95°C)None–Industrial (–40°C ≤ T C≤ +95°C)IT •Revision:ATable 1: Key Timing ParametersNote: 1.Backward compatible to 1600, CL = 11 (-125).WRITE OperationWRITE bursts are initiated with a WRITE command. The starting column and bank ad-dresses are provided with the WRITE command, and auto precharge is either enabled ordisabled for that access. If auto precharge is selected, the row being accessed is pre-charged at the end of the WRITE burst. If auto precharge is not selected, the row willremain open for subsequent accesses. After a WRITE command has been issued, theWRITE burst may not be interrupted. For the generic WRITE commands used in Fig-ure 82 (page 163) through Figure 90 (page 168), auto precharge is disabled.During WRITE bursts, the first valid data-in element is registered on a rising edge ofDQS following the WRITE latency (WL) clocks later and subsequent data elements willbe registered on successive edges of DQS. WRITE latency (WL) is defined as the sum ofposted CAS additive latency (AL) and CAS WRITE latency (CWL): WL = AL + CWL. Thevalues of AL and CWL are programmed in the MR0 and MR2 registers, respectively. Priorto the first valid DQS edge, a full cycle is needed (including a dummy crossover of DQS,DQS#) and specified as the WRITE preamble shown in Figure 82 (page 163). The halfcycle on DQS following the last data-in element is known as the WRITE postamble.The time between the WRITE command and the first valid edge of DQS is WL clocks±t DQSS. Figure 83 (page 164) through Figure 90 (page 168) show the nominal casewhere t DQSS = 0ns; however, Figure 82 (page 163) includes t DQSS (MIN) and t DQSS(MAX) cases.Data may be masked from completing a WRITE using data mask. The data mask occurson the DM ball aligned to the WRITE data. If DM is LOW, the WRITE completes normal-ly. If DM is HIGH, that bit of data is masked.Upon completion of a burst, assuming no other commands have been initiated, the DQwill remain High-Z, and any additional input data will be ignored.Data for any WRITE burst may be concatenated with a subsequent WRITE command toprovide a continuous flow of input data. The new WRITE command can be t CCD clocksfollowing the previous WRITE command. The first data element from the new burst isapplied after the last element of a completed burst. Figure 83 (page 164) and Figure 84(page 164) show concatenated bursts. An example of nonconsecutive WRITEs is shownin Figure 85 (page 165).Data for any WRITE burst may be followed by a subsequent READ command after t WTRhas been met (see Figure 86 (page 165), Figure 87 (page 166), and Figure 88(page 167)).Data for any WRITE burst may be followed by a subsequent PRECHARGE command,providing t WR has been met, as shown in Figure 89 (page 168) and Figure 90(page 168).Both t WTR and t WR starting time may vary, depending on the mode register settings(fixed BC4, BL8 versus OTF).Figure 80: t WPRE TimingDQS - DQS#tt CKCK#。

HPMLDL系列服务器

HPMLDL系列服务器hpML系列服务器HP ProLiant ML110G7(C8R00A)参数规格差不多参数产品类型工作组级产品类别塔式产品结构4U处理器CPU类型奔腾双核CPU型号奔腾双核G860CPU频率3GHzHP ProLiant ML330 G6(600911-AA1)参数规格差不多参数产品类型企业级产品类别塔式产品结构5U处理器CPU类型Intel 至强5600CPU型号Xeon E5620CPU频率 2.4GHz智能加速主2.666GHz频标配CPU1颗数量最大CPU2颗数量制程工艺32nm三级缓存12MB总线规格QPI 5.86GT/sCPU核心四核HP ProLiant ML330 G6(B9D22A)参数规格差不多参数产品类型企业级产品类别塔式产品结构5U处理器CPU类型Intel 至强5600 CPU型号Xeon E5606CPU频率 2.13GHz标配CPU1颗数量最大CPU2颗数量制程工艺32nm三级缓存8MB总线规格QPI 4.8GT/sHP ProLiant ML330 G6(600911-AA1)参数规格差不多参数产品类型企业级产品类别塔式产品结构5U处理器CPU类型Intel 至强5600CPU型号Xeon E5620CPU频率 2.4GHz智能加速主2.666GHz频标配CPU1颗数量最大CPU2颗数量制程工艺32nm三级缓存12MB总线规格QPI 5.86GT/sCPU核心四核HP ProLiant ML350 G6(638180-AA1)参数规格差不多参数产品类别塔式产品结构5U处理器CPU类型Intel 至强5600CPU型号Xeon E5606CPU频率 2.13GHz标配CPU1颗数量最大CPU2颗数量制程工艺32nm三级缓存8MB总线规格QPI 4.8GT/sCPU核心四核CPU线程四线程数主板HP ProLiant ML350 G6(600431-AA5)参数规格差不多参数产品类别塔式产品结构5U处理器CPU类型Intel 至强5600CPU型号Xeon E5620CPU频率 2.4GHz智能加速主2.666GHz频标配CPU1颗数量最大CPU2颗数量制程工艺32nm三级缓存12MB总线规格QPI 5.86GT/sCPU核心四核CPU线程八线程数HP ProLiant ML350 G6(594869-AA1)参数规格差不多参数产品类别塔式产品结构5U处理器CPU类型Intel 至强5600CPU型号Xeon E5620CPU频率 2.4GHz智能加速主2.666GHz频标配CPU1颗数量最大CPU2颗数量制程工艺32nm三级缓存12MB总线规格QPI 5.86GT/sCPU核心四核CPU线程八线程数HP ProLiant ML310e Gen8(686146-AA5)参数规格差不多参数产品类型企业级产品类别塔式产品结构4U处理器CPU类型Intel 至强E3-1200 v2 CPU型号Xeon E3-1220 v2CPU频率 3.1GHz标配CPU1颗数量最大CPU4颗数量制程工艺22nm三级缓存8MB总线规格DMI 5GT/sHP ProLiant ML310e Gen8(686147-AA5)参数规格差不多参数产品类型企业级产品类别塔式产品结构4U处理器CPU类型Intel 至强E3-1200 v2 CPU型号Xeon E3-1240 v2CPU频率 3.4GHz智能加速主3.8GHz频标配CPU1颗数量最大CPU4颗数量制程工艺22nm三级缓存8MBHP ProLiant ML350e Gen8(C3Q10A)参数规格差不多参数产品类型企业级产品类别塔式产品结构5U处理器CPU类型Intel 至强E5-2400 CPU型号Xeon E5-2403CPU频率 1.8GHz标配CPU1颗数量最大CPU4颗数量制程工艺32nm三级缓存10MB总线规格QPI 6.4GT/sHP ProLiant ML350e Gen8(C3Q08A)参数规格差不多参数产品类型企业级产品类别塔式产品结构5U处理器CPU类型Intel 至强E5-2400 CPU型号Xeon E5-2407CPU频率 2.2GHz标配CPU1颗数量最大CPU4颗数量制程工艺32nm三级缓存10MB总线规格QPI 6.4GT/sHP ProLiant ML350e Gen8(C3Q09A)参数规格差不多参数产品类型企业级产品类别塔式产品结构5U处理器CPU类型Intel 至强E5-2400 CPU型号Xeon E5-2420CPU频率 1.9GHz标配CPU1颗数量最大CPU4颗数量制程工艺32nm三级缓存15MB总线规格QPI 6.4GT/sHP ProLiant ML350e Gen8(C3F91A)参数规格差不多参数产品类型企业级产品类别塔式产品结构5U处理器CPU类型Intel 至强E5-2400 CPU型号Xeon E5-2430CPU频率 2.2GHz标配CPU1颗数量最大CPU4颗数量制程工艺32nm三级缓存15MB总线规格QPI 6.4GT/sHP ProLiant ML350p Gen8(646675-AA1)参数规格差不多参数产品类别塔式产品结构5U处理器CPU类型Intel 至强E5-2600 CPU型号Xeon E5-2609CPU频率 2.4GHz标配CPU1颗数量最大CPU2颗数量制程工艺32nm三级缓存10MB总线规格QPI 6.4GT/sHP ProLiant ML350p Gen8(668271-AA5)参数规格差不多参数产品类别塔式产品结构5U处理器CPU类型Intel 至强E5-2600 CPU型号Xeon E5-2620CPU频率2GHz智能加速主2.5GHz频标配CPU1颗数量最大CPU2颗数量制程工艺32nm。

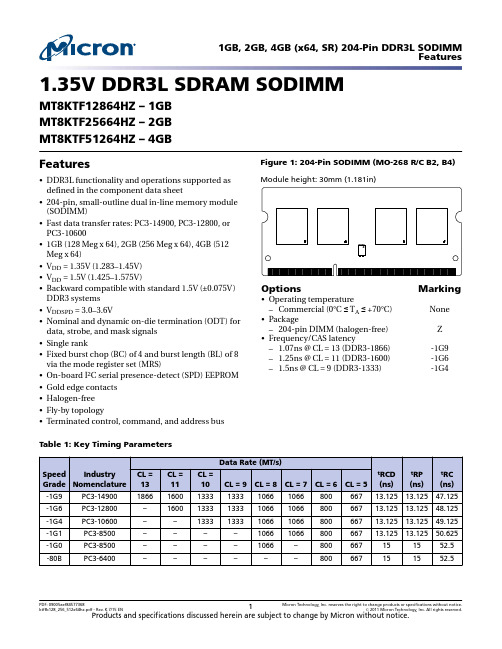

MT8KTF51264HZ-1G6E1

1.35V DDR3L SDRAM SODIMMMT8KTF12864HZ – 1GB MT8KTF25664HZ – 2GB MT8KTF51264HZ – 4GB Features•DDR3L functionality and operations supported as defined in the component data sheet•204-pin, small-outline dual in-line memory module (SODIMM)•Fast data transfer rates: PC3-14900, PC3-12800, or PC3-10600•1GB (128 Meg x 64), 2GB (256 Meg x 64), 4GB (512Meg x 64)•V DD = 1.35V (1.283–1.45V)•V DD = 1.5V (1.425–1.575V)•Backward compatible with standard 1.5V (±0.075V)DDR3 systems •V DDSPD = 3.0–3.6V•Nominal and dynamic on-die termination (ODT) for data, strobe, and mask signals •Single rank•Fixed burst chop (BC) of 4 and burst length (BL) of 8via the mode register set (MRS)•On-board I 2C serial presence-detect (SPD) EEPROM •Gold edge contacts •Halogen-free •Fly-by topology•Terminated control, command, and address bus Figure 1: 204-Pin SODIMM (MO-268 R/C B2, B4)Module height: 30mm (1.181in)OptionsMarking•Operating temperature–Commercial (0°C ≤ T A ≤ +70°C)None •Package–204-pin DIMM (halogen-free)Z •Frequency/CAS latency– 1.07ns @ CL = 13 (DDR3-1866)-1G9– 1.25ns @ CL = 11 (DDR3-1600)-1G6– 1.5ns @ CL = 9 (DDR3-1333)-1G4Table 1: Key Timing ParametersTable 2: AddressingTable 3: Part Numbers and Timing Parameters – 1GB Modules1Table 4: Part Numbers and Timing Parameters – 2GB Modules1Table 5: Part Numbers and Timing Parameters – 4GB Modules1Notes: 1.The data sheet for the base device can be found on Micron’s web site.2.All part numbers end with a two-place code (not shown) that designates component and PCB revisions.Consult factory for current revision codes. Example: MT8KSF51264HZ-1G9P1.Pin AssignmentsTable 6: Pin AssignmentsNotes: 1.Pin 78 is NF for 1GB and 2GB; A15 for 4GB.2.Pin 80 is NF for 1GB; A14 for 2GB and 4GB.Pin DescriptionsThe pin description table below is a comprehensive list of all possible pins for all DDR3modules. All pins listed may not be supported on this module. See Pin Assignments forinformation specific to this module.Table 7: Pin DescriptionsTable 7: Pin Descriptions (Continued)DQ MapsTable 8: Component-to-Module DQ Map, R/C B2 (PCB 1092)Table 9: Component-to-Module DQ Map, R/C B4 (PCB 1348)Functional Block Diagram Figure 2: Functional Block DiagramS0#A[15/14/13:0]RAS#WE#CKE0A[15/14/13:0]: DDR3 SDRAMWE#: DDR3 SDRAMCKE0: DDR3 SDRAMRESET#: DDR3 SDRAMCK0CK0#CK1CK1#V REFCAV SSV DDControl, command,and address terminationV DDSPDV TTV REFDQClock, control, command, and address line terminations:TTV DDNote: 1.The ZQ ball on each DDR3 component is connected to an external 240Ω ±1% resistorthat is tied to ground. It is used for the calibration of the component’s ODT and outputdriver.1GB, 2GB, 4GB (x64, SR) 204-Pin DDR3L SODIMMFunctional Block DiagramGeneral DescriptionDDR3 SDRAM modules are high-speed, CMOS dynamic random access memory mod-ules that use internally configured 8-bank DDR3 SDRAM devices. DDR3 SDRAM mod-ules use DDR architecture to achieve high-speed operation. DDR3 architecture is essen-tially an 8n-prefetch architecture with an interface designed to transfer two data wordsper clock cycle at the I/O pins. A single read or write access for the DDR3 SDRAM mod-ule effectively consists of a single 8n-bit-wide, one-clock-cycle data transfer at the inter-nal DRAM core and eight corresponding n-bit-wide, one-half-clock-cycle data transfersat the I/O pins.DDR3 modules use two sets of differential signals: DQS, DQS# to capture data and CKand CK# to capture commands, addresses, and control signals. Differential clocks anddata strobes ensure exceptional noise immunity for these signals and provide precisecrossing points to capture input signals.Fly-By TopologyDDR3 modules use faster clock speeds than earlier DDR technologies, making signalquality more important than ever. For improved signal quality, the clock, control, com-mand, and address buses have been routed in a fly-by topology, where each clock, con-trol, command, and address pin on each DRAM is connected to a single trace and ter-minated (rather than a tree structure, where the termination is off the module near theconnector). Inherent to fly-by topology, the timing skew between the clock and DQS sig-nals can be easily accounted for by using the write-leveling feature of DDR3.Serial Presence-Detect EEPROM OperationDDR3 SDRAM modules incorporate serial presence-detect. The SPD data is stored in a256-byte EEPROM. The first 128 bytes are programmed by Micron to comply withJEDEC standard JC-45, "Appendix X: Serial Presence Detect (SPD) for DDR3 SDRAMModules." These bytes identify module-specific timing parameters, configuration infor-mation, and physical attributes. The remaining 128 bytes of storage are available for useby the customer. System READ/WRITE operations between the master (system logic)and the slave EEPROM device occur via a standard I2C bus using the DIMM’s SCL(clock) SDA (data), and SA (address) pins. Write protect (WP) is connected to V SS, per-manently disabling hardware write protection. For further information refer to Microntechnical note TN-04-42, "Memory Module Serial Presence-Detect."Electrical SpecificationsStresses greater than those listed may cause permanent damage to the module. This is astress rating only, and functional operation of the module at these or any other condi-tions outside those indicated in each device's data sheet is not implied. Exposure to ab-solute maximum rating conditions for extended periods may adversely affect reliability. Table 10: Absolute Maximum RatingsTable 11: Operating ConditionsNotes: 1.Module is backward-compatible with 1.5V operation. Refer to device specification fordetails and operation guidance.2.V TT termination voltage in excess of the stated limit will adversely affect the commandand address signals’ voltage margin and will reduce timing margins.3.T A and T C are simultaneous requirements.4.For further information, refer to technical note TN-00-08: “Thermal Applications,”available on Micron’s web site.5.The refresh rate is required to double when 85°C < T C≤ 95°C.DRAM Operating ConditionsRecommended AC operating conditions are given in the DDR3 component data sheets.Component specifications are available at . Module speed grades correlatewith component speed grades, as shown below.Table 12: Module and Component Speed GradesDesign ConsiderationsSimulationsMicron memory modules are designed to optimize signal integrity through carefully de-signed terminations, controlled board impedances, routing topologies, trace lengthmatching, and decoupling. However, good signal integrity starts at the system level.Micron encourages designers to simulate the signal characteristics of the system'smemory bus to ensure adequate signal integrity of the entire memory system.PowerOperating voltages are specified at the DRAM, not at the edge connector of the module.Designers must account for any system voltage drops at anticipated power levels to en-sure the required supply voltage is maintained.I DD SpecificationsTable 13: DDR3 I DD Specifications and Conditions – 1GB (Die Revision J)Values are for the MT41K128M8 DDR3L SDRAM only and are computed from values specified in the 1.35V 1GbTable 14: DDR3 I DD Specifications and Conditions – 2GB (Die Revision K)Values are for the MT41K256M8 DDR3L SDRAM only and are computed from values specified in the 1.35V 2GbTable 15: DDR3 I DD Specifications and Conditions – 4GB (Die Revision E)Values are for the MT41K512M8 DDR3L SDRAM only and are computed from values specified in the 1.35V 4GbTable 16: DDR3 I DD Specifications and Conditions – 4GB (Die Revision N)Values are for the MT41K512M8 DDR3L SDRAM only and are computed from values specified in the 1.35V 4GbTable 17: DDR3 I DD Specifications and Conditions – 4GB (Die Revision P)Values are for the MT41K512M8 DDR3L SDRAM only and are computed from values specified in the 1.35V 4GbSerial Presence-Detect EEPROMFor the latest SPD data, refer to Micron's SPD page: /spd .Table 18: Serial Presence-Detect EEPROM DC Operating ConditionsTable 19: Serial Presence-Detect EEPROM AC Operating ConditionsNotes:1.Guaranteed by design and characterization, not necessarily tested.2.To avoid spurious start and stop conditions, a minimum delay is placed between the fall-ing edge of SCL and the falling or rising edge of SDA.3.For a restart condition, or following a WRITE cycle.1GB, 2GB, 4GB (x64, SR) 204-Pin DDR3L SODIMMSerial Presence-Detect EEPROMModule DimensionsFigure 3: 204-Pin DDR3 SODIMM3.8 (0.150)1.8 (0.071)(2X)2.0 (0.079) RFront viewTYP45° 4XNotes:1.All dimensions are in millimeters (inches); MAX/MIN or typical (TYP) where noted.2.The dimensional diagram is for reference only.8000 S. Federal Way, P .O. Box 6, Boise, ID 83707-0006, Tel: 208-368-4000/products/support Sales inquiries: 800-932-4992Micron and the Micron logo are trademarks of Micron Technology, Inc.All other trademarks are the property of their respective owners.This data sheet contains minimum and maximum limits specified over the power supply and temperature range set forth herein.Although considered final, these specifications are subject to change, as further product development and data characterization some-times occur.1GB, 2GB, 4GB (x64, SR) 204-Pin DDR3L SODIMMModule DimensionsMouser ElectronicsAuthorized DistributorClick to View Pricing, Inventory, Delivery & Lifecycle Information:M icron Technology:MT8KTF25664HZ-1G6K1MT8KTF51264HZ-1G6P1MT8KTF51264HZ-1G9P1MT8KTF51264HZ-1G6N1。

MEMORY存储芯片N25Q512A13GSF40中文规格书

Output Electrical Characteristics and Operating Conditions Table 18: Differential AC Output ParametersNote: 1.The typical value of V OX(AC) is expected to be about 0.5 × V DDQ of the transmitting de-vice and V OX(AC) is expected to track variations in V DDQ . V OX(AC) indicates the voltage atwhich differential output signals must cross.Figure 15: Differential Output Signal LevelsV OXV SSQV DDQTable 19: Output DC Current DriveNotes: 1.For I OH(DC); V DDQ = 1.7V, V OUT = 1,420mV. (V OUT - V DDQ )/I OH must be less than 21˖ for val-ues of V OUT between V DDQ and V DDQ - 280mV.2.For I OL(DC); V DDQ = 1.7V, V OUT = 280mV. V OUT /I OL must be less than 21˖ for values of V OUT between 0V and 280mV.3.The DC value of V REF applied to the receiving device is set to V TT .4.The values of I OH(DC) and I OL(DC) are based on the conditions given in Notes 1 and 2. They are used to test device drive current capability to ensure V IH,min plus a noise margin and V IL,max minus a noise margin are delivered to an SSTL_18 receiver. The actual current val-ues are derived by shifting the desired driver operating point (see output IV curves)along a 21˖ load line to define a convenient driver current for measurement.2Gb: x4, x8, x16 DDR2 SDRAM Output Electrical Characteristics and Operating ConditionsExtended Mode Register (EMR)The extended mode register controls functions beyond those controlled by the mode register; these additional functions are DLL enable/disable, output drive strength, on-die termination (ODT), posted AL, off-chip driver impedance calibration (OCD), DQS#enable/disable, RDQS/RDQS# enable/disable, and output disable/enable. These func-tions are controlled via the bits shown in Figure 38. The EMR is programmed via the LM command and will retain the stored information until it is programmed again or the de-vice loses power. Reprogramming the EMR will not alter the contents of the memory ar-ray, provided it is performed correctly.The EMR must be loaded when all banks are idle and no bursts are in progress, and the controller must wait the specified time t MRD before initiating any subsequent opera-tion. Violating either of these requirements could result in an unspecified operation.Figure 38: EMR Definition21Notes: 1.E16 (BA2) is only applicable for densities ุ1Gb, reserved for future use, and must be pro-grammed to 0.2.Mode bits (E n ) with corresponding address balls (A n ) greater than E12 (A12) are re-served for future use and must be programmed to 0.3.Not all listed AL options are supported in any individual speed grade.4.As detailed in the Initialization section notes, during initialization of the OCD operation,all three bits must be set to 1 for the OCD default state, then set to 0 before initializa-tion is finished.2Gb: x4, x8, x16 DDR2 SDRAM Extended Mode Register (EMR)Table 44: Truth Table – CKENotes: 1.CKE (n ) is the logic state of CKE at clock edge n ; CKE (n - 1) was the state of CKE at theprevious clock edge.2.Current state is the state of the DDR2 SDRAM immediately prior to clock edge n .mand (n ) is the command registered at clock edge n , and action (n ) is a result of command (n ).4.The state of ODT does not affect the states described in this table. The ODT function is not available during self refresh (see ODT Timing (page 129) for more details and spe-cific restrictions).5.Power-down modes do not perform any REFRESH operations. The duration of power-down mode is therefore limited by the refresh requirements.6.“X” means “Don’t Care” (including floating around V REF ) in self refresh and power-down. However, ODT must be driven high or low in power-down if the ODT function is enabled via EMR.7.All states and sequences not shown are illegal or reserved unless explicitly described elsewhere in this document.8.Valid commands for power-down entry and exit are NOP and DESELECT only.9.On self refresh exit, DESELECT or NOP commands must be issued on every clock edge oc-curring during the t XSNR period. READ commands may be issued only after t XSRD (200clocks) is satisfied.10.Valid commands for self refresh exit are NOP and DESELECT only.11.Power-down and self refresh can not be entered while READ or WRITE operations,LOAD MODE operations, or PRECHARGE operations are in progress. See SELF REFRESH (page 117) and SELF REFRESH (page 78) for a list of detailed restrictions.12.Minimum CKE high time is t CKE = 3 × t CK. Minimum CKE LOW time is t CKE = 3 × t CK.This requires a minimum of 3 clock cycles of registration.13.Self refresh mode can only be entered from the all banks idle state.14.Must be a legal command, as defined in Table 37 (page 72).2Gb: x4, x8, x16 DDR2 SDRAM Power-Down Mode。

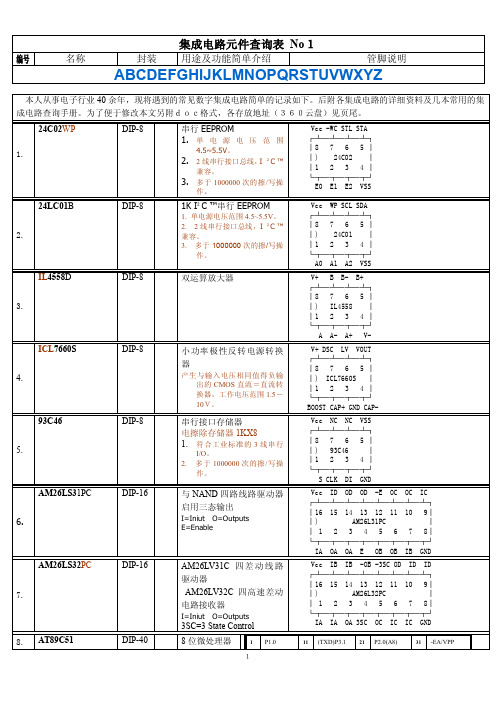

集成电路元件查询表

4 P1.3

14 (T0)P3.4

24 P2.3(A11)

34 P0.5(AD5)

5 P1.4

15 (T1)P3.5

25 P2.4(A12) 35 P0.4(AD4)

6 P1.5

16 (-WR)P3.6 26 P2.5(A13) 36 P0.3(AD3)

7 P1.6

17 (-RD)P3.7

27 P2.6(A14)

┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐

│20 19 18 17 16 15 14 13 12 11│

│)

UPD424256

Hale Waihona Puke ││1 2 3 4 5 6 7 8 9 10│

└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘

I/O1 I/O2–WE–RAS NC A0 A1 A2 A3 VCC

X4 快速页模式 DRAM\n 同上

SNI 的串行网 1 COL

络接口

2 RXD

│

│ 1 2 3 4 5 6 7 8│

└┬─┬─┬─┬─┬─┬─┬─┬┘

IA IA OA 3SC OC IC IC GND

11 (TXD)P3.1 21 P2.0(A8)

31 -EA/VPP

编号

名称

AT89S52 9.

ATMEG16A 10.

CA3096E

11.

12. CA3140

集成电路元件查询表 No2

-CS

5 A3

12

VSS

19

A10

6 A2

13

I/O4

20

-OE

7 A1

14

I/O5

21

-WE

多通道光电耦合器与光电

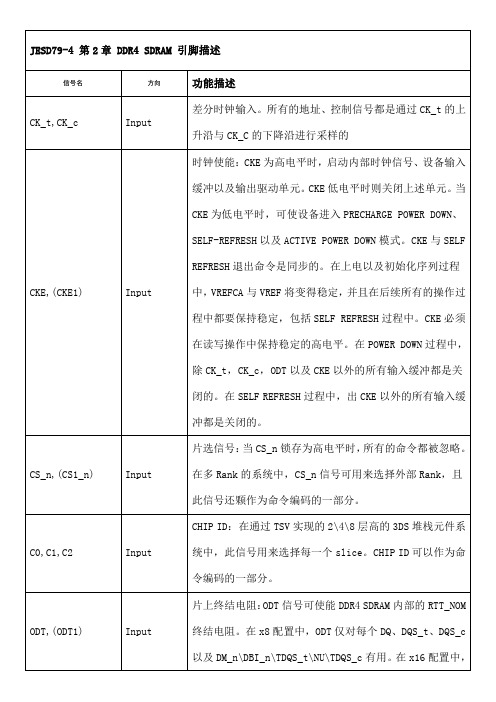

JE第章DDRSDRAM引脚描述

Input

Bank组输入:BG0-BG1可以选择当前的ACT、RD、WRT或是PRE命令是对哪一个Bank组进行操作。在MRS命令中,BG0也参与模式寄存器的选择。在x4、x8系统中,有BG0与BG1,而x16系统中,仅有BG0。

A0-A17

Input

地址总线:在ACT命令中作为行地址,在读写命令中作为列地址,从而可定位到存储阵列中的确定位置。(A10/AP, A12/BC_n, RAS_n/A16, CAS_n/A15 与 WE_n/A14可作为额外的地址总线使用。在MRS命令中,地址总线还作为操作码使用,即写入模式寄存器的值。A17仅在x4系统中可用。

A10/AP

Input

自动刷新:此位可控制在完成读写操作好是否进行自动刷新操作,高电平为开启自动刷新,低电平为关闭自动刷新。在PRE命令中,A10为还可作为是否进行全bank操作的开关。如果仅有一个bank进行刷新,则由bank地址来确定哪个bank来进行操作。

A12/BC_n

Input

Burst选择:在选择On-The-Fly时,此位作为Burst长度的选择信号。具体细节参考命令真值表。

TDQS_t,TDQS_c

Output

终端数据选通:TDQS_t\TDQS_c仅在x8系统中应用。当MR1寄存器中的A11为高电平时,DRAM就会使能相似终端阻抗(same termination resistance)功能,同时TDQS_c与TDQS_t将会应用与DQS_t\DQS_c。当MR1寄存器中的A11为低电平时,DM\DBI\TDQS将会作为数据掩码或数据总线翻转功能使用,且A11、A12、A10与TDQS_c都不会使用。在x4与x16 DRAM中TDQS必须是禁止的,也就是MR1寄存器中的A11为永远为低电平。

MMSZ4xxxT1G系列和SZMMSZ4xxxT1G系列零点电阻电源器件的商品说明书

MMSZ4686T1G MMSZ4686T1G.MMSZ4xxxT1G Series, SZMMSZ4xxxT1G Series Zener Voltage Regulators 500 mW, Low I ZT SOD−123 Surface MountThree complete series of Zener diodes are offered in the convenient, surface mount plastic SOD−123 package. These devices provide a convenient alternative to the leadless 34−package style.Features•500 mW Rating on FR−4 or FR−5 Board•Wide Zener Reverse V oltage Range − 1.8 V to 43 V•Low Reverse Current (I ZT) − 50 m A•Package Designed for Optimal Automated Board Assembly •Small Package Size for High Density Applications•ESD Rating of Class 3 (>16 kV) per Human Body Model•SZ Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC−Q101 Qualified and PPAP Capable•These Devices are Pb−Free and are RoHS Compliant*Mechanical Characteristics:CASE:V oid-free, transfer-molded, thermosetting plastic case FINISH:Corrosion resistant finish, easily solderableMAXIMUM CASE TEMPERATURE FOR SOLDERING PURPOSES: 260°C for 10 SecondsPOLARITY:Cathode indicated by polarity band FLAMMABILITY RATING:UL 94 V−0MAXIMUM RATINGSRating Symbol Max Units Total Power Dissipation on FR−5 Board,(Note 1) @ T L = 75°CDerated above 75°C P D5006.7mWmW/°CThermal Resistance, (Note 2) Junction−to−Ambient R q JA340°C/WThermal Resistance, (Note 2) Junction−to−Lead R q JL150°C/WJunction and Storage Temperature Range T J, T stg−55 to+150°CStresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.1.FR−5 = 3.5 X 1.5 inches, using the minimum recommended footprint.2.Thermal Resistance measurement obtained via infrared Scan Method.*For additional information on our Pb−Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.Cathode AnodeSee specific marking information in the device marking column of the Electrical Characteristics table on page 3 of this data sheet.DEVICE MARKING INFORMATIONSOD−123CASE 425STYLE 1Device Package Shipping†ORDERING INFORMATIONMARKING DIAGRAM†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our T ape and Reel Packaging Specifications Brochure, BRD8011/D.MMSZ4xxxT1G SOD−123(Pb−Free)3,000 /Tape & ReelMMSZ4xxxT3G SOD−123(Pb−Free)10,000 /Tape & Reel xx= Device Code (Refer to page 3)M= Date CodeG= Pb−Free Package(Note: Microdot may be in either location)1SZMMSZ4xxxT1G SOD−123(Pb−Free)3,000 /Tape & ReelSZMMSZ4xxxT3G SOD−123(Pb−Free)10,000 /Tape & ReelELECTRICAL CHARACTERISTICS (T A = 25°C unless otherwise noted, V F = 0.9 V Max. @ I F = 10 mA)Symbol ParameterV Z Reverse Zener Voltage @ I ZTI ZT Reverse CurrentI R Reverse Leakage Current @ V RVR Reverse VoltageI F Forward CurrentV F Forward Voltage @ I FProduct parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.ELECTRICAL CHARACTERISTICS (T A = 25°C unless otherwise noted, V F = 0.9 V Max. @ I F = 10 mA)Device*DeviceMarkingZener Voltage (Note 3)Leakage CurrentV Z (Volts)@ I ZT I R @ V RMin Nom Max m A m A VoltsMMSZ4678T1G CC 1.71 1.8 1.89507.51 MMSZ4679T1G CD 1.90 2.0 2.105051 MMSZ4680T1G CE 2.09 2.2 2.315041 MMSZ4681T1G CF 2.28 2.4 2.525021 MMSZ4682T1G CH 2.565 2.7 2.8355011 MMSZ4683T1G CJ 2.85 3.0 3.15500.81 MMSZ4684T1G CK 3.13 3.3 3.47507.5 1.5 MMSZ4685T1G CM 3.42 3.6 3.78507.52 MMSZ4686T1G CN 3.70 3.9 4.105052 MMSZ4687T1G CP 4.09 4.3 4.525042 SZMMSZ4687T1G CG6 4.09 4.3 4.525042 MMSZ4688T1G CT 4.47 4.7 4.9450103 MMSZ4689T1G CU 4.85 5.1 5.3650103 MMSZ4690T1G/T3G CV 5.32 5.6 5.8850104 MMSZ4691T1G CA 5.89 6.2 6.5150105 MMSZ4692T1G CX 6.46 6.87.145010 5.1 MMSZ4693T1G CY7.137.57.885010 5.7 MMSZ4694T1G CZ7.798.28.61501 6.2 MMSZ4695T1G DC8.278.79.14501 6.6 MMSZ4696T1G DD8.659.19.56501 6.9 MMSZ4697T1G DE9.501010.505017.6 MMSZ4698T1G DF10.451111.55500.058.4 MMSZ4699T1G DH11.401212.60500.059.1 MMSZ4700T1G DJ12.351313.65500.059.8 MMSZ4701T1G DK13.301414.70500.0510.6 MMSZ4702T1G DM14.251515.75500.0511.4 MMSZ4703T1G†DN15.201616.80500.0512.1 MMSZ4704T1G DP16.151717.85500.0512.9 MMSZ4705T1G DT17.101818.90500.0513.6 MMSZ4706T1G DU18.051919.95500.0514.4 MMSZ4707T1G DV19.002021.00500.0115.2 MMSZ4708T1G DA20.902223.10500.0116.7 MMSZ4709T1G DX22.802425.20500.0118.2 MMSZ4710T1G DY23.752526.25500.0119.0 MMSZ4711T1G†EA25.652728.35500.0120.4 MMSZ4712T1G EC26.602829.40500.0121.2 MMSZ4713T1G ED28.503031.50500.0122.8 MMSZ4714T1G EE31.353334.65500.0125.0 MMSZ4715T1G EF34.203637.80500.0127.3 MMSZ4716T1G EH37.053940.95500.0129.6 MMSZ4717T1G EJ40.854345.15500.0132.6 3.Nominal Zener voltage is measured with the device junction in thermal equilibrium at T L = 30°C ±1°C.*Include SZ-prefix devices where applicable.†MMSZ4703 and MMSZ4711 Not Available in 10,000/Tape & ReelTYPICAL CHARACTERISTICSV Z , T E M P E R A T U R E C O E F F I C I E N T (m V /C )°θV Z , NOMINAL ZENER VOLTAGE (V)Figure 1. Temperature Coefficients (Temperature Range −55°C to +150°C)V Z , T E M P E R A T U R E C O E F F I C I E N T (m V /C )°θ100101V Z , NOMINAL ZENER VOLTAGE (V)Figure 2. Temperature Coefficients (Temperature Range −55°C to +150°C)1.21.00.80.60.40.20T, TEMPERATURE (5C)Figure 3. Steady State Power Derating P p k, P E A K S U R G E P O W E R (W A T T S )PW, PULSE WIDTH (ms)Figure 4. Maximum Nonrepetitive Surge PowerP D , P O W E R D I S S I P A T I O N (W A T T S )V Z , NOMINAL ZENER VOLTAGEFigure 5. Effect of Zener Voltage onZener ImpedanceZ Z T , D Y N A M I C I M P E D A N C E ()ΩTYPICAL CHARACTERISTICSC , C A P A C I T A N C E (p F )V Z , NOMINAL ZENER VOLTAGE (V)Figure 6. Typical Capacitance 1000100101V Z , ZENER VOLTAGE (V)1001010.10.01I Z , Z EN E R C U R R E N T (m A )V Z , ZENER VOLTAGE (V)1001010.10.01I R , L E A K A G E C U R R E N T (A )μV Z , NOMINAL ZENER VOLTAGE (V)Figure 7. Typical Leakage Current10001001010.10.010.0010.00010.00001I Z , Z E N E R C U R R E N T (m A )Figure 8. Zener Voltage versus Zener Current(V Z Up to 12 V)Figure 9. Zener Voltage versus Zener Current(12 V to 91 V)SOD−123CASE 425−04ISSUE GDATE 07 OCT 2009SCALE 5:1NOTES:1.DIMENSIONING AND TOLERANCING PER ANSIY14.5M, 1982.2.CONTROLLING DIMENSION: INCH.DIM MIN NOM MAXMILLIMETERSINCHESA0.94 1.17 1.350.037A10.000.050.100.000b0.510.610.710.020c1.600.150.055D 1.40 1.80E 2.54 2.69 2.840.100---3.680.140L0.253.860.0100.0460.0020.0240.0630.1060.1450.0530.0040.0280.0710.1120.152MIN NOM MAX3.56H E---------0.006------------GENERICMARKING DIAGRAM**For additional information on our Pb−Free strategy and solderingdetails, please download the ON Semiconductor Soldering andMounting Techniques Reference Manual, SOLDERRM/D.SOLDERING FOOTPRINT**This information is generic. Please refer to device datasheet for actual part marking. Pb−Free indicator, “G” ormicrodot “ G”, may or may not be present.XXX= Specific Device CodeM= Date CodeG= Pb−Free Package1STYLE 1:PIN 1. CATHODE2. ANODE0.910.036ǒmminchesǓSCALE 10:1------q001010°°°°(Note: Microdot may be in either location) MECHANICAL CASE OUTLINEPACKAGE DIMENSIONSON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries.ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor theON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries.ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor’s product/patent coverage may be accessed at ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.PUBLICATION ORDERING INFORMATIONTECHNICAL SUPPORTNorth American Technical Support:Voice Mail: 1 800−282−9855 Toll Free USA/Canada Phone: 011 421 33 790 2910LITERATURE FULFILLMENT :Email Requests to:*******************ON Semiconductor Website: Europe, Middle East and Africa Technical Support:Phone: 00421 33 790 2910For additional information, please contact your local Sales RepresentativeMMSZ4686T1G MMSZ4686T1G.。

莫贾V2416A系列迷你型无风扇、振动防护计算机产品介绍说明书

V2416A SeriesCompact,fanless,vibration-proof computers for rolling stock applicationsFeatures and Benefits•Intel Celeron/Core i7processor•Two hot-swappable2.5-inch HDD or SSD storage expansion trays•Dual independent DVI-I displays•2Gigabit Ethernet ports with M12X-coded connectors•2CFast sockets for OS backup•M12A-coded power connector•Compliant with EN50121-4•Complies with all EN50155mandatory test items1•IEC61373certified for shock and vibration resistance•Ready-to-run Debian7,Windows Embedded Standard7,and Windows10Embedded IoT Enterprise2016LTSB platforms•-40to70°C wide-temperature models available•Supports SNMP-based system configuration,control,and monitoring(Windows only)CertificationsIntroductionThe V2416A Series embedded computers are based on the Intel3rd Gen processor and feature4RS-232/422/485serial ports,dual LAN ports,and 3USB2.0hosts.In addition,the V2416A computers provide dual DVI-I outputs and comply with the mandatory test items of the EN50155 standard,making them suitable for a variety of industrial applications.The CFast socket,SATA connectors,and USB sockets provide the V2416A computers with the reliability needed for industrial applications that require data buffering and storage expansion.Most importantly,the V2416A computers come with2hot-swappable storage trays for inserting additional storage media,such as hard disk or solid-state drives,and support hot swapping for convenient,fast,and easy storage replacement. Each storage tray has its own LED to indicate whether or not a storage module is plugged in.The V2416A Series computers come preinstalled with a choice of Linux Debian7or Windows Embedded Standard7to provide programmers with a familiar environment in which to develop sophisticated,bug-free application software at a low cost.1.This product is suitable for rolling stock railway applications,as defined by the EN50155standard.For a more detailed statement,click here:/doc/specs/EN_50155_Compliance.pdfAppearanceFront View Rear ViewSpecificationsComputerCPU V2416A-C2Series:Intel®Celeron®Processor1047UE(2M cache,1.40GHz)V2416A-C7Series:Intel®Core™i7-3517UE Processor(4M cache,up to2.80GHz) System Chipset Mobile Intel®HM65Express ChipsetGraphics Controller Intel®HD Graphics4000(integrated)System Memory Pre-installed4GB DDR3System Memory Slot SODIMM DDR3/DDR3L slot x1Supported OS Linux Debian7Windows Embedded Standard7(WS7E)32-bitWindows Embedded Standard7(WS7E)64-bitStorage Slot CFast slot x2Computer InterfaceEthernet Ports Auto-sensing10/100/1000Mbps ports(M12X-coded)x2Serial Ports RS-232/422/485ports x4,software selectable(DB9male)USB2.0USB2.0hosts x1,M12D-coded connectorUSB2.0hosts x2,type-A connectorsAudio Input/Output Line in x1,Line out x1,M12D-codedDigital Input DIs x6Digital Output DOs x2Video Input DVI-I x2,29-pin DVI-D connectors(female)Digital InputsIsolation3k VDCConnector Screw-fastened Euroblock terminalDry Contact On:short to GNDOff:openI/O Mode DISensor Type Dry contactWet Contact(NPN or PNP)Wet Contact(DI to COM)On:10to30VDCOff:0to3VDCDigital OutputsConnector Screw-fastened Euroblock terminalCurrent Rating200mA per channelI/O Type SinkVoltage24to40VDCLED IndicatorsSystem Power x1Storage x1Hot-swappable2LAN2per port(10/100/1000Mbps)Serial2per port(Tx,Rx)Serial InterfaceBaudrate50bps to921.6kbpsFlow Control RTS/CTS,XON/XOFF,ADDC®(automatic data direction control)for RS-485,RTSToggle(RS-232only)Isolation N/AParity None,Even,Odd,Space,MarkData Bits5,6,7,8Stop Bits1,1.5,2Serial SignalsRS-232TxD,RxD,RTS,CTS,DTR,DSR,DCD,GNDRS-422Tx+,Tx-,Rx+,Rx-,GNDRS-485-2w Data+,Data-,GNDRS-485-4w Tx+,Tx-,Rx+,Rx-,GNDPower ParametersInput Voltage12to48VDCPower Connector M12A-coded male connectorPower Consumption(Max.) 3.3A@12VDC0.82A@48VDCPower Consumption40W(max.)Physical CharacteristicsHousing AluminumIP Rating IP30Dimensions(with ears)250x86x154mm(9.84x3.38x6.06in)Dimensions(without ears)275x92x154mm(10.83x3.62x6.06in)Weight4,000g(8.98lb)Installation DIN-rail mounting(optional),Wall mounting(standard) Protection-CT models:PCB conformal coating Environmental LimitsOperating Temperature Standard Models:-25to55°C(-13to131°F)Wide Temp.Models:-40to70°C(-40to158°F) Storage Temperature(package included)-40to85°C(-40to185°F)Ambient Relative Humidity5to95%(non-condensing)Standards and CertificationsEMC EN55032/24EMI CISPR32,FCC Part15B Class AEMS IEC61000-4-2ESD:Contact:6kV;Air:8kVIEC61000-4-3RS:80MHz to1GHz:20V/mIEC61000-4-4EFT:Power:2kV;Signal:2kVIEC61000-4-5Surge:Power:2kVIEC61000-4-6CS:10VIEC61000-4-8PFMFRailway EN50121-4,IEC60571Railway Fire Protection EN45545-2Safety EN60950-1,IEC60950-1Shock IEC60068-2-27,IEC61373,EN50155Vibration IEC60068-2-64,IEC61373,EN50155DeclarationGreen Product RoHS,CRoHS,WEEEMTBFTime332,173hrsStandards Telcordia(Bellcore),GBWarrantyWarranty Period3yearsDetails See /warrantyPackage ContentsDevice1x V2416A Series computerInstallation Kit8x screw,for storage installation2x storage key1x wall-mounting kit8x washer,for HDD/SSDDocumentation1x document and software CD1x quick installation guide1x warranty cardDimensionsOrdering InformationModel Name CPU Memory(Default)OS CFast(CTO)Backup CFast(CTO)Hot-SwappableSSD/HDD Tray(CTO)Operating Temp.ConformalCoatingV2416A-C2Celeron1047UE4GB or optional1(Optional)1(Optional)2(Optional)-25to55°C–V2416A-C2-T Celeron1047UE4GB or optional1(Optional)1(Optional)2(Optional)-40to70°C–V2416A-C2-CT-T Celeron1047UE4GB or optional1(Optional)1(Optional)2(Optional)-40to70°C✓V2416A-C7i7-3517UE4GB or optional1(Optional)1(Optional)2(Optional)-25to55°C–V2416A-C7-T i7-3517UE4GB or optional1(Optional)1(Optional)2(Optional)-40to70°C–V2416A-C7-CT-T i7-3517UE4GB or optional1(Optional)1(Optional)2(Optional)-40to70°C✓V2416A-C2-W7E Celeron1047UE4GB8GB1(Optional)2(Optional)-25to55°C–V2416A-C2-T-W7E Celeron1047UE4GB8GB1(Optional)2(Optional)-40to70°C–V2416A-C7-T-W7E Core i7-3517UE4GB8GB1(Optional)2(Optional)-40to70°C–Accessories(sold separately)Battery KitsRTC Battery Kit Lithium battery with built-in connectorCablesCBL-M12XMM8PRJ45-BK-100-IP67M12-to-RJ45Cat-5E UTP gigabit Ethernet cable,8-pin X-coded male connector,IP67,1mCBL-M12(FF5P)/Open-100IP67A-coded M12-to-5-pin power cable,IP67-rated5-pin female M12connector,1mConnectorsM12A-5PMM-IP685-pin male circular threaded D-coded M12USB connector,IP68M12X-8PMM-IP678-pin male X-coded circular threaded gigabit Ethernet connector,IP67M12A-5P-IP68A-coded screw-in sensor connector,female,IP68,4.05cmM12A-8PMM-IP678-pin male circular threaded A-codes M12connector,IP67-rated(for field-installation)Power AdaptersPWR-24270-DT-S1Power adapter,input voltage90to264VAC,output voltage24V with2.5A DC loadPower CordsPWC-C7AU-2B-183Power cord with Australian(AU)plug,2.5A/250V,1.83mPWC-C7CN-2B-183Power cord with two-prong China(CN)plug,1.83mPWC-C7EU-2B-183Power cord with Continental Europe(EU)plug,2.5A/250V,1.83mPWC-C7UK-2B-183Power cord with United Kingdom(UK)plug,2.5A/250V,1.83mPWC-C7US-2B-183Power cord with United States(US)plug,10A/125V,1.83mAntennasANT-WDB-ANF-0407 2.4/5GHz,omni-directional antenna,4/7dBi,N-type(male)Wall-Mounting KitsV2400Isolated Wall Mount Kit Wall-mounting kit with isolation protection,2wall-mounting brackets,4screwsDIN-Rail Mounting KitsDK-DC50131DIN-rail mounting kit,6screws©Moxa Inc.All rights reserved.Updated Jun12,2019.This document and any portion thereof may not be reproduced or used in any manner whatsoever without the express written permission of Moxa Inc.Product specifications subject to change without notice.Visit our website for the most up-to-date product information.。

AMD加速处理器列表

AMD加速处理器列表AMD Accelerated Processing Unit (APU)前称AMD Fusion,整合CPU和GPU。

目录•1 时程表•2 桌上型平台和笔电平台o 2.1 第一代AMD APU,基于AMD 10h(K10、K12/12h)▪ 2.1.1 Llanoo 2.2 第二代AMD APU,基于AMD Piledriver架构▪ 2.2.1 Trinity▪ 2.2.2 Richlando 2.3 第三代AMD APU,基于AMD Jagaur架构▪ 2.3.1 Kabinio 2.4 第四代AMD APU,基于AMD Steamroller架构▪ 2.4.1 Kaverio 2.5 第六代 AMD APU,基于 AMD Excavator 架构▪ 2.5.1 'Carrizo' (2015, 28 nm)o 2.6 第七代 AMD APU,基于 AMD Excavator 架构▪ 2.6.1 'Bristol Ridge' (2016, 28 nm)o 2.7 'Raven Ridge' (2017)•3 服务器核心o 3.1 Opteron X1100-series 'Kyoto' (28nm)o 3.2 Opteron X2100系列 'Kyoto' (2013, 28 nm)o 3.3 Opteron X3000系列 (2017, 28 nm) [26]•4 低功耗核心o 4.1 基于AMD Bobcat架构▪ 4.1.1 Brazos: 'Desna', 'Ontario', 'Zacate' (2011, 40nm)▪ 4.1.2 Brazos 2.0: 'Ontario', 'Zacate' (2012, 40 nm) ▪ 4.1.3 Brazos-T: 'Hondo' (2012, 40 nm)o 4.2 基于AMD Jagaur架构▪ 4.2.1 Temash▪ 4.2.2 Kabinio 4.3 第五代AMD APU 'Beema', 'Mullins',基于PUMA 核心 (2014, 28 nm)▪ 4.3.1 Mullins▪ 4.3.2 Beemao 4.4 'Carrizo-L' (2015, 28 nm)o 4.5 'Stoney Ridge' (2016,28nm)•5 嵌入式核心o 5.1 G系列▪ 5.1.1 Brazos: 'Ontario' and 'Zacate' (2011, 40 nm) ▪ 5.1.2 'Kabini' (2013, 28 nm)▪ 5.1.3 'Steppe Eagle' (2014, SoC,28nm)▪ 5.1.4 'Crowned Eagle' (2014, SoC,28nm)▪ 5.1.5 I家族: 'Brown Falcon' (2016, SoC,28nm)▪ 5.1.6 J家族: 'Prairie Falcon' (2016, SoC,28nm)▪ 5.1.7 LX家族 (2016, SoC,28nm)o 5.2 R系列▪ 5.2.1 Comal: 'Trinity' (2012, 32 nm)▪ 5.2.2 'Bald Eagle' (2014,28nm)▪ 5.2.3 'Merlin Falcon' (2015, SoC,28nm)•6 另见•7 备注•8 参考资料•9 外部链接时程表代号状态型号制程TDP 核心Radeon coresOntario 已发售C-30, C-50,C-60,C-7040nmbulk9W 1-2 Bobcat 80Zacate 已发售E-240, E-350,E-45040nmbulk18W 1-2 Bobcat 80Llano 已发售A6-3670, A8-3850等32nmSOI35W~100W2-4 K-10/Stars160~400Wichita 原定2012年上半年产品计划被取消28nmbulk~9W 1-2 Bobcat --Krishna 原定2012年上半年产品计划被取消28nmbulk~18W 2-4 Bobcat --Trinity 已发售A10-5800K 等32nmSOI17W~100W2-4Piledrivers128~384Richland 已发售A10-6800K 等32nmSOI17W~100W2-4Piledrivers128~384Kaveri 已发售A10-7850K等28nmSOI15W~95W2-4Steamrollers256~512Kabini 已发售Athlon5350 ,Sempron3850 等28nmSOI9~25W 2-4 Jaguar 128Beema 已发售A6 6410 ,A46310 等28nmSOI15W 2-4 Puma 128Mullins 已发售A10 Micro6700T , 等28nmSOI15W 2-4 Puma 128Carrizo 已发售Athlon X4 835,84528nmSOI 45W~65W2-4Excavator--Bristol Ridge 已出货A10-9700 等28nmSOI35W~65W2-4Excavator256~512桌上型平台和笔电平台第一代AMD APU,基于AMD 10h(K10、K12/12h)第一款Fusion处理器代号为“Swift”,最早将用于代号为“Shrike”笔记型电脑平台。

EM4-DINAV33DXR中文资料(List Unclassifed)中文数据手册「EasyDatasheet - 矽搜」

20(90) A (AV2)

频率

50到60赫兹

接口模块规范

RS422/RS485 (根据要求) Type

连接

地址 协议 数据(双向)

动态(只读) 静态(只写)

数据格式 波特率 隔离

2

AR2950模块

多点 双向(静 和动态变量)

2或4线,最大距离 1200米终止直接

模块上

255,由辅助键盘可选 MODBUS/JBUS

50%

0.1至100.0米

/ 脉冲

12V +辅助24VDC

逻辑状态:

OFF 2V, ON 10V

15mA最大值

1kΩ

1kΩ,亲密接触

100kΩ,开触点

通过光电耦合器方法,

2000 V 数字输入

测量输入,

2000 V 数字输入

电输入.

至5A)

每页最多4个变量 第1页:千瓦时,千乏 第2A:克瓦(T -t -t -t )

输出:2000伏

AQ2940模块

四种工作模式 可选:

完全和部分能源 米(千瓦时及无功电能) 无需使用数字 输入 完全和部分能源 米(千瓦时及无功电能) 按时间周期管理

(t -t -t -t );

总能量米

(千瓦时,千乏)和总 "日间/夜间"气 仪表;

总能量米

(千瓦时,千乏),GAS 和水表;

2

20Hz最大

1级累计.以EN61036 2级累计.以EN61268 Ib: 5A, Imax: 10A 0.1Ib: 500mA, 启动电流:20毫安 联合国:见附表"系列代码" Ib: 20A, Imax: 90A 0.1Ib: 2A, 启动电流:80毫安 联合国:见附表"系列代码"

ULN2004AIDRE4资料

PACKAGING INFORMATIONOrderable Device Status (1)Package Type Package DrawingPins Package Qty Eco Plan (2)Lead/Ball Finish MSL Peak Temp (3)ULN2004AID ACTIVE SOIC D 1640Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM ULN2004AIDE4ACTIVE SOIC D 1640Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM ULN2004AIDR ACTIVE SOIC D 162500Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM ULN2004AIDRE4ACTIVE SOIC D 162500Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM ULN2004AIN ACTIVE PDIP N 1625Pb-Free (RoHS)CU NIPDAU N /A for Pkg Type ULN2004AINE4ACTIVE PDIP N 1625Pb-Free (RoHS)CU NIPDAU N /A for Pkg Type ULN2004AINSR ACTIVE SO NS 162000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM ULN2004AINSRE4ACTIVESONS162000Green (RoHS &no Sb/Br)CU NIPDAULevel-1-260C-UNLIM(1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan -The planned eco-friendly classification:Pb-Free (RoHS),Pb-Free (RoHS Exempt),or Green (RoHS &no Sb/Br)-please check /productcontent for the latest availability information and additional product content details.TBD:The Pb-Free/Green conversion plan has not been defined.Pb-Free (RoHS):TI's terms "Lead-Free"or "Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all 6substances,including the requirement that lead not exceed 0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Pb-Free (RoHS Exempt):This component has a RoHS exemption for either 1)lead-based flip-chip solder bumps used between the die and package,or 2)lead-based die adhesive used between the die and leadframe.The component is otherwise considered Pb-Free (RoHS compatible)as defined above.Green (RoHS &no Sb/Br):TI defines "Green"to mean Pb-Free (RoHS compatible),and free of Bromine (Br)and Antimony (Sb)based flame retardants (Br or Sb do not exceed 0.1%by weight in homogeneous material)(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.PACKAGE OPTION ADDENDUM5-Feb-2007Addendum-Page 1IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and todiscontinue any product or service without notice. Customers should obtain the latest relevant informationbefore placing orders and should verify that such information is current and complete. All products are soldsubject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale inaccordance with TI’s standard warranty. Testing and other quality control techniques are used to the extentTI deems necessary to support this warranty. Except where mandated by government requirements, testingof all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design. Customers are responsiblefor their products and applications using TI components. To minimize the risks associated with customerproducts and applications, customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license, either express or implied, is granted under any TI patentright, copyright, mask work right, or other TI intellectual property right relating to any combination, machine,or process in which TI products or services are used. Information published by TI regarding third-partyproducts or services does not constitute a license from TI to use such products or services or a warranty orendorsement thereof. Use of such information may require a license from a third party under the patents orother intellectual property of the third party, or a license from TI under the patents or other intellectualproperty of TI.Reproduction of information in TI data books or data sheets is permissible only if reproduction is withoutalteration and is accompanied by all associated warranties, conditions, limitations, and notices.Reproduction of this information with alteration is an unfair and deceptive business practice. TI is notresponsible or liable for such altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI forthat product or service voids all express and any implied warranties for the associated TI product or serviceand is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.Following are URLs where you can obtain information on other Texas Instruments products and applicationsolutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotive/broadbandBroadbandDSP DigitalControl /digitalcontrol Interface Military /military Logic Power Mgmt Optical Networking /opticalnetworkSecurity /security Microcontrollers Low Power Wireless /lpw Telephony /telephonyVideo & Imaging /video/wirelessWirelessMailing Address: Texas InstrumentsPost Office Box 655303 Dallas, Texas 75265Copyright © 2007, Texas Instruments Incorporated。

KL03 芯片系列参考手册说明书