G698L308T1U中文资料

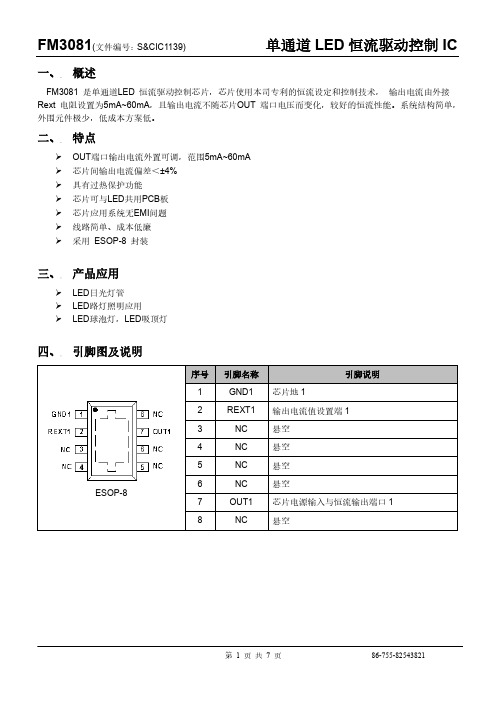

G1085T41T中文资料

FeaturesAvailable in Adjust VersionSpace Saving TO-252 Package and TO-263 PackageInternal Short Circuit Current Limiting Internal Over Temperature ProtectionOutput Current 3AApplicationsPost Regulation for Switching DC/DC Con-verterHigh Efficiency Linear Regulator Battery ChargerBattery Powered InstrumentationMotherboardGeneral DescriptionThe G1085 is a low dropout linear regulator with a dropout of 1.2V at 3A of load current. It is avail-able in an adjustable version, which can set the output from 1.25V to 5V with only two external resistors.The G1085 provides over temperature and over current protection circuits to prevent it from being damaged by abnormal operating conditions. The G1085 is available in TO-252 package and TO- 263 packages. A minimum of 100µF tantalum electrolytic capacitor is required at the output to improve the transient response and stability.Ordering InformationPIN OPTIONORDER NUMBERORDER NUMBER(Pb free)MARKINGTEMP. RANGEPACKAGE1 2 3G1085T43U G1085T43Uf G1085 -40°C to +85°C TO-252 GND/ADJ V OUT V IN G1085T53U G1085T53UfG1085-40°C to +85°CTO-263GND/ADJV OUTV IN* For other package types and pin options, please contact us at sales @Order Number IdentificationType Pin Option TypePart NumberPACKAGE TYPE PIN OPTION PACKINGT4: TO-252 12 3 U & D: Tape & Reel Direction T5: TO-263 3: GND/ADJ V OUT V IN T: TubePackage Type Typical Application [Note 4]: Type of C OUTV V OUT123TO-252、TO-263Input Voltage…………………………….………………7V Power Dissipation Internally Limited (Note 2) Maximum Junction Temperature…...……………….150°C Storage Temperature Range…..…-65°C ≤ T J ≤+150°CReflow Temperature (soldering, 10sec)…………260°C Thermal Resistance Junction to AmbientTO-252(1)………………………………….………125°C/W TO-263(1)………………………………….………100°C/W Thermal Resistance Junction to CaseTO-252………….………………..………..….……10°C/W TO-263…..………………………...……..…………6°C/W ESD Rating (Human Body Model)……......................2kVNote (1): See Recommended Minimum Footprint(V IN -V ADJ ) Voltage………..…………...………..2.5V~5.5V Temperature Range……………..….….-40°C ≤ T A ≤85°C Electrical CharacteristicsOperating Conditions: V IN ≤ 7V, T A =T J = 25°C unless otherwise specified. [Note3]PARAMETER CONDITION MIN TYP MAX UNITReference Voltage V IN - V OUT = 2V, I OUT = 10mA1.2251.2501.275VLine Regulation(V OUT + 1.5V) < V IN < 7V, I OUT = 10mA --- 0.5 1 % Load Regulation (V IN - V OUT ) = 2V, 10mA < I OUT <3A --- 0.04 0.5 % Dropout Voltage ∆V OUT = 2%, I OUT = 3A --- 1.3 1.4 V Current Limit(V IN - V OUT ) = 2V---5.4---AAdjust Pin Current Change V IN - V OUT = 2V, 10mA < I OUT < 3A --- 0.15 --- µA Minimum Load Current 1.5V < (V IN - V OUT ) < 5.25V 10 --- --- mA Quiescent Current V IN - V OUT = 2V---80150µARipple Rejection f = 120Hz, C OUT = 10µF Tantalum,(V IN - V OUT ) = 3V, I OUT = 1A--- 48 --- dBTemperature StabilityV IN = 4V, I O =10mA --- 0.3 --- %RMS Output Noise (% of V OUT ) T A = 25°C, 10Hz < f < 10kHz, I LOAD = 10mA --- 0.007 --- %Thermal Shutdown Junction Temperature --- 150 --- °CThermal Shutdown Hysteresis--- 30 --- °CNote 1: Absolute Maximum Ratings are limits beyond which damage to the device may occur. Operating Con-ditions are conditions under which the device functions but the specifications might not be guaranteed. For guaranteed specifications and test conditions see the Electrical Characteristics.Note 2: The maximum power dissipation is a function of the maximum junction temperature, T Jmax ; total thermal re-sistance, θJA , and ambient temperature T A . The maximum allowable power dissipation at any ambient tem-perature is T jmax -T A / θJA . If this dissipation is exceeded, the die temperature will rise above 150°C and ICwill go into thermal shutdown.Note3: Low duty pulse techniques are used during test to maintain junction temperature as close to ambient as possible.Note4: The type of output capacitor should be tantalum or aluminum.Output VoltageThe G1085 provides an adjustable output voltage from 1.25V to 5V. with two external resistors. It can be for-mulated as:R2 V OUT = 1.25V x (1+R1) + IADJx R2I ADJ = 80µA (TYP)Dropout VoltageThe input/output Voltage differential at which the regulator output no longer maintains regulation against further reductions in input voltage. Measured when the output drops 2% below its nominal value. Dropout voltage is affected by junction temperature, load cur-rent and minimum input supply requirements. Line RegulationThe change in output voltage for a change in input voltage. The measurement is made under conditions of low dissipation or by using pulse techniques such that average chip temperature is not significantly af-fected.Load RegulationThe change in output voltage for a change in load current at constant chip temperature. The measure-ment is made under conditions of low dissipation or by using pulse techniques such that average chip tem-perature is not significantly affected.Maximum Power DissipationThe maximum total device dissipation for which the regulator will operate within specifications.Quiescent Bias CurrentCurrent which is used to operate the regulator chip and is not delivered to the load.(V IN -V OUT =3V, V OUT =1.25V, C IN =100µF, C OUT =100µF, T A =25°C, unless otherwise noted.)I L =100mALine Transient ResponseLoad Transient ResponseOutput NoiseShort Circuit-CurrentDropout Voltage vs. I OUTLoad RegulationOutput Voltage vs. TemperatureAdj Pin Current vs. TemperatureG1085T43(TO-252) Max. PowerDissipation vs. PCB Top CopperG1085T43(TO-252) Max. Power Dissipation vs. T AMB (still air)Recommend Minimum FootprintG1085T53(TO-263) Max. Power Dissipation vs. PCB Top Copper Area T = 25°C ; Still AirG1085T53(TO-263) Max. Power Dissipation vs. TAMB (still air)TO-252 (T4) PackageDIMENSION IN MILLIMETER DIMENSION IN INCHSYMBOLMIN. MAX. MIN. MAX.A 2.19 2.38 0.086 0.094 A1 0.89 1.27 0.035 0.050 b 0.64 0.89 0.025 0.035 C 0.46 0.58 0.018 0.023 D 5.97 6.22 0.235 0.245E 6.35 6.73 0.250 0.265 E1 5.21 5.46 0.2050.215 e 2.26 BSC 0.09 BSC e1 3.96 5.18 0.156 0.204 F 0.46 0.58 0.018 0.023 L1 0.89 2.03 0.035 0.080 L2 0.64 1.02 0.025 0.040 L3 2.40 2.80 0.095 0.110 H 9.40 10.40 0.370 0.410 θ 0° 4° 0° 4°TO-263 (T5) PackageMILLIMETER INCH SYMBOLMIN MAX MIN MAXA 4.30 4.70 0.169 0.185 A1 1.22 1.32 0.048 0.055 A2 2.45 2.69 0.104 0.106 b 0.69 0.94 0.027 0.037 b1 1.22 1.40 0.048 0.055 C 0.36 0.56 0.014 0.022 D 8.64 9.652 0.340 0.380 E 9.7010.54 0.382 0.415 e 2.29 2.79 0.090 0.110 e1 4.83 5.33 0.190 0.210 H 14.60 15.78 0.575 0.625 L 4.70 5.84 0.185 0.230 L1 1.20 1.778 0.047 0.070 L2 2.24 2.84 0.088 0.111 L3 1.40MAX 0.055MAXPackage OrientationPACKAGE Q’TY/REELTO-252 2,500 ea TO-263 1,000 eaGMT Inc. does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and GMT Inc. reserves the right at any time without notice to change said circuitry and specifications.TO-252 Package OrientationTO-263 Package OrientationFeed DirectionFeed Direction。

SL2.2S规格书,usb HUB大全,替换FE1.1S,GL850,GL852,PL2586

USB2.0 HUB控制器集成电路USB 2.0 HIGH SPEED 4-PORT HUB CONTROLLERSL2.2s数据手册Data Sheet内容目录第一章管脚分配 (3)1.1 SL2.2S管脚图 (3)1.2 SL2.2S管脚定义 (3)第二章 功能叙述 (5)2.1综述 (5)2.2指示灯 (5)2.2.1单灯方案 (5)2.2.2多灯方案 (6)2.2.3 LED指示定义 (6)2.3过流保护 (6)2.4充电支持 (6)2.5I2C接口 (7)2.6EEPROM设置 (7)第三章电气特性 (8)3.1极限工作条件 (8)3.2工作范围 (8)3.3直流电特性 (8)3.4HS/FS/LS电气特性 (8)3.5ESD特性 (8)附录一封装 (9)表格目录表格1: 端口LED定义 (6)表格 2 : ACTIVE LED定义 (6)表格3:EEPROM数据结构定义 (7)表格4: 最大额定值 (8)表格5: 工作范围 (8)表格6: 直流电特性 (8)插图目录图1:SSOP28 管脚图 (3)图2:单灯方案配置 (5)图3: 5灯方案配置 ............................................................................... (6)图 4:附录 封装图 ................................................................................... .9第一章管脚分配1.1SL2.2s管脚图图1:SSOP28 管脚图1.2SL2.2s管脚定义管脚名称28Die IO类型定义Pin#VSS 1 P 芯片地XOUT 2 O晶振PAD XIN 3 IDM4 4 B下行口4的USB信号DP4 5 BDM3 6 B下行口3的USB信号DP3 7 BDM2 8 B下行口2的USB信号DP2 9 BDM1 10 B下行口1的USB信号DP1 11 BVDD18 12 P 模拟1.8vVDD33 13 P 模拟3.3v - 14 NCUDM 15 B上行口的USB信号UDP 16 BRESET_N 17 I,Pu 芯片外部复位输入- 18 NCPSELF 19 I,Pu 高为自供电,低为总线供电VDD5 20 P 5v输入VDD33 21 P 3.3v输出DRV 22 B,Pu 点灯驱动信号LED1 23 B,Pu 点灯驱动信号LED2 24 B,Pu 点灯驱动信号PWRN 25 B,Pu 下行口电源输出控制,低有效OVCRN/SDA 26 B,PuI2C SDA数据线,内部上拉;芯片初始化完成后作为过流保护输入脚,低有效SCL 27 B,Pu I2C SCL时钟输出VDD18 28 P 数字1.8v注释:O,输出;I 输入;B 双向;P 电源/接地;Pu 上拉;Pd 下拉;NC 悬空;第二章 功能叙述2.1综述SL2.2s 是一颗高集成度,高性能,低功耗的USB2.0集线器主控芯片;该芯片采用STT 技术,单电源供电方式,芯片供电电压为5v , 内部集成5V 转3.3V,只需在外部电源添加滤波电容;芯片自带复位电路,低功耗技术让他更加出众。

NCP551SN27T1G、NCP551SN28T1G和NCV551SN36T1G:电路板组件工业有

NCP551SN27T1G NCP551SN28T1G NCV551SN36T1GNCP551, NCV551Voltage Regulator - CMOS,Low Iq, Low-Dropout150 mAThe NCP551 series of fixed output low dropout linear regulators are designed for handheld communication equipment and portable battery powered applications which require low quiescent. The NCP551series features an ultra −low quiescent current of 4.0 m A. Each device contains a voltage reference unit, an error amplifier, a PMOS power transistor, resistors for setting output voltage, current limit, and temperature limit protection circuits.The NCP551 has been designed to be used with low cost ceramic capacitors and requires a minimum output capacitor of 0.1 m F. The device is housed in the TSOP −5 surface mount package. Standard voltage versions are 1.4, 1.5, 1.8, 2.5, 2.7, 2.8, 2.9, 3.0, 3.1, 3.2, 3.3,3.6, 3.8 and 5.0 V . Other voltages are available in 100 mV steps.Features•Low Quiescent Current of 4.0 m A Typical •Maximum Operating V oltage of 12 V •Low Output V oltage Option•High Accuracy Output V oltage of 2.0%•Industrial Temperature Range of −40°C to 85°C (NCV551, T A = −40°C to +125°C)•NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC −Q100Qualified and PPAP Capable•These Devices are Pb −Free and are RoHS CompliantTypical Applications•Battery Powered Instruments •Hand −Held Instruments •Camcorders and CamerasFigure 1. Representative Block DiagramV inV outEnable OFFON See detailed ordering and shipping information in the package dimensions section on page 11 of this data sheet.ORDERING INFORMATIONTSOP −5(SOT23−5, SC59−5)SN SUFFIX CASE 483PIN CONNECTIONS AND MARKING DIAGRAM13N/CVin 2GND Enable4V out5(Top View)xxxAYW G G xxx = Specific Device Code A = Assembly Location Y = YearW = Work Week G = Pb −Free Package(Note: Microdot may be in either location)PIN FUNCTION DESCRIPTIONPin No.Pin Name Description1V in Positive power supply input voltage.2GND Power supply ground.3Enable This input is used to place the device into low−power standby. When this input is pulled low, thedevice is disabled. If this function is not used, Enable should be connected to V in.4N/C No Internal Connection.5V out Regulated output voltage.MAXIMUM RATINGSRating Symbol Value Unit Input Voltage V in0 to 12V Enable Voltage V EN−0.3 to V in+0.3V Output Voltage V out−0.3 to V in+0.3V Power Dissipation P D Internally Limited W Operating Junction Temperature T J+150°COperating Ambient Temperature NCP551NCV551T A−40 to +85−40 to +125°CStorage Temperature T stg−55 to +150°C Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionalityshould not be assumed, damage may occur and reliability may be affected.1.This device series contains ESD protection and exceeds the following tests:Human Body Model 2000 V per MIL−STD−883, Method 3015Machine Model Method 200 VCharge Device Model (CDM) tested C3B per EIA/JESD22−C101.tchup capability (85°C) "100 mA DC with trigger voltage.THERMAL CHARACTERISTICSRating Symbol Test Conditions Typical Value Unit Junction−to−Ambient R q JA 1 oz Copper Thickness, 100 mm2250°C/W PSIJ−Lead 2Y J−L2 1 oz Copper Thickness, 100 mm268°C/W NOTE:Single component mounted on an 80 x 80 x 1.5 mm FR4 PCB with stated copper head spreading area. Using the following boundary conditions as stated in EIA/JESD 51−1, 2, 3, 7, 12.ELECTRICAL CHARACTERISTICS(V in = V out(nom.) + 1.0 V, V EN = V in, C in = 1.0 m F, C out = 1.0 m F, T A = 25°C, unless otherwise noted.)Characteristic Symbol Min Typ Max UnitOutput Voltage (T A = 25°C, I out = 10 mA) 1.4 V1.5 V1.8 V2.5 V2.7 V2.8 V2.9 V3.0 V3.1 V3.2 V3.3 V3.6 V3.8 V5.0 V V out1.3581.4551.7462.4252.6462.7442.8422.9403.0383.1363.2343.5283.7244.901.41.51.82.52.72.82.93.03.13.23.33.63.85.01.4421.5451.8542.5752.7542.8562.9583.0603.1623.2643.3663.6723.8765.10VOutput Voltage (T A = T low to T high, I out = 10 mA) 1.4 V1.5 V1.8 V2.5 V2.7 V2.8 V2.9 V3.0 V3.1 V3.2 V3.3 V3.6 V3.8 V5.0 V V out1.3441.4401.7282.4002.6192.7162.8132.9103.0073.1043.2013.4923.6864.8501.41.51.82.52.72.82.93.03.13.23.33.63.85.01.4561.5601.8722.6002.7812.8842.9873.0903.1933.2963.3993.7083.9145.150VLine Regulation (V in = V out + 1.0 V to 12 V, I out = 10 mA)Reg line−1030mV Load Regulation (I out = 10 mA to 150 mA, V in = V out + 2.0 V)Reg load−4065mVOutput Current (V out = (V out at I out = 100 mA) −3%)1.4 V−2.0 V (V in = 4.0 V)2.1 V−3.0 V (V in = 5.0 V)3.1 V−4.0 V (V in = 6.0 V)4.1 V−5.0 V (V in = 8.0 V)I o(nom.)150150150150−−−−−−−−mADropout Voltage (I out = 10 mA, Measured at V out−3.0%)1.4 V1.5 V, 1.8 V,2.5 V2.7 V, 2.8 V, 2.9 V,3.0 V, 3.1 V, 3.2 V, 3.3 V, 3.6 V, 3.8 V, 5.0 V V in−V out−−−17013040250220150mVQuiescent Current(Enable Input = 0 V)(Enable Input = V in, I out = 1.0 mA to I o(nom.))1.4 V−2.0 V options, V in = 4.0 V2.1 V−3.0 V options, V in = 5.0 V3.1 V−4.0 V options, V in = 6.0 V4.1 V−5.0 V options, V in = 8.0 V I Q−−0.14.01.08.0m AOutput Voltage Temperature Coefficient T c−"100−ppm/°CEnable Input Threshold Voltage(Voltage Increasing, Output Turns On, Logic High) (Voltage Decreasing, Output Turns Off, Logic Low)V th(en)1.3−−−−0.3VELECTRICAL CHARACTERISTICS (continued)(V in = V out(nom.) + 1.0 V, V EN = V in , C in = 1.0 m F, C out = 1.0 m F, T A = 25°C, unless otherwise noted.)Output Short Circuit Current (V out = 0 V)1.4 V −2.0 V (V in = 4.0 V)2.1 V −3.0 V (V in = 5.0 V)3.1 V −4.0 V (V in = 6.0 V)4.1 V −5.0 V (V in = 8.0 V)I out(max)160160160160350350350350600600600600mA3.Maximum package power dissipation limits must be observed.PD +T J(max)*T A R q JA4.Low duty cycle pulse techniques are used during testing to maintain the junction temperature as close to ambient as possible.5.NCP551T low = −40°CT high = +85°C NCV551T low = −40°CT high = +125°C.DEFINITIONSLoad RegulationThe change in output voltage for a change in output current at a constant temperature.Dropout VoltageThe input/output differential at which the regulator output no longer maintains regulation against further reductions in input voltage. Measured when the output drops 3% below its nominal. The junction temperature, load current, and minimum input supply requirements affect the dropout level. Maximum Power DissipationThe maximum total dissipation for which the regulator will operate within its specifications.Quiescent CurrentThe quiescent current is the current which flows through the ground when the LDO operates without a load on its output: internal IC operation, bias, etc. When the LDO becomes loaded, this term is called the Ground current. It is actually the difference between the input current (measured through the LDO input pin) and the output current.Line RegulationThe change in output voltage for a change in input voltage. The measurement is made under conditions of low dissipation or by using pulse technique such that the average chip temperature is not significantly affected.Line Transient ResponseTypical over and undershoot response when input voltage is excited with a given slope.Thermal ProtectionInternal thermal shutdown circuitry is provided to protect the integrated circuit in the event that the maximum junction temperature is exceeded. When activated at typically 160°C, the regulator turns off. This feature is provided to prevent failures from accidental overheating.Maximum Package Power DissipationThe maximum power package dissipation is the power dissipation level at which the junction temperature reaches its maximum operating value, i.e. 125°C. Depending on the ambient power dissipation and thus the maximum available output current.3.25G R O U N D C U R R E N T (m A )3.05Figure 2. Ground Pin Current versusOutput Current 3.35I out , OUTPUT CURRENT (mA)3.33.13.23.15Figure 3. Ground Pin Current versusOutput Current3.35G R O U N D C U R R E N T (m A )3.153.45I out , OUTPUT CURRENT (mA)3.43.23.33.250.50Figure4. Ground Pin Current versusInput Voltage V in , INPUT VOLTAGE (VOLTS)Figure 5. Ground Pin Current versusInput VoltageG R OU N D P I N C U R R E N T (m A )11.522.533.540.50V in , INPUT VOLTAGE (VOLTS)G R OU N D P I N C U R R E N T (m A )11.522.533.5440004−200200−60064200TIME (m s)Figure 6. Line Transient Response Figure 7. Line Transient Response8TIME (m s)−20004006−400−400O U T P U T V O L T A G E D E V I A T I O N (m V )V i n , I N P U T V O L T A G E (V )O U T P U T V O L T A G E D E V I A T I O N (m V )V i n , I N P U T V O L T A G E (V )4−−4200TIME (m s)Figure 8. Line Transient Response Figure 9. Line Transient ResponseTIME (m s)−20004006−−400O U T P U T V O L T A G E D E V I A T I O N (m V )V i n , I N P U T V O L T A G E (V )O U T P U T V O L T A G E D E V I A T I O N (m V )V i n , I N P U T V O L T A G E (V )−600−−4200Figure 10. Line Transient Response Figure 11. Line Transient ResponseTIME (m s)−20004006−−400O U T P U T V O L T A G E D E V I A T I O N (m V )V i n , I N P U T V O L T A G E (V )O U T P U T V O L T A G E D E V I A T I O N (m V )V i n , I N P U T V O L T A G E (V )−600600800TIME (m s)150O U T P U T V O L T A G E D E V I A T I O N (m V )−1000TIME (ms)Figure 12. Load Transient Response ON Figure 13. Load Transient Response OFFTIME (ms)−50000I o u t , O U T P U T C U R R E N T (m A )−O U T P U T V O L T A G E D E V I A T I O N (m V )I o u t , O U T P U T C U R R E N T (m A )Figure 14. Load Transient Response OFF TIME (ms)Figure 15. Load Transient Response ONTIME (ms)150−5005000−−01000O U T P U T V O L T A G E D E V I A T I O N (m V )I o u t , O U T P U T C U R R E N T (m A )O U T P U T V O L T A G E D E V I A T I O N (m V )I o u t , O U T P U T C U R R E N T (m A )12Figure 16. Turn −On Response 3TIME (m s)0132V o u t , O U T P U T V O L T A G E (V )E N A B L E V O L T A G E (V )Figure 17. Turn−On ResponseTIME (m s)V o u t , O U T P U T V O L T A G E (V )E N A B L E V O L T A G E(V )Figure 18. Output Voltage versus Input Voltage Figure 19. Output Voltage versus Input Voltage2V o u t , O U T P U T V O L T A G E (V O L T S )3V in , INPUT VOLTAGE (VOLTS)2.50.51.51V o u t , O U T P U T V O L T A G E (V O L T S )V in , INPUT VOLTAGE (VOLTS)APPLICATIONS INFORMATIONA typical application circuit for the NCP551 series is shown in Figure 20.Input Decoupling (C1)A 0.1 m F capacitor either ceramic or tantalum is recommended and should be connected close to the NCP551package. Higher values and lower ESR will improve the overall line transient response.Output Decoupling (C2)The NCP551 is a stable Regulator and does not require any specific Equivalent Series Resistance (ESR) or a minimum output current. Capacitors exhibiting ESRs ranging from a few m W up to 3.0 W can thus safely be used.The minimum decoupling value is 0.1 m F and can be augmented to fulfill stringent load transient requirements.The regulator accepts ceramic chip capacitors as well as tantalum devices. Larger values improve noise rejection and load regulation transient response.Enable OperationThe enable pin will turn on or off the regulator. These limits of threshold are covered in the electrical specification section of this data sheet. If the enable is not used then the pin should be connected to V in .HintsPlease be sure the V in and GND lines are sufficiently wide.When the impedance of these lines is high, there is a chance to pick up noise or cause the regulator to malfunction.Set external components, especially the output capacitor,as close as possible to the circuit, and make leads as short as possible.ThermalAs power across the NCP551 increases, it might become necessary to provide some thermal relief. The maximum power dissipation supported by the device is dependent upon board design and layout. Mounting pad configuration on the PCB, the board material, and also the ambient temperature effect the rate of temperature rise for the part.This is stating that when the NCP551 has good thermal conductivity through the PCB, the junction temperature will be relatively low with high power dissipation applications.The maximum dissipation the package can handle is given by:PD +T J(max)*T AR q JAIf junction temperature is not allowed above the maximum 125°C, then the NCP551 can dissipate up to 400 mW @ 25°C.The power dissipated by the NCP551 can be calculated from the following equation:P tot +ƪV in *I gnd (I out )ƫ)[V in *V out ]*I outorV inMAX +P tot)V out *I outI GND )I outIf a 150 mA output current is needed then the ground current from the data sheet is 4.0 m A. For an NCP551SN30T1 (3.0 V), the maximum input voltage will then be 5.6 V .Battery or Unregulated VoltageFigure 20. Typical Application CircuitOFFONm FFigure 21. Current Boost RegulatorFigure 22. Current Boost Regulator withShort Circuit LimitFigure 23. Delayed Turn −onFigure 24. Input Voltages Greater than 12 VThe NCP551 series can be current boosted with a PNP transist-or. Resistor R in conjunction with V BE of the PNP determines when the pass transistor begins conducting; this circuit is not short circuit proof. Input/Output differential voltage minimum is increased by V BE of the pass resistor.Short circuit current limit is essentially set by the V BE of Q2 and R1. I SC = ((V BEQ2 − ib * R2) / R1) + I O(max) RegulatorIf a delayed turn −on is needed during power up of several volt-ages then the above schematic can be used. Resistor R, and capacitor C, will delay the turn −on of the bottom regulator.A regulated output can be achieved with input voltages that exceed the 12 V maximum rating of the NCP551 series with the addition of a simple pre −regulator circuit. Care must be taken to prevent Q1 from overheating when the regulated output (V out ) is shorted to GND .ORDERING INFORMATIONDeviceNominalOutput Voltage Marking Package Shipping†NCP551SN15T1G 1.5LAO TSOP−5(Pb−Free)3000 / Tape & Reel NCP551SN18T1G 1.8LAP TSOP−5(Pb−Free)3000 / Tape & Reel NCP551SN25T1G 2.5LAQ TSOP−5(Pb−Free)3000 / Tape & Reel NCP551SN27T1G 2.7LAR TSOP−5(Pb−Free)3000 / Tape & Reel NCP551SN28T1G 2.8LAS TSOP−5(Pb−Free)3000 / Tape & ReelNCP551SN29T1G 2.9LJL TSOP−5(Pb−Free)3000 / Tape & ReelNCP551SN30T1G 3.0LAT TSOP−5(Pb−Free)3000 / Tape & ReelNCP551SN31T1G 3.1LJM TSOP−5(Pb−Free)3000 / Tape & ReelNCP551SN32T1G 3.2LIV TSOP−5(Pb−Free)3000 / Tape & ReelNCP551SN33T1G 3.3LAU TSOP−5(Pb−Free)3000 / Tape & ReelNCP551SN50T1G 5.0LAV TSOP−5(Pb−Free)3000 / Tape & ReelNCV551SN14T1G* 1.4AAT TSOP−5(Pb−Free)3000 / Tape & ReelNCV551SN15T1G* 1.5LFZ TSOP−5(Pb−Free)3000 / Tape & ReelNCV551SN18T1G* 1.8LGA TSOP−5(Pb−Free)3000 / Tape & ReelNCV551SN25T1G* 2.5LGB TSOP−5(Pb−Free)3000 / Tape & ReelNCV551SN27T1G* 2.7LGC TSOP−5(Pb−Free)3000 / Tape & ReelNCV551SN28T1G* 2.8LGD TSOP−5(Pb−Free)3000 / Tape & ReelNCV551SN30T1G* 3.0LGE TSOP−5(Pb−Free)3000 / Tape & ReelNCV551SN31T1G* 3.1LJR TSOP−5(Pb−Free)3000 / Tape & ReelNCV551SN32T1G* 3.2LFR TSOP−5(Pb−Free)3000 / Tape & ReelNCV551SN33T1G* 3.3LGG TSOP−5(Pb−Free)3000 / Tape & ReelNCV551SN36T1G* 3.6AEJ TSOP−5(Pb−Free)3000 / Tape & ReelNCV551SN38T1G* 3.8AD5TSOP−5(Pb−Free)3000 / Tape & ReelNCV551SN50T1G* 5.0LGF TSOP−5(Pb−Free)3000 / Tape & ReelNOTE:Additional voltages in 100 mV steps are available upon request by contacting your ON Semiconductor representative.†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our T ape and Reel Packaging Specific-ations Brochure, BRD8011/D.*NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC−Q100 Qualified and PPAP Capable.PACKAGE DIMENSIONSTSOP −5SN SUFFIX CASE 483−02ISSUE KNOTES:1.DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.2.CONTROLLING DIMENSION: MILLIMETERS.3.MAXIMUM LEAD THICKNESS INCLUDES LEAD FINISH THICKNESS. MINIMUM LEAD THICKNESS IS THE MINIMUM THICKNESS OF BASE MATERIAL.4.DIMENSIONS A AND B DO NOT INCLUDE MOLD FLASH, PROTRUSIONS, OR GATE BURRS. MOLDFLASH, PROTRUSIONS, OR GATE BURRS SHALL NOT EXCEED 0.15 PER SIDE. DIMENSION A.5.OPTIONAL CONSTRUCTION: AN ADDITIONAL TRIMMED LEAD IS ALLOWED IN THIS LOCATION.TRIMMED LEAD NOT TO EXTEND MORE THAN 0.2FROM BODY .DIM MIN MAX MILLIMETERS A 3.00 BSC B 1.50 BSC C 0.90 1.10D 0.250.50G 0.95 BSC H 0.010.10J 0.100.26K 0.200.60M 0 10 S2.503.00__ǒmm inchesǓ*For additional information on our Pb −Free strategy and solderingdetails, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.SOLDERING FOOTPRINT*2XDETAIL ZTOP VIEWON Semiconductor and the are registered trademarks of Semiconductor Components Industries, LLC (SCILLC) or its subsidiaries in the United States and/or other countries.SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC’s product/patent coverage may be accessed at /site/pdf/Patent −Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. “Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended,or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATIONNCP551SN27T1G NCP551SN28T1G NCV551SN36T1G。

nuc980 手册

nuc980 手册1. 介绍Nuc980 手册是为初学者和专业人士提供的一份详尽的使用指南。

该手册旨在帮助用户了解 Nuc980 系列产品的基本知识,掌握其功能和操作方法,以便更好地使用和开发该系列产品。

2. 产品概述Nuc980 是一款高性能的系统级芯片,由台湾新唐科技(Nuvoton Technology)公司研发。

该芯片集成了 ARM Cortex-A9 处理器,提供了丰富的外设接口和强大的处理能力,适用于嵌入式系统和物联网设备领域。

3. 硬件接口Nuc980 手册提供了详细的硬件接口说明,包括 GPIO 引脚、外部存储器接口、串口、以太网、USB 和音频接口等。

对于每个接口,手册都提供了引脚定义、电气特性和使用方法等详细信息,以便用户能够正确连接外部设备并进行开发。

4. 芯片功能Nuc980 手册详细介绍了芯片的各项功能,包括处理器架构、片内存储器、时钟控制器、中断控制器等。

用户可以通过阅读手册了解芯片的功能特点,并根据实际需求进行开发和优化。

5. 软件开发Nuc980 手册提供了涵盖丰富软件开发内容,包括操作系统、编译器、调试工具等。

手册介绍了针对 Nuc980 芯片的软件开发流程和开发环境的搭建方法,以及常用的软件开发工具的使用技巧。

6. 示例代码为了帮助用户更好地理解和应用 Nuc980 芯片,手册还提供了大量的示例代码。

这些示例代码覆盖了芯片的各个功能模块,可以作为用户开发的起点,节省用户的开发时间。

7. 附录Nuc980 手册附录部分包含了一些补充性的内容,如常见问题解答、技术规范、参考文献等。

用户可以在遇到问题时查看附录部分,以快速找到解决方案。

总结:Nuc980 手册作为一份全面而详尽的使用指南,为用户提供了丰富的硬件接口信息、功能说明、软件开发指导和示例代码等。

通过阅读和理解手册内容,用户可以更好地掌握 Nuc980 芯片的使用方法和开发技巧,从而快速、高效地完成各种嵌入式系统和物联网设备的开发工作。

奥普尚科技APS0251苹果Lightning OTG输出取电芯片说明书

销售部2:TEL:130****8198,QQ:2881651176投诉与建议:134****1600数据手册DATASHEETAPS0251苹果Lightning OTG输出取电芯片(Rev:1.2)销售部2:TEL:130****8198,QQ:2881651176投诉与建议:134****1600一、概述APS0251采用CMOS工艺制造,是一款苹果 Lightning OTG输出取电认证通信协议芯片,提供苹果通讯协议握手信号,完成苹果手机与周边外设的连接,使其提供3.3V电压输出。

二、特点1、工作电压:1.5V~6.5V。

2、内置4MHz晶振,精度±2%。

3、集成度高,极少的外围元器件。

4、电路简单,价格优势明显。

5、稳定性高,兼容性强。

6、支持给周边外部设备供电。

三、功能1、输出3.3V,300mA电源提供给手机周边外设供电。

2、3.3V电压输出升压到5V提供给手机周边外设供电。

四、应用范围1、苹果Lightning取电小风扇。

2、苹果Lightning取电蓝牙耳机。

3、苹果Lightning取电LED阅读灯。

4、苹果Lightning取电手机保护壳套。

5、苹果Lightning取电补水仪。

6、苹果Lightning取电拍照补光灯。

7、苹果Lightning取电FM发射器。

8、苹果Lightning取电手机应急充电器。

五、苹果设备、iOS系统、配件支持1、支持iPhone、iPad、iPad mini、iPod touch、iPod nano等苹果设备。

2、支持苹果iOS系统所有版本。

六、系统框图销售部2:TEL:130****8198,QQ:2881651176投诉与建议:134****1600七、封装及引脚定义描述1、封装及引脚定义APS0251 SOT23-6L2、引脚定义描述序号引脚定义I/O类型功能描述1 DATA I/O 苹果通讯协议握手信号。

2 GND P 芯片地。

AD698中文资料

Universal LVDT Signal Conditioner AD698

FUNCTIONAL BLOCK DIAGRAM

AMP OSCILLATOR VOLTAGE REFERENCE

AD698

B A B FILTER A

AMP

PRODUCT DESCRIPTION

PRODUCT HIGHLIGHTS

REV. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. © Analog Devices, Inc., 1995 One Technology Way, P.O. Box 9106, Norwood. MA 02062-9106, U.S.A. Tel: 617/329-4700 Fax: 617/326-8703

1. The AD698 offers a single chip solution to LVDT signal conditioning problems. All active circuits are on the monolithic chip with only passive components required to complete the conversion from mechanical position to dc voltage. 2. The AD698 can be used with many different types of position sensors. The circuit is optimized for use with any LVDT, including half-bridge and series opposed, (4 wire) configurations. The AD698 accommodates a wide range of input and output voltages and frequencies. 3. The 20 Hz to 20 kHz excitation frequency is determined by a single external capacitor. The AD698 provides up to 24 volts rms to differentially drive the LVDT primary, and the AD698 meets its specifications with input levels as low as 100 millivolts rms. 4. Changes in oscillator amplitude with temperature will not affect overall circuit performance. The AD698 computes the ratio of the secondary voltage to the primary voltage to determine position and direction. No adjustments are required. 5. Multiple LVDTs can be driven by a single AD698 either in series or parallel as long as power dissipation limits are not exceeded. The excitation output is thermally protected. 6. The AD698 may be used as a loop integrator in the design of simple electromechanical servo loops. 7. The sum of the transducer secondary voltages do not need to be constant.

GSL2682_DataSheet_Chinese_RevA1.7

4.4.1. 睡眠模式...................................................................................................................................15

4.4.2. 运行模式...................................................................................................................................15

4.3.6. IRQ 中断....................................................................................................................................14

4.4. 运行模式...........................................................................................................................................15

功耗 o 正常模式: 〈9mA o 绿色模式: 〈3mA o 深度睡眠 :〈60uA

封装 o QFN48,6x6 mm

2

Silead Inc. 上海思立微电子科技有限公司-多点电容触控 IC

GSL2682 Capacitive Touchscreen Controller

目录

性能 ......................................................................................................................................................................1 目录 ......................................................................................................................................................................3 1. 管脚和原理图.............................................................................................................................................6

Dupline 8通道输入模块说明书

Du line®Specifications are subject to change without notice (01.02.2007)1•8-channel transmitter•8 contact or NPN transistor inputs (G2120 5501) or 8voltage or PNP transistor inputs (G2120 5502)•Open printed circuit board•Bracket for DIN-rail mounting available•LED-indications for supply and Dupline ®carrier •DC or Dupline ®supplied•Channel coding by GAP 1605Product DescriptionDupline transmitter design -ed to be a part of the Dupline ®concept for push buttons and lamps in eleva-tors. I nstaller friendlymounting, operation andmaintenance without re -quire m ent of any special tools or programming.Type SelectionSupply Ordering no.Ordering no.8 contact or NPN transistor inputs 8 voltage or PNP transistor input 10-30 VDCG 2120 5501 700G 2120 5502 700Input Specifications Type G2120 5501Supply Specifications (cont.)Input-Module for ElevatorsCurrent consumption When Dupline supplied≤ 0.9 mA Transient protection voltage 800 V Insultation voltage:Supply - Dupline ®None Supply - OutputsNoneType G 2120 5501 700, G 2120 5502 700Input Specifications Type G2120 5502General SpecificationsSupply SpecificationsPower supply DC types Installation cat III (IEC 60664)Operational voltage (V DD In )10-30 VDC (ripple included)Ripple≤ 3 V Reverse polarity protection Yes Power dissipation ≤ 0.5 W Current consumption≤ 20 mAC H A N N E L P R O G R A M P L U GDup (Dupline S)GNDPow (Supply input)DC+I1I2I3I4I5I6I7I8S u p p l yL i n eDu line®2Specifications are subject to change without notice (01.02.2007)Mode of OperationConnect the DC supply volt-age to the system through a G 2196 000X 700 Master Module, which also performs the channel generator func-tion and the RS485 commu-nication link to the elevator controller (please refer to the data sheet for G2196.. for details).Every I nput is given its indi-vidual address with the cod-ing unit GAP 1605 (Please refer to the respective datasheet for details). TheON/OFF-signal that is applied to the input of the module is associated to the address given to that input. An input pulse stretcher (only G 2201 5501) is used on every input to assure that the changes of input signals (even extremely short ones)are communicated by the system.No LED indication for Supply and Line when Dupline ®sup-plied.Pin AllocationPin Dup Gnd Pow DC+I1I2I3I4I5I6I7I8Input/Output Dupline ®Signal Dup. + Supply GndSupply In DC Out Input 1Input 2Input 3Input 4Input 5Input 6Input 7Input 8Wiring DiagramsG 2120 550. 700AccessoriesAluminum bracket for DIN mounting (Vertical)8047-bracket PVC bracket forDIN mounting (Horisontal)ELEVAT -Bracket DIN-railFMD 411C H A N N E L P R O G R A M P L U GDup (Dupline S)GNDPow (Supply input)DC+I1I2I3I4I5I6I7I8S u p p l yL i n eG2120 5501G2120 5502。

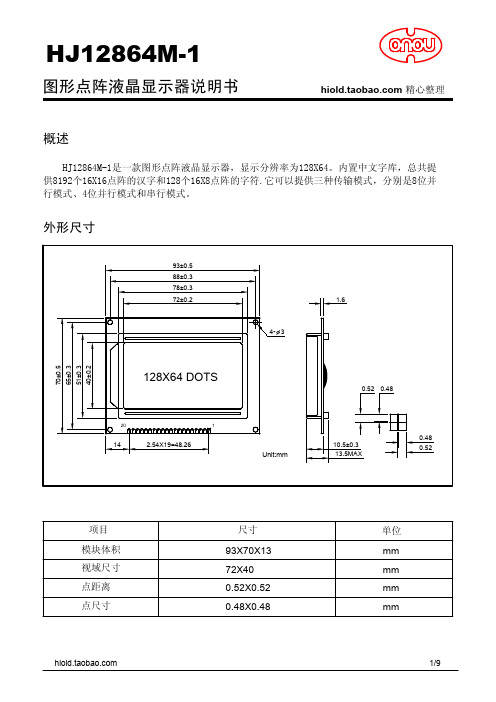

带字库型液晶屏12864中文资料 ST7920 (HJ12864M)

概述HJ12864M-1是一款图形点阵液晶显示器,显示分辨率为128X64。

内置中文字库,总共提供8192个16X16点阵的汉字和128个16X8点阵的字符.它可以提供三种传输模式,分别是8位并行模式、4位并行模式和串行模式。

外形尺寸项目尺寸单位mm mm mm mm93X70X1372X400.52X0.520.48X0.48模块体积视域尺寸点距离点尺寸HJ12864M-1 1/9图形点阵液晶显示器说明书模块接口定义并行模式接口定义串行模式接口定义片选端,高电平有效串行数据输入端CLK 串行同步时钟CS SID H/L 电源负极电源正极对比度调节0V +5V _123VSS VDD V0引脚号电平功能说明名称H/L H/L 背光电源正极19A 背光电源负极20K+5V 0VPSB=H :并行模式 PSB=L :串行模式15PSB H/L 复位端,低电平有效17/RESETH/L 456HJ12864M-1功能说明系统界面配合RS和RW可选择控制界面的4种模式:RS RW功能说明L L MPU写指令到指令暂存器(IR)L H读出忙标志(BF)及地址计数器(AC)的状态H L MPU写数据到数据暂存器(DR)H H MPU从数据暂存器(DR)中读出数据忙标志(BF)BF标志提供内部工作情况,BF=1表示模块在进行内部操作,此时模块不接受外部指令和数据;BF=0,表示模块为准备状态,可接受外部指令和数据。

利用STATUS RD 指令,可以将BF读到DB7总线 ,从而检验模块的工作状态。

地址计数器(AC)地址计数器(AC)用来存储DDRAM/CGRAM/GDRAM之一的地址,可由指令改变,之后读取或写入DDRAM/CGRAM/GDRAM的值时,地址计数器(AC)的值就会自动加1。

当RS=0,RW=1和RE=1时,地址计数器(AC)的值将被读到DB6-DB0中。

中文字型ROM(CGROM)和半宽字型ROM(HCGROM)字型产生ROM提供8192个中文字型和128个数字符号,利用两个字节将字型编码写入DDRAM,对应的内容将显示出来。

QMC6983矽睿传感器

EN

Enables 1° To 2° Degree Compass Heading Accuracy , Allows for Pedestrian Navigation and LBS Applications Maximizes Sensor’s Full Dynamic Range and Resolution

TI

A

L

FEATURES

BENEFIT

QMC6983 CONTENTS

1 2

吉泓盛一级代理0755-61681691 61681692

3

4

5

6

8

9

2

CO

N

FI

7

INTE RNAL SCHEMA TIC DIA GRAM ..............................................................................................................3 1.1 Internal Schematic Diagram ............................................................................................................3 SPECIFICA TIONS AND I/ O CHARA CTERIS TICS ..........................................................................................3 2.1 Product Specifications ....................................

S-80831中文资料

Hysteresis characteristics

5% typ.

Detection voltage

0.8 to 6.0 V (0.1 V step)

Nch open-drain active low and CMOS active low output SC-82AB Super-small plastic package TO-92 Plastic package SOT-89-3 Miniaturized power mold plastic package SOT-23-5 Very-small plastic package

Battery checker Power failure detector Power monitor for pagers, calculators,

organizers,

Constant voltage power monitor for cameras,

video equipment, communication devices

OUT VDD NC VSS

1 2 3

OUT VDD VSS

1 Bottom view

2

3

1

2

3

Figure 1

Seiko InstrALL PACKAGE HIGH-PRECISION VOLTAGE DETECTOR S-808 Series

2

Seiko Instruments Inc.

易网

SUPER-SMALL PACKAGE HIGH-PRECISION VOLTAGE DETECTOR S-808 Series

Table 1

Detection voltage range (V) 0.8V±2.0% 0.9V±2.0% 1.0V±2.0% 1.1V±2.0% 1.2V±2.0% 1.3V±2.0% 1.4V±2.0% 1.5V±2.0% 1.6V±2.0% 1.7V±2.0% 1.8V±2.0% 1.9V±2.0% 2.0V±2.0% 2.1V±2.0% 2.2V±2.0% 2.3V±2.0% 2.4V±2.0% 2.5V±2.0% 2.6V±2.0% 2.7V±2.0% 2.8V±2.0% 2.9V±2.0% 3.0V±2.0% 3.1V±2.0% 3.2V±2.0% 3.3V±2.0% 3.4V±2.0% 3.5V±2.0% 3.6V±2.0% 3.7V±2.0% 3.8V±2.0% 3.9V±2.0% 4.0V±2.0% 4.1V±2.0% 4.2V±2.0% 4.3V±2.0% 4.4V±2.0% 4.5V±2.0% 4.6V±2.0% 4.7V±2.0% 4.8V±2.0% 4.9V±2.0% 5.0V±2.0% 5.1V±2.0% 5.2V±2.0% 5.3V±2.0% 5.4V±2.0% 5.5V±2.0% 5.6V±2.0% 5.7V±2.0% 5.8V±2.0% 5.9V±2.0% 6.0V±2.0% Hysteresis width VHYS typ.(V) 0.034 0.044 0.054 0.064 0.073 0.083 0.093 0.075 0.080 0.085 0.090 0.095 0.100 0.105 0.110 0.115 0.120 0.125 0.130 0.135 0.140 0.145 0.150 0.155 0.160 0.165 0.170 0.175 0.180 0.185 0.190 0.195 0.200 0.205 0.210 0.215 0.220 0.225 0.230 0.235 0.240 0.245 0.250 0.255 0.260 0.265 0.270 0.275 0.280 0.285 0.290 0.295 0.300 Nch Open Drain(Low) SC-82AB S-80808ANNP-E7Y-T2 S-80809ANNP-E7Z-T2 S-80810ANNP-E70-T2 S-80811ANNP-E71-T2 S-80812ANNP-E72-T2 S-80813ANNP-EDA-T2 S-80814ANNP-EDB-T2 S-80815ANNP-EDC-T2 S-80816ANNP-EDD-T2 S-80817ANNP-EDE-T2 S-80818ANNP-EDF-T2 S-80819ANNP-EDG-T2 S-80820ANNP-EDH-T2 S-80821ANNP-EDJ-T2 S-80822ANNP-EDK-T2 S-80823ANNP-EDL-T2 S-80824ANNP-EDM-T2 S-80825ANNP-EDN-T2 S-80826ANNP-EDP-T2 S-80827ANNP-EDQ-T2 S-80828ANNP-EDR-T2 S-80829ANNP-EDS-T2 S-80830ANNP-EDT-T2 S-80831ANNP-EDV-T2 S-80832ANNP-EDW -T2 S-80833ANNP-EDX-T2 S-80834ANNP-EDY-T2 S-80835ANNP-EDZ-T2 S-80836ANNP-ED0-T2 S-80837ANNP-ED1-T2 S-80838ANNP-ED2-T2 S-80839ANNP-ED3-T2 S-80840ANNP-ED4-T2 S-80841ANNP-ED5-T2 S-80842ANNP-ED6-T2 S-80843ANNP-ED7-T2 S-80844ANNP-ED8-T2 S-80845ANNP-ED9-T2 S-80846ANNP-EJA-T2 S-80847ANNP-EJB-T2 S-80848ANNP-EJC-T2 S-80849ANNP-EJD-T2 S-80850ANNP-EJE-T2 S-80851ANNP-EJF-T2 S-80852ANNP-EJG-T2 S-80853ANNP-EJH-T2 S-80854ANNP-EJJ-T2 S-80855ANNP-EJK-T2 S-80856ANNP-EJL-T2 S-80857ANNP-EJM-T2 S-80858ANNP-EJN-T2 S-80859ANNP-EJP-T2 S-80860ANNP-EJQ-T2 TO-92 — — — — — — — S-80815ANY S-80816ANY S-80817ANY S-80818ANY S-80819ANY S-80820ANY S-80821ANY S-80822ANY S-80823ANY S-80824ANY S-80825ANY S-80826ANY S-80827ANY S-80828ANY S-80829ANY S-80830ANY S-80831ANY S-80832ANY S-80833ANY S-80834ANY S-80835ANY S-80836ANY S-80837ANY S-80838ANY S-80839ANY S-80840ANY S-80841ANY S-80842ANY S-80843ANY S-80844ANY S-80845ANY S-80846ANY S-80847ANY S-80848ANY S-80849ANY S-80850ANY S-80851ANY — S-80853ANY — — — — — — — SOT-89-3 — — — — — — — S-80815ANUP-EDC-T2 S-80816ANUP-EDD-T2 S-80818ANUP-EDF-T2 SOT-23-5 — — — — — — — — — S-80818ANMP-EDF-T2

氢溴酸右美沙芬片人体药代动力学及生物等效性研究 (1)

教育和健康教育,通过政府行为和多种渠道,最大限度的普及群众性的院前急救知识和急救技术,才能最大限度的降低院前病死率和致残率。

参考文献:[1] 田育红,李奇林,黄力.73875例院前急救病例特点的分析[J].世界急危重病医学,2006,3(4):1368~1369[2] 邹强.呼吸心脏骤停1683例院前急救死亡分析[J].四川医学,2004,25(3):307~308[3] 陈云兵.高原地区院前急救的流行病学研究[J].四川医学,2009,30(1):32~34[4] 梁实,江捍平,贾清旺,等.深圳市2002年度院前死亡1122例分析[J].中华急诊医学杂志,2004,13(11):733~736[5] 蒋键,陈尔真.652例急诊抢救室死亡患者分析[J].中国急救医学,2001,4(21):230~231[6] 瞿惠春.874例院外猝死临床分析与急救干预[J].中国急救医学,2001,1(21):14~16[7] 刘德红.53例心源性猝死的临床分析[J].世界急危重病医学,2005,2(4):787~790(收稿日期:2009-03-05)论著氢溴酸右美沙芬片人体药代动力学及生物等效性研究杨晓燕1,田晓娟1,刘泽源2(1.北京市药品审评中心,北京100053;2.军事医学科学院附属307医院,北京100000)=摘要> 目的 在中国健康成年男性志愿者中研究氢溴酸右美沙芬片受试制剂与参比制剂的生物等效性和相对生物利用度。

方法 本试验采用双周期自身随机交叉试验设计。

20名受试者分两组,先后口服受试和参比制剂60m g ,两次用药间隔1周。

采用HPLC -M S -M S 测定。

结果 受试制剂及参比制剂右美沙芬C m ax 为(5132?4131)L g /L 和(5110?3193)L g /L ;T max 为(1190?0164)h 和(2135?0184)h ;t 1/2(ke)为(5127?1123)h 和(6130?1191)h ;AUC 0-tn 为(4116624?4511097)L g #h /L 和(4312911?4817679)L g #h /L,AU C 0-]为(4417446?5013424)L g #h /L 和(4617772?5315734)L g #h /L ;相对生物利用度F 0-tn 、F 0-]分别为(98100?17131)%、(96120?17169)%。

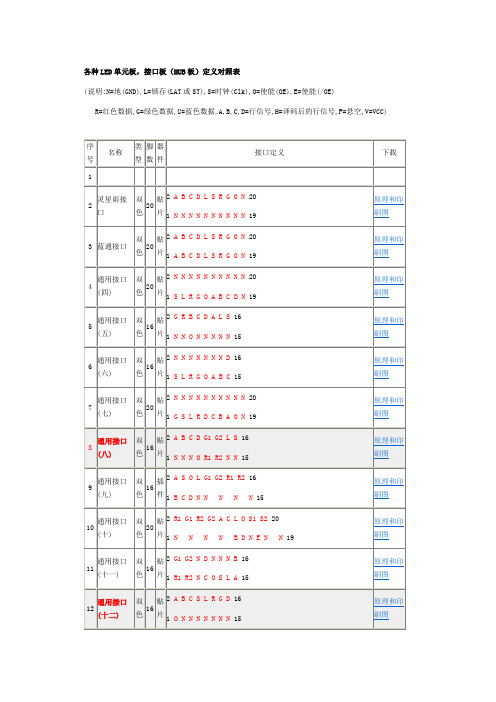

各种LED单元板,接口板(HUB板)定义对照表

各种LED单元板,接口板(HUB板)定义对照表(说明:N=地(GND),L=锁存(LAT或ST),S=时钟(Clk),O=使能(OE),E=使能(/OE)R=红色数据,G=绿色数据,U=蓝色数据,A,B,C,D=行信号,H=译码后的行信号,F=悬空,V=VCC)88 通用接口(八十八) 全彩 16 贴片 2 OE CLK LAT R1 R2 G B F 16 1 N N N N N N N N 15原理和印刷图89 通用接口(八十九) 全彩 20 贴片 2 G1 B1 R1 F CLK LAT OE G2 B2 R2 20 1 N N N N N N N N N N 19 原理和印刷图90通用接口(九十)全彩 16 贴片 2 G1 F G2 F F F F N 16 1 R1 B1 R2 B2 CLK LAT OE F 15 原理和印刷图92 通用接口(九十二) 全彩 20 贴片 2 G1 R2 B2 F F F A C L N 201 R1 B1 G2 F F F N B S O 19 原理和印刷图93 通用接口(九十三) 双色 20 贴片 2 S L R1 G1 O A B C D S 20 1 F F R2 G2 N N N F N N 19 原理和印刷图94 通用接口(九十四) 全彩 16 贴片 2 G1 R2 B2 G3 R4 B4 L N 16 1 R1 B1 G2 R3 B3 G4 S O 15 原理和印刷图94A 通用接口(九十四A) 全彩 16贴片 2 G1 R2 B2 G3 R4 B4 L N 16 1 R1 B1 G2 R3 B3 G4 S O 15原理和印刷图95 通用接口(九十五) 全彩 26 贴片 2 R2 R4 F F G2 G4 B2 B4 N F F F N 26 1 R1 R3 F F G1 G3 B1 B3 N CLK LAT O N 25 原理和印刷图 96 通用接口(九十六) 全彩 8 贴片 1 L N BD O GD N S RD 8 原理和印刷图 97 通用接口(九十七) 全彩 10 贴片 2 G N N A B 10 1 R B S L O 9原理和印刷图98 通用接口(九十八) 虚拟 20 贴片 2 G1 R2 G2 R3 N N N N N N 20 1 R1 U1 R2 U2 A B C CLK LAT O 19 原理和印刷图99 通用接口(九十九) 全彩 32 贴片 2 B N N N R2 G2 U2 N B N N N R2 G2 U2 N 32 1 A C S L R1 G1 U1 O A C D L R1 G1 U1 O 31 原理和印刷图100通用接口(一百)全彩 16 贴片 2 B N N N R2 G2 U2 N 16 1 A C S L R1 G1 U1 O 15 原理和印刷图101 通用接口(一零一) 单色 16贴片 2 O S R F F F F L 161 F F N F F F F F 15原理和印刷图102 通用接口(一零二) 全彩 26 贴片2 R2 R4 N G2 G4 N B2 B4 CLK LAT O A B 26原理和印刷图1 R1 R3 N G1 G3 N B1 B3 N N N N N 25103 通用接口(一零三) 全彩 16贴片 2 GD N F N B N LAT N 16 1 RD BD F F A C CLK OE 8原理和印刷图104 通用接口(一零四) 全彩 14贴片 2 LAT CLK OE RA GD BD RB 14 1 N N N N N N N 7 原理和印刷图105 通用接口(一零五) 虚拟 16贴片 2 GD RB N N N N N N 16 1 RA BD OE LAT CLK A B C 8 原理和印刷图106 通用接口(一零六) 全彩 10贴片 2 LAT CLK BD GD RD 10 1 OE N N N N 5 原理和印刷图107 通用接口(一零七) 全彩 10贴片 2 S L O R B 10 1 N N N N G 5原理和印刷图108 通用接口(一零八) 全彩 26贴片 2 RD1 GD1 BD1 RD2 GD2 BD2 CLK LAT OE A B C D 261 N N N N N N N N N NN N N 13原理和印刷图 109 通用接口(一零九) 全彩 16贴片 2 F BD1 N N N N N N 16 1 RD1 GD1 LAT CLK OE RD2 GD2 BD2 8 原理和印刷图110 通用接口(一一零) 全彩 26贴片 2 R2 N N R4 N N N A B C 26 1 R1 G1 B1 R3 G2 B2 CLK LAT OE D 13原理和印刷图111 通用接口(一一一) 全彩 26贴片 2 N N N N N N N N B3 B1 G3 G1 R3 R1 26 1 F A CLK LAT OE OE OE B4 B2 G4 G2 R4 R2 13 原理和印刷图 112 通用接口(一一二) 双色 26贴片 2 R1 G1 R2 G2 R3 G3 R4 G4 A B CLK OE LAT 26 1 N N N N N N N N N N N N N 13 原理和印刷图113 通用接口(一一三) 全彩 20贴片 2 N N N N N N N N N N 20 1 CLK LAT DR DG OE A B C D DB 10 原理和印刷图114 通用接口(一一四) 全彩 16贴片 2 N DB N N N N N N 16 1 DR DG LAT CLK OE N N N 8 原理和印刷图115 通用接口(一一五) 全彩 10 贴片2 G N C A B 10原理和印刷图1 R B S L O 9116 通用接口(一一六) 全彩 60贴片 2 R2 R4 R6 R8 R10 R12 R14 R16 G2 G4 G6 G8 G10 G12 G14 G16B2 B4 B6 B8 B10 B12 B14 B16 O O O LAT CLK N 60 1 R1 R3 R5 R7 R9 R11 R13 R15 G1 G3 G5 G7 G9 G11 G13 G15 B1B3 B5 B7 B9 B11 B13 B15 N N N N N N 59原理和印刷图 117 通用接口(一一七) 全彩 26贴片 2 N LAT N O N R2 R4 G2 G4 B2 B4 N F 26 1 N CL K N O O R1 R3 G1 G3 B1 B3 N F 25 原理和印刷图118 通用接口(一一八) 全彩 16贴片 2 RB1 B1 RB2 B2 N N N B 16 1 RA1 G1 RA2 G2 CLK LAT O A 15 原理和印刷图119 通用接口(一一九) 全彩 16贴片 2 N O L R1 G1 U1 A C 16 1 N O O S R2 G2 U2 B 15 原理和印刷图120 通用接口(一二零) 虚拟 16贴片 2 G1 R2A B2 R2B F F LAT N 16 1 R1A B1 G2 R1B F F CLK OE 15 原理和印刷图121 通用接口(一二一) 虚拟 16贴片 2 RB1 U1 RB2 U2 N N N N 16 1 RA1 G1 RA2 G2 S L O A 15原理和印刷图122 通用接口(一二二) 虚拟 26贴片 2 RB1 U1 RB2 U2 N RB3 U3 RB4 U4 N L A B 26 1 RA1 G1 RA2 G2 N RA3 G3 RA4 G4 N S O N 25 原理和印刷图123 通用接口(一二三) 虚拟 30贴片 2 RB1 U1 RA2 G2 N F S S L L O O A F B 30 1 RA1 G1 N RB2 U2 F N N N N N N N B A 29 原理和印刷图124 通用接口(一二四) 全彩 20贴片 2 N N N N N N N O B D 20 1 S S L L R G U O A C 19原理和印刷图。

G698中文资料

MIN

0.8 1 ----4.50 4.23 3.88 3.25 3.04 2.86 2.59 3.6 --0.87 3 0.5 8

TYP MAX

----16.5 13.9 4.60 4.32 3.96 3.30 3.10 2.91 2.64 5.3 70 1.25 5 0.88 --5.5 5.5 25 22 4.69 4.40 4.04 3.37 3.16 2.96 2.69 7 --1.29 --1.2 ---

Ordering Information

ORDER NUMBER TEMP. RANGE

G698H(L)xxxT1U G699LxxxT1U -40°C ~ +105°C -40°C ~ +105°C

PACKAGE

SOT23-5 SOT23-5

Note:T1 : SOT23-5

U : Tape & Reel * xxx specifies the threshold voltage. e.g. 263 denotes the 2.63V threshold voltage.

()is for G698H

*G699 ONLY

Ver: 1.3 Jun 03, 2004

TEL: 886-3-5788833

1

元器件交易网

Global Mixed-mode Technology Inc.

Absolute Maximum Ratings

Power-Supply Voltages

Fully Specified Over Temperature Available in Three Output Configurations Push-Pull RESET Output (G698L) Push-Pull RESET Output (G698H) Open-Drain RESET Output (G699L) Externaelay Generator 14µA Supply Current Guaranteed Reset Valid to VCC = 0.8V Power Supply Transient Immunity 5 pin SOT23-5 Packages 2% Threshold Accuracy

HC32L130_HC32L136系列用户手册Rev1.4

HC32L130系列/ HC32L136系列32位ARM® Cortex®-M0+ 微控制器用户手册前言非常感谢大家对华大半导体产品的支持和信赖。

使用本系列产品前,请系统阅读本手册和“数据手册”。

➢本手册的目的和对象读者本手册主要介绍本系列的功能、操作事项和使用方法。

对象读者为使用本系列实际开发产品的工程师。

※本手册介绍外设功能的构成和操作说明,但不包括该系列的规格说明。

关于芯片规格,详情参见其对应的“数据手册”。

➢样本程序和开发环境华大半导体提供外设功能运行用的样本程序和本系列所需的开发环境说明。

关于华大微控制器的运行规格和使用方法,请联系本公司。

➢微控制器支持信息:/mcu.htm©2019 华大半导体有限公司- 保留所有权利目录前言 (2)目录 (3)简介 (34)产品特性超低功耗MCU (35)1功能模块 (36)1.132 位CORTEX M0+ 内核 (37)1.264K Byte FLASH (37)1.38K Byte RAM (37)1.4时钟系统 (37)1.5工作模式 (38)1.6硬件实时时钟RTC (38)1.7通用IO 端口 (38)1.8中断控制器 (38)1.9复位控制器 (39)1.10DMAC (40)1.11定时器/计数器 (40)1.12超低功耗脉冲计数器PCNT (42)1.13看门狗WDT (43)1.14通用异步收发器UART0~UART1 (43)1.15低功耗异步收发器LPUART0~LPUART1 (43)1.16同步串行接口SPI (44)1.17I2C 总线 (44)1.18蜂鸣器Buzzer (45)1.19时钟校准电路 (45)1.20唯一识别号UID (45)1.21CRC16/32 硬件循环冗余校验码 (45)1.2232位硬件除法器 (46)1.23AES 硬件加密 (46)1.24TRNG 真随机数发生器 (46)1.2512 Bit SARADC (46)1.26电压比较器VC (47)1.27低电压检测器LVD (47)1.28运放OPA (48)1.29LCD 驱动 (48)1.30嵌入式调试系统 (48)1.31在线编程模式 (49)1.32高安全性 (49)2引脚配置及功能 (50)2.1封装示意图 (50)2.2引脚功能说明 (54)3系统结构 (64)3.1概述 (64)3.2系统地址划分 (65)3.3存储器和模块地址分配 (66)4工作模式 (68)4.1运行模式 (70)4.2休眠模式 (72)4.3深度休眠模式 (74)5系统控制器(SYSCTRL) (77)5.1系统时钟介绍 (77)5.1.1内部高速RC时钟RCH (78)5.1.2内部低速RC 时钟RCL (78)5.1.3外部低速晶振时钟XTL (79)5.1.4外部高速晶振时钟XTH (79)5.1.5锁相环时钟PLL (79)5.1.6时钟启动过程 (80)5.2系统时钟切换 (81)5.2.1标准的时钟切换流程 (81)5.2.2RCH不同振荡频率间切换流程 (82)5.2.3从其它时钟切换到XTL示例 (82)5.2.4从其它时钟切换到XTH示例 (83)5.2.5从其它时钟切换到RCL示例 (83)5.2.6从其它时钟切换到RCH示例 (84)5.2.7PLL与RCH相互切换示例,参考时钟为RCH (84)5.2.8PLL与XTH相互切换示例,参考时钟为XTH (85)5.3时钟校准模块 (86)5.4中断唤醒控制 (88)5.4.1从深度休眠模式唤醒后执行中断服务程序的方法 (88)5.4.2从深度休眠模式唤醒后不执行中断服务程序的方法 (88)5.4.3使用退出休眠特性 (89)5.5寄存器 (91)5.5.1系统控制寄存器0(SYSCTRL0) (92)5.5.2系统控制寄存器1(SYSCTRL1) (94)5.5.3系统控制寄存器2(SYSCTRL2) (96)5.5.4RCH 控制寄存器(RCH_CR) (97)5.5.5XTH 控制寄存器(XTH_CR) (98)5.5.6RCL 控制寄存器(RCL_CR) (99)5.5.7XTL 控制寄存器(XTL_CR) (100)5.5.8PLL 控制寄存器(PLL_CR) (101)5.5.9外围模块时钟控制寄存器(PERI_CLKEN) (103)6复位控制器(RESET) (105)6.1.1上电下电复位POR (105)6.1.2外部复位引脚复位 (106)6.1.3WDT复位 (106)6.1.4PCA复位 (106)6.1.5LVD低电压复位 (106)6.1.6Cortex-M0+ SYSRESETREQ复位 (106)6.1.7Cortex-M0+ LOCKUP复位 (106)6.2寄存器 (107)6.2.1复位标识寄存器(RESET_FLAG) (107)6.2.2外围模块复位控制寄存器(PREI_RESET) (109)7中断控制器(NVIC) (111)7.1概述 (111)7.2中断优先级 (111)7.3中断向量表 (112)7.4中断输入和挂起行为 (113)7.5中断等待 (116)7.6中断源 (117)7.7中断结构图 (119)7.8寄存器 (121)7.8.1中断使能设置寄存器(SCS_SETENA) (121)7.8.2中断使能清除寄存器(SCS_CLRENA) (122)7.8.3中断挂起状态设置寄存器(SCS_SETPEND) (122)7.8.4中断挂起状态清除寄存器(SCS_CLRPEND) (123)7.8.5中断优先级寄存器(SCS_IPR0) (124)7.8.6中断优先级寄存器(SCS_IPR1) (125)7.8.7中断优先级寄存器(SCS_IPR2) (126)7.8.8中断优先级寄存器(SCS_IPR3) (127)7.8.9中断优先级寄存器(SCS_IPR4) (128)7.8.10中断优先级寄存器(SCS_IPR5) (129)7.8.11中断优先级寄存器(SCS_IPR6) (130)7.8.12中断优先级寄存器(SCS_IPR7) (131)7.8.13中断屏蔽特殊寄存器(SCS_PRIMASK) (132)7.9软件基本操作 (133)7.9.1外部中断使能 (133)7.9.2NVIC 中断使能和清除使能 (133)7.9.3NVIC 中断挂起和清除挂起 (133)7.9.4NVIC 中断优先级 (133)7.9.5NVIC 中断屏蔽 (134)8端口控制器(GPIO) (135)8.1端口控制器简介 (135)8.2端口控制器主要特性 (135)8.3.1端口配置功能 (136)8.3.2端口数字复用功能 (138)8.3.3端口中断功能 (140)8.4端口配置操作流程 (141)8.4.1端口复用配置为模拟端口操作流程 (141)8.4.2端口复用配置为数字通用端口操作流程 (141)8.4.3端口复用配置为数字功能端口操作流程 (141)8.4.4端口复用配置为调试测试端口操作流程 (141)8.4.5端口复用配置为红外输出信号操作流程 (141)8.4.6端口高电平中断操作流程 (142)8.4.7端口低电平中断操作流程 (142)8.4.8端口上升沿中断操作流程 (142)8.4.9端口下降沿中断操作流程 (142)8.4.10端口上拉使能配置操作流程 (143)8.4.11端口下拉使能配置操作流程 (143)8.4.12端口增强驱动配置操作流程 (143)8.4.13端口开漏输出配置操作流程 (143)8.4.14端口位置位操作流程 (143)8.4.15端口位清零操作流程 (143)8.4.16端口位置位清零操作流程 (143)8.5端口控制器寄存器描述 (144)8.5.1端口PA (148)8.5.1.1端口PA00功能配置寄存器(PA00_SEL) (148)8.5.1.2端口PA01功能配置寄存器(PA01_SEL) (149)8.5.1.3端口PA02功能配置寄存器(PA02_SEL) (150)8.5.1.4端口PA03功能配置寄存器(PA03_SEL) (151)8.5.1.5端口PA04功能配置寄存器(PA04_SEL) (152)8.5.1.6端口PA05功能配置寄存器(PA05_SEL) (153)8.5.1.7端口PA06功能配置寄存器(PA06_SEL) (154)8.5.1.8端口PA07功能配置寄存器(PA07_SEL) (155)8.5.1.9端口PA08功能配置寄存器(PA08_SEL) (156)8.5.1.10端口PA09功能配置寄存器(PA09_SEL) (157)8.5.1.11端口PA10功能配置寄存器(PA10_SEL) (158)8.5.1.12端口PA11功能配置寄存器(PA11_SEL) (159)8.5.1.13端口PA12功能配置寄存器(PA12_SEL) (160)8.5.1.14端口PA13功能配置寄存器(PA13_SEL) (161)8.5.1.15端口PA14功能配置寄存器(PA14_SEL) (162)8.5.1.16端口PA15功能配置寄存器(PA15_SEL) (163)8.5.1.17端口PA输入输出配置寄存器(PADIR) (164)8.5.1.18端口PA输入值寄存器(PAIN) (165)8.5.1.19端口PA输出值配置寄存器(PAOUT) (166)8.5.1.20端口PA数模配置寄存器(PAADS) (167)8.5.1.21端口PA位置位寄存器(PABSET) (168)8.5.1.22端口PA位清零寄存器(PABCLR) (169)8.5.1.23端口PA位置位清零寄存器(PABSETCLR) (170)8.5.1.24端口PA驱动能力配置寄存器(PADR) (171)8.5.1.25端口PA上拉使能配置寄存器(PAPU) (172)8.5.1.26端口PA下拉使能配置寄存器(PAPD) (173)8.5.1.27端口PA开漏输出配置寄存器(PAOD) (174)8.5.1.28端口PA高电平中断使能配置寄存器(PAHIE) (175)8.5.1.29端口PA低电平中断使能配置寄存器(PALIE) (176)8.5.1.30端口PA上升沿中断使能配置寄存器(PARIE) (177)8.5.1.31端口PA下降沿中断使能配置寄存器(PAFIE) (178)8.5.1.32端口PA中断状态寄存器(PA_STA T) (179)8.5.1.33端口PA中断清除寄存器(PA_ICLR) (180)8.5.2端口PB (181)8.5.2.1端口PB00功能配置寄存器(PB00_SEL) (181)8.5.2.2端口PB01功能配置寄存器(PB01_SEL) (182)8.5.2.3端口PB02功能配置寄存器(PB02_SEL) (183)8.5.2.4端口PB03功能配置寄存器(PB03_SEL) (184)8.5.2.5端口PB04功能配置寄存器(PB04_SEL) (185)8.5.2.6端口PB05功能配置寄存器(PB05_SEL) (186)8.5.2.7端口PB06功能配置寄存器(PB06_SEL) (187)8.5.2.8端口PB07功能配置寄存器(PB07_SEL) (188)8.5.2.9端口PB08功能配置寄存器(PB08_SEL) (189)8.5.2.10端口PB09功能配置寄存器(PB09_SEL) (190)8.5.2.11端口PB10功能配置寄存器(PB10_SEL) (191)8.5.2.12端口PB11功能配置寄存器(PB11_SEL) (192)8.5.2.13端口PB12功能配置寄存器(PB12_SEL) (193)8.5.2.14端口PB13功能配置寄存器(PB13_SEL) (194)8.5.2.15端口PB14功能配置寄存器(PB14_SEL) (195)8.5.2.16端口PB15功能配置寄存器(PB15_SEL) (196)8.5.2.17端口PB输入输出配置寄存器(PBDIR) (197)8.5.2.18端口PB输入值寄存器(PBIN) (198)8.5.2.19端口PB输出值配置寄存器(PBOUT) (199)8.5.2.20端口PB数模配置寄存器(PBADS) (200)8.5.2.21端口PB位置位寄存器(PBBSET) (201)8.5.2.22端口PB位清零寄存器(PBBCLR) (202)8.5.2.23端口PB位置位清零寄存器(PBBSETCLR) (203)8.5.2.24端口PB驱动能力配置寄存器(PBDR) (204)8.5.2.25端口PB上拉使能配置寄存器(PBPU) (205)8.5.2.26端口PB下拉使能配置寄存器(PBPD) (206)8.5.2.27端口PB开漏输出配置寄存器(PBOD) (207)8.5.2.29端口PB低电平中断使能配置寄存器(PBLIE) (209)8.5.2.30端口PB上升沿中断使能配置寄存器(PBRIE) (210)8.5.2.31端口PB下降沿中断使能配置寄存器(PBFIE) (211)8.5.2.32端口PB中断状态寄存器(PB_STA T) (212)8.5.2.33端口PB中断清除寄存器(PB_ICLR) (213)8.5.3端口PC (214)8.5.3.1端口PC00功能配置寄存器(PC00_SEL) (214)8.5.3.2端口PC01功能配置寄存器(PC01_SEL) (215)8.5.3.3端口PC02功能配置寄存器(PC02_SEL) (216)8.5.3.4端口PC03功能配置寄存器(PC03_SEL) (217)8.5.3.5端口PC04功能配置寄存器(PC04_SEL) (218)8.5.3.6端口PC05功能配置寄存器(PC05_SEL) (219)8.5.3.7端口PC06功能配置寄存器(PC06_SEL) (220)8.5.3.8端口PC07功能配置寄存器(PC07_SEL) (221)8.5.3.9端口PC08功能配置寄存器(PC08_SEL) (222)8.5.3.10端口PC09功能配置寄存器(PC09_SEL) (223)8.5.3.11端口PC10功能配置寄存器(PC10_SEL) (224)8.5.3.12端口PC11功能配置寄存器(PC11_SEL) (225)8.5.3.13端口PC12功能配置寄存器(PC12_SEL) (226)8.5.3.14端口PC13功能配置寄存器(PC13_SEL) (227)8.5.3.15端口PC14功能配置寄存器(PC14_SEL) (228)8.5.3.16端口PC15功能配置寄存器(PC15_SEL) (229)8.5.3.17端口PC输入输出配置寄存器(PCDIR) (230)8.5.3.18端口PC输入值寄存器(PCIN) (231)8.5.3.19端口PC输出值配置寄存器(PCOUT) (232)8.5.3.20端口PC数模配置寄存器(PCADS) (233)8.5.3.21端口PC位置位寄存器(PCBSET) (234)8.5.3.22端口PC位清零寄存器(PCBCLR) (235)8.5.3.23端口PC位置位清零寄存器(PCBSETCLR) (236)8.5.3.24端口PC驱动能力配置寄存器(PCDR) (237)8.5.3.25端口PC上拉使能配置寄存器(PCPU) (238)8.5.3.26端口PC下拉使能配置寄存器(PCPD) (239)8.5.3.27端口PC开漏输出配置寄存器(PCOD) (240)8.5.3.28端口PC高电平中断使能配置寄存器(PCHIE) (241)8.5.3.29端口PC低电平中断使能配置寄存器(PCLIE) (242)8.5.3.30端口PC上升沿中断使能配置寄存器(PCRIE) (243)8.5.3.31端口PC下降沿中断使能配置寄存器(PCFIE) (244)8.5.3.32端口PC中断状态寄存器(PC_STAT) (245)8.5.3.33端口PC中断清除寄存器(PC_ICLR) (246)8.5.4端口PD (247)8.5.4.1端口PD00功能配置寄存器(PD00_SEL) (247)8.5.4.3端口PD02功能配置寄存器(PD02_SEL) (249)8.5.4.4端口PD03功能配置寄存器(PD03_SEL) (250)8.5.4.5端口PD04功能配置寄存器(PD04_SEL) (251)8.5.4.6端口PD05功能配置寄存器(PD05_SEL) (252)8.5.4.7端口PD06功能配置寄存器(PD06_SEL) (253)8.5.4.8端口PD07功能配置寄存器(PD07_SEL) (254)8.5.4.9端口PD输入输出配置寄存器(PDDIR) (255)8.5.4.10端口PD输入值寄存器(PDIN) (256)8.5.4.11端口PD输出值配置寄存器(PDOUT) (257)8.5.4.12端口PD数模配置寄存器(PDADS) (258)8.5.4.13端口PD位置位寄存器(PDBSET) (259)8.5.4.14端口PD位清零寄存器(PDBCLR) (260)8.5.4.15端口PD位置位清零寄存器(PDBSETCLR) (261)8.5.4.16端口PD驱动能力配置寄存器(PDDR) (262)8.5.4.17端口PD上拉使能配置寄存器(PDPU) (263)8.5.4.18端口PD下拉使能配置寄存器(PDPD) (264)8.5.4.19端口PD开漏输出配置寄存器(PDOD) (265)8.5.4.20端口PD高电平中断使能配置寄存器(PDHIE) (266)8.5.4.21端口PD低电平中断使能配置寄存器(PDLIE) (267)8.5.4.22端口PD上升沿中断使能配置寄存器(PDRIE) (268)8.5.4.23端口PD下降沿中断使能配置寄存器(PDFIE) (269)8.5.4.24端口PD中断状态寄存器(PD_STAT) (270)8.5.4.25端口PD中断清除寄存器(PD_ICLR) (271)8.5.5端口辅助功能 (272)8.5.5.1端口辅助功能配置寄存器0(GPIO_CTRL0) (272)8.5.5.2端口辅助功能配置寄存器1(GPIO_CTRL1) (273)8.5.5.3端口辅助功能配置寄存器2(GPIO_CTRL2) (275)8.5.5.4端口辅助功能定时器门控选择(GPIO_TIMGS) (276)8.5.5.5端口辅助功能定时器ETR选择(GPIO_TIMES) (277)8.5.5.6端口辅助功能定时器捕获输入选择(GPIO_TIMCPS) (278)8.5.5.7端口辅助功能PCA捕获选择(GPIO_PCAS) (279)9I2C总线(I2C) (280)9.1I2C 简介 (280)9.2I2C 主要特性 (280)9.3I2C 协议描述 (281)9.3.1I2C 总线上数据传输 (281)9.3.2起始位或重复起始信号 (282)9.3.3从机地址传输 (282)9.3.4数据传输 (282)9.4I2C 功能描述 (284)9.4.1I2C 工作模式 (285)9.4.2仲裁与同步逻辑 (285)9.4.3串行时钟发生器 (286)9.4.4输入滤波器 (286)9.4.5地址比较器 (286)9.4.6中断产生器 (287)9.4.7I2C 主机发送模式 (287)9.4.8I2C 主机接收模式 (290)9.4.9I2C 从机接收模式 (292)9.4.10I2C 从机发送模式 (296)9.4.11I2C 其他杂项状态 (298)9.5I2C 操作模式 (299)9.5.1初始化程序 (299)9.5.2启动主机发送功能 (299)9.5.3启动主机接收功能 (299)9.5.4I2C中断程序 (300)9.5.5无指定模式的状态 (300)9.5.6主发送器状态 (301)9.5.7主接收状态 (302)9.5.8从接收器状态 (303)9.5.9从发送器状态 (305)9.6I2C寄存器描述 (308)9.6.1I2C波特率计数器使能寄存器(I2Cx_TMRUN) (308)9.6.2I2C波特率计数器配置寄存器(I2Cx_TM) (309)9.6.3I2C配置寄存器(I2Cx_CR) (310)9.6.4I2C数据寄存器(I2Cx_DATA) (311)9.6.5I2C地址寄存器(I2Cx_ADDR) (312)9.6.6I2C状态寄存器(I2Cx_STAT) (313)10串行外设接口(SPI) (314)10.1SPI 简介 (314)10.2SPI 主要特性 (314)10.3SPI 功能描述 (315)10.3.1SPI 主机查询方式 (315)10.3.2SPI 主机DMA方式 (316)10.3.3SPI 主机数据时钟时序 (317)10.3.4SPI 从机查询方式 (318)10.3.5SPI 从机DMA方式 (319)10.3.6SPI 从机数据时钟时序 (320)10.4SPI 中断 (321)10.5SPI 多主机/多从机系统的配置 (322)10.6SPI 引脚配置说明 (323)10.7SPI 寄存器描述 (324)10.7.1SPI配置寄存器(SPIx_CR) (325)10.7.2SPI片选配置寄存器(SPIx_SSN) (326)10.7.3SPI状态寄存器(SPIx_STA T) (327)10.7.4SPI数据寄存器(SPIx_DA TA) (328)10.7.5SPI配置寄存器2(SPIx_CR2) (329)10.7.6SPI中断清除寄存器2(SPIx_ICLR) (330)11时钟校准模块(CLKTRIM) (331)11.1CLKTRIM 简介 (331)11.2CLKTRIM主要特性 (331)11.3CLKTRIM功能描述 (332)11.3.1CLKTRIM校准模式 (332)11.3.1.1时钟校准原理 (332)11.3.1.2时钟校准模块硬件结构 (332)11.3.1.3时钟校准软件流程 (333)11.3.2CLKTRIM监测模式 (335)11.3.2.1时钟监测原理 (335)11.3.2.2时钟监测硬件结构 (335)11.3.2.3时钟监测软件流程 (335)11.4CLKTRIM寄存器描述 (338)11.4.1配置寄存器(CLKTRIM_CR) (339)11.4.2参考计数器初值配置寄存器(CLKTRIM_REFCON) (341)11.4.3参考计数器值寄存器(CLKTRIM_REFCNT) (341)11.4.4校准计数器值寄存器(CLKTRIM_CALCNT) (342)11.4.5中断标志位寄存器(CLKTRIM_IFR) (343)11.4.6中断标志位清除寄存器(CLKTRIM_ICLR) (344)11.4.7校准计数器溢出值配置寄存器(CLKTRIM_CALCON) (345)12硬件除法器模块(HDIV) (346)12.1HDIV 简介 (346)12.2HDIV主要特性 (346)12.3HDIV功能描述 (347)12.3.1HDIV操作流程 (347)12.4HDIV寄存器描述 (348)12.4.1被除数寄存器(HDIV_DIVIDEND) (348)12.4.2除数寄存器(HDIV_DIVISOR) (349)12.4.3商寄存器(HDIV_QUOTIENT) (349)12.4.4余数寄存器(HDIV_REMAINDER) (350)12.4.5符号寄存器(HDIV_SIGN) (350)12.4.6状态寄存器(HDIV_STAT) (351)13FLASH控制器(FLASH) (352)13.1概述 (352)13.2FLASH容量划分 (352)13.3功能描述 (353)13.3.1页擦除(Sector Erase) (353)13.3.3写操作(Program) (355)13.3.4读操作(Read) (357)13.4擦写时间 (358)13.5读等待周期 (360)13.6擦写保护 (360)13.6.1擦写保护位 (360)13.6.2PC地址擦写保护 (360)13.7寄存器写保护 (361)13.8寄存器 (362)13.8.1TNVS参数寄存器(FLASH_TNVS) (362)13.8.2TPGS参数寄存器(FLASH_TPGS) (363)13.8.3TPROG参数寄存器(FLASH_TPROG) (363)13.8.4TSERASE寄存器(FLASH_TSERASE) (364)13.8.5TMERASE参数寄存器(FLASH_TMERASE) (364)13.8.6TPRCV参数寄存器(FLASH_TPRCV) (365)13.8.7TSRCV参数寄存器(FLASH_TSRCV) (365)13.8.8TMRCV参数寄存器(FLASH_TMRCV) (366)13.8.9CR寄存器(FLASH_CR) (367)13.8.10IFR寄存器(FLASH_IFR) (368)13.8.11ICLR寄存器(FLASH_ICLR) (368)13.8.12BYPASS寄存器(FLASH_BYPASS) (369)13.8.13SLOCK寄存器(FLASH_SLOCK) (369)14RAM控制器(RAM) (370)14.1概述 (370)14.2功能描述 (370)14.2.1RAM地址范围 (370)14.2.2读写位宽 (371)14.2.3奇偶校验 (371)14.3寄存器 (372)14.3.1控制寄存器(RAM_CR) (372)14.3.2奇偶校验出错地址寄存器(RAM_ERRADDR) (373)14.3.3出错中断标志寄存器(RAM_IFR) (373)14.3.4出错中断标志清除寄存器(RAM_ICLR) (374)15DMA控制器(DMAC) (375)15.1概述 (375)15.2功能框图 (377)15.3基本功能 (380)15.3.1软件-块(Block)传输 (380)15.3.2软件-突发(Burst)传输 (383)15.3.3硬件-块(Block)传输 (385)15.3.4硬件-突发(Burst)传输 (386)15.4寄存器 (388)15.4.1DMAC_CONF (389)15.4.2DMAC_CONFA0、DMAC_CONFA1 (390)15.4.3DMAC_CONFB0、DMAC_CONFB1 (392)15.4.4DMAC_SRCADR0、DMAC_SRCADR1 (394)15.4.5DMAC_DSTADR0、DMAC_DSTADR1 (395)16通用定时器(TIM0/1/2/3) (396)16.1通用定时器简介 (396)16.1.1基本特性(TIM0/1/2) (396)16.1.2基本特性(TIM3) (398)16.2Timer 功能描述 (399)16.2.1定时计数器 (399)16.2.2定时器预除频 (399)16.2.3模式0 计数定时器功能 (399)16.2.3.1功能框图 (400)16.2.3.2计数波形 (401)16.2.3.3计数功能 (402)16.2.3.4定时功能 (402)16.2.3.5时序图 (402)16.2.3.6Buzzer功能 (403)16.2.3.7设置示例 (404)16.2.4模式1 脉宽测量PWC (405)16.2.4.1PWC功能框图 (405)16.2.4.2PWC波形测量时序图 (406)16.2.4.3PWC单次触发模式 (408)16.2.4.1设置示例 (408)16.2.5模式2/3比较捕获模式 (410)16.2.5.1计数器 (410)16.2.5.2计数器波形 (411)16.2.5.3重复计数 (414)16.2.5.4数据缓存 (415)16.2.5.5比较输出OCREF (419)16.2.5.6独立PWM输出 (422)16.2.5.7互补PWM输出 (423)16.2.5.8有死区的PWM输出 (424)16.2.5.9单脉冲输出 (425)16.2.5.10比较中断 (426)16.2.5.11捕获输入 (427)16.2.5.12设置示例 (430)16.2.6模式2/3从模式 (433)16.2.6.1门控计数 (433)16.2.6.2触发功能 (434)16.2.6.3复位计数 (434)16.2.7正交编码计数功能 (435)16.2.8Timer触发ADC (437)16.2.9刹车控制 (438)16.2.10Timer 互联 (438)16.2.11GATE输入互联 (439)16.2.12ETR输入互联 (439)16.2.13CHx捕获输入互联 (440)16.2.14DMA (440)16.2.14.1设置示例 (442)16.3Timer 寄存器描述 (443)16.4模式0定时器寄存器描述 (444)16.4.116位模式重载寄存器(TIMx_ARR) (444)16.4.216位模式计数寄存器(TIMx_CNT) (444)16.4.332位模式计数寄存器(TIMx_CNT32) (445)16.4.4控制寄存器(TIMx_M0CR) (446)16.4.5中断标志寄存器(TIMx_IFR) (448)16.4.6中断标志清除寄存器(TIMx_ICLR) (448)16.4.7死区时间寄存器(TIMx_DTR) (449)16.5脉冲宽度测量PWC寄存器描述 (450)16.5.116位模式计数寄存器(TIMx_CNT) (450)16.5.2控制寄存器(TIMx_M1CR) (451)16.5.3中断标志寄存器(TIMx_IFR) (453)16.5.4中断标志清除寄存器(TIMx_ICLR) (453)16.5.5主从模式控制寄存器(TIMx_MSCR) (454)16.5.6输出控制滤波(TIMx_FLTR) (455)16.5.7控制寄存器(TIMx_CR0) (456)16.5.8比较捕获寄存(TIMx_CCR0A ) (456)16.6模式2,3寄存器描述 (457)16.6.116位模式重载寄存器(TIMx_ARR) (457)16.6.216位模式计数寄存器(TIMx_CNT) (457)16.6.3控制寄存器(TIMx_M23CR) (458)16.6.4中断标志寄存器(TIMx_IFR) (461)16.6.5中断标志清除寄存器(TIMx_ICLR) (463)16.6.6主从模式控制寄存器(TIMx_MSCR) (464)16.6.7输出控制/输入滤波(TIMx_FLTR) (466)16.6.8ADC触发控制寄存器(TIMx_ADTR) (469)16.6.9通道0控制寄存器(TIMx_CRCH0) (470)16.6.10通道1/2控制寄存器(TIM3_CRCH1/2)(仅TIM3存在) (472)16.6.11死区时间寄存器(TIMx_DTR) (474)16.6.12重复周期设置值(TIMx_RCR) (476)16.6.13通道0比较捕获寄存器(TIMx_CCR0A/B) (477)16.6.14通道1/2比较捕获寄存器(TIM3_CCR1/2 A/B) (仅TIM3存在) (478)17低功耗定时器(LPTIM) (479)17.1LPTimer 简介 (479)17.2LPTimer 功能描述 (480)17.2.1计数功能 (481)17.2.2定时功能 (481)17.3LPTimer 互连 (482)17.3.1GATE互联 (482)17.3.2EXT互联 (482)17.3.3Toggle输出互联 (483)17.4LPTimer 寄存器描述 (484)17.4.1计数器计数值寄存器(LPTIM_CNT) (485)17.4.2重载寄存器(LPTIM_ARR) (485)17.4.3控制寄存器(LPTIM_CR) (486)17.4.4中断标志寄存器(LPTIM_IFR) (487)17.4.5中断标志清除寄存器(LPTIM_ICLR) (487)18可编程计数阵列(PCA) (488)18.1PCA简介 (488)18.2PCA功能描述 (489)18.2.1PCA定时/计数器 (490)18.2.1.116位自由计数模式 (491)18.2.1.216位重载计数模式 (491)18.2.2PCA捕获功能 (493)18.2.3PCA比较功能 (495)18.2.3.1比较翻转输出模式 (495)18.2.3.2PCA 16位PWM功能 (497)18.2.3.3PCA模块4的WDT功能 (498)18.2.3.4PCA 8位PWM功能 (499)18.3PCA模块与其他模块互连及控制 (502)18.4PCA寄存器描述 (503)18.4.1控制寄存器(PCA_CCON) (504)18.4.2模式寄存器(PCA_CMOD) (505)18.4.3计数寄存器(PCA_CNT) (506)18.4.4中断清除寄存器(PCA_ICLR) (506)18.4.5比较捕获模式寄存器(PCA_CCAPM0~4) (507)18.4.6比较捕获数据寄存器高8位(PCA_CCAP0~4H) (508)18.4.7比较捕获数据寄存器低8位(PCA_CCAP0~4L) (508)18.4.8比较捕获16位寄存器(PCA_CCAP0~4) (509)18.4.9比较高速输出标志寄存器(PCA_CCAPO) (509)18.4.10周期寄存器(PCA_CARR) (510)18.4.11增强PWM控制(PCA_EPWM) (510)19高级定时器(TIM4/5/6) (511)19.1Advanced Timer 简介 (511)19.2Advanced Timer 功能描述 (513)19.2.1基本动作 (513)19.2.1.1基本波形模式 (513)19.2.1.2比较输出 (514)19.2.1.3捕获输入 (515)19.2.2时钟源选择 (515)19.2.3计数方向 (516)19.2.3.1锯齿波计数方向 (516)19.2.3.2三角波计数方向 (516)19.2.4数字滤波 (516)19.2.5软件同步 (517)19.2.5.1软件同步启动 (517)19.2.5.2软件同步停止 (518)19.2.5.3软件同步清零 (518)19.2.6硬件同步 (518)19.2.6.1硬件同步启动 (518)19.2.6.2硬件同步停止 (518)19.2.6.3硬件同步清零 (519)19.2.6.4硬件同步捕获输入 (519)19.2.6.5硬件同步计数 (520)19.2.7缓存功能 (521)19.2.7.1缓存传送时间点 (522)19.2.7.2通用周期基准值缓存传送时间点 (522)19.2.7.3通用比较基准值缓存传送时间点 (522)19.2.7.4捕获输入值缓存传送时间点 (522)19.2.7.5清零动作时缓存传送 (522)19.2.8通用PWM输出 (523)19.2.8.1PWM展频输出 (523)19.2.8.2独立PWM输出 (523)19.2.8.3互补PWM输出 (524)19.2.8.4多相PWM输出 (526)19.2.9正交编码计数 (528)19.2.9.1位置计数模式 (528)19.2.9.2公转模式 (531)19.2.10周期间隔响应 (534)19.2.11保护机制 (534)19.2.12中断说明 (535)19.2.12.1计数比较匹配中断 (535)19.2.12.2计数周期匹配中断 (535)19.2.12.3死区时间错误中断 (535)19.2.13DMA (536)19.2.14刹车保护 (536)19.2.14.1端口刹车与软件刹车 (536)19.2.14.2低功耗模式自动刹车 (537)19.2.14.3输出电平同高同低刹车 (537)19.2.14.4VC 刹车 (537)19.2.15内部互连 (539)19.2.15.1中断触发输出 (539)19.2.15.2AOS 触发 (540)19.2.15.3端口触发TRIGA-TRIGD (541)19.2.15.4比较输出VC 与Advanced Timer 互连 (541)19.3寄存器描述 (542)19.3.1通用计数基准值寄存器(TIMx_CNTER) (544)19.3.2通用周期基准值寄存器(TIMx_PERAR) (544)19.3.3通用周期缓存寄存器(TIMx_PERBR) (545)19.3.4通用比较基准值寄存器(TIMx_GCMAR-GCMDR) (545)19.3.5专用比较基准值寄存器(TIMx_SCMAR-SCMBR) (546)19.3.6死区时间基准值寄存器(TIMx_DTUAR- DTDAR) (546)19.3.7通用控制寄存器(TIMx_GCONR) (547)19.3.8中断控制寄存器(TIMx_ICONR) (549)19.3.9端口控制寄存器(TIMx_PCONR) (551)19.3.10缓存控制寄存器(TIMx_BCONR) (554)19.3.11死区控制寄存器(TIMx_DCONR) (555)19.3.12滤波控制寄存器(TIMx_FCONR) (556)19.3.13有效周期寄存器(TIMx_VPERR) (558)19.3.14状态标志寄存器(TIMx_STFLR) (559)19.3.15硬件启动事件选择寄存器(TIMx_HSTAR) (561)19.3.16硬件停止事件选择寄存器(TIMx_HSTPR) (563)19.3.17硬件清零事件选择寄存器(TIMx_HCELR) (565)19.3.18硬件捕获A事件选择寄存器(TIMx_HCPAR) (567)19.3.19硬件捕获B事件选择寄存器(TIMx_HCPBR) (569)19.3.20硬件递加事件选择寄存器(TIMx_HCUPR) (571)19.3.21硬件递减事件选择寄存器(TIMx_HCDOR) (573)19.3.22软件同步启动寄存器(TIMx_SSTAR) (575)19.3.23软件同步停止寄存器(TIMx_SSTPR) (576)19.3.24软件同步清零寄存器(TIMx_SCLRR) (577)19.3.25中断标志寄存器(TIMx_IFR) (578)19.3.26中断标志清除寄存器(TIMx_ICLR) (580)19.3.27展频及中断触发选择(TIMx_CR) (581)19.3.28AOS选择控制寄存器(TIMx_AOSSR) (583)19.3.29AOS选择控制寄存器标志清除(TIMx_AOSCL) (584)19.3.30端口刹车控制寄存器(TIMx_PTBKS) (585)19.3.31端口触发控制寄存器(TIMx_TTRIG) (586)19.3.32AOS 触发控制寄存器(TIMx_ITRIG) (587)19.3.33端口刹车极性控制寄存器(TIMx_PTBKP) (588)20实时时钟(RTC) (589)20.1实时时钟简介 (589)20.2实时时钟功能描述 (591)20.2.1上电设定 (591)20.2.2RTC 计数开始设定 (591)20.2.3系统低功耗模式切换 (591)20.2.4读出计数寄存器 (592)20.2.5写入计数寄存器 (592)20.2.6闹钟设定 (593)20.2.71Hz 输出 (593)20.2.8时钟误差补偿 (594)20.3RTC 中断 (596)20.3.1RTC 闹钟中断 (596)20.3.2RTC 周期中断 (596)20.4RTC 寄存器描述 (597)20.4.1控制寄存器0(RTC_CR0) (598)20.4.2控制寄存器1(RTC_CR1) (600)20.4.3秒计数寄存器(RTC_SEC) (602)20.4.4分计数寄存器(RTC_MIN) (602)20.4.5时计数寄存器(RTC_HOUR) (603)20.4.6日计数寄存器(RTC_DAY) (605)20.4.7周计数寄存器(RTC_WEEK) (606)20.4.8月计数寄存器(RTC_MON) (607)20.4.9年计数寄存器(RTC_YEAR) (607)20.4.10分闹钟寄存器(RTC_ALMMIN) (608)20.4.11时闹钟寄存器(RTC_ALMHOUR) (608)20.4.12周闹钟寄存器(RTC_ALMWEEK) (609)20.4.13时钟误差补偿寄存器(RTC_COMPEN) (610)21看门狗定时器(WDT) (612)21.1WDT 简介 (612)21.2WDT 功能描述 (613)21.2.1WDT溢出后产生中断 (613)21.2.2WDT溢出后产生复位 (613)21.3WDT 寄存器描述 (615)21.3.1WDT 清除控制寄存器(WDT_RST) (615)21.3.2WDT_CON 寄存器 (616)22脉冲计数器(PCNT) (617)22.1脉冲计数器简介 (617)22.2脉冲计数器主要特性 (617)22.3脉冲计数器功能描述 (618)22.3.1整体框图 (618)22.3.2信号说明 (618)22.3.3计数模式 (619)22.3.3.1单通道脉冲计数模式(Single Mode) (619)22.3.3.2双通道非交脉冲计数模式(Dual Mode) (620)22.3.3.3双通道正交脉冲记数模式(Quad Mode) (621)22.3.4脉冲宽度滤波 (623)22.3.5超时 (623)22.4PCNT 寄存器描述 (624)22.4.1PCNT 启动寄存器(PCNT_RUN) (625)22.4.2PCNT 控制寄存器(PCNT_CTRL) (626)22.4.3PCNT 滤波控制寄存器(PCNT_FLT) (627)22.4.4PCNT 超时控制寄存器(PCNT_TOCR) (628)22.4.5PCNT 命令寄存器(PCNT_CMD) (629)22.4.6PCNT 状态寄存器1(PCNT_SR1) (630)22.4.7PCNT 计数寄存器(PCNT_CNT) (630)22.4.8PCNT 计数溢出寄存器(PCNT_TOP) (631)22.4.9PCNT 计数溢出缓存寄存器(PCNT_BUF) (631)22.4.10PCNT 中断标识寄存器(PCNT_IFR) (632)22.4.11PCNT 中断清除寄存器(PCNT_ICR) (633)22.4.12PCNT 中断使能寄存器(PCNT_IEN) (633)22.4.13PCNT 同步状态寄存器(PCNT_SR2) (634)23通用同步异步收发器(UART) (635)23.1概述 (635)23.2功能框图 (636)23.3工作模式 (637)23.3.1Mode0(同步模式,半双工) (637)23.3.1.1发送数据 (637)23.3.1.2接收数据 (637)23.3.2Mode1(异步模式,全双工) (638)23.3.2.1发送数据 (638)23.3.2.2接收数据 (639)23.3.3Mode2(异步模式,全双工) (639)23.3.3.1发送数据 (639)23.3.3.2接收数据 (640)23.3.4Mode3(异步模式,全双工) (640)23.3.4.1发送数据 (640)23.3.4.2接收数据 (641)23.4波特率编程 (642)23.4.1Mode0 (642)23.4.2Mode1/3 (642)23.4.3Mode2 (646)23.5传输数据结构 (647)23.6帧错误检测 (647)23.7多机通讯 (648)23.7.1自动地址识别 (648)23.7.2给定地址 (648)23.7.3广播地址 (649)23.7.4举例 (649)23.8DMAC硬件握手 (649)23.9硬件流控 (650)23.9.1nRTS流控 (650)23.9.2CTS流控 (650)23.10收发端缓存 (652)23.10.1接收缓存 (652)23.10.2发送缓存 (652)23.11寄存器 (654)23.11.1数据寄存器(UARTx_SBUF) (654)23.11.2控制寄存器(UARTx_SCON) (655)23.11.3地址寄存器(UARTx_SADDR) (657)23.11.4地址掩码寄存器(UARTx_SADEN) (657)23.11.5标志位寄存器(UARTx_ISR) (658)23.11.6标志位清除寄存器(UARTx_ICR) (659)23.11.7波特率寄存器(UARTx_SCNT) (659)24低功耗同步异步收发器(LPUART) (660)24.1概述 (660)24.2功能框图 (661)24.3配置时钟和传输时钟 (661)24.3.1配置时钟 (661)24.3.2传输时钟 (661)24.4工作模式 (662)24.4.1Mode0(同步模式,半双工) (662)24.4.1.1发送数据 (662)24.4.1.2接收数据 (662)24.4.2Mode1(异步模式,全双工) (663)24.4.2.1发送数据 (663)24.4.2.2接收数据 (663)24.4.3Mode2(异步模式,全双工) (664)24.4.3.1发送数据 (664)24.4.3.2接收数据 (664)24.4.4Mode3(异步模式,全双工) (665)24.4.4.1发送数据 (665)24.4.4.2接收数据 (665)24.5.1Mode0 (667)24.5.2Mode1/3 (667)24.5.3Mode2 (667)24.6传输数据结构 (671)24.7帧错误检测 (672)24.8多机通讯 (672)24.8.1自动地址识别 (672)24.8.2给定地址 (673)24.8.3广播地址 (673)24.8.4举例 (673)24.9DMAC硬件握手 (674)24.10硬件流控 (674)24.10.1nRTS流控 (675)24.10.2CTS流控 (676)24.11收发端缓存 (677)24.11.1接收缓存 (677)24.11.2发送缓存 (678)24.12寄存器 (679)24.12.1数据寄存器(LPUARTx_SBUF) (679)24.12.2控制寄存器(LPUARTx_SCON) (680)24.12.3地址寄存器(LPUARTx_SADDR) (682)24.12.4地址掩码寄存器(LPUARTx_SADEN) (682)24.12.5标志位寄存器(LPUARTx_ISR) (683)24.12.6标志位清除寄存器(LPUARTx_ICR) (684)24.12.7波特率寄存器(LPUARTx_SCNT) (684)25循环冗余校验(CRC) (685)25.1概述 (685)25.2功能框图 (685)25.3功能描述 (685)25.4寄存器 (686)25.4.1控制寄存器(CRC_CR) (686)25.4.2结果寄存器(CRC_RESULT) (687)25.4.3数据寄存器(CRC_DA TA) (687)25.5软件基本操作 (689)25.5.1CRC16编码模式 (689)25.5.2CRC16检验模式 (689)25.5.3CRC32编码模式 (689)25.5.4CRC32检验模式 (690)26真随机数发生器(TRNG) (691)26.1概述 (691)26.2功能框图 (691)26.4寄存器 (692)26.4.1控制寄存器(TRNG_CR) (692)26.4.2模式寄存器(TRNG_MODE) (693)26.4.3数据寄存器0(TRNG_DA TA0) (694)26.4.4数据寄存器1(TRNG_DA TA1) (694)26.5软件基本操作 (695)26.5.1生成64bits真随机数的操作流程(上电第一次) (695)26.5.2生成64bits真随机数的操作流程(非上电第一次生成) (696)27高级加密标准模块(AES) (697)27.1功能定义 (697)27.1.1AES算法简述 (697)27.1.2AES模块功能描述 (699)27.2模块寄存器说明 (700)27.2.1控制寄存器(AES_CR) (700)27.2.2数据寄存器(AES_Data) (701)27.2.3密钥寄存器(AES_Key) (702)27.3异常机制 (703)27.4本模块操作说明 (704)27.4.1IP操作的共同点 (704)27.4.2加密操作流程 (704)27.4.3解密操作流程 (704)27.4.4数据示例 (705)27.5运行时间说明 (706)28液晶控制器(LCD) (707)28.1LCD简介 (707)28.2LCD主要特性 (707)28.3LCD框图 (708)28.4LCD驱动波形 (709)28.4.1静态驱动波形 (709)28.4.21/2Duty 1/2Bias驱动波形 (710)28.4.31/2Duty 1/3Bias驱动波形 (711)28.4.41/3Duty 1/2Bias驱动波形 (712)28.4.51/3Buty 1/3Bias驱动波形 (713)28.4.61/4Duty 1/2Bias驱动波形 (714)28.4.71/4Duty 1/3Bias驱动波形 (715)28.4.81/6Duty 1/3Bias驱动波形 (716)28.4.91/8Duty 1/3Bias驱动波形 (717)28.5LCD Bias产生电路 (718)28.5.1内部电阻模式 (718)28.5.2外部电容模式 (719)28.5.3外部电阻模式 (720)28.7中断 (721)28.8LCD 显示模式 (721)28.8.1LCD 显示模式1 (MODE = 1) (722)28.8.2LCD 显示模式0 (MODE = 0) (723)28.9LCD 寄存器 (724)28.9.1配置寄存器0(LCD_CR0) (725)28.9.2配置寄存器1(LCD_CR1) (727)28.9.3中断清除寄存器(LCD_INTCLR) (728)28.9.4输出配置寄存器0(LCD_POEN0) (728)28.9.5输出配置寄存器1(LCD_POEN1) (729)28.9.6LCD_RAM0~7 (731)28.9.7LCD_RAM8~F (732)29模数转换器(ADC) (733)29.1模块简介 (733)29.2ADC框图 (734)29.3转换时序及转换速度 (735)29.4单次转换模式 (736)29.5扫描转换模式 (738)29.5.1顺序扫描转换模式 (738)29.5.2插队扫描转换模式 (740)29.5.3扫描转换触发DMA读取 (744)29.6连续转换累加模式 (745)29.7ADC转换外部触发源 (748)29.8ADC转换结果比较 (749)29.9ADC中断 (750)29.10使用温度传感器测量环境温度 (751)29.11ADC 模块寄存器 (753)29.11.1ADC 基本配置寄存器0(ADC_CR0) (755)29.11.2ADC 基本配置寄存器1(ADC_CR1) (757)29.11.3ADC 顺序扫描转换通道配置寄存器0(ADC_SQR0) (759)29.11.4ADC 顺序扫描转换通道配置寄存器1(ADC_SQR1) (760)29.11.5ADC 顺序扫描转换通道配置寄存器2(ADC_SQR2) (761)29.11.6ADC 插队扫描转换通道配置寄存器(ADC_JQR) (762)29.11.7ADC 顺序扫描转换通道x转换结果(ADC_SqrResult0 - 15) (762)29.11.8ADC 插队扫描转换通道x转换结果(ADC_JqrResult0 - 3) (763)29.11.9ADC 转换结果(ADC_Result) (763)29.11.10A DC 转换结果累加值(ADC_ResultAcc) (764)29.11.11ADC 比较上阈值(ADC_HT) (764)29.11.12A DC 比较下阈值(ADC_LT) (765)29.11.13A DC 中断标志寄存器(ADC_IFR) (766)29.11.14A DC 中断清除寄存器(ADC_ICR) (767)29.11.15A DC 单次转换或顺序扫描转换外部中断触发源配置寄存器(ADC_ExtTrigger0) (768)29.11.16A DC 插队扫描转换外部中断触发源配置寄存器(ADC_ExtTrigger1) (770)29.11.17A DC 单次转换启动控制寄存器(ADC_SglStart) (772)29.11.18A DC 顺序扫描转换启动控制寄存器(ADC_SqrStart) (772)29.11.19A DC 插队扫描转换启动控制寄存器(ADC_JqrStart) (773)30模拟比较器(VC) (774)30.1模拟电压比较器VC 简介 (774)30.2电压比较器框架图 (775)30.3建立/响应时间 (775)30.4滤波时间 (776)30.5迟滞功能 (776)30.6VC 寄存器 (777)30.6.1VC 配置寄存器(VC_CR) (778)30.6.2VC0 配置寄存器(VC0_CR) (780)30.6.3VC1 配置寄存器(VC1_CR) (782)30.6.4VC0 输出配置寄存器(VC0_OUT_CFG) (784)30.6.5VC1 输出配置寄存器(VC1_ OUT_CFG) (786)30.6.6VC 中断寄存器(VC_IFR) (788)31低电压检测器(LVD) (789)31.1LVD 简介 (789)31.2LVD 框图 (789)31.3迟滞功能 (790)31.4数字滤波 (790)31.5配置示例 (791)31.5.1LVD配置为低电压复位 (791)31.5.2LVD配置为电压变化中断 (791)31.6LVD寄存器 (792)31.6.1LVD 配置寄存器(LVD_CR) (792)31.6.2LVD 中断寄存器(LVD_IFR) (794)32运算放大器(OPA) (795)32.1OPA 特性 (795)32.2OPA 功能描述 (796)32.2.1PGA功能 (796)32.2.2运放功能 (796)32.3配置 (797)32.3.1PGA增益 (797)32.3.2单位增益PGA (798)32.3.3正向输入PGA (798)32.3.4反向输入PGA (799)32.3.5级联反向输入PGA (800)32.3.6级联正向输入PGA (801)32.3.7两运放差分PGA (802)32.4OPA寄存器 (804)32.4.1OPA 配置寄存器(OPA_CR0) (805)32.4.2OPA 配置寄存器(OPA_CR1) (807)32.4.3OPA 配置寄存器(OPA_CR2) (809)33模拟其它寄存器 (811)33.1BGR 配置寄存器(BGR_CR) (811)34SWD 调试接口 (812)34.1SWD 调试附加功能 (812)34.2ARM® 参考文档 (813)34.3调试端口引脚 (814)34.3.1SWD 端口引脚 (814)34.3.2SW-DP 引脚分配 (814)34.3.3SWD 引脚上的内部上拉 (814)34.4SWD 端口 (815)34.4.1SWD协议简介 (815)34.4.2SWD 协议序列 (815)34.4.3SW-DP 状态机(复位、空闲状态、ID 代码) (816)34.4.4DP 和AP 读/写访问 (816)34.4.5SW-DP 寄存器 (817)34.4.6SW-AP 寄存器 (818)34.5内核调试 (819)34.6BPU(断点单元) (819)34.6.1BPU 功能 (819)34.7DWT(数据观察点) (820)34.7.1DWT 功能 (820)34.7.2DWT 程序计数器采样寄存器 (820)34.8MCU 调试组件(DBG) (821)34.8.1对低功耗模式的调试支持 (821)34.8.2对定时器、看门狗的调试支持 (821)34.9调试模式模块工作状态控制(DEBUG_ACTIVE) (822)35电气特性 (824)35.1测试条件 (824)35.1.1最小和最大数值 (824)35.1.2典型数值 (824)35.1.3供电方案 (825)35.2绝对最大额定值 (826)35.3工作条件 (828)35.3.1通用工作条件 (828)35.3.2上电和掉电时的工作条件 (828)35.3.3内嵌复位和LVD模块特性 (829)35.3.4内置的参考电压 (831)35.3.6从低功耗模式唤醒的时间 (835)35.3.7外部时钟源特性 (836)35.3.7.1外部输入高速时钟 (836)35.3.7.2外部输入低速时钟 (836)35.3.7.3高速外部时钟XTH (837)35.3.7.4低速外部时钟XTL (838)35.3.8内部时钟源特性 (840)35.3.8.1内部RCH振荡器 (840)35.3.8.2内部RCL振荡器 (840)35.3.9PLL特性 (841)35.3.10存储器特性 (841)35.3.11EFT特性 (841)35.3.12ESD特性 (842)35.3.13I/O端口特性 (842)35.3.13.1输出特性——端口 (842)35.3.13.2输入特性——端口PA,PB,PC,PD, RESET (843)35.3.13.3端口外部输入采样要求——Timer Gate/Timer Clock (844)35.3.13.4端口漏电特性——PA,PB,PC,PD (844)35.3.14RESETB引脚特性 (845)35.3.15ADC特性 (845)35.3.16VC特性 (848)35.3.17OPA特性 (848)35.3.18LCD控制器 (850)36唯一设备ID 寄存器(80 位) (851)37封装尺寸 (852)38附录A SysTick 定时器 (857)38.1SysTick 定时器简介 (857)38.2设置SysTick (857)38.3SysTick 寄存器 (858)38.3.1SysTick 控制和状态寄存器(CTRL) (858)38.3.2SysTick 重载寄存器(LOAD) (858)38.3.3SysTick 当前值寄存器(V AL) (858)38.3.4SysTick 校准值寄存器(CALIB) (859)39附录B 文档约定 (860)39.1寄存器相关缩写词列表 (860)39.2词汇表 (860)版本记录& 联系方式 (861)。

亿光直插光耦ELT3081

亿光直插光耦ELT30814PIN DIP ZERO-CROSS TRIAC DRIVER PHOTOCOUPLER ELT304X, ELT306X, ELT308X SeriesFeatures:Peak breakdown voltage -400V: ELT304X -600V: ELT306X -800V: ELT308XHigh isolation voltage between input and output (Viso=5000 V rms )Zero voltage crossingPb free and RoHS compliant.UL and cUL approved(No. E214129) VDE approved (No.40028391) SEMKO approved NEMKO approved DEMKO approved FIMKO approvedDescriptionThe ELT304X, ELT306X and ELT308X series of devices each consist of a GaAs infrared emitting diode optically coupled to a monolithic silicon zero voltage crossing photo triac.They are designed for use with a discrete power triac in the interface of logic systems to equipment powered from 110 to 380 VAC lines,such as solid-state relays, industrial controls, motors, solenoids and consumer appliances.Applications●Solenoid/valve controls ●Light controls●Static power switch ●AC motor drivers ●E.M. contactors●Temperature controls ●AC Motor startersSchematicPin Configuration 1. Anode 2. Cathode 3. Terminal 4. TerminalAbsolute Maximum Ratings (Ta=25 )Parameter Symbol Rating Unit Input Forward current I F60mA Reverse voltage V R6VPower dissipation P D100mWOutputOff-state OutputTerminal Voltage ELT304XV DRM400V ELT306X600ELT308X800Peak Repetitive Surge Current I TSM1APower dissipation P C300mW Total power dissipation P TOT330mW Isolation voltage*1V ISO5000Vrms Operating temperature T OPR-55 to 100 Storage temperature T STG-55 to 125 Soldering Temperature*2T SOL260 Notes:*1AC for 1 minute, R.H.= 40 ~ 60% R.H. In this test, pins 1& 2 are shorted together, and pins3 & 4are shorted together. *2 For 10 secondsElectro-Optical Characteristics (Ta=25 unless specified otherwise)InputParameter Symbol Min.Typ.*Max.Unit Condition Forward Voltage V F-- 1.5V I F=30mA Reverse Leakage current I R--10µA V R=6V OutputParameter Symbol Min.Typ.*Max.Unit ConditionPeak Blocking Current ELT304XI DRM--100nA V DRM = Rated V DRMI F=0mAELT306XELT308X500Peak On-state Voltage V TM--3V I TM=100mA peak, I F=Rated I FTCritical Rate of Rise off-state Voltage ELT304XELT306Xdv/dt1000--V/µsV PEAK=Rated V DRM,I F=0 (Fig. 10)ELT308X600--Inhibit Voltage (MT1-MT2voltage above which devicewill not trigger)V INH--20V I F= Rated I FTLeakage in lnhibited State I DRM2--500µA I F= Rated I FT,V DRM=Rated V DRM, off stateTransfer CharacteristicsParameter Symbol Min.Typ.*Max.Unit ConditionLED Trigger Current ELT3041ELT3061ELT3081I FT--15mA Main terminal Voltage=3V ELT3042ELT3062ELT3082--10ELT3043ELT3063ELT3083--5Holding Current I H-280-µA * Typical values at T a= 25°CTypical Electro-Optical Characteristics CurvesFigure 10. Static dv/dt Test Circuit & WaveformMeasurement MethodThe high voltage pulse is set to the required V PEAK value and applied to the D.U.T. output side through the RC circuit above. LED current is not applied. The waveform V T is monitored using a x100 scope probe. By varying R TEST , the dv/dt (slope) is increased, until the D.U.T. is observed to trigger (waveform collapses). The dv/dt is then decreased until the D.U.T. stops triggering. At this point,τRC is recorded and the dv/dt calculated.For example, V PEAK = 600V for ELT306X series. The dv/dt value is calculated as follows:V PEAKApplied V T WaveformτRC0.632 x V PEAK0.63 x 600τRCdv/dt = = 378τRC0.632 x V PEAK τRCdv/dt =50 ?10 k ?D.U.T.R TESTHigh Voltage Pulse SourceC TEST V TA KT1T2Zero Crossing CircuitOrder InformationPart NumberELT304X(Y)(Z)-Vor ELT306X(Y)(Z)-Vor ELT308X(Y)(Z)-VNoteNoteX = Part No. (1, 2, or 3)Y = Lead form option (S, S1, M or none)Z = Tape and reel option (TA, TB, TU,TD or none).V=VDE safety approved optionOption Description Packing quantity None Standard DIP-4100units per tube M Wide lead bend(0.4 inch spacing)100units per tube S(TA)Surface mount lead form+ TA tape & reel option1000units per reel S(TB)Surface mount lead form+ TB tape & reel option1000units per reel S1(TA)Surface mount lead form (low profile) + TA tape & reel option1000 units per reel S1(TB)Surface mount lead form (low profile) + TB tape & reel option1000 units per reel S (TU)Surface mount lead form + TU tape & reel option1500units per reel S(TD)Surface mount lead form + TD tape & reel option1500units per reelS1(TU)Surface mount lead form (low profile) + TU tape & reel option1500units per reel S1(TD)Surface mount lead form (low profile) + TD tape & reel option1500 units per reelPackage Dimension(Dimensions in mm) Standard DIP TypeOption M TypeOption S TypeOption S1 TypeRecommended pad layout for surface mount leadformDevice MarkingNotes EL denotes EverlightT3083denotes Device Number Y denotes 1 digit Year code WWdenotes 2 digit Week code Vdenotes VDE optionT3083EL YWW VTape dimensionsDimension No.Po P1P2t W K Dimension(mm) 4.0±0.112.0±0.1 2.0±0.10.35±0.116.0±0.3 4.75±0.1Tape dimensionsDimension No.A B C D EF Dimension(mm)16.00±0.37.5±0.1 1.75±0.18.0±0.1 2.0±0.1 4.0±0.1Dimension No.G H I J K L Dimension(mm)1.55±0.0510.4±0.10.4±0.054.60±0.15.1±0.11.55±0.05Precautions for Use1. Soldering Condition1.1 (A) Maximum Body Case Temperature Profile for evaluation of Reflow ProfileNote: Reference: IPC/JEDEC J-STD-020DPreheatTemperature min (T smin) 150 °CTemperature max (T smax)200°CTime (T smin to T smax) (t s)60-120 secondsAverage ramp-up rate (T smax to T p) 3 °C/second maxOtherLiquidus Temperature (T L)217 °CTime above Liquidus Temperature (t L)60-100 secPeak Temperature (T P) 260°CTime within 5 °C of Actual Peak Temperature: T P-5°C 30 sRamp-Down Rate from Peak Temperature 6°C /second max.Time 25°C to peak temperature8 minutes max.Reflow times 3 times.DISCLAIMER1.Above specification may be changed without notice. EVERLIGHT will reserve authority on material change for abovespecification.2.When using this product, please observe the absolute maximum ratings and the instructions for using outlined in thesespecification sheets. EVERLIGHT assumes no responsibility for any damage resulting from use of the product which does not comply with the absolute maximum ratings and the instructions included in these specification sheets.3.These specification sheets include materials protected under copyright of EVERLIGHT corporation. Please don’treproduce or cause anyone to reproduce them without EVERLIGHT’s consent.。

HY27UA081G1M资料