用于PCI-Express 3.0协议分析仪的仿真设计验证工具

pcie协议分析仪

竭诚为您提供优质文档/双击可除pcie协议分析仪篇一:网络协议分析仪使用淮海工学院计算机工程学院实验报告书课程名:《tcp/ip与网络互联》题目:实验三网络协议分析仪使用班级:网络122学号:姓名:一、实验目的通过本次实验,熟悉Flukenetworks公司协议分析仪的使用,掌握opV软件的使用,掌握网上数据采集方法,并利用专家系统对其进行分析。

二、实验内容1、把Fluke协议分析仪正确接入网中。

2、在主机上执行opV软件。

3、设置捕获条件进行捕包。

4、利用专家系统对其进行分析。

三、实验步骤与源程序1.把Fluke协议分析仪正确接入网络中并启动;2.打开optiViewbrowser软件;3.进行捕包操作,并利用专家系统对icmp及tcp、udp 数据包进行分析;四、测试数据与实验结果1.首先在两台计算机上进行路由器配置,使用ping命令测试连通性2.、启动opV软件,其界面如图3-1所示。

3、设置过滤器,利用opV捕获Rip数据包,利用专家系统分析Rip数据包。

Rip数据包如图3-2所示。

02表示命令字段,表示响应报文;01表示版本号为1;00000002表示tcp/ip协议;c0a80100表示信宿网络的ip地址192.168.1.0;4.设置过滤器,捕获ip数据包,并启动捕获。

利用opV 捕获ip数据包,利用专家系统分析ip数据包。

46表示版本为0x46;00表示服务类型为0x00;0028表示数据包总长度为40byte;0011表示标识为17;0000表示片偏移为0x0000;0102分别表示生存时间与协议标识为1,2;08bc表示校验和为0x08bbc;3ac0012d表示原地址:58.92.1.45e0000016表示目的地址:224.0.0.22;5.设置过滤器,捕获aRp数据包,并启动捕获。

利用opV捕获aRp数据包,利用专家系统分析aRp数据包。

0010表示硬件类型为1;0800表示协议类型ipv4;0604表示硬件地址,协议地址长度分别为6,4;0001表示操作类型为1,表示aRp请求;c81F660ed462表示发送方硬件地址;c0a8030a表示发送方ip地址192.168.3.10;000000000000表示目的硬件地址;c0a80301表示目的ip地址192.168.3.16.设置过滤器,捕获icmp数据包,并启动捕获。

五款信号完整性仿真分析工具

SI五款信号完整性仿真工具介绍(一)Ansoft公司的仿真工具现在的高速电路设计已经达到GHz的水平,高速PCB设计要求从三维设计理论出发对过孔、封装和布线进行综合设计来解决信号完整性问题。

高速PCB设计要求中国工程师必须具备电磁场的理论基础,必须懂得利用麦克斯韦尔方程来分析PCB设计过程中遇到的电磁场问题。

目前,Ansoft公司的仿真工具能够从三维场求解的角度出发,对PCB设计的信号完整性问题进行动态仿真。

Ansoft的信号完整性工具采用一个仿真可解决全部设计问题:SIwave是一种创新的工具,它尤其适于解决现在高速PCB和复杂IC封装中普遍存在的电源输送和信号完整性问题。

该工具采用基于混合、全波及有限元技术的新颖方法,它允许工程师们特性化同步开关噪声、电源散射和地散射、谐振、反射以及引线条和电源/地平面之间的耦合。

该工具采用一个仿真方案解决整个设计问题,缩短了设计时间。

它可分析复杂的线路设计,该设计由多重、任意形状的电源和接地层,以及任何数量的过孔和信号引线条构成。

仿真结果采用先进的3D图形方式显示,它还可产生等效电路模型,使商业用户能够长期采用全波技术,而不必一定使用专有仿真器。

(二)SPECCTRAQuestCadence的工具采用Sun的电源层分析模块:Cadence Design Systems的SpecctraQuest PCB信号完整性套件中的电源完整性模块据称能让工程师在高速PCB设计中更好地控制电源层分析和共模EMI。

该产品是由一份与Sun Microsystems公司签署的开发协议而来的,Sun最初研制该项技术是为了解决母板上的电源问题。

有了这种新模块,用户就可根据系统要求来算出电源层的目标阻抗;然后基于板上的器件考虑去耦合要求,Shah表示,向导程序能帮助用户确定其设计所要求的去耦合电容的数目和类型;选择一组去耦合电容并放置在板上之后,用户就可运行一个仿真程序,通过分析结果来发现问题所在。

PCIE 3.0简介及信号和协议测试方法

PCIE 3.0简介及信号和协议测试方法安捷伦科技(中国)有限公司:李凯一、前言PCI Express(简称PCIE)总线是PCI总线的串行版本,其采用多对高速串行的差分信号进行高速传输,每对差分线上的信号速率可以是1代的2.5Gbps、2代的5Gbps以及现在正逐渐开始应用的3代8Gbps。

PCIE标准是由PCI-SIG组织制定,自从推出以来,1代和2代标准已经在PC和Server上逐渐普及,用于支持高速显卡以及其它接口卡对于高速数据传输的要求。

出于支持更高总线数据吞吐率的目的,PCI-SIG组织在2010年制定了PCIE 3.0,即PCIE 3代的规范。

目前,PCIE 3.0已经开始出现在一些高端的Server上,而在普通PC上的应用也是指日可待。

那么PCIE 3.0总线究竟有什么特点?对于其测试有什么特殊的地方呢?我们这里就来探讨一下。

二、PCIE 3.0简介1、信号速率的变化首先我们看一下制定PCIE 3代规范的目的,其目的主要是要在现有的FR4板材和接插件的基础上提供比PCIE 2代高一倍的有效数据传输速率,同时保持和原有1代、2代设备的兼容。

别看这是个简单的目的,但实现起来可不容易。

我们知道,PCIE 2代在每对差分线上的数据传输速率是5Gbps,相对于1代提高了1倍;而3代要相对于2代把速率也提高一倍,理所当然的是把数据传输速率提高到10Gbps。

但是就是这个10Gbps把PCI-SIG给难住了,因为PC和Server上出于成本的考虑,普遍使用便宜的FR4的PCB板材以及廉价的接插件,无论采用什么技术都很难保证10Gbps的信号还能在原来的信号路径上可靠地传输很远的距离(典型距离是15~30cm)。

因此PCI-SIG最终决定把PCIE 3代的数据传输速率定在8Gbps。

但是8Gbps比着2代的5Gbps并没有高一倍,所以PCI-SIG决定在3代标准中把在1代和2代中使用的8b/10b编码去掉。

PCIe 3.0 Tx 信号品质一致性测试方法和步骤

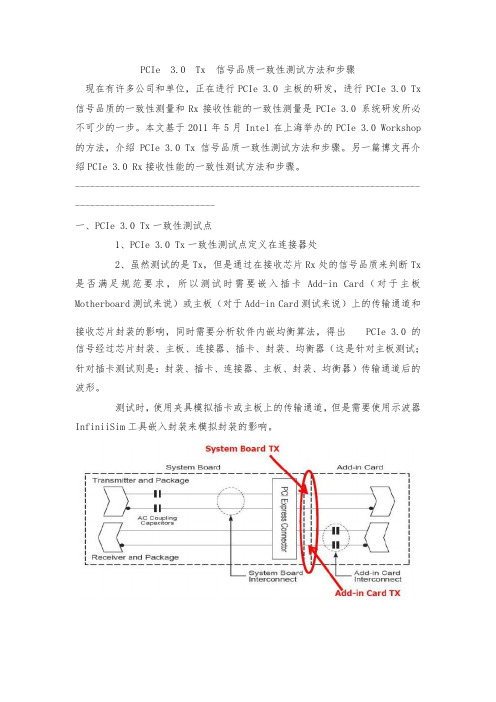

测试时,使用夹具模拟插卡或主板上的传输通道,但是需要使用示波器 InfiniiSim 工具嵌入封装来模拟封装的影响。

即需要同时捕获时钟信号和数据信号,用 Sigtest 进行后分析。 用 SMP-SMA 电缆连接时钟信号,用 SMA-SMA 电缆连接数据信号。示波器

内要对时钟信号和数据信号做差,如果使用 Infiniium 示波器,把时钟连接到 1 和 3 通道,把数据连接到 2 和 4 通道,Infiniium 示波器内部的 FPGA 可以自动 1-3 和 2-4 做差运算,减少捕获波形和运算时间。

PCIe 3.0 Tx 信号品质一致性测试方法和步骤 现在有许多公司和单位,正在进行 PCIe 3.0 主板的研发,进行 PCIe 3.0 Tx 信号品质的一致性测量和 Rx 接收性能的一可少的一步。本文基于 2011 年 5 月 Intel 在上海举办的 PCIe 3.0 Workshop 的方法,介绍 PCIe 3.0 Tx 信号品质一致性测试方法和步骤。另一篇博文再介 绍 PCIe 3.0 Rx 接收性能的一致性测试方法和步骤。 -----------------------------------------------------------------------------------------------一、PCIe 3.0 Tx 一致性测试点

影响嵌入到信号里,通过 InfiniiSim 工具可以做这件事情。InfiniiSim 是一个 嵌入和去嵌入工具,可以嵌入传输线或封装的影响,或把传输线或封装的影响去 掉。但是,需要使用测试手段或仿真手段提取传输线或封装的 S 参数。

是德科技 USB 2.0 和 3.0 协议分析仪

是德科技U4611A/B USB 2.0/3.0协议分析仪采用MegaZoom 技术的3.7.x 版本技术资料唯有是德科技能够提供深入、快速分析当前高性能超高速(SuperSpeed)USB 设计所必需的测试工具。

高性能分析–实时端点分析–实时链路分析–实时LTSSM–详细的性能记录–可定制的触发、计数、过滤即时访问捕获到的数据–分段存储器可更高效地保存多次事件捕获的结果–可捕获多达18 GB 的数据–直观的图形用户界面只需点击一下即可查看数据–面向规范的清晰数据解码概述Keysight U4611A/B USB 协议分析仪提供业界领先的实时性能分析、LTSSM 状态跟踪、最全面的触发系统以及高达18 GB 的可定制数据分析特性,从而将协议分析仪的易用性提升到更高水平。

是德科技提供的协议分析仪是在复杂超高速USB 系统中查找间歇性问题的最佳工具。

对于当今的USB 开发商和集成商来讲,要想确保他们设计的产品与日益增长的无数USB 设备完全兼容是几乎不可能的任务。

通常,捕获大批量流量会遇到很多困难,例如迹线缓冲区空间有限、查看数据时等待时间过长、搜索和保存速度太慢等。

随着USB 3.0 设计不再局限于基本功能,USB 设计人员正力求使新的和现有的USB 器件发挥最佳性能。

MegaZoom™ 技术可实时分析USB 操作,并提供详细的操作性能显示。

Keysight U4611A/B USB 协议分析仪能够即时显示捕获到的数据,甚至拥有高达18 GB 的数据轨迹捕获深度,从而克服了这些限制。

通过硬件加速千兆位以太网(高达70 MB/s)或PCI Express(高达550 MB/s)将轨迹数据传输到主机,无需等待即可分析完全深度数据。

例如,只需15 秒便可获得完整18 GB 轨迹的直方图。

数据可以显示为变址前(Pre-indexed)和压缩轨迹数据形式,可通过多个分析处理器进行分析。

图 1. U4611A/B 分析仪以直通模式连接,并记录主机与被测器件之间交换的流量。

用于PCI—Express 3.0协议分析仪的仿真设计验证工具

20 。 0 9 作为 形化系统设计( S)软件 的新成 员 , G I) 该软件提供标 准的开发平 台用于设 计机 器人 和 f主控制 系统 。N a VE { I b lW L

A L 5 4的 额定 ] 作温 度 范 罔 为 一 0摄 氏度 至 + 5摄 氏 D 50 4 8

度。

阶 段 的 P I 3 O通 讯 中 加 以 描 述 )像 硅 后 期 阶段 瞍 什 分 Ce . I 0 /

离追踪文件同样 的 ‘ 乐和分析 ? 式 通过提取 l / O流 数据 {

和 交 换 包 中 示 的 潜 在 缺 陷 特 征 .i P S Sm A S支持 发 皙 在 提 交 刨 硅 设计 之 前 更 完 整 得 测 试和 测 试逻 辑 没计 , 除 可能 导 消

D o e L D驱动 器降低 照明产品的尺 寸和成本 ids E

Doe 公 词 推 一 款 额 定 l 的 线 性 模 式 恒 流 L D驱 i s d A E

动器 , 专门用于降低包括手 电筒 、 应急照明 , 同照 明和池 畔 仡 应Ⅲ 等通 件照 明产 品的尺寸和成本 。 j 高集成 的 I D1 1 E ) 0 D驱 动器 采用优化 的小尺 寸扁平 L L D N封 装 ,集成 _… 个独 特的 ”基底仃 取预偏置 品体管 ” F r ,

4 0 H 至Biblioteka 6 0 MHz 5M z 00 的高频 接收器和发射器信 号链 。 这个检 波 器 只需 _ 25 至 3 V单 电源 下 l作 ,} 电流 不 到 存 . V . 3 肖耗 1 mA . 输 入端内部采 用交流耦合 , 定输入阻抗 为 5 0欧 8 额 0

姆 。R S输 足 线 性 响 应 的 直 流 电 压 , 9 0 z 的 转 换 M 在 0 MH 时 增 益 为 1 7 , R 。 A L 5 4在 3 d . V 、 MS D 5 0 8 , 0 B范 同 内都 具 有 色

Cadence全新SpeedBridge Adapter实现对PCIe 3.0设计的确认和验证

Cadence 全新SpeedBridge Adapter 实现对PCIe 3.0

设计的确认和验证

【中国,2013 年7 月30 日】全球电子设计创新领先企业Cadence 设计系统公司(NASDAQ:CDNS)今天宣布推出全新用于PCIe 3.0 的SpeedBridge® Adapter。

它为设计师们提供了一个重要的工具,来验证和确认他们的PCI Express (PCIe)设计。

这一全新适配器在搭配Cadence® Palladium® VerificaTIon CompuTIng Platform 一起使用时,能很容易建立并快速调试基于PCIe 的设计;它向后兼容基于PCIe 2.0、1.1 和1.0a 的设计。

用于PCIe 3.0 的SpeedBridge Adapter 通过在运行生产级软件驱动程序和操作系统的硅片前环境中提供与真实世界流量的高速交互,缩短

了上市时间并降低了系统风险。

SpeedBridge Adapter 设计用于硅片前RTL、及基于PCIe 的ASIC 和系统级芯片(SoCs)的集成,并允许在真实世界工作条件下进行系统仿真。

该适配器通过实际ASIC 或SoC 软件与硬件、驱动程序和应用程序开发对经

过仿真的PCIe 3.0 设计进行验证,并可搭配现有软件及软件测试程序或分析

程序一起运行。

设计师们面临挑战,需要越来越多地在控制日益增强的设计复杂性和

日益缩短的上市时间窗口之间取得平衡,Cadence 公司负责系统和软件实现。

泰克为PCI Express 3.0推出逻辑分析仪测试解决方案

两 路 数 据 包 信 号 存 在 不 同 幅值 跳 变 的 情 况 下 , 别 测 试 突 分

发 式 光 接 收 模 块 的误 码 性 能 。试 验 中使 用 的 被 测 突 发 式

c yf r p i l u eain J .L g t . c n 1 ,1 9 , r t a b sOp r t [ ] ih w Teh o. 4 o O c o 9

E 3 O s u Qi X, a weie , t 1 2 si r e P, u B u l k J e a.Ano eve f a— n v r i o s w p

sve o ia e wo ks i i ptc ln t r nPr c I . Sy p. Si a s,Cic is o . nt m gn l r ut,

E ]Ot Y, wat R G, t 1 s a S r e a.Hi — p e , u s— d , a k z g S ed B rt h Mo e P c —

etCa bl — pa e Optc lR e eve n n t nt ne us Clc Re ov — ia c i r a d I s a a o o k c —

m si e P N Uptem Ln [] i o i t O s a i J .We ej eo, 0 6 snnh G r k t lkdpt 20 ti

( 0) 1 .

E ]B u eie ,e a.D —o pe u s— d r n mi e fr 7 a w l kJ t 1 C c u l b rt n d mo eta s t r o t 1 2 一 / p te m P N [ ] E eto . L t ,2 0 , 0 . 5Gb s u sr a O J . lc n et r . 04 4

力科公司发布极高性价比的便携式USB3.0协议分析仪

提 高 大型 应 用 开 发 的功 能 性

L b E 2 1 为更多 高级用 户和开发 组提供全 新特 a VI W 0 0

wh t e z s ,了解关于L b E 2 1更多信息 ,点 as w/ h / n a VI W 0 0

击此处 , 载L b E 2 1 评估版软件 。 下 a VI W 0 0

中 。外部 尺寸仅为 5 英寸x 英寸x1 英寸 ,它提供 了全面的 6 2

功 能 集 合 ,完 全 支 持 US 3 0 2 0 析 。 B .和 .分

产 品研发副总裁雷得 . 奥古斯丁这么说。由于尺寸小巧和低价

格 ,力科的A v o 3 di rT 将允许存储设备O M厂商装备更多的 s E

S ATA设备 ̄ US . n即插 即用接 口绑定在 一起 ,以便 能 N B3 o

从 而保 持 了力 科多年 来 的高 速信 号探 测方 面 的专 家形 象 .

Ad i r基于力科Vo a e验证系统一世界上使 用最 广泛 的 vs o y gr S prpe B u eS ed US 分析仪 同的市场领先的 可靠性 。 Ad io 拥有直观化 C vsr T3 ATC 波形视 图对于使用和理 解US 协议的全部好处 ,这种独 有的层次化显示提供 了数 B 据 帧级 别的可 观测性 能 ,也 包括在 更高 层US 事件 的解码 B 并且保持 了与这款旗舰 产品相

配置工具 ,帮助 用户通过 网络 浏览 器远 程访 问并 配置他 们 性 ,改 善复 用代码 、组vI 的接 口以及更快 的创建 时 间的层 级 ,并 从 编译 版 本 中分 离 出VI 代码 ,以帮 助 源代 码 管 源 理 。这 些功 能可理 想用于 对用 户 、软 件版本 和计算 机平 台

泰克为PCI Express3.0推出逻辑分析仪测试解决方案

统行 为的时 间相关 特点 ,从协议层分析开始一直到物理层 ,调试难检

问题 的根 本 原 因 。

泰克P I .N试解决方案基于泰克上一代PCe Ce 3o l协议和逻辑分析产品,达些产品 已经被业内芯片厂商 、系统设计人员

◎ 了解更 多信息 ,请访问泰克公司T t r @tkrnx wie一 et i t o 。

N与天津 中德举行签约仪式 ,携手共建 “ I 虚拟仪器技术 中心"

NI 天津 中德 职 业 技 术 学 院 就 共 建 “ 与 天津 中德 一美 国 N 虚 拟仪 器技 术 中心 ”在 天 津 中德 职 业 技 术 学 院 举 行 了 隆重 的 签 I 约 仪 式 。这 是 NI 多 年 与 国 内高 等 院 校 联 合培 养 虚 拟 仪 器技 术 人 才 之 后 ,与 高等 职 业 教 育 院校 进 行 的 又 一 重要 合 作 。 在 NI 校 市场 部 经理 徐 资 与 天 津 中 德职 业 技 术 学 院 院 长 李 大 卫作 为 双 方 代 表 签 署 了 “ 院 天津 中德 — — 美 国 N 虚拟 仪 器 技 术 I

能包括灵活的集成数据视 图,分析和显示与物 理层事件 相关 的协议业务流量。逻辑分析仪功能包括多种 探测选项 、完善的 触发及原始符号和通路数据时 间相关波形和分解的列表数据 图。新的PC e I解决方案扩展 了T A7 0 系列高性 能逻辑分析仪 L 00

产 品组 合 ,适 用于 T A70 主机 ,包 括TL T 1便 携 式 主 机 ̄ T A7 1 台式 主 机 。 L 00 A 02 H L 06

态

力科推出用于PCI-Express 3.0协议分析仪的新仿真设计验证工具

◎了解更多信息 ,请访问ht: w t // ww. he sh r.o c / e sp pi=20 p r d- cwa cm.n nw .h ? o z d 5。

中国科技核心期刊

一8 — 7

黼 裂墓 期

业

力科推 出用于P IEpes3O C- xr 。协议分析仪 பைடு நூலகம் 的新仿真设计验证工具

力科推 出新的分析 工具显著扩展P I E p es .协议测试 。新的软件工具 叫smP s C - x rs 0 3 i As ,针对硅 前期的仿真和设计验 证开发阶段 。SmP S i AS 基于力科现有的用以显示和分析通 信数据的用户界面,扩展 了通常用在硅后期测试的仿真环境 的强 大通信数据分析能力。S n p y ,世界上主要的半导体设计和制造软件 与I 的领导者之一 ,将是第一个在 其PC — x rs y oss P I E p es D s n r 验证I软件中支持SmP S ei Wae g P i AS 的厂商。D s n r 用户通过使用诸如新思VC 这样的仿真器 ,可以导出仿真矢 ei Wae a S

技 术工 程 师 配 合支 持 。 通 过 此 开 放 实 验 室 ,R&S 司 将 满 足 用 户 在 无 线 通 信 、航 空 航 公 天 、 通 用 射 频 与 微 波 测 试 、 音视 频 测 试 ,以 及 电磁 兼 容 等 多 个 方 面 的

面向国产OS的PCI采集卡软硬件设计与验证

中图分类号:TP274.2 文献标识码:A

文章编号:1002-2279-( 2017 )02-0059-05

Design and Verification of Software and Hardware of PCI Acquisition Card for Domestic OS

L iu Ju n xia 1,Yang X ianw en 2

第2期 2017年 4 月

•微机应用•

微处理机 MICROPROCESSORS

No. 2 Apr., 2017

面向国产O S 的 PCI采集卡软硬件设计与验证

刘军霞\杨先文2

(1.河南省军区自动化站,郑 州 450003; 2.信息工程大学,郑 州 450004)

摘 要 :为了满足国产操作系统上数据采集的性能要求,在 研 究 P C I采集卡原理的基础上,提

L in u x 作为一种支持多用户、多 任 务 、多线程和 多 C P U 的 开 放 式 操 作 系 统 (operating system ,OS)内 核 ,已 被 国 产 O S 广 泛 采 纳 ,出现了中标麒麟[3]等许 多优秀产品。由 于 O S关系关键领域信息化的自主 可控安 全 ,因 而推广国产O S 的意义重大。 目前,针 对 P C I采集卡的驱动和应用程序设计大多针对 W in d o w s 平 台 [4-5],面 向 国 产 O S 的软件设计是亟待 解决的问题。

PCI acquisition card based on FPGA and L inux is proposed. The hardware is m ainly designed for

FPG A contro l lo g ic ,in c lu d in g clo c k m odule,data a cq u isitio n m odule,F IF O m odule and m ain control

力科推出用于PCI

力科推出用于PCI

力科推出用于PCI-Express 3.0协议测试的分析工具

力科今天宣布推出新的分析工具显着扩展PCI-Express 3.0协议测试。

新的软件工具叫SimPASS,针对硅前期的仿真和设计验证开发阶段。

SimPASS基于力科现有的用以显示和分析通信数据的用户界面,扩展了通常用在硅后期测试的仿真环境的强大通信数据分析能力。

Synopsys,世界上主要的半导体设计和制造软件与IP的领导者之一,将是第一个在其PCI-Express DesignWare 验证IP软件中支持SimPASS的厂商。

DesignWare用户通过使用诸如新思VCS这样的仿真器,可以导出仿真矢量文件和使用SiMPASS PE的分析能力。

用于PCI-Express的SimPASS PE是SiMPASS系列产品中的第一个工具。

SimPASS允许RTL仿真矢量文件(在硅前期阶段的PCIe 3.0 I/O通讯中加以描述)像硅后期阶段硬件分离追踪文件同样的方式显示和分析。

通过提取

I/O流中数据和交换包中显示的潜在缺陷特征,SimPASS支持开发者在提交到硅设计之前更完整得测试和调试逻辑设计,消除可能导致昂贵和时间浪费的二次设计的设计缺陷方面的重大进展。

PCIe 3.0开发者面临的主要问题是,需要快速发现在LTSSM和不正确的信用流交换中的电源转换状态缺陷,并追踪到来源,这样可以显着降低新产品面向市场的开发时间和费用。

“力科SimPASS PE为设计者提供了一个新的观察和分析PCIe I/O通讯。

大型分析仪器仿真软件ISTS3.0操作技巧介绍说明

大型分析仪器仿真软件ISTS3.0 仿真培训系统操作说明书北京东方仿真软件技术有限公司2008年8月一、培训软件启动和主要模块 (3)二、实验操作说明 (9)1、开机操作 (9)2、分析标准样品 (14)3、分析待测样品 (17)4、数据处理界面 (19)5、实验完成 (20)一、培训软件启动和主要模块在正确安装完成后,在界面上有该软件的启动快捷方式。

双击该图标,启动软件运行。

软件运行后,进入如下界面(见图2),输入姓名、学号和机器号后,还需输入教师站IP地址。

点“单机练习”或“局域网模式”启动软件。

进入工艺选择,如图3。

(图2)(图3)然后进入“培训项目”界面,气相色谱技能大赛里面的“给定物质定性定量分析”。

(见图4),点击左上角的“启动项目”。

进入导航界面。

(见图5)(图4)进入导航页面,主要包括“主界面(即导航页面)”“操作界面”“试题说明”。

(图5)操作界面(图6)试题说明(图7)二.实验操作说明点击界面中左下角功能钮“操作界面”,直接进入实验操作。

主界面如图6。

学员做气相色谱仿真实验“给定物质定性定量分析”,可按以下步骤操作(对此软件有一定程度的熟悉后,并不需要严格按以下步骤操作,学员完全可以根据对所学知识的理解,进行些创造性的操作)。

下面说明部分只以一个实验的完整操作讲解,其他实验灵活运用,操作方法类似。

(图8) 1、开机操作(1)点击色谱仪,打开色谱仪柱温箱门,检查色谱柱是否安装。

选择色功能钮色谱仪载气设置进样设置谱柱类型。

(2)设定载气流量:点击“气体钢瓶”上,弹出“气体设置”窗口。

回答问题“氢气钢瓶的瓶身颜色”。

根据需要开载气到一定流量,在载气输入框中写入50(可自行设计载气流量)。

点击“确定”。

如下图(3)点击色谱仪,打开色谱仪电源,(4)点击“电脑屏幕”,打开“分析控制”界面,设定柱温、进样口温度和检测器。

然后“发送方法”。

“进样口温度”:点击“设置”。

温度设为:230~240℃。

PCIE 3.0简介及信号和协议测试方法

PCIE 3.0简介及信号和协议测试方法安捷伦科技(中国)有限公司:李凯一、前言PCI Express(简称PCIE)总线是PCI总线的串行版本,其采用多对高速串行的差分信号进行高速传输,每对差分线上的信号速率可以是1代的2.5Gbps、2代的5Gbps以及现在正逐渐开始应用的3代8Gbps。

PCIE标准是由PCI-SIG组织制定,自从推出以来,1代和2代标准已经在PC和Server上逐渐普及,用于支持高速显卡以及其它接口卡对于高速数据传输的要求。

出于支持更高总线数据吞吐率的目的,PCI-SIG组织在2010年制定了PCIE 3.0,即PCIE 3代的规范。

目前,PCIE 3.0已经开始出现在一些高端的Server上,而在普通PC上的应用也是指日可待。

那么PCIE 3.0总线究竟有什么特点?对于其测试有什么特殊的地方呢?我们这里就来探讨一下。

二、PCIE 3.0简介1、信号速率的变化首先我们看一下制定PCIE 3代规范的目的,其目的主要是要在现有的FR4板材和接插件的基础上提供比PCIE 2代高一倍的有效数据传输速率,同时保持和原有1代、2代设备的兼容。

别看这是个简单的目的,但实现起来可不容易。

我们知道,PCIE 2代在每对差分线上的数据传输速率是5Gbps,相对于1代提高了1倍;而3代要相对于2代把速率也提高一倍,理所当然的是把数据传输速率提高到10Gbps。

但是就是这个10Gbps把PCI-SIG给难住了,因为PC和Server上出于成本的考虑,普遍使用便宜的FR4的PCB板材以及廉价的接插件,无论采用什么技术都很难保证10Gbps的信号还能在原来的信号路径上可靠地传输很远的距离(典型距离是15~30cm)。

因此PCI-SIG最终决定把PCIE 3代的数据传输速率定在8Gbps。

但是8Gbps比着2代的5Gbps并没有高一倍,所以PCI-SIG决定在3代标准中把在1代和2代中使用的8b/10b编码去掉。

Magma推出功能验证工具Quartz Formal

Magma推出功能验证工具Quartz Formal

佚名

【期刊名称】《中国集成电路》

【年(卷),期】2004(000)006

【总页数】1页(P8)

【正文语种】中文

【中图分类】TP311.56

【相关文献】

1.Magma推出针对IBM-Chartered工艺平台的90纳米设计工具包 [J],

2.力科推出用于PCI-Express

3.0协议分析仪的新仿真设计验证工具 [J],

3.泰克推出业内首个用于MIPI M-PHY调试与验证的测试工具 [J],

4.泰克推出业内首个用于MIPI M-PHY调试与验证的测试工具对最新高速M-PHY规范的支持,包括DPOJET工具套件以及针对泰克示波器的M-PHY DigRFv4解码 [J],

5.CFCA推出具有签名验证功能普通证书应用工具包 [J],

因版权原因,仅展示原文概要,查看原文内容请购买。

pcie协议测试方案

PCIe协议测试方案简介PCI Express(PCIe)是一种高速串行计算机扩展总线接口标准,用于连接计算机的外部设备和扩展卡。

在设计和开发PCIe设备时,为了确保设备的兼容性和稳定性,需要进行PCIe协议测试。

本文档将介绍一种基于软件和硬件结合的PCIe协议测试方案,用于验证PCIe设备的协议一致性和正确性。

该方案不仅可以提高测试效率,还可以提供更全面的测试覆盖率,确保设备的稳定性和可靠性。

测试环境搭建为了进行PCIe协议测试,需要搭建相应的测试环境。

测试环境包括以下组件:1.测试主机:用于发送和接收PCIe协议的测试数据。

2.设备模拟器:用于模拟PCIe设备的行为,接收和处理来自测试主机的测试数据。

3.测试工具:用于生成和分析PCIe协议的测试数据,以及监视测试过程中的信号和状态。

具体的测试环境搭建步骤如下:1.搭建测试主机:选择一台性能较好的计算机作为测试主机,安装操作系统和相应的PCIe驱动程序。

2.购买设备模拟器:根据需要模拟的PCIe设备类型,选择相应的设备模拟器进行购买。

3.安装和配置测试工具:根据实际情况选择合适的测试工具,并按照厂商提供的说明进行安装和配置。

4.连接测试设备:将测试主机和设备模拟器通过PCIe接口进行连接,确保连接稳定可靠。

5.配置测试参数:根据需要测试的协议特性和功能,配置测试工具的参数,包括数据传输速率、协议版本等。

测试流程PCIe协议测试流程可以分为以下几个阶段:1.初始化阶段:在该阶段,测试主机与设备模拟器建立起通信连接,并进行必要的初始化配置。

2.链路层测试:在该阶段,测试主机发送链路层数据,并检查设备模拟器返回的应答是否符合PCIe协议规范。

3.传输层测试:在该阶段,测试主机发送传输层数据,并检查设备模拟器返回的应答是否符合PCIe协议规范。

4.发送和接收信号测试:在该阶段,测试主机发送特定信号并验证设备模拟器的返回信号是否正常。

5.错误处理测试:在该阶段,测试主机发送错误数据,并验证设备模拟器的错误处理能力。

pcie协议分析仪

pcie协议分析仪PCIe协议分析仪。

PCIe(Peripheral Component Interconnect Express)是一种用于连接外部设备的高速串行计算机扩展总线标准。

它是PCI总线的最新版本,旨在取代PCI和AGP标准。

PCIe协议分析仪是用于分析PCIe协议的工具,它可以帮助工程师深入了解和分析PCIe总线上的数据传输和通信过程。

PCIe协议分析仪的原理是通过捕获和分析PCIe总线上的数据流,从而实现对数据传输的监控和分析。

它可以帮助工程师识别和解决PCIe总线上的通信问题,提高系统的稳定性和可靠性。

PCIe协议分析仪通常包括硬件和软件两部分。

硬件部分包括捕获数据的PCIe探头和数据存储设备,软件部分包括用于分析和显示数据的分析软件。

通过硬件和软件的配合,PCIe协议分析仪可以实现对PCIe总线上数据的全面监控和分析。

PCIe协议分析仪的功能包括但不限于:1. 数据捕获,能够捕获PCIe总线上的数据流,包括命令、地址和数据等信息。

2. 数据分析,能够对捕获的数据进行解析和分析,识别数据传输过程中的问题和异常。

3. 时序分析,能够分析数据传输的时序特性,包括时钟、数据有效性和延迟等参数。

4. 事件触发,能够根据预设条件触发数据捕获,以便对特定事件进行分析和跟踪。

5. 协议验证,能够验证PCIe协议的遵从性,确保系统的兼容性和稳定性。

使用PCIe协议分析仪的好处包括但不限于:1. 故障排除,能够帮助工程师快速定位PCIe总线上的通信问题,缩短故障排除时间。

2. 性能优化,能够帮助工程师分析PCIe总线上的数据传输性能,优化系统的性能和效率。

3. 协议验证,能够验证系统对PCIe协议的遵从性,确保系统的兼容性和稳定性。

在实际应用中,工程师可以根据具体的需求选择合适的PCIe协议分析仪。

一般来说,选择PCIe协议分析仪时需要考虑以下几个方面:1. 数据捕获能力,包括数据传输速率、数据存储容量和数据捕获的灵活性。

凌华科技主导新版COMExpress3.0规范的制定

凌华科技主导新版COMExpress3.0规范的制定

佚名

【期刊名称】《测控技术》

【年(卷),期】2016(35)10

【摘要】凌华科技是PCI工业电脑制造商协会(PICMG)的执行委员,并主导了这次新版COMExpress3.0规范的制定。

凌华科技最近发布的新款嵌入式模块化电脑Express-BD7,即采用新版COMEx—press3.0标准中的全新Type7引脚。

新版Type7引脚以低功率、高性能与增加10GbE容量的设计,成为小型封装规格的翘楚,将有利于工业自动化与数据通信等产业。

【总页数】1页(P158-158)

【关键词】凌华科技;电脑制造商;工业自动化;10GbE;数据通信;PCI;模块化;嵌入式【正文语种】中文

【中图分类】TP273

【相关文献】

1.凌华科技宣布支持SGeT通用物联网连接器(UIC)规范与XRCE实时的设备数

据传输协议 [J], ;

2.凌华科技:专注行业做技术的主导者 [J], 梁秀璟

3.凌华科技在PICMG协会中主导新版COM Express3.0规范的制定新版Type7

引脚以低功率、高性能与增加10GbE容量的设计,成为小型封装规格的翘楚 [J],

4.凌华科技在PICMG协会中主导新版COM Express 3.0规范的制定 [J],

5.凌华科技新版引脚Type 7 [J],

因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

W id Ri e n v r

电话 :0 0 4 9 1 5 1 6 3 8 8

,f /www. n r v . o ,t / p: wi d i er m c

大 的Ec i s 集成开发环境(DE 工具 , lp e I )

拥 有 由恩 智 浦 设 计 的 全 新 、直 观 的 用 户 界 面 、针 对 C re — 0 化 的 编 译 器 和 o tx M 优

础算法 ,并且包含机 器人和 自主式车 辆

的 运 动 控 制 函 数 。利 用 这 一 新 软 件 ,工 程 师 和 科 学 家 能 够 更 快 地 将 设 想 付诸 实 现 ,对 实 时 嵌 入 式 * F 件 进 行 无 n GA硬 P 缝 部 署 ,并 通 过 整 合 各 种 处 理 平 台 、 第

强多核能力

VxW o k 6 8 备 增 强 的 系统 性 r s .具

电 话 :0 0 2 0 3 8 1 88 -0 1

ht /www. c o . om t / p: 1 r yc e

能 、更小的空 间占用和更高 的硬件平台

灵活 性 。作 为 风 河 最 新 版 本 的Vx ok W rs

供标准 的开发平台用于 设计机器 人和 自

效地帮助 客户提高产 品质量、改善产 品 用 ,并 能 支 持 完 整 的 产 品 设 计 周期 ,为

用 户提 供 端 到端 解 决 方 案 。

L PCXp e s 开 发 平 台 基 于 功 能 强 rso

主控制 系统。它可 以提 供丰富的机 器人 兼容性 、提升产品性能。

平 台 ,VxW O k 6 8 可 提 供 多种 灵 r s .还

分利用Te t n k o 的集成化S 引擎和 PI CE

Te t n k o QC 的 精 确 提 取 功 能 。 应 用 于 P

~5 个时序情景时 ,Te t n k o 可以使用 针对L C 0C r x M 的在线开 5 0 P 10 ot - 0 1 e

Wid ie V Wok 68 n Rv r x rs .提供更

现。

Le o Cr y

延 并加 大 晶粒 尺 寸的 全 局 悲观 容 限 。 对 于 关 键 性 路 径 和 连 线 分 析 ,Te t n kO f T k o QC 提 供 了 高精 度模 式 ,充 1 e tn ] P

SmP S 议 分 析 一 起 使 用提 升 了 设 计 OCV( i AS 协 A—OCV) 限 降 低 技 术 。 通 过 将 容

电话 :8 0 2 — 6 2 0 8 0 3 2

ht /www. i o t / p: n. m e

生 产 力 并 有 助 于 保 证 协 议 错 误 和 性 能 问 A— 入 时 序 收 敛 流 程 ,设 计 团 队 O CV纳 题 在 进 入 硅 生 产 之 前 的 仿 真 中就 能 被 发 能 够 最 大 程 度 降 低 可 导 致 投 片 进 度 拖

电 话 :0 0 6 l - 2 8 1 - 5 7 2 8

, : sc . x c r , / n n p. o f / n

静态时序分析平台

时序分 析平 台Te 0 可在 不牺牲 kt n

时 间 。此 外 ,该 软 件 还 包 含 能 够 轻 松 在 硅设计之前 更完整得测试和调 试逻辑设 精 度 的 前提 下 较 传统 工具 大 幅提 高 容

NI

硬 件 上 有 效运 行 多场 景分 析 。为解 决

SmP S P 为 设 计 者 提 供 了 一 个 新 的 4 nm及 4 nm以 下 设 计 团 队 所 面 临 的 i A S E 0 0 观 察 和 分 析 PCI I O通 信 的 途 径 ,和 时 序 收 敛 问 题 ,T k o 支 持 Ad a c d e / e tn vne

可以 在低成 本 实时嵌入式硬 件上实现的机 器人I P,用 计 ,消除 可能导致 昂贵和 时间浪费 的二 量 ,显 著缩 短运 行时 间 ,

于避障 、动力学和搜 寻算法 ,帮 助 自主 次 设 计 的 设 计 缺 陷 方 面 的 重 大 进 展 。 系统 或 机 器 人 选 择 极 佳 路 径 。

P Ln J / wD调试 用于P - x rs 30 CIE p e s .协议分析仪 函数库 、L C— i k TAG s

的仿真设计验证工具

探针和 目标板 ,为用户提供丰富的开发

用 于 P I E p es i AS P 工 具 ,加 速 产 品开 发 ,缩 短 新 品上 市 时 C — x rs的SmP S E 间。

NXP Se ion u t r m c d c os

i AS 三 方 软 件 工具 和 预 制 机 器 人 平 台 ,达 到 是SM P S 系 列 产 品 中 的 第一 个 工 具 。 软件的最大灵活性 。 S mPAS 允 许 RTL 真 矢 量 文 件 ( i S 仿 在

e . I O Lb E a VI W Ro o is 0 9 够 从 硅 前 期 阶 段 的 PCI 30 / 通 信 中加 b tc 2 0 能 C + /C +、 . 件 和 VH DL 语 言 中 导 以 描 述 )像 硅 后 期 阶 段 硬 件 分 离 追 踪 文 m文 等 / 入 代 码 , 并利 用 内 置驱 动 程 序 与 多种 传 件 同样 的 方式 显 示 和 分 析 。 通 过 提 取 I 感器 (N I  ̄ L DAR、 红 外 传 感 器 、声 纳 和 O流 中数 据和交换 包 中显示的潜 在缺 陷 I n 支 GPS )进 行 通 信 ,从 而 大 幅 度缩 短 开 发 特 征 ,Si PASS 持 开 发 者 在 提 交 到