基于FPGA的数字信源设计

基于FPGA的高准确度数字频率信号源设计

G i S a — i UO Ja n HIY n b n 一

XI o g y n E S n —u

( .C l g fEet nca dIfr t n otw s r oyeh ia U iesy ia 0 2 1 ol eo lcr i n nomai ,N r et n P ltc ncl nvri ,X ’ n70 7 ; e o o h e t 1

(. 1 西北工 业大 学电子信 息 学院 , 西安 7 0 7 ; . 10 2 2 空军航 空 大 学电子 工程 系, 长春 10 2 ) 3 0 2

摘 要 介绍了直接数字频率合成技术的实现方法, 分析了其优越的技术 的数字 频率信号源 。仿 真结果 表 明, 与传 统 的信号 源相 比 , 使用该 方 法实现 的信 号源 , 其信 号种 类

K e r s Dii in Frq e c y t ss tc n q e S p l s i ao FP y wo d gt sg a l a l e u n y s nhe i e h iu u p y o cl tr l GA

引 言

信 号 源 是 电子 设 备 特 别 是 测 试 设 备 的必 备 部

A s at T er la o e o D Dr t i t ytei eh o g ae nteF G — bt c r h azt nm t do D S( i c D ga S n s )t nl ybsdo P A i i ei i h f e il h s c o h sn

第2 6卷

第 4期

文章 编 号 :00 22 20 ) 4— 0 4 4 10 —70 (0 6 0 06 —0

中 图分 类 号 : N 8 T 9

基于FPGA的SR FM数字接收机的设计

基于FPGA的SR FM数字接收机的设计基于FPGA的SR FM数字接收机的设计随着科技的快速发展,无线通信技术也在不断进步。

作为一种常见的调制解调技术,频率调制(Frequency Modulation,简称FM)广泛应用于广播、电视和无线通信等领域。

FM调制与解调技术的研究和开发是无线通信领域的重要课题之一。

本文旨在介绍基于可编程逻辑门阵列(Field-ProgrammableGate Array,简称FPGA)的无线数字接收机设计,并通过SR (Software Radio)技术实现FM信号的接收和解调。

首先,我们对FM调制原理进行简要回顾。

FM调制是基于载波频率的变化来传输信息的一种调制方式。

FM调制信号的频偏与原始信号的幅度成正比。

FM信号的接收主要包括两个步骤:解调和恢复信号。

传统的FM解调技术主要采用锁相环或者鉴频器等模拟电路来完成。

而基于FPGA的SR技术可以使用数字处理来实现FM信号的解调,极大提高了系统的灵活性和可靠性。

FPGA是一种可编程逻辑设备,其内部具有大量逻辑门、寄存器和乘法器等功能模块,通过对这些模块进行组合和配置,可以实现各种数字电路的设计。

在基于FPGA的SR FM数字接收机中,我们可以使用FPGA实现数字滤波器、解调器和数字信号处理等模块,并通过配置FPGA中的逻辑来实现不同的调制解调方式和功能。

为了实现FM信号接收和解调的功能,我们需要设计FPGA中的数字滤波器。

数字滤波器可以用来去除信号中的噪声和杂散,并提取出所需的基带信号。

在FM信号接收中,常用的数字滤波器有低通滤波器和带通滤波器。

低通滤波器用于去除高频干扰,而带通滤波器则可提取出指定频率范围内的信号。

通过在FPGA中实现这些数字滤波器,我们可以滤除不必要的频率分量,保留所需的有用信号。

接下来,我们需要设计FPGA中的解调器。

解调器可以将FM调制信号恢复为原始的基带信号。

常用的FM解调方法有信号鉴频法和频率鉴别法。

基于FPGA与AD9854的宽带扫频信号源设计

b a s e d o n FPGA a nd AD9 8 5 4

Do n g J i a n j i n g Z h a n g Xi a o q i n g

( S c h o o l o f I n s t r u me n t a t i o n S c i e n c e a n d Op t o - e l e c t r o n i c s E n g i n e e r i n g , B e i j i n g I n f o r ma t i o n S c i e n c e a n d Te c h n o l o g y Un i v e r s i t y , B e i j i n g 1 0 0 1 9 2 , C h i n a )

V H DL , c o n t r o l l i n g l o g i c p r o g r a ms o f br o a d b a n d f r e q u e n c y - s we e p s o u r c e s y s t e m a r e d e s i g n e d a n d c o mp i l e d . Te s t r e s u l t s

b e e n a f o c u s o f r e s e a r c h i n r e c e n t y e a r s . Th i s p a p e r i n t r o d u c e s t h e b a s i c t h e o r y o f DDS a nd a n a l y s e s d e t a i l e d l y p r i nc i p l e o f f r e q u e n c y s we e p s i g n a l o u t p u t o f DDS c h i p AD9 8 5 4 i n Ra mp e d FS K mo d e . Cy e l o n e l I I EP3 C1 0 E1 4 4 C8 N F PGA o f Al t e r a

基于FPGA的数字信号处理系统设计与实现

基于FPGA的数字信号处理系统设计与实现数字信号处理(DSP)是对数字信号进行处理和分析的技术方法,广泛应用于通信、音频、图像等领域。

其中,利用可编程逻辑器件进行数字信号处理的算法加速已成为一种重要的技术趋势。

本文主要讨论基于FPGA(Field Programmable Gate Array)的数字信号处理系统的设计与实现。

一、FPGA的基础知识及特点FPGA是一种具有可编程逻辑和可编程连接的硬件器件,能够实现用户自定义的数字电路功能。

与固定功能的ASIC(Application-Specific Integrated Circuit)相比,FPGA具有灵活性强、开发周期短、成本低等优势。

在数字信号处理系统中,FPGA可以作为一种高性能的实现平台。

二、数字信号处理系统的基本框架数字信号处理系统通常包括信号的采集、预处理、算法处理和结果输出等步骤。

在FPGA上实现数字信号处理系统时,通常将这些步骤划分为不同的模块,并将其设计成可并行执行的结构,以提高系统的吞吐量和性能。

1. 信号采集与预处理信号采集模块通常用于将模拟信号转换成数字信号,并对其进行采样和量化处理。

预处理模块则用于滤波、降噪、增益控制等处理,以准备信号供后续的算法处理模块使用。

2. 算法处理算法处理模块是数字信号处理系统的核心,其中包括常用的信号处理算法,例如快速傅里叶变换(FFT)、数字滤波器、自适应滤波器等。

这些算法通常采用并行处理的方式,以提高系统性能。

3. 结果输出结果输出模块将经过处理的数字信号转换成模拟信号,并通过数字至模拟转换器(DAC)输出。

此外,还可以添加显示设备或通信接口,以直观地观察处理结果或将结果传输到其他设备。

三、基于FPGA的数字信号处理系统的设计流程基于FPGA的数字信号处理系统设计一般包括硬件设计和软件设计两个层面。

1. 硬件设计硬件设计主要包括系统的功能分析与规划、模块的设计与实现以及系统的验证与测试。

基于FPGA的通信系统设计

基于FPGA的通信系统设计随着信息技术的发展,通信系统的应用已经渗透到了我们生活的方方面面,从智能手机到物联网,从基站到卫星通信,通信系统无处不在。

如何设计高效、可靠的通信系统成为了通信领域的重要研究方向之一。

本文将探讨基于FPGA的通信系统设计,介绍FPGA的基本概念和通信系统的基础知识,同时结合实际案例,深入分析FPGA的在通信系统中的应用。

一、FPGA的基本概念FPGA是可编程逻辑门阵列(Field-Programmable Gate Array,简称FPGA)的缩写,是由可编程逻辑器件和可编程时钟、存储器等辅助电路组成的可编程集成电路。

与传统的专用集成电路相比,FPGA可以根据需要重复编程,适应不同的应用场景。

FPGA的优点在于其可以完成高速、高精度的数据处理和控制操作,同时具有较强的可靠性和抗干扰能力。

二、通信系统的基础知识通信系统是在信道传输介质上进行信息传输和交换的一种系统,包括发送端、接收端和传输介质。

通信系统的基本要素包括信号源、调制解调器、信道、接收器和信号处理器。

其中,调制解调器是将数字信号转换为模拟信号或者将模拟信号转换为数字信号的重要组成部分。

三、FPGA在通信系统中的应用FPGA在通信系统中的应用非常广泛,从通信协议的实现到信号处理的优化都有涉及。

下面将以LTE无线通信系统为例,介绍其FPGA在通信系统中的应用。

1. 通信协议的实现LTE是一种4G无线通信标准,其通信协议的实现需要高效、稳定的硬件支持。

FPGAs与硬件描述语言(HDL)结合可以实现高度定制化的硬件设计,并且可以通过高层次综合工具转化为可编程逻辑块和可编程时序。

FPGA实现的通信协议处理器可在保证性能和效率的同时保持灵活性,使其适应不同的协议标准。

2. 信号处理的优化FPGA可以对一些通信信号处理算法进行硬件实现,从而提高信号处理的效率和速度。

例如,在LTE中,可以采用FPGA实现高速傅里叶变换(FFT)算法,从而大大提高了LTE信号处理的速度,并且能够保证处理时间的稳定性和可靠性。

(完整word版)基于FPGA的数字通信系统报告

基于FPGA的数字通信系统设计指导老师:李东明项目负责人:何兴凯项目成员:杜川王光辉李莉玲摘要:设计并实现了了一种基于FPGA的片上数字通信系统。

系统主要由编译码模块,调制解调模块,频率合成模块,FIR数字滤波模块,位同步模块以及加密解密模块组成,由这些模块组成一个完整的通信系统片上系统。

一、项目背景在通信领域,尤其是无线通信方面,随着技术的不断更新和新标准的发布,通信系统也在朝着高速率,高质量,高可靠性等方向不断发展着。

但可以清楚地看到,当今动辄成百上千兆的数据流一股脑的涌进,任何一个高速数据传输系统的稳定性和安全性等方方面面都面临着极大的挑战,稍有考虑不周之处就会引起各种各样的问题,为了提高通信系统的稳定性,将系统构建在一个芯片的内部,即构建所谓的片上系统,应该可以大幅度提高系统的稳定性。

借助于通信原理以及EDA技术等课程的专业知识,设计了一个基于FPGA的数字通信系统,主要目的是在片上系统的设计思想指导下,设计并实现一个片上数字通信系统。

二、系统总体方案设计鉴于当前高速数字通信系统的设计方案大多是现场可编程门阵列(FPGA)加片外存储介质(SDRAM、SRAM、DDR等)的组合,本次设计方案同样采用这种组合方式,具体为一片FPGA、三片静态存储器(SRAM)和一片高速数据传输芯片。

FPGA具有管脚多、内部逻辑资源丰富、足够的可用IP核等优点,用作整个高速数字通信系统的控制核心极为合适,本方案中选用Altera公司的高性价比CycloneII系列FPGA芯片;静态存储用具有的一大优点就是数据读取速度快,且控制信号简单,易操纵,适用作高速数据存储介质,其处理速度和存储容量均满足系统设计的需要。

与传统的DSP(数据信号处理器)或DPP(通用处理器)相比,FPGA在某些信号处理任务中表现出非常强的性能,而单片机的处理也显然逊色很多。

以下为整体的系统流程图:图1 系统设计框图三、程序运行平台Quartus II 9.0;Nios II 9.0 IDE ;Alter SOPC Builder 等四、系统模块具体实现1、编译码模块:信源编码有两个基本功能:一是提高信息传输的有效性,二是模拟信号完成AD转换后,可以实现数字化传输。

基于FPGA的BPSK调制与解调器设计

基于FPGA的BPSK调制与解调器设计FPGA (Field-Programmable Gate Array)是一种可编程逻辑设备,能够实现数字电路的设计和实现。

BPSK(Binary Phase Shift Keying)是一种调制技术,常用于数字通信中。

本文将介绍如何基于FPGA设计一个BPSK调制与解调器。

首先,我们需要了解BPSK调制与解调的原理。

BPSK调制将二进制数据转换为正负的相位差异,其中“1”表示正相位,“0”表示负相位。

解调器则将接收到的信号解调为相应的二进制数据。

FPGA可以用于实现BPSK调制与解调器的设计,具有灵活性和高性能。

下面是一个简单的BPSK调制与解调器的设计流程:1.确定FPGA的型号和资源:根据设计需求,选择合适的FPGA型号和资源,包括逻辑门、片上存储器等,以满足设计要求。

2.信号生成与调制:使用FPGA内部的时钟信号生成器生成时钟信号,然后使用逻辑门实现二进制数据的生成。

通过相位控制电路,将生成的二进制数据转换为正弦波信号,实现BPSK调制。

3.发送信号:使用FPGA的GPIO引脚或其他输出接口将调制后的信号发送出去。

可以通过DAC芯片将数字信号转换为模拟信号,然后通过无线电频率调谐电路发送出去。

4.接收信号与解调:接收到的信号经过模拟前端的放大与滤波处理后,使用ADC芯片将模拟信号转换为数字信号。

接着,使用FPGA的GPIO引脚或其他输入接口将数字信号输入FPGA内部。

5.解调处理与数据恢复:使用FPGA的逻辑门实现解调处理过程,通过比较接收到的信号相位与参考信号相位的差异,恢复出原始数据。

可以使用时钟信号控制数据恢复过程,确保数据的完整性和准确性。

6.输出结果与数据处理:通过FPGA的GPIO引脚或其他输出接口将已解调的二进制数据输出。

可以使用逻辑门对输出数据进行处理,例如进行CRC校验等。

设计完成后,可以将设计好的FPGA程序烧录到FPGA芯片中,并通过测试与调试确保其功能正常。

基于fpga的信号采集电路设计

基于fpga的信号采集电路设计

FPGA作为一种可编程逻辑器件,在信号采集电路设计中具有很高的灵活性和自适应性。

以下是基于FPGA的信号采集电路设计的步骤和考虑因素:

1. 确定采集信号的类型和范围,包括采集的电压、频率和信号形态等。

这有助于选择合适的FPGA型号和外部接口芯片。

2. 设计硬件电路,包括ADC芯片、时钟电路、滤波器等。

这些硬件电路需要兼容FPGA,并能够提供稳定且可靠的信号采集。

3. 根据硬件电路设计,编写FPGA的硬件描述语言(HDL)程序,包括FPGA的驱动和控制程序。

这些程序需要能够将采集到的信号转换成数字信号,并将其存储在FPGA的内存中。

4. 对FPGA进行仿真和调试,验证电路的正确性和性能。

这包括对硬件电路的功能测试和对FPGA程序的逻辑测试等。

5. 将FPGA程序烧录到FPGA中,实现信号采集的实时处理和存储。

此外,可以将FPGA与其他计算机或控制器等设备进行连接,以实现更加复杂的信号处理和控制功能。

在设计基于FPGA的信号采集电路时,还需考虑以下因素:

1. 采样率和带宽:选择合适的ADC芯片和时钟电路,以满足采样率和带宽的要求。

2. 噪声和信号失真:设计适当的滤波和放大电路,以减小噪声和防止信号失真。

3. 存储和传输:根据实际需求,选择合适的存储器和接口芯片,以保证数据的可靠存储和传输。

4. 系统可靠性和稳定性:考虑系统的可靠性和稳定性,采用合适的电路保护和参数调节措施,以防止电路故障和系统失效。

5. 开发工具和环境:选择合适的FPGA开发工具和环境,以提高开发效率和降低制造成本。

基于FPGA的数字信号处理技术研究与设计

基于FPGA的数字信号处理技术研究与设计数字信号处理技术的发展日益深入,随着FPGA(Field Programmable Gate Array)的出现,数字信号处理技术的应用也得以不断拓展,因此,我们将基于FPGA探讨数字信号处理技术的相关研究与设计。

1. 基于FPGA的数字信号处理技术简介FPGA是一种可编程的集成电路。

它具有现场可编程性和高度灵活性,可以承担任何数字电路的任务。

数字信号处理技术是指将信号处理数字化,以实现信号的处理和传输。

它广泛应用于通讯、医疗、工控和汽车等领域。

2. 应用FPGA实现数字信号处理技术的优势2.1 高速度FPGA的可编程性可以使其在实现数字信号处理技术时具有很高的运行速度,适用于高速数据的处理。

2.2 灵活性强FPGA在设计时灵活性较强,可以根据不同的需求,不同的任务进行编程,使得其在数字信号处理的各个领域都可以得到广泛的应用。

2.3 可重构性强FPGA在设计过程中均为可编程电路。

根据不同的需要和电路的修改,FPGA 可以通过简单的修改程序或重构电路来重新配置。

3. 基于FPGA的数字信号处理技术研究与设计案例3.1 旋转速度计旋转速度计是一种普遍应用的传感器器件,可以用来测量液体、气体等的旋转速度或流量。

过去的旋转速度计大多利用着串行外设接口(SPI)进行通讯,外设接口在通讯时速度、带宽比较低,限制了旋转速度计测量速度。

基于FPGA的数字信号处理技术,可以实现高速率的旋转速度测量。

在这个案例中,一个基于FPGA的旋转速度计被设计出来,通过FPGA芯片的内部收发器(SERDES)实现高速并行通讯,从而提高了数字信号处理速度。

3.2自适应滤波器自适应滤波器是一种使用在信号处理中的数字滤波器。

在过去的自适应滤波器设计中,常常需要使用优化算法进行复杂的配置,这种滤波器应用在实时系统中需要耗费大量的时间,效率并不高。

所以,基于FPGA的数字信号处理技术,可以更好的解决这个问题。

基于FPGA的DDS信号发生器的设计与实现

基于FPGA的DDS信号发⽣器的设计与实现⼀、实现环境 软件:Quartus II 13.0 硬件:MP801⼆、DDS基本原理 DDS(Direct Digital Synthesizer)即数字合成器,是⼀种新型的频率合成技术,具有相对带宽⼤,频率转换时间短,分辨率⾼和相位连续性好等优点。

较容易实现频率、相位及幅度的数控调制,⼴泛应⽤于通信领域。

DDS的实现⽰意图如下图所⽰: 1、将需要合成的信号的数据存储在rom中,合成待输出信号的⽅法请参考: 2、dds_control实现的功能是将存储在rom中的待合成的信号的数据按照⼀定的规则取出来: dds_control主要由相位累加和频率累加来实现,简单的说,通过控制相位累加和频率累加来实现从rom中取出不同时刻的数据。

(1)相位累加器位数为N位(24~32),相位累加器把正弦信号在相位上的精度定义为N位,其分辨率位1/2N ,决定⼀个波形的起始时刻在哪个点; (2)频率累加器⽤来控制每隔⼏个点从rom中取⼀个数据,决定⼀个波形的频率; (3)若DDS的时钟频率为F clk ,频率控制字fword = 1,则输出频率为 F out = F clk/2N,这个频率相当于“基频”,若fword = B,则输出频率 F out = B * F clk/2N。

因此理论上由以上三个参数就可以得出任意的 f o 输出频率,且可以得出频率分辨率由时钟频率和累加器的位数决定的结论。

当参考时钟频率越⾼,累加器位数越⾼,输出频率分辨率就越⾼。

3、从FPGA中出来的信号都是数字信号(dds_control输出的信号都为数字信号),需要通过dac芯⽚来将数字信号转换为模拟信号,这样将dac芯⽚输出的信号接⼊到⽰波器中,才能看到波形; 4、举例说明频率控制和相位控制: 如上图所⽰,这个是⼀个由33个点构成的正弦波信号,(rom_addr,rom_data),纵坐标为存储在rom中的正弦波信号,横坐标为dds_control ⽣成的地址信号。

毕业设计(论文)-基于fpga的函数信号发生器的设计与实现[管理资料]

![毕业设计(论文)-基于fpga的函数信号发生器的设计与实现[管理资料]](https://img.taocdn.com/s3/m/e1d8101a81c758f5f61f67f8.png)

基于FPGA的函数信号发生器的设计与实现摘要波形发生器己成为现代测试领域应用最为广泛的通用仪器之一,代表了信号源的发展方向。

直接数字频率合成(DDS)是二十世纪七十年代初提出的一种全数字的频率合成技术,其查表合成波形的方法可以满足产生任意波形的要求。

由于现场可编程门阵列(FPGA)具有高集成度、高速度、可实现大容量存储器功能的特性,能有效地实现DDS技术,极大的提高函数发生器的性能,降低生产成本。

本文首先介绍了函数波形发生器的研究背景和DDS的理论。

然后详尽地叙述了用FPGA完成DDS模块的设计过程,接着分析了整个设计中应处理的问题,根据设计原理就功能上进行了划分,将整个仪器功能划分为控制模块、外围硬件、FPGA器件三个部分来实现。

最后就这三个部分分别详细地进行了阐述。

本文利用Altera的设计工具QuartuSH并结合VeI’i1og一HDL语言,采用硬件编程的方法很好地解决了这一问题。

论文最后给出了系统的测量结果,并对误差进行了一定分析,结果表明,,、三角波、锯齿波、方波,通过实验结果表明,本设计达到了预定的要求,并证明了采用软硬件结合,利用FPGA技术实现波形发生器的方法是可行的。

关键词:函数发生器,直接数字频率合成,现场可编程门阵列The Design and Realize of DDS Based on FPGAAbstractArbitrary Waveform Generator(AWG) is one of the most popular instruments in modern testing domains,Which represents the developing direction of signal sources· Direct Digital frequency Synthesis(DDS) advance dearly in full digital technology for frequency synthesis,its LUT method for synthes waveform .Adapts togenerate arbitrary Waveform· Field programable GateArray(FPGA)has the feature sof Iargeseale integration,high working frequency and ean realize lal’ge Memory,50FPGAeaneffeetivelyrealizeDDS.The of Corporation Altera ehosen to do the main digitalProcessing work,which based on its large sale and highs Peed. The 53C2440MCU ehosenasa control ehip· Inthisdesign,how to design the fpga chip and theInter faee between the FPGA and the control ehiP the the method ofSoftware and hardware Programming,the design used the software Quartus11 and languageverilog一HDL solves ,the PrineiPle of DDS and Basis of EDA technology introdueed Problem is the design are analyzed and the whole fun into three Parts:masterehiP,FPGA deviee and PeriPheral three Parts are described indetail disadvantage and thing sneed toadv anceareal Of the dissertation,or asquare wave with in the frequency rangeto20MHz .Planed and the way to use software and hardware Programming method and DDS Technology to realize Functional Waveform Generatoravailable.Keywords:DDS;FPGA;Functional Waveform Generator目录第一章绪论 ................................................ IV ............................................................................................................... IV ................................................................................................................. V ......................................................................................................... V....................................................................................................... VI .............................................................................................................. VII ...................................................................................................... VIIDMA输出方式.......................................................................... VII...................................................................................................... VII..................................................................................................... V III 第二章直接数字频率合成器的原理及性能 ................................................ I .................................................................................................................. I .......................................................................................................... I......................................................................................................... I I DDS原理 ............................................................................................. I II 第三章基于FPGA的DDS模块的实现 .......................................................... I (FPGA)简介 ............................................................................................. I II软件并建立工程 ....................................................................... I I新建Block Diagram/Schematic File并添加模块电路。

基于FPGA的数字信号发生器设计

基于FPGA的数字信号发生器设计摘要数字信号发生器是数字信号处理中不可缺少的调试设备,在生产生活中的应用非常广泛。

本文所设计的内容就是基于Altera公司的现场可编程门阵列(FPGA)实现数字信号发生器的设计,FPGA具有密度高,功耗低,体积小,可靠性高等特点,设计时可以不必过多考虑具体硬件连接;本设计中应用VHDL硬件描述语言进行描述,使该数字信号发生器可以产生正弦波、方波、三角波、锯齿波四个独立的波形,并能对所产生的四种波形的频率和幅度进行调节。

关键词:直接数字频率合成;数字波形发生器;FPGA;DDS;VHDLDesign Of FPGA-based Digital Signal GeneratorYang Chunjian(College of Physics Science and Information Engineering, Jishou University,Jishou Hunan 416000)AbstractDigital signal transmitter as a test facility is an important part of information processing system. In the production of a wide range of application of life. This content is designed by Altera, based on field programmable gate array (FPGA) design of digital signal generator, FPGA has a high density, low power consumption, small size, high reliability, can not have too much to consider wher designing specific hardware connection; the design of the application of VHDL hardware description language to describe, so that the digital signal generator can produce sine, square, triangle, sawtooth waveforms of four independent,and is able to produce four waveforms by the frequency and amplitude adjustment.Key words:Direct Digital Frequency Synthesis;Digital Waveform Generator; FPGA;DDS;VHDL目录第一章绪论 (1)1.1 背景与意义 (1)1.2 国内外发展现状 (1)第二章相关工具介绍 (3)2.1 DDS技术 (3)2.2 FPGA简介 (4)2.3 VHDL简介 (5)2.4 QuartusⅡ简介 (7)第三章系统硬件电路设计 (9)3.1 数字信号发生器的系统组成 (9)3.2 设计原理及要求 (9)3.3 输入部分 (10)3.3.1频率、幅值和波形转换部分 (10)3.3.2系统时钟电路 (12)3.3.3 电源电路的设计 (12)3.4 FPGA部分 (12)3.5 D/A转换部分 (13)3.5.1 DAC0832转换器简介 (14)3.6 滤波电路 (15)第四章系统软件设计 (17)4.1软件系统流程图 (17)4.2 数字信号发生器的软件设计 (17)4.2软件各模块 (18)4.2.1 主控制模块 (18)4.2.2 波形数据产生模块 (19)结束语 (23)参考文献 (24)附录 (25)第一章绪论1.1 背景与意义在电子技术领域,常常需要波形、频率、幅度都可调的电信号,用于产生这种电信号的电子仪器称作信号发生器。

基于FPGA的高速数字信号处理系统设计与实现

基于FPGA的高速数字信号处理系统设计与实现随着时代的进步和科技的发展,数字信号处理(Digital Signal Processing,简称DSP)在各个领域中扮演着重要角色。

而FPGA (Field Programmable Gate Array)作为一种强大的可编程逻辑器件,已经被广泛应用于高速信号处理系统中。

本文将探讨基于FPGA的高速数字信号处理系统的设计与实现。

1. 引言高速数字信号处理系统在实时性和处理速度方面要求较高。

传统的通用处理器往往无法满足这些需求,而FPGA的并行处理能力和灵活性使其成为处理高速数字信号的理想选择。

本文将着重讨论FPGA系统的设计和实现。

2. FPGA基础知识2.1 FPGA原理FPGA是一种可编程逻辑器件,由大量的可编程逻辑单元和存储单元构成。

通过编程可以实现逻辑门、存储器和各种电路。

FPGA的可重构性使得其适用于不同的应用领域。

2.2 FPGA架构常见的FPGA架构包括查找表(Look-up Table,简称LUT)、寄存器和可编程互连网络。

LUT提供逻辑功能,寄存器用于数据存储,而可编程互连网络则实现不同逻辑单元之间的连接。

3. 高速数字信号处理系统设计3.1 系统需求分析在设计高速数字信号处理系统之前,需要明确系统的需求和目标。

这可能包括处理速度、资源利用率、功耗等方面的要求。

3.2 系统架构设计基于FPGA的高速数字信号处理系统的架构设计是关键步骤之一。

需要根据系统需求和目标来选择合适的算法和硬件结构。

可以采用流水线结构、并行处理结构等以提高处理速度。

3.3 硬件设计硬件设计包括选择FPGA器件、选择合适的外设、设计适配电路等。

通过合理的硬件设计可以实现信号处理系统的高速和稳定运行。

4. 实现与验证4.1 FPGA编程使用HDL(Hardware Description Language)进行FPGA编程。

常用的HDL语言包括VHDL和Verilog。

基于FPGA的高性能数字信号处理系统设计

基于FPGA的高性能数字信号处理系统设计随着数字信号处理技术的发展,数字信号处理系统在通信、雷达、生物医学、图像处理等领域中得到了广泛应用。

而FPGA技术则因其高性能、可编程性和可重构性成为数字信号处理系统中的重要组成部分。

本文将从以下几个方面阐述基于FPGA的高性能数字信号处理系统设计,包括FPGA架构、数字信号处理算法、系统级设计方法和应用案例。

FPGA架构FPGA(Field Programmable Gate Array)是一种基于现场可编程的硬件逻辑芯片。

FPGA内部由可编程逻辑单元(PL)、内存单元(BRAM)和数字信号处理单元(DSP)等模块组成,可以实现数字信号处理和数据通路等复杂的逻辑功能。

FPGA架构的选择对数字信号处理系统的性能和功耗有很大的影响。

通常选择的FPGA架构有两种:面向计算型的FPGA和面向通信型的FPGA。

其中,面向计算型的FPGA适用于高性能计算应用,提供高速的时钟频率和大量的计算资源;而面向通信型的FPGA适用于高速数据通信应用,能够提供高速的数据传输和处理效率。

数字信号处理算法数字信号处理算法是数字信号处理系统的核心部分,其主要任务是实现输入信号的特定操作,例如通信领域的调制、解调、信道编码和解码,图像处理领域的滤波、变换和分割等。

不同的数字信号处理算法对FPGA内部资源的需求也不同。

为了实现高性能的数字信号处理,使用一些常见的优化方法也是必不可少的。

如采用低复杂度算法、算法设计的并行化等方法,可以降低算法的时间和空间复杂度,从而提升系统的性能。

系统级设计方法在数字信号处理系统设计中,系统级设计方法是至关重要的。

系统级设计旨在将不同模块的功能组合起来,并通过优化系统架构、分配资源,以实现数字信号处理任务。

常用的系统级设计方法包括时序分析、时序优化、布局和布线等。

时序分析可帮助设计人员识别电路中的时序约束,从而避免电路时序问题。

时序优化则是通过合理的资源分配和时钟树设计来优化时序关系。

基于FPGA和AD768的高精度多路信号源设计

至几十 / ( 2 与采样 保 持 电容 取值 和信 号峰 峰值 相 关 ) s , 所 以输 出信 号频 率较 低 , 于 D S原 理生成 的方波信 基 D 号 的上 升沿 和下 降沿 时 间取 决 于采样 时 间 ,显 然不能 满 足设 计要 求 。为此 ,提 出了 以下实 现方 案 。 该 信 号源 由 F GA 作 为主控 单元 , P 通过 L VDS芯

*国 家 自然 科 学基 金 资助 项 目 (0 7 2 0 AA0 Z 2 ) 4 3 1 收 稿 日期 :2 0 —51 ;修 回 日期 :2 0 —81 0 90 ~3 0 90— 3

为实现信号 的高精度输 出,必须选用分辨率高的 D AC,本文采用 AD7 8 6 ,它具有 1 的分 辨率 ,理论 6位 精度 为1 2 / 一o 0 2 , . 0 能够满足 0 0 精度 的设计要 .1

中 图 分 类 号 :TN9 4 1 1 . 文 献 标 识 码 :A

O 引 言

信 号 源设计 常常采 用 多路模 拟复 用器 结合 采样 保 持 电路 实 现多路 信号 输 出 , 由于采 样 时间需要 几 s 甚

信号 源 作 为一 种 电子测 量 和计量 设备 ,通 常 可产

生 大量 的标 准信号 和用 户定 义信 号 。 由于它具 有 高精

成 自动测 试 系统 。在各 种实 验应 用和 测试 处理 中 ,既 可 根据使 用 者的要 求 ,将信 号源 作为激 励 源来仿 真 各

种测 试信 号并 提供 给被 测 电路 ,以满 足测 量或 各种 实 际需 要 ,也 可作为 一种 测量 仪器来 完 成一定 的测试 功 能 。本 文介 绍 的信 号 源 即采 用 F GA 与 AD7 8结 合 P 6 实 现高精 度信 号输 出,该方 法具 有结 构简单 、配 置灵 活 、 出信号 精度 高 的特点 , 输 可用 于对 存储 测试 系统 、

信号源FPGA概要设计20100528

信号源系统FPGA概要设计北京阿格思科技有限公司2010-4-11目录:信号源系统FPGA概要设计 (1)1. 系统简要说明 (4)1.1 设计目的 (4)1.2 设计平台 (4)1.3 设计输入输出及参考文档 (4)1.4 系统框图及工作模式说明 (4)1.4.1 整体系统框图描述 (4)1.4.2整体系统时钟域分析 (6)1.4.3整体系统顶层外端口定义 (7)1.4.4 系统工作模式描述 (8)1.5 设计指标 (11)1.6 系统资源消耗评估 (11)2. 主机接口模块功能详细描述 (12)2.1 基本规格描述 (12)2.2主机接口模块端口信号描述 (12)2.3 状态机描述 (13)2.4 主要输入输出信号规格描述 (16)3. FLASH接口模块功能详细描述 (19)3.1基本规格描述 (19)3.2 信号描述 (20)3.3 状态机描述 (21)3.4 主要输入输出信号规格描述 (21)4. 外存接口模块功能详细描述 (21)4.1基本规格描述 (21)4.2 IP信号及整体外存模块层次描述 (22)4.2.1 IP接口信号 (22)4.2.2外存模块整体框图 (24)4.3 状态机描述 (24)4.4 主要输入输出信号规格描述 (29)5. 数据输出接口模块功能详细描述 (32)5.1基本规格描述 (32)5.2 信号描述 (34)5.3 状态机描述 (37)5.4 主要输入输出信号规格描述 (38)1. 系统简要说明1.1 设计目的为实现在FCT200-HD系统中,完成对于不同厂家与不同类型的数字电视主板测试的测试信号驱动。

1.2 设计平台使用ISE11.4开发环境,使用Verliog语言进行设计。

1.3 设计输入输出及参考文档设计输入:《FCT200-HD平台信号源系统概要设计》。

设计输出:指导详细FPGA逻辑设计。

1.4 系统框图及工作模式说明1.4.1 整体系统框图描述下图为系统总体框图(数字部分):下图为系统总体框图(模拟部分):1.4.2整体系统时钟域分析●模拟部分时钟域1.4.3整体系统顶层外端口定义系统顶层TOP外端口信号定义:1.4.4 系统工作模式描述FPGA内部有以下3种主要工作模式:A.数据下载模式数据下载模式是指在外部主机的控制下,将图形数据文件下载到FLAH芯片中。

基于FPGA的GM4943A雷达信号源设计

84M i c r o c o n t r o l l e r s &E m b e d d e d S ys t e m s 2021年第6期w w w .m e s n e t .c o m .c n基于F P G A 的G M 4943A 雷达信号源设计陈坤1,穆仕博2,潘亮1,3(1.中国空空导弹研究院,洛阳471009;2.驻中国空空导弹研究院军事代表室;3.航空制导武器航空科技重点实验室)摘要:本文在研究国产四通道雷达信号源芯片GM 4943A 的工作机理和内部寄存器操作的基础上,基于F P G A 技术其及信号源控制模块,并在V i v a d o 16.2软件环境中进行软件编程和设计实现㊂测试结果表明,该雷达信号源模块具有频率㊁相位和幅度可调可控的能力,具有数字化高分辨率㊁高稳定㊁大带宽和快速切换等特点,基本满足工程应用需求,对雷达信号源的开发设计具有一定参考价值㊂关键词:D D S 技术;GM 4943A ;F P G A 技术;雷达信号源中图分类号:T P 333 文献标识码:AD e s i g n o f G M 4943A R a d a r S i gn a l S o u r c e B a s e d o n F P G A C h e n K u n 1,M u S h i b o 2,P a n L i a n g1,3(1.C h i n a A i r b o r n e M i s s i l e A c a d e m y ,L u o y a n g 471009,C h i n a ;2.C h i n a M i l i t a r y R e pr s e n t a t i v e O f f i c e i n C h i n a A i r b o r n e M i s s i l e A c a d e m y ;3.A v i a t i o n K e y L a b o r a t o r y o f S c i e n c e a n d T e c h n o l o g y o n A i r b o r n e G u i d e d W e a po n )A b s t r a c t :B y s t u d y o f t h e w o r k i n g m e c h a n i s m a n d i n t e r n a l r e g i s t e r o p e r a t i o n o f t h e d o m e s t i c f o u r -c h a n n e l r a d a r s i g n a l s o u r c e c h i pGM 4943A ,a s i g n a l s o u r c e c o n t r o l m o d u l e i s d e s i gn e d w i t h t h e V i v a d o 16.2s o f t w a r e e n v i r o n m e n t b a s e d o n F P G A.T h e t e s t r e s u l t s s h o w t h a t t h e r a d a r s i g n a l s o u r c e m o d u l e h a s t h e a d j u s t a b l e a n d c o n t r o l l a b l e c a p a b i l i t y o f f r e q u e n c y ,p h a s e a n d a m pl i t u d e ,a n d h a s t h e c h a r a c -t e r i s t i c s o f d i g i t a l h i g h r e s o l u t i o n ,h i g h s t a b i l i t y ,l a r g e b a n d w i d t h a n d f a s t s w i t c h i n g ,w h i c h b a s i c a l l y m e e t s t h e n e e d s o f e n g i n e e r i n g a p p l i -c a t i o n a n d h a s c e r t a i n r e f e r e n c e v a l u e f o r t h e d e v e l o p m e n t a n d d e s i g n o f r a d a r s i gn a l s o u r c e .K e yw o r d s :D D S t e c h n o l o g y ;GM 4943A ;F P G A t e c h n o l o g y ;r a d a r s i g n a l s o u r c e 0 引 言信号发生器也称为信号源,其输出信号类型有正弦波㊁函数信号㊁调制信号等,常采用频率合成技术进行设计㊂频率合成技术[1]的发展大致经历了三个阶段:第一阶段是直接模拟合成技术,它是利用一个或多个不同的晶振作为基准信号源,经过混频㊁倍频㊁低通滤波等电路调理后,产生需要的离散频率,输出信号具有稳定的优点,不过信号频率低㊁形式单一,同时调试难度大;第二阶段是间接锁相环频率合成技术,主要利用模拟锁相环路实现频率合成,具有方便调试的优点,不过信号频率切换速度较慢;第三阶段是直接数字频率合成技术,实现了数字化控制相位㊁频率和幅度,产生信号具有频率高㊁任意波形㊁频率分辨率高㊁快速频率转换㊁相位连续等优点㊂本文利用国产的D D S 芯片,采用F P G A 技术[2]设计实现雷达信号源㊂1 G M 4943A 芯片简介1.1 性 能GM 4943A [3]作为一款具有4个通道超宽带的信号源,在雷达信号处理领域有广泛应用㊂作为一款成熟的国产化D D S 芯片,具有丰富的功能,内部包括4路独立的D D S 通道,每路有独立的相位㊁频率和幅度控制,支持线性扫描㊁非线性扫描㊁频率键控㊁相位键控㊁幅度控制和R AM 扫描等功能㊂1.2 功 能GM 4943A 主要实现单频点信号产生㊁信号调制以及多种模式的扫频信号产生㊂内部集成D D S _C O R E 电路,采用两路并行的结构以降低芯片功耗㊂D D S _C O R E 电路内主要有串行S P I 接口㊁配置寄存器㊁线性扫描模块㊁R AM 相关模块㊁D A C 模块等㊂1.3 D D S 原理直接数字频率合成技术D D S (D i r e c t D i g i t a l S yn t h e -s i z e r),是利用奈奎斯特采样定理把一系列数字信号通过D /A 转换器转换为模拟信号,即数字化控制频率㊁相位和幅度㊂通过配置寄存器,D D S _C O R E 实现控制逻辑产生频率㊁相位和幅度,进而输出相应正弦波形㊂D D S _C O R E基本结构如图1所示㊂敬请登录网站在线投稿(t o u ga o .m e s n e t .c o m.c n )2021年第6期85图1 D D S _C O R E 基本结构f 0=f s ˑFTW /248(1)P h a s e =360ˑP OW /216(2)A m=A m a x ˑAS F /214(3)式中,f 0㊁P h a s e 和A m 分别表示输出波形的频率㊁相位和幅度,F TW ㊁P OW 和A S F 分别表示频率字㊁相位字和幅度字,f s 和A m a x 分别表示系统时钟频率和输出波形最大幅度值㊂1.4 工作模式D D S _C O RE 工作时,根据产生频率控制字㊁相位控制字和幅度控制字的方式不同,芯片的工作模式大致可分为如下6种:单频点模式;使用外部I /O 接口直接调频模式;键控模式;线性扫描调试模式;分段式非线性扫描调制模式;R AM 扫描模式㊂当GM 4943A 工作于以上任何一种模式时,均可开启混频功能,实现第二奈奎斯特带信号的输出,芯片D A C 频谱特性如图2所示㊂图2 D A C 频谱特性2 硬件及软件设计作为一款功能强大的雷达信号产生芯片,在雷达信号领域具有广泛应用㊂基于中频信号的应用需求,设计产生4通道的线性调频信号[5],信号波形要求如下:通道一:从f 1频点向上扫描10MH z㊂通道二:从f 1频点向下扫描10MH z㊂通道三:从f 2频点向上扫描10MH z㊂通道四:从f 2频点向下扫描10MH z ㊂注意:f 1和f 2为两个中心频点㊂2.1 硬件设计本文将F P G A 作为主控芯片,采用8线S P I 接口配置GM 4943A 芯片的工作模式及其相应寄存器㊁相应电源转换芯片,提供GM 4943A 工作所需要的1.2V 和2.5V 电压㊂2.2 软件设计GM 4943A 支持线性扫描和分段式非线性扫描[3],其中分段式非线性扫描由4段线性扫描组合而成,每段线性扫描有相应的起始频率㊁终点频率㊁扫描率㊁扫描步进以及扫描控制方式等,实现的扫描方式有C h i r p 扫描㊁正三角扫描㊁上斜三角扫描㊁下斜三角扫描以及任意方向扫描㊂扫描模式的功能寄存器配置如表1所列㊂表1 扫描模式的功能寄存器配置S w e e p_m o d e [2:0]扫描方式000任意方向扫描001上斜三角扫描010下斜三角扫描011正三角扫描100C h i r p 扫描注:其中下斜三角扫描时,注意频率字配置寄存器一定按照顺序设置,否则不能产生向下线性调频信号㊂扫描率取决于扫描定时控制寄存器(s w e e p _r a m pr a t e S R R ),确定相邻两扫描点变化的时间间隔㊂扫描时间间隔由式t =S R RˑT s w e e p 决定,T s w e e p 为扫描定时器时钟周期,与系统时钟的关系为f s w e e p =f s y s _c l k /8,即系统时钟八分频㊂S R R 为扫描定时控制寄存器中的16位配置字,可分为向上扫描定时控制字S R R 0和向下扫描定时控制字S R R 1,分别控制上斜/下斜扫描的间隔时间㊂扫描步进取决于扫描步进寄存器,提供扫描的步进量,在扫描率定时器配置的时间间隔下,扫描累加器一次累加一个步进值,可分为向上扫描步进寄存器D F TW 0和向下扫描步进寄存器D F TW 1,分别控制上斜/下斜的扫描步进㊂以上斜三角扫描为例,其配置步骤如下:①配置m o d e 寄存器为100;②配置s w e e p_m o d e 寄存器为001;③配置F TWO ㊁F TW 1㊁D F TW 0㊁D F TW 1㊁S R R 0寄存器;④初始化P S X _0为0值;86M i c r o c o n t r o l l e r s &E m b e d d e d S ys t e m s 2021年第6期w w w .m e s n e t .c o m .c n⑤提供I O _U P D A T A 脉冲信号;⑥P S X _0为高电平时,则启动向上扫描㊂若扫描功能r e t u r n _z e r o 开启,则扫描完成后频率字累加器和相位累加器自动清零,即0频0相输出;若c o n -t i n u e 开启,则自动重新扫描;若扫描功能r e t u r n _s t a r t 开启,则自动恢复到起始频率并输出;若扫描功能s t a y _e n d 开启,则保持终点频率并输出㊂设计中,考虑数字化会导致输出波形掺杂着大量的杂散信号[5],为获得较干净的频谱输出,采取下列方式进行优化设计:a .合理选择输出频段,一般选择时钟频率的1/4~1/3,且输出频段尽量窄;b .输出频点避免如f s y s _c l k /3㊁f s y s _c l k /4㊁f s y s _c l k /5等整数分之输入参考系统时钟频率附近㊂如b 中f s ys _c l k /n 谐波的引入会引起假信号,分析带宽中应避免㊂2.3 设计实现基于以上软硬件设计,在V i v a d o 16.2软件开发环境中,针对芯片GM 4943A 设计实现雷达信号源控制模块㊂设计中采用有限状态机技术,利用V H D L 语言编写雷达信号源控制模块文件,其中有限状态机涉及的程序流程状态有:初始化/工作模式/模式参数生成/总线传输及配置和波形输出等状态,程序流程如图3所示㊂图3 雷达信号源控制模块程序流程图3 实验测试经过调试,该系统可达到预计的设计需求,实现了4通道频率㊁相位和幅度的可调可控线性调频波形输出㊂图4为不同通道的同相调制,图5为生成的线性调频信号㊂设计中采用的系统时钟频率为1.2G H z ,则该系统的时钟分辨率为4.26ˑ10e (-6)H z ,相位分辨率为0.0055ʎ;同时,为避免分析带宽中的时钟谐波,系统响应时间及切换时间采用了最精确扫描时间,即T s w e e p 约为6.67n s㊂图4不同通道的同相调制图5 线性调频信号4 结 语本文基于F P G A 技术和D D S 芯片GM 4943A ,利用V H D L 语言设计实现一个具有4通道频率㊁相位和幅度可调可控的信号发生器㊂测试结果表明,该设计得到的信号发生器能够实现频率精度高㊁波形质量好和频带范围宽的线性调频信号波形,满足课题的工程应用需要,具有国产化应用的借鉴价值㊂参考文献[1]郑朋伟.基于A D 9957的款第信号发生器的设计与实现[D ].西安:西安电子科技大学,2018.[2]梁状.基于D D S 的高频函数信号发生器设计与实现[D ].哈尔滨:哈尔滨理工大学,2018.[3]成都振芯科技股份有限公司.GM 4943A 四通道2.5G S P S 超宽带雷达信号源,2017.[4]卓康.基于D D S 的复杂雷达信号发生器设计[D ].成都:电子科技大学,2017.[5]王韧.基于D D S 的高性能雷达信号发生器的设计与实现[D ].西安:西安电子科技大学,2017.陈坤,主要研究方向为雷达导引头信号处理设计及开发和质量工程等;潘亮(工程师),主要研究方向为雷达导引头信号处理嵌入式系统开发及航空电子设备总线嵌入式设计㊂通信作者:潘亮,ji l e r c o m -e r @163.c o m ㊂(责任编辑:薛士然 收稿日期:2020-12-07)。

一种低复杂度数字互相关器的设计及其fpga实现

一种低复杂度数字互相关器的设计及其fpga实现

一种低复杂度数字互相关器的设计及其FPGA实现是一个比

较有用的设计,它主要用于对数字信号进行精准的计算和处理。

该设计主要包括一个输入多路复用器、一个滤波器、一个

FIFO缓冲器和用于计算和处理的核心部分。

输入多路复用器

可以将多个输入信号源进行分开处理,并将各个信号源分别进行分割和处理,以便与其他信号做精确的计算和处理。

滤波器也可以用于有效地去噪,使得计算结果更加可靠和精确。

FIFO缓冲器则可以将所有的输入信号的计算结果进行分类和

存储,以备后续使用。

而核心部分则是将输入信号应用复数运算,并将复数运算结果进行幅度和相位转换,以取得最终的结果。

要在FPGA上实现这种低复杂度数字互相关器,我们首先要

使用模块化编程,将所有的组件都分解成小块,然后采用高度可配置的方式来实现各个组件的定制,以便较好地组合和完成计算和处理。

其次,我们可以使用基于低维数字逻辑的设计方案,将这些小的组件通过一定的数字逻辑组合起来,这样就能实现设计思想所蕴涵的函数。

最后,在FPGA中最重要的就

是要考虑系统的吞吐率问题,这可以通过改变设计中各个组件的运行时间来实现,以得到最大容量的处理能力。

总之,一种低复杂度的数字互相关器的设计以及在FPGA中

的实现要用到模块化编程、低维数字逻辑和合理的系统吞吐率配置,以进一步提高处理的效率,使得设计的函数能够以更快的速度达到预期的效果。

基于FPGA和AD768的高精度多路信号源设计

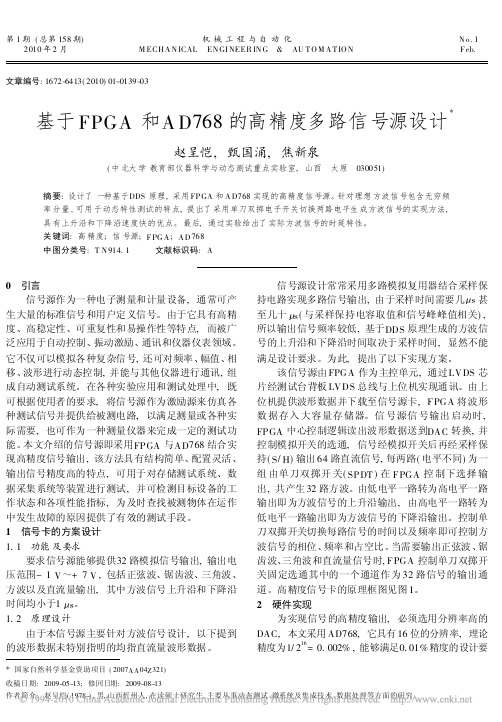

第1期(总第158期)2010年2月机械工程与自动化M ECHA N ICAL EN GI NEER IN G & AU T O M A T IO N N o.1F eb.文章编号:1672-6413(2010)01-0139-03基于FPGA 和A D 768的高精度多路信号源设计*赵呈恺,甄国涌,焦新泉(中北大学教育部仪器科学与动态测试重点实验室,山西 太原 030051)摘要:设计了一种基于DDS 原理,采用FP GA 和A D768实现的高精度信号源。

针对理想方波信号包含无穷频率分量、可用于动态特性测试的特点,提出了采用单刀双掷电子开关切换两路电平生成方波信号的实现方法,具有上升沿和下降沿速度快的优点。

最后,通过实验给出了实际方波信号的时延特性。

关键词:高精度;信号源;F PG A ;A D 768中图分类号:T N 914.1 文献标识码:A*国家自然科学基金资助项目(2007AA 04Z 321)收稿日期:2009-05-13;修回日期:2009-08-13作者简介:赵呈恺(1978-),男,山西忻州人,在读硕士研究生,主要从事动态测试、微系统及集成技术、数据处理等方面的研究。

0 引言信号源作为一种电子测量和计量设备,通常可产生大量的标准信号和用户定义信号。

由于它具有高精度、高稳定性、可重复性和易操作性等特点,而被广泛应用于自动控制、振动激励、通讯和仪器仪表领域。

它不仅可以模拟各种复杂信号,还可对频率、幅值、相移、波形进行动态控制,并能与其他仪器进行通讯,组成自动测试系统。

在各种实验应用和测试处理中,既可根据使用者的要求,将信号源作为激励源来仿真各种测试信号并提供给被测电路,以满足测量或各种实际需要,也可作为一种测量仪器来完成一定的测试功能。

本文介绍的信号源即采用FPGA 与AD 768结合实现高精度信号输出,该方法具有结构简单、配置灵活、输出信号精度高的特点,可用于对存储测试系统、数据采集系统等装置进行测试,并可检测目标设备的工作状态和各项性能指标,为及时查找被测物体在运作中发生故障的原因提供了有效的测试手段。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

课程设计(论文)说明书题目:基于FPGA的数字信源设计院(系):信息与通信学院专业:学生姓名:学号:指导教师:职称:讲师2011年12 月1 日摘要设计一个基于FPGA的数字信源,首先简要介绍了单极性非归零码、双极性非归零码、单极性归零码、双极性归零码,然后根据码型转换原理设计发生器模块。

由于EDA 技术可以简化电路,集成多块芯片,减小电路体积,所以程序采用Verilog硬件描述语言进行描述,并用quartus II软件仿真实现所有功能,最后将功能集成到FPGA上,并设计电路、制作实物,产生的基带码稳定、可靠,可满足不同数字基带系统传输需要。

关键词:数字信源;数字基带码;EDA;V erilog;FPGAAbstractFPGA-based design a letter-number generator with, first of all we briefly introduce unipolar NRZ code, bipolar NRZ, Unipolar zero yards code, bipolar zero yards code, differential code , alternating polarity code, phase code, code-reversal, and third-order high-density bipolar codes etc. Then we design generator module under the code-conversion design principles. As EDA technology can make circuit simple, integrate multiple chips, reduce the size of circuits, so we take advantage of VHDL to describe it and use quartus II software to simulate .Finally we integrate all the fetures into the FPGA, and design circuit to generate stable and reliable base-band code to meet the different base-band digital transmission system needs.Key words:Digital signal source;digital base-band code; EDA; Verilog; FPGA目录引言 (1)1 理论分析 (2)1.1 数字基带信号的码型设计原则....................................................... 错误!未定义书签。

1.2 非归零码(NRZ码) ........................................................................... 错误!未定义书签。

1.2.1 单极性............................................................................................ 错误!未定义书签。

1.2.2 双极性 (2)1.3 归零码(RZ码) (2)1.3.1 单极性 (3)1.3.2 双极性 (3)1.4 总体组成框图 (3)2 数字信源的硬件与软件设计 (5)2.1 码元产生电路的设计 (5)2.2 CPLD最小系统的设计 (5)2.3 基带信号产生电路的设计 (6)2.4系统软件设计 (8)3 电路板的制作与调试 (11)3.1 电路板的制作 (11)3.2 电路板的调试 (12)4 总结 (14)谢辞 (15)参考文献 (16)引言FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。

它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

FPGA采用了逻辑单元阵列LCA(Logic Cell Array)这样一个概念,内部包括可配置逻辑模块CLB(Configurable Logic Block)、输出输入模块IOB(Input Output Block)和内部连线(Interconnect)三个部分。

现场可编程门阵列(FPGA)是可编程器件。

与传统逻辑电路和门阵列(如PAL,GAL及CPLD器件)相比,FPGA具有不同的结构,FPGA利用小型查找表(16×1RAM)来实现组合逻辑,每个查找表连接到一个D触发器的输入端,触发器再来驱动其他逻辑电路或驱动I/O,由此构成了既可实现组合逻辑功能又可实现时序逻辑功能的基本逻辑单元模块,这些模块间利用金属连线互相连接或连接到I/O模块。

FPGA的逻辑是通过向内部静态存储单元加载编程数据来实现的,存储在存储器单元中的值决定了逻辑单元的逻辑功能以及各模块之间或模块与I/O间的联接方式,并最终决定了FPGA所能实现的功能,FPGA允许无限次的编程.数字基带信号,是信源发出的、未经调制或频谱变换、直接在有效频带与信号频谱相对应的信道上传输的数字信号,是消息代码的电波形,是用不同的电平或脉冲来表示相应的消息代码。

数字基带信号的类型很多,常见的有矩形脉冲,三角波、高斯脉冲和升余弦脉冲等。

最常用的是矩形脉冲,因为矩形脉冲易于形成和变换。

数字基带信号是数字信息的一种表现形式,被用于数字基带传输系统。

可以用不同电压或电流的代码来表示基带码。

不同形式的基带码具有不同的频谱结构,合理地设计基带码是基带传输首先要考虑的问题。

1 理论分析1.1 数字基带信号的码型设计原则(1)对于传输频率很低的信道来说,线路传输码型的频谱中应不含直流分量。

(2)可以从基带信号中提取位定时信号。

在基带传输系统中,需要从基带信号上提取位定时信息,这就要求编码功率谱中具有位定时线谱。

(3)要求基带编码具有内在检错能力。

(4)码型变换过程应具有透明性,即与信源的统计特性无关。

(5)尽量减少基带信号频谱中的高频分量。

这样可以节省传输频带,提高信道的频谱利用率,还可以减少串扰。

1.2 非归零码(NRZ码)非归零码分为两种,即单极性和双极性。

1.2.1单极性这种传输码的零电平与正电平(或负电平)分别对应于二进制代码中的“0”码与“1”码。

他的特点是:脉冲极性单一,有直流分量;脉冲波的占空比为100%,即一个脉冲持续的时间等于一个码元的宽度,在整个码元期间电平保持不变。

该码经常在近距离传输时被采用。

图1-1单极性非归零码1.2.2 双极性这种传输码的正、负电平分别对应于二进制代码中的“1”码与“0”码。

从信号的一般统计规律看,由于“1”码与“0”码出现的概率相等,所以这种传输码的平均电平为零,即无直流分量。

这样在接收端恢复信号时,其判决电平可取为0V,因而可消除因信道对直流电平的衰减而带来判决电平变化的影响。

这种传输码还有抗干扰能力强的特点。

该码常在CCITT的V系列接口标准或RS232C接口标准中使用。

图1-2 双极性非归零码1.3 归零码(RZ码)归零码也分为两种,即单极性和双极性。

1.3.1 单极性与单极性非归零码不同,发送“1”时在整个码元期间高电平只持续一段时间,在码元的其余时间内则返回到零电平,即此方式中,在传送“1”码时发送一个宽度小于码元持续时间的归零脉冲;传送“0”码时不发送脉冲。

其特征是所用脉冲宽度比码元宽度窄。

主要优点是可以直接提取同步信号。

单极性归零码脉冲间隔明显,有利于减小码元间的波形干扰和提取同步时钟信息,但由于脉宽窄,码元能量小,匹配接收时的输出信噪比要比NRZ码低。

图1-3 单极性归零码1.3.2 双极性这种传输码与单极性归零码相似,都是脉冲的持续时间小于码元宽度,并且都是在码元时间内回到零值。

与单极性归零码不同的是,“1”码与“0”码分别是用正、负两种电平来表示。

由于相邻脉冲之间必有零电平区域存在,因此,在接收端根据接收波形归于零电平便知道1b的信息已接收完毕,以便准备下一比特信息的接收。

正负脉冲的前沿起了启动信号的作用,后沿起了终止信号的作用,有利于接收端提取定时信号。

因此可以保持正确的比特同步,即收发之间无需特别定时,且各符号独立地构成起止方式。

此方式也叫做自同步方式。

图1-4 双极性归零码1.4 总体组成框图此次的数字通信信源课程设计的设计步骤主要涉及到码元的产生与输出。

码元的产生主要用拨码开关进行实现,通过对开关的开关状态的设定,产生不同的码元.本系统产生NRZ信号为集中插入帧同步码时分复用信号,信号码速率为256KB, 按实际要求,帧结构如图2.2所示,帧长为32位,其中首位无定义,第2位到第8位是帧同步码(7 位巴克码1110010) ,另外24位为3路数据信号,每路8位。

对于码元的输出主要设计到FPGA或单片机进行设计,其方案如下:方案一:利用FPGA我们可以对晶振产生的频率进行分频的设计,这次的分频主要用EPM7128进行实现。

为了实现信源长度为32位,发出信号前8位为群同步码,后24位为数字信源,信源速率为256bit/s的码形,我们可以将输出频率分别分频为128Hz、64Hz、32Hz、16Hz、8Hz的方波。

其原理方框图的如图1-5所示。

并行码产生器八选一八选一八选一八选一EPM7128四选一图1-5 数字通信信源原理方框图方案二:利用单片机我们可以对晶振产生的频率进行分频的设计,这次的分频主要用89C52进行实现。

同样为了实现信源长度为32位,发出信号前8位为群同步码,后24位为数字信源,信源速率为256bit/s的码形,我们可以将P1.0,P1.1,P1.2的输出频率分别设为128Hz、64Hz、32Hz,将P2.0,P2.1的频率分别设为16Hz、8Hz,其中P1口用于控制74LS151八位数据选择器,P2口用于控制四位数据选择器,这样就可以实现32为码元的输出,并且信源速率为256bit/s。

其原理方框图1-6所示:并行码产生器八选一八选一八选一八选一89C52四选一图1-6 数字通信信源原理方框图由上述所示的两种方案,其原理近乎相同,但是当我们的分频设计的软件实现时,可以看出用方案一通过运用quartus II等软件进行EDA仿真设计能较好的实现,程序的编辑较方案二简单且实用性强,因此在这次的设计中我选择用方案一进行码元的输出。