FPGA课程设计多功能数字钟讲解

基于FPGA多功能数字钟的设计

• 181•人类社会步入高速发展的电子时代,电子产品逐渐代替机械产品走入我们的生活。

随着科技的进步人们对电子产品的要求越来越高、传统产品已经不能满足人们的需求。

体积小、多功能、节能、环保开始成为了电子产品发展的新目标。

本文基于VHDL 语言,利用Quartus Ⅱ设计了一款多功能数字钟,内部包含秒表、闹钟、定时器、时钟四个模块。

经过实验仿真表明多功能数字钟能很好地满足生活中的各种需要。

本产品设计主要使用VHDL 语言描述了各个模块的功能来实现主要电路,最后在Quartus II 上完成了调试与仿真。

VHDL 语言实现电子设计,是一个以软件设计为主,器件配置相结合的过程,能从多个层次对数字系统进行设计,设计数字电路更为灵活方便,设计周期也可大大减小,提高了设计效率和可靠性。

我们需要的功能,在通过使用预先设计好的别的开关进一步让数字钟工作。

通过LED 显示屏可以看到数字。

本文通过软件Quartus II 9.0设计出各个模块并往开发板内写入程序实现我们想要的功能。

3 软件部分3.1 时钟部分时钟设计有三个要求第一,具有时、分、秒计数显示的功能,并以24h 循环计时。

第二,走时误差小于等于每天10s 。

第三,具有调节分钟、小时、秒以及清零的功能。

通常情况不需要让时钟停止工作,所以这部分模块就相当于实现了计数功能,对一直不断给入的1HZ 脉冲进行计数。

秒、分、时分了三个模块进行连接。

qw 是个基于FPGA多功能数字钟的设计大连理工大学城市学院 方润生 邓佳宁 于海霞图1 系统整体过渡模块,也是校正时间所用的模块。

校正时有两个开关,一个校正分、一个校正时。

如图2所示,qw 模块主要是为了实现调时功能。

实际工程中做了元件例化。

元件例化的主要作用是在大型项目的设计中许多底层文件需要反复使用,我们写好底层文件之后通过component 语句可以直接对底层文件进行调用方便了项目的设计。

3.2 闹钟闹钟在到达设置的时间时会发出持续一分钟的信号,可提前手动关闭。

fpga数字时钟课程设计

fpga数字时钟课程设计FPGA数字时钟课程设计随着科技的不断发展,数字时钟已经成为现代人生活中必不可少的物品。

数字时钟的准确性和便捷性吸引了越来越多的人使用。

而现在,我们可以通过FPGA数字时钟课程设计来实现一个高精度的数字时钟。

FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,可以通过编程实现各种不同的功能。

数字时钟的实现也可以通过FPGA来完成。

在FPGA数字时钟课程设计中,我们需要先确定时钟的基础部分。

时钟的基础部分由时钟信号产生器、时钟分频器、时钟计数器和时钟显示器组成。

时钟信号产生器需要产生一个稳定的时钟信号,以供后续的计数器和分频器使用。

我们可以通过FPGA中的时钟模块来产生一个稳定的时钟信号。

接下来,时钟分频器需要将时钟信号分频,使得计数器可以进行精确的计数。

分频器的分频系数可以通过FPGA中的数码开关进行设置。

然后,时钟计数器需要根据分频器的设定进行精确的计数。

计数器的计数值可以通过FPGA中的计数器模块进行设置。

时钟显示器需要将计数器的计数值进行显示。

我们可以通过FPGA 中的数码管模块来实现时钟的显示功能。

除了基础部分,我们还可以通过添加更多的功能来完善数字时钟。

例如,我们可以添加闹钟功能、日期显示功能等,以增加数字时钟的实用性。

在FPGA数字时钟课程设计中,我们可以使用VHDL(VHSIC Hardware Description Language)语言进行编程。

VHDL是一种硬件描述语言,可以用于FPGA和ASIC的设计。

通过编写VHDL 程序,我们可以实现数字时钟的各种功能。

FPGA数字时钟课程设计是一个非常有趣和实用的课程项目。

通过这个项目,我们可以深入了解数字时钟的工作原理,熟悉FPGA的编程方法,同时也可以锻炼自己的编程能力。

基于FPGA的多功能数字钟设计报告

***大学电工电子实验报告EDA技术基础设计报告多功能数字钟设计电子信息科学与技术年 月 日多功能数字钟设计一.任务解析用Verilog硬件描述语言设计数字钟,实现:1、具有时、分、秒计数显示功能,以二十四小时循环计时。

2、具有调节小时,分钟的功能。

3、具有整点报时同时LED灯花样显示的功能。

4、【发挥】三键(模式选择,加,减)调整,数码管闪烁指示功能。

5、【发挥】增加闹钟任意设定功能,时间精确到分。

二.方案论证第2页,共19页三.重难点解析1、模式选择键的设计//模式选择键。

有5个模式,m0为正常走钟;m1为调分;m2为调时;m3为闹钟调分;m4为闹钟调时。

module mode_key(key,clr,m);input key,clr;output [2:0]m;reg [2:0]m;always @(posedge key or negedge clr) beginif(!clr) m=0;else if(m==4) m=0;else m=m+1;endendmodule2、数字钟秒钟计数设计module cnt60_sec(clk,clr,q,c);input clk,clr;output [6:0]q;output c;reg [6:0]q;reg c;always @(posedge clk or negedge clr) beginif(!clr) begin q=0;c=0;endelse if(q[3:0]==9) begin q[3:0]=0;if(q[6:4]==5) begin q[6:4]=0; c=1;endelse q[6:4]=q[6:4]+1;end第3页,共19页else begin q[3:0]=q[3:0]+1;q[6:4]=q[6:4];c=0;endendendmodule、秒钟计数模块就是一个60的计数器,计数到59的时候清零,进位加1。

调时不需要控制秒钟,所以没有加模式选择按键。

数字钟课程设计fpga

数字钟课程设计 fpga一、课程目标知识目标:1. 学生能理解数字钟的基本原理和组成,掌握数字钟的计时方法。

2. 学生能了解FPGA的基本概念,掌握FPGA在数字钟设计中的应用。

3. 学生能掌握数字钟设计中涉及的二进制、十进制转换方法。

技能目标:1. 学生能够运用所学知识,设计并实现一个简单的数字钟电路。

2. 学生能够使用FPGA编程,实现数字钟的功能。

3. 学生能够通过实验操作,培养动手能力和团队协作能力。

情感态度价值观目标:1. 学生对数字电路产生兴趣,树立学习信心,形成积极的学习态度。

2. 学生在学习过程中,培养创新精神和实践能力,增强对科技发展的关注。

3. 学生通过合作学习,培养团队意识,学会尊重他人,分享成果。

课程性质:本课程为电子技术实践课程,结合理论教学,注重培养学生的实际操作能力和创新思维。

学生特点:学生为高中生,具备一定的电子技术基础,对新鲜事物充满好奇,喜欢动手实践。

教学要求:教师需引导学生运用所学知识,通过实验操作,掌握数字钟设计方法,提高学生的实践能力和创新精神。

同时,关注学生的情感态度价值观培养,使学生在学习过程中形成良好的学习习惯和团队合作意识。

将课程目标分解为具体的学习成果,便于后续教学设计和评估。

二、教学内容1. 数字钟原理及组成- 数字钟工作原理- 数字钟各部分功能及相互关系2. FPGA基础知识- FPGA基本概念- FPGA在数字电路设计中的应用3. 数字钟设计与实现- 数字钟计时方法- 二进制与十进制转换方法- 数字钟电路设计流程4. FPGA编程与实验操作- FPGA编程基础- 数字钟功能模块编程- 实验操作步骤与注意事项5. 数字钟综合设计与调试- 设计要求与评价指标- 设计方案撰写与展示- 团队合作与交流教学内容安排与进度:第一周:数字钟原理及组成、FPGA基础知识学习第二周:数字钟设计与实现、FPGA编程基础学习第三周:数字钟功能模块编程、实验操作第四周:数字钟综合设计与调试、成果展示与评价教材章节:第一章:数字钟原理及组成第二章:FPGA基础知识第三章:数字钟设计与实现第四章:FPGA编程与实验操作第五章:数字钟综合设计与调试教学内容遵循科学性和系统性原则,结合课程目标,确保学生能够掌握数字钟设计与FPGA编程相关知识,培养实践能力和创新精神。

基于FPGA的数字钟设计

数字钟的设计一、 设计要求设计一个数字钟,要求用数码管分别显示时、分、秒的计数,同时可以进行时间设置,并且要求在整点的时候能够实现报时功能。

二、 设计原理计数器在正常工作下是对1Hz的频率计数,在调整时间状态下是对调整的时间模块进行计数;控制按键来选择是正常计数还是调整时间,并决定是调整时还是分;时间显示的LED数码管采用动态扫描实现;在整点到达时,还具有整点报时功能。

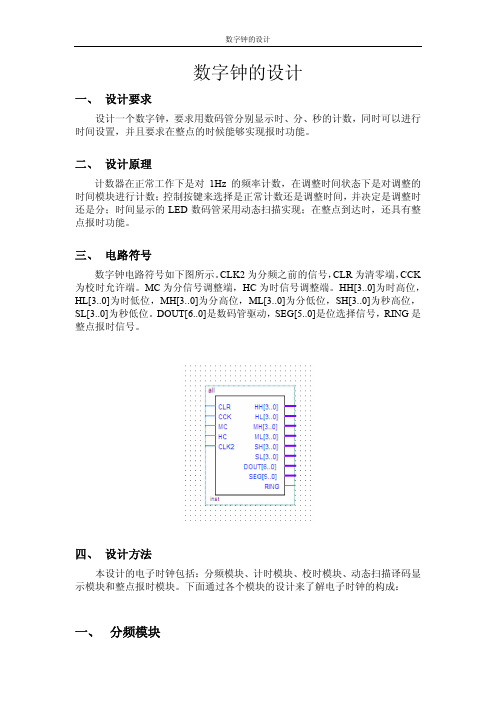

三、 电路符号数字钟电路符号如下图所示。

CLK2为分频之前的信号,CLR为清零端,CCK 为校时允许端。

MC为分信号调整端,HC为时信号调整端。

HH[3..0]为时高位,HL[3..0]为时低位,MH[3..0]为分高位,ML[3..0]为分低位,SH[3..0]为秒高位,SL[3..0]为秒低位。

DOUT[6..0]是数码管驱动,SEG[5..0]是位选择信号,RING是整点报时信号。

四、 设计方法本设计的电子时钟包括:分频模块、计时模块、校时模块、动态扫描译码显示模块和整点报时模块。

下面通过各个模块的设计来了解电子时钟的构成:一、 分频模块程序附录:module clk2clk1s(clk,clk1s); input clk;output clk1s;reg clk1s;reg [3:0] cnt;always@(posedge clk)if(cnt==4'b1111)beginclk1s<=~clk1s;cnt<=0;endelsecnt<=cnt+1; endmodule波形仿真:二、 计时模块六十进制计数器六十进制计数器程序附录:六十进制计数器模块:module m60(clk,clr,qh,ql,cao);input clk,clr;output cao;output[3:0] qh,ql;reg [3:0] qh,ql;reg cao;always @(posedge clk or negedge clr) beginif(clr==0)beginqh<=4'h0;ql<=4'h0;cao<=0;endelse if(ql==9)beginql<=0;if(qh==5)beginqh<=0;cao<=1;endelse qh=qh+1;endelsebeginql<=ql+1;cao<=0;endendendmodule二十四进制计数器模块:module m24(clk,clr,qh,ql);input clk,clr;output[3:0] qh,ql;reg [3:0] qh,ql;always @(posedge clk or negedge clr) beginif(clr==0)beginqh<=4'h0;ql<=4'h0;endelse if(qh==2)beginql<=ql+1;if(ql==3)beginqh<=0;ql<=0;endendelse if(ql==9)beginqh<=qh+1;ql<=0;endelseql<=ql+1; end endmodule波形仿真:清零清零正常计时三、 校时模块四、 动态译码显示模块CCK 为0不支持校时,有进位信号时产生分(时)脉冲程序附录:1、位扫描信号(HH,HL,MH,ML,SH,SL逐位扫描,并输出)module sel(clk,hh,hl,mh,ml,sh,sl,out);input clk;input [3:0] hh,hl,mh,ml,sh,sl;output [3:0] out;reg [3:0] out;reg [3:0] ss=0;always @(posedge clk)beginif(ss<4'b0101)ss<=ss+1;elsess<=0;endalways @(posedge clk)begincase(ss)4'd0:out<=sl;4'd1:out<=sh;4'd2:out<=ml;4'd3:out<=mh;4'd4:out<=hl;4'd5:out<=hh;endendmodule仿真图:2、段扫描信号(选择数码管点亮哪一位)module seg(clk,seg);input clk;output [5:0] seg;reg [5:0] seg;reg [3:0] ss=0;always @(posedge clk)beginif(ss<4'b0101)ss<=ss+1;elsess<=0;endalways @(posedge clk)begincase(ss)4'd0:seg<=6'b111110;4'd1:seg<=6'b111101;4'd2:seg<=6'b111011;4'd3:seg<=6'b110111;4'd4:seg<=6'b101111;4'd5:seg<=6'b011111;default:seg<=6'b111111;endcaseend3、4—7译码module decode4_7(decodeout,indec); output[6:0] decodeout;input[3:0] indec;reg[6:0] decodeout;always @(indec)begincase(indec)4'd0:decodeout=7'b1111110;4'd1:decodeout=7'b0110000;4'd2:decodeout=7'b1101101;4'd3:decodeout=7'b1111001;4'd4:decodeout=7'b0110011;4'd5:decodeout=7'b1011011;4'd6:decodeout=7'b1011111;4'd7:decodeout=7'b1110000;4'd8:decodeout=7'b1111111;4'd9:decodeout=7'b1111011;default: decodeout=7'b0000000;endcaseendendmodule五、 整点报时模块六、 数字钟仿真图数字钟的设计注:动态扫描的时钟频率尽量要快。

基于FPGA的多功能数字钟课程设计

F PG A课程设计报告(实现多功能数字钟)一、标题:设计多功能数字钟控制电路二、任务书:用MAX+PLU SⅡ软件及Verilog HDL语言设计一个多功能的数字钟,包括有时、分、秒的计时,以及校时(对小时、分钟和秒能手动调整以校准时间)、正点报时(每逢整点,产生“嘀嘀嘀嘀-嘟”,4短一长的报时音)等附加功能。

三、关键词:24进制、60进制、正点报时、校时、数字钟四、总体方案:多功能数字钟控制电路框图是由三部分组成的,即秒分时控制电路、整点报时控制电路、时段控制电路。

用Verilog HDL硬件描述语言完成编译和仿真。

五、原理框图如下:↓↓↓六、Verilog HDL硬件描述语言编写的功能模块:/*秒计数器m60*/module m60(M,CP60M,CPM,RD); output [7:0]M;output CP60M;input CPM;input RD;reg [7:0]M;wire CP60M;always@(negedge RD or posedge CPM) beginif(!RD)begin M[7:0]<=0;endelsebeginif((M[7:4]==5)&&(M[3:0]==9))beginM[7:0]<=0;endelsebeginif(M[3:0]==9)beginM[3:0]<=0;if(M[7:4]==5)begin M[7:4]<=0;endelse M[7:4]<=M[7:4]+1;endelse M[3:0]<=M[3:0]+1;endendendassign CP60M=~(M[6]&M[4]&M[3]&M[0]); endmodule/*分计数器m60*/module m60(M,CP60M,CPM,RD);output [7:0]M;output CP60M;input CPM;input RD;reg [7:0]M;wire CP60M;always@(negedge RD or posedge CPM) beginif(!RD)begin M[7:0]<=0;endelsebeginif((M[7:4]==5)&&(M[3:0]==9))beginM[7:0]<=0;endelsebeginif(M[3:0]==9)beginM[3:0]<=0;if(M[7:4]==5)begin M[7:4]<=0;endelse M[7:4]<=M[7:4]+1;endelse M[3:0]<=M[3:0]+1;endendendassign CP60M=~(M[6]&M[4]&M[3]&M[0]); endmodule/*小时计数器m24*/module m24(H,CPH,RD);output [7:0]H;input CPH,RD;reg [7:0]H;always@(negedge RD or posedge CPH) beginif(!RD) H[7:0]<=0;elsebeginif((H[7:4]==2)&&(H[3:0]==3))beginH[7:0]<=0;endelsebeginif(H[3:0]==9)begin H[3:0]<=0;H[7:4]<=H[7:4]+1;endelse H[3:0]<=H[3:0]+1;endendendendmodule/*秒分时控制计数器xiaoshi2*/module xiaoshi2(CPM,CPH,CPS,CP60M,CP60S,SWM,SWH);output CPM,CPH;input SWM,SWH;input CPS,CP60S,CP60M;reg CPM,CPH;always@(SWM or SWH or CPS or CP60S or CP60M)begincase({SWM,SWH})2'b01: begin CPM<=CPS;CPH<=CP60M;end2'b10: begin CPM<=CP60S;CPH<=CPS;enddefault: begin CPM<=CP60S;CPH<=CP60M;end endcaseendendmodule/*时段控制器sdkz*/module sdkz(h,sk);input [7:0]h;output sk;reg sk;always@(h)beginif((h<=5)||(h>=19))sk<=1;elsesk<=0;endendmodule/*报时计数器baoshi*/module baoshi(m6,m4,m3,m0,s6,s4,s3,s0,dy,gy,bshi); input m6,m4,m3,m0,s6,s4,s3,s0,dy,gy;output bshi;wire bm;reg bshi;assign bm=m6&m4&m3&m3&m0&s6&s4&s0; always@(bm or s3 or dy or gy)beginif(bm&s3)bshi<=gy;else if(bm)bshi<=dy;elsebshi<=0;endendmodule七:各模块原理图及仿真波形:24进制原理图:60进制原理图:电路原理图:时段控制:报时:1、秒计数器仿真波形2、分计数器的仿真波形3、小时计数器的仿真波形4、秒分时控制电路的仿真波形5、时段控制的仿真波形6、报时器的仿真波形八、顶层文件及仿真波形顶层文件的仿真波形:管脚号的分配如下:十:课程设计结论:此次课程设计通过最终下载及编译可实现以上功能,在七段显示器上可实现秒、分计数器60进制,时计数器24进制显示,以及调节CLK1、CLK2的频率可使计数器上数字延时显示。

基于FPGA多功能数字钟的设计

3、状态转换功能模块

该模块实现电路各状态之间的转换功能,若仅完成基本功能,系统 应包含4个状态,分别为正常计时、对秒位进行设置、对分位进行设置 和对小时位进行设置。若完成扩展功能,还可增加其他状态。这部分可 以用脉冲键输入进行切换,也可以用拨动开关进行切换。根据所选择的 切换方式,自行编写程序。

4、校时功能模块

此模块主要在状态切换到设置时,可以将时、分、秒位设置成需要的 数值,此功能可以由脉冲键输入完成。

5、译码功能模块

此模块功能将计数器产生的数值,通过编译,形成对应七段数码 管显示格式的编码。七段数码管的a-g对应实验箱上的主要引脚为 O50-O56。

6、LED显示模块

本模块使用实验箱上的8个数码管进行显示,为动态显示法,需采用 扫描的方式进行显示。此方法对于扫描频率有一定的要求,在设计时需 考虑采用那个频率作为扫描信号。8个数码管的扫描信号对应实验箱上的 引脚为SO58-SO65。

四、系统仿真

将每个模块编译成功后,进行仿真测试,若仿真结果符合设计 要求,再配置输入输出引脚,若不符合,请返回修改程序,直至仿 真结果合格。将仿真结果截图,记录至设计报告中。

精品课件!

精品课件!

五、硬件验证

将编译通过、仿真结果正确且引脚信息配置正确的程序下载至 实验箱的FPGA中,硬件验证设计是否符合要求。

2、计时功能模块

计时模块需对时、分、秒进行计数,其中小时位为24进制,分 钟和秒钟位为60进制。可以用一段程序对时、分、秒进行连续计数, 也可以对时、分、秒的高位和低位分别计数。注意,如果采用连续 计数方式,因为每位显示时有高位和低位之分,所以需将十进制数 据用BCD码进行转换后,才能输出到七段数码管上显示。

此电子钟分两种工作状态: 1、正常计时的状态; 2、设置时间的状态。

多功能数字钟FPGA实现

实验报告:多功能数字钟081180008 陈家伟一、设计任务本实验使用verilog HDL语言在FPGA平台上实现了一个简单的多功能数字钟,它主要包含一下几个主要功能:(1)实现基本计时功能,并以24小时显示。

(2)实现校时功能。

(3)实现闹钟功能:设定闹钟时间,采用蜂鸣器提示,并且实现了自动关闭。

(4)实现跑表功能:具有启动、停止、继续、复位功能。

在本实验中,最大的问题便是多个功能并行时的干扰问题,需要在设计时对功能切换过程可能产生的干扰充分把握,实现多个功能的并存。

二、输入输出界面的设计在实验中,输入输出界面需要首先考虑,以保证整个系统设计的统一性。

在输入界面的设计上,由于按键资源的限制,必须考虑各个功能键的复用;在输出界面的设计上,由于显示资源的限制,必须考虑数码管显示界面的复用。

输入界面设计如下:(1)KEY1(PIN_122)为模式切换键。

整个系统具有4种功能模式:计时(mode0)、校时(mode1)、闹钟(mode2)、跑表(mode3)。

由KEY1负责模式的切换。

(2)KEY2(PIN_121)为复用键。

mode0(计时)下,KEY2键不起作用;mode1(校时)下,KEY2键使时间增加;mode2(闹钟)下,KEY2键使闹钟设置对应位增加;mode3(跑表)下,KEY2键控制跑表的开始、暂停、继续。

(3)KEY3(PIN_123)为复用键。

mode0(计时)下,KEY3键不起作用;mode1(校时)下,KEY3键负责时位、分位的切换;mode2(闹钟)下,KEY3键负责闹钟设置时位、分位的切换;mode3(跑表)下,KEY3控制跑表的复位。

输入界面设计时主要考虑的是尽量将不同模式下相近的功能归并到同一个按键上来,一方面方便用户的操作,另一方面也使得设计简洁明了,减少的错误的出现。

输出界面(四位数码管显示器)设计如下:(1)mode0(计时)下,四位数码管显示的是24小时计时:左边两个数码管显示小时;右边两个数码管显示分钟;最右边数码管的dp以闪动显示秒。

基于XilinxFPGA的数字钟设计

基于FPGA的多功能数字钟一、设计题目基于Xilinx FPGA的多功能数字钟设计二、设计目的1.掌握可编程逻辑器件的应用开发技术——设计输入、编译、仿真和器件编程;2.熟悉一种EDA软件使用;3.掌握Verilog设计方法;4.掌握分模块分层次的设计方法;5.用Verilog完成一个多功能数字钟设计;6.学会FPGA的仿真。

三、设计内容设计实验项目九多功能电子钟✧功能要求:利用实验板设计实现一个能显示时分秒的多功能电子钟,具体要求为:基本功能:1)准确计时,以数字形式显示时、分、秒,可通过按键选择指示当前显示时间范围模式;2)计时时间范围 00:00:00-23:59:593)可实现校正时间功能;4)可通过实现时钟复位功能:00:00:00扩展功能:1)定时报:时间自定(不要求改变),闹1分钟(1kHz)---利用实验板LED或外接电路实现。

2)仿广播电台正点报时:XX:59:[51,53,55,57(500Hz);59(1kHz)] ---利用实验板LED或外接电路实现。

3)报整点时数:XX:00:[00.5-XX.5](1kHz),自动、手动---利用实验板LED或外接电路实现。

4)手动输入校时;5)手动输入定时闹钟;6)万年历;7)其他扩展功能;✧设计步骤与要求:1)计算并说明采用Basys2实验板时钟50MHz实现系统功能的基本原理。

2)在Xilinx ISE13.1 软件中,利用层次化方法,设计实现模一百计数及显示的电路系统,设计模块间的连接调用关系,编写并输入所设计的源程序文件。

3)对源程序进行编译及仿真分析(注意合理设置,以便能够在验证逻辑的基础上尽快得出仿真结果)。

4)输入管脚约束文件,对设计项目进行编译与逻辑综合,生成下载所需.bit类型文件。

5)在Basys2实验板上下载所生成的.bit文件,观察验证所设计的电路功能。

四、总体设计思路主体分为分频模块,正常时间模块(包含两个模60计数器和一个模24计数器子模块),闹钟模块(分为一个模60计数器模块,一个模24计数器模块,四个比较器模块),电台报时模块,数码管显示模块(分为模式选择模块,片选信号及扫描程序模块,和译码模块)。

基于FPGA的数字钟课程设计

集成电路设计课程设计报告专业班级学号姓名基于FPGA的数字钟课程设计1.任务和设计要求设计具有时、分、秒计数显示,以24小时循环计时的时钟电路,带有清零和校准功能;2.设计原理采用硬件描述语言Verilog 进行编程,实现20MHZ晶振到1HZ的分频;采用verilog 语言实现数字表功能实现的各个模块;通过各个模块的代码生成相应的模块原理图;再将各个模块生成的原理图进行叠加组成一个数字表系统;3.系统设计设计的数字表有6个输入,16个输出;6个输入中,有一个是时钟信号,开发板上的28号引脚输入的50MHZ的时钟信号;一个清零端,当数字表正常显示时,按下清零端可以实现数字钟整体电路图:4.各个模块设计基于EP1C6Q240C8的数字钟设计,有6个模块组成:Fdiv 分频模块Control 模式选择模块Tune 校正模块Zoushi 时间正常运行模块Saomiao 数码管动态扫描模块;Decoder BCD译码模块;Fdiv 模块:功能:实现20MHZ的时钟信号分成10KHZ的信号和1HZ的信号;输入:clk 为20MHZ的时钟信号;输出:f10000HZ 为10KH的时钟信号;F1HZ 为1HZ的时钟信号;Fdiv 模块代码:module fdiv(clk,f10000Hz,f1Hz);output f10000Hz,f1Hz;input clk;reg f10000Hz,f1Hz;integer CNT1=0,CNT2=0;always@(posedge clk)beginif(CNT1<1999)beginCNT1=CNT1+1;f10000Hz<=1'b0;endelsebeginCNT1=0;f10000Hz<=1'b1;endendalways@(posedge f10000Hz)beginif(CNT2<9999)beginCNT2=CNT2+1;f1Hz<=1'b0;endelsebeginCNT2=0;f1Hz<=1'b1;endendendmodulefdiv 模块波形仿真:由于实际的分频波形仿真中,由于要将20MHZ的分成1HZ的,需要将信号缩小20 000 000倍,因此,此处采用将20HZ的先分成10HZ,然后再将10HZ的分成1HZ的时钟信号;在仿真中这样整,在实际演示中再改下代码,实现真正的20MHZ到1HZ的分频;它们只是一个倍数关系而已;Control 模块:功能:实现电子表的正常显示及时间校正模式的转换;输入:key 模式修改键,每来一个高电平,mode加一次。

基于FPGA的多功能数字时钟设计

7.利用适配器将综合后的网络表文件针对某一具体的目标器件进行逻辑映射操作,包括底层器件配置、逻辑分割、逻辑优化和布局布线。

8.在适配完成后,产生多项设计结果:(a)适配报告,包括芯片内部资源利用情况,设计的布尔方程描述情况等;(b)适配后的仿真模型;(c)器件编程文件。根据适配后的仿真模型,可以进行适配后时序仿真,因为已经得到器件的实际硬件特性(如时延特性),所以仿真结果能比较精确的预期未来芯片的实际性能。如果仿真结果达不到设计要求,就修改VHDL源代码或选择不同速度和品质的器件,直至满足设计要求。

1.CLB是FPGA的主要组成部分。图2-1是CLB基本结构框图,它主要由逻辑函数发生器、触发器、数据选择器等电路组成。CLB中3个逻辑函数发生器分别是G、F和H,相应的输出是G’、F’和H’。G有4个输入变量G1、G2、G3和G4;F也有4个输入变量F1、F2、F3和F4。这两个函数发生器是完全独立的,均可以实现4输入变量的任意组合逻辑函数。逻辑函数发生器H有3个输入信号;前两个是函数发生器的输出G’和F’,而另一个输入信号是来自信号变换电路的输出H1。这个函数发生器能实现3输入变量的各种组合函数。这3个函数发生器结合起来,可实现多达9变量的逻辑函数。

基于FPGA的数字时钟课程设计

西安郵電學院基于FPGA的数字时钟成员:技术规范一、功能定义1、分频:在电子钟的设计中,涉及到的频率有三个:(1):1Hz的秒计时频率,用来进行秒计时;(2):4Hz的按键防抖频率;(3):1000Hz的循环扫描频率;因此在分频模块应实现将芯片中的高频率时钟分频得到上面的三个所需频率。

2、控制:进行正常计时,时间调整,时间复位模式的选择:(1)时间初始复位;(2)选择秒时间调整的模式;(3)选择分时间调整的模式;(4)选择小时时间调整的模式;3、计时:进行调整时间,正常计时;(1)正常计时;(2)调整秒计时;(3)调整分计时;(4)调整时计时;4、选择输出:进行时间高低位的变换及循环扫描输出:(1)进行时间高低位的变换;(2)进行时间的循环扫描;5、译码:对时间进行七段数码管的译码:二、总引脚定义设计思路:一、总体设计思路图:二、功能引脚定义1、总体引脚(1)K[1]:输入,控制是否进入调整模式,调时模式或调分模式。

(2)K[2]:输入,根据K1的选择进行加1调时。

(3)CLK:输入,1赫兹,控制秒钟的频率。

(4)CLK1K:输入,1K赫兹,控制时间的连续扫描输出。

(5)[7:0]LED:输出,七段显示译码管的输入。

(6)[5:0]SEG:输出,控制六个数码管的是否接通。

(7) SC:输入,时间复位。

2、(1)控制模块:输出控制信号和时分秒计时。

控制信号控制时分秒是否正常计时。

K[1]:输入,控制是否进入调整模式,调时模式或调分模式。

K[2]:输入,根据K1的选择进行加1调时。

SC:输入,时间复位。

[5:0]SEC:复位秒计时。

[5:0]MIN:复位、调时分计时。

[5:0]HOUR:复位、调时时计时。

KEN:控制是否进行正常及时、进入调时复位状态。

(2)计时模块秒计时:输出正常的秒计时或复位计时。

分计时:输出正常的分计时或复位计时或调时计时。

时计时:输出正常的时计时或复位计时或调时计时。

(3)时间扫描模块:利用高频率的时钟不断地循环扫描是分秒计时,以便循环译码;输出控制信号,控制数码管是否有效;此模块同时进行时间的高地位的计算与输出。

基于FPGA多功能数字钟的设计

实验名称:基于FPGA的数字时钟设计一、实验目的:通过实验熟练运用Verilog HDL语言和 FPGA开发软件,使用BASYS2开发板设计一个可调式并且较复杂的数字时钟。

二、实验硬件要求:计算机、BASYS2开发板、蜂鸣器三、实验内容:1、电路功能:在ISE Design Suite 14.7软件开发环境下,使用Verilog描述语言、结合FPGA开发板编译和仿真数字时钟;要求时钟能进行基本的计时功能,按照:“时:分”来显示时间,秒的功能由流水灯表示;能引入秒脉冲进行校时、校分,并可用rst信号给清零;具有整点报时功能,当计时到整点的时候蜂鸣器开始鸣响,响声为乐曲“铃儿响叮当”。

2、电路图:3、Veilog 程序:1)分频模块div_clk:module divclk(sys_clk,rst,sec_clk);input sys_clk,rst;//系统时钟,复位output reg sec_clk;//秒时钟输出reg[27:0] cnt;//分频计数器,在人眼可识别范围之内always @(negedge sys_clk)beginif(rst)//对计数器进行复位begincnt <= 28'h0000000;sec_clk <= 1'b0;endelseif(cnt >= 28'h17d783f)begincnt <= 28'h0000000;sec_clk <= ~sec_clk;endelse cnt <= cnt+1'b1;endendmodule2)时钟计时模块clockmoduleclock(clk,rst,key,hor_h,hor_l,min_h,min_l,sec_h,sec_l,speak,sys_clk); input clk,rst,sys_clk;input [3:0]key;output [3:0]hor_h,hor_l,min_h,min_l,sec_h,sec_l;output speak;reg [3:0]hor_h,hor_l,min_h,min_l,sec_h,sec_l;reg speak;always@(posedge clk or posedge rst)beginif(rst)beginsec_h <=4'h0;sec_l <=4'h0;min_h <=4'h0;min_l <=4'h0;hor_h <=4'h0;hor_l <=4'h0;endelsecase(key)4'b1000:beginif(hor_h >= 4'h2)hor_h <= 4'h0;elsehor_h <= hor_h + 1'b1;end4'b0100:beginif(hor_l >= 4'h9||(hor_h >= 4'h2 && hor_l >= 4'h3)) hor_l <= 4'h0;elsehor_l <= hor_l + 1'b1;end4'b0010:beginif(min_h >= 4'h5)min_h <= 4'h0;elsemin_h <= min_h + 1'b1;end4'b0001:beginif(min_l >= 4'h9)min_l <= 4'h0;elsemin_l <= min_l + 1'b1;enddefault :beginif(sec_l >= 4'h9)beginsec_l <= 4'h0;if(sec_h >= 4'h5)beginsec_h <= 4'h0;if(min_l >= 4'h9)beginmin_l <= 4'h0;if(min_h >= 4'h5)beginmin_h <= 4'h0;if(hor_l >= 4'h9||(hor_h >= 4'h2 && hor_l >= 4'h3))beginhor_l <= 4'h0;if(hor_h >= 4'h2)hor_h <= 4'h0;elsehor_h <= hor_h + 1'b1;endelsehor_l <= hor_l + 1'b1;endelsemin_h <= min_h + 1'b1;endelsemin_l <= min_l + 1'b1;endelsesec_h <= sec_h + 1'b1;endelsesec_l <= sec_l + 1'b1;endendcaseendalways @(posedge clk)beginif(rst)speak <= 1'b0;else if(min_h == 4'h0 && min_l <=4'h0 && sec_h <= 4'h0)speak <= 1'b1;elsespeak <= 1'b0;endendmodule3)发声模块speaker:module speaker(clk,rst,en,f);input clk,rst,en;output reg f;reg [6:0] tonestep;reg [3:0] tonecode;reg [19:0] divcnt;reg [19:0] cntnum;reg sub_clk;reg[24:0] sub_cnt;always@(posedge clk)beginif(rst) beginsub_cnt <= 0;cntnum <= 0;divcnt <= 0;f <= 0;sub_clk <=0;endelse beginif(sub_cnt >=1500000)beginsub_clk <= ~sub_clk;sub_cnt <=0;endelse sub_cnt <= sub_cnt + 1'b1;if(en == 1'b1)begincase(tonecode)1:cntnum <= 95444;2:cntnum <= 85052;3:cntnum <= 75750;4:cntnum <= 71625;5:cntnum <= 63775;6:cntnum <= 56825;7:cntnum <= 50600;default : cntnum <= 0;endcaseif(cntnum == 0)f <= 1'b0;elseif(divcnt >= cntnum)begindivcnt <= 0;f <= ~f;endelse divcnt <= divcnt + 1'b1;endendendalways@(posedge sub_clk)beginif(rst)begintonestep <= 0;tonecode <= 0;endelseif(tonestep <=80)tonestep <= tonestep + 1'b1;else tonestep <= 0;case(tonestep)7'b0000000:tonecode <= 3;7'b0000001:tonecode <= 3;7'b0000010:tonecode <= 8;7'b0000011:tonecode <= 3;7'b0000100:tonecode <= 3;7'b0000101:tonecode <= 8;7'b0000110:tonecode <= 8;7'b0000111:tonecode <= 3;7'b0001000:tonecode <= 3;7'b0001001:tonecode <= 3;7'b0001010:tonecode <= 3;7'b0001011:tonecode <= 8;7'b0001100:tonecode <= 8;7'b0001101:tonecode <= 3;7'b0001110:tonecode <= 3;7'b0001111:tonecode <= 8;7'b0010000:tonecode <= 3;7'b0010001:tonecode <= 3;7'b0010010:tonecode <= 8;7'b0010011:tonecode <= 8;7'b0010101:tonecode <= 3; 7'b0010110:tonecode <= 3; 7'b0010111:tonecode <= 3; 7'b0011000:tonecode <= 8; 7'b0011001:tonecode <= 8; 7'b0011010:tonecode <= 3; 7'b0011011:tonecode <= 3; 7'b0011100:tonecode <= 8; 7'b0011101:tonecode <= 5; 7'b0011110:tonecode <= 5; 7'b0011111:tonecode <= 8; 7'b0100000:tonecode <= 8; 7'b0100001:tonecode <= 1; 7'b0100010:tonecode <= 1; 7'b0100011:tonecode <= 8; 7'b0100100:tonecode <= 2; 7'b0100101:tonecode <= 2; 7'b0100110:tonecode <= 8; 7'b0100111:tonecode <= 8; 7'b0101000:tonecode <= 3; 7'b0101001:tonecode <= 3; 7'b0101010:tonecode <= 3; 7'b0101011:tonecode <= 3; 7'b0101100:tonecode <= 8; 7'b0101101:tonecode <= 8; 7'b0101110:tonecode <= 4; 7'b0101111:tonecode <= 4; 7'b0110000:tonecode <= 8; 7'b0110001:tonecode <= 4; 7'b0110010:tonecode <= 4;7'b0110100:tonecode <= 8; 7'b0110101:tonecode <= 4; 7'b0110110:tonecode <= 4; 7'b0110111:tonecode <= 4; 7'b0111000:tonecode <= 8; 7'b0111001:tonecode <= 4; 7'b0111010:tonecode <= 8; 7'b0111011:tonecode <= 8; 7'b0111100:tonecode <= 4; 7'b0111101:tonecode <= 4; 7'b0111110:tonecode <= 8; 7'b0111111:tonecode <= 3; 7'b1000000:tonecode <= 3; 7'b1000001:tonecode <= 8; 7'b1000010:tonecode <= 8; 7'b1000011:tonecode <= 3; 7'b1000100:tonecode <= 3; 7'b1000101:tonecode <= 3; 7'b1000110:tonecode <= 8; 7'b1000111:tonecode <= 3; 7'b1001000:tonecode <= 8; 7'b1001001:tonecode <= 3; 7'b1001010:tonecode <= 8; 7'b1001011:tonecode <= 5; 7'b1001100:tonecode <= 5; 7'b1001101:tonecode <= 8; 7'b1001110:tonecode <= 5; 7'b1001111:tonecode <= 5; 7'b1010000:tonecode <= 8; 7'b1000001:tonecode <= 8;7'b1000010:tonecode <= 4;7'b1000011:tonecode <= 4;7'b1000100:tonecode <= 8;7'b1000101:tonecode <= 2;7'b1000110:tonecode <= 2;7'b1000111:tonecode <= 8;7'b1001000:tonecode <= 8;7'b1001001:tonecode <= 1;7'b1001010:tonecode <= 1;7'b1001011:tonecode <= 1;7'b1001100:tonecode <= 1;7'b1001101:tonecode <= 8;7'b1001110:tonecode <= 8;7'b1001111:tonecode <= 5;7'b1010000:tonecode <= 5;7'b1010001:tonecode <= 8;7'b1010010:tonecode <= 3;7'b1010011:tonecode <= 3;7'b1010100:tonecode <= 8;7'b1010101:tonecode <= 8;7'b1010110:tonecode <= 2;7'b1010111:tonecode <= 2;7'b1011000:tonecode <= 8;7'b1011001:tonecode <= 1;7'b1011010:tonecode <= 1;7'b1011011:tonecode <= 8;7'b1011100:tonecode <= 8;endcaseendendmodule4)数码管显示模块seg:module seg(q,ctr,h_h,h_l,m_h,m_l,clk,rst);output[6:0]q;output[3:0] ctr;input[3:0] h_h,h_l,m_h,m_l;input clk,rst;reg[6:0] q;reg[25:0] count;reg[3:0] temp;reg[3:0] scan;always @ (posedge clk)beginif (rst)begincount = 0;endelsebegincount = count +1;endendalways @ (posedge clk ) //Seg Scanbeginif(rst)beginscan<=4'b0000;endelsecase(count[11:10]) // 执行设计时将扫描频率改回 2'b00: scan<=4'b0111;2'b01: scan<=4'b1011;2'b10: scan<=4'b1101;2'b11: scan<=4'b1110;endcaseendassign ctr = scan;always @ (posedge clk) //Seg Scanbeginif(rst)begintemp<=4'b0000;endelsecase(count[11:10]) // 执行设计时将扫描频率改回 2'b00: temp<=h_h;2'b01: temp<=h_l;2'b10: temp<=m_h;2'b11: temp<=m_l;endcaseendalways @(posedge clk) //数码管译码beginif(rst)beginq<=7'b0000000;endelsecase(temp)4'd0:q<=7'b0000001; //04'd1:q<=7'b1001111; //14'd2:q<=7'b0010010; //24'd3:q<=7'b0000110; //34'd4:q<=7'b1001100; //44'd5:q<=7'b0100100; //54'd6:q<=7'b0100000; //64'd7:q<=7'b0001111; //74'd8:q<=7'b0000000; //84'd9:q<=7'b0000100; //9default:q<=7'b0000001;endcaseendendmodule5)秒计时流水灯模块sec_ledmodule sec_led(input sys_clk,input rst,output [7:0] led);reg[24:0] cnt;reg[7:0] led_reg;always@(posedge sys_clk)beginif(rst)cnt <= 0;else cnt <= cnt+1;endalways@(posedge sys_clk)beginif(rst)led_reg <= 8'b0000_0001;else if (cnt == 25'd4*******)beginled_reg <= led_reg << 1;if(led_reg==8'b1000_0000)led_reg<=8'b0000_0001;endassign led=led_reg;Endmodule6键盘修改模块:module keyboard(input sys_clk,// input rst_n,input ps2_clk,input ps2_data,output reg[3:0] key_val);wire [15:0]xkey;reg ps2cf,ps2df;reg clk25=0;reg [7:0]ps2c_filter,ps2d_filter;reg [10:0]shift1,shift2;assign xkey={shift2[8:1],shift1[8:1]};assign rst_n=1;always@(posedge sys_clk)clk25=~clk25;always@(posedge clk25 or negedge rst_n) beginif(!rst_n)beginps2c_filter<=0;ps2d_filter<=0;ps2cf<=1;ps2df<=1;endelsebeginps2c_filter[7]<=ps2_clk;ps2c_filter[6:0]<=ps2c_filter[7:1];ps2d_filter[7]<=ps2_data;ps2d_filter[6:0]<=ps2c_filter[7:1];if(ps2c_filter==8'b1111_1111)ps2cf<=1;elseif(ps2c_filter==8'b0000_0000)ps2cf<=0;if(ps2d_filter==8'b1111_1111)ps2df<=1;elseif(ps2d_filter==8'b0000_0000)ps2df<=0;endendalways@(negedge ps2cf or negedge rst_n)beginif(!rst_n)beginshift1<=0;shift2<=1;endelsebeginshift1<={ps2df,shift1[10:1]};shift2<={shift1[0],shift2[10:1]};endendparameterone = 16'b0001_0110_0001_0110,//{16,16},two = 16'b0001_1110_0001_1110,//{1e,1e},three = 16'b0010_0110_0010_0110,//{26,26},four = 16'b0010_0101_0010_0101,//{25,25},onen = 16'b1111_0000_0001_0110,//{F0,16},twon = 16'b1111_0000_0001_1110,//{F0,1E},threen = 16'b1111_0000_0010_0110,//{F0,26},fourn = 16'b1111_0000_0010_0101;//{F0,25};always@(xkey)case(xkey)one:key_val<=4'b1000;two:key_val<=4'b0100;three:key_val<=4'b0010;four:key_val<=4'b0001;onen:key_val<=4'b0000;twon:key_val<=4'b0000;threen:key_val<=4'b0000;fourn:key_val<=4'b0000;default:key_val<=4'b0000;endcaseendmodulemodule keyboard(input sys_clk,// input rst_n,input ps2_clk,input ps2_data,output reg[3:0] key_val);wire [15:0]xkey;reg ps2cf,ps2df;reg clk25=0;reg [7:0]ps2c_filter,ps2d_filter;reg [10:0]shift1,shift2;assign xkey={shift2[8:1],shift1[8:1]};assign rst_n=1;always@(posedge sys_clk)clk25=~clk25;always@(posedge clk25 or negedge rst_n)beginif(!rst_n)beginps2c_filter<=0;ps2d_filter<=0;ps2cf<=1;ps2df<=1;endelsebeginps2c_filter[7]<=ps2_clk;ps2c_filter[6:0]<=ps2c_filter[7:1];ps2d_filter[7]<=ps2_data;ps2d_filter[6:0]<=ps2c_filter[7:1];if(ps2c_filter==8'b1111_1111)ps2cf<=1;elseif(ps2c_filter==8'b0000_0000)ps2cf<=0;if(ps2d_filter==8'b1111_1111)ps2df<=1;elseif(ps2d_filter==8'b0000_0000)ps2df<=0;endendalways@(negedge ps2cf or negedge rst_n)beginif(!rst_n)beginshift1<=0;shift2<=1;endelsebeginshift1<={ps2df,shift1[10:1]};shift2<={shift1[0],shift2[10:1]};endendparameterone = 16'b0001_0110_0001_0110,//{16,16},two = 16'b0001_1110_0001_1110,//{1e,1e},three = 16'b0010_0110_0010_0110,//{26,26},four = 16'b0010_0101_0010_0101,//{25,25},onen = 16'b1111_0000_0001_0110,//{F0,16},twon = 16'b1111_0000_0001_1110,//{F0,1E},threen = 16'b1111_0000_0010_0110,//{F0,26},fourn = 16'b1111_0000_0010_0101;//{F0,25};always@(xkey)case(xkey)one:key_val<=4'b1000;two:key_val<=4'b0100;three:key_val<=4'b0010;four:key_val<=4'b0001;onen:key_val<=4'b0000;twon:key_val<=4'b0000;threen:key_val<=4'b0000;fourn:key_val<=4'b0000;default:key_val<=4'b0000;endcaseendmodule4、仿真波形图和波形解释:(1)、仿真波形图:(2)、波形解释:将系统的50Mhz的时钟频率进行分频为1hz的频率。

基于FPGA的数字钟

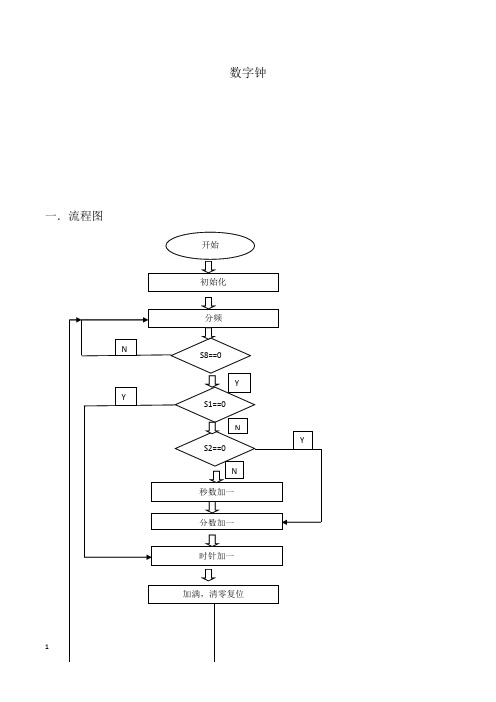

数字钟一.流程图二.功能解释功能:显示时—分—秒、整点报时、小时和分钟可调等基本功能。

整个钟表的工作应该是在1Hz信号的作用下进行,这样每来一个时钟信号,秒增加1秒,当秒从59秒跳转到00秒时,分钟增加1分,同时当分钟从59分跳转到00分时,小时增加1小时,小时的范围为0~23时。

为了显示的方便,由于分钟和秒钟显示的范围都是从0~59,所以可以用一个3位的二进制码显示十位,用一个四位的二进制码(BCD码)显示个位,对于小时因为他的范围是从0~23,所以可以用一个2位的二进制码显示十位,用一个4位的二进制码(BCD码)显示个位。

调整时间的按键用按键模块的S1和S2,S1调节小时,每按下一次,小时增加一个小时;S2调整分钟,每按下一次,分钟增加一分钟。

另外用S8按键作为系统时钟复位,复位后全部显示00—00—00三.代码,仿真图1.分频器分频器的作用是对50Mhz的系统时钟信号进行分频,得到频率为1000hz的信号,作为显示器的输入信号。

源程序如下:module fenpin(input CP, output CPout );reg CPout;reg [31:0] Cout;reg CP_En;always @(posedge CP ) //将50MHz分频为1kHzbeginCout <= (Cout == 32'd50000) ? 32'd0 : (Cout + 32'd1);CP_En <= (Cout == 32'd50000) ? 1'd1 : 1'd0;CPout <= CP_En;endendmodule功能仿真波形如图所示(以五分频为例):2.控制器和计数器控制器的作用是,调整小时和分钟的值,并能实现清零功能。

计数器的作用是实现分钟和秒钟满60进1,小时则由23跳到00。

当到达59分55秒的时候,LED灯会闪烁来进行报时。

基于FPGA的多功能数字钟设计

本科生毕业论文(设计)题目: 基于FPGA 的多功能数字钟设计学 院 电子信息工程学院 学科门类 工学装 订 线基于FPGA的多功能数字钟设计摘要当前基于各种数字器件的数字钟种类繁多,对于不同的数字器件的设计方式有所不同,例如基于单片机的数字钟设计和基于CPLD的数字钟设计以及基于FPGA的数字钟设计等等。

可以根据不同的设计要求如响应灵敏度等选择不同的数字器件进行合理设计。

本文介绍基于FPGA的多功能数字钟设计,FPGA具有硬件实现数据处理具有实时性高,可靠稳定的优点。

在硬件方面主要由控制开关、消抖电路、APEX 20KE FPGA 和LED显示等几部分组成。

在编程方面采用VerilogHDL语言实现编程,仿真环境采用MAX+PLUSⅡ软件,以实现数字计时,闹铃和定点报时等功能设计。

该系统具有体积小、功耗低、价格便宜、安全可靠,维护和升级方便的优点,具有较好的应用前景。

关键词:数字钟 FPGA VerilogHDL MAX+PLUSⅡThe Digital(多功能)Clock Based on FPGAABSTRACTThere are many of logic devices which are based on the digital clock at present.The methods are different For a different logic device design. For example, The digital clock based on SCN(Switched Circuit Network), The digital clock based on CPLD(Complex Programable Logic Device)and The digital clock based onFPGA (Field Programmable Gate Array),and so on.We can choosing a different logic devices reasonable to design based on different design requirements such as sensitivity. This article introduces the digital clock based on FPGA. FPGA with data-processing hardwareWith real-time high, the advantages of reliable stability. In terms of hardware from the main control switches, circuit Consumers buffeting, APEX 20KE FPGA and the LED display,We using Programming VerilogHDL hardware On the hardware side programming,and they can digital hardware logic on time, alarm and fixed-point design features such as timekeepingKey words:The Digital Clock Field Programmable Gate Array VerilogHDL MAX+PLUSⅡ目录一概述 (1)1.1 课题的来源、意义 (1)1.2 课题的研究目标、内容及方法手段 (1)1.2.1 课题的研究目标、内容 (1)1.2.2课题的研究方法及手段 (1)二数字钟的原理及软硬件的选择 (3)2.1系统原理 (3)2.2数字钟硬件的选择和设计 (4)2.2.1消抖电路的设计 (5)2.2.2 FPGA的选择 (5)2.2.3 LED显示模块的设计 (6)2.2.4数字钟编译仿真软件的选择 (6)2.2.5数字钟编程语言的选择 (7)三程序设计部分 (8)3.1编译仿真波形及分析 (8)3.1.1主控模块 (8)3.1.2时间模块 (8)3.1.3时间数据与时间设置 (10)3.1.4时间及其设置模块 (11)3.1.5显示模块 (12)3.1.6秒表模块 (13)3.1.7日期自动工作模块 (14)3.1.8日期设置模块 (15)3.1.9日期设置与自动工作模块 (16)3.1.10闹钟模块 (17)3.1.11分频模块 (18)3.1.12多功能数字钟电路图 (19)四验证 (21)五结论 (22)谢辞 (23)参考文献 (24)附录 (25)一概述1.1课题的来源、意义20世纪末,电子技术获得了飞速的发展,在其推动下,现代电子产品几乎渗透了社会的各个领域,有力地推动了社会生产力的发展和社会信息化程度的提高,同时也使现代电子产品性能进一步提高,产品更新换代的节奏也越来越快。

基于FPGA的数字时钟设计

基于FPGA的数字时钟设计数字时钟是现代生活中必不可少的时间展示设备,广泛应用于各种场所,如家庭、办公室、学校等。

随着科技的不断发展,数字时钟的功能也得到不断升级,为人们日常生活提供了更多的便利和体验。

本文将介绍基于FPGA的数字时钟设计方案。

FPGA(Field Programmable Gate Array)是可编程门阵列的缩写,是一种现场可编程逻辑器件。

FPGA具有可编程性强、功能强大、极低的延迟等特点,被广泛应用于数字系统设计中。

本文中使用FPGA来实现数字时钟设计方案。

数字时钟的核心是计时电路,计时电路可以通过FPGA实现,使用FPGA来实现数字时钟的主要优点是可编程性强,能够满足不同需求的设计。

一、数字时钟的设计思路1、时钟信号的产生数字时钟的起点是时钟信号的产生,时钟信号的产生一般需要使用晶振。

晶振可以在一定频率范围内提供稳定的时钟信号。

FPGA可以通过将晶振与逻辑电路相连接,从而得到稳定的时钟信号。

2、计时电路的设计在数字时钟中,需要实现时、分、秒的计时功能。

这可以采用三个计时器来实现。

计时器可以使用FPGA内置的计数器实现,也可以通过逻辑电路实现。

计时器根据时钟信号的变化而变化,通过累计时钟信号的脉冲数计算出时、分、秒。

3、数码管的控制数字时钟的时间要通过数码管进行显示,数码管需要接受来自FPGA的控制信号才能正常显示数字。

通常采用多路复用器的方式来控制数码管的显示。

这里可以使用FPGA内置的多路复用器实现,FPGA输出控制信号,控制多路复用器选择哪个数码管进行显示。

数字时钟的硬件设计主要包括以下部分:时钟信号发生电路包含晶振以及晶振产生的时钟信号经过变压器传送到电路板上。

在电路板上,时钟信号经过电路处理,产生一定的电平和频率,供后续计时模块使用。

2、计时模块计时模块包括三个计时器,分别用于计算时、分、秒。

计时器通过累加时钟信号的脉冲数计算时间。

计时模块的输出需要送到数码管的控制模块进行显示。

基于FPGA的数字钟设计

电子课程设计实验报告本报告共有两个项目——数字钟和音乐计算器,每个项目由三部分组成,第一部分为工程顶层图,第二部分为模块划分及功能,第三部分为实验中遇到的问题及解决方法,最后是对课程的一点建议。

项目一:数字钟一.顶层图二.模块划分及功能数字钟主要有分频,输入,计时,闹钟,数据选择,音乐,显示七大模块,其中各模块的功能介绍如下:1.分频模块(fenpin):功能是产生用于计时,扫描输入,扫描显示,以及播放音乐所需的各个频率的信号。

2.输入模块(input):功能是识别键盘的输入,具体来说,主要是判断是否有键按下,并且确定按下的是哪个键,并给出相应的操作信号。

3.计时模块(minute,hour):分为分计时(minute)和小时计时(hour)两个小模块,分别完成分位与小时为的计时与时间设置功能,正常计时是每次清零后从00:00开始计时,若预置时间,则从预置数开始计。

4.闹钟模块(alart):功能是设置闹钟和整点报时,当切换至闹钟设置时,可以输入时间,并将其记录下来,当时钟时间与闹钟预设时间相同时,给出一个脉冲信号,另一功能是当时钟为整点时给出一个脉冲信号。

5.数据选择(sel):功能是设置时间时将键盘输入的数据传给计时和显示模块,当设置闹钟时将键盘输入的数据传给闹钟和显示模块。

6.音乐(music):功能是当闹钟部分给出给出响铃信号(闹钟和整点)时响起两端不同的音乐。

7.扫描显示(display):功能是在数码管上分别显示时间的四位数值,并且当时间设置至某一位时点亮相应的小数点。

三.问题及解决方法1.语法错误因为第一个项目是数字钟,刚接触时对VHDL语言还不是非常熟悉,因此常常会犯忘掉分号或是END IF 之类的错误,这类问题根据编译时的提示都能解决。

2.键盘的稳定性问题最初设计的键盘扫描方式是一直扫描,当有按键按下时也不断给出该键的位置并执行相应的操作,但是在上板后发现键盘不稳定,具体表现是当按下某个键时两次扫描给出的位置可能有偏差,例如按着2键,可能在中间某一次会显示成3,最后解决的方法是当检测到如果有按键按下时边将扫描列的高电平锁定在该列,例如检测到有按键1时,便将列输出锁定为“1000”,直到按键松开时再从下一列重新开始扫描,这样键盘就稳定了很多。

FPGA课程设计多功能数字钟讲解

多功能数字钟开课学期:2014—2015 学年第二学期课程名称:FPGA课程设计学院:信息科学与工程学院专业:集成电路设计与集成系统班级:学号:姓名:任课教师:2015 年7 月21 日说明一、论文书写要求与说明1.严格按照模板进行书写。

自己可以自行修改标题的题目2.关于字体:a)题目:三号黑体加粗。

b)正文:小四号宋体,行距为1.25倍。

3.严禁抄袭和雷同,一经发现,成绩即判定为不及格!!!二、设计提交说明1.设计需要提交“电子稿”和“打印稿”;2.“打印稿”包括封面、说明(即本页内容)、设计内容三部分;订书机左边装订。

3.“电子稿”上交:文件名为“FPGA课程设计报告-班级-学号-某某.doc”,所有报告发送给班长,由班长统一打包后统一发送到付小倩老师。

4.“打印稿”由班长收齐后交到:12教305办公室;5.上交截止日期:2015年7月31日17:00之前。

第一章绪论2关键词:FPGA,数字钟3第二章FPGA的相关介绍32.1 FPGA概述42.2 FPGA特点42.3 FPGA设计注意5第三章Quartus II与Verilog HDL相关介绍63.1 Quartus II63.2 Verilog HDL7第四章设计方案74.1数字钟的工作原理74.2 按键消抖84.3时钟复位84.4时钟校时84.5数码管显示模块。

8第五章方案实现与验证85.1产生秒脉冲85.2秒个位进位95.3按键消抖95.4复位按键设置95.5 数码管显示。

105.6 RTL结构总图11第六章实验总结14第七章Verilog HDL源代码附录15第一章绪论现代社会的标志之一就是信息产品的广泛使用,而且是产品的性能越来越强,复杂程度越来越高,更新步伐越来越快。

支撑信息电子产品高速发展的基础就是微电子制造工艺水平的提高和电子产品设计开发技术的发展。

前者以微细加工技术为代表,而后者的代表就是电子设计自动化(electronic design automatic, EDA)技术。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

多功能数字钟开课学期:2014—2015 学年第二学期课程名称:FPGA课程设计学院:信息科学与工程学院专业:集成电路设计与集成系统班级:学号:姓名:任课教师:2015 年7 月21 日说明一、论文书写要求与说明1.严格按照模板进行书写。

自己可以自行修改标题的题目2.关于字体:a)题目:三号黑体加粗。

b)正文:小四号宋体,行距为1.25倍。

3.严禁抄袭和雷同,一经发现,成绩即判定为不及格!!!二、设计提交说明1.设计需要提交“电子稿”和“打印稿”;2.“打印稿”包括封面、说明(即本页内容)、设计内容三部分;订书机左边装订。

3.“电子稿”上交:文件名为“FPGA课程设计报告-班级-学号-姓名.doc”,所有报告发送给班长,由班长统一打包后统一发送到付小倩老师。

4.“打印稿”由班长收齐后交到:12教305办公室;5.上交截止日期:2015年7月31日17:00之前。

第一章绪论 (3)关键词:FPGA,数字钟 (3)第二章FPGA的相关介绍 (4)2.1 FPGA概述 (4)2.2 FPGA特点 (4)2.3 FPGA设计注意 (5)第三章Quartus II与Verilog HDL相关介绍 (7)3.1 Quartus II (7)3.2 Verilog HDL (7)第四章设计方案 (8)4.1数字钟的工作原理 (8)4.2 按键消抖 (8)4.3时钟复位 (8)4.4时钟校时 (8)4.5数码管显示模块。

(8)第五章方案实现与验证 (9)5.1产生秒脉冲 (9)5.2秒个位进位 (9)5.3按键消抖 (9)5.4复位按键设置 (10)5.5 数码管显示。

(10)5.6 RTL结构总图 (11)第六章实验总结 (14)第七章Verilog HDL源代码附录 (15)第一章绪论现代社会的标志之一就是信息产品的广泛使用,而且是产品的性能越来越强,复杂程度越来越高,更新步伐越来越快。

支撑信息电子产品高速发展的基础就是微电子制造工艺水平的提高和电子产品设计开发技术的发展。

前者以微细加工技术为代表,而后者的代表就是电子设计自动化(electronic design automatic, EDA)技术。

本设计采用的VHDL是一种全方位的硬件描述语言,具有极强的描述能力,能支持系统行为级、寄存器传输级和逻辑门级这三个不同层次的设计;支持结构、数据流、行为三种描述形式的混合描述,覆盖面广,抽象能力强,因此在实际应用中越来越广泛。

ASIC是专用的系统集成电路,是一种带有逻辑处理的加速处理器;而FPGA是特殊的ASIC芯片,与其它的ASIC芯片相比,它具有设计开发周期短、设计制造成本低、开发工具先进、标准产品无需测试、质量稳定以及可实时在线检测等优点。

在控制系统中,键盘是常用的人机交换接口,当所设置的功能键或数字键按下的时候,系统应该完成该键所对应的功能。

因此,按键信息输入是与软件结构密切相关的过程。

根据键盘结构的不同,采用不同的编码方法,但无论有无编码以及采用什么样的编码,最后都要转换成为相应的键值,以实现按键功能程序的转移。

[1]钟表的数字化给人们生产生活带来了极大的方便,而且大大地扩展了钟表原先的报时功能。

诸如定时自动报警、定时启闭电路、定时开关烘箱、通断动力设备,甚至各种定时电气的自动启用等,所有这些都是以钟表数字化为基础的。

因此研究数字钟以及扩大其应用有着非常现实的意义。

关键词:FPGA,数字钟第二章FPGA的相关介绍FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。

它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

2.1 FPGA概述系统设计师可以根据需要通过可编辑的连接把FPGA内部的逻辑块连接起来,就好像一个电路试验板被放在了一个芯片里。

一个出厂后的成品FPGA的逻辑块和连接可以按照设计者而改变,所以FPGA可以完成所需要的逻辑功能。

FPGA一般由3种可编程电路和一个用于存放编程数据的静态存储器SRAM组成。

这3种可编程电路是:可编程逻辑模块(CLB--Configurable Logic Block)、输入/输出模块(IOB--I/O Block)和互连资源(IR—Interconnect Resource)。

可编程逻辑模块CLB 是实现逻辑功能的基本单元,它们通常规则的排列成一个阵列,散布于整个芯片;可编程输入/输出模块(IOB)主要完成芯片上的逻辑与外部封装脚的接口,它通常排列在芯片的四周;可编程互连资源包括各种长度的连接线段和一些可编程连接开关,它们将各个CLB之间或CLB、IOB之间以及IOB之间连接起来,构成特定功能的电路。

FPGA一般来说比ASIC(专用集成芯片)的速度要慢,无法完成复杂的设计,而且消耗更多的电能。

但是他们也有很多的优点比如可以快速成品,可以被修改来改正程序中的错误和更便宜的造价。

厂商也可能会提供便宜的但是编辑能力差的FPGA。

因为这些芯片有比较差的可编辑能力,所以这些设计的开发是在普通的FPGA上完成的,然后将设计转移到一个类似于ASIC的芯片上。

另外一种方法是用CPLD(复杂可编程逻辑器件备)。

2.2 FPGA特点FPGA的基本特点主要有:1)采用FPGA设计ASIC电路,用户不需要投片生产,就能得到合用的芯片。

2)FPGA可做其它全定制或半定制ASIC电路的中试样片。

3)FPGA内部有丰富的触发器和I/O引脚。

4)FPGA是ASIC电路中设计周期最短、开发费用最低、风险最小的器件之一。

5)FPGA采用高速CHMOS工艺,功耗低,可以与CMOS、TTL电平兼容。

可以说,FPGA芯片是小批量系统提高系统集成度、可靠性的最佳选择之一。

编程互连资源IR可以将FPGA内部的CLB和CLB之间、CLB和IOB之间连接起来,构成各种具有复杂功能的系统。

FPGA是由存放在片内RAM中的程序来设置其工作状态的,因此,工作时需要对片内的RAM进行编程。

用户可以根据不同的配置模式,采用不同的编程方式。

加电时,FPGA芯片将EPROM中数据读入片内编程RAM中,配置完成后,FPGA 进入工作状态。

掉电后,FPGA恢复成白片,内部逻辑关系消失,因此,FPGA能够反复使用。

FPGA的编程无须专用的FPGA编程器,只须用通用的EPROM、PROM编程器即可。

当需要修改FPGA功能时,只需换一片EPROM即可。

这样,同一片FPGA,不同的编程数据,可以产生不同的电路功能。

因此,FPGA的使用非常灵活。

FPGA有多种配置模式:并行主模式为一片FPGA加一片EPROM的方式;主从模式可以支持一片PROM编程多片FPGA;串行模式可以采用串行PROM编程FPGA;外设模式可以将FPGA作为微处理器的外设,由微处理器对其编程。

2.3 FPGA设计注意不管你是一名逻辑设计师、硬件工程师或系统工程师,甚或拥有所有这些头衔,只要你在任何一种高速和多协议的复杂系统中使用了FPGA,你就很可能需要努力解决好器件配置、电源管理、IP集成、信号完整性和其他的一些关键设计问题。

不过,你不必独自面对这些挑战,因为在当前业内领先的FPGA公司里工作的应用工程师每天都会面对这些问题,而且他们已经提出了一些将令你的设计工作变得更轻松的设计指导原则和解决方案。

本次实验所采用的FPGA器件是Altera Cyclone V 5CSEMA5F31C6NFPGA实物图FPGA数码管介绍,每节数码管低电平点亮高电平熄灭。

LED序号如下图所示:根据上图所示的顺序,可以得出显示的数组代码。

4'd0: HEX0=7'b1000000; //0 低电平点亮高电平熄灭4'd1: HEX0=7'b1111001; //14'd2: HEX0=7'b0100100; //24'd3: HEX0=7'b0110000; //34'd4: HEX0=7'b0011001; //44'd5: HEX0=7'b0010010; //54'd6: HEX0=7'b0000010; //64'd7: HEX0=7'b1111000; //74'd8: HEX0=7'b0000000; //84'd9: HEX0=7'b0010000; //9default: HEX0=7'b1111111; //不符合条件的显示零第三章Quartus II与Verilog HDL相关介绍3.1 Quartus IIQuartus II 是Altera公司的综合性PLD/FPGA开发软件,原理图、VHDL、VerilogHDL 以及AHDL(Altera Hardware 支持Description Language)等多种设计输入形式,内嵌自有的综合器以及仿真器,可以完成从设计输入到硬件配置的完整PLD设计流程。

Quartus II支持Altera的IP核,包含了LPM/MegaFunction宏功能模块库,使用户可以充分利用成熟的模块,简化了设计的复杂性、加快了设计速度。

对第三方EDA工具的良好支持也使用户可以在设计流程的各个阶段使用熟悉的第三方EDA工具。

Quartus II 软件拥有友好的界面,使用便捷,功能强大,当中可编程逻辑设计环境采用完成集成化,是先进的EDA工具软件。

该软件具备诸多特点(例如:开放性,与结构无联系,多平台设计,完全集成化,设计库丰富、工具模块化等),支持原理图、VHDL、VerilogHDL以及AHDL等多种设计输入形式。

Quartus II能够在多系统上使用,为用户的设计方式提供了完善的图形界面。

具有运行速度快,界面统一,功能集中,学用简单等特点。

3.2 Verilog HDLVerilog HDL是一种硬件描述语言(HDL:Hardware Description Language),以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。

Verilog HDL和VHDL是世界上最流行的两种硬件描述语言,都是在20世纪80年代中期开发出来的。

前者由Gateway Design Automation公司(该公司于1989年被Cadence公司收购)开发。

两种HDL均为IEEE 标准。

第四章设计方案4.1数字钟的工作原理振荡器产生稳定的高频脉冲信号,作为数字钟的时间基准,然后经过分频器输出标准秒脉冲。