FPGA可编程逻辑器件芯片EP2S90F780C4N中文规格书

FPGA可编程逻辑器件芯片EP3SL70F780C4中文规格书

•Encrypted transistor and logic cell library models •Encrypted input or output buffer circuit models for single-ended and differential I/O •Single-ended and differential sample SPICE decks •User guide describing the model usageThe HSPICE models provide options to simulate buffer behavior for following I/O feature:•RS OCT with and without calibration •RT OCT with calibration •Internal weak pull-up •Open drain •Bus-hold5.1.20.2. Net Length ReportsThe net length information consists of the package trace delay information from die pad to package pin. Each pin in an FPGA package has its own net length information.This information is important for you to perform board trace compensation to optimize the channel-to-channel skew on your board design.You can obtain the net length reports for Intel Agilex devices from the Board Design Guidelines Solutions Center under Tools, Models, and Libraries .Related InformationBoard Design Guidelines Solution Center: Tools, Models, and Libraries Download center for net length reports for Intel FPGA devices5.2. Intel Agilex LVDS SERDES Design Guidelines5.2.1. Use PLLs in Integer PLL Mode for LVDSEach I/O sub-bank has its own PLL (I/O PLL) to drive the SERDES channels. These I/O PLLs operate in integer mode only.5.2.2. Use High-Speed Clock from PLL to Clock SERDES OnlyThe high-speed clock generated from the PLL is intended to clock the SERDES circuitry only. Do not use the high-speed clock to drive other logic because the allowed frequency to drive the core logic is restricted by the PLL F OUT specification.For more information about the F OUT specification, refer to the Intel Agilex Device Data Sheet .5.I/O and LVDS SERDES Design GuidelinesUG-20214 | 2021.04.05Send Feedback5.2.3. Pin Placement for Differential ChannelsEach GPIO sub-bank contains its own PLL. A PLL can drive all receiver and transmitter channels in the same sub-bank. However , the individual PLL cannot drive receiver and transmitter channels in another I/O sub-bank. You must use the dedicated clock pins to drive the LVDS PLLs.The pin index number 0-47 and pin index number 48-95 from device pin out files are respectively assigned to bottom sub-bank and top sub-bank in a single GPIO bank.Refer to External Memory Interface Pin Placement Requirements for more information about the sub-bank arrangement for each I/O bank.PLLs Driving DPA-Enabled Differential Receiver ChannelsFor differential receivers, the PLL can drive all channels in the same I/O sub-bank but cannot drive across banks.Each differential receiver in an I/O bank has a dedicated DPA circuit to align the phase of the clock to the data phase of its associated channel.DPA usage adds some constraints to the placement of high-speed differential receiver channels. The Intel Quartus Prime compiler automatically checks the design and issues error messages if there are placement guidelines violations. Adhere to the guidelines to ensure proper high-speed I/O operation.Related InformationExternal Memory Interface Pin Placement Requirements on page 1225.2.4. SERDES Pin Pairs for Soft-CDR ModeYou can use only specific SERDES pin pairs in soft-CDR mode. Refer to the pinout file of each device to determine the SERDES pin pairs that support the soft-CDR mode.5.2.5. Placing LVDS Transmitters and Receivers in the Same I/O BankIf you want to place both LVDS transmitter and receiver interfaces in the same I/O bank, you can use an external PLL.5.2.5.1. Using an External PLL•To use an external PLL, in the LVDS SERDES IP parameter editor , turn on the Use external PLL option.•You can generate two instances of the LVDS SERDES IP—a receiver and a transmitter .•In each instance, you can use up to the following number of channels:—12 transmitters —12 DPA or non-DPA receivers —8 soft-CDR receivers5.I/O and LVDS SERDES Design GuidelinesUG-20214 | 2021.04.05Send Feedback6.Troubleshooting GuidelinesGPIO Debug GuidelinesThe following table lists the failure symptoms and the associated debug actions that you can take to identify the failure areas when designing GPIO systems with Intel Agilex devices. These debug guidelines are just initial debug actions and do not necessarily resolve the failures in your designs.Table 72.GPIO Debug Guidelines Failure SymptomsRecommended Debug Actions 1.2 V LVCMOS output at the entire bank does not reach 1.2V •Check the power-up and power-down sequences of each voltage rail with respect to time.•Compare the power sequences as per recommendation in the Intel Agilex Power Management User Guide.•Verify the VCCIO_PIO voltage signal is 1.2 v.Intel Quartus Prime software shows an error messages to indicate incorrect I/O settings for V CCIO during design compilation.Error message example: Illegal constraint of I/O bank to the location <I/O bank>.•Select the I/O pins specified in the error message and check the I/O settings for the pins.Intel Quartus Prime software shows illegal I/O error message during design compilation.Error message example: Programmable VOD option is set to 1 for pin <pin_name>, but setting is not supported by <I/O standard>.•Select the I/O pins specified in the error message and set the pins to the correct I/O function. Refer to the device pin-outs file for more information about the pin functions.Unable to configure a pin as an open-drain output pin.•Make sure the pin is set to the correct voltage specification per the device data sheet.•To ensure the pin is correctly set to open-drain output,check the compilation report or the resource property editor .Unable to configure a pin to use the bus-hold feature.•Make sure the pin is not set to programmable pull-up resistor . The bus-hold feature is not available when the pin is set to programmable pull-up resistor .High-Speed SERDES I/O Debug GuidelinesThe following table lists the failure symptoms and the associated debug actions that you can take to identify the failure areas when designing high-speed SERDES systems with Intel Agilex devices. These debug guidelines are just initial debug actions and do not necessarily resolve the failures in your designs.UG-20214 | 2021.04.05Send FeedbackISO 9001:2015Registered。

FPGA可编程逻辑器件芯片EP3SL70F780C4N中文规格书

•fp32_adder_inexact•fp32_adder_overflow•fp32_adder_underflowFigure 34.Sum of Two FP16 Multiplication with FP32 Addition Modefp32_adder_invalidfp32_adder_inexactfp32_adder_overflowfp32_adder_underflow*This block diagram shows the functional representation of the DSP block. The pipeline registers are embedded within the various circuits of the DSP block.fp16_adder_zero(extended format)3.2.2.4. Sum of Two FP16 Multiplication with Accumulation ModeThis mode performs a summation of two half-precision multiplication and accumulatethe value into single-precision format:fp32_result(t) = [fp16_mult_top_a(t) * fp16_mult_top_b(t)] + [fp16_mult_bot_a(t) *fp16_mult_bot_b(t)] + fp32_result(t-1)The following are exception flags supported in flushed and bfloat16 formats:•fp16_mult_top_invalid•fp16_mult_top_inexact•fp16_mult_top_overflow•fp16_mult_top_underflow•fp16_mult_bot_invalid•fp16_mult_bot_inexact•fp16_mult_bot_overflow•fp16_mult_bot_underflow•fp16_adder_invalid•fp16_adder_inexact•fp16_adder_overflow•fp16_adder_underflow•fp32_adder_invalid3.Intel Agilex Variable Precision DSP Blocks Operational ModesUG-20213 | 2021.02.05Send Feedback•fp32_adder_inexact•fp32_adder_overflow•fp32_adder_underflowThe following are exception flags supported in extended format:•fp16_mult_top_invalid•fp16_mult_top_inexact•fp16_mult_top_infinite•fp16_mult_top_zero•fp16_mult_bot_invalid•fp16_mult_bot_inexact•fp16_mult_bot_infinite•fp16_mult_bot_zero•fp16_adder_invalid•fp16_adder_inexact•fp16_adder_infinite•fp16_adder_zero•fp32_adder_invalid•fp32_adder_inexact•fp32_adder_overflow•fp32_adder_underflowFigure 35.Sum of Two FP16 Multiplication with Accumulation Mode*This block diagram shows the functional representation of the DSP block. The pipeline registers are embedded within the various circuits of the DSP block.fp32_adder_invalid fp32_adder_inexact fp32_adder_overflow fp32_adder_underflowfp16_adder_zero(extended format)3.Intel Agilex Variable Precision DSP Blocks Operational ModesUG-20213 | 2021.02.05Send Feedback3.2.2.5. FP16 Vector One ModeThis mode performs a summation of two half-precision multiplications with the chainininput from the previous variable DSP Block. The output is a single-precision floating-point value which is fed into chainout.Table 19.Equations Applied to FP16 Vector One ModeChainin Parameter Vector One with Floating-pointAddition Vector One with Floating-pointSubtractionDisable fp32_result = (fp16_mult_top_a *fp16_mult_top_b) + (fp16_mult_bot_a*fp16_mult_bot_b)fp32_chainout = fp32_adder_a fp32_result = (fp16_mult_top_a *fp16_mult_top_b) - (fp16_mult_bot_a *fp16_mult_bot_b)fp32_chainout = fp32_adder_aEnable fp32_result = (fp16_mult_top_a *fp16_mult_top_b) + (fp16_mult_bot_a*fp16_mult_bot_b) + fp32_chaininfp32_chainout = fp32_adder_a fp32_result = (fp16_mult_top_a *fp16_mult_top_b) - (fp16_mult_bot_a *fp16_mult_bot_b) - fp32_chaininfp32_chainout = fp32_adder_aThe following are exception flags supported in flushed and bfloat16 formats:•fp16_mult_top_invalid•fp16_mult_top_inexact•fp16_mult_top_overflow•fp16_mult_top_underflow•fp16_mult_bot_invalid•fp16_mult_bot_inexact•fp16_mult_bot_overflow•fp16_mult_bot_underflow•fp16_adder_invalid•fp16_adder_inexact•fp16_adder_overflow•fp16_adder_underflow•fp32_adder_invalid•fp32_adder_inexact•fp32_adder_overflow•fp32_adder_underflowThe following are exception flags supported in extended format:•fp16_mult_top_invalid•fp16_mult_top_inexact•fp16_mult_top_infinite•fp16_mult_top_zero•fp16_mult_bot_invalid•fp16_mult_bot_inexact3.Intel Agilex Variable Precision DSP Blocks Operational ModesUG-20213 | 2021.02.05Send Feedback。

FPGA可编程逻辑器件芯片EP1S20F780C5中文规格书

dataa datab datac datad

Six-Input LUT

(Function0)

datae1 dataf1

Six-Input LUT

(Function1)

combout0 combout1

In a sparsely used device, functions that could be placed into one ALM may be implemented in separate ALMs. The Quartus II Compiler spreads a design out to achieve the best possible performance. As a device begins to fill up, the Quartus II software automatically utilizes the full potential of the Stratix II ALM. The Quartus II Compiler automatically searches for functions of common inputs or completely independent functions to be placed into one ALM and to make efficient use of the device resources. In addition, you can manually control resource usage by setting location assignments.

FPGA可编程逻辑器件芯片EP2SGX60DF780C5中文规格书

PLL SpecificationsPLLSpecificationsf See the DC & Switching Characteristics chapter in volume 1 of theStratix II GX Device Handbook (or the Stratix II Device Handbook) forinformation about PLL timing specificationsClocking Stratix II and Stratix II GX devices provide a hierarchical clock structureand multiple PLLs with advanced features. The large number of clockingresources in combination with the clock synthesis precision provided byenhanced and fast PLLs provides a complete clock-management solution.Global and Hierarchical ClockingStratix II and Stratix II GX devices provide 16 dedicated global clocknetworks and 32 regional clock networks. These clocks are organized intoa hierarchical clock structure that allows for 24 unique clock sources perdevice quadrant with low skew and delay. This hierarchical clockingscheme provides up to 48 unique clock domains within the entireStratix II or Stratix II GX device. Table1–17 lists the clock resourcesavailable on Stratix II devices.There are 16 dedicated clock pins (CLK[15..0]) on Stratix II andStratix II GX devices to drive either the global or regional clock networks.Four clock pins drive each side of the Stratix II device, as shown inFigures1–39and 1–40. Enhanced and fast PLL outputs can also drive theglobal and regional clock networks.Table1–17.Clock Resource Availability in Stratix II and Stratix II GX Devices(Part 1 of2)Description Stratix II Device Availability Stratix II GX Device Availability Number of clock input pins24 12Number of global clock networks1616Number of regional clocknetworks3232Global clock input sources Clock input pins, PLL outputs, logicarray Clock input pins, PLL outputs, logic array, inter-transceiver clocksRegional clock input sources Clock input pins, PLL outputs, logicarray Clock input pins, PLL outputs, logic array, inter-transceiver clocksNumber of unique clock sources in a quadrant 24 (16 global clocks and 8 regionalclocks)24 (16 GCLK and 8 RCLK clocks)Number of unique clock sources in the entire device 48 (16 global clocks and 32 regionalclocks)48 (16 GCLK and 32 RCLK clocks)ClockingTables1–20 and 1–21 show which PLLs are available in each Stratix II andStratix II GX device, respectively, and which input clock pin drives whichPLLs.Table1–20.Stratix II Device PLLs and PLL Clock Pin Drivers(Part 1 of2)Input PinAll Devices EP2S60 to EP2S180 Devices Fast PLLsEnhancedPLLsFast PLLsEnhancedPLLs 123456789101112CLK0v v v(1)v (1)CLK1(2)v v v(1)v (1)CLK2v v v(1)v (1)CLK3(2)v v v(1)v (1)CLK4v v CLK5v v CLK6v v CLK7v v CLK8v v v(1)v (1)CLK9 (2)v v v(1)v (1)CLK10v v v(1)v (1)CLK11 (2)v v v(1)v (1)CLK12v vCLK13v vCLK14v vCLK15v vPLL5_FB vPLL6_FB vPLL11_FB vPLL12_FB v PLL_ENA v v v v v v v v v v v v FPLL7CLK(2)vFPLL8CLK(2)vFPLL9CLK(2)vDocument Revision HistoryContents Stratix II Device Handbook, Volume2ClockingTables1–23 and 1–24 show the global and regional clocks that the PLLoutputs drive.Table1–23.Stratix II Global and Regional Clock Outputs From PLLs(Part 1 of3)Clock NetworkPLL Number and TypeEP2S15 through EP2S30 Devices EP2S60 through EP2S180 Devices Fast PLLsEnhancedPLLsFast PLLsEnhancedPLLs 123456789101112GCLK0v v v vGCLK1v v v vGCLK2v v v vGCLK3v v v vGCLK4v v GCLK5v v GCLK6v v GCLK7v v GCLK8v v v vGCLK9v v v vGCLK10v v v vGCLK11v v v vGCLK12v vGCLK13v vGCLK14v vGCLK15v vRCLK0v v vRCLK1v v vRCLK2v v vRCLK3v v vRCLK4v v vRCLK5v v vRCLK6v v vRCLK7v v vRCLK8v v RCLK9v v。

FPGA可编程逻辑器件芯片EP3SL50F780C4N中文规格书

Stratix III Device Handbook, Volume 2Electrical CharacteristicsThis chapter describes the electrical characteristics, switching characteristics, and I/O timing for Stratix ®III devices. Electrical characteristics include operating conditions and power consumption. Switching characteristics include core performance specifications and periphery performance. A glossary is also included for your reference.Operating ConditionsWhen Stratix III devices are implemented in a system, they are rated according to a set of defined parameters. To maintain the highest possible performance and reliability of Stratix III devices, system designers must consider the operating requirements described in this chapter.Stratix III devices are offered in both commercial and industrial grades. Commercial devices are offered in –2 (fastest), –3, –4, and –4L speed grades. Industrial devices are offered only in –3, –4, and –4L speed grades.1In this chapter, a prefix associated with the operating temperature range is attached to the speed grades; commercial with a “C” prefix and industrial with an “I” prefix. For example, commercial devices are indicated as C2, C3, C4, and C4L per respective speed grades. Industrial devices are indicated as I3, I4, and I4L.Absolute Maximum RatingsAbsolute maximum ratings define the maximum operating conditions for Stratix III devices. The values are based on experiments conducted with the device and theoretical modeling of breakdown and damage mechanisms. The functionaloperation of the device is not implied at these conditions. Conditions beyond those listed in Table 1–1 may cause permanent damage to the device. Additionally, device operation at the absolute maximum ratings for extended periods may have adverse effects on the device.Table 1–1.Absolute Maximum Ratings for Stratix III Devices (Note 1)(Part 1 of 2)SymbolParameterMinimum Maximum Unit V CCL Selectable core voltage power supply -0.5 1.65V V CC I/O registers power supply-0.5 1.65V V CCD_PLL Phase-locked loop (PLL) digital power supply -0.5 1.65V V CCA_PLL PLL analog power supply-0.5 3.75V V CCPT Programmable power technology power supply -0.5 3.75V V CCPGM Configuration pins power supply -0.5 3.9V V CCPD I/O pre-driver power supply -0.5 3.9V V CCIOI/O power supply-0.53.9VSIII52001-2.3Chapter 1:Stratix III Device Datasheet: DC and Switching CharacteristicsElectrical CharacteristicsStratix III Device Handbook, Volume 2V CC_CLKIN Differential clock input power supply (top and bottom I/O banks only)-0.5 3.75V V CCBAT Battery back-up power supply for design security volatile key register -0.5 3.75V V I DC Input voltage-0.5 4.0V T J Operating junction temperature -55125°C I OUT DC output current, per pin -2540mA T STGStorage temperature (No bias)-65150°CTable 1–1.Absolute Maximum Ratings for Stratix III Devices (Note 1)(Part 2 of 2)Symbol ParameterMinimum Maximum UnitChapter 1:Stratix III Device Datasheet: DC and Switching Characteristics Electrical CharacteristicsStratix III Device Handbook, Volume 2Table 1–2.Maximum Allowed Overshoot During TransitionsSymbolParameterConditionOvershoot Duration as a % ofHigh TimeUnit Vi (AC)AC Input Voltage (1)4100.000%4.0579.330%4.146.270%4.1527.030%4.215.800%4.259.240%4.3 5.410%4.353.160%4.4 1.850%4.45 1.080%4.50.630%4.550.370%4.60.220%4.650.130%4.70.074%4.750.043%4.80.025%4.850.015%Chapter 1:Stratix III Device Datasheet: DC and Switching CharacteristicsElectrical CharacteristicsStratix III Device Handbook, Volume 2V CCPGMConfiguration pins power supply, 3.3 V— 3.135 3.3 3.465V Configuration pins power supply, 3.0 V — 2.853 3.15V Configuration pins power supply, 2.5 V — 2.375 2.5 2.625V Configuration pins power supply, 1.8 V — 1.71 1.8 1.89V V CCPD (1)I/O pre-driver power supply, 3.3 V— 3.135 3.3 3.465V I/O pre-driver power supply, 3.0 V — 2.85 3 3.15V I/O pre-driver power supply, 2.5 V — 2.375 2.5 2.625V V CCIOI/O power supply, 3.3 V — 3.135 3.3 3.465V I/O power supply, 3.0 V— 2.85 3 3.15V I/O power supply, 2.5 V — 2.375 2.5 2.625V I/O power supply, 1.8 V — 1.71 1.8 1.89V I/O power supply, 1.5 V — 1.425 1.5 1.575V I/O power supply, 1.2 V— 1.14 1.2 1.26V V CC_CLKIN Differential clock input power supply (top and bottom I/O banks only)— 2.375 2.5 2.625V V CCBAT (3)Battery back-up power supply for design security volatile key register — 1.0— 3.3V V I DC Input voltage —-0.3— 3.6V V OOutput voltage—0—V CCIO V T J Operating junction temperatureFor commercialuse 0—85°C For industrial use (2)-40—100°C t RAMPPower Supply Ramptime (For V CCPT )Normal POR (PORSEL=0)50 µs — 5 ms —Fast POR (PORSEL=1)50 µs — 5 ms —Power Supply Ramptime (For all power supplies except V CCPT )Normal POR (PORSEL=0)50 µs —100 ms —Fast POR (PORSEL=1)50 µs—12 ms—Notes to Table 1–3:(1)V CCPD is 2.5, 3.0, or 3.3V. For a 3.3-V I/O standard, V CCPD =3.3 V. For a 3.0-V I/O standard, V CCPD = 3.0 V. For a 2.5-V or lower I/O standard,V CCPD =2.5V.(2)For the EP3SL340, EP3SE260, and EP3SL200 devices in the I4L ordering code, the industrial junction temperature range is from 0° C to100° C, regardless of supply voltage.(3)Altera recommends a 3.0-V nominal battery voltage when connecting V CCBAT to a battery for volatile key backup. If you do not use the volatilesecurity key, you may connect the V CCBAT to either GND or a 3.0-V power supply.Table 1–3.Recommended Operating Conditions for Stratix III Devices (Part 2 of 2)SymbolParameterConditionsMinimum Typical Maximum UnitChapter 1:Stratix III Device Datasheet: DC and Switching Characteristics Electrical CharacteristicsStratix III Device Handbook, Volume 2Parameter Symbol Conditions V CCIOUnit1.2V 1.5V 1.8V2.5V3.0V/3.3V MinMaxMinMaxMinMaxMinMaxMinMaxLow sustaining current I SUSL V IN >V IL (maximum)22.5 —25.0 —30.0 —50.0 —70.0 —µA High sustaining current I SUSH V IN <V IH (minimum)-22.5 —-25.0 —-30.0 —-50.0 —-70.0 —µA Low overdrive currentI ODL0V <V IN <V CCIO—120—160—200—300—500µA。

FPGA可编程逻辑器件芯片EP2S90F1020C5中文规格书

The Stratix II clock networks can be disabled (powered down) by both static and dynamic approaches. When a clock net is powered down, all the logic fed by the clock net is in an off-state thereby reducing the overall power consumption of the device.The global and regional clock networks can be powered down statically through a setting in the configuration (.sof or .pof) file. Clock networks that are not used are automatically powered down through configuration bit settings in the configuration file generated by the Quartus II software. The dynamic clock enable/disable feature allows the internal logic to control power up/down synchronously on GCLK and RCLK nets and PLL_OUT pins. This function is independent of the PLL and is applied directly on the clock network or PLL_OUT pin, as shown in Figures2–37 through2–39.1The following restrictions for the input clock pins apply:•CLK0 pin -> inclk[0] of CLKCTRL•CLK1 pin -> inclk[1] of CLKCTRL•CLK2 pin -> inclk[0] of CLKCTRL•CLK3 pin -> inclk[1] of CLKCTRLIn general, even CLK numbers connect to the inclk[0] port ofCLKCTRL, and odd CLK numbers connect to the inclk[1] portof CLKCTRL.Failure to comply with these restrictions will result in a no-fiterror.Enhanced & Fast PLLsStratix II devices provide robust clock management and synthesis using up to four enhanced PLLs and eight fast PLLs. These PLLs increase performance and provide advanced clock interfacing and clock-frequency synthesis. With features such as clock switchover,spread-spectrum clocking, reconfigurable bandwidth, phase control, and reconfigurable phase shifting, the Stratix II device’s enhanced PLLs provide you with complete control of clocks and system timing. The fast PLLs provide general purpose clocking with multiplication and phase shifting as well as high-speed outputs for high-speed differential I/O support. Enhanced and fast PLLs work together with the Stratix IIhigh-speed I/O and advanced clock architecture to provide significant improvements in system performance and bandwidth.Document Revision HistoryConfigurationf See the Configuring Stratix II & Stratix II GX Devices chapter in volume 2of the Stratix II Device Handbook or the Stratix II GX Device Handbook formore information about configuration schemes in Stratix II andStratix II GX devices.Device Security Using Configuration Bitstream EncryptionStratix II FPGAs are the industry’s first FPGAs with the ability to decrypta configuration bitstream using the Advanced Encryption Standard(AES) algorithm. When using the design security feature, a 128-bitsecurity key is stored in the Stratix II FPGA. To successfully configure aStratix II FPGA that has the design security feature enabled, it must beconfigured with a configuration file that was encrypted using the same128-bit security key. The security key can be stored in non-volatilememory inside the Stratix II device. This non-volatile memory does notrequire any external devices, such as a battery back-up, for storage.PPAMAX II device or microprocessor and flash device vJTAG Download cable (4)MAX II device or microprocessor andflash device Notes for Table 3–5:(1)In these modes, the host system must send a DCLK that is 4× the data rate.(2)The enhanced configuration device decompression feature is available, while the Stratix II decompression feature is not available.(3)Only remote update mode is supported when using the AS configuration scheme. Local update mode is not supported.(4)The supported download cables include the Altera USB Blaster universal serial bus (USB) port download cable,MasterBlaster serial/USB communications cable, ByteBlaster II parallel port download cable, and theByteBlasterMV parallel port download cable.Table 3–5.Stratix II Configuration Features (Part 2 of 2)ConfigurationSchemeConfiguration Method Design Security Decompression Remote System UpgradeConfiguration & Testing 1An encryption configuration file is the same size as a non-encryption configuration file. When using a serial configurationscheme such as passive serial (PS) or active serial (AS),configuration time is the same whether or not the designsecurity feature is enabled. If the fast passive parallel (FPP)scheme us used with the design security or decompressionfeature, a 4× DCLK is required. This results in a slowerconfiguration time when compared to the configuration time ofan FPGA that has neither the design security, nordecompression feature enabled. For more information aboutthis feature, refer to AN 341: Using the Design Security Feature inStratix II Devices. Contact your local Altera sales representativeto request this document.Device Configuration Data DecompressionStratix II FPGAs support decompression of configuration data, which saves configuration memory space and time. This feature allows you to store compressed configuration data in configuration devices or other memory, and transmit this compressed bit stream to Stratix II FPGAs. During configuration, the Stratix II FPGA decompresses the bit stream in real time and programs its SRAM cells.Stratix II FPGAs support decompression in the FPP (when using a MAX II device/microprocessor and flash memory), AS and PS configuration schemes. Decompression is not supported in the PPA configuration scheme nor in JTAG-based configuration.Remote System UpgradesShortened design cycles, evolving standards, and system deployments in remote locations are difficult challenges faced by modern system designers. Stratix II devices can help effectively deal with these challenges with their inherent re-programmability and dedicated circuitry to perform remote system updates. Remote system updates help deliver feature enhancements and bug fixes without costly recalls, reduce time to market, and extend product life.Stratix II FPGAs feature dedicated remote system upgrade circuitry to facilitate remote system updates. Soft logic (Nios® processor or user logic) implemented in the Stratix II device can download a new configuration image from a remote location, store it in configuration memory, and direct the dedicated remote system upgrade circuitry to initiate a reconfiguration cycle. The dedicated circuitry performs error detection during and after the configuration process, recovers from any error condition by reverting back to a safe configuration image, and provides。

FPGA可编程逻辑器件芯片EP2S130F780C4N中文规格书

Stratix II Architecture Figure2–56.DQS Phase-Shift Circuitry Notes(1), (2), (3), (4)Notes to Figure2–56:(1)There are up to 18 pairs of DQS and DQSn pins available on the top or the bottom of the Stratix II device. There areup to 10 pairs on the right side and 8 pairs on the left side of the DQS phase-shift circuitry.(2)The t module represents the DQS logic block.(3)Clock pins CLK[15..12]p feed the phase-shift circuitry on the top of the device and clock pins CLK[7..4]p feedthe phase circuitry on the bottom of the device. You can also use a PLL clock output as a reference clock to the phase-shift circuitry.(4)You can only use PLL 5 to feed the DQS phase-shift circuitry on the top of the device and PLL 6 to feed the DQSphase-shift circuitry on the bottom of the device.These dedicated circuits combined with enhanced PLL clocking andphase-shift ability provide a complete hardware solution for interfacingto high-speed memory.f For more information on external memory interfaces, refer to theExternal Memory Interfaces in Stratix II & Stratix II GX Devices chapter involume 2 of the Stratix II Device Handbook or the Stratix II GX DeviceHandbook.Programmable Drive StrengthThe output buffer for each Stratix II device I/O pin has a programmabledrive strength control for certain I/O standards. The LVTTL, LVCMOS,SSTL, and HSTL standards have several levels of drive strength that theuser can control. The default setting used in the Quartus II software is themaximum current strength setting that is used to achieve maximum I/Operformance. For all I/O standards, the minimum setting is the lowestdrive strength that guarantees the I OH/I OL of the standard. Usingminimum settings provides signal slew rate control to reduce systemnoise and signal overshoot.High-Speed Differential I/O with DPA SupportHigh-Speed Differential I/O with DPA SupportStratix II devices contain dedicated circuitry for supporting differential standards at speeds up to 1 Gbps. The LVDS and HyperTransport differential I/O standards are supported in the Stratix II device. In addition, the LVPECL I/O standard is supported on input and output clock pins on the top and bottom I/O banks.The high-speed differential I/O circuitry supports the following high speed I/O interconnect standards and applications:■SPI-4 Phase 2 (POS-PHY Level 4)■SFI-4■Parallel RapidIO■HyperTransport technologyThere are four dedicated high-speed PLLs in the EP2S15 to EP2S30 devices and eight dedicated high-speed PLLs in the EP2S60 to EP2S180 devices to multiply reference clocks and drive high-speed differential SERDES channels.Tables 2–21 through 2–26 show the number of channels that each fast PLL can clock in each of the Stratix II devices. In Tables 2–21 through 2–26 the first row for each transmitter or receiver provides the number of channels driven directly by the PLL. The second row below it shows the maximum channels a PLL can drive if cross bank channels are used from theadjacent center PLL. For example, in the 484-pin FineLine BGA EP2S15Non-Stratix II VCC = 3.3 Vv (1)v (2)v (3)Level shifter required Level shifter required VCC = 2.5 V v (1), (4)v (2)v (3)Level shifter required Level shifter required VCC = 1.8 V v (1), (4)v (2), (5)v Level shifter requiredLevel shifter requiredVCC = 1.5 Vv (1), (4)v (2), (5)v (6)v vNotes to Table 2–20:(1)The TDO output buffer meets V OH (MIN) = 2.4 V .(2)The TDO output buffer meets V OH (MIN) = 2.0 V .(3)An external 250- pull-up resistor is not required, but recommended if signal levels on the board are not optimal.(4)Input buffer must be 3.3-V tolerant.(5)Input buffer must be 2.5-V tolerant.(6)Input buffer must be 1.8-V tolerant.Table 2–20.Supported TDO/TDI Voltage Combinations (Part 2 of 2)DeviceTDI InputBuffer Power Stratix II TDO V C C I O Voltage Level in I/O Bank 4VC C I O = 3.3 V V C C I O = 2.5 V V C C I O = 1.8 V V C C I O = 1.5 V V C C I O = 1.2 VDocumentRevision HistoryTable2–27 shows the revision history for this chapter.Table2–27.Document Revision History (Part 1 of2)Date andDocumentVersionChanges Made Summary of Changes May 2007, v4.3Updated “Clock Control Block” section.—Updated note in the “Clock Control Block” section.—Deleted Tables 2-11 and 2-12.—Updated notes to:●Figure2–41●Figure2–42●Figure2–43●Figure2–45—Updated notes to Table2–18.—Moved Document Revision History to end of the chapter.—August 2006,v4.2Updated Table2–18 with note.—April 2006, v4.1●Updated T able2–13.●Removed Note 2 from T able2–16.●Updated “On-Chip Termination” section and T able2–19 toinclude parallel termination with calibration information.●Added new “On-Chip Parallel Termination with Calibration”section.●Updated Figure2–44.●Added parallel on-chip terminationdescription andspecification.●Changed RCLKnames to match theQuartus II software inT able2–13.December2005, v4.0Updated “Clock Control Block” section.—July 2005, v3.1●Updated HyperT ransport technology information in Table2–18.●Updated HyperT ransport technology information inFigure2–57.●Added information on the asynchronous clear signal.—May 2005, v3.0●Updated “Functional Description” section.●Updated T able2–3.●Updated “Clock Control Block” section.●Updated T ables2–17 through 2–19.●Updated T ables2–20 through 2–22.●Updated Figure2–57.—March 2005, 2.1●Updated “Functional Description” section.●Updated T able2–3.—。

FPGA可编程逻辑器件芯片EP2S130F780I5N中文规格书

Stratix II GX Architectureload acts as a preset when the asynchronous load data input is tied high.When the asynchronous load/preset signal is used, the labclkena0signal is no longer available.The LAB row clocks [5..0] and LAB local interconnect generate theLAB-wide control signals. The MultiTrack™ interconnects haveinherently low skew. This low skew allows the MultiTrack interconnectsto distribute clock and control signals in addition to data.Figure2–34 shows the LAB control signal generation circuit.Figure2–B-Wide Control SignalsAdaptive Logic ModulesAdaptive Logic Modules The basic building block of logic in the Stratix II GX architecture is the ALM. The ALM provides advanced features with efficient logic utilization. Each ALM contains a variety of look-up table (LUT)-based resources that can be divided between two adaptive LUTs (ALUTs). With up to eight inputs to the two ALUTs, one ALM can implement various combinations of two functions. This adaptability allows the ALM to be completely backward-compatible with four-input LUT architectures. One ALM can also implement any function of up to six inputs and certain seven-input functions.In addition to the adaptive LUT-based resources, each ALM contains two programmable registers, two dedicated full adders, a carry chain, a shared arithmetic chain, and a register chain. Through these dedicated resources, the ALM can efficiently implement various arithmetic functions and shift registers. Each ALM drives all types of interconnects: local, row, column, carry chain, shared arithmetic chain, register chain, and direct link interconnects. Figure2–35 shows a high-level block diagram of the Stratix II GX ALM while Figure2–36 shows a detailed view of all the connections in the ALM.Figure2–35.High-Level Block Diagram of the Stratix II GX ALMTriMatrix MemoryFigure2–51.M4K RAM Block Control SignalsThe R4, C4, and direct link interconnects from adjacent LABs drive theM4K RAM block local interconnect. The M4K RAM blocks cancommunicate with LABs on either the left or right side through these rowresources or with LAB columns on either the right or left with the columnresources. Up to 16 direct link input connections to the M4K RAM blockare possible from the left adjacent LABs and another 16 possible from theright adjacent LAB. M4K RAM block outputs can also connect to left andright LABs through direct link interconnect. Figure2–52 shows the M4KRAM block to logic array interface.。

FPGA可编程逻辑器件芯片EP2AGX260EF29C4N中文规格书

DMC P ROGRAMMING M ODELa)Enter into self-refreshb)Change the clock frequency, as requiredc)Wait for DLL lockd)Exit self refreshe)Write new control register valuesf)Set init bit in DMC_CTL register and poll the MEMINITDONE and DLLCALDONE bits within theDMC_STAT registerg)Write to the DMC_DLLCTL register.Note that for cases where the DDR2 interface has already been initialized (whether it is via an XML file loaded in during a debug session, or through code executed during the booting process), the user needs to perform second-time initialization as described above.Saving Power with the DMCThis section discusses the suggested flow to enter and exit DDR self-refresh before and after the processor enters the HIBERNATE state.For this procedure, the system is in normal operation and the EXT_WAKE signal is high.1.Put the SDRAM in self-refresh mode by setting the DMC_CTL.SRREQ bit.S TEP R ESULT:The DDR goes through the self-refresh entry sequence and enters the Self Refresh state.S TEP R ESULT:The DMC_STAT.SRACK bit is set.S TEP R ESULT:The CKE pin is driven low by the controller when the DDR has entered Self-Refresh.2.Read the DMC_DLLCTL register to get the current DLL tap and calibration settings. This can be used laterto quickly lock and start normal DDR operation. The values read are stored in the DPM registers.3.Initialize the Power-On Reset Delay register to the appropriate values to count off the time requiredfor core V DD to reach a safe value when exiting the Hibernate state.4.Enter the Hibernate state by following the procedure detailed in the DPM chapter. Hibernate is indi-cated by the EXT_WAKE signal going low.5.When EXT_WAKE goes low, the part enters Hibernate state and remains here until brought out by thisstate through SYS_PWRGD pin/counter expiry.6.When a wake-up event occurs, first the EXT_WAKE signal goes high.A DDITIONAL I NFORMATION:When core V DD power reaches a proper value, the Core domain logic is reset.The DDR controller drives the input of the CKE pad low. When this counter reaches 0 a CounterADSP-BF60X DMC R EGISTER D ESCRIPTIONS11:9 (R/W)RDTOWR Read-to-Write Cycle.The DMC_CTL.RDTOWR bits select the number of cycles that the DMCadds when a write operation follows a read operation. Note thatvalues 101 through 111 are reserved.00 Cycles Added1 1 Cycle Added2 2 Cycles Added3 3 Cycles Added4 4 Cycles Added8 (R/W)ADDRMODE Addressing (Page/Bank) Mode.The DMC_CTL.ADDRMODE bit selects whether the DMC uses page orbank interleaving for addressing. When using page interleaving, thebank address bits follow the most significant column address bits.When using bank interleaving, the bank address bits follow the mostsignificant row address bits.0Bank Interleaving1Page Interleaving6 (R/W)PREC Precharge.The DMC_CTL.PREC bit enables pre-charge, which closes DRAM rowsimmediately after access. When disabled, all accesses result in therespective DRAM rows remaining open, until the DMC needs toclose them.0No Effect1Enable Precharge5 (R/W)DPDREQ Deep Power Down Request.The DMC_CTL.DPDREQ bit enables deep powerdown mode if lowpower DMC operation is enabled (DMC_CTL.LPDDR =1}). When theprocessor does not require the data stored in SDRAM (assume resetstate of SDRAM), the DMC may put the SDRAM in deep powerdownmode. When the DMC is in deep powerdown, any data accessescause the DMC to generate a bus error.0Disable Deep Powerdown1Enable Deep PowerdownTable 11-3:DMC_CTL Register Fields (Continued)Bit No.(Access)Bit Name Description/EnumerationD YNAMIC M EMORY C ONTROLLER (DMC)F UNCTIONAL D ESCRIPTION•Sends and receives data to/from the protocol controller.•Creates suitable read/write response and sends read data back to the system crossbar bus.The system crossbar slave interface supports the following:•all burst lengths (1 – 16)•incremental and wrap bursts•data transfer sizes of 8, 16 or 32-bits•arrival of write data before write address•generation of error responses which includes–any access to un-implemented region of the external memory space–any access when the SDRAM is in self-refresh, power-down or deep power down (in case of LPDDR)–any access when the direct command interface is in operationRead/Write Command and Data BuffersThe system crossbar interface comprises of a four deep read command buffer and a four deep writecommand buffer. Up to four write commands and four read commands can be waiting for access to the SDRAM. The system crossbar write buffer is 32 deep. It can support write data interleaving of two. The system crossbar read buffer is 32 deep.Peripheral Bus Slave InterfaceThe peripheral bus slave interface connects the dynamic memory controller to the peripheral bus and provides a host controller with access to the registers. The peripheral bus slave interface supports the following features:•read and write word accesses•32-bit data bus•Ability to extend a transfer using PREADY•Generation of PSLVERR when unimplemented registers are accessed or when read-only registers are written.Architectural ConceptsThe following sections provide information on the architecture of the interface.。

FPGA可编程逻辑器件芯片EP3C40F780I7N中文规格书

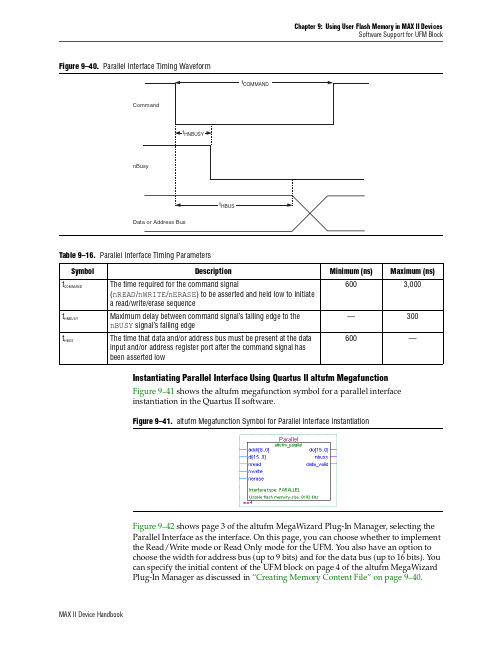

Chapter 9:Using User Flash Memory in MAX II DevicesSoftware Support for UFM Block Figure9–40.Parallel Interface Timing WaveformTable9–16.Parallel Interface Timing ParametersInstantiating Parallel Interface Using Quartus II altufm MegafunctionFigure9–41 shows the altufm megafunction symbol for a parallel interfaceinstantiation in the Quartus II software.Figure9–41.altufm Megafunction Symbol for Parallel Interface InstantiationFigure9–42 shows page 3 of the altufm MegaWizard Plug-In Manager, selecting theParallel Interface as the interface. On this page, you can choose whether to implementthe Read/Write mode or Read Only mode for the UFM. You also have an option tochoose the width for address bus (up to 9 bits) and for the data bus (up to 16 bits). Youcan specify the initial content of the UFM block on page 4 of the altufm MegaWizardPlug-In Manager as discussed in “Creating Memory Content File” on page9–40.10.Replacing Serial EEPROMs with MAXII User Flash MemoryIntroductionEach MAX® II device has a user flash memory (UFM) block to store up to 8 Kbits ofuser data. You can use the UFM block to replace on-board flash and EEPROMmemory devices which are used to store ASSP or processor configuration bits, orelectronic ID information for a board during manufacturing. MAX II device logiccapacity allows integration of system power-on reset (POR), interface bridging, andI/O expansion designs in addition to these serial flash capabilities.This chapter provides a comprehensive listing of 2-Kbit, 4-Kbit, and 8-Kbit, non-volatile memory devices that could be potentially replaced by MAX II UFM devices.Table10–1 shows the capacity for the UFM block for all MAX II devices.Table10–1.MAX II UFM Array SizeThis chapter contains the following sections:■“Design Considerations” on page10–1■“List of Vendors and Devices” on page10–2Design ConsiderationsThe MAX II UFM can be programmed, erased, and verified through the Joint TestAction Group (JTAG) port or through connections to/from the logic array inaccordance with IEEE Std. 1532-2002. There are 13 interface signals to and from theUFM block and logic array which allow the logic array to read or write to the UFMduring device user mode. A reference design or user logic can be used to interface theUFM to many standard interface protocols such as Serial Communication Interface(SCI), Serial Peripheral Interface (SPI), Inter-Integrated Circuit (I2C), Microwire, orother proprietary protocols. Altera's Quartus® II altufm megafunction providesinterface logic for a subset of these interfaces (parallel and SPI). Any interfaces notprovided by the megafunction or design examples, require you to create user logic tobridge the UFM block to your desired interface protocol.f For more information about programming and erasing the UFM block and/or thealtufm megafunction, refer to the Using User Flash Memory in MAX II Devices chapterin the MAX II Device Handbook.Section IV.In-System ProgrammabilitySection IV: In-System ProgrammabilityRevision History12.Real-Time ISP and ISP Clamp for MAXII DevicesIntroductionDuring in-system programming, most CPLDs automatically tri-state theirinput/output (I/O) pins to prevent contention issues on a board. After successfulprogramming, the device enters user mode and the new design begins to function.Apart from this normal programming mode, MAX® II devices also support real-timein-system programmability (ISP) and ISP Clamp programming modes, which allowcontrol of I/O and device behavior during ISP. This chapter describes the followingtwo features and how to use them in the Quartus® II software, as well as the Jam™Standard Test and Programming Language (STAPL) and Jam STAPL Byte-CodePlayers:■“Real-Time ISP” on page12–1■“ISP Clamp” on page12–4Real-Time ISPReal-time ISP allows you to program a MAX II device while the device is still inoperation. The new design only replaces the existing design when there is a powercycle to the device (i.e., powering down and powering up again). This feature enablesyou to perform in-field updates to the MAX II device at any time without affecting theoperation of the whole system.How Real-Time ISP WorksFor normal ISP operation, downloading the new design data from the configurationflash memory (CFM) to the SRAM begins after the completion of CFM programming.During the process of CFM programming and subsequent downloading of CFM datato SRAM, I/O pins will remain tri-stated. After the CFM download to the SRAM, thedevice resets and enters user mode operation. Figure12–1 shows the flow of normalprogramming.Figure12–1.MAX II Device with Normal ISP Operation11ProgrammingData2。

FPGA可编程逻辑器件芯片EP2SGX60CF780I4N中文规格书

Chapter 1:Stratix III Device Data Sheet: DC and Switching Characteristics Electrical CharacteristicsStratix III Device Handbook, Volume 2Table 1–9 lists OCT variation with temperature and voltage after power-upcalibration. Use Table 1–9 and Equation 1–1 to determine OCT variation without re-calibration.Table 1–8.Stratix III On-Chip Termination Resistance Tolerance SpecificationSymbol Description Conditions Resistance Tolerance UnitC2C3, I3C4, I4R OCT_UNCALInternal series termination without calibration—25-Ω R S 3.3/3.0/2.5Internal series termination without calibration (25-Ω setting)V CCIO = 3.3/3.0/2.5 V ±30±40±40%25-Ω R S 1.8/1.5Internal series termination without calibration (25-Ω setting)V CCIO = 1.8/1.5 V ±30±50±50%25-Ω R S 1.2Internal series termination without calibration (25-Ω setting)V CCIO = 1.2 V ±35±60±60%50-Ω R S 3.3/3.0/2.5Internal series termination without calibration (50-Ω setting)V CCIO = 3.3/3.0/2.5 V ±30±40±40%50-Ω R S 1.8/1.5Internal series termination without calibration (50-Ω setting)V CCIO = 1.8/1.5 V ±30±50±50%50-Ω R S 1.2Internal series termination without calibration (50-Ω setting)V CCIO = 1.2 V±35±60±60%Equation 1–1.OCT Variation Without Re-Calibration (Note 1)Notes to Equation 1–1:(1)R OCT value calculated from Equation 1–1 shows the range of OCT resistance with the variation of temperature andV CCIO .(2)R SCAL is the OCT resistance value at power-up.(3)∆T is the variation of temperature with respect to the temperature at power-up.(4)∆V is the variation of voltage with respect to the V CCIO at power-up.(5)dR/dT is the percentage change of R SCAL with temperature.(6)dR/dV is the percentage change of R SCAL with voltage.R OCT R SCAL 1dR dT ------∆T ⨯〈〉dR dV ------∆V ⨯〈〉±+⎝⎭⎛⎫=Table 1–9.On-Chip Termination Variation after Power-up Calibration (Part 1 of 2) (Note 1)SymbolDescriptionV CCIO (V)Commercial Typical Unit dR/dVOCT variation with voltage without re-calibration30.029%/mV 2.50.036%/mV 1.80.065%/mV 1.50.104%/mV 1.20.177%/mVChapter 1:Stratix III Device Data Sheet: DC and Switching CharacteristicsElectrical CharacteristicsStratix III Device Handbook, Volume 2Pin CapacitanceTable 1–10 shows the Stratix III device family pin capacitance. Hot-SocketingTable 1–11 lists the hot-socketing specifications for Stratix III devices.Internal Weak Pull-Up ResistorTable 1–12 lists the weak pull-up resistor values for Stratix III devices.dR/dTOCT variation with temperature without re-calibration30.294%/°C2.50.301%/°C 1.80.355%/°C 1.50.344%/°C 1.20.348%/°C Note to Table 1–9:(1)Valid for V CCIO range of ±5% and temperature range of 0° to 85° C.Table 1–9.On-Chip Termination Variation after Power-up Calibration (Part 2 of 2) (Note 1)SymbolDescriptionV CCIO (V)Commercial Typical UnitTable 1–10.Stratix III Device CapacitanceSymbol ParameterTypical Unit C IOTB Input capacitance on top/bottom I/O pins 4pF C IOLR Input capacitance on left/right I/O pins 4pF C CLKTB Input capacitance on top/bottom non-dedicated clock input pins4pF C CLKLR Input capacitance on left/right non-dedicatedclock input pins4pF C OUTFBInput capacitance on dual-purpose clock output/feedback pins5pF C CLK1, C CLK3, C CLK8, and C CLK10Input capacitance for dedicated clock inputpins2pFTable 1–11.Stratix III Hot-Socketing SpecificationsSymbol Parameter Maximum I IOPIN (DC)DC current per I/O pin 300 μA I IOPIN (AC)AC current per I/O pin8 mA for ≤ 10 nsChapter 1:Stratix III Device Data Sheet: DC and Switching CharacteristicsI/O TimingStratix III Device Handbook, Volume 2Chapter 1:Stratix III Device Data Sheet: DC and Switching CharacteristicsI/O TimingStratix III Device Handbook, Volume 2。

FPGA可编程逻辑器件芯片EP2SGX60DF780C4N中文规格书

Power ConsumptionPower Consumption Altera® offers two ways to calculate power for a design: the Excel-based PowerPlay Early Power Estimator power calculator and the Quartus®II PowerPlay Power Analyzer feature.The interactive Excel-based PowerPlay Early Power Estimator is typically used prior to designing the FPGA in order to get an estimate of device power. The Quartus II PowerPlay Power Analyzer provides better quality estimates based on the specifics of the design after place-and-route is complete. The Power Analyzer can apply a combination of user-entered, simulation-derived and estimated signal activities which, combined with detailed circuit models, can yield very accurate power estimates.In both cases, these calculations should only be used as an estimation of power, not as a specification.f For more information about PowerPlay tools, refer to the PowerPlay EarlyPower Estimator User Guide and the PowerPlay Early Power Estimator andPowerPlay Power Analyzer chapters in volume 3 of the Quartus IIHandbook.The PowerPlay Early Power Estimator is available on the Altera web siteat . See Table5–4 on page5–3 for typical I CC standbyspecifications.Timing Model The DirectDrive TM technology and MultiTrack TM interconnect ensurepredictable performance, accurate simulation, and accurate timinganalysis across all Stratix II device densities and speed grades. Thissection describes and specifies the performance, internal timing, externaltiming, and PLL, high-speed I/O, external memory interface, and JTAGtiming specifications.All specifications are representative of worst-case supply voltage andjunction temperature conditions.1The timing numbers listed in the tables of this section areextracted from the Quartus II software version 5.0 SP1.Preliminary & Final TimingTiming models can have either preliminary or final status. The Quartus IIsoftware issues an informational message during the design compilationif the timing models are preliminary. Table5–33 shows the status of theStratix II device timing models.Timing ModelFigure5–6.Measurement Setup for t zxTable5–35 specifies the input timing measurement setup.Table5–35.Timing Measurement Methodology for Input Pins(Part 1 of2)Notes(1)–(4)I/O StandardMeasurement Conditions Measurement Point V CCIO (V)V REF (V)Edge Rate (ns)V M E A S (V)LVTTL (5) 3.135 3.135 1.5675 LVCMOS (5) 3.135 3.135 1.5675 2.5 V (5) 2.375 2.375 1.1875 1.8 V (5) 1.710 1.7100.855 1.5 V (5) 1.425 1.4250.7125 PCI (6) 2.970 2.970 1.485 PCI-X (6) 2.970 2.970 1.485 SSTL-2 Class I 2.325 1.163 2.325 1.1625 SSTL-2 Class II 2.325 1.163 2.325 1.1625 SSTL-18 Class I 1.6600.830 1.6600.83 SSTL-18 Class II 1.6600.830 1.6600.83 1.8-V HSTL Class I 1.6600.830 1.6600.83DC & Switching CharacteristicsPerformanceTable 5–36 shows Stratix II performance for some common designs. All performance values were obtained with the Quartus II softwarecompilation of library of parameterized modules (LPM), or MegaCore ® functions for the finite impulse response (FIR) and fast Fourier transform (FFT) designs.1.8-V HSTL Class II 1.6600.830 1.6600.831.5-V HSTL Class I 1.3750.688 1.3750.68751.5-V HSTL Class II 1.3750.688 1.3750.68751.2-V HSTL with OCT 1.1400.570 1.1400.570Differential SSTL-2 Class I2.325 1.163 2.325 1.1625Differential SSTL-2 Class II 2.325 1.163 2.325 1.1625Differential SSTL-18 Class I 1.6600.830 1.6600.83Differential SSTL-18 Class II 1.6600.830 1.6600.831.5-V Differential HSTL Class I 1.3750.688 1.3750.68751.5-V Differential HSTL Class II 1.3750.688 1.3750.68751.8-V Differential HSTL Class I 1.6600.830 1.6600.831.8-V Differential HSTL Class II 1.6600.8301.6600.83LVDS2.3250.100 1.1625HyperTransport 2.3250.400 1.1625LVPECL3.1350.1001.5675Notes to Table 5–35:(1)Input buffer sees no load at buffer input.(2)Input measuring point at buffer input is 0.5 × V CCIO .(3)Output measuring point is 0.5 × V CC at internal node.(4)Input edge rate is 1 V/ns.(5)Less than 50-mV ripple on V CCIO and V CCPD , V CCINT = 1.15 V with less than 30-mV ripple (6)V CCPD = 2.97 V , less than 50-mV ripple on V CCIO and V CCPD , V CCINT = 1.15 VTable 5–35.Timing Measurement Methodology for Input Pins (Part 2 of 2)Notes (1)–(4)I/O StandardMeasurement Conditions Measurement PointV CCIO (V)V REF (V)Edge Rate (ns)V M E A S (V)。

FPGA可编程逻辑器件芯片EP2SGX30DF780I4中文规格书

Logic Array BlocksApplications and Protocols Supported with Stratix II GX DevicesEach Stratix II GX transceiver block is designed to operate at any serial bitrate from 600 Mbps to 6.375 Gbps per channel. The wide data rate rangeallows Stratix II GX transceivers to support a wide variety of standardsand protocols, such as PCI Express, GIGE, SONET/SDH, SDI, OIF-CEI,and XAUI. Stratix II GX devices are ideal for many high-speedcommunication applications, such as high-speed backplanes,chip-to-chip bridges, and high-speed serial communications links.Example Applications Support for Stratix II GXStratix II GX devices can be used for many applications, including:■Traffic management with various levels of quality of service (QoS)and integrated serial backplane interconnect■Multi-port single-protocol switching (for example, PCI Express,GIGE, XAUI switch, or SONET/SDH)Logic Array Blocks Each logic array block (LAB) consists of eight adaptive logic modules (ALMs), carry chains, shared arithmetic chains, LAB control signals, local interconnects, and register chain connection lines. The local interconnect transfers signals between ALMs in the same LAB. Register chain connections transfer the output of an ALM register to the adjacent ALM register in a LAB. The Quartus II Compiler places associated logic in a LAB or adjacent LABs, allowing the use of local, shared arithmetic chain, and register chain connections for performance and area efficiency. Table2–17 shows Stratix II GX device resources. Figure2–32 shows the Stratix II GX LAB structure.Table2–17.Stratix II GX Device ResourcesDeviceM512 RAMColumns/BlocksM4K RAMColumns/BlocksM-RAMBlocksDSP BlockColumns/BlocksLABColumnsLAB RowsEP2SGX306/2024/14412/164936 EP2SGX607/3295/25523/366251 EP2SGX908/4886/40843/487168 EP2SGX1309/6997/60963/638187Adaptive Logic ModulesFigure2–41.ALM in Arithmetic ModeWhile operating in arithmetic mode, the ALM can support simultaneoususe of the adder’s carry output along with combinational logic outputs.In this operation, the adder output is ignored. This usage of the adderwith the combinational logic output provides resource savings of up to50% for functions that can use this ability. An example of suchfunctionality is a conditional operation, such as the one shown inFigure2–42. The equation for this example is:R = (X < Y) ? Y : XTo implement this function, the adder is used to subtract ‘Y’ from ‘X’. If‘X’ is less than ‘Y’, the carry_out signal will be ‘1’. The carry_outsignal is fed to an adder where it drives out to the LAB local interconnect.It then feeds to the LAB-wide syncload signal. When asserted,syncload selects the syncdata input. In this case, the data ‘Y’ drivesthe syncdata inputs to the registers. If ‘X’ is greater than or equal to ‘Y’,the syncload signal is de-asserted and ‘X’ drives the data port of theregisters.Figure2–42.Conditional Operation ExampleThe arithmetic mode also offers clock enable, counter enable, synchronous up and down control, add and subtract control, synchronous clear, synchronous load. The LAB local interconnect data inputs generate the clock enable, counter enable, synchronous up and down and add and subtract control signals. These control signals may be used for the inputs that are shared between the four LUTs in the ALM. The synchronous clear and synchronous load options are LAB-wide signals that affect all registers in the LAB. The Quartus II software automatically places any registers that are not used by the counter into other LABs.。

FPGA可编程逻辑器件芯片EP2SGX30DF780C4中文规格书

SignalTap II Embedded Logic Analyzerf For more information on JTAG, see the following documents:■The IEEE Std. 1149.1 (JTAG) Boundary-Scan Testing for Stratix II &Stratix II GX Devices chapter of the Stratix II Device Handbook,Volume2 or the Stratix II GX Device Handbook, Volume 2■Jam Programming & Test Language SpecificationSignalTap II Embedded Logic Analyzer Stratix II devices feature the SignalTap II embedded logic analyzer, which monitors design operation over a period of time through the IEEE Std.1149.1 (JTAG) circuitry. You can analyze internal logic at speed without bringing internal signals to the I/O pins. This feature is particularly important for advanced packages, such as FineLine BGA®packages, because it can be difficult to add a connection to a pin during the debugging process after a board is designed and manufactured.Configuration The logic, circuitry, and interconnects in the Stratix II architecture areconfigured with CMOS SRAM elements. Altera® FPGA devices arereconfigurable and every device is tested with a high coverageproduction test program so you do not have to perform fault testing andcan instead focus on simulation and design verification.Stratix II devices are configured at system power-up with data stored inan Altera configuration device or provided by an external controller (e.g.,a MAX®II device or microprocessor). Stratix II devices can be configuredusing the fast passive parallel (FPP), active serial (AS), passive serial (PS),passive parallel asynchronous (PPA), and JTAG configuration schemes.The Stratix II device’s optimized interface allows microprocessors toconfigure it serially or in parallel, and synchronously or asynchronously.The interface also enables microprocessors to treat Stratix II devices asmemory and configure them by writing to a virtual memory location,making reconfiguration easy.In addition to the number of configuration methods supported, Stratix IIdevices also offer the design security, decompression, and remote systemupgrade features. The design security feature, using configurationbitstream encryption and AES technology, provides a mechanism toprotect your designs. The decompression feature allows Stratix II FPGAsto receive a compressed configuration bitstream and decompress thisdata in real-time, reducing storage requirements and configuration time.The remote system upgrade feature allows real-time system upgradesfrom remote locations of your Stratix II designs. For more information,see “Configuration Schemes” on page3–7.Configuration & TestingOperating ModesThe Stratix II architecture uses SRAM configuration elements that require configuration data to be loaded each time the circuit powers up. The process of physically loading the SRAM data into the device is called configuration. During initialization, which occurs immediately after configuration, the device resets registers, enables I/O pins, and begins to operate as a logic device. The I/O pins are tri-stated during power-up, and before and during configuration. Together, the configuration and initialization processes are called command mode. Normal device operation is called user mode.SRAM configuration elements allow Stratix II devices to be reconfigured in-circuit by loading new configuration data into the device. With real-time reconfiguration, the device is forced into command mode with a device pin. The configuration process loads different configuration data, reinitializes the device, and resumes user-mode operation. You can perform in-field upgrades by distributing new configuration files either within the system or remotely.PORSEL is a dedicated input pin used to select POR delay times of 12 ms or 100 ms during power-up. When the PORSEL pin is connected to ground, the POR time is 100 ms; when the PORSEL pin is connected to V CC, the POR time is 12 ms.The nIO PULLUP pin is a dedicated input that chooses whether the internal pull-ups on the user I/O pins and dual-purpose configuration I/O pins (nCSO, ASDO, DATA[7..0], nWS, nRS, RDYnBSY, nCS, CS, RUnLU, PGM[2..0], CLKUSR, INIT_DONE, DEV_OE, DEV_CLR) are on or off before and during configuration. A logic high (1.5, 1.8, 2.5, 3.3 V) turns off the weak internal pull-ups, while a logic low turns them on.Stratix II devices also offer a new power supply, V CCPD, which must be connected to 3.3 V in order to power the 3.3-V/2.5-V buffer available on the configuration input pins and JTAG pins. V CCPD applies to all the JTAG input pins (TCK, TMS, TDI, and TRST) and the configuration input pins when VCCSEL is connected to ground. See Table3–4 for more information on the pins affected by VCCSEL.The VCCSEL pin allows the V CCIO setting (of the banks where the configuration inputs reside) to be independent of the voltage required by the configuration inputs. Therefore, when selecting the V CCIO, the V IL and V IH levels driven to the configuration inputs do not have to be a concern.Document Revision HistoryTable5–12.LVPECL SpecificationsSymbol Parameter Conditions Minimum Typical Maximum Unit V CCIO (1)I/O supply voltage 3.135 3.300 3.465V V ID Input differential voltage3006001,000mV swing (single-ended)V ICM Input common mode voltage 1.0 2.5V V OD Output differential voltageR L = 100 Ω525970mV (single-ended)R L = 100 Ω1,6502,250mV V OCM Output common modevoltage90100110ΩR L Receiver differential inputresistorNote to Table5–12:(1)The top and bottom clock input differential buffers in I/O banks 3, 4, 7, and 8 are powered by V CCINT, not V CCIO.The PLL clock output/feedback differential buffers are powered by VCC_PLL_OUT. For differential clockoutput/feedback operation, VCC_PLL_OUT should be connected to 3.3 V.Table5–13.HyperTransport Technology SpecificationsSymbol Parameter Conditions Minimum Typical Maximum Unit2.375 2.500 2.625V V CCIO I/O supply voltage for left andright I/O banks (1, 2, 5, and 6)R L = 100 Ω300600900mV V ID Input differential voltage swing(single-ended)V ICM Input common mode voltage R L = 100 Ω385600845mV V OD Output differential voltageR L = 100 Ω400600820mV (single-ended)ΔV OD Change in V OD between highR L = 100 Ω75mV and lowV OCM Output common mode voltage R L = 100 Ω440600780mV ΔV OCM Change in V OCM between highR L = 100 Ω50mV and lowR L Receiver differential input90100110ΩresistorTable5–14.3.3-V PCI Specifications(Part 1 of2)Symbol Parameter Conditions Minimum Typical Maximum Unit V CCIO Output supply voltage 3.0 3.3 3.6V V IH High-level input voltage0.5 × V CCIO V CCIO + 0.5V。

FPGA可编程逻辑器件芯片EP2SGX90EF1152C4N中文规格书

Carry ChainThe carry chain provides a fast carry function between the dedicated adders in arithmetic or shared arithmetic mode. Carry chains can begin in either the first ALM or the fifth ALM in a LAB. The final carry-out signal is routed to an ALM, where it is fed to local, row, or column interconnects. The Quartus II Compiler automatically creates carry chain logic during compilation, or you can create it manually during design entry. Parameterized functions, such as LPM functions, automatically take advantage of carry chains for the appropriate functions. The Quartus II Compiler creates carry chains longer than 16 (8 ALMs in arithmetic or shared arithmetic mode) by linking LABs together automatically. For enhanced fitting, a long carry chain runs vertically, allowing fast horizontal connections to TriMatrix memory and DSP blocks. A carry chain can continue as far as a full column. To avoid routing congestion in one small area of the device when a high fan-in arithmetic function is implemented, the LAB can support carry chains that only utilize either the top half or the bottom half of the LAB before connecting to the next LAB. The other half of the ALMs in the LAB is available for implementing narrower fan-in functions in normal mode. Carry chains that use the top four ALMs in the first LAB will carry into the top half of the ALMs in the next LAB within the column. Carry chains that use the bottom four ALMs in the first LAB will carry into the bottom half of the ALMs in the next LAB within the column. Every other column of the LABs are top-half bypassable, while the other LAB columns are bottom-half bypassable. Refer to “MultiTrack Interconnect” on page2–63 for more information on carry chain interconnect.Shared Arithmetic ModeIn shared arithmetic mode, the ALM can implement a three-input add. In this mode, the ALM is configured with four 4-input LUTs. Each LUT either computes the sum of three inputs or the carry of three inputs. The output of the carry computation is fed to the next adder (either to adder1 in the same ALM or to adder0 of the next ALM in the LAB) using a dedicated connection called the shared arithmetic chain. This shared arithmetic chain can significantly improve the performance of an adder tree by reducing the number of summation stages required to implement an adder tree. Figure2–43 shows the ALM in shared arithmetic mode.Stratix II GX ArchitectureAdaptive Logic ModulesFigure2–44.Example of a 3-Bit Add Utilizing Shared Arithmetic ModeShared Arithmetic ChainIn addition to the dedicated carry chain routing, the shared arithmeticchain available in shared arithmetic mode allows the ALM to implementa three-input add, which significantly reduces the resources necessary toimplement large adder trees or correlator functions. The sharedarithmetic chains can begin in either the first or fifth ALM in a LAB. TheQuartus II Compiler automatically links LABs to create shared arithmeticchains longer than 16 (8ALMs in arithmetic or shared arithmetic mode).For enhanced fitting, a long shared arithmetic chain runs verticallyStratix II GX ArchitectureAdaptive Logic ModulesFigure2–45.Register Chain within a LAB Note(1)Note to Figure2–45:(1)The combinational or adder logic can be utilized to implement an unrelated, un-registered function.。

FPGA可编程逻辑器件芯片EP1S20F780I7N中文规格书

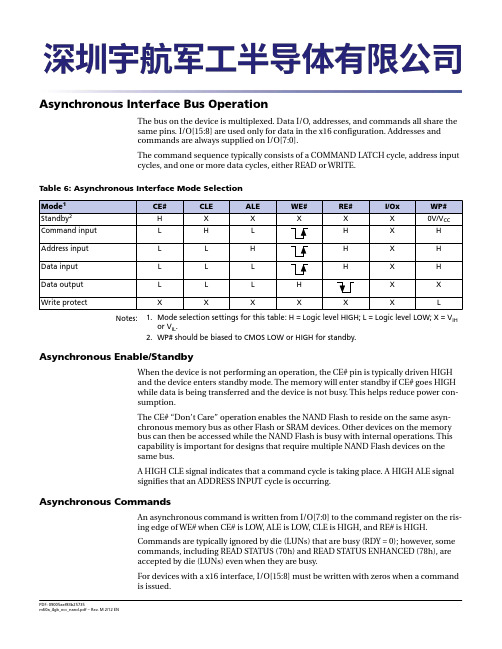

Asynchronous Interface Bus OperationThe bus on the device is multiplexed. Data I/O, addresses, and commands all share thesame pins. I/O[15:8] are used only for data in the x16 configuration. Addresses andcommands are always supplied on I/O[7:0].The command sequence typically consists of a COMMAND LATCH cycle, address inputcycles, and one or more data cycles, either READ or WRITE.Table 6: Asynchronous Interface Mode SelectionNotes: 1.Mode selection settings for this table: H = Logic level HIGH; L = Logic level LOW; X = V IHor V IL.2.WP# should be biased to CMOS LOW or HIGH for standby.Asynchronous Enable/StandbyWhen the device is not performing an operation, the CE# pin is typically driven HIGHand the device enters standby mode. The memory will enter standby if CE# goes HIGHwhile data is being transferred and the device is not busy. This helps reduce power con-sumption.The CE# “Don’t Care” operation enables the NAND Flash to reside on the same asyn-chronous memory bus as other Flash or SRAM devices. Other devices on the memorybus can then be accessed while the NAND Flash is busy with internal operations. Thiscapability is important for designs that require multiple NAND Flash devices on thesame bus.A HIGH CLE signal indicates that a command cycle is taking place. A HIGH ALE signalsignifies that an ADDRESS INPUT cycle is occurring.Asynchronous CommandsAn asynchronous command is written from I/O[7:0] to the command register on the ris-ing edge of WE# when CE# is LOW, ALE is LOW, CLE is HIGH, and RE# is HIGH.Commands are typically ignored by die (LUNs) that are busy (RDY = 0); however, somecommands, including READ STATUS (70h) and READ STATUS ENHANCED (78h), areaccepted by die (LUNs) even when they are busy.For devices with a x16 interface, I/O[15:8] must be written with zeros when a commandis issued.Table 7: Command Set (Continued)Notes:1.Busy means RDY = 0.2.These commands can be used for interleaved die (multi-LUN) operations (see InterleavedDie (Multi-LUN) Operations (page 106)).3.Do not cross plane address boundaries when using READ for INTERNAL DATA MOVE andPROGRAM for INTERNAL DATA MOVE.4.These commands supported only with ECC disabled.5.Issuing a READ PAGE CACHE series (31h, 00h-31h, 3Fh) command when the array is busy(RDY = 1, ARDY = 0) is supported if the previous command was a READ PAGE (00h-30h)or READ PAGE CACHE series command; otherwise, it is prohibited.6.Issuing a PROGRAM PAGE CACHE (80h-15h) command when the array is busy (RDY = 1,ARDY = 0) is supported if the previous command was a PROGRAM PAGE CACHE (80h-15h) command; otherwise, it is prohibited.7.OTP commands can be entered only after issuing the SET FEATURES command with thefeature address.4Gb, 8Gb, 16Gb: x8, x16 NAND Flash MemoryCommand DefinitionsTable 9: READ ID Parameters for Address 00h (Continued)Table 11: Parameter Page Data Structure (Continued)。

FPGA可编程逻辑器件芯片EP2SGX60CF780C4N中文规格书

Chapter 4:TriMatrix Embedded Memory Blocks in Stratix III DevicesClocking ModesClocking ModesStratix III TriMatrix memory blocks support the following clocking modes:■Independent■Input/output■Read/write■Single clock1Violating the setup or hold time on the memory block address registers could corrupt the memory contents. This applies to both read and write operations.1Altera recommends using a memory block clock that comes through global clock routing from an on-chip PLL set to 50% output duty cycle to achieve the maximummemory block performance. Use Quartus II to report timing for this and othermemory block clocking schemes.f For more information refer to the Stratix III Device Family Errata Sheet.Table4–9 shows the clocking mode versus memory mode support matrix.Table4–9.Stratix III TriMatrix Memory Clock ModesIndependent Clock ModeStratix III TriMatrix memory blocks can implement independent clock mode for truedual-port memories. In this mode, a separate clock is available for each port (A andB). Clock A controls all registers on the port A side, while clock B controls all registerson the port B side. Each port also supports independent clock enables for port A andport B registers. Asynchronous clears are supported only for output latches andoutput registers on both ports.Input/Output Clock ModeStratix III TriMatrix memory blocks can implement input/output clock mode for trueand simple dual-port memories. In this mode, an input clock controls all registersrelated to the data input to the memory block, including data, address, byte-enables,read enables, and write enables. An output clock controls the data output registers.Asynchronous clears are available on output latches and output registers only.Chapter 4:TriMatrix Embedded Memory Blocks in Stratix III DevicesDesign ConsiderationsRead/Write Clock ModeStratix III TriMatrix memory blocks can implement read/write clock mode for simpledual-port memories. In this mode, a write clock controls the data-input,write-address, and write-enable registers. Similarly, a read clock control thedata-output, read-address, and read-enable registers. The memory blocks supportindependent clock enables for both the read and write clocks. Asynchronous clearsare available on data output latches and registers only.When using read/write mode, if you perform a simultaneous read/write to the sameaddress location, the output read data will be unknown. If you require the output datato be a known value in this case, use either single-clock mode or input/output clockmode and choose the appropriate read-during-write behavior in the Megawizard.Single Clock ModeStratix III TriMatrix memory blocks can implement single-clock mode for truedual-port, simple dual-port, and single-port memories. In this mode, a single clock,together with a clock enable, is used to control all registers of the memory block.Asynchronous clears are available on output latches and output registers only.Design ConsiderationsThis section describes guidelines for designing with TriMatrix memory blocks.Selecting TriMatrix Memory BlocksThe Quartus II software automatically partitions user-defined memory intoembedded memory blocks by taking into account both speed and size constraintsplaced on your design. For example, the Quartus II software may spread out amemory across multiple memory blocks when resources are available to increase theperformance of the design. You can manually assign the memory to a specific blocksize via the RAM MegaWizard Plug-In Manager.MLABs can implement single-port SRAM through emulation via the Quartus IIsoftware. Emulation results in minimal additional logic resources being used. Becauseof the dual-purpose architecture of the MLAB, it only has data input registers andoutput registers in the block. MLABs gain input address registers and additionaloptional data output registers from adjacent ALMs by using register packing.f For more information about register packing, refer to the Logic Array Blocks andAdaptive Logic Modules in Stratix III Devices chapter in volume 1 of the Stratix III DeviceHandbook.Conflict ResolutionWhen using the memory blocks in true dual-port mode, it is possible to attempt twowrite operations to the same memory location (address). Since no conflict resolutioncircuitry is built into the memory blocks, this results in unknown data being written tothat location. Therefore, you must implement conflict resolution logic external to thememory block to avoid address conflicts.xxiv List of TablesSection I: Device CoreRevision HistoryChapter 5:DSP Blocks in Stratix III DevicesOperational Mode DescriptionsThe second-stage and output registers are triggered by the positive edge of the clocksignal and are cleared on power up. The following DSP block signals control theoutput registers within the DSP block:■clock[3..0]■ena[3..0]■aclr[3..0]Operational Mode DescriptionsThe various modes of operation are discussed below.Independent Multiplier ModesIn independent input and output multiplier mode, the DSP block performs individualmultiplication operations for general-purpose multipliers.9-, 12-, and 18-Bit MultiplierYou can configure each DSP block multiplier for 9-, 12-, or 18-bit multiplication. Asingle DSP block can support up to eight individual 9×9 multipliers, six 12×12multipliers, or up to four individual 18×18 multipliers. For operand widths up to9bits, a 9×9 multiplier is implemented. For operand widths from 10 to 12 bits, a12×12 multiplier is implemented, and for operand widths from 13 to 18 bits, an18×18 multiplier is implemented. This is done by the Quartus II software byzero-padding the LSBs. Figure5–8, Figure5–9, and Figure5–10 show the DSP block inthe independent multiplier operation mode.Figure5–8.18-Bit Independent Multiplier Mode for Half-DSP Blockwresult_0[ ]data bdata b。

FPGA可编程逻辑器件芯片EP2S90F780C5中文规格书

TransceiversThe rx_syncstatus signal is not available in bit-slipping mode.Channel AlignerThe channel aligner is available only in XAUI mode and aligns the signalsof all four channels within a transceiver. The channel aligner follows theIEEE802.3ae, clause 48 specification for channel bonding.The channel aligner is a 16-word FIFO buffer with a state machinecontrolling the channel bonding process. The state machine looks for an/A/ (/K28.3/) in each channel, and aligns all the /A/ code groups in thetransceiver. When four columns of /A/ (denoted by //A//) aredetected, the rx_channelaligned signal goes high, signifying that allthe channels in the transceiver have been aligned. The reception of fourconsecutive misaligned /A/ code groups restarts the channel alignmentsequence and sends the rx_channelaligned signal low.Figure2–19 shows misaligned channels before the channel aligner andthe aligned channels after the channel aligner.Figure2–19.Before and After the Channel AlignerStratix II GX ArchitectureRate MatcherRate matcher is available in Basic, PCI Express, XAUI, and GIGE modes and consists of a 20-word deep FIFO buffer and a FIFO controller. Figure2–20 shows the implementation of the rate matcher in the Stratix II GX device.Figure2–20.Rate MatcherIn a multi-crystal environment, the rate matcher compensates for up to a ±300-PPM difference between the source and receiver clocks. Table2–8 shows the standards supported and the PPM for the rate matcher tolerance.Table2–8.Rate Matcher PPM Support Note(1)Standard PPMXAUI±100PCI Express (PIPE)±300GIGE±100Basic Double-Width±300Note to Table2–8:(1)Refer to the Stratix II GX Transceiver User Guide for the Altera®-defined scheme. Basic ModeIn Basic mode, you can program the skip and control pattern for rate matching. In single-width Basic mode, there is no restriction on the deletion of a skip character in a cluster. The rate matcher deletes the skip characters as long as they are available. For insertion, the rate matcher inserts skip characters such that the number of skip characters at the output of rate matcher does not exceed five. In double-width mode, the rate matcher deletes skip character when they appear as pairs in the upper and lower bytes. There are no restrictions on the number of skip characters that are deleted. The rate matcher inserts skip characters as pairs.TransceiversGIGE ModeIn GIGE mode, the rate matcher adheres to the specifications in clause36of the IEEE 802.3 documentation for idle additions or removals. The ratematcher performs clock compensation only on /I2/ ordered sets,composed of a /K28.5/+ followed by a /D16.2/-. The rate matcher doesnot perform clock compensation on any other ordered set combinations.An /I2/ is added or deleted automatically based on the number of wordsin the FIFO buffer. A K28.4 is given at the control and data ports when theFIFO buffer is in an overflow or underflow condition.XAUI ModeIn XAUI mode, the rate matcher adheres to clause 48 of the IEEE 802.3aespecification for clock rate compensation. The rate matcher performsclock compensation on columns of /R/ (/K28.0/), denoted by //R//.An //R// is added or deleted automatically based on the number ofwords in the FIFO buffer.PCI Express ModePCI Express mode operates at a data rate of 2.5 Gbps, and supports lanewidths of ×1, ×2, ×4, and ×8. The rate matcher can support up to±300-PPM differences between the upstream transmitter and thereceiver. The rate matcher looks for the skip ordered sets (SOS), whichusually consist of a /K28.5/ comma followed by three /K28.0/ skipcharacters. The rate matcher deletes or inserts skip characters whennecessary to prevent the rate matching FIFO buffer from overflowing orunderflowing.The Stratix II GX rate matcher in PCI Express mode has FIFO overflowand underflow protection. In the event of a FIFO overflow, the ratematcher deletes any data after the overflow condition to prevent FIFOpointer corruption until the rate matcher is not full. In an underflowcondition, the rate matcher inserts 9'h1FE (/K30.7/) until the FIFO is notempty. These measures ensure that the FIFO can gracefully exit theoverflow and underflow condition without requiring a FIFO reset.8B/10B DecoderThe 8B/10B decoder (Figure2–21) is part of the Stratix II GX transceiverdigital blocks (PCS) and lies in the receiver path between the rate matcherand the byte deserializer blocks. The 8B/10B decoder operates insingle-width and double-width modes, and can be bypassed if the8B/10B decoding is not necessary. In single-width mode, the 8B/10Bdecoder restores the 8-bit data + 1-bit control identifier from the 10-bitcode. In double-width mode, there are two 8B/10B decoders in parallel,which restores the 16-bit (2 × 8-bit) data + 2-bit (2 × 1-bit) control identifierfrom the 20-bit (2 × 10-bit) code. This 8B/10B decoder conforms to theIEEE 802.3 1998 edition standards.。

FPGA可编程逻辑器件芯片EP2S90F780I3N中文规格书