DSP与串行AD组成的高速并行数据采集系统

基于DSP技术的高速数据采集系统

J.数 字 信 号 数 据 采 集 的准 确 性 和 实 时性 是 关 系 到 整 个 系 统 精 度 的关 键 问 题 。受 运 算 速 度 及 算 l, t

章 启 成

( 南京 工程 学 院 , 江苏 南 京 2 】0 ) 110

【 摘 要 】 传输带宽和抗干扰能力是评价数据采集系统性能的重要指标 。本文采用高速数字信号处

理 ( i t i a P ̄'s g 简称 D P 心 片 T S 2 C 0构 成嵌 入 式数据 采 集 系统 , Dga Sg l l e i , il n sn S )4 4 - M 30 5 实现 数 据 的 高速 采 集 、 佶输 和存储 , 块化设 计 思 想及 大规模 可 编程 器件 的采 用 , 系统 具备 较 强 的可扩 展 性 。 模 使

【 关键词】 数据采集

D P 存储器 S

数 据 的正 确 实 时 采 集 是 系 统 数 据 分 析 和实 施 监 测 、 制 的前 提 , 控 因而 数 据 采 集 系 统 往 往 是 系 统

设计 和 歼 发 人 员 所非 常 关心 的 问题 。对 于数 据 采 集 系 统 的 性 能 , 从 以下 几 个 方 面 进 行 评 估 : 应

友好 等 特 点 。

系统 应 在 一 定 范 围 内 随指 标 要 求 变 化 可 扩 展 ;

( ) 机 交互 能 力 工 作 于 现 场 的采 集 器 还 应 具 备 便 携 性 、 于操 作 、 定 参 数 方 便 , 机 界 面 4人 易 设 人 小 文 没计‘ 数据 采 集 系 统 是 “ 字式 闭环 控 制 系统 ” 子 系 统 , 于 大 型 高 速 旋 转 机 械 的 多 参 的 数 的 用 数 实 时控 制 与监 测 。 虽 然 大 系统 采 用 双 闭环 反 馈 控 制 方 式 , 负 反 馈 本 身 只 能 对 前 项 通 道 上 出 现 但

基于DSP和高速A/D的电力系统多通道同步采样

A/D转换结束后产生一个中断信号EOC通知DSP读取数据,DSP通过地址选择相应A/D芯片及相关通道后,将16位数据读回。DSP以A/D转换器采集转换后的三相电压、三相电流实时数据作为计算基础。1.3 DSP核心部分电路 DSP及其外围接口电路是整个系统的核心,它由32位浮点DSP、振荡器+锁相倍频器、电压监测及看门狗电路、片外SDRAM、片外Flash、片外铁电存储器等电路组成。,电路实现了整个系统的上电复位、看门狗、电压检测以及扩展管理芯片对系统复位的功能。

外部的25 MHz振荡器通过倍频芯片和二进制计数器分别对DSP和AD转换器提供同步的150 MHz和3.125 MHz工作时钟。 DSP在上电复位以后,首先通过EDMA方式自动加载Flash前1 kB的Bootload程序,在该Bootload程序里写入后续加载程序的入口地址,即可实现应用程序的自动加载工作。之后对SDRAM进行自检,以避免SDRAM单元出错造成工作不正常或数据出错,同时SDRAM也是DSP存储A/D采样数据、进行数据运算输出的中间及最终结果、通信等数据缓存的场所。 FRAM可以实现在失电下保存数据,并且读写次数超过1012次,可以实现无延时写入。该FRAM通过DSP的McBSP接口相连,存储ADC每个模拟通道的DC偏移、精度修正的数据以及运行时的接线方式等参数。DSP处理完成的数据,通过其内部集成的主机接口(HPI)与上位机进行数据交互,主机可以通过DMA或EDMA方式随机或整块地访问共享RAM7。2 采样系统的软件设计 系统的软件设计基于TMS320C6711D芯片指令集,充分利用其高速,支持浮点运算,流水线操作等特点,采用C语言和汇编语言混合编程,遵循模块化、自顶向下、逐步细化的编程思想。程序使用模块化设计,主要包括采集模块、主循环模块和HPI交互协议模块3大模块,流程框图分别。3 结束语 本系统已经通过各种功能测试,并在国内某知名电表公司的电能质量监测仪产品上成功使用,精确检测电压电流有效值、功率、2~50次电压电流谐波的有效值、相位、电压波动与闪变、三相不平衡等各项电能质量参数,基本精度达到0.2级,谐波监测精度达到A级。该设计方案使用方便、实时性好、抗干扰能力强、测量精度高、性价比优,可在电力系统中广泛应用。

基于AD和DSP的高速数据采集系统方案介绍(优.选)

基于A/D和DSP的高速数据采集系统方案介绍中频信号分为和差两路,高速A/D与DSP组成的数据采集系统要分别对这两路信号进行采集。

对于两路数据采集电路,A/D与DSP的接口连接是一样的。

两个A/D同时将和路与差路信号采样,并分别送入两个FIFO;DSP分时从两个FIFO中读出采集的数据,完成数据的采集。

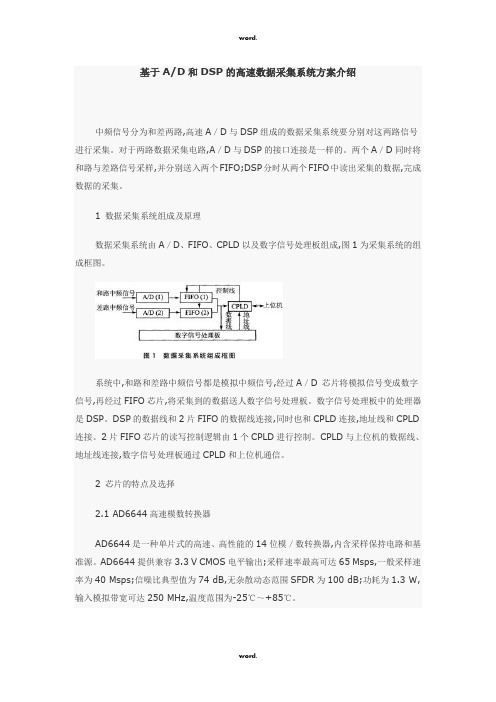

1 数据采集系统组成及原理数据采集系统由A/D、FIFO、CPLD以及数字信号处理板组成,图1为采集系统的组成框图。

系统中,和路和差路中频信号都是模拟中频信号,经过A/D 芯片将模拟信号变成数字信号,再经过FIFO芯片,将采集到的数据送人数字信号处理板。

数字信号处理板中的处理器是DSP。

DSP的数据线和2片FIFO的数据线连接,同时也和CPLD连接,地址线和CPLD 连接。

2片FIFO芯片的读写控制逻辑由1个CPLD进行控制。

CPLD与上位机的数据线、地址线连接,数字信号处理板通过CPLD和上位机通信。

2 芯片的特点及选择2.1 AD6644高速模数转换器AD6644是一种单片式的高速、高性能的14位模/数转换器,内含采样保持电路和基准源。

AD6644提供兼容3.3 V CMOS电平输出;采样速率最高可达65 Msps,一般采样速率为40 Msps;信噪比典型值为74 dB,无杂散动态范围SFDR为100 dB;功耗为1.3 W,输入模拟带宽可达250 MHz,温度范围为-25℃~+85℃。

AD6644采用三级子区式的转换结构,既保证了精度又降低了功耗,其功能框图如图2所示。

它的模拟信号输入方式是差分结构,每个输入的电压以2.4 V为中心,上下范围在0.55 V以内。

由于两个输入的相位相差180°,所以AD6644的模拟输入信号的最大峰一峰值为2.2 V。

由图2可以看出,差分模拟输入端先经过缓冲后进入第一个采样保持器(TH1)。

当编码时钟为高时,TH1进入保持状态。

TH1内保持的值作为粗的5位ADC1的输入。

基于DSP的高速数据采集与处理系统

基于DSP的高速数据采集与处理系统摘要:提出了一种基于DSP的高速数据采集系统的设计方案,对其中高速A/D、高速缓存、DSP控制以及数据通讯接口等内容进行了讨论,提出了更为有效的同步控制方式。

该设计方案电路简单、可进行多通道扩展、具有一定的通用性。

关键词:DSP 高速A/D FIFO 异步串行通讯在电子测量中,常常需要对高速信号进行采集与处理。

例如,在光传感技术中,对光脉冲散射信号的测量;在雷达工程中,对电磁脉冲信号的测量等,就需要对高速信号进行采集与算是,而且对此类高速信号的测量,往往对数据采集与处理系统提出严格的要求。

本文设计并实现了一种基于DSP的高速数据采集与处理。

该设计方案电路简单、可靠性好、具有一定的通用性、可以进行多通道扩展。

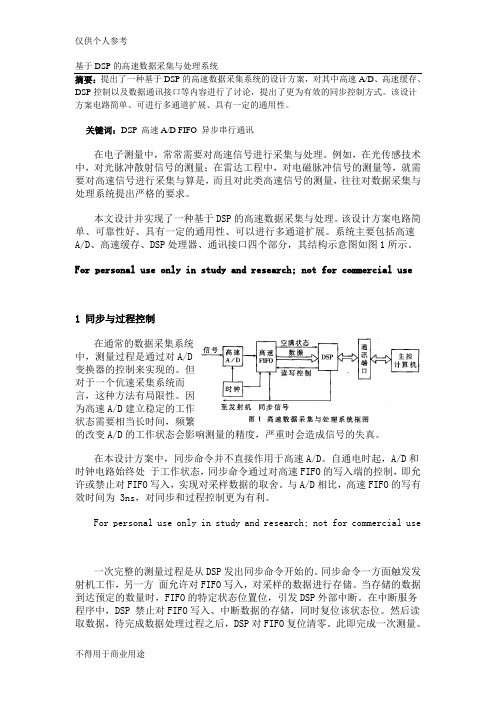

系统主要包括高速A/D、高速缓存、DSP处理器、通讯接口四个部分,其结构示意图如图1所示。

For personal use only in study and research; not for commercial use1 同步与过程控制在通常的数据采集系统中,测量过程是通过对A/D变换器的控制来实现的。

但对于一个伉速采集系统而言,这种方法有局限性。

因为高速A/D建立稳定的工作状态需要相当长时间,频繁的改变A/D的工作状态会影响测量的精度,严重时会造成信号的失真。

在本设计方案中,同步命令并不直接作用于高速A/D。

自通电时起,A/D和时钟电路始终处于工作状态,同步命令通过对高速FIFO的写入端的控制,即允许或禁止对FIFO写入,实现对采样数据的取舍。

与A/D相比,高速FIFO的写有效时间为 3ns,对同步和过程控制更为有利。

For personal use only in study and research; not for commercial use一次完整的测量过程是从DSP发出同步命令开始的。

同步命令一方面触发发射机工作,另一方面允许对FIFO写入,对采样的数据进行存储。

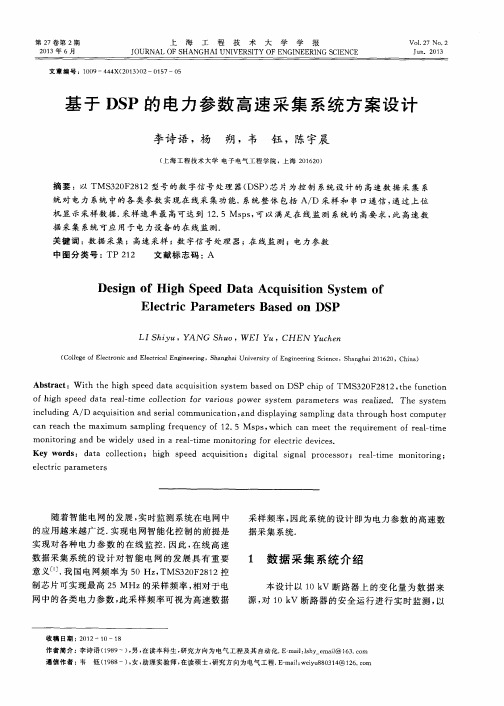

基于DSP的电力参数高速采集系统方案设计

据 采集 系统 可应 用于 电力设备 的在线监 测. 关 键 词 :数据 采集 ;高速 采样 ; 数 字信 号 处理 器 ; 在 线监 测 ;电力参数 中 图分 类 号 :T P 2 1 2 文献 标 志码 : A

随着智 能 电 网的发展 , 实 时监 测系统 在 电 网中 的应 用越 来 越广 泛. 实 现 电网智 能化 控制 的前 提是

实 现对各 种 电力 参 数 的 在 线监 控 . 因此 , 在线 高 速

采样 频率 , 因此 系统 的设计 即为 电力参 数 的高 速数

据采 集 系统.

数据 采集 系 统 的设 计 对 智 能 电 网的 发 展具 有 重 要 意义 J . 我 国电 网频 率 为 5 0 Hz , TMS 3 2 0 F 2 8 1 2控 制芯 片可 实现 最高 2 5 MHz 的采 样频 率 , 相 对 于 电

o f hi gh s pe e d d at a r e a l — t i me c ol l e c t i o n f or v a r i ou s p owe r s ys t e m pa r a me t e r s wa s r e a l i z e d

第 2 7卷 第 2期 2 0 1 3年 6月

上

海

工

程

技

术

大

学

学

报

V0 1 . 2 7 No . 2

J O UR NAL OF S HANGHAI UNI VE RS I TY 0F EN GI NE E RI NG S C I E NC E

基于DSP的高速数据采集系统设计与实现

基于DSP的高速数据采集系统设计与实现近年来,数字信号处理(Digital Signal Processing,DSP)得到了广泛的应用,特别是在高速数据采集系统中。

高速数据采集系统的设计和实现,对于科学研究和工业控制等领域至关重要。

因此,本文将重点讨论基于DSP的高速数据采集系统的设计和实现。

一、引言高速数据采集系统是一种用于采集高速数字信号的电子设备。

它们广泛应用于无线电通信、医疗仪器、控制系统、航空航天等领域。

为了更好地满足市场需求,高速数据采集系统需要具有高分辨率、高速率、高精度和低噪声等特性。

目前,市场上的高速数据采集系统大多采用DSP芯片作为数据处理核心。

DSP 芯片具有高性能、低功耗、灵活性强等特点,可以大大提高数据采集、处理和储存的效率。

因此,DSP技术已经成为高速数据采集系统设计的重要手段之一。

二、基于DSP的高速数据采集系统的设计和实现基于DSP的高速数据采集系统可以分为以下几个部分:信号输入模块、信号调理模块、数据处理模块和数据输出模块。

1. 信号输入模块信号输入模块是高速数据采集系统的核心组成部分之一。

其主要功能是将来自传感器和信号源的传输数据进行采集。

在设计信号输入模块时,需要考虑到信号源的信号特性以及传输介质的特性。

一般情况下,采用ASIC(Application Specific Integrated Circuit)芯片实现数据采集的模拟前端电路。

在信号输入模块中,需要进行信号放大、滤波、采样和数据转换等一系列操作。

这些操作需要满足系统对信号采集的高分辨率、高速率、高精度和低噪声的要求。

2. 信号调理模块信号调理模块用于对采集到的原始数据进行处理和提取。

该模块的主要任务是对信号进行滤波、去噪、分频和分析等操作,以便更好地适应后续的数据处理和分析。

信号调理模块的实现方式通常采用DSP芯片进行数据处理。

DSP芯片可以根据不同的信号特性,运用不同的算法进行信号调理。

在设计信号调理模块时,需要根据信号的特性和需求选择和设计合适的算法。

基于DSP的多通道高速数据采集系统

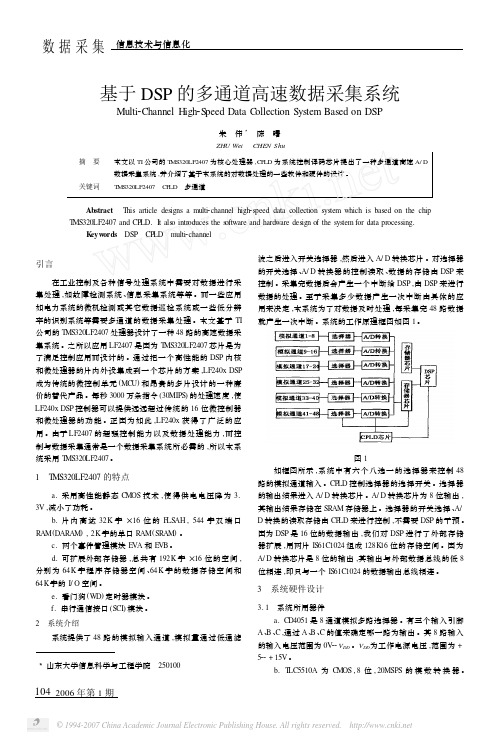

基于DSP 的多通道高速数据采集系统Multi 2Channel High 2S peed Data C ollection System Based on DSP朱 伟3 陈 曙ZH U Wei CHEN Shu摘 要 本文以TI 公司的T MS320LF2407为核心处理器,CP LD 为系统控制译码芯片提出了一种多通道高速A/D 数据采集系统,并介绍了基于本系统的对数据处理的一些软件和硬件的设计。

关键词 T MS320LF2407 CP LD 多通道 Abstract This article designs a multi 2channel high 2speed data collection system which is based on the chip T MS320LF2407and CP LD.It als o introduces the s oftware and hardware design of the system for data processing.K eyw ords DSP CP LD multi 2channel3山东大学信息科学与工程学院 250100引言在工业控制及各种信号处理系统中需要对数据进行采集处理,如故障检测系统、信息采集系统等等。

而一些应用如电力系统的微机检测或其它数据巡检系统或一些低分辨率的识别系统等需要多通道的数据采集处理。

本文基于TI 公司的T MS320LF2407处理器设计了一种48路的高速数据采集系统。

之所以应用LF2407是因为T MS320LF2407芯片是为了满足控制应用而设计的。

通过把一个高性能的DSP 内核和微处理器的片内外设集成到一个芯片的方案,LF240x DSP成为传统的微控制单元(MC U )和昂贵的多片设计的一种廉价的替代产品。

每秒3000万条指令(30MIPS )的处理速度,使LF240x DSP 控制器可以提供远远超过传统的16位微控制器和微处理器的功能。

基于DSP和ADS8364的高速数据采集处理系统.

基于DSP和ADS8364的高速数据采集处理系统随着现代科学技术的发展和计算机技术的普及,高速数据采集系统已应用于越来越多的场合,如通信、雷达、生物医学、机器人、语音和图像处理等领域。

本文介绍的数据采集处理系统采用CPLD控制ADS8364完成数据的A/D转换,转换后的数据预先存储到FIFO中,再经DSP进行前端的数字信号处理后,通过USB总线传给上位机,并在上位机上进行存储、显示和分析等。

该系统完全可以满足信号采集处理对高精度及实时性的要求。

1 系统原理数据采集处理系统主要由前端信号调理电路、ADC芯片ADS8364、CPLD 芯片EPM3128A、DSP芯片TMS320F2812、USB芯片CY7C68013及其外围电路组成。

系统原理框图如图l所示。

系统主要完成的任务为:DSP接收上位机通过USB总线发送的命令,完成系统工作参数的设置,并通过模拟地址/数据总线与CPLD进行通信,向CPLD发送控制命令;对外部的多路模拟量输入进行信号调理,在CPLD控制下进行单通道或多通道A/D转换,将采集到的数据存储在一片FIFO芯片中;当FIFO中存储的数据半满时,对DSP产生一个中断信号,DSP收到此中断信号后,取出FIFO中的部分数据,进行前端数字信号处理,将处理完毕的数据通过USB总线传给上位机;上位机实现各种图形界面操作和后端信号处理,对所采集的信号进行分析。

系统可对输入的多路模拟信号进行同步采样,这就使得采集到的数据不仅含有模拟信号的幅度特性,同时还保持不同模拟信号之间的相位差异;采样频率可以预置,以适应不同速率的采样要求。

2 系统硬件系统硬件包括信号调理模块、A/D转换模块、DSP处理器模块、CPLD 逻辑控制模块以及USB通信模块。

2.1 信号调理模块的设计外部的多路模拟量输入信号往往是微弱的传感器信号,信号的幅值较小,为了方便且不失一般性,假定其幅值范围为O~25mV。

ADS8364待转换的模拟输入电压范围应保持在AGND-0.3V和AVDD+O.3V之间。

基于DSP的双路高速数据采集系统的设计

基于DSP的双路高速数据采集系统的设计[摘要]:文章提出了一种基于DSP高速数据采集系统,该系统实现了对双路数兆赫兹的模拟信号进行采样和存储。

通过DSP控制数据采集和处理,通过串行口将SRAM中的数据上传到微机,以便进行进一步处理。

[关键字]:双路; 高速采样; DSP1. 引言数据采集是获取信息的基本手段,数字信号处理器(DSP)的出现,很好地满足了高速数据采集系统对于核心处理器的要求,并使得在其上实现数字信号处理算法变得简单。

本文本着实用、可靠、安全、简洁及经济等设计原则,提出了一种设计开发基于DSP技术的高速数据采集系统及数字信号处理方法。

2. 系统硬件电路设计本设计以DSP最小系统为中心,将外界模拟信号通过数据输入通道送到高速A/D转换器件进行采样和转换。

A/D转换结果先由TCL5510缓冲,然后在DSP 的控制下缓存到SRAM。

RS232接口电路用来实现系统与PC机之间的串行通信。

2.1 过程控制开机后,DSP发出时钟脉冲给ADC,控制AD转换。

每转换一次,立刻将16位(两路)数据写入2片512Kbyte(扩位连接)的存储器中。

这样一直循环采集,直到存储器满。

然后DSP置低INT0通知单片机读取数据,得到通知后,单片机将工作状态信号置为有效以应答,然后单片机直接控制SRAM读取数据(2片SRAM分别读取),并不断通过串口RS232将数据上传到PC机,当读取完数据后,再将工作状态信号置为无效。

DSP检测到工作状态信号置为无效后,又开始下一次的采集。

此时,PC机对上传的数据进行处理,如此循环。

2.2 高速A/D转换器高速A/D转换器选用TI公司的TLC5510,采样位数8位,最高采样速率20MSPS,模拟输入带宽达到了75 MHz,片内带有输入缓存和采样保持器,8位并行数据输出。

TLC5510的采集控制信号由DSP给出。

由于采集的是两路同步信号,为了达到完全同步和高速,采用两路并行工作的方式,即选择的是两片TLC5510,同时进行采集,然后并行的将这两路8位数据读入DSP,然后同时将这两路8位数据写入2片512KByte的SRAM中,基本原理如图1所示。

基于DSP的多通道高速数据采集系统

如框图所示 , 系统 中有 六个 八 选 一 的选择 器来 控 制 4 8

路的模拟通道输入。C L 控制选择器的选择开关。选择器 PD

的输 出结果进 入 AD转换 芯 片。AD 换芯 片为 8 / /转 位输 出 , 其输 出结果存储 在 SA R M存储 器上 。选 择器 的开关选择 、 D转换的读取存储 由 C L PD来进行控制 , 不需要 DP的干 预。 S 因为 DP l 位的数 据输 出 , S是 6 我们 对 DP进行 了外部存 储 S 器扩展 , 用两片 I 112 组成 1 K6 的存 储空 间。因为 S C04 6 2 1位 8

朱伟

陈 曙

H N Su z U W蕊 H C E h

Ab ta t T i r ce d s n utc a n lhg —p e aa cl cin ss m hc s bsd Olte c i sr c hsat l ei sa m l-h n e hse d dt ol t yt w i i ae i h hp i g i i e o e h T 30 F 4 7 ad C L MS 2 L 2 0 n P D.I as t d cstesf aea dh rw r eino tesse frd t rcsig t l i r u e ot r n ad aedsg f ytm aapo es . ono h w h o n

3 系统硬件设计

3 1 系统 所用器件 . ‘

a C 45 是 8通道模拟 多路 选择器 。有 三个 输入 引脚 . D01

系统提供 了 4 路 的模 拟输 入通 道 , 拟量 通 过低 通滤 8 模

A B c通过 A B C的值来确定哪一路为输出。其 8 、 、, 、、 路输入

基于DSP的高速多通道同步数据采集系统

基于DSP的高速多通道同步数据采集系统摘要:本文介绍了一种基于DSP的高速多通道同步数据采集系统。

该系统采用高精度的ADC和FPGA作为数据采集和处理的核心部件,通过DMA传输实现了多通道同步数据采集,并可以通过网络接口将采集的数据实时传输到上位机。

实验结果表明,该系统具有高精度、高速率和高可靠性等优点,可以满足对多通道同步数据采集的高要求。

关键词:DSP;高速多通道;同步数据采集;DMA传输;网络接口1. 引言在科学研究、医学诊断、工业控制等领域中,对数据采集系统的要求越来越高。

随着科学技术的不断发展,现代数据采集系统的要求也变得越来越高。

要求数据采集速度快、采集精度高、可靠性强、系统稳定性好。

因此,如何设计一种高速、高精度、高可靠性的多通道同步数据采集系统成为研究的热点之一。

2. 系统框架基于上述需求,本文设计了一种基于DSP的高速多通道同步数据采集系统。

该系统的部件结构如下图所示:其中,ADC为数据采集部分,FPGA为数据处理部分,DSP为数据管理和传输部分。

3. 数据采集部分数据采集部分采用高精度的ADC为核心部件。

该ADC采用的是16位的Sigma-Delta型ADC,采样率可达到100kSPS,可以满足多通道高速同步采集的要求。

为了实现多通道同步采集,采集部分还需要将多个通道的信号进行采集,并进行同步处理。

实现该功能需要向FPGA发送同步信号。

为了避免信号在传输过程中的延迟造成的误差,我们使用了双向同步FIFO,并设置了一些额外的同步逻辑来确保采集的信号可以达到很高的同步精度。

4. 数据处理部分数据处理部分采用FPGA作为核心部件。

该FPGA可以对采集到的数据进行在线实时处理。

在此过程中,FPGA实现了信号滤波、频率分析、功率谱分析、时域分析等多种功能。

这些功能可以满足不同领域的数据处理要求。

5. 数据管理和传输部分数据管理和传输部分采用DSP作为核心部件。

DSP主要负责管理数据的存储和传输。

一种多通道高速并行数据采集系统的设计与实现

图象 数据通道

广泛 的应 用 。 目前 已经大 量 使用 在 航 空 、航 天 、

军工领 域 中的有 关 飞行器 安全 检测 [ 1 ] ,以及 飞机

蜂窝 复合材 料 的检测 等方 面 。但在 应 用 中 ,该 技

术 虽 然体现 了一 定 的优越 性 .同时也 存在 一 些 问 题 。 由于采 用该方 法 必须 依靠 温 差 ,飞机 着 陆须 尽快 检查 ,时 间越 长 ,图像越 模糊 ,因此 ,要及 时获 得检测 数 据 .就 必须 设计 一个 具 有 高速 、实 时性 的红外 图象 数 据采 集 系 统 来 减少 检 测 误 差 。 根据该 系统 的特点 ,本文 采用 D P F G S + P A结 构设 计 的红外 图像采 集 系统满 足 了高 速数 据采 样 、快 速 运够 识 别 的汇 编 语 N I语 Sf  ̄

收 稿 日期 : 0 6 0 — 1 2 0 — 6 2

言代 码 ,这 使 得 D P 用 程 序 的开 发 如虎 添 翼 。 S应

3 电 子 元 器 件 主 用 2 0 .0 删 .h a C .e 2 0 61 C i E D nt n

行数据 采 集的设 计思路 。

关键 词 :数 据采 集 ;F G P A;数 据压 缩 ; D P S ;多通 道 ;高速 并行

0 引言

红外 热 成像 检测 技术 在检 测 领域 正 日益 得 到

标 提取 。其 系统 原理 如 图1 所示 。

,黑 __ ■■ __ ■_ ,_ ■l _ ■

据进行 处理 。

11 D P 片的选 择 . S芯

要 完成数 据 和信 息 的收集 和转 发 功 能 ,而用 现场

采用DSP+FPGA为核心实现DSP的高速并行处理系统

1 s2 I 的冗余 5

过 :0 I ; 1 3 s 5 2×7 x 0×2次 处 理 的 总 时 问 为 : 1 5 2×

7 2× 0I =22S 0× 3 s . 。可 见 1S内处 理 17Mbt x 1 i数 据 大 概 需要 3块 D P 考 虑 到 硬件 冗余 和 以后 的升 S, 级 需 求 , 终 确 定 采 用 4块 D P构 建 并 行 处 理 最 S

适 宜构 建多处 理 器 系 统 。 因此 , 性 能 和 功 耗 的角 从

度 , 终 采 用 TgrH C A S —S 0 _ 用 处 最 i S AR D PT 1 13 e 通

理器。

技 术 , 算 的 速 度 和 精 度 能 得 到 大 大 的 提 升 , 是 运 但 传 统单 处理 器系 统受 到 自身 特 性 的限制 , 算 速度 运

系统 。 我 们 认 为 可 采 用 以 D P+F G 形 式 为 核 心 、 S PA

1 并行 D P数量的分析 S

当今 占主要 地位 的高 性 能 D P有 很 多 种 , 合 S 综

20 0 7年 6月 2 0日收到 国家 自然科学基金资助项 目 (0 3 0 0 资助 6527 )

难以提高 , 仍无法满足其要求。现 阶段唯有建立 多 D P高速并行处理 系统 , S 不但能满足系统的实时性 要求 , 还易于建立一致性 的通用平 台。

文章 主要 就 是 介 绍 采 用 以 D P+ F G 的 形 S PA

式 2, , 提出了一种多 D P高速并行处理来提高运 J S 算速度的方案 , 并实现 了软硬 件通用处理平 台。多 信号并行处理技术 , 多路 D P并行技术研究是本文 S

维普资讯

基于DSP的高速数据采集系统的设计

基于DSP的高速数据采集系统的设计[摘要] 本文在讨论了TMS320VC5409DSP芯片和ADS7805AD转换芯片的特点的基础上,设计了具有较高精度和速度的数据采集系统。

并且给出了DSP芯片和AD转换芯片的接口原理图以及详细的串口初始化程序。

此系统不仅可以实现高速的数据采集与处理,而且精度高,稳定性好。

[关键词] ADS7805TMS320VC5409数据采集1 引言数据采集是获取信息的基本手段,而随着科技的发展,对数据采集系统及仪器的许多技术指标都提出了更高的要求。

要求不仅能稳定高速的进行高精度的数据采集与处理,而且还要有良好的人机界面以便能够对信号进行实时的分析与观测。

DSP作为数字信号处理器以其高速、高精度的性能广泛应用于数据采集、图像处理等控制领域。

本文设计的高速数据采集系统的主控制芯片即是采用TI公司提供的数字信号处理器(DSP)TMS320VC5409A-160芯片,A/D转换芯片选用的是AD公司推出的并行芯片ADS7805。

这些集成度较高的芯片,很好的实现了高速度、高精度、灵活、稳定、通用等优点。

2 系统总体方案设计本系统是一个高速信号采集处理系统,其硬件总体结构如图1所示。

系统的工作流程为:本数据采集处理系统通过USB接口接收PC机命令,进行数据采集与数据传输。

当系统接收指令后,将被测信号经过AD调理为适合DSP系统的电压范围,经过AD转换器转化成为数字信号预先存储到片外的RAM中,再经DSP按照一定的算法进行前端的数字信号处理后,通过总线传给上位机,并在上位机上进行存储、显示和分析等。

3各单元模块的设计从图1可以看出,在本设计中主要有A/D转换电路、DSP芯片、总线驱动器、FLASH存储器及SDRAM、逻辑控制单元和电源等组成。

下面介绍主要单元模块的设计。

3.1DSP基本系统的设计本设计采用的是TMS320VC5409A-160芯片。

这是TI公司的一款高性能、低功耗、高性价比的32位定点DSP芯片。

基于DSP的高速AD采集技术研究

基于DSP的高速AD采集技术研究一、引言数字信号处理已经成为各种现代控制系统的基础组成部分,需要各种传感器实时采集数据并进行处理。

高速AD采集技术是数字信号处理中不可缺少的一部分,通过使用这一技术,可以获得高速信号的精确数字表示。

其中的DSP技术可以使AD采集信号更准确、更灵活、更可靠。

本文将讨论基于DSP的高速AD采集技术,并介绍应用于该技术前的需求分析、硬件平台和软件设计的设计原则及方案。

二、前置需求分析在进行市场需求分析时,首先需要澄清AD转换器的类型,如采用高速PAM、Delta-SIGMA、SAR类型等。

这取决于所需的带宽和制噪能力。

高速PAM型AD转换器适用于高速采样和窄带传输,Delta-SIGMA的转换速度适中,制噪能力较高,广泛应用于无线通讯设备中。

SAR型转换器的转换速度可达到每秒数百兆赫,制噪能力很弱,但成本是最低的。

对于高速AD采集技术的要求之一是快速数据处理能力。

常用的方案是基于FPGA硬件设计方案和基于DSP硬件处理方案,本文重点关注DSP技术应用于该流程中实现高精准度和高速数据处理。

三、硬件平台及软件设计基于DSP处理采集数据可以更方便地实现高速AD采集处理,由于DSP的先进性和灵活性,使它能够应用于多种类型的信号处理任务。

在进行硬件平台的设计中,广泛应用FPGA进行高速数据缓存,此外,还可以同时采用SDRAM存储。

在设计FPGA和DSP硬件平台之前,必须考虑以下几个因素:1. 应用的速度:需确定高速采样频率及数据流的处理速度。

2. 采用的接口类型:为接驳采样或传感器而且必须确定合适的接口类型,并优化输入于输出速度及时延时间等。

3. 存储器结构:选用合适的存储器结构进行数据的缓存。

4. 电源相关要求:需满足高精度要求,其安装需要特殊的混频器。

5. 小型化和远离电场的要求:在实现高速AD采集处理的过程中需为电子电磁干扰(EMI)设定防止或减轻的措施,以保证数据的可靠性。

dsp与串行ad组成的高速并行数据采集系统

DSP与串行A/D组成的高速并行数据采集系统[日期:200577] 来源:今日电子作者:吉林大学通信工程学院卢海军王树勋[字体:大中小]摘要:根据高速定点DSP芯片TMS320VC5402的多通道缓冲串口特点和串行A/D转换芯片TLV1572的工作特性,提出了两片串行A/D和一片DSP串口的通信方案。

该系统充分利用了DSP的两个缓冲串口,可以使两路A/D转换数据高速并行传输。

同时文中给出了系统的硬件原理图和软件设计的部分关键程序。

关键词:DSP;多通道缓冲串口;A/D转换;数据采集引言TMS320VC5402(以下简称C5402)是德州仪器公司1999年推出的定点数字信号处理器(DSP)。

与TMS320C54x系列的其他芯片相比,C5402以其独有的高性能、低功耗和低价格受到了人们的广泛青睐。

C5402增强外设有软件等待状态发生器、锁相环时钟发生器、6通道直接存储器访问(DMA)控制器、增强型8位并行主机接口(HPI)等。

两个可编程的多通道缓冲串口(McBSP)能够全双工、快速地与其他同步串口进行数据交换,硬件连接简单,串口的工作模式和传送数据的格式可通过编程实现。

因为C5402内部没有集成A/D,因此在数据采集时需要使用A/D转换芯片,A/D芯片与C5402的接口设计成为一个重要的问题。

A/D转换芯片一般有串行A/D和并行A/D。

为了充分利用C5402所提供的多通道缓冲串口资源,简化系统设计,本文系统使用了TI公司的高速串行A/D来同时完成两路数据采集,大大提高了串口工作效率。

串行A/D芯片TLV1572TLV1572是高速的十位串行A/D转换芯片,可以通过3或4个串行口线直接与DSP或其他数字微处理器串口相连,不需要外加逻辑,但是转换速度受SCLK供给时钟的限制。

TLV1572与DSP的多通道缓冲串口相连是通过CS、SCLK、DO和FS四条线完成的,此时DSP的CLKR产生移位脉冲,FSR产生帧同步信号,并分别提供给TLV1572。

高速DSP与串行ADC

高速DSP与串行A/D转换器TLC2558接口的设计摘要:根据高速定点DSP芯片TMS320F206的特点,提出使用串行A/D转换器TLC2558作为DSP系统的模拟量输入部分,解决了以往基于并行数据传输的A/D转换器不能与高速DSP进行很好配合的问题。

在此基础上设计了DSP与串行A/D转换器连接的硬件电路,并就A/D转换在软件设计时应注意的问题进行了探讨。

关键词:串行通信,A/D转换,DSP,同步串行口DSP(Digital Signal Processor)芯片与单片机相比,具有运算速度更快、功能更强的特点,它自诞生以来在工业控制领域的应用越来越广泛。

随着DSP芯片应用的普及,DSP处理速度快的特点使它在与普通A/ D转换器接口时遇上了困难,使普通的、以并行接口传输数据的A/D转换器与DSP接口时出现读数不可靠的问题。

为此,需要利用DSP芯片的其它接口资源作为A/D转换数据的输入。

1 芯片简介1.1 TMS320F206TMS320F206是TI公司TMS320C2xx系列16位高速定点DSP芯片,具有先进的哈佛结构,采用流水线操作和高度专业化的指令系统,集成了片内外围设备和片内存储器。

当采用20MHz晶振作为时钟源时,它的主时钟周期为50ns。

F206芯片具有一个同步串行口,它能提供与编译码器、串行A/D转换器等串行器件的直接通信。

在20MHz的时钟下,发送和接收操作的最大传输速率是10Mbit/s,并有四级深度的发送和接收F IFO缓冲器,在与同步串行口相关的引脚中,DX为发送串行数据引脚;FSX是帧同步信号,用来启动传送(数据帧的开始);CLKX为发送时钟信号,定时进行位传送。

同步串行口接收部分对应的引脚相应为DR、FSR和CLKR。

1.2 TLC2558TLC2558也是TI公司生产的高性能12位串行模数转换器,共有8路模拟通道,最大采样率为400ksps,自带有8级FIFO,输入模拟量电压在0~5V之间。

基于DSP和AD976A的高速数据采集系统设计

基于DSP和AD976A的高速数据采集系统设计宋宇飞,沈卫康,周云松,戎红军(南京工程学院通信工程学院,江苏南京 211167)摘要:介绍了数据采集系统的发展状况,分析了高速数据采集系统应满足的性能要求,给出了系统硬件结构图及主要模块电路,说明了系统软件的结构与主要程序流程。

使用AD976A为A/D 转换芯片,DSP(TMS320C5402)为中央控制芯片,F T245BM为USB2.0通信接口芯片,FLASH 为数据存储芯片,最终完成了高速数据采集系统的设计方案。

关键词:DSP;数据采集;USB通信接口;数据存储中图分类号:TP274 文献标识码:A 文章编号:1672-1616(2007)19-0077-04 开放化、高速化和高精度化都是现代信息技术的发展趋势和研究热点。

数据采集系统是通信技术和数控技术领域的重要功能模块,应用领域十分广泛。

传统的数据采集系统,其中央控制多采用单片机或中规模数字电路,A/D芯片的采样速率也仅有几k/s到十几k/s。

现代数据采集系统要求高速、高精度及系统上具有数字信号处理功能。

传统的数据采集系统不完全满足这些要求,所以研究高速数据采集系统就显得十分必要。

本次设计的中央控制芯片选用DSP(Digital Signal Processor,数字信号处理芯片)。

DSP具有高速、高精度的运算能力,强大、方便的数据通信能力,灵活、可靠的编程与信号处理能力。

设计选用的A/D转换芯片是AD公司推出的AD976A,其转换精度是16位,转换速率最高可达200k/s。

系统的核心采用DSP控制AD976A实现高速数据采集的功能。

系统还需完成必要的数据通信与数据存储功能。

数据通信是将系统所采集的数据经通信接口传给上位机。

数据存储是在系统上存储必要的数据,防止数据由于系统突然掉电而丢失。

另外,DSP除完成对系统的中央控制外,还可以编写相关的数字信号处理算法程序。

这样就可在系统上方便实现对所采集的数据进行实时的数字信号处理,而不必增加其他硬件电路。

一文解析DSP与AD7656的高速AD采集电路

一文解析DSP与AD7656的高速AD采集电路一文解析DSP与AD7656的高速AD采集电路一、AD7656简介AD7656具有最大4 LSBS INL和每通道达250kSPS的采样率,并且在片内包含一个2.5V内部基准电压源和基准缓冲器。

该器件仅有典型值160mW 的功耗,比最接近的同类双极性输入ADC的功耗降低了60% 。

AD7656包含一个低噪声、宽带采样保持放大器(T/H),以便处理输入频率高达8MHz的信号。

该AD7656还具有高速并行和串行接口,可以与微处理器(mcu)或数字信号处理器(DSP)连接。

AD7656在串行接口方式下,能提供一个菊花链连接方式,以便把多个ADC连接到一个串行接口上。

AD7656工作原理:AD7656足具有独立的六通道逐次逼近型(SAR)的模数转换器,转换处理和数据的精度是通过CONVST信号和一个内部晶振控制的。

3个CONVST管脚允许3路ADC对独立同步采样。

当3个CONVST管脚连接到一起时,就可以进行6个通道的同步采样。

AD7656具有高速的并行和串行接口,允许其与Microprocessors和DSP进行接口。

当使用串行接口模式时,AD7656具有的菊花链特性允许多个ADC和一个串行接口连接。

由于在电力继电保护产品中以并行接口连接设计为主,所以下面将以并行接口的连接方式介绍其工作原理。

首先,通过MCU或DSP控制CONVST管脚启动转换,并保持该信号为高电平。

AD7656启动转换信号后会自动输出BUSY信号,BUSY信号下降沿时,代表转换已经全部完成。

此时,AD7656内部的6个寄存器中已经保存了转换的数据,然后通过控制片选CS和读RD 信号依次顺序读出6个通道AD转换值。

读出AD转换值后,改变CONVST为低电平信号。

注意在设计时,一定要保证AD转换过程中CONVST管脚保持高电平。

AD7656的应用:当前,继电保护产品在不断地更新换代并改变着设计模式。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

DSP与串行A/D组成的高速并行数据采集系统[日期:200577] 来源:今日电子作者:吉林大学通信工程学院卢海军王树勋[字体:大中小]摘要:根据高速定点DSP芯片TMS320VC5402的多通道缓冲串口特点和串行A/D转换芯片TLV1572的工作特性,提出了两片串行A/D和一片DSP串口的通信方案。

该系统充分利用了DSP的两个缓冲串口,可以使两路A/D转换数据高速并行传输。

同时文中给出了系统的硬件原理图和软件设计的部分关键程序。

关键词:DSP;多通道缓冲串口;A/D转换;数据采集引言TMS320VC5402(以下简称C5402)是德州仪器公司1999年推出的定点数字信号处理器(DSP)。

与TMS320C54x系列的其他芯片相比,C5402以其独有的高性能、低功耗和低价格受到了人们的广泛青睐。

C5402增强外设有软件等待状态发生器、锁相环时钟发生器、6通道直接存储器访问(DMA)控制器、增强型8位并行主机接口(HPI)等。

两个可编程的多通道缓冲串口(McBSP)能够全双工、快速地与其他同步串口进行数据交换,硬件连接简单,串口的工作模式和传送数据的格式可通过编程实现。

因为C5402内部没有集成A/D,因此在数据采集时需要使用A/D转换芯片,A/D芯片与C5402的接口设计成为一个重要的问题。

A/D转换芯片一般有串行A/D和并行A/D。

为了充分利用C5402所提供的多通道缓冲串口资源,简化系统设计,本文系统使用了TI公司的高速串行A/D来同时完成两路数据采集,大大提高了串口工作效率。

串行A/D芯片TLV1572TLV1572是高速的十位串行A/D转换芯片,可以通过3或4个串行口线直接与DSP或其他数字微处理器串口相连,不需要外加逻辑,但是转换速度受SCLK供给时钟的限制。

TLV1572与DSP的多通道缓冲串口相连是通过CS、SCLK、DO和FS四条线完成的,此时DSP的CLKR产生移位脉冲,FSR产生帧同步信号,并分别提供给TLV1572。

当TLV1572与其他串口微处理器相连接时FS必须提供高电平,通过CS、SCLK、DO三条线来完成数据传输。

当CS为高时,A/D芯片各管脚处于三态状态。

在CS由高变低时,TLV1572检测FS引脚的状态来确定工作模式,若FS为低则为DSP模式,若FS为高则为其他微处理器模式。

图一TL1572在DSP模式下的转换时序图图二TL1572在微处理器模式下的转换时序图当TLV1572工作在DSP模式时,必须保证在CS变低时,FS为低电平,并且要锁存一定时间。

CS为低时,DO跳出三态状态,但是直到FS为高时芯片才脱离休眠状态。

TLV1572在每个时钟SCLK的下降沿检测FS的状态,一旦检测到FS为高,TLV1572开始采样。

在FS的下降沿,A/D芯片通过移位时钟将数据移到DO上。

在6个前导0传送之后,DSP可以在时钟的下降沿得到A/D转换的数据,如图1所示。

在最低位移出之后,A/D芯片自动进入休眠状态,直到FS下一次有效。

如果FS在16位传输完成后立即有效,则A/D开始新的数据转换,此时A/D为连续转换。

若FS在TLV1572转换数据的过程中变高,则A/D芯片被复位,开始新的数据转换周期。

因此可以通过设置FS,改变数据传输的位数。

当TLV1572工作在非DSP模式下时,FS引脚必须接高电平。

在每次转换的过程中都必须提供16个时钟信号,若微处理器无法一次接收16位数据,可以分成8位两次接收,两次接收的时间间隔不能大于100μs,此时CS必须一直处于有效状态。

在DSP模式下转换的开始是由FS信号有效来决定的,而在微处理器模式下,数据转换CS有效后的第一个时钟信号上升沿开始的,如图2所示。

在微处理器模式下,也可以通过设置CS来改变传送的位数。

C5402的多通道缓冲串口C5402提供两个高速、全双工、多通道缓冲串行口McBSP0、McBSP1,用数据线D(R/X)、帧同步线FS(R/X)和移位时钟线CLK(R/X)实现发送数据和接收数据。

McBSP通过6个引脚(DX、DR、CLKX、CLKR、FSX和FSR)与外设接口。

(1)CLKX(发送时钟输入或输出)芯片内部发送以为寄存器(XSR)通过该时钟信号将数据发送到DX引脚。

该串口可以通过PCR寄存器的CLKXM位配置成使用内部时钟或者使用外部时钟。

(2)FSX(发送帧同步输入或输出)FSX是发送开始的标志,串口可以通过PCR寄存器的FXM位配置成输入或输出。

(3)DX(串行数据发送)串口数据发送是通过该口进行的。

(4)CLKR(接收时钟)CLKR用来接收外部时钟信号,该时钟信号将DR数据移入接收移位寄存器(RSR)。

可以通过PCR寄存器的CLKRM位配置成使用内部时钟或者使用外部时钟。

(5)FSR(接收帧同步输入)FSR接收帧同步脉冲信号,标志数据接收开始。

可以通过PCR寄存器的FRM位配置成输入,也可以配置成输出。

(6)DR(串行数据接收)串口数据接收是通过该口进行的。

接收过程中,数据首先通过移位时钟CLKR的作用下移入RSR(接收移位寄存器),然后,RSR中的数据再拷贝到DDR(数据接收寄存器),拷贝完成时,产生RINT中断通知CPU来响应或REVTA中断通知DMA响应,同时设置RRDY 中断标志位,也可以用查询方式来完成,从数据寄存器中读出数据。

CLKX、CLKR、FSX、FSR即可以由内部采样率发生器产生,也可以由外部设备驱动。

McBSP分别在相应时钟的上升沿和下降沿进行数据检测。

每个McBSP最多可支持128通道的发送和接收,串行字长可选,包括8、12、16、20、24和32位,还支持μ率和A率数据压缩扩展。

系统硬件设计在分析了C5402多通道缓冲串口和串行A/D转换器TLV1572工作特点后,可以利用TLV1572工作在DSP模式,使其与C5402进行接口,在同步时钟信号的作用下完成A/D转换的数据传输。

图3为整个数据采集系统的硬件原理图,本系统根据C5402的多通道缓冲串口特性,充分利用两个缓冲串口与两片串行A/D TLV1572进行数据传输。

为了达到与C5402很好匹配,A/D电源和参考电压都接了3.3V。

A/D的FS接DSP的FSX和FSR,使数据输入的帧同步信号由DSP产生。

SCLK接DSP的CLKX和CLKR,这样数据的输入和输出时钟均来自DSP。

C5402与两片A/D进行数据传输时,设置串口中断工作在00模式,即串口数据到达触发中断,这样CPU可以根据哪片A/D传输数据产生相应的串口中断RINT0或RINT1。

当两个串口的数据同时到达,即同时申请中断时,C5402的CPU会根据中断优先级响应RINT0中断,然后再响应中断RINT1。

为了保证数据通信的可靠性,避免数据冲突,在响应RINT1中断的过程中,串口0无中断请求。

C5402芯片内配置有4K×16bit片内屏蔽式的ROM(F000FFFF)。

在4K ROM资源里包含了Bootloader程序,它允许程序放在外部较慢的存储器或微处理器中,并调到高速的DRAM 存储器中运行,大大减小了C5402内部掩膜的需要,降低了电路设计成本。

系统独立工作的内部逻辑由CPLD来完成,如图4所示。

C5402上电复位装载时,由于Bootloader程序在初始化时设置XF为高电平,在系统进入并行引导装载模式后,C5402从数据寻址为0FFFFh单元(A15=1,选中Flash)中读取将要载入的程序存储区首地址,和并行转载数据流。

此时,C5402可以将AT29LV1024 Flash地址08000h~0FFFFh单元中的数据读到C5402对应于0000h~7FFFh寻址区的片内DARAM 和片外SRAM IS61LV6164中。

Bootloader程序结束后,在这个系统中,用户程序的第一条语句为RSBX XF,即置XF 引脚为低电平,Flash始终不选通。

这样,SRAM的高32K区域(08000h~0FFFFh)被释放出来,可以作为DSP系统运行时的数据区或程序区使用。

系统软件设计系统的软件设计主要包括多通道缓冲串口的初始化、串口中断服务程序和并行装载程序设计等。

● 程序设计应注意的问题(1)McBSP工作在数据接收中断方式,因此全局中断和串口中断的相应位应该合理设置。

同时,在设置中断向量表时,使中断向量表的位置与处理器模式状态寄存器PMST中的中断向量指针IPTR相对应,使IPTR的9位地址指向128字的中断向量所在的程序页,同时,中断向量表要严格按照C5402规定的格式编写,否则不能正确地产生需要的中断结果。

(2)要实现DSP数据采集系统的脱机独立运行,需要给每台DSP配备独立的程序存储器,在整个系统上电或者复位时,由引导装载程序将存于片外的程序代码装载到片内DARAM或者系统的扩展存储器中,然后运行程序来完成对McBSP进行设置和其他程序。

(3)为了实现两路A/D和C5402之间的时序匹配,避免数据冲突,需要注意C5402采样率发生寄存器SRGR1中CLKGDV位的设置,使C5402工作时钟周期大于两个串口中断的响应时间。

若TLV1572以400KSPS转换速率来计算,每片A/D应该是每2.5μs向DSP发送一次数据,申请中断,CPU响应中断来接收数据。

DSP工作在100MHz时,时钟周期为10ns,因此每个缓冲串口中断服务程序中可以执行一个少于125个时钟周期的程序而不影响串口的接收,若串口中断程序的时间不够用,还可以适当降低A/D转换速率,为串口中断提供更长的中断服务时间。

● 串口接收的部分初始化程序下面根据多通道缓冲串口的特性和两路串行A/D工作的要求,主要介绍一下串口接收的软件设计和串口部分关键设置。

;=====初始化串口0=====stm #0, SPSA0stm #0000h, SPSD0 ; #0000H写入SPCR10stm #1, SPSA0stm #0000h, SPSD0 ; #0000H写入SPCR20stm #2, SPSA0stm #0040h, SPSD0 ; #0040H写入RCRC10,每字16位stm #3, SPSA0stm #0040h, SPSD0 ; #0040H写入RCR20,每帧一段,每段一字stm #6, SPSA0stm #000fh, SPSD0 ; #0009H写入SRGR10,时钟周期CLKG=6.4MHzstm #7, SPSA0stm #300fh, SPSD0 ; #3010H写入SRGR20,帧周期为16个CLKGstm #0eh,SPSA0stm #0a04h, SPSD0 ; #0A04H写入PCR0,FSX, CLKX输出,FSR,CLKR输入;=====初始化串口1=====串口1的初始化程序参见串口0;=====启动接收=======stm #0,SPSA0stm #0001h, SPSD0 ;启动串口0接收stm #1,SPSA0stm #00c0h, SPSD0 ;内部产生时钟产生FSGstm #0,SPSA1stm #0001h, SPSD1 ;启动串口1接收stm #1,SPSA1stm #00c0h, SPSD1 ;内部产生时钟产生FSG;==串口0接收中断子程序===.sect "brint0"host_brint0:rsbx intm ;关中断ldm drr0,Astl A,*ar4+ ;接收……其他处理程序rete结束语本文介绍了两片串行A/D与C5402组成的数据采集系统,该系统硬件连接简单,A/D的采样率可以通过串口时钟灵活设置,通用性强。