74HC595

74HC595中文手册(手工翻译,可复制)

74HC595/74HCT595

它是带控制端的8位串行输入并行输入的移位寄存器,具有3态输出。

特点

➢8位串行输入

➢8位串行或并行输出

➢带有3态输出的存储寄存器

➢移位寄存器具有清零控制端

➢100MHz移位输出频率

➢输出能力:并行输出,总线驱动;串行输出,标准输出

应用

串行数据转并行

远程控制保持寄存器

相关描述

74HC/HCT595是高速硅栅CMOS元件与低功耗肖特基TTL引脚兼容。

它们符合JEDEC第7A号标准。

“595”是一个带存储器的8级串行移位寄存器,有3态输出。

移位寄存器以及存储寄存器有独立的时钟输入端。

当SH_CP端接收一个上跳沿时数据会发生移位。

当ST_CP端接收一个上跳沿时,移位寄存器中的数据将被送入存储寄存器。

当SH_CP端和ST_CP端短接时,移位寄存器当中所存储的数据将会永远比存储寄存器中的数据状态早一个时钟周期。

移位寄存器有一个串行输入(DS端)以及一个标准的串行级联输出端(Q7’)。

该芯片的8位移位寄存器有一个复位引脚(MR,低电平有效)。

存储寄存器有8条并行的3态总线连接至输出引脚。

只要芯片的输出使能引脚(OE)处于低电平,芯片就实时将存储寄存器中的数据输出至输出引脚。

74HC595简介

74HC595简介DS:串行数据输入,接Arduino的某个数字I/O引脚。

Q0~Q7:8位并行数据输出,可以直接控制8个LED,或者是七段数码管的8个引脚。

Q7′:级联输出端,与下一个74HC595的DS相连,实现多个芯片之间的级联。

SH_CP:移位寄存器的时钟输入。

上升沿时移位寄存器中的数据依次移动一位,即Q0中的数据移到Q1中,Q1中的数据移到Q2中,依次类推;下降沿时移位寄存器中的数据保持不变。

ST_CP:存储寄存器的时钟输入。

上升沿时移位寄存器中的数据进入存储寄存器,下降沿时存储寄存器中的数据保持不变。

应用时通常将ST_CP 置为低点平,移位结束后再在ST_CP端产生一个正脉冲更新显示数据。

MR:重置(RESET),低电平时将移位寄存器中的数据清零,应用时通常将它直接连高电平(VCC)。

OE:输出允许,高电平时禁止输出(高阻态)。

引脚不紧张的情况下可以用Arduino的一个引脚来控制它,这样可以很方便地产生闪烁和熄灭的效果。

实际应用时可以将它直接连低电平(GND)。

在一些不是很复杂的应用中,可以将MR和OE分别接VCC和地,只对DS、SH_CP和ST_CP三个引脚进行相关控制。

二 C语言程序#include<reg52.h>#include<intrins.h>#include<lcd.h>#define uchar unsigned char#define uint unsigned intsbit DS = P2^7;sbit SH_CP = P3^0;sbit ST_CP = P3^1;sbit duanx = P3^2;uchar disp_buffer[4];uchar const table[10]={48,49,50,51,52,53,54,55,56,57}; //1到9的ASCII码uchar const table2[]={0x3f,0x06,0x5b,0x4f,0x66,0x6d,0x7d,0x07,0x7f,0x6f,0x77,0x7c,0x39,0x5e,0x79,0x71};//共阴void remove_data(uchar Re_data);void lcd_init(void);void main(void){uint j = 0;uchar *s1 = "VALUE:",temp_data,disp_data,a;write_str(s1,0,0);write_str(s2,0,1);while(1){duanx = 0;a = table2[j++];remove_data(a);delay(100);disp_data = a;temp_data = disp_data/1000; writlcd();write_char(table[temp_data],7,0); temp_data = disp_data%1000/100; writlcd();write_char(table[temp_data],8,0); temp_data = disp_data%100/10; writlcd();write_char(table[temp_data],9,0); temp_data = disp_data%10;write_char(table[temp_data],10,0); if(j == 9 )j = 0;}}void remove_data(uchar Re_data){uint i;for(i=8; i>0; i--){if(Re_data&0x80)//判断高位是否为1 DS = 1;elseDS = 0;SH_CP = 0;_nop_();_nop_();SH_CP = 1;Re_data <<=1; //Re_data左移一位ST_CP = 0;_nop_();_nop_();ST_CP = 1; //上升沿将数据送到输出锁存器_nop_();_nop_();ST_CP = 0;}void lcd_init(void){lcd_rest();lcd_winst(0x01);set_cur(1);其中程序中红色部分便是对74HC595进移位和锁存操作。

移位寄存器74HC595中文资料

移位寄存器74HC595中文资料--------------------------------------------------------------------------------移位寄存器74HC595中文资料74HC595 是一款漏极开路输出的CMOS 移位寄存器,输出端口为可控的三态输出端,亦能串行输出控制下一级级联芯片。

74HC595特点:高速移位时钟频率Fmax>25MHz标准串行(SPI)接口CMOS 串行输出,可用于多个设备的级联低功耗:TA =25℃时,Icc=4μA(MAX)图1 74HC595引脚图74HC595引脚功能表:管脚编号管脚名管脚定义功能1、2、3、4、5、6、7、15QA—QH三态输出管脚8GND电源地9SQH串行数据输出管脚10SCLR移位寄存器清零端11SCK数据输入时钟线12RCK输出存储器锁存时钟线13OE输出使能14SI数据线15VCC电源端图2 74HC595逻辑图74HC595真值表:输入管脚输出管脚SISCKSCLRRCKOEXXXXHQA—QH 输出高阻XXXLQA—QH 输出有效值XXLXX移位寄存器清零L上沿HXX移位寄存器存储LH上沿HXX移位寄存器存储HX下沿HXX移位寄存器状态保持XXX上沿X输出存储器锁存移位寄存器中的状态值XXX下沿X输出存储器状态保持74HC595参数:Absolute Maximum Ratings绝对最大额定值参数数值Supply Voltage电源电压(VCC)−0.5 to +7.0VDC Input Voltage 直流输入电压(VIN)−1.5 to VCC +1.5VDC Output V oltage 直流输出电压(VOUT)−0.5 to VCC +0.5VClamp Diode Current 钳位二极管电流(IIK, IOK)±20mADC Output Current直流输出电流,每个引脚(输出)±35mADC VCC or GND Current,per pin (ICC)±70mAStorage Temperature Range 储存温度范围(TSTG)−65℃to +150℃Power Dissipation 功耗(PD)(Note 3)600mWS.O. Package only500mWLead Temperature (TL) (Soldering 10 seconds)260℃Recommended Operating Conditions建议操作条件参数最小最大单位Supply Voltage电源电压(VCC)26vDC Input or Output Voltage(VIN, VOUT)输入输出电压0VCCVOperating Temperature Range工作温度范围(TA)−40+85℃Input Rise or Fall Times 输入上升或下降时间(tr,tf) VCC = 2.0V-1000nsVCC = 4.5V-500nsVCC = 6.0V-400nsDC SPECIFICATIONS直流电气规格Symbol 符号Parameter 参数Conditions 条件VCCTA=25℃TA= −40to85℃TA= −55to125℃UNIT 单位典型Guaranteed Limits保证界限VIHMinimum High Level Input V oltage最大高电平输入电压-2.0V-1.51.51.5V4.5V-3.153.153.156.0V-4.24.24.2VILMaximum LOW Level Input V oltage最大低电平输入电压-2.0V-0.50.50.5V4.5V-1.351.351.356.0V-1.81.81.8VOHMinimum HIGH Level Output V oltage最大高电平输出电压VIN=VIH or VIL|IOUT|≤20μA2.0V2.01.91.91.9V4.5V4.54.44.44.46.0V6.05.95.95.9Q'HVIN = VIH or VILV|IOUT| ≤4.0mA4.5V4.23.983.843.7|IOUT| ≤5.2mA6.0V5.25.485.345.2QA thru QHVIN = VIH or VILV|IOUT| ≤6.0mA4.5V4.23.983.843.7IOUT| ≤7.8mA6.0V5.75.485.345.2VOLMaximum LOW Level Output V oltage最大低电平输出电压VIN=VIH or VIL|IOUT| ≤20μA2.0V0.10.10.1V4.5V0.10.10.16.0V0.10.1Q'HVIN = VIH or VILV|IOUT| ≤4mA4.5V0.20.260.330.4|IOUT| ≤5.2mA6.0V0.20.260.330.4QA thru QHVIN = VIH or VILV|IOUT| ≤6.0mA4.5V0.20.260.330.4|IOUT| ≤7.8mA6.0V0.20.260.330.4IINMaximum Input Current最大输入电流VIN=VCC or GND6.0V±0.1±1.0±1.0μAIOZMaximum 3-STATE Output Leakage最大3态输出泄漏电流VOUT = VCC or GND G = VIH6.0V-±0.5±5.0±10μAICCMaximum Quiescent Supply Current电源电流VIN=VCC or GND IOUT = 0μA6.0V-8.080160μA交流电气特性:Symbol 符号Parameter 参数Conditions 条件典型Guaranteed LimitUNIT 单位fMax最高工作频率-5030MHztPHL, tPLHMaximum Propagation Delay,最大传输延迟SCK to Q’HCL = 45 pF1220nstPHL, tPLHMaximum Propagation Delay, 最大传输延迟RCK to QA thru QHCL = 45 pF1830nstPZH, tPZLMaximum Output Enable Time from G to QA thru QH 最大输出启用时间G to QA thru QH RL=1kΩ CL=45pF1728nstPHZ, tPLZMaximum Output Disable Time from G to QA thru QH最大输出禁用时间G to QA thru QH RL=1kΩ CL=5pF1525nstSMinimum Setup Time from SER to SCK--20nstSMinimum Setup Time from SCLR to SCK--20nstSMinimum Setup Time from SCK to RCK--40nstHMinimum Hold Time from SER to SCK--nstWMinimum Pulse Width of SCK or RCK--16ns本文来自: 原文网址:/info/cmos/0083302.html。

4、74hc595

什么是 74HC595

74HC595 是具有 8 位移位寄存器和一个存储器,三态输出功能。 移位寄存器和存储器是分别的时钟。 数据在 SCHcp 的上升沿输入,在 STcp 的上升沿进入的存储寄存器中去。如果两个时钟连在一起,则移位寄存 器总是比存储寄存器早一个脉冲。移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的 低电平复位,存储寄存器有一个并行 8 位的,具备三态的总线输出,当使能 OE 时(为低电平),存储寄存器的数 据输出到总线。

2.2 动态显示

输入管脚

输出管脚

SCL

SI

SCK

RCK

OE

R

X

X

X

X

H

QA—QH 输出高阻

X

X

X

X

L

QA—QH 输出有效值

X

X

L

X

X

移位寄存器清零

L

上沿

H

X

X

移位寄存器存储 L

H

上沿

H

X

X

移位寄存器存储 H

X

下沿

H

X

X

移位寄存器状态保持

X

X

X

上沿

X

输出存储器锁存移位寄存器中的状态值

X

X

X

下沿

X

输出存储器状态保持

IO0SET = spi_ds; else

IO0CLR = spi_ds; data <<= 1; IO0SET = spi_shcp; } IO0SET = spi_stcp; }

1 引言

单片机应用系统中使用的显示器主要有 LED 和 LCD 两种。近年来也有用 CRT 显示的。前者价格低廉,配置灵 活,与单片机接口方便;后者可进行图形显示,但接口较复杂,成本也较高。LED(Ling Emiting Diode)是发光二极 管的缩写。实际应用非常普遍的是八段 LED 显示器。LED 显示器在大型报时屏幕,银行利率显示,城市霓虹灯建 设中,得到广泛应用。在这些需要多位 LED 显示的场合,怎样实现系统稳定,价格低廉的显示,成为决定其成本

74HC595详解

74HC595 详解

工作电压2-6V,推荐5V。

14 脚串行输入:595 的数据来源只有这一个口,一次只能输入一个位,那

幺连续输入8 次,就可以积攒为一个字节了。

13 脚OE 输出使能控制脚:如果它不工作,那幺595 的输出就是高阻态,595 就不受我们程序控制了,这显然违背我们的意愿。

OE 的上面画了一条线,表示他是低电平有效。

于是我们将他接GND。

10 脚SRCLR 位移寄存器清空脚:他的作用就是将位移寄存器中的数据

全部清空,这个很少用到,所以我们一般不让他起作用,也是低电平有效,于是我们给他接VCC。

12 脚RCLK 存储寄存器:数据从位移寄存器转移到存储寄存器,也是需要

时钟脉冲驱动的,这就是12 脚的作用。

它也是上升沿有效。

11 脚SRCLK 移位寄存器时钟输入:当一个新的位数据要进来时,已经进

入的位数据就在移位寄存器时钟脉冲的控制下,整体后移,让出位置。

分析下数据输入和输出过程:

假如,我们要将二进制数据0111 1111 输入到595 的移位寄存器中,下面。

74HC595芯片资料53971

74HC595芯片资料8位串行输入/输出或者并行输出移位寄存器,具有高阻关断状态。

三态。

特点8位串行输入8位串行或并行输出存储状态寄存器,三种状态输出寄存器可以直接清除100MHz的移位频率输出能力并行输出,总线驱动串行输出;标准中等规模集成电路应用串行到并行的数据转换Remote control holding register.描述595是告诉的硅结构的CMOS器件,兼容低电压TTL电路,遵守JEDEC标准。

595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SCHcp的上升沿输入,在STcp的上升沿进入的存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

参考数据CPD决定动态的能耗,PD=CPD×VCC×f1+∑(CL×VCC2×f0)F1=输入频率,CL=输出电容f0=输出频率(MHz)Vcc=电源电压功能表H=高电平状态L=低电平状态↑=上升沿↓=下降沿Z=高阻NC=无变化×=无效当MR为高电平,OE为低电平时,数据在SHCP上升沿进入移位寄存器,在STCP上升沿输出到并行端口。

/***************************************************************************************/ 给个74HC595的"慢动作"void WriteSIOByte(unsigned char val){unsigned char i;ACC = val;for (i = 8; i > 0; i --) {SRCLK = 0;//拉低74HC595时钟_rrca_();//右移一位数据SER = CY;//发送74HC595一位串行数据SRCLK = 1;//拉高74HC595时钟_nop_();//延时}SER = 1;//释放数据总线//以下3条指令若在多字节时,应该移入多字节全发送完后在执行此3条指令RCLK = 0;_nop_();//延时RCLK = 1;//打入并行数据}74ls595"速射"hotpowerfor(i = 0; i < buffsize; i ++){SBUF = siobuff[i];while(TI == 0);TI = 0;}RCLK = 0;_nop_();//延时RCLK = 1;//打入并行数据/************************************************************************/摘要:本文介绍了应用移位寄存器芯片74HC595实现LED动、静态显示的基本原理。

74hc595驱动数码管

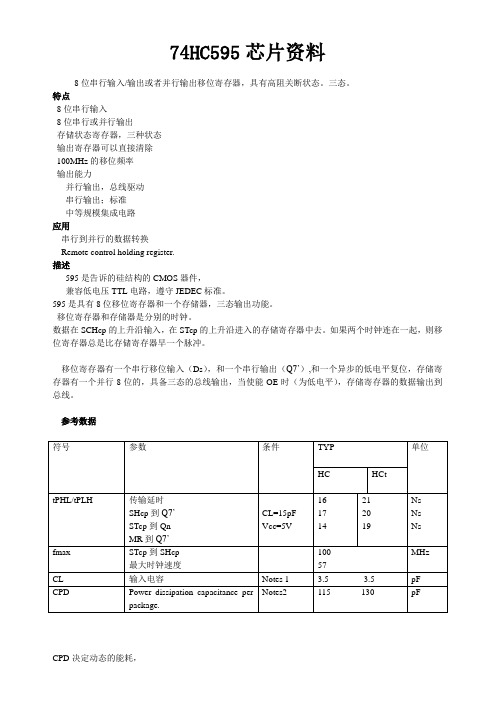

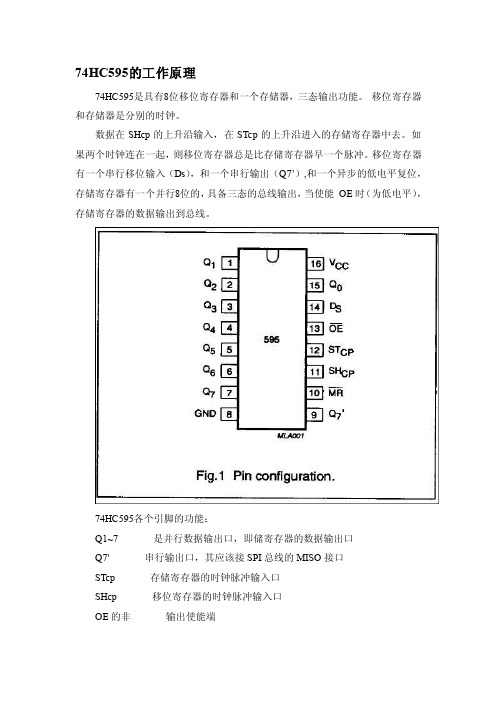

74HC595的工作原理74HC595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SHcp的上升沿输入,在STcp的上升沿进入的存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

74HC595各个引脚的功能:Q1~7 是并行数据输出口,即储寄存器的数据输出口Q7' 串行输出口,其应该接SPI总线的MISO接口STcp 存储寄存器的时钟脉冲输入口SHcp 移位寄存器的时钟脉冲输入口OE的非输出使能端MR的非芯片复位端Ds 串行数据输入端程序说明:每当SHcp上升沿到来时,DS引脚当前电平值在移位寄存器中左移一位,在下一个上升沿到来时移位寄存器中的所有位都会向左移一位,同时Q7'也会串行输出移位寄存器中高位的值,这样连续进行8次,就可以把数组中每一个数(8位的数)送到移位寄存器;然后当STcp上升沿到来时,移位寄存器的值将会被锁存到锁存器里,并从Q1~7引脚输出。

//74HC595串行输出数据void outdisp(unsigned char num){unsigned char i;for (i=0;i<8;i++ ){DS=num;SHCP=1;SHCP=0;num<<=1;}}74595的数据端:1)、QA--QH: 八位并行输出端,可以直接控制数码管的8个段。

2)、QH': 级联输出端。

我将它接下一个595的SER端。

3)、SER: 串行数据输入端。

74595的控制端说明:1) 、/SCLR(10脚): 低点平时将移位寄存器的数据清零。

通常我将它接Vcc。

2)、SCK(11脚):上升沿时数据寄存器的数据移位。

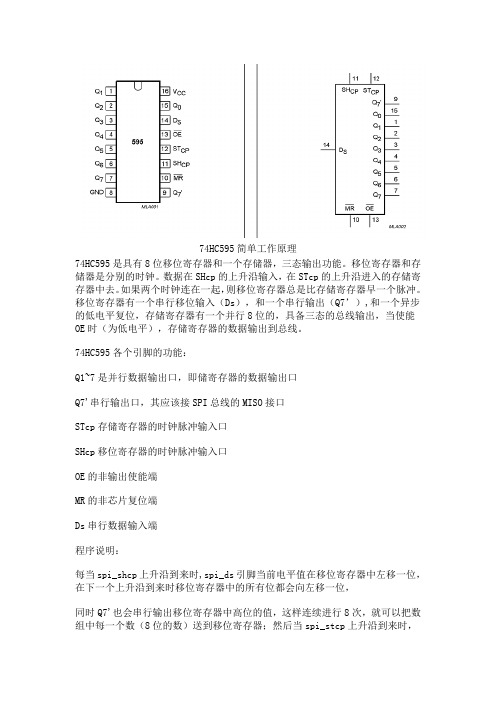

74HC595完整中文资料

74HC595是8位串行输入/输出或者并行输出移位寄存器,具有 咼阻、关、断状态。

三态。特点8位串行输入8位串行或并行输出 存储状态寄存 器,三种状态输出寄存器可以直接清除100MHz的移位频率输出能 力 并行输出,总线驱动 串行输出;

标准 中等规模集成电路应用 串行到并行的数据转换Remote c ontrol holding register.描述595是告诉的硅结构的CMO器件,

CPD决 定动态的能耗,PD=CPD< VCC< f1 +刀(CLXVCC2< f0) F 1=输入频率,。1=输出电容f0=输出频率(MHZ Vcc=电源电压 引脚说明符号引脚描述

内部结构

结合引脚说明就能很快理解595的工作情况

功能表:

管脚编号

管脚名

管脚定义功能

1、2、3、4、5、6、

7、15

QA—QH

2)74595的主要优点是具有数据存储寄存器,在移位的过程中,输出 端的数据可以保持不变。这在串行速度慢的场合很有用处,数码管没 有闪烁感。

与164只有数据清零端相比,595还多有输出端时能/禁止控制 端,可以使输出为高阻态。

3)595是串入并出带有锁存功能移位寄存器,它的使用方法很简单, 在正常使用时SCLR为高电平,G为低电平。从SER每输入一位数据, 串行输595是串入并出带有锁存功能移位寄存器,它的使用方法很简 单,如下面的真值表,在正常使用时SCLF为高电平,G为低电平。 从SER每输入一位数据,串行输入时钟SCK上升沿有效一次,直到八 位数据输入完毕,输出时钟上升沿有效一次,此时,输入的数据就被

送到了输出端。入时钟SCK上升沿有效一次,直到八位数据输入完毕, 输出时钟上升沿有效一次,此时,输入的数据就被送到了输出端。

74HC595简介

74HC595简介DS:串行数据输入,接Arduino的某个数字I/O引脚。

Q0~Q7:8位并行数据输出,可以直接控制8个LED,或者是七段数码管的8个引脚。

Q7′:级联输出端,与下一个74HC595的DS相连,实现多个芯片之间的级联。

SH_CP:移位寄存器的时钟输入。

上升沿时移位寄存器中的数据依次移动一位,即Q0中的数据移到Q1中,Q1中的数据移到Q2中,依次类推;下降沿时移位寄存器中的数据保持不变。

ST_CP:存储寄存器的时钟输入。

上升沿时移位寄存器中的数据进入存储寄存器,下降沿时存储寄存器中的数据保持不变。

应用时通常将ST_CP 置为低点平,移位结束后再在ST_CP端产生一个正脉冲更新显示数据。

MR:重置(RESET),低电平时将移位寄存器中的数据清零,应用时通常将它直接连高电平(VCC)。

OE:输出允许,高电平时禁止输出(高阻态)。

引脚不紧张的情况下可以用Arduino的一个引脚来控制它,这样可以很方便地产生闪烁和熄灭的效果。

实际应用时可以将它直接连低电平(GND)。

在一些不是很复杂的应用中,可以将MR和OE分别接VCC和地,只对DS、SH_CP和ST_CP三个引脚进行相关控制。

二 C语言程序#include<reg52.h>#include<intrins.h>#include<lcd.h>#define uchar unsigned char#define uint unsigned intsbit DS = P2^7;sbit SH_CP = P3^0;sbit ST_CP = P3^1;sbit duanx = P3^2;uchar disp_buffer[4];uchar const table[10]={48,49,50,51,52,53,54,55,56,57}; //1到9的ASCII码uchar const table2[]={0x3f,0x06,0x5b,0x4f,0x66,0x6d,0x7d,0x07,0x7f,0x6f,0x77,0x7c,0x39,0x5e,0x79,0x71};//共阴void remove_data(uchar Re_data);void lcd_init(void);void main(void){uint j = 0;uchar *s1 = "VALUE:",temp_data,disp_data,a;write_str(s1,0,0);write_str(s2,0,1);while(1){duanx = 0;a = table2[j++];remove_data(a);delay(100);disp_data = a;temp_data = disp_data/1000; writlcd();write_char(table[temp_data],7,0); temp_data = disp_data%1000/100; writlcd();write_char(table[temp_data],8,0); temp_data = disp_data%100/10; writlcd();write_char(table[temp_data],9,0); temp_data = disp_data%10;write_char(table[temp_data],10,0); if(j == 9 )j = 0;}}void remove_data(uchar Re_data){uint i;for(i=8; i>0; i--){if(Re_data&0x80)//判断高位是否为1 DS = 1;elseDS = 0;SH_CP = 0;_nop_();_nop_();SH_CP = 1;Re_data <<=1; //Re_data左移一位ST_CP = 0;_nop_();_nop_();ST_CP = 1; //上升沿将数据送到输出锁存器_nop_();_nop_();ST_CP = 0;}void lcd_init(void){lcd_rest();lcd_winst(0x01);set_cur(1);其中程序中红色部分便是对74HC595进移位和锁存操作。

74HC595

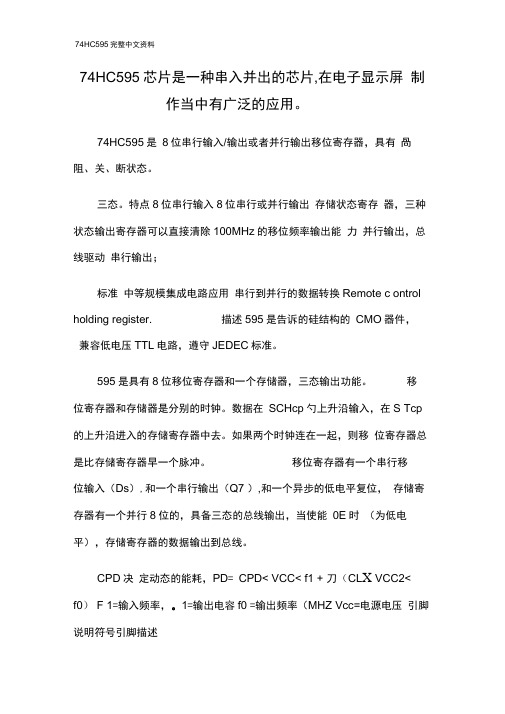

74HC595引脚说明工作原理简述:一、74HC595逻辑功能:它和74HC164的功能类似,都是串入并出的IO接口,将串行的数据,转为并行的输出,这样可以节约MCU的IO口资源。

主要应用在多路LED指示或多位数码管驱动方面。

但与74HC164比,595主要还有以下更优越的功能:1.支持3态输出,当第13脚为高电平时,595无输出;2.具有数据锁存功能,这样不会影响移位时的瞬时输出;3.具有数据输出功能,可以更方便的进行595级联二、595引脚描述:1. 第1脚:数据输出端QB2. 第2脚:数据输出端QC3. 第3脚:数据输出端QD4. 第4脚:数据输出端QE5. 第5脚:数据输出端QF6. 第6脚:数据输出端QG7. 第7脚:数据输出端QH8. 第8脚:电源GND9. 第9脚:串行数据输入端SQH,时钟下降沿数据移出10. 第10脚:复位引脚RESET11. 第11脚:数据移位时钟输入端SCK12. 第12脚:数据锁存信号输入端RCK13. 第13脚:数据输出使能端/OE,低电平有效14. 第14脚:串行数据输入端A,时钟上升沿数据移入15. 第15脚:数据输出端QA16. 第16脚:电源VDD三、74HC595工作原理简述:74HC595是一款具有8位移位寄存器和一个存储器,三态输出功能的驱动芯片。

移位寄存器和存储器分别具有独立的时钟信号。

数据在SHCP的上升沿输入,在STCP的上升沿进入到存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(DS),和一个串行输出(Q7’),和一个异步的低电平复位(MR),存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

四、74HC595实现LED静、动态显示基本原理2.1 静态显示每位LED显示器段选线和74HC595的并行输出端相连,每一位可以独立显示(见图1)。

74HC595资料

2.0V

-

0.5

0.5

0.5

V

4.5V

-

1.35

1.35

Hale Waihona Puke 1.356.0V-

1.8

1.8

1.8

VOH

Minimum HIGH Level Output Voltage最大高电平输出电压

VIN=VIH or VIL|IOUT|≤20μA

2.0V

2.0

1.9

1.9

1.9

V

4.5V

4.5

4.4

4.4

4.4

−65℃to +150℃

Power Dissipation功耗(PD)

(Note 3)

600mW

S.O. Package only

500mW

Lead Temperature (TL) (Soldering 10 seconds)

260℃

Recommended Operating Conditions建议操作条件

VIN=VCC or GND IOUT = 0μA

6.0V

-

8.0

80

160

μA

交流电气特性:

Symbol符号

Parameter参数

Conditions条件

典型

Guaranteed Limit

UNIT单位

fMax

最高工作频率

-

50

30

MHz

tPHL, tPLH

Maximum Propagation Delay,最大传输延迟SCK to Q’ H

−0.5 to VCC +0.5V

Clamp Diode Current钳位二极管电流(IIK, IOK)

LED驱动芯片-74HC595中文资料

2V

75

175

tPZL 的最大延迟时 CL =50pF

间(普通状态) CL =150pF 2V

100

245

CL =50pF 4.5V 15

35

TA=25 to 85℃ TA=-55 to 125℃

极限值

4.8

4.0

24

20

28

24

265

315

367

441

53

63

74

88

45

54

63

76

220

265

306

58

210

CL =150pF 2V

83

294

tPHL SCK 到 Q’H 的 CL =50pF 4.5V

14

42

tPLH 最大延迟时间 CL =150pF 4.5V

17

58

CL =50pF 6V

10

36

CL =150pF 6V

14

50

CL =50pF 2V

70

175

tPHL tPLH

RCK 到 QA 至 QH 的最大延迟

17

42

tPHZ

G 到 QA 至 QH 的最大延迟时

RL =1kΩ

2V 4.5V

75 15

175 35

tPLZ

间(高阻态) CL =50pF

6V

13

30

SER 到 SCK 最

tS

小状态建立时

间

2V

100

4.5V

20

6V

17

SCLR 到 SCK

tR

最小状态建立

时间

2V

50

74HC595引脚和原理说明

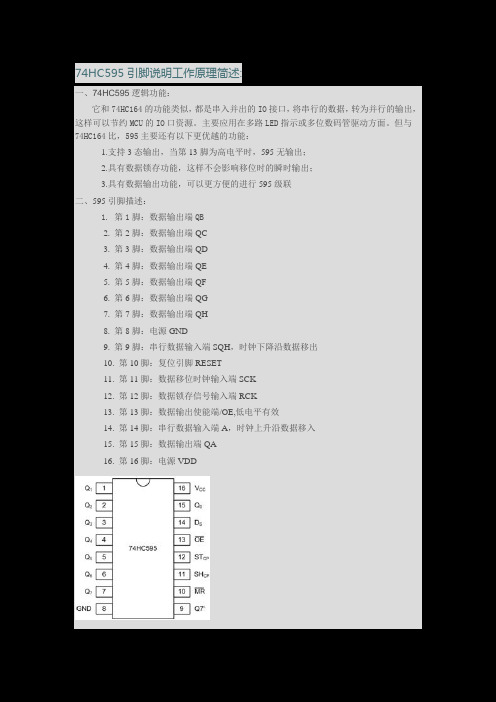

74HC595引脚和原理说明74HC595是一款串行输入并行输出的移位寄存器芯片,常用于扩展微控制器的GPIO引脚数量。

它可以扩展输出引脚数量,实现同时控制多个设备的功能,而只使用微控制器上的几个引脚。

下面将详细介绍74HC595的引脚和原理。

1.DSRCK:数据输入时钟引脚,用于控制数据输入的时序。

2.SER:串行输入引脚,通过这个引脚输入数据。

3.RCLK:寄存器时钟引脚,用于将数据从移位寄存器传输到输出寄存器。

4.SRCLK:移位寄存器时钟引脚,用于控制移位寄存器的数据移位。

5.OE:输出使能引脚,控制输出寄存器是否被使能。

6.Q0-Q7:并行输出引脚,用于控制外部设备。

在工作原理方面,74HC595具有多个移位寄存器,其中有一个移位寄存器用于串行数据输入,另一个用于并行数据输出。

它通过移位寄存器实现了数据的移位和缓存功能。

当移位寄存器时钟(SRCLK)上升沿到来时,串行输入引脚(SER)上的数据被移位寄存器接收。

这样,在每个移位寄存器时钟周期内,数据从一个寄存器移动到下一个,直到移动到最后一个寄存器。

当寄存器时钟(RCLK)上升沿到来时,移位寄存器中的数据被存储到输出寄存器中。

这样,在每个寄存器时钟周期内,数据从移位寄存器传输到输出寄存器。

输出寄存器中的数据通过并行输出引脚(Q0-Q7)控制外部设备。

这些引脚可以连接到其他设备,例如LED、继电器、数码管等等。

通过编程控制输出寄存器的数据,可以实现对这些外部设备的控制。

然而,为了保护外部设备和减少功耗,输出使能引脚(OE)可用于控制输出寄存器是否被使能。

当该引脚为低电平时,输出寄存器被使能,数据可以传输到外部设备。

当该引脚为高电平时,输出寄存器被禁用,外部设备不受控制。

除了上述功能,74HC595还具有级联功能。

通过将多个74HC595连接在一起,可以扩展输出引脚的数量。

此时,第一个74HC595的输出引脚(Q0-Q7)连接到第二个74HC595的串行输入引脚(SER),以此类推。

74HC595资料

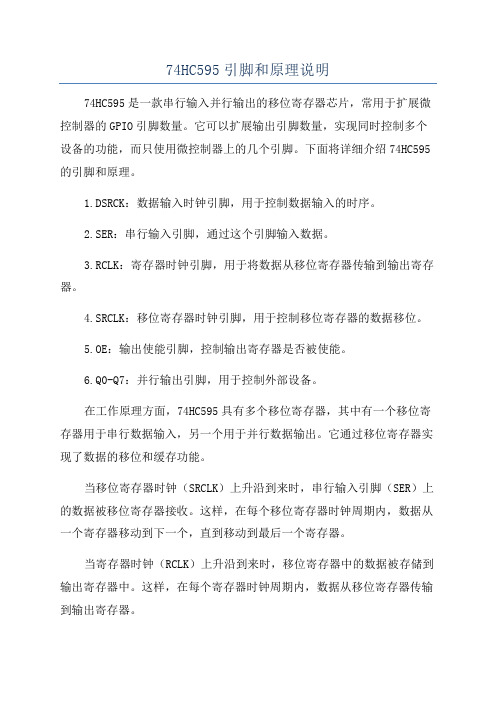

74HC595简单工作原理74HC595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SHcp的上升沿输入,在STcp的上升沿进入的存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

74HC595各个引脚的功能:Q1~7是并行数据输出口,即储寄存器的数据输出口Q7'串行输出口,其应该接SPI总线的MISO接口STcp存储寄存器的时钟脉冲输入口SHcp移位寄存器的时钟脉冲输入口OE的非输出使能端MR的非芯片复位端Ds串行数据输入端程序说明:每当spi_shcp上升沿到来时,spi_ds引脚当前电平值在移位寄存器中左移一位,在下一个上升沿到来时移位寄存器中的所有位都会向左移一位,同时Q7'也会串行输出移位寄存器中高位的值,这样连续进行8次,就可以把数组中每一个数(8位的数)送到移位寄存器;然后当spi_stcp上升沿到来时,移位寄存器的值将会被锁存到锁存器里,并从Q1~Q7引脚输出;附子程序:voidhc595send_data(uint8data)//要传输的数据,建议用数组的方法来查询{uint8i;IO0CLR=spi_stcp;12脚for(i=0;i<8;i++){IO0CLR=spi_shcp;11脚if((data&0x80)!=0)IO0SET=spi_ds;elseIO0CLR=spi_ds;data<<=1;IO0SET=spi_shcp;}IO0SET=spi_stcp;}1引言单片机应用系统中使用的显示器主要有LED和LCD两种。

近年来也有用CRT显示的。

前者价格低廉,配置灵活,与单片机接口方便;后者可进行图形显示,但接口较复杂,成本也较高。

74HC595完整中文资料

74HC595芯片是一种串入并出的芯片,在电子显示屏制作当中有广泛的应用。

74HC595是8位串行输入/输出或者并行输出移位寄存器,具有高阻、关、断状态。

三态。

特点 8位串行输入 8位串行或并行输出存储状态寄存器,三种状态输出寄存器可以直接清除 100MHz的移位频率输出能力并行输出,总线驱动串行输出;标准中等规模集成电路应用串行到并行的数据转换 Remote contr ol holding register. 描述 595是告诉的硅结构的CMOS器件,兼容低电压TTL电路,遵守JEDEC标准。

595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SCHcp的上升沿输入,在STcp 的上升沿进入的存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

CPD决定动态的能耗, PD=CPD×VCC×f1+∑(CL×VCC2×f0) F1=输入频率,CL=输出电容 f0=输出频率(MHz) Vcc=电源电压引脚说明符号引脚描述内部结构结合引脚说明就能很快理解 595的工作情况引脚功能表:真值表:74595的控制端说明:/SRCLR(10脚): 低点平时将移位寄存器的数据清零。

通常我将它接Vcc。

SCK(11脚):上升沿时数据寄存器的数据移位。

QA-->QB-->QC-->...-->QH;下降沿移位寄存器数据不变。

(脉冲宽度:5V时,大于几十纳秒就行了。

我通常都选微秒级)RCK(12脚):上升沿时移位寄存器的数据进入数据存储寄存器,下降沿时存储寄存器数据不变。

(通常我将RCK置为低电平,) 当移位结束后,在RCK端产生一个正脉冲(5V时,大于几十纳秒就行了。

HC595完整中文资料

74HC595芯片是一种串入并出的芯片,在电子显示屏制作当中有广泛的应用。

74HC595是8位串行输入/输出或者并行输出移位寄存器,具有高阻、关、断状态。

三态。

特点 8位串行输入 8位串行或并行输出存储状态寄存器,三种状态输出寄存器可以直接清除 100MHz的移位频率输出能力并行输出,总线驱动串行输出;标准中等规模集成电路应用串行到并行的数据转换 Remote contr ol holding register. 描述 595是告诉的硅结构的CMOS器件,兼容低电压TTL电路,遵守JEDEC标准。

595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SCHcp的上升沿输入,在STcp 的上升沿进入的存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

CPD决定动态的能耗, PD=CPD×VCC×f1+∑(CL×VCC2×f0) F1=输入频率,CL=输出电容 f0=输出频率(MHz) Vcc=电源电压引脚说明符号引脚描述内部结构结合引脚说明就能很快理解 595的工作情况引脚功能表:真值表:的驱动电流(25mA)比74595(35mA)的要小,14脚封装,体积也小一些。

2)74595的主要优点是具有数据存储寄存器,在移位的过程中,输出端的数据可以保持不变。

这在串行速度慢的场合很有用处,数码管没有闪烁感。

与164只有数据清零端相比,595还多有输出端时能/禁止控制端,可以使输出为高阻态。

3)595是串入并出带有锁存功能移位寄存器,它的使用方法很简单,在正常使用时SCLR为高电平, G为低电平。

从SER每输入一位数据,串行输595是串入并出带有锁存功能移位寄存器,它的使用方法很简单,如下面的真值表,在正常使用时SCLR为高电平, G为低电平。

74HC595中文资料

概述:74HC595 是一款漏极开路输出的CMOS 移位寄存器,输出端口为可控的三态输出端,亦能串行输出控制下一级级联芯片。

特点:高速移位时钟频率Fmax>25MHz标准串行(SPI)接口CMOS 串行输出,可用于多个设备的级联低功耗:TA =25℃时,Icc=4μA(MAX)图2 74HC595逻辑图真值表:输入管脚输出管脚SI SCK SCLR RCK OEX X X X H QA—QH 输出高阻X X X X L QA—QH 输出有效值X X L X X 移位寄存器清零L 上沿H X X 移位寄存器存储LH 上沿H X X 移位寄存器存储HX 下沿H X X 移位寄存器状态保持X X X 上沿X 输出存储器锁存移位寄存器中的状态值X X X 下沿X 输出存储器状态保持引脚功能表:管脚编号管脚名管脚定义功能1、2、3、4、5、6、7、15QA—QH 三态输出管脚8 GND 电源地9 SQH 串行数据输出管脚10 SCLR 移位寄存器清零端11 SCK 数据输入时钟线12 RCK 输出存储器锁存时钟线13 OE 输出使能14 SI 数据线15 VCC 电源端图1 74HC595引脚图Absolute Maximum Ratings绝对最大额定值参数数值Supply Voltage电源电压(VCC)−0.5 to +7.0VDC Input Voltage 直流输入电压(VIN)−1.5 to VCC +1.5V DC Output Voltage 直流输出电压(VOUT)−0.5 to VCC +0.5V Clamp Diode Current 钳位二极管电流(IIK, IOK)±20mADC Output Current直流输出电流,每个引脚(输出)±35mADC VCC or GND Current,per pin (ICC)±70mAStorage Temperature Range 储存温度范围(TSTG)−65℃ to +150℃Power Dissipation 功耗(PD)(Note 3)600mWS.O. Package only500mWLead Tem perature (TL) (Soldering 10 seconds)260℃Recommended Operating Conditions建议操作条件参数最小最大单位Supply Voltage电源电压(VCC)26v DC Input or Output Voltage(VIN, VOUT)输入输出电压0VCC V Operating Tem perature Range工作温度范围(TA)−40+85℃Input Rise or Fall Times 输入上升或下降时间(tr,tf) VCC = 2.0V-1000ns VCC = 4.5V-500ns VCC = 6.0V-400ns DC SPEC IFICATIONS直流电气规格Symbol 符号Parameter 参数Conditions 条件VCCTA=25℃TA=−40to85℃TA=−55to125℃UNIT单位典型Guaranteed Limits保证界限VIH Minimum HighLevel Input Voltage最大高电平输入电压-2.0V- 1.5 1.5 1.5V4.5V- 3.153.15 3.156.0V- 4.2 4.2 4.2VIL Maximum LOWLevel Input Voltage最大低电平输入电压-2.0V-0.50.50.5V4.5V- 1.351.35 1.356.0V- 1.8 1.8 1.8VOH Minimum HIGHLevel OutputVoltage最大高电平VIN=VIH orVIL|IOUT|≤20μA2.0V2.01.9 1.9 1.9V4.5V4.54.4 4.4 4.46.0V6.05.9 5.9 5.9输出电压Q'H VIN = VIH or VILV |IOUT| ≤4.0mA 4.5V 4.2 3.98 3.84 3.7|IOUT| ≤5.2mA 6.0V5.25.485.34 5.2QA thru QH VIN = VIH or VILV |IOUT| ≤6.0mA 4.5V 4.2 3.98 3.84 3.7IOUT| ≤ 7.8mA 6.0V5.75.485.34 5.2VOL Maximum LOWLevel OutputVoltage最大低电平输出电压VIN=VIH orVIL|IOUT| ≤20μA2.0V00.10.10.1V4.5V00.10.10.16.0V00.10.10.1Q'HVIN = VIH or VILV |IOUT| ≤ 4mA 4.5V 0.2 0.26 0.33 0.4|IOUT| ≤5.2mA 6.0V0.20.260.33 0.4QA thru QHVIN = VIH or VILV |IOUT| ≤6.0mA 4.5V 0.20.26 0.33 0.4|IOUT| ≤7.8mA 6.0V0.20.260.330.4IIN Maximum InputCurrent最大输入电流VIN=VCC orGND6.0V-±0.1±1.0±1.0μAIOZ Maximum 3-STATEOutput Leakage最大3态输出泄漏电流VOUT = VCC orGND G = VIH6.0V-±0.5±5.0±10μAICC MaximumQuiescent SupplyCurrent电源电流VIN=VCC orGND IOUT = 0μA6.0V-8.080160μA交流电气特性:Symbol 符号Parameter 参数Conditions条件典型GuaranteedLimitUNIT单位fMax最高工作频率-5030MHztPHL, tPLH Maximum Propagation Delay,最大传输延迟SCK to Q’ HCL = 45 pF1220nstPHL, tPLH Maximum Propagation Delay, 最大传输延迟RCK to QA thru QHCL = 45 pF1830nstPZH, tPZL Maximum Output Enable Tim e from G to QAthru QH 最大输出启用时间G to QA thru QHRL=1kΩCL=45pF1728nstPHZ, tPLZ Maximum Output Disable Tim e from G to QAthru QH最大输出禁用时间G to QA thru QHRL=1kΩCL=5pF1525nstS Minimum Setup Time from SER to SCK--20nstS Minimum Setup Time from SCLR to SCK--20ns tS Minimum Setup Time from SCK to RCK--40ns tH Minimum Hold Time from SER to SCK--0ns tW Minimum Pulse Width of SCK or RCK--16ns 交流电气特性:(续)Symbol 符号Parameter 参数Conditions条件VCCTA = 25℃TA =−40 to85℃TA =−55 to125℃UNIT单位典型Guaranteed Limits 保证界限fMax Maximum OperatingFrequency最高工作频率CL = 50 pF2.0V106 4.8 4.0MHz4.5V453024206.0V50352824tPHL, tPLH Maximum PropagationDelay from SCK to Q’ H最大传输延迟传播延迟CK to QCL = 50 pF 2.0V 58 210 265 315nsCL = 150 pF 2.0V83294367441CL = 50 pF 4.5V 14 42 53 63CL = 150 pF 4.5V17587488CL = 50 pF 6.0V 10 36 45 54CL = 150 pF 6.0V14506376tPHL, tPLH Maximum PropagationDelay from RCK to QA thruQHCK to QCK to Q最大传输延迟RCK to QA thru QHCKto QCK to QCL = 50 pF 2.0V 70 175 220 265nsCL = 150 pF 2.0V105245306368CL = 50 pF 4.5V 21 3544 53CL = 150 pF 4.5V28496174CL = 50 pF 6.0V 18 30 37 45CL = 150 pF 6.0V26425363tPHL, tPLH Maximum PropagationDelay from SCLR to Q’ H最大传输延迟to Q’ H-2.0V-175221261ns4.5V-3544526.0V-303744tPZH, tPZL Maximum Output Enablefrom G to QA thru QH最大输出启用RL=1kΩCL=50pF2.0V 75 175 220 265nsRL=1kΩCL=150pF2.0V100245306368CL= 50pF 4.5V 15 35 44 53CL = 150pF 4.5V20496174CL = 50 pF 6.0V13303745CL = 150 pF 6.0V17425363CPD Power DissipationCapacitance,G = VCC-90 ---pFG = GND150---OutputsEnabled (Note 6)功耗电容CIN Maximum InputCapacitance最大输入电容--5101010pFCOUT Maximum Output最大输出电容--15202020pF图3 74HC595 时序图图应用电路图:图4 87LPC76x与74HC595单片机构成的键盘显示电路图5。

74hc595默认电平

74hc595默认电平

74HC595是带有存储寄存器和三态输出的8位串行移位寄存器。

关于其默认电平,需要看具体的引脚:

/SRCLK(10脚,即Shift Register Clock,移位寄存器时钟):此引脚在低电平时会重置芯片(数据清零)。

在常规操作中,它通常默认接高电平。

/OE(13脚,即Output Enable,输出使能):当此引脚为高电平时,输出会被禁止。

在常规操作中,为了使595正常输出,它通常默认接低电平。

但如果需要让595在不受控制时输出高阻态(比如在某些初始化或复位阶段),可能需要用IO控制并加上拉电阻。

DS(Data Serial,串行数据输入):这是数据的来源口,但它本身并没有默认的电平状态,而是取决于你想输入的数据。

Q0-Q7:这些是8位并行输出引脚,它们的电平状态取决于存储在移位寄存器中的数据。

请注意,以上信息是基于74HC595的常见应用和操作。

在具体的项目或应用中,可能会有所不同。

因此,建议参考相关的数据手册或应用笔记以获取更详细和准确的信息。

74HC595中文资料_数据手册_参数

图 SERIAL数据 INPUT 14 11 10 12 13转移时钟重启 LATCH时钟 OUTPUT ENABLE转 移寄存器 LATCH 15 1 2 3 4五 6 7 9 Q A Q B Q C Q D Q E Q F Q G Q H SQ H一个 V CC = PIN 16 GND = PIN 8平行数据产出 SERIAL数据 OUTPUT引脚分配 13 14 15 16 9 10 11 12五 4 3 2 1 8 7 6锁定时钟输出启用一个 Q A V CC SQ H重启 SHIFT CLOCK Q E Q D Q C Q B GND Q H Q G Q F订购信息设备包 运输 ? 74HC595DR2G SOIC-16 (无铅) 2500磁带和卷轴 74HC595DTR2G TSSOP-16 * 2500磁带和卷轴 ?有关磁带和 卷轴规格的信息,包括零件方向和磁带尺寸,请参阅我们的74hc595磁带和卷轴包 74hc595装规格手册,BRD8011 / D. *该封装本身具有无铅功能.74HC595中文资料第3 页精选内容: 74HC595 3最大额定值符号参数值单元 V CC 直流电源电压(参考GND) - 0.5至+ 7.0 V V IN直流输入电压(参考GND) - 0.5至 V CC + 0.5 V V OUT直流输出电压(参考GND) - 0.5至V CC + 0.5 V 我 在直流输入 电流,每个引脚 ±20嘛 我 出去了直流输出电流,每个引脚 ±35嘛 我 CC DC电源 电流,V CC 和GND引脚 ±75嘛 P D.静止空气中的功率耗散, SOIC封装? TSSOP封 装? 500 450毫瓦 T STG储存温度 - 65至+ 150 _C T L引线温度,距壳体1毫米,持续10 秒 (SOIC或TSSOP封装) 260 _C74hc595强调超过最大额定值74hc595可能会损坏设 备.最大额定值是压力仅限评级.不建议在推荐操作条件之上进行功能操作.长时间暴 露在高于推荐操作条件的应力下可能会影响设备74hc595可靠性. ?降额 - SOIC封 装: - 从65到125°C时为7 MW / _C TSSOP封装: - 从65_到125_C的6.1 MW / _C有 关高频或高负载考虑事项,请参阅安森美半导体高速CMOS数据手册(DL129 / D) 的第2章.推荐工作条件符号参数敏马克斯单元 V CC直流电源电压(参考GND) 2.0 6 V V IN ,V OUT 直流输入电压,输出电压 (参考GND) 0 V CC V T A.工作温 度,所有封装类型 - 55 + 125 _C T R ,T F输入上升和下降时间 V CC = 2.0 V (图1) V CC = 4.5V V CC = 6.0 V 0 0 0 1000 500 400 NS此设备包含保护防止损坏的电路由于高静态电压或电领域.但是,必 须采取预防措施被采取以避免任何应用程序电压高于最大额定值这个高阻抗电路 的电压 - CUIT. 为了正确的操作,V IN 和 V OUT 应该受到限制 范围GND V(V IN 或V OUT )V V CC .未使用的输入必须始终为绑定到适当的逻辑电压 电平(例 如,GND或V CC ).未使用的输出必须保持打开状态.74HC595中文资料第1页精选 内容:74HC595中文资料第7页精选内容: 74HC595 7功能表 手术输入结果函数重启串行输入一个转移时钟闩时钟产量启用转移寄存器内容闩 寄存器内容串行产量 SQ H平行输出 Q A - Q H复位移位寄存器大号 X X L,H, ↓ 大→号SR大N号+ 1üü大S号R Gü→将S数R 据H 移ü入移换74h档c5寄95存位器寄H存D器↑保持L,不H变,H↓X大L号,DH→,S↓R LA,; SHR,N↓ 大号 ü ü ü ü转移移位寄存器内容锁定寄存器 H X L,H,↓ ↑大号 ü SR N →LR N ü SR N锁存寄存器保持不变不变 X X X L,H,↓大号 * ü * ü启用并行输 出 X X X X大号 * ** *启用强制输出为高阻抗状态 X X X X H * ** * ? SR =移位寄存器 内容 D =数据(L,H)逻辑电平 ↑=低到高 * =取决于复位和移位时钟输入 LR =锁 存寄存器内容 U =保持不变 ↓=从高到低 ** =取决于锁存时钟74hc595输入引脚说明 I1N4)PU7T4ShcA5(95串引行脚数据输入.该引脚上的数据被移入 8位串行移位寄存器.控制输入移 位时钟(引脚11)移位寄存器时钟输入.从低到高的过渡该输74hc595入会导致串行

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

8位串行输入/输出或者并行输出移位寄存器,具有高阻关断状态。

三态。

特点

8位串行输入

8位串行或并行输出

存储状态寄存器,三种状态

输出寄存器可以直接清除

100MHz的移位频率

输出能力

并行输出,总线驱动

串行输出;标准

中等规模集成电路

应用

串行到并行的数据转换

Remote control holding register.

描述

595是告诉的硅结构的CMOS器件,

兼容低电压TTL电路,遵守JEDEC标准。

595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SCHcp的上升沿输入,在STcp的上升沿进入的存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存

储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

参考数据

C P

D 决定动态的能耗,

P D =C PD ×V CC ×f 1+∑(C L ×V CC 2×f 0)

F 1=输入频率,C L =输出电容 f 0=输出频率(MHz ) Vcc=电源电压

符号

参数

条件

TYP

单位 HC

H C t

t PHL /t PLH 传输延时

SHcp 到Q7’ STcp 到Qn MR 到Q7’

C L =15pF Vcc=5V 16 17 14

21 20 19

Ns Ns Ns

f max

STcp 到SHcp 最大时钟速度

100 57

MHz

C L

输入电容 Notes 1

3.5 3.5

pF C PD Power dissipation c apacitance per p ackage.

Notes2 115 130

pF

引脚说明 符号 引脚 描述 Q0…Q7 15, 1, 7 并行数据输出 GND 8 地

Q7’ 9 串行数据输出 MR 10 主复位(低电平) SH CP

11

移位寄存器时钟输入

ST CP

12

存储寄存器时钟输入

OE

13 输出有效(低电平)

D S 14 串行数据输入 V CC 16

电源

功能表

输入

输出

功能

SH CP

ST C P O E MR D S Q

7’

Q

n

××L ↓×L N

C MR为低电平时紧紧影响移位寄存器

×↑L L ×L L空移位寄存器到输出寄存器

××H L ×L Z清空移位寄存器,并行输出为

高阻状态

↑×L H H Q

6’

N

C

逻辑高电平移入移位寄存器

状态0,包含所有的移位寄存

器状态移入,例如,以前的状

态6(内部Q6”)出现在串行输

出位。

×↑L H ×N

C Q

n’

移位寄存器的内容到达保持

寄存器并从并口输出

↑↑L H ×Q

6’Q

n’

移位寄存器内容移入,先前的

移位寄存器的内容到达保持

寄存器并输出。

H=高电平状态L=低电平状态↑=上升沿

↓=下降沿

Z=高阻

NC=无变化

×=无效

当MR为高电平,OE为低电平时,数据在SH CP上升沿进入移位寄存器,在ST CP上升沿输出到并行端口。