示波器设计

简易数字存储示波器设计

简易数字存储示波器设计摘要本文介绍了一种简易的数字存储示波器的设计。

示波器是一种广泛使用的电子测试仪器,用于显示电压随时间变化的波形。

数字存储示波器通过将波形样本存储在内存中,然后再进行显示,具有更高的分辨率和更多的功能。

本设计基于嵌入式系统,并通过一块液晶显示屏显示波形。

引言示波器是电子工程师和电子爱好者常用的测试设备之一。

然而,传统的示波器通常比较昂贵,且功能复杂。

为了满足一些简单的测试需求,我们设计了一款简易的数字存储示波器。

数字存储示波器具有存储和显示波形的功能,并且可以通过嵌入式系统实现。

本设计的核心部分是使用嵌入式开发板、模数转换器和液晶显示屏构建的简易数字存储示波器。

设计方案硬件设计嵌入式开发板本设计使用一块嵌入式开发板作为主要的处理器和控制单元。

开发板上应具备足够的计算能力和接口,以支持模数转换器、存储器和显示屏的连接。

模数转换器模数转换器(ADC)负责将输入的模拟信号转换为数字信号。

常见的ADC芯片有多种型号可选,选择合适的芯片以满足高精度和合适的采样率要求。

存储器用于存储模拟信号的样本数据。

根据要求,可以选择适当的存储器类型,如SRAM或SD卡。

显示屏显示屏用于显示存储器中的波形样本。

一块液晶显示屏是一个常见的选择,因为它可以提供高清晰度的图像和良好的视觉效果。

软件设计数据采集软件的第一步是通过ADC采集模拟信号,并将其转换为数字信号。

通过选择适当的采样率和转换精度,可以确保捕捉到所需的信号信息。

数据存储采集到的模拟信号样本将存储在嵌入式开发板的存储器中。

可以根据需要选择适当的存储器类型,以满足手头的需求。

从存储器中读取波形样本,然后将其显示在液晶显示屏上。

通过适当的算法和图形库,可以实现波形的平滑显示和良好的视觉效果。

操作流程本设计的操作流程如下:1.将待测试的电路连接到示波器的输入端口。

2.启动示波器,并设置合适的采样率和采样时间。

3.通过液晶显示屏查看波形样本。

4.根据需要对波形进行测量或分析。

示波器的信号处理算法与电路设计研究

示波器的信号处理算法与电路设计研究示波器是电子测量仪器中十分常见的一种,主要用于显示电信号的波形,在电子技术中有非常重要的作用。

示波器通过对电信号进行采样、量化、记录和显示等一系列处理,让人们能够更好地观测到电信号的变化。

在实际应用中,为了更好地适应电子技术的需求,示波器的信号处理算法和电路设计得到了不断的改善和优化。

一、示波器的基本原理及分类示波器最初是基于阳极射线管(CRT)的原理设计而来的,它通过在荧光屏上显示图像来表现出电信号的变化。

示波器可以根据所处理的信号类型、测量要求以及使用环境等因素,分为模拟示波器和数字示波器两种类型。

模拟示波器采用的是模拟电路,它通过对原始电信号的放大、滤波、延时等处理,将电信号转化为人们可以观察的波形图。

数字示波器则采用了数字处理技术,将电信号进行采样、量化、数字化等处理,通过数字显示芯片将波形图显示在屏幕上。

与模拟示波器相比,数字示波器具有更高的准确性、更高的分辨率以及更多的功能。

二、示波器的信号处理算法与技术1. 信号采样与量化技术示波器最基本的功能就是采集电信号,将其转化为数字信号进行处理。

信号的采样和量化是数字示波器的基础,这也直接影响到示波器的准确性和分辨率。

采样率是指所采集的每秒钟的采样数,它决定了示波器的最高频率。

量化技术则是将连续的电信号转化为离散的数字信号,量化位数越高,则示波器的准确度也越高。

现今的示波器一般采用12位或14位的ADC进行量化,通过数字信号处理技术得到分辨率更高的显示效果。

2. FFT分析技术快速傅里叶变换(FFT)是一种常用的频域分析方法,在示波器中也得到了广泛的应用。

FFT可以将时间域的波形图转化为频域的谱图,通过分析谱图来了解电信号的频域特征。

FFT分析技术可以有效地识别出杂散干扰、噪音等问题,并对电路进行改进和优化。

3. 自适应滤波技术示波器中常用的滤波器可以消除一些随机噪声,但是对于信号的变化速度过快的情况,传统的滤波器就显得无能为力。

简易数字存储示波器设计

简易数字存储示波器设计数字存储示波器是一款用于测量电信号的仪器,它可以将收集到的信号进行数字化处理,并将结果显示在屏幕上。

本文将介绍一个简易的数字存储示波器的设计。

1. 设计目标设计一个简易的数字存储示波器,使其能够接收并显示电信号的波形,并具备一定的存储功能。

该示波器需要具备以下功能:能够调节触发电平、可以调节扫描速度、能够通过按钮进行保存和回放存储的波形。

设计需要保证简易、易于操作、能够满足基本的测量需求。

2. 硬件设计(1)电路板设计:设计一个电路板用于信号的采集和存储。

该电路板包括模拟前端电路用于信号的采集,数字转换电路将模拟信号转换为数字信号,以及存储器用于存储采集到的数据。

(2)显示屏和按键:电路板上需要配备一个液晶显示屏,用于显示采集到的波形图像。

同时,设计按键用于调节触发电平、扫描速度以及保存和回放。

3. 软件设计(1)数据采集:通过模拟前端电路采集信号,并使用数字转换电路将模拟信号转换为数字信号。

采用适当的采样率,将数据进行采样,并存储到存储器中。

(2)数据显示:通过显示屏将存储器中的数据显示为波形图像。

根据采样率和扫描速度,将存储器中的数字信号转换为波形,并在屏幕上显示。

(3)触发控制:通过按键调节触发电平,设置触发条件,使得波形显示能够达到最佳效果。

设计合适的触发电路用于触发信号。

(4)数据存储和回放:设计按键和存储器用于保存和回放采集到的波形。

按下保存键后,将当前的波形数据保存到存储器中,按下回放键后,将存储器中的波形数据重新显示在屏幕上。

4. 使用方法使用该简易数字存储示波器,首先将信号源连接到示波器的输入端,然后通过按键进行触发电平的调节和扫描速度的设置。

在适当的触发条件下,示波器将开始采集并显示信号的波形。

当波形满足要求后,可以通过按键将波形数据保存到存储器中。

保存后的波形可以通过按键进行回放,重新显示在屏幕上。

5. 总结通过以上的设计和实现,可以得到一个简易的数字存储示波器。

STM32的数字示波器设计

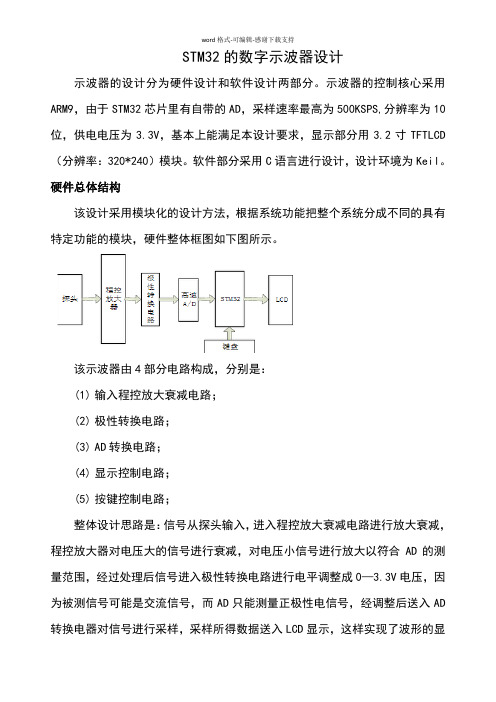

STM32的数字示波器设计示波器的设计分为硬件设计和软件设计两部分。

示波器的控制核心采用ARM9,由于STM32芯片里有自带的AD,采样速率最高为500KSPS,分辨率为10位,供电电压为3.3V,基本上能满足本设计要求,显示部分用3.2寸TFTLCD (分辨率:320*240)模块。

软件部分采用C语言进行设计,设计环境为Keil。

硬件总体结构该设计采用模块化的设计方法,根据系统功能把整个系统分成不同的具有特定功能的模块,硬件整体框图如下图所示。

该示波器由4部分电路构成,分别是:(1)输入程控放大衰减电路;(2)极性转换电路;(3)AD转换电路;(4)显示控制电路;(5)按键控制电路;整体设计思路是:信号从探头输入,进入程控放大衰减电路进行放大衰减,程控放大器对电压大的信号进行衰减,对电压小信号进行放大以符合AD的测量范围,经过处理后信号进入极性转换电路进行电平调整成0—3.3V电压,因为被测信号可能是交流信号,而AD只能测量正极性电信号,经调整后送入AD 转换电器对信号进行采样,采样所得数据送入LCD显示,这样实现了波形的显示。

按键控制可以通过不同的按键来控制波形的放大和缩小,同时也可以改变采样间隔,以测量更大频率范围的信号。

STM32处理器介绍STM32系列基于专为要求高性能、低成本、低功耗的嵌入式应用专门设计的ARM Cortex-M3内核。

按性能分成两个不同的系列:STM32F103“增强型”系列和STM32F101“基本型”系列。

增强型系列时钟频率达到72MHz,是同类产品中性能最高的产品;基本型时钟频率为36MHz,以16位产品的价格得到比16位产品大幅提升的性能,是16位产品用户的最佳选择。

两个系列都内置32K 到128K的闪存,不同的是SRAM的最大容量和外设接口的组合。

时钟频率72MHz 时,从闪存执行代码,STM32功耗36mA,是32位市场上功耗最低的产品。

本设计所用的STM32F103VCT6集成的片上功能如下:(1) 1.2v内核供电,1.8V/2.5V/3.3/V存储器供电,3.3V外部I/O供电(2)外部存储控制器(3)(3) LCD 控制器(4) 4通道DNA并有外部请求引脚(5) 3通道UART(6) 2通道SPI(7) 1通道IIC总线接口1通道IIS总线接口(8) AC’97编解码器接口(9) 兼容SD主接口协议1.0版和MMC卡协议2.11兼容版(10) 2通道USB主机1通道USB设备(11) 4通道PWM定时器和1通道内部定时器/看门狗定时器(12) 8通道10位ADC和触摸屏接口(13) 80个通用I/O和24通道外部中断源LCD显示介绍LCD液晶显示器是Liquid Crystal Display的简称,LCD的构造是在两片平行的玻璃当中放置液态晶体,两片玻璃中间有许多垂直和水平的细小电线,通过通电与否来控制杆状水晶分子改变方向,将光线折射出来产生画面。

示波器功能扩展电路设计实验报告

示波器功能扩展电路设计实验报告实验报告:示波器功能扩展电路设计一、实验目的1.学习和掌握示波器的工作原理及使用方法。

2.通过设计扩展电路,探究示波器的功能与应用。

3.培养实验操作能力和创新思维。

二、实验原理示波器是一种常用的电子测量仪器,主要用于观察和测量交流电压随时间的变化情况。

其基本原理是利用高速电子枪将电子打在荧光屏上,产生随时间变化的电信号图形。

通过设计扩展电路,可以进一步拓展示波器的功能和应用范围。

三、实验步骤1.准备实验材料和工具,包括示波器、信号发生器、电阻、电容、电感等电子元件。

2.设计扩展电路,根据实验需求选择合适的电子元件,搭建电路。

3.连接信号发生器,为示波器提供输入信号。

4.开启示波器,观察并记录实验结果。

5.分析实验数据,评估扩展电路的功能和性能。

四、实验结果与分析1.设计了一个频率计扩展电路,将示波器的频率测量范围从50MHz扩展至200MHz。

通过该电路,可以实现对高频信号的精确测量。

2.设计了一个李萨育图形测量电路,利用两个信号发生器产生正弦波信号,通过示波器观察其合成信号的相位差。

实验结果表明,该电路可以实现对相位差的精确测量。

3.设计了一个数字信号发生器扩展电路,将示波器与计算机连接,通过计算机软件控制示波器产生不同幅度、频率和相位的数字信号。

该电路可以用于测试数字信号的特性和性能。

4.对实验结果进行分析,评估扩展电路的功能和性能。

以频率计扩展电路为例,通过对比扩展前后的测量结果,发现扩展后的测量精度得到了显著提高。

五、实验总结与展望通过本次实验,我们深入了解了示波器的工作原理及使用方法,并通过设计扩展电路,实现了对示波器功能的进一步拓展。

实验结果表明,通过合理设计电路和选择电子元件,可以显著提高示波器的测量精度和应用范围。

展望未来,示波器将在更多领域得到应用和发展。

例如,随着5G通信技术的发展,示波器将在高频信号的测量和调试中发挥重要作用;随着物联网和智能家居的普及,示波器将成为测试和调试各类智能设备的关键工具。

数字示波器毕业设计

数字示波器毕业设计数字示波器毕业设计在现代电子技术领域中,示波器是一种常用的测试仪器,用于观察和分析电信号的波形。

随着科技的不断进步,传统的模拟示波器已经逐渐被数字示波器所取代。

数字示波器具有更高的精度、更大的带宽和更多的功能,成为电子工程师日常工作中不可或缺的工具。

本文将探讨数字示波器的毕业设计,介绍其原理、设计思路和实现方法。

一、数字示波器的原理数字示波器的原理基于模拟信号的采样和数字信号的处理。

首先,模拟信号通过采样器进行采样,将连续的模拟信号转换为离散的数字信号。

然后,这些离散的数据通过数字信号处理器进行处理,包括存储、显示和分析。

最后,通过显示器将处理后的数字信号转换为可视化的波形图。

二、数字示波器的设计思路在进行数字示波器的毕业设计时,需要考虑以下几个方面的设计思路:1. 采样率和带宽:示波器的采样率和带宽是其性能的重要指标。

采样率决定了示波器对信号的采样精度,而带宽则决定了示波器能够显示的信号频率范围。

在设计过程中,需要根据实际需求确定采样率和带宽,并选择合适的模数转换器和数字信号处理器。

2. 存储和显示:示波器需要能够对采样的数据进行存储和显示。

存储器的容量和速度决定了示波器可以存储和处理的数据量,而显示器的分辨率和刷新率则决定了示波器显示波形的清晰度和流畅度。

在设计过程中,需要选择合适的存储器和显示器,并考虑存储和显示的算法和接口设计。

3. 波形分析:数字示波器不仅可以显示波形,还可以进行波形分析。

波形分析功能包括频谱分析、峰值检测、触发等,可以帮助工程师更好地理解和分析信号。

在设计过程中,需要选择合适的算法和接口,实现波形分析功能。

三、数字示波器的实现方法数字示波器的实现方法主要包括硬件设计和软件设计两个方面。

1. 硬件设计:硬件设计包括模数转换器、存储器、显示器、触发电路等的选型和接口设计。

在选型过程中,需要考虑采样率、带宽、存储容量、显示分辨率等指标,并选择合适的器件。

接口设计需要考虑数据传输的速度和稳定性,确保数据的准确性和可靠性。

一款简易示波器的设计方案

款简易示波器的设计方案随着电子通信以及教学事业的发展,示波器的应用越来越广泛,它在教学中所起到的作用越来越重要,示波器可以测量信号的幅度,频率以及波形等等,但是高精度的示波器非常昂贵,对于非盈利事业的教学组织来说无疑不合适,所以提出了一种以单片机为控制核心的简易示波器设计方案。

它由前向控制部分,数据采集和存储部分, 51 单片机控制部分以及按键和 MS12864R 显示部分组成。

1 简易数字示波器的工作原理以及总体框架本设计硬件电路部分由单片机控制系统电路,前向输入调理电路,模数转换和存储电路,以及按键显示电路组成。

其工作的基本思路就是以单片机为控制核心,让 AD 芯片完成数据的离散化,采集数据经过缓冲暂存于存储器里面,当波形显示时,单片机从存储器的读使能端读取采集数据存于数组中,然后进行相应的数据处理并把所存取得数据按一定的顺序打在液晶显示器相应的位置上,从而再现波形信号 ;其中输入调理电路由阻抗变换电路,信号抬升电路以及频率测量电路构成,阻抗变换电路是为了提高输入阻抗,信号抬升是为了使信号的幅度满足 AD 芯片的输入幅度要求,频率测量电路主要是测量周期性信号的频率。

总体设计框图如图 1 所示。

2 硬件设计 2.1 前端信号的处理本模块具有两信号位置的变换主要由阻抗变换电路,信号抬升电路构成, 阻抗变换采用 ua741 构建的阻随放大电路, 信 用 ua741 构成的加法电路, 信号位置的处理主要是对被测输 入信号在幅度与偏移方面进行线性处理,使信号在垂直方向处于 A/D 转换器的输入范围内。

波形变换电路是用来测量 输入信号的频率,但是单片机属于数字器件,为此,我们需 随着写入数据或者读取数据而使地址指针进行递增或者递 减来实现寻址,两者中间接了一个缓冲器,这样可以起到数 据缓冲作用,在MCU 与AD 之间接入FIFO 的作用是起到数 据缓冲的作用,因为 AD 的时钟高于 MCU 的工作频率,所 以让 AD 和 FIFO 同步工作来存储 AD 转换的输出数据,实 验中 AD 与 FIFO 的时钟同步,来自于 ALE 引脚,为了使时 钟更加稳定, 可以让 ALE 信号先经过与门再送往采集存储模 块;FIFO 有3个标志位引脚,FF 满标志,HF 半满标志以及 EF 空标志,本设计只利用了 FF 满标志,当 FIFO 存满时通 知单片机来读取数据,这是单片机使 FIFO 的写使能禁止, 大功能, 是输入信号位置的变换 ;二是信号波形的变换 号抬升电路采 要对输入信号进行波形变换以及脉冲整形;硬件电路设计如 图2 所示。

简易示波器课程设计报告

课程设计报告课程名称综合电子设计题目简易数字示波器指导教师起止日期系别自动化专业自动控制学生姓名班级/学号成绩摘要本系统由CPLD,单片机控制模块,键盘,LED,幅度控制模块,低通滤波模块组成,采用当前主流DDS 技术完成,能产生从1HZ-260KHZ 正弦波,方波,三角波以及这三种同频率波的线性组合,失真度限制在6%之内。

一、功能介绍1. 具有产生正弦波、方波、三角波三种周期性波形的性能。

2. 用键盘输入编辑生成上述三种波形(同周期)的线性组合波形。

3. 输出波形频率范围为1Hz~200kHz(非正弦波频率按10 次谐波计算;重复频率可调,频率步进间隔1Hz。

)4. 输出波形幅度范围0~5V(峰-峰值),可按步进为0.1V(峰-峰值)。

5. 具有显示输出波形种类、重复频率(周期)和幅度的功能。

6. 增加稳幅输出功能,当负载变化时,输出电压幅度变化不大于±3%(负载变化范围:100Ω~∞)。

二、方案论证与比较常见信号源的制作方法有:方案一:采用锁相式频率合成。

将一个高稳定度和高精确度的标准频率经过加减乘除的运算产生同样稳定度的大量离散频率技术,它在一定程度上既要频率稳定精确,又要频率在很大范围内可变的矛盾。

但频率受VCO 可变频率范围的影响,高低频率比不可能做的很高,而且只能产生方波和正弦波。

方案二:采用模拟奋力元件或单片压控函数发生器MAX0832,可产生正弦波,方波,三角波,通过调整外部元件可改变输出频率,但采用模拟器件由于元件分散性太大,即使使用单片函数发生器,参数也与外部元件有关,外接的电阻电容对参数影响很大,不能实现波形运算输出等智能化的功能。

方案三:采用DDFS,即直接数字频率合成技术,以Nyquist 时域采样原理为基础,在时域中进行频率合成,它可以快速转换频率,频率,相位,幅度都可以实现程控,便于单片机控制,所以,本系统采用此方案。

三、系统设计系统总体设计方框图:系统设计方案:1、实现A/D芯片的模数转换功能,通过keil的watch窗口观察ADC0读取的数据的变化。

基于单片机的简易示波器设计

基于单片机的简易示波器设计一、系统结构和工作原理1.1 系统结构该系统设计方案是以AVR单片机为核心,再加上前端信号调理电路、键盘控制、LCD 显示构成的简易示波器,其系统结构框图如图l所示。

1.2 工作原理系统的主控芯片是AVR系列单片机ATmega16,单片机内部自带一个10 bits精度的逐次逼近型模数转换器,内建采样/保持电路。

ADC的时钟是可编程的,触发源选择为定时器/计数器0溢出;ATmega16的定时器的时钟源也是可编程的,这样就可以通过控制定时器/计数器0溢出中断频率来控制ADC的采样频率。

二、硬件设计2.1 信号调理电路信号调理电路要完成的功能是:程控放大,叠加直流分量。

程控放大的作用是:当输入信号的幅度很小的时候就需要对输入信号进行放大,使得被测信号可以在LCD上尽可能清楚的显示出来。

叠加直流分量的作用是:ATmega16自带的A/D是单电源的,没办法输入负压而待测信号又往往有负压。

这时候就需要一个可以把负压抬高到0电平以上的电路,如图2。

R1、R2分别由一个模拟开关CD4051来连接不同的电阻实现程控放大功能;可调电阻R9用来设置信号调理电路加入的直流分量的大小;放大后的信号和直流分量最后由U3模拟加法器叠加后输出。

三、软件设计系统软件设计主要分为主程序模块、触发模块、显示模块和A/D转换采样及频率控制模块。

图2 信号调理电路 3.1 主程序模块系统在一次采样未完成之前,只查询键盘。

按下按键进行相应操作,如无键按下则继续查询键盘,直到采样完成为止。

采样完成后触发数据,只从数据里取出符合显示要求的数据并将波形显示在LCD 上,进入下一次采样,如此循环。

图3为系统主程序工作流程。

图3 简易示波器系统程序流程图3.2 触发模块采用硬件触发功能会增大系统硬件电路的复杂度,因此采用软件实现方式。

一个周期的正弦波同一电压值对应两个不同的波形位置(除去最大值与最小值)。

先找一个比触发电平小的电压,在此基础上再找与触发电平相同或更大的电压就可以判断出大于或等于触发电平的Y NYN开 始系统初始化开机动画键盘扫描及功能采样完毕?数字触发清波形显示区数据运算及显 示波形循环幅度等于 最大值?程控放大器放大倍数下降一级数据就是上升沿的触发点。

基于labview的示波器设计

毕业设计(论文)题目:基于labview的示波器设计摘要设计:基于labview的示波器设计。

其主要介绍虚拟仪器的概念、组成和虚拟仪器开发软件LabVIEW,以及基于LabVIEW 的数据采集系统。

同时具体LabVIEW软件实现虚拟数字示波器。

比较了虚拟仪器和硬件仪器的各自特点。

分析了虚拟仪器的先进性,介绍了LABVIEW系列软件的应用方法和最新功能【关键词】示波器、虚拟仪器、函数模快、前面板、程序框图、接口板、控制件、数据采集。

AbstractDesign: Based on labview oscilloscope designIts main introduction hypothesized instrument concept, composition andhypothesized instrument development software labview as well as basedon Labview data acquisition system Simultaneously specificallyintroduced how uses the data acquisition card and the Labview softwarerealization hypothesized digital oscilloscope Compared withhypothesized instrument and hardware instrument respectivecharacteristic Introduced the Labview series software application method and thenewest function.[ Key word ] the oscilloscope, the hypothesized instrument, the letterdigital-analog are quick, the data acquisition.一、绪论1、虚拟仪器概况虚拟仪器(virtual instrumention)是基于计算机的仪器。

基于ESP32的多功能示波器设计

基于ESP32的多功能示波器设计

概述

本文介绍了一种基于ESP32的多功能示波器设计。

该示波器可以测量电压和电流,支持串口通信,通过WiFi模块实现远程访问

和控制。

硬件设计

该示波器的主要硬件包括ESP32开发板、电压和电流传感器、LCD显示屏、WiFi模块和按键。

其中,ESP32开发板是实现微控

制器功能的主要芯片,电压和电流传感器用于测量电路参数,LCD

显示屏用于显示测量结果,WiFi模块支持远程访问和控制,按键

与开发板连接,用于控制和调整参数。

软件设计

该示波器的软件设计主要包括测量、显示、通信和控制等功能。

其中,测量部分通过电压和电流传感器获取电路参数,并对数据进

行采样、处理和存储;显示部分通过LCD显示屏实时展示测量结果;通信部分通过串口和WiFi模块实现与其他设备的数据传输和

远程访问;控制部分通过按键和WiFi模块实现参数设置和控制命令发送。

结论

基于ESP32的多功能示波器设计实现了电路参数的测量和实时显示,同时支持串口通信和远程访问和控制。

该设计具有成本低、便于调试和扩展的优点,可以为电子工程师和爱好者提供一种有用的工具。

便携式示波器设计毕业设计

便携式示波器设计毕业设计便携式示波器设计毕业设计在现代科技的快速发展下,电子技术已经成为了我们日常生活中不可或缺的一部分。

而作为电子技术领域中的重要工具之一,示波器的作用也日益凸显。

然而,传统的示波器体积庞大、重量沉重,限制了其在某些场合的使用。

因此,设计一款便携式示波器成为了一个有意义的毕业设计课题。

便携式示波器的设计需要考虑多个方面的因素,包括体积、重量、功耗、性能等。

首先,为了实现便携性,设计师需要将传统示波器的体积和重量进行大幅度的减小。

这需要采用小型化的元器件和紧凑的电路板设计,以确保整个示波器可以轻松携带和操作。

同时,为了降低功耗,设计师还需要选择低功耗的元器件,并合理设计电路结构,以减少能量的损耗。

其次,便携式示波器的性能也是设计过程中需要关注的重要方面。

一方面,示波器需要具备足够的带宽和采样率,以满足各种电子设备的测试需求。

另一方面,示波器的灵敏度和精确度也需要得到保证,以确保测试结果的准确性。

为了实现这些要求,设计师需要在保证性能的前提下,尽可能地减小电路的复杂度和功耗。

在便携式示波器的设计过程中,还需要考虑到用户的使用体验。

一方面,设计师需要关注示波器的人机交互界面,以确保用户可以方便地操作和控制示波器。

另一方面,设计师还需要考虑示波器的数据存储和传输功能,以便用户可以方便地保存和分享测试数据。

为了实现这些功能,设计师需要合理选择和配置示波器的硬件和软件系统。

除了上述的技术要求,设计师在便携式示波器的设计过程中还需要考虑到成本和可行性等因素。

毕竟,作为一项毕业设计,设计师的资源和时间都是有限的。

因此,设计师需要在满足基本要求的前提下,尽可能地降低成本和提高可行性。

这需要设计师具备一定的经济学和工程学知识,以合理地选择和配置元器件,并进行成本效益分析。

综上所述,便携式示波器的设计是一项具有挑战性和意义的毕业设计课题。

设计师需要在体积、重量、功耗、性能、用户体验、成本和可行性等多个方面进行综合考虑,以实现一款既小巧便携又功能强大的示波器。

基于Arduino的数字示波器设计

基于Arduino的数字示波器设计

Arduino是一款开源的硬件和软件平台,非常适合初学者学习

电子和编程。

基于Arduino开发一款数字示波器,需要以下材料:

1. Arduino Uno板

2. OLED屏幕

3. Potentiometer电位器

4. 电容和电阻器材

5. 杜邦线

示波器主要有两个功能,一个是采集信号,一个是显示波形。

采集信号需要一个输入电路,示波器输入电路通常采用阻容耦合,

保证输入信号不改变原有波形,同时能够减小干扰信号。

本设计采

用一个独立的输入电路,可以读取0到5V范围内的电压信号。

均压

电路可通过电容放大器解决。

将OLED屏幕与Arduino Uno板相连,使用OLED库显示波形。

调节Potentiometer电位器,使波形在屏幕上移动。

最后,将Arduino编程实现示波器的基本功能,如采集、显示、触发亚分等。

具体代码实现可参考相关示例。

总的来说,开发基于Arduino的数字示波器并不难,特别是对

于初学者来说。

根据具体需求,可以适当增加模块,定制更强大的

功能。

数字示波器完整设计过程!

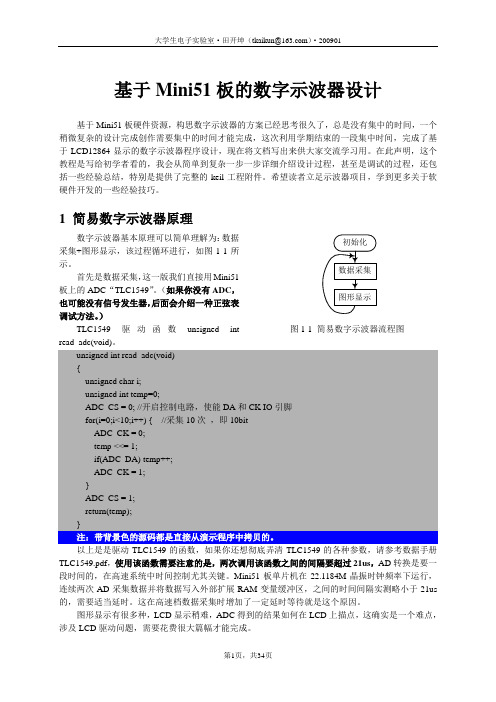

基于Mini51板的数字示波器设计基于Mini51板硬件资源,构思数字示波器的方案已经思考很久了,总是没有集中的时间,一个稍微复杂的设计完成创作需要集中的时间才能完成,这次利用学期结束的一段集中时间,完成了基于LCD12864显示的数字示波器程序设计,现在将文档写出来供大家交流学习用。

在此声明,这个教程是写给初学者看的,我会从简单到复杂一步一步详细介绍设计过程,甚至是调试的过程,还包括一些经验总结,特别是提供了完整的keil工程附件。

希望读者立足示波器项目,学到更多关于软硬件开发的一些经验技巧。

1 简易数字示波器原理数字示波器基本原理可以简单理解为:数据采集+图形显示,该过程循环进行,如图1-1所示。

首先是数据采集,这一版我们直接用Mini51板上的ADC“TLC1549”。

(如果你没有ADC,也可能没有信号发生器,后面会介绍一种正弦表调试方法。

)TLC1549驱动函数unsigned int read_adc(void)。

图1-1 简易数字示波器流程图unsigned int read_adc(void){unsigned char i;unsigned int temp=0;ADC_CS = 0; //开启控制电路,使能DA和CK IO引脚for(i=0;i<10;i++) { //采集10次,即10bitADC_CK = 0;temp <<= 1;if(ADC_DA) temp++;ADC_CK = 1;}ADC_CS = 1;return(temp);}以上是是驱动TLC1549的函数,如果你还想彻底弄清TLC1549的各种参数,请参考数据手册TLC1549.pdf,使用该函数需要注意的是,两次调用该函数之间的间隔要超过21us,AD转换是要一段时间的,在高速系统中时间控制尤其关键。

Mini51板单片机在22.1184M晶振时钟频率下运行,连续两次AD采集数据并将数据写入外部扩展RAM变量缓冲区,之间的时间间隔实测略小于21us 的,需要适当延时。

基于STM32的多功能示波器设计

基于STM32的多功能示波器设计高级组:示波器论文——李振辉队一、摘要示波器是一种十分常用电子测量仪器,它将电信号转换成图像信息或者数值输出,方便人们对各种电现象的研究。

但是传统示波器具有不方便携带,功能不易拓展等缺点。

本设计一种多功能存储示波器,该示波器采用STM32处理器,实现了采样、处理、存储等功能;采用双电源供电;可对波形进行存储和再现。

而且其大小仅为与成人手掌大小一般,充分体现了此多功能示波器的便携性,满足了现场测试的要求,同时降低了成本。

二、设计要求1.基本要求1)可以单片机显示屏上实时地显示当前电压值,并且有波形显示以及坐标方格显示。

2)示波器最高测量电压不低于10V,精度不低于20mv。

3)具有改变采样频率以及幅度变换功能,即改变“X增益”和“Y增益”,并且有图像上下移动的功能。

4)具有输入电压过高的报警功能,电压达到设定值提醒功能,电压动荡提醒功能等。

5)支持图像保存功能以及图像回调功能。

2.拓展要求1)具有多通道信号输入功能,即可以同时测量多路信号。

2)利用十字交叉线精确标志处出波形上点的横纵坐标,实现横纵坐标的对应显示。

3)人机交互功能,上位机通讯功能,以及其他创新功能。

三、数字示波器的性能参数设计我们都知道数字示波器,所谓数字示波器其实就是通过采样定理对模拟的连续信号进行数据采集,再经A/D转换器转换成数字信号,使用软件编程等一系列的技术制造出来的高性能示波器。

数字存储示波器的指标很多,包括采样率、带宽、灵敏度、通道数、存储容量、扫描时间和最大输入电压等。

其中关键的技术指标主要有采样率、垂直灵敏度(分辨率)、水平扫描速度(分辨率)。

这几项指标直接与所选A/D、FIFO和高速运放器件的性能,以及电路设计有关。

下面根据所选器件的性能参数,合理地分析和确定示波器的采样率和分辨率。

1、采样率与水平扫描分辨率采样率主要取决于A/D转换器的转换速率,由于最高测量电压不低于10V,精度不低于20mv,故在此使用STM单片机内置的12位的A/D转换器即可。

基于LABVIEW的虚拟示波器的设计

基于LABVIEW的虚拟示波器的设计虚拟示波器是一种基于计算机软件实现的示波器,可以通过图形界面显示电压随时间变化的波形。

基于LABVIEW的虚拟示波器,可以利用LABVIEW提供的丰富的图形化编程工具和硬件接口,实现更多功能和灵活性。

设计虚拟示波器的关键是收集、处理和显示波形数据。

基于LABVIEW的虚拟示波器可以通过各种数据采集设备(例如模拟输入IO卡或者USB采集设备)连接到电路中并接收电压信号。

这些设备通常提供了多个输入通道,可以同时采集多个信号。

LABVIEW的硬件接口模块可以帮助用户方便地与这些设备进行交互。

数据采集完成后,虚拟示波器需要将采集到的数据进行处理和显示。

在LABVIEW中,可以使用信号处理的工具包,对采集的数据进行滤波、傅里叶变换等处理,以便更好地展示电压信号的特征。

通过使用LABVIEW的图形显示工具,可以将处理后的数据以波形的形式进行直观的观察。

虚拟示波器不仅仅可以显示波形数据,还可以提供其他功能,例如自动测量、功率谱分析、频率响应等。

通过LabVIEW的功能模块,可以方便地实现这些功能。

例如,可以使用自动测量模块来自动计算波形的最大值、最小值、平均值等指标。

也可以使用频谱分析模块对波形进行频率分析,显示不同频率的成分。

除了显示波形数据和提供其他功能,虚拟示波器还可以提供一些调试和分析工具,以帮助用户更好地理解电路中的问题。

通过在LABVIEW界面中增加控件,用户可以实现诸如光标测量、自动触发等功能。

还可以通过在界面中增加控制按钮,实现波形的暂停、回放等功能,以便用户更好地分析和调试电路。

虚拟示波器的设计需要考虑用户的需求和易用性。

LABVIEW提供了丰富的图形化编程工具和灵活的界面设计功能,可以根据用户的需求进行定制。

同时,LABVIEW还支持导出数据到其他格式,如Excel或者MATLAB,方便用户进行深入的数据分析和处理。

在设计虚拟示波器时,还需考虑性能和稳定性问题。

简易数字示波器设计报告

简易数字示波器设计报告学校:苏州大学学院:电子信息学院班级:电子与通信工程组员:王婷杨静芝范静第一章设计内容与要求1. 1 设计内容:设计并制作一台具有实时采样方式和等效采样方式的数字示波器,示意图如图1所示。

图1 数字示波器示意图1. 2 基本设计要求:(1)被测周期信号的频率范围为10Hz~10MHz,仪器输入阻抗为1M ,显示屏的刻度为8 div×10div,垂直分辨率为8bits,水平显示分辨率≥20点/ div。

(2)垂直灵敏度要求含1V/div、0.1V/div两档。

电压测量误差≤5%。

(3)实时采样速率≤1MSa/s,等效采样速率≥200MSa/s;扫描速度要求含20ms/div、2μs /div、100 ns/div三档,波形周期测量误差≤5%。

(4)仪器的触发电路采用内触发方式,要求上升沿触发,触发电平可调。

(5)被测信号的显示波形应无明显失真。

1. 3 扩展要求:(1)提高仪器垂直灵敏度,要求增加2mV/div档,其电压测量误差≤5%,输入短路时的输出噪声峰-峰值小于2mV。

(2)增加单次触发功能,即按动一次“单次触发”键,仪器能对满足触发条件的信号进行一次采集与存储(被测信号的频率范围限定为10Hz~50kHz)。

第二章系统的总体设计2. 1 总体框图:2. 2 硬件系统设计:2.2.1输入信号调理电路:图2输入信号调理电路该电路中涉及到的芯片有:(1)AD603:在很多信号采集系统中,信号变化的幅度都比较大,那么放大以后的信号幅值有可能超过A/D转换的量程,所以必须根据信号的变化相应调整放大器的增益。

在自动化程度要求较高的系统中,希望能够在程序中用软件控制放大器的增益,或者放大器本身能自动将增益调整到适当的范围。

AD603正是这样一种具有程控增益调整功能的芯片。

它是美国ADI公司的专利产品,是一个低噪、90MHz带宽增益可调的集成运放,如增益用分贝表示,则增益与控制电压成线性关系,压摆率为275V/μs。

示波器触发电路设计分析

示波器触发电路设计分析一、设计原理示波器触发电路的作用以及实现原理示波器触发电路是示波器电路的核心部分,用于稳定光标位置,保持示波器稳定输出,减小示波器输出波形的抖动和浮动。

其设计原理是基于信号特征的匹配和比较,通过适当的阈值控制确定光标位置,实现精确的波形稳定输出。

二、设计要求示波器触发电路设计所需要考虑的各项要求和指标示波器触发电路设计需要考虑的重要要求包括:稳定性、灵敏性、速度、抗噪性、线性度、抗干扰性等。

同时,还需要根据不同应用场景的要求,针对性地考虑电源噪声、信号的频率范围、时间分辨率、脉冲响应等因素。

三、设计方法示波器触发电路设计的具体方法示波器触发电路设计的具体方法包括:根据信号特征选择成本适宜、性能稳定的比较器和锁相环等基础元器件,通过等效电路分析及仿真技术确定电路参数,完成电路拓扑结构的设计,进而加以测试实验,通过不断的调整和优化,最终完成优秀示波器触发电路的设计。

四、设计优化示波器触发电路设计过程中的优化方法示波器触发电路设计过程中的优化方法主要包括仿真参数分析、电路实验验证及深度学习算法等。

可以通过研究电路非线性特性的变化规律,增加新型芯片元器件、改变电路布线方式等进行优化。

五、应用场景示波器触发电路在实际应用中需要考虑的应用场景示波器触发电路在实际应用中的应用场景包括:医疗器械、航空航天、汽车电子等各个领域。

不同应用场景对示波器触发电路的性能和稳定性要求不同,需要根据实际需求进行综合考虑分析。

案例一: Philips公司生产的OFW65C示波器触发电路设计该示波器触发电路设计原理基于锁相环技术,具有高灵敏、高速度特性。

其应用于科研与工业制造中,提供适应性强、性价比高的优质服务。

案例二: Tektronix公司生产的TDS5xx及TDS6xx示波器触发电路设计该示波器触发电路设计采用了高性能比较器、线性各阶滤波器与数字噪声抑制器等针对电子仪器行业特定要求的优化策略,具有高速度、高可靠性特点,并成功应用于高端通信、微电子芯片等领域。

便携式示波器课程设计

便携式示波器课程设计一、课程目标知识目标:1. 理解示波器的基本原理,掌握便携式示波器的操作方法;2. 学会使用便携式示波器观察波形,识别常见信号特征;3. 掌握示波器在物理实验和工程测量中的应用。

技能目标:1. 能够正确连接便携式示波器与被测电路,进行基本操作;2. 培养学生动手实践能力,通过实际操作,学会波形分析;3. 提高学生的问题解决能力,能运用示波器检测并处理简单的电路问题。

情感态度价值观目标:1. 培养学生对物理实验和电子技术的兴趣,激发探究精神;2. 增强学生的团队合作意识,培养在实验中互相协作、共同解决问题的能力;3. 培养学生严谨、客观、科学的实验态度,提高对实验结果的责任感。

本课程针对高年级学生,结合学科特点和教学要求,设计上述目标。

课程强调理论与实践相结合,注重培养学生的实践技能和问题解决能力,同时关注学生情感态度的培养,提高学生的综合素养。

通过本课程的学习,使学生能够熟练使用便携式示波器,并为后续相关课程打下坚实基础。

二、教学内容1. 示波器原理及分类:介绍示波器的工作原理、种类及便携式示波器的特点;- 教材章节:第二章第二节“示波器的原理与分类”2. 便携式示波器操作方法:详细讲解便携式示波器的按键功能、操作步骤和注意事项;- 教材章节:第二章第三节“便携式示波器的使用方法”3. 波形观察与分析:教授如何观察波形,识别信号的频率、幅度等特征;- 教材章节:第三章第一节“波形的观察与分析”4. 示波器应用案例:通过实际案例,展示示波器在物理实验和工程测量中的应用;- 教材章节:第三章第二节“示波器的应用实例”5. 实践操作与问题解决:安排学生进行实践操作,培养动手能力,学习解决实际电路问题;- 教材章节:第四章“实践操作与问题解决”6. 小组讨论与总结:组织学生进行小组讨论,分享学习心得,总结示波器的使用技巧;- 教材章节:第五章“小组讨论与总结”教学内容按照以上大纲进行安排,确保教学内容的科学性和系统性。

labview示波器设计

摘要随着电子技术、计算机技术的高速发展及其在电子测量技术和仪器领域中的应用,新的测试理论、新的测试方法、新的测试领域以及新的仪器结构不断出现,电子测量仪器的功能和作用己经发生质的变化。

在市场的需求和相关技术支持下,促使了基于个人计算机的测控仪器—虚拟仪器的发展。

虚拟仪器利用计算机强大的处理能力,使得它成为了一种很好的工具,其应用范围也越来越广泛。

与传统仪器相比,虚拟仪器在智能化程度、处理能力和可操作性等方面均具有明显的技术优势。

示波器是在科学研究和工程设计中广泛应用的一种通用仪器。

目前研制一种结构简单、操作方便、生产技术要求不高、费用低的新型数字示波器是非常必要的。

本文介绍了一种新型的示波器:虚拟示波器。

虚拟示波器是虚拟仪器技术的一种具体应用。

该虚拟仪器基于计算机平台,实现比传统仪器更强大的功能。

本设计采用模块化的软件设计思想编写,每个功能的实现由一个模块完成。

所设计的虚拟示波器主要由仿真信号发生、参数测量、波形显示和存储模块等组成。

将这些子模块在虚拟仪器的框图程序中按照一定的逻辑关系组合起来,就形成了完整的虚拟示波器。

它具有传统仪器所没有的许多优点,如波形可以存储为图片或是数据文件,可以长久保存并随时调用,波形显示可以进行单、双通道的切换、成本低廉,可以根据需要进行功能拓展。

本设计所采用的软件是美国NI公司推出的LabVIEW。

LabVIEW是一种基于图形化编程语言的开发环境,具有十分强大的数据库。

它为虚拟仪器设计者提供了一个便捷、轻松的设计环境。

是目前应用最广泛的虚拟仪器开发平台软件之一。

关键词:示波器,虚拟仪器,LabVIEW- I- IIABSTRACTWith electronics technique and computer technique developing so fast and their application in electronic measurement and instrument realm,the new test theories, new test method, new test realm and new instrument structure appear continuously. The function of electronics measuring instrument has changed thoroughly. Under the market requirement and related technique support, test and control instrument ---Virtual Instrument (VI) based on personal computer have got development.Virtual Instrument makes use of a strong processing ability of computer, making it become a kind of very useful tool, its application is also more and more extensive. Compared with traditional instrument, VI has obvious technique advantages in the degree of Intelligence, processing ability and maneuverability etc.Oscillograph is a kind of general instrument extensively used in science research and engineering design. It is very necessary to develop a new kind of digital oscillograph with simple structure, being operated facilely, requesting not high level manufacture technology and low cost.This paper introduces a new type of oscillograph: Virtual Oscillograph. The virtual oscillograph is a kind of application of VI technology. This VI is based on a computer, which realizes the stronger function than traditional instrument.The virtual oscillograph we designed consists signal generate, parameter measurement, output display and wave storage modules. These Sub VI can be put together according to the certain logic relation in the frame diagram of the VI, then the virtual oscillograph is completely realized. It has many advantages that the traditional instrument doesn't have, such as saving wave as pictures or permanent data ,using data at any time,displaying wave through two channels,cost low and extending function when needed.The software used in the paper is LabVIEW .LabVIEW is a kind of software based on graphic language, it has a very strong database. It provides a convenient and relaxed designing environment for the VI designer. It is one of the most widely used- IIIsoftware for developing the virtual instrument currently. KEY WORDS:oscillograph, virtual instrument, labview- IV前言电子测量技术发展总是与自然科学,特别是电子技术的最新发展紧密相连的。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数字存储示波器题目任务:设计一简易数字存储示波器1.总体框架图:2.题目要求指标(1) 信号频率范围: 10Hz~10MHz;要求输入电阻: Ri>100kΩ;(2) 垂直点数:32级/div;水平点数:20点/div;(3) 垂直灵敏度:0.01V/div ,0.1V/div,1V/div,误差≤5% ;(4) 水平扫瞄速度: 0.2s/div,0.2ms/div,20μs/div,误差≤5%;(5) 触发功能要求:单次触发、扩展、内触发、上升沿、电平可调;(6) 显示波形无明显失真;(7) 产生100kHz,0.3V的校准方波;报告主要内容:1.对赛题要求的分析2.具体实现方案讨论及器件参数计算3.模拟部分电路设计及数字控制部分软件编写4.安装调试及所遇到的问题5.测试结果分析6.总结1. 对赛题要求的分析(1) 工作流程:A/D采集、双口RAM存储、D/A显示。

需要器件:A/D、单片机、D/A、FPGA等主要器件;(2) 内触发上升沿、触发电平可调;扫描速度 0.2s/div,0.2ms/div,20 μ s/div;垂直灵敏度0.1V/div, 1V/div,0.01V/div移动扩展。

要具有控制功能:1.控制器 2. 人机接口2. 具体方案讨论2.1 采样方式的选择实时采样和等效时间采样:实时采样即按照AD的采样速率对波形进行满足奈奎斯特采样速率的采样;等效采样是在周期信号频率过高,AD速率无法满足奈奎斯特采样速率时,间隔整数倍周期T+最小采样间隔时间对信号进行采样。

具体示意图见下:题中要求输入信号频率范围:10Hz~10MHz,样点直接恢复方式为至少20点/周期, A/D 转换速率应小于1Ms/s。

故对于高频信号(大于500KHz),应采用等效采样方式,低频信号采用实时采样方式。

2.2 控制器件的选择1.对控制器件的要求* AD采集速率:高达1000kHz(1 μ s),低至 20ms;(决定于扫描速度)* 样点恢复速率:DA时钟为10MHz,绝对满足输出波形要求。

* 幅度档位调节:1V/div,0.1V/div,0.01V/div采用程控放大器实现。

* 水平档位调节:0.2s/div,0.2ms/div,20 μ s/div,由X轴(水平)扫描速率决定。

2.三种方案(1) VLSI:例如 FPGA。

特点:可以实现较快的采样及处理速度,但仅用FPGA时程序烦琐,且实现良好的人机界面时难度较大。

(2) MCU:可以实现基本功能,但处理速度速度不能达到采样速率的要求。

(3) MCU+FPGA:MCU和FPGA可以适当分工,MCU控制人机接口以及与FPGA的通讯,FPGA实现具体器件的控制功能。

综上:第三种方案实现最为容易,且器材获得方便,成本较低,故选择第三种方案。

总体电路示意图:2.3 技术指标初步分配(误差是定量指标)(1)信号通道前向通道(采集、存储)≤2.5%后向通道(恢复)≤2%2.5% + 2% = 4.5% ≤ 5%(2)时基(时间基线、扫描速度)控制信号(采样时钟)误差忽略不计扫描电压及输出电路≤2%3. 部分电路设计及模拟将该简易DSO划分为3个部分:Y 通道(前、后向通道)、X通道和控制器3.1 前向通道* 初步控制作用S1 校零,S2校满度* 内容:信号调理电路;低通滤波器;电平移位;前向通道通道性能分析;触发电路。

(1)输入电路* 要求: Ri’≥100kΩ,输入噪声电压影响;* 输入电阻(阻抗)对被测系统的影响:Z越高,影响越小。

* 输入电路* 取R≥ 100kΩ* 运算放大器OP27初步核算:输入电阻:Ri’ =R// Ri ≈ R ≈ 100kΩ;输入端噪声电压:3.6nV,而最高灵敏度时的测量分辨力为:312μV, 3.6nV《 312μV (2)信号调理电路* 作用:使信号符合A/D输入的要求(预计A/D输入≤5V)* 增益计算要求输入幅度(灵敏度×8div ):8V, 0.8V,0.08V。

显然垂直灵敏度和前端放大倍数成反比例关系,垂直灵敏度的调整可以通过改变前端程控放大器的倍数来实现,设计要求垂直灵敏度×8div最大为8V,故显示信号的幅度在-4~+4V之间,而A/D (TLC5540)输入电压为0~5V。

这可以通过电平变换电路用电压幅度在-5~+5V的信号得到,故此时增益为1.25。

同理其他增益为: 12.5,125(由程控实现)。

* 电路图* 有关解释程控开关Sn:必须是模拟开关,选择集成开关MAX4501;增益调节电阻Rnn ,模拟开关的内阻计人其中;补偿电容C1,C2,C3:改善通道频响特性。

(3)低通滤波器* 作用:实时采样时(输入信号频率小于50KHz)抗混迭,滤除高频分量,以改善采样效果,避免输出波形失真。

* 采样信号的频谱混迭现象及改善方法:* 抗混迭滤波器电路* 有关解释运算放大器构成有源低通滤波器;二阶Butterworth低通滤波器。

(4)电平移位电路由于A/D要求+极性输入电压,而此前电路输出±极性电压,故必需此电路来进行电平转换,以适应AD转换的要求。

(5)前向通道性能分析内容:频率特性的模拟;元器件参数的影响;环境温度的影响。

前向通道频率特性的模拟:(用EWB对程控增益放大器和低通滤波器模拟分析)结果:-3dB带宽80kHz〉50kHz 满足设计要求。

6)触发电路* 要求:内触发、正沿、触发电平可以调节;* 电路说明:触发采用比较器,比较电平的极性为+、可以调节;输出为下降沿,向单片机申请中断。

3.2 信号的采样、量化、存储 (DSO的基本技术)(1)垂直分辨率与A/D位数的关系:示波器垂直方向共8格,要求每格32级,共有32×8=256级,,因而采用8位A/D即可,垂直分辨率为8位。

(2)扫描速度与采样频率的关系1.对于实时采样:假设扫描速度为t s/div,每格点数为n,采样频率为fs,则:fs=n/t。

当n=20时,针对不同的扫描速度,可以得到不同的采样频率(见附表)。

在n一定的情况下,扫描速度的改变是通过改变采样频率来实现的,50KHz的正弦波在采样频率为1Mhz时,每周期可采样20个点,可以很好的恢复采样前的信号。

2.对于等效采样:此时采样频率不需要满足奈奎斯特采样速率。

故俩者之间无关。

综上(1),(2)可得到A/D的技术要求:1.转换速率:20 μ s/div ;1μs/点;1 Ms/s2.量化位数:32级/div × 8=256级/8div256=28取8bit量化误差:1LSB=1/28 0.4%3.输入幅度:+( 0---5)V选择:TLC5540(3)存储容量与水平分辨率的关系:存储容量表明水平方向划分细微的程度,是水平分辨率的倒数。

要求示波器显示屏水平刻度为10div,水平分辨率为20点/div。

显示满屏幕需要200个点,故存储容量256 byte足够,考虑波形扩展需要,使用1024byte,FPGA内部集成的双口RAM。

3.3后向通道(1)设计要求:将数字信号(RAM中的数据)恢复为模拟信号并作为通用示波器的Y 输入信号(8V), A、B信号从同一个Y端输入。

要考虑的问题:信号恢复电路及器件选择,同步扫描电压。

(2)信号恢复显示频率和存储器读出频率的关系:显示屏上显示的信号是从存储器中读出的信号,只要使观察到的波形不闪烁即可。

* 采用器件:D/A* 恢复速率:选择适宜人眼的观察速率10kHz ,100 μs/点200点× 100 μs/点=20 ms这样可以免除的高速D/A的要求(是DSO的优点);D/A 选择 THS5651。

(3)同步扫描电压设计* 同步作用:显示稳定的信号波形* 同步扫描电压设计:两种产生扫描电压的方法:1.通用示波器扫描电压:要同步信号,与题目要求不符。

2.简易DSO产生:选择由简易DSO产生,使用另一块DA。

* 扫描电压的产生:D/A选择THS5651,与信号恢复器件一致。

D/A输入数据为10 bit (000—1FF)H递增,实际为阶梯波而不是斜波。

关于扩展显示的信号恢复基本思想在两个页面中取连续的200点,扫描电压与前相同,因此,扩展显示是移动地在两个页面中显示一个页面,关键是控制方法软件编写。

采用每次给存储器扫描地址+2或更多的方法来实现。

3.4 控制器件的设计控制器的作用:控制、数据处理;控制器的组成:控制器自身、人机接口。

(1)键盘采用矩阵扫描非编码键盘,由8个按键组成。

对键盘的解释:1.按下的键状态为“0”;2.s/div和V/div为+1键;3.默认的仪器工作状态:0.2ms/div 、0.1V/div;4.扩展移动键每按一次+2,16,32;5.单片机扫描键盘,有键按下时判断所按下的键并向顶底层控制器FPGA发送信号。

6.仪器的复位键(RESET)不属于键盘管理。

(2)控制器的硬件设计1. DSO的操作时序键盘输入——(相关设置)启动——等待触发——仪器操作(采集、存储、数据处理、信号恢复、显示)见图:(3)控制器件的选择MCU:AT89S52FPGA:CYCLONE_EP1C3T144C8(可以在线编程)(4)FPGA控制器电路图:(5)总体控制器电路* 对控制电路的说明单片机部分:液晶显示器是其外设;与FPGA 的连接是P0、P2口;键盘中断优线于触发中断;输出信号恢复和产生扫描电压的数据;FPGA部分:AD,DA是其外设;采样频率由内部PLL锁相环分频产生,对应于各个水平档位。

DA的频率为固定的10kHz。

4 安装调试5 测试结果5.1 测试结果记录 (测试项目要针对设计要求)2.垂直灵敏度3.扫描速度5.2 测试结果总评价6 小结(1)模拟电路部分设计较合理;(2)两层控制;(3)充分利用片内存储器;(4)充分利用新颖电子技术。

7 展望(1)采用程控电阻和模拟开关(2)扩展功能的再扩展,利用双扫描和CRT的Z通道(3)数字信号处理。