PCIE基础知识

pcie基本原理

pcie基本原理PCI Express(Peripheral Component Interconnect Express)是一种高速串行总线标准,用于连接计算机内部的各种设备和组件,例如显卡、网卡、声卡等。

PCIe基于串行传输方式和点对点连接的思想,相比传统的并行总线具有更高的带宽和更低的延迟。

1. PCIe物理层PCIe物理层包括差分信号传输、时钟恢复、电源管理等方面。

差分信号传输是PCIe最关键的特性之一,它使用两条反向传输线代表一个数据位,实现了抗干扰性能更好和更远距离的数据传输。

时钟恢复是指接收端通过解码发送端发送过来的时钟信息来恢复本地时钟,从而实现同步通信。

电源管理则是为了节省能源,在设备空闲或未使用时自动进入低功耗模式。

2. PCIe数据链路层PCIe数据链路层负责将上层逻辑层的请求转换成可被物理层发送的数据包,并在接收端将数据包还原成原始请求。

数据链路层分为两个子层:逻辑子层(Logical Sublayer)和传输子层(Transport Sublayer)。

逻辑子层主要负责错误检测和纠正,传输子层则负责流量控制和错误恢复。

3. PCIe传输层PCIe传输层是PCIe中最重要的层次之一,它定义了数据包如何在发送端和接收端之间传输。

PCIe采用基于令牌的流控制方式,发送端将数据包打成一个个TLP(Transaction Layer Packet),并通过令牌的方式将TLP交给接收端。

如果接收端准备好接收数据,则返回一个令牌给发送端,发送端才会将数据包发送出去。

这种流控制方式可以有效地避免数据包丢失和冲突。

4. PCIe事务层PCIe事务层是PCIe协议中最高层次的逻辑,它定义了如何进行读写操作、配置设备、中断处理等操作。

PCIe事务分为两种类型:读取(Read)和写入(Write)。

读取操作由请求者发起,写入操作由请求者或响应者发起。

配置空间是一种特殊的地址空间,用于存储设备的配置信息。

PCIe协议相关资料要点

PCIe协议相关资料要点PCIe(Peripheral Component Interconnect Express)是一种计算机总线标准,用于连接计算机系统的外部设备。

它在现代计算机中广泛应用于图形卡、存储卡和扩展卡等设备的连接。

下面是PCIe协议的相关资料要点。

一、PCIe协议概述PCIe协议是一种高速串行通信协议,用于在计算机系统中传输数据。

它取代了传统的PCI总线,提供更高的带宽和更可靠的性能。

PCIe协议具有以下特点:1. 高速性能:PCIe协议支持多个通道和多个数据传输通路,并且每个通道都可以达到多Gbps的传输速度。

2. 点对点连接:PCIe协议采用点对点连接方式,每个设备都直接连接到主机,并且不会与其他设备共享带宽。

3. 热插拔支持:PCIe协议支持热插拔功能,可以在计算机运行时插入或拔出设备,而无需重新启动系统。

4. 多功率状态支持:PCIe协议支持多功率状态,可以有效地管理设备的能耗。

二、PCIe协议架构PCIe协议的架构包括物理层、数据链路层和传输层。

每个层级都有不同的功能和责任。

1. 物理层(Physical Layer):物理层负责在发送和接收设备之间传输数据。

它定义了数据传输的电气特性、传输速度和功耗等参数。

2. 数据链路层(Data Link Layer):数据链路层负责在发送和接收设备之间建立可靠的数据传输连接。

它通过发送和接收数据包来确保数据的完整性和可靠性。

3. 传输层(Transport Layer):传输层负责数据的路由和传输。

它根据设备的地址和标识符来确定数据的发送和接收。

三、PCIe协议数据传输PCIe协议的数据传输分为读取和写入两种方式。

1. 读取(Read):读取是指从PCIe设备读取数据到主机内存。

读取传输由主机启动,并且主机提供要读取的目标地址。

读取过程中,设备将数据传输到主机内存中的指定地址。

2. 写入(Write):写入是指将数据从主机内存写入到PCIe设备。

pcie基本原理

pcie基本原理PCIe基本原理PCIe(Peripheral Component Interconnect Express)是一种高速、点对点的串行总线标准,用于连接计算机内部的外部设备。

它是目前最流行的计算机总线标准之一,被广泛用于连接各种设备,如显卡、网卡、存储控制器等。

本文将介绍PCIe的基本原理,以帮助读者更好地理解这一技术。

PCIe采用串行传输方式,相比传统的并行总线,具有更高的带宽和更低的延迟。

它采用差分信号传输,即同时传输正负两路信号,以减少信号干扰和提高传输速度。

PCIe总线的带宽通常用“xN”来表示,其中“x”表示总线的通道数,而“N”表示每个通道的数据传输速率。

例如,PCIe 3.0 x16表示具有16个通道,每个通道的传输速率为PCIe 3.0规范下的速率。

PCIe总线采用多通道的方式来提高数据传输速度。

每个通道都有自己的发送和接收端口,可以同时进行数据传输。

此外,PCIe还支持多路复用技术,即将多个数据流通过同一物理通道传输,以提高总线的利用率。

这种设计使PCIe具有更高的带宽和更好的扩展性,可以满足不同设备对数据传输速度的需求。

PCIe总线还采用了“插槽”和“连接器”的设计,以便用户可以方便地连接和更换设备。

每个PCIe插槽都有一定数量的针脚,用于传输数据、电源和地线。

连接器则负责将插槽与设备连接起来,保证信号传输的可靠性和稳定性。

PCIe插槽通常分为不同的规格,如PCIe x1、PCIe x4、PCIe x8和PCIe x16等,以适应不同设备的需求。

PCIe总线还具有“热插拔”和“热插拔”功能,用户可以在计算机运行时插入或拔出设备,而无需重新启动计算机。

这使得设备的更换和升级变得更加方便快捷。

此外,PCIe还支持“链路层发现”和“链路层训练”功能,用于自动检测和优化总线的性能,以提高数据传输的稳定性和可靠性。

总的来说,PCIe是一种高速、灵活、可靠的计算机总线标准,被广泛应用于各种设备之间的连接。

pcie基础知识(二)

pcie基础知识(二)本文主要讲述PCIE的相关缩写、术语;不同模式、配置;枚举等基础知识。

一、designware pcie产品:Dual Mode coreRC coreEP coreSwitch core二、架构:Common Xpress Port Logic (CXPL)实现大部分的传输层逻辑,所有的数据链路层逻辑,物理层的MAC部分(包括LTSSM)。

这个module就是所说的core。

XADM和RADM都是针对传输应用添加的模块。

比如说添加传输队列,仲裁TLP transmmision。

Transmit Application-Dependent Module (XADM)Receive Application-Dependent Module (RADM)Configuration-Dependent Module (CDM)Power Management Controller (PMC)Local Bus Controller (LBC)Message Generation (MSG_GEN)Hot Plug Control (hotplug_ctrl)三、核心(CXPL)操作3.1 DM/RC/EP 模式下的初始化在reset之后,通过检测device_type输入进入到RC或者EP模式,CDM内部配置寄存器为复位值。

LTSSM前配置:keep the app_ltssm_enable signal deasserted after reset until the application is ready to establish a Link and start receiving and transmitting TLPs,在这个阶段通过DBI配置好配置寄存器。

开始LTSSM:assert app_ltssm_enable to allow the LTSSM to begin Link establishment3.2 Link EstablishmentPIPE口,和usb3.0一样。

PCI-E资料(全)

TxData Command Status RxData PClk

Transaction Link xx

State machines for Link Training and Status State Machine (LTSSM) and lane0lane deskew

转向PCIe主要是为了实现显著增强系统吞吐量、扩容性和灵活性的目标,同时还要降低制造成本,而这 些都是基于总线的传统互连标准所达不到的。PCI Express标准在设计时着眼于未来,并且能够继续演 进,从而为系统提供更大的吞吐量。第一代PCIe规定的吞吐量是每秒2.5千兆比特(Gbps),第二代规 定的吞吐量是5.0 Gbps,而最近公布PCIe 3.0标准已经支持8.0 Gbps的吞吐量。在PCIe标准继续充分利 用最新技术来提供不断加大的吞吐量的同时,采用分层协议也便于PCI向PCIe的演进,并保持了与现有 PCI应用的驱动程序软件兼容性。

Chip Set with Root Complex

PCIe RC Controller

PHY

PHY PCIe Endpoint

Endpoint

图3:SoC芯片内的PHY和控制器运用

正如上文所述,2个端口之间的虚线代表着链路。PCIe链路是单向的,并采用了低压差分信号。PCIe规 格定义了链路可以包含多达32个并行通道,用于将PCIe 1.x(2.5Gbps)链路的吞吐量扩展至80 Gbps, 或将PCIe 2.0(5.0 Gbps)的吞吐量扩展至160 Gbps。同一链路内的每个线路(Lane)均提供了自己的 内嵌时钟信号,因而无需在PC电路板上实现线路长度匹配——这种匹配是以前PCI接口为了保持时序所 必需的。

PCIe规格内所定义的此协议遵循的是开源促进会(OSI)模型。此协议分隔成5个基本层,如图2左侧所 示。本节对机械层和物理层进行了综述;后续各节将针对链路层、事务处理层和应用层进行说明。

什么是PCIe卡?您需要了解的有关PCIExpress卡的所有信息

什么是PCIe卡?您需要了解的有关PCIExpress卡的所有信息PCI Express(PCIe)标准的出现是为了满足网络设备对更高带宽、更大灵活性和更好性能的需求。

PCIe在首次亮相后已经得到充分开发并广泛应用于许多网络设备,特别是对于PCIe卡。

什么是PCI快速卡?有多少种类型的 PCIe 卡?PCIe x8 或 PCIe x16 是什么意思?我可以在 2.0 插槽中使用 PCIe 3.0 卡吗?如何找到最好的PCI快速卡?在这篇文章中找到答案。

什么是 PCIe 卡?PCIe卡(又名PCI Express卡,基于PCIe的卡)是指一种具有PCIe接口的网络适配器,在主板级连接中用作扩展卡接口。

具体而言,基于 PCIe 的扩展卡设计用于安装在主机、服务器和网络交换机等设备主板中基于PCIe 的插槽中。

大多数PC的主板都有PCIe插槽,仅用于将PCIe卡安装在相应的PCIe插槽中。

(插槽的宽度等于或宽度为卡。

PCI 与 PCI-X 与 PCI-E 是具有不同设计和拓扑的三个版本的网络适配器。

最新的PCIe卡已经进行了改进,成为选择网卡时的必然趋势。

进一步学习:PCI vs PCI-X vs PCI-E,为什么选择PCI-E卡?PCIe 卡如何工作?PCI Express卡不像处理来自多个源的数据的总线那样执行,而是可以通过开关实现一系列点对点连接,以控制数据需要去哪里。

插入PCIe网卡后,将在插槽和卡之间形成逻辑连接以进行通信,称为互连或链路,从而在两个PCIe端口之间启用点对点通信通道,并允许它们都发送和接收普通的PCI请求和中断。

如下图所示,PCIe 插槽包含一个或多个通道。

对于x2链路,每个通道由两个不同的数据传输对组成,一对用于传输数据,另一对用于接收数据。

因此,每个通道由四根导线或信号迹线组成。

有多少种类型的 PCIe 卡?基于 PCIe 卡尺寸•PCIe 卡版本和插槽宽度:确保PCI Express 卡类型与您当前的设备和网络环境兼容。

PCIe的原理及体系架构_学习笔记

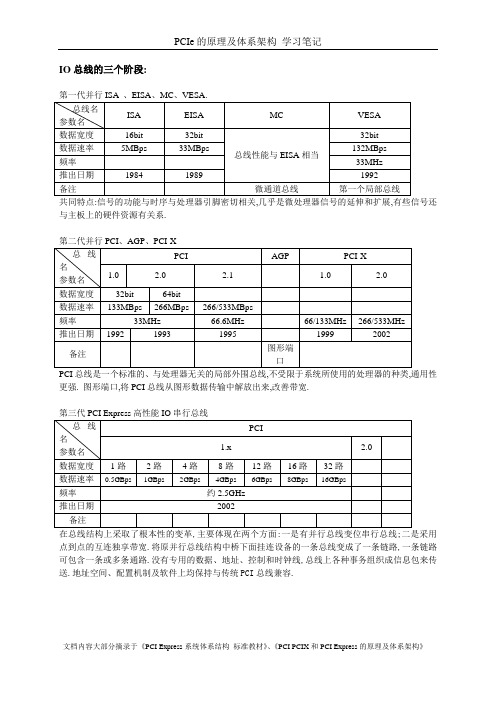

IO总线的三个阶段:第一代并行ISA 、EISA、MC、VESA.共同特点:信号的功能与时序与处理器引脚密切相关,几乎是微处理器信号的延伸和扩展,有些信号还与主板上的硬件资源有关系.第二代并行PCI、AGP、PCI-XPCI总线是一个标准的、与处理器无关的局部外围总线,不受限于系统所使用的处理器的种类,通用性更强. 图形端口,将PCI总线从图形数据传输中解放出来,改善带宽.第三代PCI Express高性能IO串行总线在总线结构上采取了根本性的变革,主要体现在两个方面:一是有并行总线变位串行总线;二是采用点到点的互连独享带宽.将原并行总线结构中桥下面挂连设备的一条总线变成了一条链路,一条链路可包含一条或多条通路.没有专用的数据、地址、控制和时钟线,总线上各种事务组织成信息包来传送.地址空间、配置机制及软件上均保持与传统PCI总线兼容.第一代和第二代都是并行总线,有多条地址线、数据线和控制线,挂接多个设备,称为下挂式总线(Multi-Drop),总线带宽由多个设备共享.通过提高数据宽度和频率来改善带宽的代价是挂接的电器负载减少(由于功耗增加和静态定时减少).PCIx与PCI相比:由于采用了PLL,频率更高性能更好;在地址和数据的基础上增加属性,从而可以高效管理缓冲区;分离事务协议相对延迟事务协议来说,提高了总线利用效率;可不需要中断引脚,改用消息信号中断(带内)体系结构,中断效率更高.基于PCI总线的结构最基本的PCI总线平台包含三级总线:FSB(Front-Side Bus)、PCI和ISA,FSB是处理器子系统的总线(Host总线),总线定义完全取决于系统所用的处理器;PCI局部总线是一个完全与处理器无关的总线,不受限微处理器的种类;ISA总线(IO扩展总线),也有采用EISA或MC总线的.不同的总线之间通过相应的桥芯片来连接.平台中两极桥是必须的,一是Host到PCI的(常称为主桥——Host桥),即北桥;另一个是PCI总线的桥(常称为扩展总线桥),即南桥.最基本的基于PCI总线的平台PCI地址空间映射x86 CPU的内存与I/O独立编址,I/O对应寄存器,内存对应RAM.因此,访问IO空间用IO读写指令,访问内存空间用内存读写指令.IO读写一般用于低速传输一些状态、控制寄存器的读写等。

PCIe基础篇(一)、基础知识扫盲

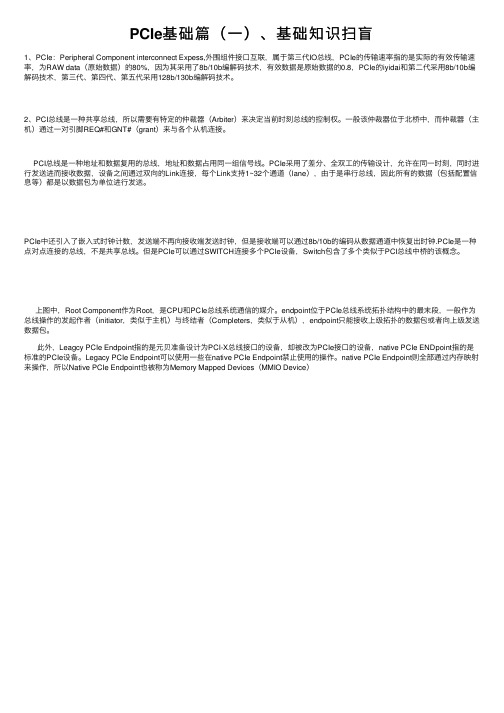

PCIe基础篇(⼀)、基础知识扫盲1、PCIe:Peripheral Component interconnect Expess,外围组件接⼝互联,属于第三代IO总线,PCIe的传输速率指的是实际的有效传输速率,为RAW data(原始数据)的80%,因为其采⽤了8b/10b编解码技术,有效数据是原始数据的0.8,PCIe的iyidai和第⼆代采⽤8b/10b编解码技术,第三代、第四代、第五代采⽤128b/130b编解码技术。

2、PCI总线是⼀种共享总线,所以需要有特定的仲裁器(Arbiter)来决定当前时刻总线的控制权。

⼀般该仲裁器位于北桥中,⽽仲裁器(主机)通过⼀对引脚REQ#和GNT#(grant)来与各个从机连接。

PCI总线是⼀种地址和数据复⽤的总线,地址和数据占⽤同⼀组信号线。

PCIe采⽤了差分、全双⼯的传输设计,允许在同⼀时刻,同时进⾏发送进⽽接收数据,设备之间通过双向的Link连接,每个Link⽀持1~32个通道(lane),由于是串⾏总线,因此所有的数据(包括配置信息等)都是以数据包为单位进⾏发送。

PCIe中还引⼊了嵌⼊式时钟计数,发送端不再向接收端发送时钟,但是接收端可以通过8b/10b的编码从数据通道中恢复出时钟.PCIe是⼀种点对点连接的总线,不是共享总线。

但是PCIe可以通过SWITCH连接多个PCIe设备,Switch包含了多个类似于PCI总线中桥的该概念。

上图中,Root Component作为Root,是CPU和PCIe总线系统通信的媒介。

endpoint位于PCIe总线系统拓扑结构中的最末段,⼀般作为总线操作的发起作者(initiator,类似于主机)与终结者(Completers,类似于从机),endpoint只能接收上级拓扑的数据包或者向上级发送数据包。

此外,Leagcy PCIe Endpoint指的是元贝准备设计为PCI-X总线接⼝的设备,却被改为PCIe接⼝的设备,native PCIe ENDpoint指的是标准的PCIe设备。

pci-e 标准 -回复

pci-e 标准-回复PCIE(Peripheral Component Interconnect Express)标准是一种计算机总线架构,用于连接计算机内部各个硬件设备,如图形卡、网络卡、存储控制器等。

它是一种高速串行接口,能够提供高带宽和低延迟的数据传输。

本文将一步一步地回答关于PCIE标准的问题,以帮助读者更好地了解它。

第一步:了解PCIE标准的起源和发展PCIE标准最早由英特尔在2004年推出,旨在取代传统的PCI(Peripheral Component Interconnect)总线,以满足日益增长的数据传输需求。

随着数据量的不断增加,PCI总线的带宽已经不能满足现代计算机系统的要求。

为了解决这个问题,PCIE标准应运而生。

第二步:理解PCIE标准的基本原理和工作原理PCIE标准基于串行接口技术,通过使用差分信号传输数据。

差分信号是指通过同时传输正负两个信号来表示信息的一种方式,具有抗干扰能力强、传输距离较远等优势。

PCIE标准将数据传输分为数据链路层和物理层两部分,其中数据链路层负责将数据整理成数据包,并管理传输的流程和错误纠正。

物理层则负责将数据包转换成串行信号,并在不同设备之间传输。

第三步:详细探究PCIE标准的相关概念和特点PCIE标准涉及到许多概念和特点,下面将逐一介绍其中一些重要的内容。

1. 通道(Lane):PCIE标准中的通道是指传输数据的单个物理通路,可以将其理解为PCIE总线的基本传输单元。

通道的数量较多,常见的配置有1通道、4通道、8通道等。

通常情况下,通道的数量越多,传输速度越快。

2. 带宽:PCIE标准具有可扩展的带宽,根据通道数量的不同,可以实现不同的数据传输速度。

常见的带宽配置有PCIE 1.0(2.5 Gbps)、PCIE 2.0(5 Gbps)和PCIE3.0(8 Gbps)等。

3. 虚拟化支持:PCIE标准还提供了对虚拟化技术的支持。

虚拟化技术可以将物理设备划分为多个虚拟设备,在同一物理系统上运行多个操作系统实例。

PCIE基础知识

PCIe总线概述随着现代处理器技术的发展,在互连领域中,使用高速差分总线替代并行总线是大势所趋.与单端并行信号相比,高速差分信号可以使用更高的时钟频率,从而使用更少的信号线,完成之前需要许多单端并行数据信号才能达到的总线带宽。

PCI总线使用并行总线结构,在同一条总线上的所有外部设备共享总线带宽,而PCIe 总线使用了高速差分总线,并采用端到端的连接方式,因此在每一条PCIe链路中只能连接两个设备.这使得PCIe与PCI总线采用的拓扑结构有所不同。

PCIe总线除了在连接方式上与PCI总线不同之外,还使用了一些在网络通信中使用的技术,如支持多种数据路由方式,基于多通路的数据传递方式,和基于报文的数据传送方式,并充分考虑了在数据传送中出现服务质量QoS (Quality of Service)问题。

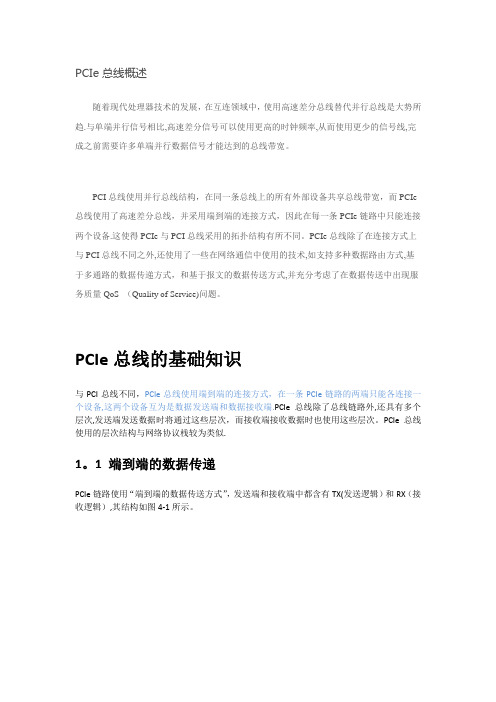

PCIe总线的基础知识与PCI总线不同,PCIe总线使用端到端的连接方式,在一条PCIe链路的两端只能各连接一个设备,这两个设备互为是数据发送端和数据接收端.PCIe总线除了总线链路外,还具有多个层次,发送端发送数据时将通过这些层次,而接收端接收数据时也使用这些层次。

PCIe总线使用的层次结构与网络协议栈较为类似.1。

1 端到端的数据传递PCIe链路使用“端到端的数据传送方式”,发送端和接收端中都含有TX(发送逻辑)和RX(接收逻辑),其结构如图4-1所示。

由上图所示,在PCIe总线的物理链路的一个数据通路(Lane)中,由两组差分信号,共4根信号线组成。

其中发送端的TX部件与接收端的RX部件使用一组差分信号连接,该链路也被称为发送端的发送链路,也是接收端的接收链路;而发送端的RX部件与接收端的TX部件使用另一组差分信号连接,该链路也被称为发送端的接收链路,也是接收端的发送链路。

一个PCIe链路可以由多个Lane组成.高速差分信号电气规范要求其发送端串接一个电容,以进行AC耦合。

该电容也被称为AC 耦合电容。

pcie基本原理

pcie基本原理

PCIe(Peripheral Component Interconnect Express)是一种高速串行总线技术,用于连接计算机内部的各种设备,如显卡、网卡、声卡等。

它是一种点对点连接方式,每个设备都有自己的通信通道,可以同时进行数据传输,从而提高了系统的性能和效率。

PCIe的基本原理是通过差分信号传输来实现高速数据传输。

差分信号是指将信号分成两个相反的信号,一个为正极信号,一个为负极信号,两个信号之间的差值就是差分信号。

这种传输方式可以有效地减少信号干扰和噪声,提高信号的稳定性和可靠性。

PCIe总线的工作原理是将数据分成小块,每个小块都有自己的地址和控制信息,然后通过差分信号传输到目标设备。

每个设备都有自己的地址和标识符,可以识别和响应来自其他设备的请求。

当一个设备需要发送数据时,它会向总线发送请求,然后等待总线的响应。

如果总线空闲,它就可以发送数据,否则就需要等待其他设备的数据传输完成。

PCIe总线的速度通常以每秒传输的数据位数来衡量,例如PCIe 3.0的速度为8Gbps,即每秒可以传输8亿个二进制位。

这种高速传输速度可以满足现代计算机对数据传输的高要求,从而提高了系统的性能和效率。

PCIe是一种高速、可靠的串行总线技术,它通过差分信号传输来

实现高速数据传输,每个设备都有自己的通信通道,可以同时进行数据传输,从而提高了系统的性能和效率。

PCIE基础知识

PCIe总线概述随着现代处理器技术的发展,在互连领域中,使用高速差分总线替代并行总线是大势所趋。

与单端并行信号相比,高速差分信号可以使用更高的时钟频率,从而使用更少的信号线,完成之前需要许多单端并行数据信号才能达到的总线带宽。

PCI总线使用并行总线结构,在同一条总线上的所有外部设备共享总线带宽,而PCIe 总线使用了高速差分总线,并采用端到端的连接方式,因此在每一条PCIe链路中只能连接两个设备。

这使得PCIe与PCI总线采用的拓扑结构有所不同。

PCIe总线除了在连接方式上与PCI总线不同之外,还使用了一些在网络通信中使用的技术,如支持多种数据路由方式,基于多通路的数据传递方式,和基于报文的数据传送方式,并充分考虑了在数据传送中出现服务质量QoS (Quality of Service)问题。

PCIe总线的基础知识与PCI总线不同,PCIe总线使用端到端的连接方式,在一条PCIe链路的两端只能各连接一个设备,这两个设备互为是数据发送端和数据接收端。

PCIe总线除了总线链路外,还具有多个层次,发送端发送数据时将通过这些层次,而接收端接收数据时也使用这些层次。

PCIe 总线使用的层次结构与网络协议栈较为类似。

1.1 端到端的数据传递PCIe链路使用“端到端的数据传送方式”,发送端和接收端中都含有TX(发送逻辑)和RX(接收逻辑),其结构如图4-1所示。

由上图所示,在PCIe总线的物理链路的一个数据通路(Lane)中,由两组差分信号,共4根信号线组成。

其中发送端的TX部件与接收端的RX部件使用一组差分信号连接,该链路也被称为发送端的发送链路,也是接收端的接收链路;而发送端的RX部件与接收端的TX部件使用另一组差分信号连接,该链路也被称为发送端的接收链路,也是接收端的发送链路。

一个PCIe链路可以由多个Lane组成。

高速差分信号电气规范要求其发送端串接一个电容,以进行AC耦合。

该电容也被称为AC 耦合电容。

PCIe引脚定义和PCIe协议层介绍

PCIe引脚定义和PCIe协议层介绍本文我们将向大家介绍PCIe引脚定义以及PCIe协议层。

1.PCIe引脚定义PCI Express,官方简称PCIe,是计算机总线的一个重要分支, 插槽图片如下:下表列出在边缘(连接器)上的PCI Express卡两侧的导线。

在印刷电路板((PCB))的焊接侧为A侧,并且组件侧的B侧。

PRSNT1# 和PRSNT2# 引脚必须比其余稍短,以确保热插入卡时其余管脚完全插入。

WAKE# 引脚采用全电压唤醒计算机,但必须拉高从备用(电源),以表明该卡是能够唤醒。

2.PCIe协议层PCIE协议中包括应用层、事务层、数据链路层和物理层。

应用层(Appl(ic)ation Layer):应用层是在事务层之上的一层,它处理与连接的设备进行的高级(通信)。

这可能包括配置设备、初始化(寄存器)、发送和接收控制命令等。

事务层(Transac(ti)on Layer):事务层是PCIe协议的核心,它负责将上层软件请求转化为数据传输和交换。

事务层处理内存读写请求、配置空间访问以及其他与连接的设备进行通信的请求。

事务层接收由应用层传来的组成TLP核心部分所需要的(信息),并将数据组装成He(ad)er 和Data(有些TLP没有DATA),计算End CRC (ECRC)。

数据链路层(Data Link Layer):数据链路层接收事务层传过来的TLP包,然后在其前面加上12bit 的Sequence ID,并根据目前所有的信息计算32bit 的CRC (LCRC),并附着在后面。

物理层(Physical Layer):主要职责是处理所有的数据物理传输,发送端数据分发到各个Lane传输(stripe),接收端把各个Lane上的数据汇总起来(De-stripe),每个Lane上加扰(Sc(ram)ble,目的是让0和1分布均匀,去除信道的电磁干扰EMI)去扰(De-scramble),以及8/10或者128/130编码解码,等等。

pcie标准

pcie标准PCIe标准。

PCIe(Peripheral Component Interconnect Express)是一种用于连接外部设备和计算机主板的高速接口标准。

它是一种串行接口,可以提供比传统PCI接口更高的数据传输速度和性能。

PCIe接口广泛应用于各种计算机和服务器系统中,是连接显卡、网卡、存储设备等外部设备的主要接口之一。

本文将介绍PCIe标准的基本原理、技术特点和应用领域。

PCIe接口采用了差分信号传输技术,可以实现更高的数据传输速率。

它采用了一种称为“数据包交换”的通信机制,能够更有效地利用总线带宽,提高数据传输效率。

此外,PCIe接口还支持热插拔和热替换功能,可以在不关闭系统的情况下插拔设备,方便用户维护和升级硬件设备。

PCIe接口的速度通常以“x1”、“x4”、“x8”、“x16”等来表示,分别代表每条通道的带宽。

其中,“x1”表示单通道,带宽为一倍的PCIe速度,而“x16”则表示16倍的速度。

通过增加通道数和提高每个通道的带宽,PCIe接口可以实现更高的数据传输速率,满足不同设备对带宽的需求。

PCIe接口在计算机和服务器系统中有着广泛的应用。

在桌面计算机中,PCIe接口通常用于连接显卡、网卡、声卡、存储控制器等设备,可以提供更高的图形处理和数据传输性能。

在服务器系统中,PCIe接口则可以连接高速存储设备、网络适配器、加速卡等,满足数据中心对高性能和高可靠性的需求。

随着技术的不断发展,PCIe标准也在不断更新和演进。

目前最新的PCIe 4.0标准已经开始投入使用,可以提供比之前版本更高的数据传输速率和带宽。

未来,PCIe 5.0和PCIe 6.0标准也正在研发中,预计将进一步提升数据传输速率,满足日益增长的数据处理需求。

总的来说,PCIe标准作为一种高速接口标准,在计算机和服务器系统中有着重要的应用。

它通过差分信号传输技术和数据包交换机制,实现了更高的数据传输速率和性能,满足了不同设备对带宽和延迟的需求。

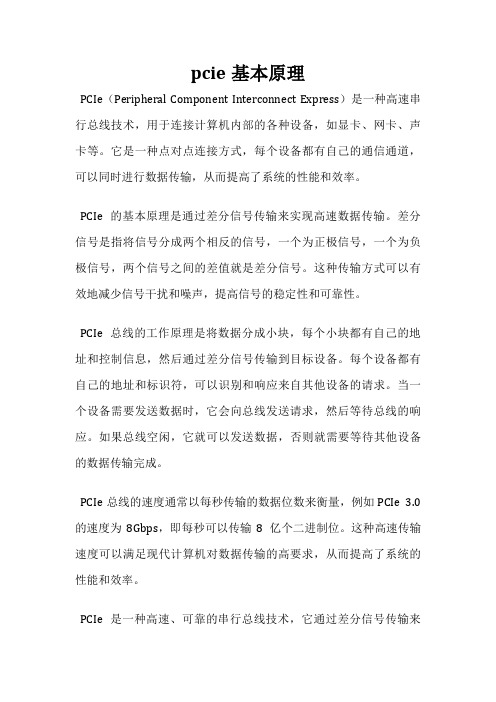

PCIe总线基础

PCIe总线物理层

• 差分信号与单端信号:单端信号地平面是电流回路,差分信号

地平面也是重要的回路,之间也是电流回路。因此在设计时候要注意差分信号的地平 面也是很重要的。不要出现不连续的地平面或者没有参考地平面。

差分的好处:

1 共模抑制比高,抗干扰能力强; 2有效抑制信号传递带来的EMI干扰,极性相反;对外界的辐射相互抵消,因此产生的 噪声也是最小的。 3 逻辑状态定位准确,不受工艺和环境的影响 ;

PCIe总线带宽

PCIe总线架构

PCIe总线架构

Intel体系中的PCIe体系架构

PCIe总线层次结构

PCIe总线层次结构

software

TLP

DLLP

PLP

PCIe总线采集卡实现模式

PCIe三种实现模式

PCIe各层封装

• 各层叠加关系

各层包结构概览

• 作用:接收链路层的东西并发送到物理线路上,2,3,4………….) 2 rxnx,rxpx(x为1 ,2,3,4………….) 3 REFCLK+和REFCLK-信号 4 PERST#信号 5 WAKE#信号 6 SMCLK和SMDAT信号 7 JTAG信号 8 PRSNT1#和PRSNT2#信号

PCI总线信号

PCIe总线技术概览

PCIe总线是PCI总线的一种实现方式,从逻辑上来说他还是PCI总线, 他的大部分的概念来源于PCI总线,因此我们要从PCI总线讲起。

目录

1 2 3

PCI总线概述 PCIE总线各层 PCIE总线板卡实现

PCI技术概览

PCIE总线信号 PCIe总线架构 PCIe总线各层 PCIe总线物理层和链路层 PCIe总线事务层

jetson orin nano的pcie的知识点 -回复

jetson orin nano的pcie的知识点-回复Jetson Orin Nano的PCIe的知识点Jetson Orin Nano是一款具有强大计算和人工智能加速功能的嵌入式计算平台,其中包括了PCIe(Peripheral Component Interconnect Express)接口。

PCIe是一种高速串行接口技术,提供了计算机系统中各种外部设备与主板之间的连接方式。

在本文中,我们将一步一步地回答有关Jetson Orin Nano的PCIe接口的知识点。

第一部分:了解PCIe接口的基础知识1. PCIe的简介PCIe是一种用于连接计算机内部或外部设备的串行接口标准。

它是PCI (Peripheral Component Interconnect)接口的继承者,具有更高的数据传输速度和更少的数据传输延迟。

2. PCIe的工作原理PCIe使用了一种基于差分信号的串行通信方法。

它将数据分成多个流,每个流都通过一个或多个差分对进行传输。

这种方式可以提供更高的带宽和更低的传输延迟。

3. PCIe的规格PCIe接口有多个版本和不同的链接速度(例如,PCIe 1.0,PCIe 2.0,PCIe 3.0,PCIe 4.0和PCIe 5.0)。

每个版本都有不同的带宽和传输速度。

第二部分:Jetson Orin Nano的PCIe接口1. Jetson Orin Nano的PCIe接口规格Jetson Orin Nano采用了PCIe 5.0规格,它提供了更高的带宽和传输速度。

具体来说,Jetson Orin Nano有一个PCIe x16插槽。

这意味着它可以支持x1、x2、x4、x8和x16的PCIe设备。

2. 使用Jetson Orin Nano的PCIe接口Jetson Orin Nano的PCIe接口可以用于连接各种外部设备,例如图形处理单元(GPU)、加速卡、存储设备、网络卡等。

PCIe接口为这些设备提供了高速数据传输通道,从而提供了卓越的性能。

(完整版)PCIe协议相关资料

(完整版)PCIe协议相关资料1.PCIe简介PCI-Express是最新的总线和接⼝标准,它原来的名称为“3GIO”,是由英特尔提出的,很明显英特尔的意思是它代表着下⼀代I/O接⼝标准。

交由PCI-SIG(PCI特殊兴趣组织)认证发布后才改名为“PCI-Express”。

这个新标准将全⾯取代现⾏的PCI和AGP,最终实现总线标准的统⼀。

它的主要优势就是数据传输速率⾼,⽬前最⾼可达到10GB/s以上,⽽且还有相当⼤的发展潜⼒。

PCI Express也有多种规格,从PCI Express 1X到PCI Express 16X,能满⾜现在和将来⼀定时间内出现的低速设备和⾼速设备的需求。

能⽀持PCI Express的主要是英特尔的i915和i925系列芯⽚组。

PCI Express(以下简称PCI-E)采⽤了⽬前业内流⾏的点对点串⾏连接,⽐起PCI以及更早期的计算机总线的共享并⾏架构,每个设备都有⾃⼰的专⽤连接,不需要向整个总线请求带宽,⽽且可以把数据传输率提⾼到⼀个很⾼的频率,达到PCI所不能提供的⾼带宽。

相对于传统PCI总线在单⼀时间周期内只能实现单向传输,PCI-E的双单⼯连接能提供更⾼的传输速率和质量,它们之间的差异跟半双⼯和全双⼯类似。

PCI-E的接⼝根据总线位宽不同⽽有所差异,包括X1、X4、X8以及X16,⽽X2模式将⽤于内部接⼝⽽⾮插槽模式。

PCI-E规格从1条通道连接到32条通道连接,有⾮常强的伸缩性,以满⾜不同系统设备对数据传输带宽不同的需求。

此外,较短的PCI-E卡可以插⼊较长的PCI-E插槽中使⽤,PCI-E接⼝还能够⽀持热拔插,这也是个不⼩的飞跃。

PCI-E X1的250MB/秒传输速度已经可以满⾜主流声效芯⽚、⽹卡芯⽚和存储设备对数据传输带宽的需求,但是远远⽆法满⾜图形芯⽚对数据传输带宽的需求。

因此,⽤于取代AGP接⼝的PCI-E 接⼝位宽为X16,能够提供5GB/s的带宽,即便有编码上的损耗但仍能够提供约为4GB/s左右的实际带宽,远远超过AGP 8X的2.1GB/s的带宽。

显卡PCIAGPPCI-E接口的区别有哪些?PCI-E接口知识科普

显卡PCIAGPPCI-E接⼝的区别有哪些?PCI-E接⼝知识科普新⼀期的新⼿训练营栏⽬⼜和⼤家见⾯了,这⼀期我们的话题是PCI-E接⼝,作为主板上可能是最⼤尺⼨的接⼝,其应⽤范围⾮常⼴泛,不仅仅局限于我们经常⽤到的独⽴显卡,其他诸如⽹卡声卡视频采集卡等设备也是通过PCI-E标准来使⽤的。

PCI-E接⼝是主板上⽐较通⽤的⼀种接⼝标准,⽬前主要提供给需要直接与CPU进⾏通讯的设备使⽤,通常是为了扩展主板上没有⽀持的功能,⽐如扩展独⽴显卡等设备,⽬的是为平台输出更加强⼒的图形能⼒,弥补核显的不⾜。

PCI-E接⼝的独⽴显卡最近⼀段时间可能⼤家听说的更多的是有关于PCI-E接⼝的固态硬盘,亦或是M.2接⼝的固态硬盘,只要是⽀持NVMe协议的SSD产品都是通过PCI-E总线来与处理器交互,最⾼⽬前⽀持到PCI-E 3.0 X4的带宽,关于这个带宽的问题,笔者会在后⾯进⾏解释。

PCI接⼝PCI总线英⽂全称为Peripheral Component Interconnect,翻译成中⽂是“外围器件互联”,是由PCISIG (PCI Special Interest Group)推出的⼀种局部并⾏总线标准。

PCI总线标准是1992年制定的,算⼀算⽐⼩狼年龄都⼤了,他的出现是由ISA(Industy Standard Architecture)总线发展⽽来。

PCI接⼝普通的PCI接⼝数据宽度为32位(bit,也就是常说的⼩b),交互速度为33MHz,理论最⼤带宽就是4Byte/s*33MHz=133MB/s,注意这⾥就变成了Byte字节,也就是通常说的⼤B,由于在计算机中数据是以⼆进制计算的,所以这个等式中的33MHz其实应该是33.33333...。

PCI(上)和PCI-X(下)后来推出的更⾼传输速度的PCI-X依然是采⽤的PCI总线标准,通过提升针脚数量来提升速度,另外PCI 64/66新规范提供了64位(bit)的数据宽度和66MHz的⼯作频率,理论带宽就提升到了533MB/s。

PCIe简介及引脚定义

PCIe简介及引脚定义

随着现代处理器技术的发展,在互连领域中,使用高速差分总线替代并行总线是大势所趋。

与单端并行信号相比,高速差分信号可以使用更高的时钟频率,从而使用更少的信号线,完成之前需要许多单端并行数据信号才能达到的总线带宽。

PCI总线使用并行总线结构,在同一条总线上的所有外部设备共享总线带宽,而PCIe总线使用了高速差分总线,并采用端到端的连接方式,因此在每一条PCIe链路中只能连接两个设备。

这使得PCIe与PCI 总线采用的拓扑结构有所不同。

PCIe总线除了在连接方式上与PCI总线不同之外,还使用了一些在网络通信中使用的技术,如支持多种数据路由方式,基于多通路的数据传递方式,和基于报文的数据传送方式,并充分考虑了在数据传送中出现服务质量QoS (Quality of Service)问题。

PCIe引脚定义如下,有4种接口尺寸,每种接口的1到11对引脚都是一样的,剩下的是差分数据线和时钟,数据线数量不同对应的PCIe尺寸也不一样,X1的PCIe板子可以插在X4的插槽上。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

PCIe总线概述随着现代处理器技术的发展,在互连领域中,使用离速差分总线替代并行总线是大势所趋。

与单端并行信号相比,高速差分信号可以使用更高的时钟频率,从而使用更少的信号线, 完成之前需要许多单端并行数据信号才能达到的总线带宽。

PCI总线使用并行总线结构,在同一条总线上的所有外部设备共享总线带宽,而PCIe 总线使用了鬲速差分总线,并釆用端到端的连接方式,因此在每一条PCIe链路中只能连接两个设备。

这使得PCIe与PCI总线釆用的拓扑结构有所不同。

PCIe总线除了在连接方式上与PCI总线不同之外,还使用了一些在网络通信中使用的技术,如支持多种数据路由方式,基于多通路的数据传递方式,和基于报丈的数据传送方式,并充分考虑了在数据传送中出现服务质量QoS (Qual ity of Service)问题。

PCIe总线的基础知识与PCI总线不同,PCIe总线使用端到端的连接方式,在一条PCIe链路的两端只能各连接一个设备,这两个设备互为是数据发送端和数据接收端。

PCIe总线除了总线链路外,还具有多个层次,发送端发送数据时将通过这些层次,而接收端接收数据时也使用这些层次。

PCIe 总线使用的层次结构与网络协议栈较为类似。

端到端的数据传递PCIe链路使用“端到端的数据传送方式”.发送端和接收端中都含有TX(发送逻辑)和RX(接收逻辑),其结构如图4-1所示。

Da" Linker layer “ Ph、sical layer ■ Data Linker la^^r图41PCIe 总线的物理链蒋由上图所示,在PCIe 总线的物理链路的一个数扌居通路(Lane)中,由两组差分信号,共4根 信号线组成。

其中发送端的TX 部件与接收端的RX 部件使用一组差分信号连接,该链路也被 称为发送端的发送链路,也是接收端的接收链路:而发送端的RX 部件与接收端的TX 部件使 用另一组差分信号连接,该链路也被称为发送端的接收链路,也是接收端的发送链路。

一个 PCIe 链路可以由多个Lane 组成。

离速差分信号电气规范要求其发送端串接一个电容,以进行AC 耦合。

该电容也被称为AC 耦合电容。

PCIe 链路使用差分信号进行数据传送,一个差分信号由D+和D-两根信号组成, 信号接收端通过比较这两个信号的差值,判斯发送端发送的是逻辑“1”还是逻辑“0”。

与单端信号相比,差分信号抗千扰的能力更强,因为差分信号在布线时要求“等长”、“等宽”、 “贴近”,而且在同层。

因此外部干扰噪声将被“同值”而且“同吋”加载到D+和D-两根信 号上,其差值在理想情况下为0,对信号的逻辑值产生的影响较小。

因此差分信号可以使用 更商的总线频率。

此外使用差分信号能有效抑制电磁干扰EMI (Electro Magnetic Interference) o 由于差分 信号D+与D-距离很近而且信号幅值相等.极性相反。

这两根线与地线间耦合电磁场的幅值 相等,将相互抵消,因此差分信号对外界的电触千扰较小。

当然差分信号的缺点也是显而易 见的,一是差分信号使用两根信号传送一位数据;二是差分信号的布线相对严格一些。

PCIe 链路可以由多条Lane 组成,目前PCIe 链路可以支持1、2. 4. 8、12、16和32个Lane, 即X1、X2、X4、X8、X12. X16和X32宽皮的PCIe 链路。

每一个Lane 上使用的总线 频率与PCIe 总线使用的版本相关。

第1个PCIe 总线规范为,之后依次为… 和。

目前PCIe 总线的置新规范为,而正在开发过 程中,预计在2010年发布。

不同的PCIe 总线规范所定义的总线频率和链路编码方式并不相 同,如表4T 所示。

如上表所示,不同的PCIe总线规范使用的总线频率并不相同,其使用的数据编码方式也不相同oPCIe 总线和规范在物理层中使用8/1 Ob编码,即在PCIe链路上的10 bit中含有8bit 的有效数据;而規范使用128/130b编码方式,即在PCIe链路上的130 bit中含有128 bit 的有效数扌松。

由上表所示,规范使用的总线频率虽然只有4GHz,但是其有效带宽是的两倍。

下文将以规范为例,说明不同宽度PCIe链路所能提供的峰值带宽,如表4-2所示。

由上表所示,X32的PCIe链路可以提供160GT/S的链路带宽,远爲于PCI/PCI-X总线所能提供的峰值带宽。

而即将推出的PCIe规范使用4GHz的总线频率,将进一步提高PCIe链路的峰值带宽。

在PCIe总线中,使用GT (Gigatransfer)计算PCIe链路的峰值带宽。

GT是在PCIe链路上传递的峰值带宽,其计算公式为总线频率X数据位宽X2。

在PCIe总线中,影响有效带宽的因素有很多,因而其有效带宽较难计算。

尽管如此,PCIe 总线提供的有效带宽还是远商于PCI总线。

PCIe总线也有其弱点,其中最究出的问题是传送延时。

IPCIe链路使用串行方式进行数据传送,然而在芯片内部,数据总线仍然是并行的,因此PCIe 链路接口需要进行串并转换,这种串并转换將产生较大的延时。

除此之外PCIe总线的数拡报文需要经过事务层、数据链路层和物理层,这些数据报文在穿越这些层次时,也舟带来延时。

在基于PCIe总线的设备中,X1的PCIe链路灵为常见,而X12的PCIe链路极少出现,X4 和X8的PCIe 设备也不多见。

Intel通常在ICH中集成了多个X1的PCIe链路用来连接低速外设,而在MCH中集成了一个X16的PCIe链路用于连接显卡控制器。

而PowerPC处理器通常能够支持X8、X4、X2和X1的PCIe 链路。

PCIe总线物理链路间的数据传送使用基于吋钟的同步传送机制,但是在物理链路上并没有吋钟线,PCIe 总线的接收端含有吋钟恢复模块CDR(Clock Data Recovery), CDR将从接收报文中提取接收时钟,从而进行同步数据传递。

值得注意的是,在一个PCIe设备中除了需要从报文中提取时钟外,还使用了REFCLK+和REFCLK-信号对作为本地参考时钟,这个信号对的描述见下文。

PCIe总线使用的信号PCIe设备使用两种电源信号供电,分别是Vcc与Vaux,其额定电压为。

其中Vcc为主电源,PCIe设备使用的主要逻辑模块均使用Vcc供电,而一些与电源管理相关的逻辑使用Vaux供电。

在PCIe设备中,一些特殊的寄存器通常使用Vaux供电,如Sticky Register,此时即使PCIe设备的Vcc被移除,这些与电源管理相关的逻辑状态和这些特殊寄存器的内容也不会发生改变。

在PCIe总线中,使用Vaux的主要原因是为了降低功耗和缩短系统恢复时间。

因为Vaux在多数情况下并不会被移除.因此当PCIe设备的Vcc恢复后•该设备不用重新恢复使用Vaux 供电的逻辑,从而设备可以很快地恢复到正常工作状状态。

PCIe链路的置大宽度为X32,但是在实际应用中,X32的链路宽度极少使用。

在一个处理器系统中,一般提供X16的PCIe插槽,并使用PETpO~15、PETnO^15和PERp(Tl5、PER--]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]nO~15 共64 根信号线组成32对差分信号,其中16对PETxx信号用于发送链路,另外16对PERxx信号用于接收链路。

除此之外PCIe 总线还使用了下列辅助信号。

1 PERST# 信号该信号为全局复位信号,由处理器系统提供,处理器系统需要为PCIe插槽和PCIe设备提供该复位信号。

PCIe设备使用该信号复位内部逻辑。

当该信号有效时,PCIe设备将进行复位操作。

PCIe总线定艾了多种复位方式,其中Cold Reset和Warm Reset这两种复位方式的实现与该信号有关,详见第节。

2 REFCLK+和REFCLK-信号在一个处理器系统中,可能含有许多PCIe设备,这些设备可以作为Add-1n卡与PCIe插槽连接,也可以作为内置模块,与处理器系统提供的PCIe链路直接相连,而不需要经过PCIe 插槽。

PCIe设备与PCIe 插槽都具有REFCLK+和REFCLK-信号,其中PCIe插槽使用这组信号与处理器系统同步。

在一个处理器系统中,通常釆用专用逻辑向PCIe插槽提供REFCLK+和REFCLK-信号,如图4-2所示。

其中100Mhz的吋钟源由晶振提供.并经过一个“一推多”的差分时钟驱动器生成多个同相位的时钟源,与PCIe插槽一一对应连接。

图42参考时钟与PCIe插橹的连接PCIe插槽需要使用参考时钟,其频率范围为100MHz±300ppm o处理器系统需要为每一个PCIe 插槽.MCH、ICH和Switch提供参考时钟。

而且要求在一个处理器系统中,时钟驱动器产生的参考时钟信号到每一个PCIe插槽(MCH、ICH和Swith)的距离差在15英寸之内。

通常信号的传播速度接近光速,约为6英寸/ns,由此可见,不同PCIe插槽间REFCLK+和REFCLK-信号的传送延时差约为。

当PCIe设备作为Add-In卡连接在PCIe插槽时,可以直接使用PCIe插槽提供的REFCLK+和REFCLK-信号,也可以使用独立的参考时钟,只要这个参考时钟在100MHz±300ppm范国内即可。

内置的PCIe设备与Add-In卡在处理REFCLK+和REFCLK-信号时使用的方法类似,但是PCIe设备可以使用独立的参考时钟.而不使用REFCLK+和REFCLK-信号。

在PCI e设备配置空间的Link Contro I Reg i ster 中,含有一个“Commo n Clock Configuration" 位。

当该位为1时,表示该设备与PCIe链路的对端设备使用“同相位”的参考时钟;如果为0,表示该设备与PCIe链路的对端设备使用的参考时钟是异步的。

在PCIe设备中,a Common Clock Configuration ”位的缺省值为0,此时PCIe设备使用的参考时钟与对端设备没有任何联系,PCIe链路两端设备使用的参考时钟可以异步设置。

这个异步时钟设置方法对于使用PCIe链路进行远程连接时尤为重要。

在一个处理器系统中,如果使用PCIe链路进行机箱到机箱间的互连,因为参考时钟可以异步设置,机箱到机箱之间进行数据传送时仅需要差分信号线即可,而不需要参考时钟,从而极大降低了连接难度。

3 WAKE#信号当PCIe设备进入休眠状态,主电源已经停止供电吋,PCIe设备使用该信号向处理器系统提交唤醒请求,使处理器系统重新为该PCIe设备提供主电源Vcc。

在PCIe总线中f WAKE#信号是可选的,因此使用WAKE#信号唤醒PCIe设备的机制也是可选的。